# RX631 Group

# SH7044 to RX631 Microcontroller Migration Guide

R01AN2207EJ0100 Rev.1.00 Sep 30, 2014

### Introduction

This application note describes points requiring special attention, points of difference, etc., that need to be borne in mind when replacing the SH7044 with the RX631 in a user system. For detailed information on each function, refer to the latest version of the User's Manual: Hardware.

### **Target Device**

RX631/RX63N

### Contents

| 1. | CPU Architecture    | 2    |

|----|---------------------|------|

| 2. | On-Chip Functions   | . 30 |

| 3. | Sample Code         | 118  |

| 4. | Reference Documents | 121  |

### 1. CPU Architecture

### 1.1 Registers

The points of difference between the registers of the SH7044 and the RX631 are described below.

### 1.1.1 General-Purpose Registers

The SH7044 and RX631 each have 16 32-bit general-purpose registers. They differ in that the register used as the stack pointer (SP) is different.

- SH7044: R15

- RX631: R0

On the SH7044, R0 is also used as an index register.

| 31       | 0 | 31 | 0      |

|----------|---|----|--------|

| R0*      |   | R  | 0 (SP) |

| R1       |   | R  | :1     |

| R2       |   | R  | 2      |

| R3       |   | R  | 3      |

| R4       |   | R  | 4      |

| R5       |   | R  | 5      |

| R6       |   | R  | 6      |

| R7       |   | R  | 7      |

| R8       |   | R  | 8      |

| R9       |   | R  | 9      |

| R10      |   | R  | 10     |

| R11      |   | R  | 11     |

| R12      |   | R  | 12     |

| R13      |   | R  | 13     |

| R14      |   | R  | 14     |

| R15 (SP) |   | R  | 15     |

Figure 1.1 Differences Between General-Purpose Registers

#### 1.1.2 Control Registers

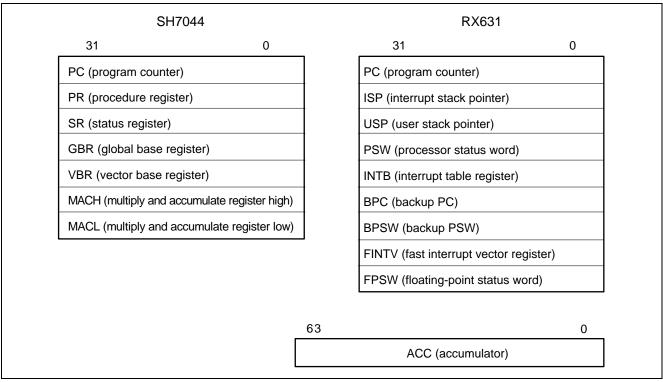

Figure 1.2 shows the points of difference between the control registers of the SH7044 and the RX631.

Figure 1.2 Differences Between Control Registers

The RX631 has no registers corresponding to PR and GBR on the SH7044. The ACC register on the RX631 corresponds to MACH and MACL on the SH7044. An outline of the control registers that are implemented on the RX631 but not on the SH7044 is presented below.

- Interrupt stack pointer/user stack pointer (ISP/USP) There are two types of stack pointer (SP): the interrupt stack pointer (ISP) and the user stack pointer (USP). Switching the stack pointer in use (ISP or USP) is accomplished by means of the stack pointer select bit (U) in the processor status word (PSW) register.

- Interrupt table register (INTB)\* Specifies the start address of the relocatable vector table.

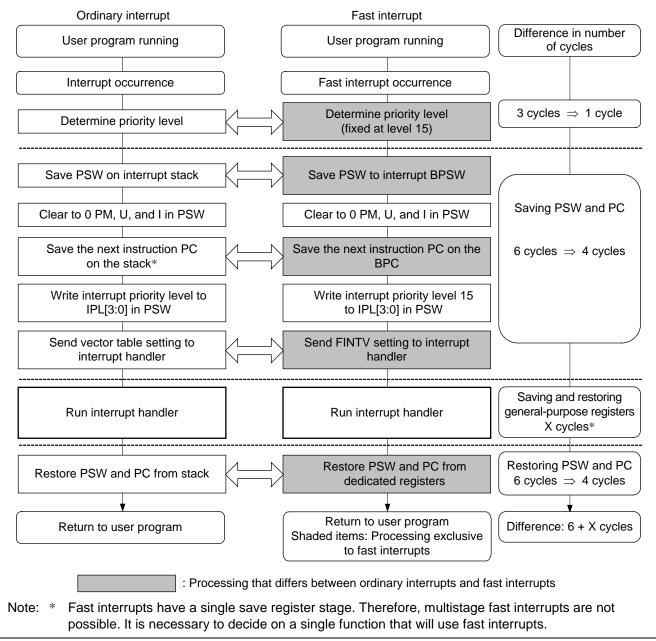

- Backup PC/backup PSW (BPC/BPSW) The RX631 supports fast interrupts in addition to ordinary interrupts. For fast interrupts, the contents of PC and PSW are saved to dedicated registers (BPC and BPSW), thereby reducing the processing time needed to save the register data. Note that BPC and BPSW do not support multiple interrupts at the same time.

- Fast interrupt vector register (FINTV) This register specifies the jump destination when a fast interrupt occurs.

- Floating-point status word (FPSW)

This register indicates the status of the calculation result (floating-point calculation result) generated by the RX631's on-chip FPU.

Note: \* The functionality of this register is equivalent to that of VBR on the SH7044.

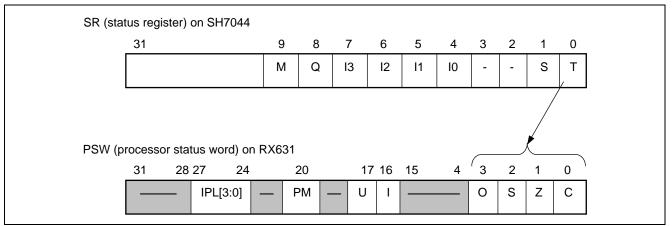

• Differences between status registers

#### Table 1.1 Differences Between SR (SH7044) and PSW (RX631)

| SR Bit Name    | PSW Bit Name | Description                                                                                                                                                                                                                                                                        |

|----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Т              | С            | The calculation result (true/false, carry/borrow, etc.) indicated by the T bit on the                                                                                                                                                                                              |

|                | Z            | SH7044 is shown by four flags (C, Z, S, and O) on the RX631.                                                                                                                                                                                                                       |

|                | S            | C: Carry flag (0/1 = No carry has occurred./A carry has occurred.)                                                                                                                                                                                                                 |

|                | 0            | Z: Zero flag                                                                                                                                                                                                                                                                       |

|                |              | S: Sign flag                                                                                                                                                                                                                                                                       |

|                |              | O: Overflow flag                                                                                                                                                                                                                                                                   |

| S              |              | Controls the functionality that prevents overflows during ALU arithmetic operations performed by the DSP unit of the SH7044.                                                                                                                                                       |

|                |              | On the RX631 there is no bit corresponding to the S bit, and the occurrence of<br>an overflow during a floating-point operation is reported by the FPSW flag. It is<br>also possible to perform exception handling when an overflow occurs.                                        |

| 10, 11, 12, 13 | IPL[3:0]     | These are the interrupt mask bits.                                                                                                                                                                                                                                                 |

| 10, 11, 12, 10 | [0.0]        | Both the SH7044 and the RX631 support level settings from 0 (lowest) to 15 (highest). Only interrupts with a priority level higher than this setting are accepted.                                                                                                                 |

| Q              | _            | The Q bit is used by the DIV0U, DIV0S, and DIV1 instructions on the SH7044.<br>There is no corresponding bit on the RX631.                                                                                                                                                         |

| М              |              | The M bit is used by the DIV0U, DIV0S, and DIV1 instructions on the SH7044.                                                                                                                                                                                                        |

|                |              | There is no corresponding bit on the RX631.                                                                                                                                                                                                                                        |

| _              | I            | Interrupt enable bit                                                                                                                                                                                                                                                               |

|                |              | 0: Interrupts are disabled.                                                                                                                                                                                                                                                        |

|                |              | 1: Interrupts are enabled.                                                                                                                                                                                                                                                         |

|                |              | This bit is used to enable interrupt requests on the RX631. The initial state is 0, so it is necessary to set this bit to 1 in order to accept interrupts. Also, this bit is cleared to 0 when an exception is accepted, and no interrupts are accepted while its value remains 0. |

|                |              | Note that the interrupt status flag of the interrupt controller is reset when an<br>interrupt request occurs, regardless of the setting of this bit.                                                                                                                               |

|                | U            | This bit specifies the stack pointer used by the RX631.                                                                                                                                                                                                                            |

|                |              | 0: Interrupt stack pointer (ISP)                                                                                                                                                                                                                                                   |

|                |              | 1: User stack pointer (USP)                                                                                                                                                                                                                                                        |

|                |              | This bit is cleared to 0 when an exception is accepted.                                                                                                                                                                                                                            |

|                | PM           | This bit specifies the processor mode of the RX631.                                                                                                                                                                                                                                |

|                |              | 0: Supervisor mode                                                                                                                                                                                                                                                                 |

|                |              | 1: User mode                                                                                                                                                                                                                                                                       |

|                |              | This bit is cleared to 0 when an exception is accepted.                                                                                                                                                                                                                            |

### 1.2 Option-Setting Memory

The RX631 is provided with an option-setting memory area containing registers for selecting the microcontroller state after a reset of the endian mode, watchdog timer operation, etc. The option-setting memory is allocated in the ROM, and it cannot be overwritten by a software program. When programming the ROM, it is necessary to program appropriate values in the option-setting memory as well.

### 1.2.1 Outline of Option-Setting Memory

An outline of the option-setting memory area is shown below.

| t                           | 031                                                      | b0                                                                                                                                                    |

|-----------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address                     |                                                          | Register Description                                                                                                                                  |

| FF7F FFE8h to<br>FF7F FFEFh | UB code A                                                | Codes necessary when using user boot mode.                                                                                                            |

| FF7F FFF0h to<br>FF7F FFF7h | UB code B                                                | (Do not overwrite these codes when using USB boot mode.)                                                                                              |

| FF7F FFF8h to<br>FF7F FFFBh | Endian select register B<br>(MDEB)<br>(user boot mode)   | Register for selecting the endian setting of the CPU.                                                                                                 |

|                             | —                                                        | _                                                                                                                                                     |

| FFFF FF80h to<br>FFFF FF83h | Endian select register S<br>(MDES)<br>(single-chip mode) | Register for selecting the endian setting of the CPU.                                                                                                 |

|                             | —                                                        | _                                                                                                                                                     |

|                             |                                                          | The OFS1 register is used to make the following two settings:                                                                                         |

| FFFF FF88h to<br>FFFF FF8Bh | Option function select register 1<br>(OFS1)              | <ul> <li>Voltage monitor 0 reset is enabled/<br/>disabled after a reset.</li> <li>HOCO oscillation is enabled/<br/>disabled after a reset.</li> </ul> |

| FFFF FF8Ch to<br>FFFF FF8Fh | Option function select register 0<br>(OFS0)              | The OFS0 register is used to make<br>settings for the independent watchdog<br>timer (IWDT) and watchdog timer<br>(WDT).                               |

|                             |                                                          |                                                                                                                                                       |

| Figure 1.4 Option-Setting Memory | / Area |

|----------------------------------|--------|

|----------------------------------|--------|

Sample settings for the option-setting memory are shown below.

| Settings for single-chip mode and big-endian */                     |

|---------------------------------------------------------------------|

| defineBIG                                                           |

| pragma address MDEreg=0xffffff80 // MDE register (Single Chip Mode) |

| fdefBIG                                                             |

| const unsigned long MDEreg = 0xffffff8; // big                      |

| else                                                                |

| const unsigned long MDEreg = 0xffffffff; // little                  |

| endif                                                               |

|                                                                     |

#### Figure 1.5 Endian Setting Example

Sample settings for OFS0 and OFS1 are shown below. (The code below is included in the automatically generated files.)

#pragma address OFS1\_REG = 0xFFFFF88 /\* OFS1 register \*/

const unsigned long OFS1\_REG = 0xFFFFFFF;

#pragma address OFS0\_REG = 0xFFFFF8C /\* OFS0 register \*/

const unsigned long OFS0\_REG = 0xFFFFFFFF;

Figure 1.6 OFS0 and OFS1 Setting Example

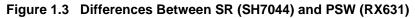

#### 1.2.2 Endian Setting

The SH7044 is fixed in big-endian mode. On the RX631, instructions are fixed in little-endian, and the data order is selectable between little-endian and big-endian. The endian setting is specified by means of the endian select bits (MDE[2:0]) in the MDES and MDEB registers in the option-setting memory.

When switching from the SH7044 to the RX631, it is possible to use big-endian order by specifying big-endian in the option settings of the genuine Renesas compiler. This allows migration without the need to be conscious of endianness in the user program.

The endian setting can be switched for each CS area in the external address space. However, instruction code cannot be allocated to an external space with an endian setting that differs from that of the chip. When allocating instruction code to an external space, ensure that an area with the same endian setting as the chip is used. (For details, see the User's Manual: Hardware.)

In actuality, code such as that shown in figure 1.5, Endian Setting Example, is generated automatically according to the compiler option setting.\*

Figure 1.7 Specifying Endianness by Compiler Option

Note: \* The automatically generated files work in the sample code operating environment described in section 3.1.

### 1.3 Reset Function

#### 1.3.1 Reset Sources

Table 1.2 lists the reset sources of the SH7044 and RX631.

#### Table 1.2Reset Sources

|            | SH7044                                                                           | RX631                                                                                                                                                                                                                                                         |

|------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset type | <ul> <li>Power-on reset (pin reset)</li> <li>Manual reset (pin reset)</li> </ul> | <ul> <li>RES# pin reset</li> <li>Power-on reset (internal reset)</li> <li>Voltage monitor 0 reset</li> <li>Voltage monitor 1 reset</li> <li>Voltage monitor 2 reset</li> <li>Deep software standby reset</li> <li>Independent watchdog timer reset</li> </ul> |

|            |                                                                                  | <ul><li>Watchdog timer reset</li><li>Software reset</li></ul>                                                                                                                                                                                                 |

#### • Reset vector configuration

The SH7044 has separate vectors for power-on resets and for manual resets (PC and SP).\* The RX631 has a single reset vector for multiple reset sources. The reset source is identified in reset status registers 0 to 2 during reset processing, and processing for the corresponding source is performed.

• Stack pointer

On the SH7044, it is necessary to specify the end address (+1) of the stack area in the reset vector. There is no stack pointer setting area in the vector table on the RX631, so the stack pointer is set in ISP and USP.

Note: \* See 1.7.4, Vector Configuration, for details of the vector tables.

|                                                                                                         | SH7044                     |  |           | RX631        |   |  |

|---------------------------------------------------------------------------------------------------------|----------------------------|--|-----------|--------------|---|--|

| H'0000000                                                                                               |                            |  | FFFFFF80h | r            | 7 |  |

| H'0000004         Vector#0 (Power-on reset PC)           H'0000004         Vector#1 (Power-on reset SP) |                            |  | FFFFFOUI  |              |   |  |

| H'0000008                                                                                               | Vector#2 (Manual reset PC) |  |           |              |   |  |

| H'000000C                                                                                               | Vector#3 (Manual reset SP) |  |           |              |   |  |

| H'00003FB                                                                                               |                            |  |           |              |   |  |

|                                                                                                         | Vector#255                 |  | FFFFFFCh  | Reset PC     |   |  |

|                                                                                                         | Vector table               |  |           | Vector table |   |  |

Figure 1.8 Reset Vectors on SH7044 and RX631

#### 1.3.2 Reset Sources and Initialization Scope

The initialization scope of the reset sources differs between the SH7044 and the RX631. Table 1.3 lists the reset types and their initialization scope on the SH7044, and table 1.4 lists the reset types and their initialization scope on the RX631. (For details, see the User's Manual: Hardware.)

#### Table 1.3 SH7044 Reset Sources and Initialization Scope

| Item                       | Power-On Reset | Manual Reset |  |

|----------------------------|----------------|--------------|--|

| CPU                        | 0              | 0            |  |

| On-chip peripheral modules | 0              |              |  |

O: Reset —: No reset

#### Table 1.4 RX631 Reset Sources and Initialization Scope

|                                                               | Reset Sources     |                   |                               |                                        |                            |                               |                               |                                |   |

|---------------------------------------------------------------|-------------------|-------------------|-------------------------------|----------------------------------------|----------------------------|-------------------------------|-------------------------------|--------------------------------|---|

| Reset Target                                                  | Res# Pin<br>Reset | Power-On<br>Reset | Voltage<br>Monitor 0<br>Reset | Independent<br>Watchdog<br>Timer Reset | Watchdog<br>Timer<br>Reset | Voltage<br>Monitor 1<br>Reset | Voltage<br>Monitor 2<br>Reset | Deep Software<br>Standby Reset |   |

| Power-on reset detection flag                                 | 0                 | —                 | —                             | —                                      | —                          | _                             | —                             | —                              | _ |

| Cold start/warm start determination flag                      | —                 | 0                 | —                             | _                                      | —                          | —                             | —                             | _                              | — |

| Voltage monitor 0 reset detection flag                        | 0                 | 0                 | _                             | _                                      | _                          | _                             | _                             | _                              | _ |

| Independent watchdog<br>timer reset detection<br>flag         | 0                 | 0                 | 0                             | _                                      | _                          | _                             | _                             | 0                              | _ |

| Independent watchdog timer registers                          | 0                 | 0                 | 0                             | _                                      | _                          | _                             | _                             | 0                              | _ |

| Watchdog timer reset detection flag                           | 0                 | 0                 | 0                             | 0                                      | _                          | _                             | _                             | 0                              | _ |

| Watchdog timer registers                                      | 0                 | 0                 | 0                             | 0                                      | _                          | _                             | _                             | 0                              | _ |

| Voltage monitor 1 reset detection flag                        | 0                 | 0                 | 0                             | 0                                      | 0                          | _                             | _                             | _                              | _ |

| Voltage monitor<br>function 1 registers                       | 0                 | 0                 | 0                             | 0                                      | 0                          | _                             | _                             | * <sup>1</sup>                 | _ |

| Voltage monitor 2 reset detection flag                        | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | _                             | _                              | _ |

| Voltage monitor<br>function 2 registers                       | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | _                             | *2                             | _ |

| Deep software standby reset detection flag                    | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | _                              | _ |

| Software reset detection flag                                 | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | 0                              | _ |

| Realtime clock registers                                      | _                 | _                 | _                             | _                                      | _                          | _                             | _                             | _                              | _ |

| High-speed on-chip<br>oscillator–related<br>registers         | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | _                              | 0 |

| Main clock oscillator-<br>related registers                   | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | _                              | 0 |

| Pin states                                                    | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | _                              | 0 |

| Low power<br>consumption-related<br>registers                 | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | _                              | 0 |

| Registers other than<br>the above, CPU, and<br>internal state | 0                 | 0                 | 0                             | 0                                      | 0                          | 0                             | 0                             | 0                              | 0 |

|                                                               |                   |                   |                               |                                        |                            |                               |                               |                                |   |

O: Reset ---: No change

Notes: 1. Only LVD1CR1 and LVD1SR are initialized.

2. Only LVD1CR2 and LVD2SR are initialized.

### 1.4 Clock Settings

#### 1.4.1 Clock Sources

The clock sources and clock generation circuits of the SH7044 and RX631 are listed below.

#### Table 1.5 List of SH7044 and RX631 Clock Sources

| SH7044                                         | RX631                                                      |

|------------------------------------------------|------------------------------------------------------------|

| Oscillator (EXTAL and XTAL) + PLL circuit      | Main clock oscillator (EXTAL and XTAL) + PLL circuit       |

|                                                | <ul> <li>Subclock oscillator (XCIN and XCOUT)</li> </ul>   |

|                                                | <ul> <li>High-speed on-chip oscillator (HOCO)</li> </ul>   |

|                                                | <ul> <li>Low-speed on-chip oscillator (LOCO)</li> </ul>    |

|                                                | <ul> <li>IWDT-dedicated on-chip oscillator</li> </ul>      |

| Note: In the description below, the high-speed | on-chip oscillator is referred to as the HOCO and the low- |

Note: In the description below, the high-speed on-chip oscillator is referred to as the HOCO and the lowspeed on-chip oscillator as the LOCO.

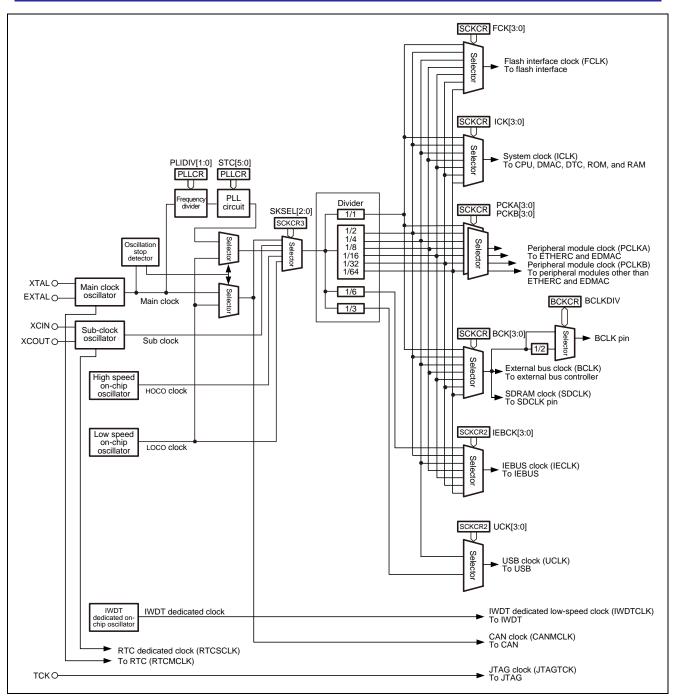

#### 1.4.2 Clock Generation Circuit

On the SH7044 clock control is not performed in software. Each peripheral device operations in synchronization with the system clock ( $\phi$ ) or a clock generated by the prescaler. On the RX631 a large variety of clocks operate under software control.

On the RX631 the LOCO operates as the clock source after a reset. The operation of necessary clock sources and PLL circuits other than the LOCO is started during system initialization, and various clocks are selected, such as the system clock and bus clocks. When making changes to clock-related settings, it is necessary to consider the register setting sequence and the oscillation and clock oscillation stabilization time.

See the following application note for details of the clock setting procedure.

RX63N Group, RX631 Group Initial Setting (R01AN1245EJ)

Figure 1.9 RX631 Clock Generation Circuit

### 1.5 **Operation Modes**

### 1.5.1 Comparison of Operation Modes

The table below shows a comparison of the operation modes of the SH7044 and RX631. For details of each operation mode, see the User's Manual: Hardware.

| Table 1.6 | Comparison | of Operation | Modes |

|-----------|------------|--------------|-------|

|-----------|------------|--------------|-------|

| SH7044<br>Operation Mode | RX631<br>Operation Mode                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCU mode 0<br>MCU mode 1 | On-chip ROM disabled<br>extended mode                                                          | An operation mode in which the on-chip ROM is disabled<br>and the external address space is enabled. The external<br>bus width differs from that of mode 0 and mode 1 on the<br>SH7044.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MCU mode 2               | On-chip ROM enabled<br>extended mode                                                           | An operation mode in which the on-chip ROM is enabled and the external address space is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Single-chip mode         | Single-chip mode                                                                               | An operation mode in which the on-chip ROM is enabled and the external address space is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Boot mode                | Boot mode                                                                                      | An operation mode in which the on-chip flash memory<br>modifying program (boot program), which is stored in a<br>dedicated area internal to the microcontroller, is run. The<br>on-chip flash memory can be programmed by a device<br>external to the microcontroller by using the asynchronous<br>serial interface.                                                                                                                                                                                                                                                                                      |

| User program mode        | Functionality equivalent<br>to the SH7044 can be<br>implemented in ordinary<br>operation mode. | An operation mode that is only transitioned to when the setting value of the FWP pin changes and in which the on-chip flash memory is programmed by a programming/erase control program that has been prepared ahead of time by the user. It is possible to implement equivalent functionality in ordinary operation mode on the RX631, so it is not necessary to change the pin states.                                                                                                                                                                                                                  |

|                          | USB boot mode /<br>user boot mode                                                              | An operation mode in which the on-chip flash memory<br>modifying program stored in the user boot area is run.<br>When the microcontroller is in the default factory state the<br>mode is USB boot mode, and when a flash memory<br>modifying program created by the user has been stored<br>in the user boot area the mode is user boot mode. It is<br>possible to use a user-defined interface to select between<br>the USB and user modes and program the on-chip flash<br>memory with a device external to the microcontroller.<br>Programming of the user boot area is only possible in<br>boot mode. |

### 1.5.2 Comparison of Memory

The figure below shows a comparison of memory maps in on-chip ROM enabled mode (on-chip ROM enabled extended mode on the RX631).

| SH7044 on-chip ROM enabled mode |                            | mode R     | X631 on-chip ROM enabled extended mode                      |  |

|---------------------------------|----------------------------|------------|-------------------------------------------------------------|--|

| 0000 0000h                      | On-chip ROM                | 0000 0000h | RAM                                                         |  |

| 0004 0000h                      |                            | 0004 0000h | Reserved area                                               |  |

|                                 |                            | 0008 0000h | Peripheral I/O registers                                    |  |

|                                 | Reserved area              | 0010 0000h | On-chip ROM<br>(E2 data flash)                              |  |

|                                 |                            | 0010 8000h | Reserved area                                               |  |

|                                 |                            | 007F 8000h | FCU-RAM area                                                |  |

|                                 |                            | 007F A000h | Reserved area                                               |  |

| 0020 0000h                      | CS0 area                   | 007F C000h | Peripheral I/O registers                                    |  |

| 0040 0000                       |                            | 007F C500h | Reserved area                                               |  |

| 0040 0000h                      | CS1 area                   | 007F FC00h | Peripheral I/O registers                                    |  |

| 0000 0000                       |                            | 0080 0000h | Reserved area                                               |  |

| 0080 0000h                      | CS2 area                   | 00E0 0000h | On-chip ROM<br>(program ROM)<br>(dedicated for programming) |  |

| 00C0 0000h                      | CS3 area                   | 0100 0000h | External address space<br>(CS area)                         |  |

| 0100 0000h                      | DRAM area                  | 0800 0000h | External address space<br>(SDRAM area)                      |  |

| 0200 0000h                      | Reserved area              | 1000 0000h | Reserved area                                               |  |

| FFFF 8000h                      | On-chip peripheral modules | FEFF E000h | On-chip ROM<br>(FCU firmware)<br>(read-only)                |  |

| FFFF 8800h                      |                            | FF00 0000h | Reserved area                                               |  |

|                                 | Reserved area              | FF7F C000h | On-chip ROM (user boot)<br>(read-only)                      |  |

|                                 |                            | FF80 0000h | Reserved area                                               |  |

| FFFF 0000h                      | On-chip RAM                | FFE0 0000h | On-chip ROM<br>(program ROM)                                |  |

| FFFF FFFFh                      |                            | FFFF FFFFh | (read-only)                                                 |  |

Figure 1.10 SH7044 and RX631 Memory Map Comparison (On-Chip ROM Enabled Mode)

The figure below shows a comparison of memory maps in single-chip mode.

|              | Single-chip mode (SH7044)  |              | Single-chip mode (RX631)                                    |

|--------------|----------------------------|--------------|-------------------------------------------------------------|

| 0000 0000h   |                            | 0000 0000h   | RAM                                                         |

| 0004 0000h   | On-chip ROM                | 0004 0000h   | Reserved area                                               |

|              |                            | 0008 0000h   | Peripheral I/O registers                                    |

|              |                            | 0010 0000h   | On-chip ROM<br>(E2 data flash)                              |

|              |                            | 0010 8000h   | Reserved area                                               |

|              |                            | 007F 8000h   | FCU-RAM area                                                |

|              |                            | 007F A000h   | Reserved area                                               |

|              |                            | 007F C000h   | Peripheral I/O registers                                    |

|              |                            | 007F C500h   | Reserved area                                               |

|              | Reserved area              | 007F FC00h   | Peripheral I/O registers                                    |

|              |                            | 0080 0000h   | Reserved area                                               |

|              |                            | 00E0 0000h   | On-chip ROM<br>(program ROM)<br>(dedicated for programming) |

|              |                            | 0100 0000h - | Reserved area                                               |

|              |                            | FEFF E000h   | On-chip ROM (FCU firmware)<br>(read-only)                   |

|              |                            | FF00 0000h - | Reserved area                                               |

|              |                            | FF7F C000h   | On-chip ROM (user boot)<br>(read-only)                      |

|              |                            | FF80 0000h   | Reserved area                                               |

| FFFF 8000h   |                            | FFE0 0000h   |                                                             |

| FFFF 8800h   | On-chip peripheral modules |              | On this DOM                                                 |

|              | Reserved area              |              | On-chip ROM<br>(program ROM)<br>(read-only)                 |

| FFFF 0000h   | On-chip RAM                |              |                                                             |

| FFFF FFFFh [ | •                          | FFFF FFFFh L |                                                             |

Figure 1.11 SH7044 and RX631 Memory Map Comparison (Single-Chip Mode)

|            | On-chip ROM disabled mode<br>(SH7044) |            | On-chip ROM disabled mode<br>(RX631)   |

|------------|---------------------------------------|------------|----------------------------------------|

| 0000 0000h |                                       | 0000 0000h | RAM                                    |

|            |                                       | 0004 0000h | Reserved area                          |

|            | CS0 space                             | 0008 0000h | Peripheral I/O registers               |

| 0040 0000h | CS1 space                             | 0010 0000h |                                        |

| 0080 0000h | CS2 space                             |            | Reserved area                          |

| 00C0 0000h | CS3 space                             |            |                                        |

| 0100 0000h | DRAM space                            | 0100 0000h | External address space<br>(CS area)    |

| 0200 0000h |                                       | 0800 0000h | External address space<br>(SDRAM area) |

|            | Reserved area                         | 1000 0000h | Reserved area                          |

| FFFF 8000h |                                       | FF00 0000h |                                        |

|            | On-chip peripheral modules            |            |                                        |

| FFFF 8800h | Reserved area                         |            | External address space                 |

| FFFF F000h |                                       |            |                                        |

| FFFF FFFFh | On-chip RAM                           | FFFF FFFFh |                                        |

The figure below shows a comparison of memory maps in on-chip ROM disabled mode.

Figure 1.12 SH7044 and RX631 Memory Map Comparison (On-Chip ROM Disabled Mode)

- On the RX631 the RAM is allocated to addresses adjacent to 0000 0000h and ROM (for reading data) to addresses adjacent to FFFF FFFFh. Also, the RX631 has on-chip E2 data flash for storing data.

- On the RX631 the peripheral IO registers are allocated within the address range from 0008 0000h to 000F FFFFh, and only the flash-related registers and peripheral clock notification register are allocated within the address range from 007F C000h to 007F FFFFh.

- On the RX631 the external address space is allocated within the address range from 0100 0000h to 0FFF FFFFh and configured as seven CS spaces of 16 MB each and a 128 MB SDRAM space.

### 1.5.3 Operation Mode Settings

Whereas on the SH7044 operation mode settings are made only with the MD1, MD0, and FWP pins, on the RX631 operation mode settings can be made by means of the MD pin and PC7 or PA6 pin when a reset is canceled, or by software after a reset is canceled.

Table 1.7 lists the operation modes that are determined by pin settings, and table 1.8 lists the operation modes that are set in software after a reset is canceled.

#### Table 1.7 Pin Settings and Operation Modes on RX631

Pin

| MD | PC7* <sup>2</sup> , PA6* <sup>2</sup> | Mode Name                                    |

|----|---------------------------------------|----------------------------------------------|

| 1  |                                       | Single-chip mode                             |

| 0  | 0                                     | Boot mode                                    |

|    | 1                                     | USB boot mode / user boot mode* <sup>1</sup> |

Notes: 1. When the microcontroller is in the default factory state the USB boot program is stored in the user boot area and the microcontroller starts in USB boot mode.

2. The pin differs according to the package type. For details, see the User's Manual: Hardware.

#### Table 1.8 SYSCR0 Register Settings and Operation Modes on RX631

#### SYSCR0 Register

| ROME Bit* <sup>1</sup>        | EXBE Bit                                | Mode Name                          |

|-------------------------------|-----------------------------------------|------------------------------------|

| 0 (ROM disabled)              | 0 (external bus disabled)               | Single-chip mode                   |

| 1 (ROM enabled)* <sup>2</sup> | 0 (external bus disabled)* <sup>2</sup> | User boot mode)                    |

| 0 (ROM disabled)              | 1 (external bus enabled)                | On-chip ROM disabled extended mode |

| 1 (ROM enabled)               | 1 (external bus enabled)                | On-chip ROM enabled extended mode  |

|                               |                                         |                                    |

Notes: 1. Once the ROME bit is cleared to 0 it cannot be set to 1 again.

2. After the STSCR0 register is reset, ROME = 1 and EXBE = 0.

### 1.6 **Processor Modes**

The RX CPU supports two processing modes: supervisor mode and user mode. These processor modes enable hierarchical CPU resource protection.

This makes it possible, when replacing the SH7044 with the RX631, to replace the software by operating in supervisor mode only, without using user mode. In other words, software can be replaced without the need to be conscious of the processor mode.

#### Table 1.9 Processor Modes

| Processor Modes | Transition Conditions                                                                                                                                                                                                                                                    | Outline                                                                                                                                                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supervisor mode | <ul> <li>Reset cancellation</li> <li>Exception occurrence<br/>(PSW.PM bit cleared to 0)</li> </ul>                                                                                                                                                                       | All CPU resources are accessible, and all<br>instructions can be executed (no limitations).<br>This is the mode in which the OS and other<br>system programs ordinarily operate.                                                                     |

| User mode       | <ul> <li>PSW.PM bit set to 1</li> <li>In this case, first set to 1 the<br/>PSW.PM bit saved to the stack, then<br/>execute the RTE instruction.</li> <li>Alternately, first set to 1 the PSW.PM<br/>bit saved to BPSW, then execute the<br/>RTFI instruction.</li> </ul> | Write access to some CPU resources, such<br>as some bits in PSW and to BPC and<br>BPSW, is restricted, and privileged<br>instructions cannot be used. This is the<br>mode in which user programs such as<br>application programs ordinarily operate. |

#### Transitioning from supervisor mode to user mode

| MVFC   | PSW,R1        | ; The RTE instruction is used to simulate return from an exception. |

|--------|---------------|---------------------------------------------------------------------|

| OR     | #00100000h,R1 | ;                                                                   |

| PUSH.L | R1            | ;                                                                   |

| MVFC   | PC,R1         | · · ·                                                               |

| ADD    | #10,R1        | · · · ·                                                             |

| PUSH.L | R1            | ;                                                                   |

| RTE    |               |                                                                     |

| NOP    |               |                                                                     |

| NOP    |               |                                                                     |

|        |               |                                                                     |

#### Transitioning from user mode to supervisor mode

Operation transitions to supervisor mode when exception handling occurs. Operation then transitions again to user mode after the return from exception handling.

Another way to cause a transition to supervisor mode is to use an instruction that generates an unconditional trap, such as the INT instruction or BRK instruction.

(TRAPA instruction)

Illegal slot instruction

General illegal

instruction

sources with dedicated vectors and up to 256 sources

when sources also used for interrupts are included.

The SH7044 has no exceptions corresponding to the privileged instruction exception or floating-point

On the SH7044 the next instruction is saved to PC when

instruction that generated this exception is saved to PC.

one of these exceptions occurs, but on the RX631 the

#### 1.7 **Exception Handling**

The points of difference regarding exception handling in general on the SH7044 and RX631, including interrupts, are described below.

#### 1.7.1 Types of Exception Handling

A comparative listing of exception sources on the SH7044 and RX631 is shown below.

| SH7044              | RX631                  | Main Points of Difference                                             |

|---------------------|------------------------|-----------------------------------------------------------------------|

| Power-on reset      | Reset                  | On the SH7044 there are separate vectors for power-on                 |

| Manual reset        |                        | resets and manual resets.                                             |

|                     |                        | On the RX631 there is a single reset vector. The reset                |

|                     |                        | source is identified in reset status registers 0 to 2 during          |

|                     |                        | reset interrupt handling, and appropriate processing is<br>performed. |

| Address error       | Access exception       | On the SH7044 this exception occurs when an attempt is                |

|                     | ·                      | made to access an access-prohibited area or an address                |

|                     |                        | to which access is prohibited.                                        |

|                     |                        | On the RX631 this exception occurs when a memory                      |

|                     |                        | protection error occurs.                                              |

|                     |                        | On the SH7044 the next instruction is saved to PC when                |

|                     |                        | this exception occurs.                                                |

|                     |                        | On the RX631 the instruction that generated this                      |

|                     |                        | exception is saved to PC.                                             |

| Interrupt (NMI)     | Non-maskable interrupt | None                                                                  |

| Interrupt           | Interrupt              | The RX631 also supports fast interrupts (level 15)                    |

| (external/internal) | (external/internal)    |                                                                       |

| TRAP instruction    | Unconditional trap     | The SH7044 has 32 sources, but the RX631 has 16                       |

(INT, BRK instruction)

Undefined instruction

Privileged instruction

Floating-point exception

#### Table 1.10 Exception Sources on SH7044 and RX631

exception.

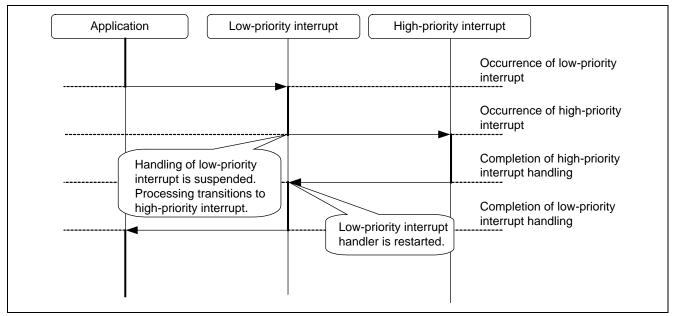

### 1.7.2 Exception Handling Priority

The comparative priority of exception sources on the SH7044 and RX631 is shown below.

| Table 1.11 Exception Event Priority | able 1.11 Exceptio | n Event Priority |  |

|-------------------------------------|--------------------|------------------|--|

|-------------------------------------|--------------------|------------------|--|

| SH7044                                | RX631                                                                                                                                                                      | Remarks                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset                        | Reset                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |

| Manual reset                          | Non-maskable interrupt                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                      |

| Address error exception               | Interrupt (external/internal)                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt (NMI)                       | Instruction access exception                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt (external/internal)         | Undefined instruction exception, privileged instruction exception                                                                                                          |                                                                                                                                                                                                                                                                                                                                                      |

| TRAP instruction                      | Unconditional trap                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                      |

| General illegal instruction exception | Operand access exception                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                      |

| Illegal slot instruction exception    | Floating-point exception                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                      |

|                                       | Power-on reset<br>Manual reset<br>Address error exception<br>Interrupt (NMI)<br>Interrupt (external/internal)<br>TRAP instruction<br>General illegal instruction exception | Power-on resetResetManual resetNon-maskable interruptAddress error exceptionInterrupt (external/internal)Interrupt (NMI)Instruction access exceptionInterrupt (external/internal)Undefined instruction exception,<br>privileged instruction exceptionTRAP instructionUnconditional trapGeneral illegal instruction exceptionOperand access exception |

Note: Among interrupts, the priority is determined by the interrupt controller.

On the SH7044 address errors have higher priority than interrupts (internal or external), but on the RX631 both instruction access exceptions and operand access exceptions have lower priority than interrupts.

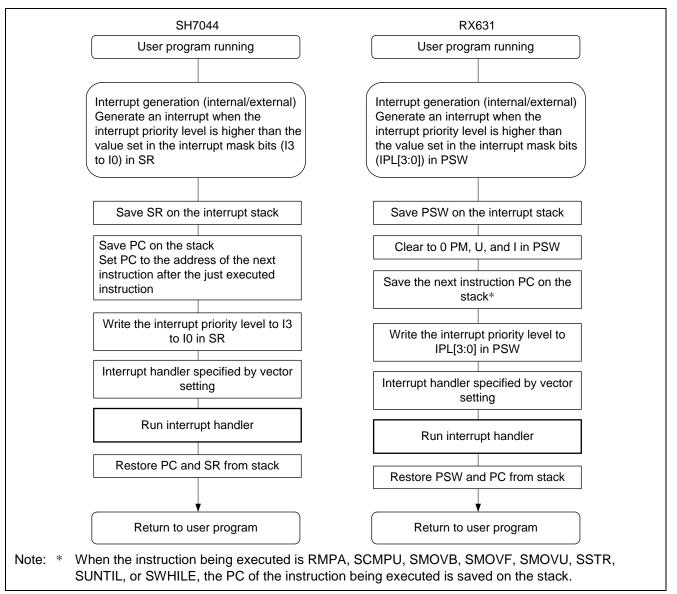

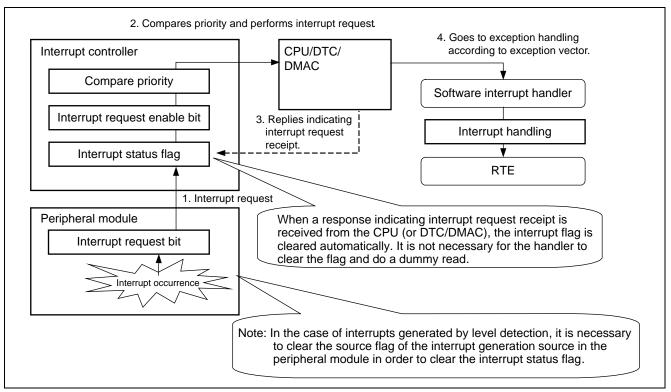

### 1.7.3 Basic Processing Sequence of Exception Handling

The basic processing sequence interrupt exception handling on the SH7044 and RX631 is shown below.

Figure 1.13 Interrupt (Internal/External) Processing Sequence

#### 1.7.4 Vector Configuration

Both the SH7044 and RX631 have a relocatable vector configuration, which allows the vector table to be reallocated. On the SH7044 the vector base register (VBR) specifies the start of the vector table. (Note that VBR is initialized to 0 after a reset, so it is not possible to change the reset vector.)

On the RX631 there are clearly separated fixed relocatable vector tables. System exceptions such as resets are assigned a fixed vector that cannot be reallocated. Reallocatable interrupt and unconditional trap vectors are assigned in a relocatable vector table, and the start address of the relocatable vector table is set in the interrupt table register (INTB). Also, the fast interrupt vector is set in the FINTV register.

SH7044 RX631 INTB VBR Vector base register Interrupt table register H'0000000 Vector #0 (power-on reset PC) Vector #0 H'0000004 Vector #1 (power-on reset SP) H'0000008 Vector #2 (manual reset PC) H'000000C Vector #3 (manual reset SP) Vector #255 Relocatable vector table FFFFFF80h H'00003FB FFFFFFCh Reset PC Vector #255 Vector table Fixed vector table

Figure 1.14 shows the differences between the vector tables.

Figure 1.14 Vector Table Settings

### 1.7.5 Interrupt Masking by SR (SH7044) and PSW (RX631)

On the RX631 the I bits in control register PSW are used to set the interrupt mask level. The I bits indicate which interrupts are enabled and which are disabled.

#### Table 1.12 Interrupt-Related Bits in SR and PSW

| SH7044         | RX631        |                                                                                                                                                                                                                                                                                               |

|----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR Register    | PSW Register | <br>Description                                                                                                                                                                                                                                                                               |

| 10, 11, 12, 13 | IPL[3:0]     | CPU interrupt mask level (priority level)                                                                                                                                                                                                                                                     |

|                |              | Setting value: 0 to Fh (levels 0 to 15)                                                                                                                                                                                                                                                       |

|                |              | When an interrupt request occurs, this level setting is compared<br>with the priority level set for the individual interrupt source, and the<br>interrupt is enabled if its level setting is higher than the mask level.                                                                      |

|                |              | Interrupt enable bit                                                                                                                                                                                                                                                                          |

|                |              | 0: Interrupts are disabled.                                                                                                                                                                                                                                                                   |

|                |              | 1: Interrupts are enabled.                                                                                                                                                                                                                                                                    |

|                |              | When an interrupt occurs, the interrupt status flag in the interrupt controller is set to 1. After a system reset, this bit is set to 1, enabling acceptance of interrupts. When an exception is accepted, this bit is cleared to 0 and no interrupts are accepted while its value remains 0. |

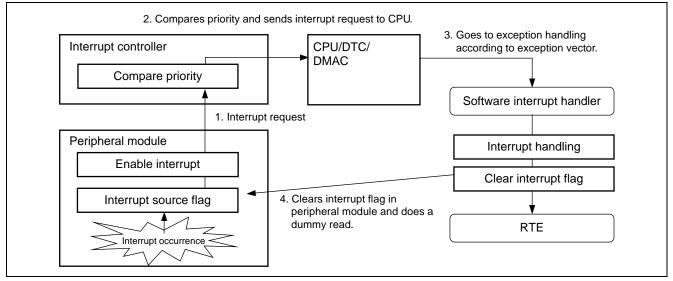

### 1.8 Interrupt Handling

This section describes the differences in interrupt handling between the SH7044 and RX631, with the focus on the interrupt controller.

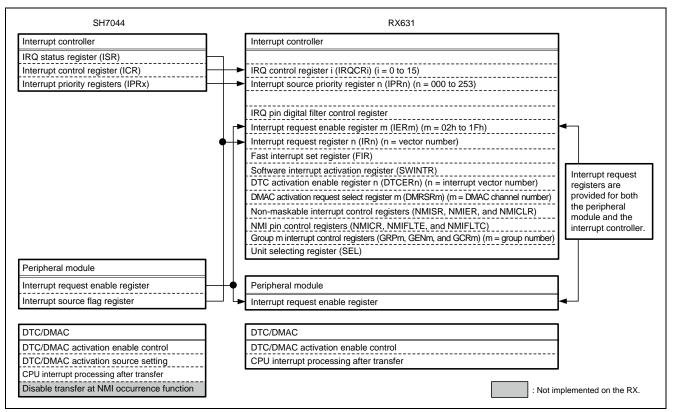

### 1.8.1 Interrupt Controller

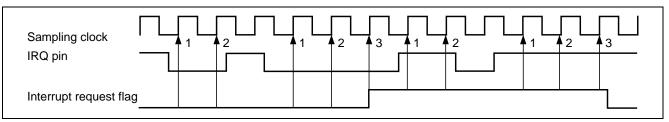

Table 1.13 lists the differences in the interrupt controller specifications.

#### Table 1.13 Comparison of Interrupt Controller Specifications

| ltem                           |                                | SH7044                                                                                                                                                                                                                 | RX631                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupts                     | Peripheral function interrupts | <ul> <li>Interrupts from peripheral modules</li> <li>Interrupt detection:<br/>Edge/level*<sup>1</sup></li> </ul>                                                                                                       | <ul> <li>Interrupts from peripheral<br/>modules</li> <li>Interrupt detection:<br/>Edge/level*<sup>1</sup></li> <li>Group interrupt function<br/>support</li> <li>Unit selection function support</li> </ul>                                                                                                                                                                                               |

|                                | External pin<br>interrupts     | <ul> <li>IRQ0 to IRQ7 pins</li> <li>Sources: 8</li> <li>Interrupt detection: Low level or falling edge can be specified for each source.</li> </ul>                                                                    | <ul> <li>IRQ0 to IRQ15 pins</li> <li>Sources: 16</li> <li>Interrupt detection: Low level, falling edge, rising edge, or both edges can be specified for each source.</li> <li>Digital filter function support</li> </ul>                                                                                                                                                                                  |

|                                | Software interrupts            | None                                                                                                                                                                                                                   | Supported                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                | Interrupt priority             | A level from 0 to Fh can be<br>specified for each source by a<br>register setting.                                                                                                                                     | A level from 0 to Fh can be<br>specified for each source by a<br>register setting.                                                                                                                                                                                                                                                                                                                        |

|                                | Fast interrupt function        | None                                                                                                                                                                                                                   | Supported                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                | DTC and DMAC control           | Activation supported* <sup>2</sup>                                                                                                                                                                                     | Activation supported                                                                                                                                                                                                                                                                                                                                                                                      |

| Non-<br>maskable<br>interrupts | NMI pin interrupts             | <ul> <li>Interrupt detection method<br/>(selection of falling or rising<br/>edge)</li> <li>NMI input level read bit<br/>provided</li> </ul>                                                                            | <ul> <li>Interrupt detection method<br/>(selection of falling or rising<br/>edge)</li> <li>Digital filter function support</li> </ul>                                                                                                                                                                                                                                                                     |

|                                | Other sources                  | <ul> <li>CPU address error</li> <li>DMAC or DTC address error</li> <li>TRAP instruction<br/>(TRAPA instruction)</li> <li>General illegal instruction<br/>(undefined code)</li> <li>Illegal slot instruction</li> </ul> | <ul> <li>Interrupt at oscillation stop<br/>detection</li> <li>WDT underflow or refresh error</li> <li>IWDT underflow or refresh<br/>error</li> <li>Voltage monitor 1 interrupt</li> <li>Voltage monitor 2 interrupt</li> <li>Undefined instruction exception</li> <li>Privileged instruction exception</li> <li>Access exception</li> <li>Floating-point exception</li> <li>Unconditional trap</li> </ul> |

Notes: 1. The detection method is fixed for fixed-connection peripheral modules.

2. On the SH7044 activation source setting is performed on the DTC or DMAC.

Figure 1.15 Differences Between Interrupt Controller Registers

Figure 1.15 shows the differences between the interrupt controllers of the SH7044 and RX631.

The interrupt controller of the SH7044 controls IRQ interrupt flags, while peripheral module interrupt flags are controlled by the peripheral modules.

On the RX631 the interrupt controller controls all interrupt status flags, for both IRQs and peripheral modules.\* In addition, the interrupt controller controls the activation source settings for the DTC and DMAC. The disable transfer at NMI occurrence function of the DTC and DMAC on the SH7044 is not implemented on the RX631.

Note: \* The interrupt controller contains an interrupt request register for each interrupt source, but there are also interrupt enable bits implemented in the peripheral modules. (For details, see the User's Manual: Hardware.)

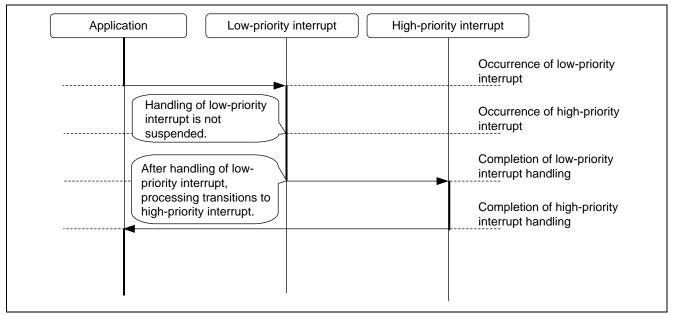

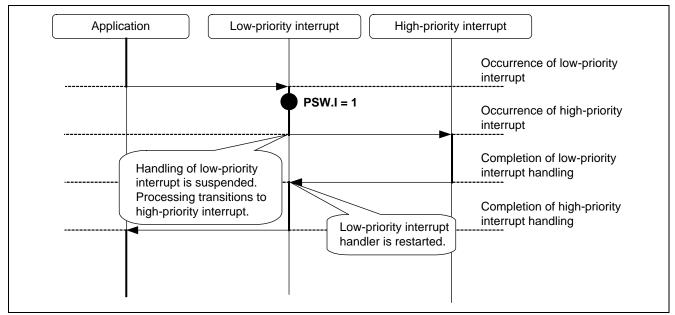

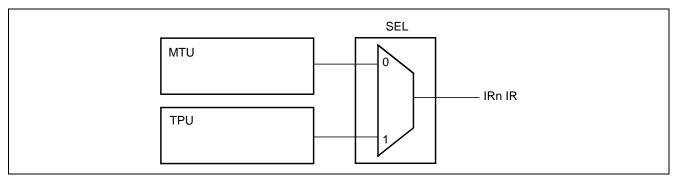

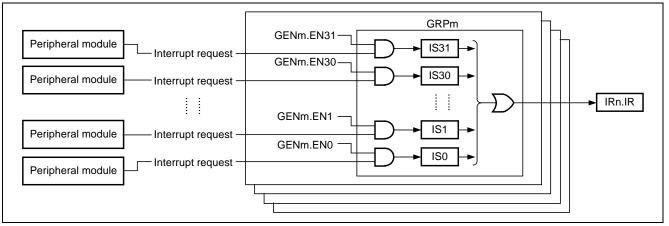

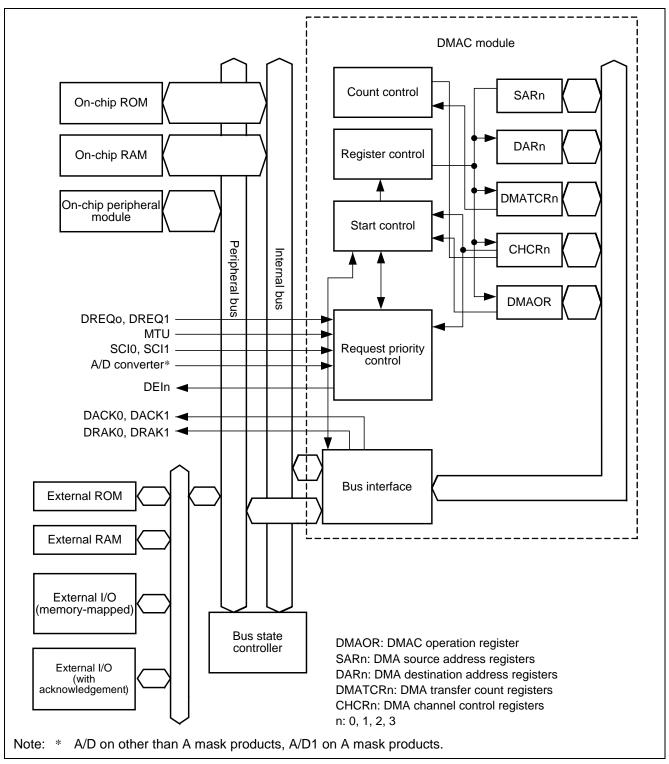

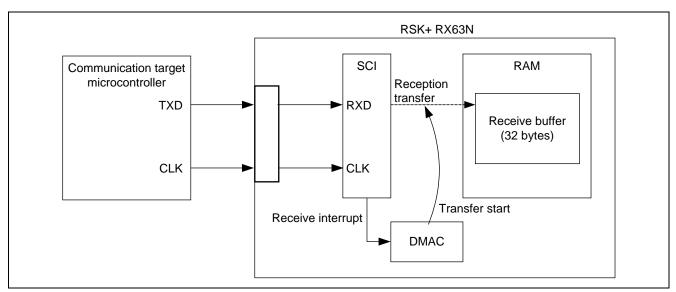

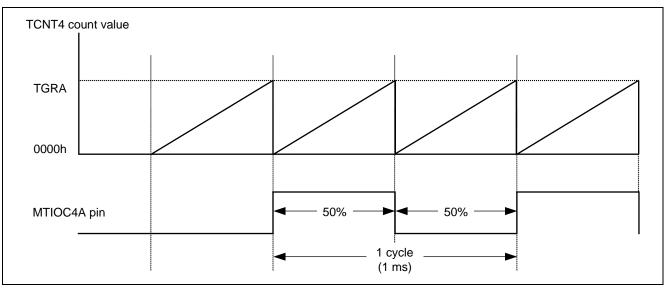

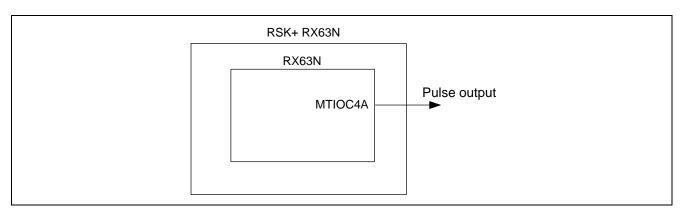

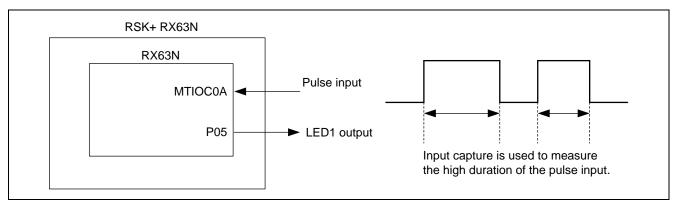

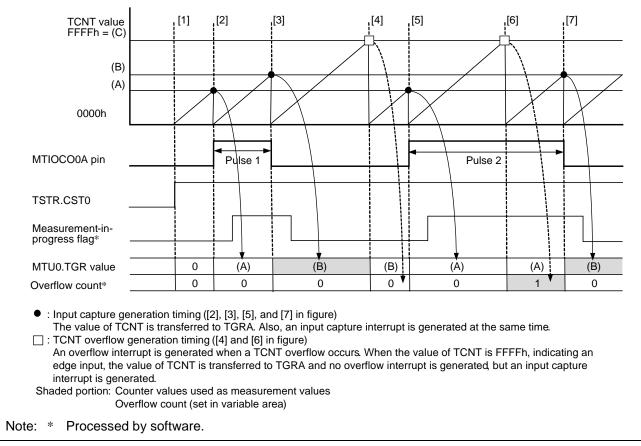

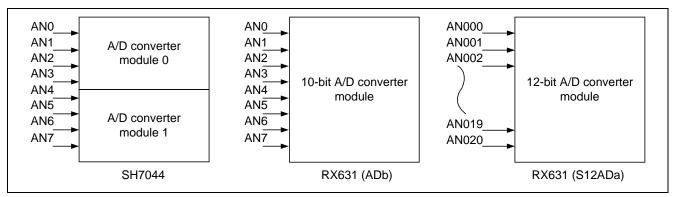

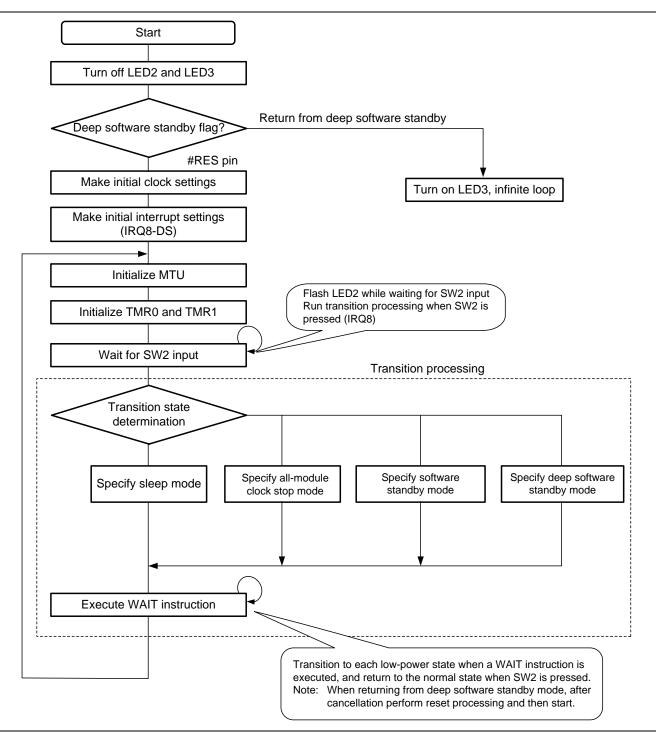

#### 1.8.2 Interrupt Flag Management