# RX62T

MTU3 Phase Counting Mode

R01AN0819ET0100 Rev.1.00 October 1, 2011

# Introduction

The RX62T Group has on-chip multi-function timer pulse unit 3 (MTU3), which comprises eight 16-bit timer channels.

### **Target Device**

RX62T

### Contents

| 1.  | Specification                                               | . 2 |

|-----|-------------------------------------------------------------|-----|

| 2.  | Multi-Function Timer Pulse Unit 3 for Phase Counting Mode   | .4  |

| 2.1 | Example of Phase Counting Mode operation                    | . 4 |

|     | Example of Procedure for Setting Phase Counting Mode        |     |

| 2.3 | Phase Counting Mode Application Example                     | . 5 |

| 3.  | Multi-Function Timer Pulse Unit 3 Software Register Setting | . 6 |

| 4.  | Experimental Result                                         | .7  |

|     | Conclusion                                                  |     |

| Rev | sion Record                                                 | 10  |

| Gen | eral Precautions in the Handling of MPU/MCU Products        | 11  |

### 1. Specification

- Comprises eight 16-bit channels

- Operating frequency is 8 to100 MHz

- [Channels 0 to 4, 6, and 7]

- Waveform output on compare match

- Input capture function

- Counter-clearing operation

- Simultaneous writing to multiple timer counters (TCNT)

- Simultaneous clearing on compare match or input capture

- Simultaneous input and output to registers in synchronization with counter operations

- Up to 12-phase PWM output in combination with synchronous operation

- [Channels 0, 3, 4, 6, and 7]

- Buffer operation specifiable

- [Channels 3, 4, 6, and 7]

- Through interlocked operation of channels 3 and 4 or 6 and 7, output of positive and negative signals in six phases (for a total of 12 phases) in Complementary -PWM and reset-PWM operation

- In Complementary PWM mode, transfer of values from buffer registers to temporary registers on peaks and troughs of the timer-counter values or writing to the buffer registers (MTU3\_4.TGRD and MTU3\_7.TGRD)

- Double-buffering selectable in Complementary PWM mode

- [Channels 3 and 4]

- Through interlocking with channel 0, a mode for driving AC synchronous motors (brushless DC motors) by using Complementary PWM output and reset PWM output is settable and allows the selection of two types of waveform output (chopping or level)

- [Channels 1 and 2]

- Independently specifiable phase-counting mode

- Capable of cascade-connected operation

- [Channel 5]

- Capable of operation as a dead-time compensation counter

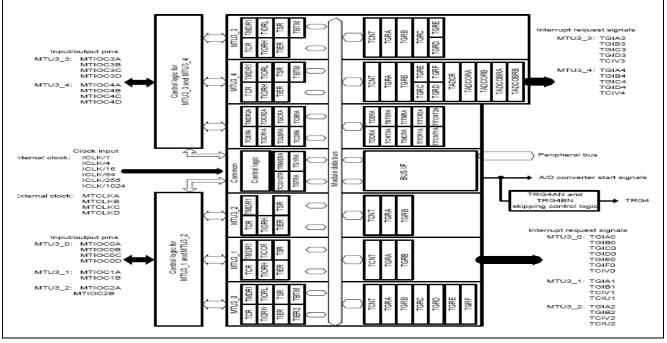

Fig. 1-1 is the block diagram of Multi-Function Timer Pulse Unit 3 (MTU3).

Figure 1-1 Block diagram for MTU3

#### Table 1-1 Specifications of Multi-Function Timer Pulse Unit 3 (MTU3) Register

| TSTR            | Timer start register                                                        |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| TOERA           | Timer output master enable register A                                       |  |  |  |  |  |  |

| TGCRA           | Timer gate control register A                                               |  |  |  |  |  |  |

| TOCR1A          | Timer output control register 1A                                            |  |  |  |  |  |  |

| TOCR2A          | Timer output control register 2A                                            |  |  |  |  |  |  |

| TCDRA           | Timer cycle data register A                                                 |  |  |  |  |  |  |

| TDDRA           | Timer dead time data register A                                             |  |  |  |  |  |  |

| TCNTSA          | Timer subcounter A                                                          |  |  |  |  |  |  |

| TCBRA           | Timer cycle buffer register A                                               |  |  |  |  |  |  |

| TITCR1A         | Timer interrupt skipping set register 1A                                    |  |  |  |  |  |  |

| TITCR2A         | Timer interrupt skipping set register 2A                                    |  |  |  |  |  |  |

| TITCNT1A        | Timer interrupt skipping set register 2/Y                                   |  |  |  |  |  |  |

| TITCNT2A        | Timer interrupt skipping counter 114<br>Timer interrupt skipping counter 2A |  |  |  |  |  |  |

| TBTERA          | Timer buffer transfer set register A                                        |  |  |  |  |  |  |

| TOLBRA          | Timer output level buffer register A                                        |  |  |  |  |  |  |

| TCR             | Timer control register                                                      |  |  |  |  |  |  |

| TMDR1           | Timer mode register 1                                                       |  |  |  |  |  |  |

| TMDR1<br>TMDR2A | Timer mode register 1<br>Timer mode register 2A                             |  |  |  |  |  |  |

| TIORH           | Timer I/O control register H                                                |  |  |  |  |  |  |

| TIORL           | Timer I/O control register L                                                |  |  |  |  |  |  |

| TIER            | Timer interrupt enable register                                             |  |  |  |  |  |  |

| TCNT            | Timer counter                                                               |  |  |  |  |  |  |

| TGRA            | Timer general register A                                                    |  |  |  |  |  |  |

| TGRB            | Timer general register B                                                    |  |  |  |  |  |  |

| TGRC            | Timer general register D                                                    |  |  |  |  |  |  |

| TGRD            | Timer general register D                                                    |  |  |  |  |  |  |

| TGRE            | Timer general register E                                                    |  |  |  |  |  |  |

| TGRE            | Timer general register F                                                    |  |  |  |  |  |  |

| TSR             | Timer status register                                                       |  |  |  |  |  |  |

| TDERA           | Timer dead time enable register A                                           |  |  |  |  |  |  |

|                 | Timer buffer operation transfer mode                                        |  |  |  |  |  |  |

| TBTM            | register                                                                    |  |  |  |  |  |  |

| TADCD           | Timer A/D converter start request                                           |  |  |  |  |  |  |

| TADCR           | control register                                                            |  |  |  |  |  |  |

| TADCORA         | Timer A/D converter start request cycle                                     |  |  |  |  |  |  |

|                 | set register A                                                              |  |  |  |  |  |  |

| TADCORB         | Timer A/D converter start request cycle set register B                      |  |  |  |  |  |  |

|                 | Timer A/D converter start request cycle                                     |  |  |  |  |  |  |

| TADCOBRA        | set buffer register A                                                       |  |  |  |  |  |  |

| TADCODDD        | Timer A/D converter start request cycle                                     |  |  |  |  |  |  |

| TADCOBRB        | set buffer register B                                                       |  |  |  |  |  |  |

# 2. Multi-Function Timer Pulse Unit 3 for Phase Counting Mode

### 2.1 Example of Phase Counting Mode operation

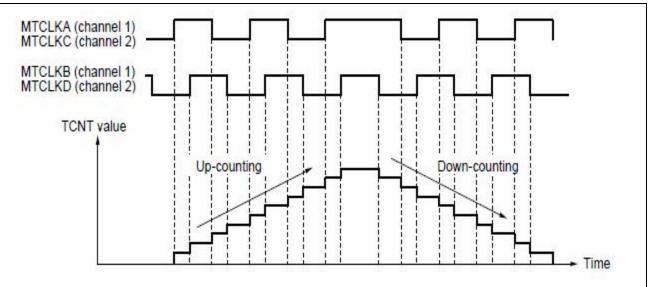

In phase counting mode, the phase difference between two external input clocks is detected and TCNT is incremented or decremented accordingly. This mode can be set for channels 1 and 2.

When phase counting mode is specified, an external clock is selected as the counter input clock and TCNT operates as an up/down-counter regardless of the setting of bits TPSC[2:0] and bits CKEG[1:0] in TCR. However, the functions of bits CCLR[1:0] in TCR and of TIOR, TIER, and TGR are valid, and input capture/compare match and interrupt functions can be used.

This can be used for two-phase encoder pulse input.

If an overflow occurs while TCNT is counting up, the TCFV flag in TSR is set to 1. If an underflow occurs while TCNT is counting down, the TCFU flag is TSR is set to 1.

The TCFD flag in TSR is the count direction flag. Read the TCFD flag to check whether TCNT is counting up or down.

Fig. 2-1 shows an example of Phase Counting Mode operation.

Figure 2-1 Example of Phase Counting Mode operation

# 2.2 Example of Procedure for Setting Phase Counting Mode

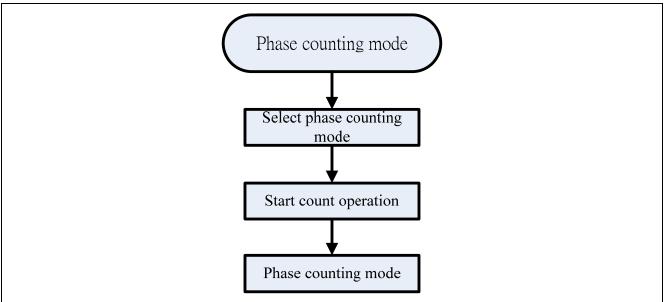

Fig. 2-2 shows an example of the procedure for setting Phase Counting Mode.

Figure 2-2 Example of Procedure for Setting Phase Counting Mode

# 2.3 Phase Counting Mode Application Example

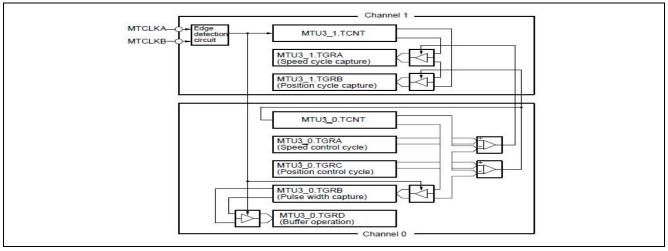

Fig. 2-3 shows an example in which channel 1 is in phase counting mode, and channel 1 is coupled with channel 0 to input 2-phase encoder pulses of a servo motor in order to detect position or speed.

Channel 1 is set to phase counting mode, and the encoder pulse A-phase and B-phase are input to MTCLKA and MTCLKB.

In channel 0, MTU0.TGRC compare match is specified as the TCNT clearing source and MTU0.TGRA and MTU0.TGRC are used for the compare match function and are set with the speed control cycle and position control cycle. MTU0.TGRB is used for input capture, with MTU0.TGRB and MTU0.TGRD operating in buffer mode. The channel 1 counter input clock is designated as the MTU3\_0.TGRB input capture source, and the widths of 2-phase encoder 4-multiplication pulses are detected.

MTU1.TGRA and MTU1.TGRB for channel 1 are designated for the input capture function and MTU0.TGRA and MTU0.TGRC compare matches in channel 0 are selected as the input capture sources to store the up/down-counter values for the control cycles.

This procedure enables the accurate detection of position and speed.

Figure 2-3 Phase Counting Mode Application Example

# 3. Multi-Function Timer Pulse Unit 3 Software Register Setting

Timer Control Register (TCR):

TCR controls the TCNT operation for each channel. The MTU has a total of ten TCR registers, one each for channels 0 to 4, 6, and 7. TCR values should be specified only while TCNT operation is stopped.

| Va       | alue after reset: | 0              |        | 1750                                                    | S             |           |   |   |   |     |

|----------|-------------------|----------------|--------|---------------------------------------------------------|---------------|-----------|---|---|---|-----|

|          |                   | . 0            | 0      | 0                                                       | 0             | 0         | 0 | 0 | 0 |     |

| Bit      | Symbol            | Bit Name       |        | Des                                                     | cription      |           |   |   |   | R/W |

| b2 to b0 | TPSC[2:0]         | Time Prescaler | Select | See                                                     | tables 15.7 t | o 15.10.  |   |   |   | R/W |

| b4, b3   | CKEG[1:0]         | Clock Edge Sel | ect    | b4 b                                                    | b4 b3         |           |   |   |   | R/W |

|          |                   |                |        | 0 0: Count at rising edge<br>0 1: Count at falling edge |               |           |   |   |   |     |

|          |                   |                |        |                                                         |               |           |   |   |   |     |

|          |                   |                |        | 1 x:                                                    | Count at bot  | n edges   |   |   |   |     |

| b7 to b5 | CCLR[2:0]         | Counter Clear  |        | See                                                     | tables 15.5 a | and 15.6. |   |   |   | R/W |

Figure 3-1 TCR Setting

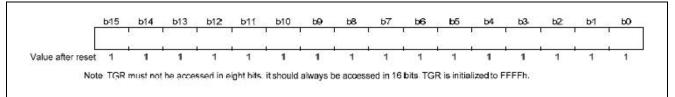

Timer General Register (TGR):

TGR is a 16-bit readable/writable register.

TGRA, TGRB, TGRC, and TGRD function as either output compare or input capture registers. TGRC and TGRD for channels 0, 3, 4, 6, and 7 can also be designated for operation as buffer registers. TGR buffer register combinations are TGRA and TGRC, and TGRB and TGRD.

Figure 3-2 TGR Setting

Timer Mode Register (TMDR):

TMDR1 specifies the operating mode of each channel. The MTU3 has a total of seven TMDR1 registers, one each for channels 0 to 4, 6, and 7. TMDR1 values should be specified only while TCNT operation is stopped.

|          |                  | b7               | b6 | b5          | ь4            | Ь3            | ь2             | b1            | ьо             |     |

|----------|------------------|------------------|----|-------------|---------------|---------------|----------------|---------------|----------------|-----|

|          |                  | -                |    | BFB         | BFA           |               | MD[3:0]        |               |                |     |

| Val      | lue after reset: | 0                | 0  | 0           | 0             | 0             | 0              | 0             | 0              | 6   |

| Bit      | Symbol           | Bit Name         |    | Descript    | ion           |               |                |               |                | R/W |

| b3 to b0 | MD[3:0]          | Mode Select      |    | These bit   | s specify the | timer operati | ng mode. Se    | e table 15.12 | 2 for details. | R/W |

| b4       | BFA              | Buffer Operation | A  | 0: TGRA     | and TGRC of   | perate norma  | ally           |               |                | R/W |

|          |                  |                  |    | 1: TGRA     | and TGRC us   | sed together  | for buffer op  | eration       |                |     |

| b5       | BFB              | Buffer Operation | B  | 0: TGRB     | and TGRD o    | perate norma  | ally           |               |                | R/W |

|          |                  |                  |    | 1: TGRB     | and TGRD us   | sed together  | for buffer op  | eration       |                |     |

| b6       | BFE              | Buffer Operation | E  | 0: MTU3_    | 0.TGRE and    | MTU3_0.TO     | RF operate     | normally      |                | R/W |

|          |                  |                  |    | 1: MTU3_    | 0.TGRE and    | MTU3_0.TO     | RF used tog    | ether for buf | fer            |     |

|          |                  |                  |    | operati     | on            | 5.30          |                |               |                |     |

| b7       |                  | (Reserved)       |    | This bit is | always read   | as 0. The w   | rite value sho | uld be 0.     |                | R/W |

#### Figure 3-3 TMDR Setting

# 4. Experimental Result

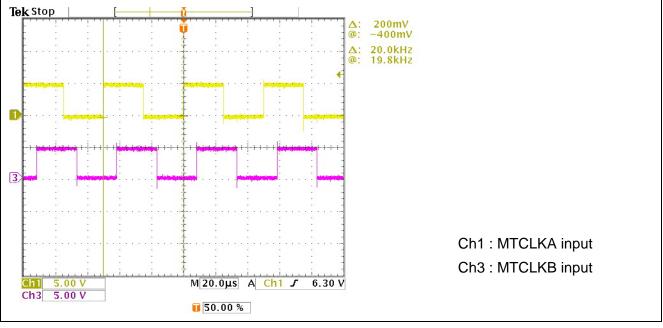

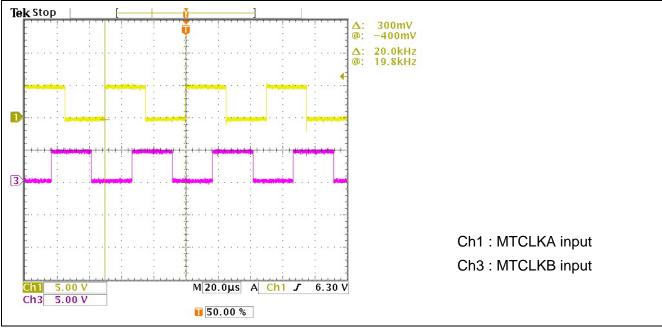

Fig. 4-1shows an example of operation in phase counting mode 1, and variable A in sample code summarizes the TCNT up-count/down-count conditions.

Fig. 4-2 shows an example of operation in phase counting mode 2, and variable A in sample code summarizes the TCNT up-count/down-count conditions.

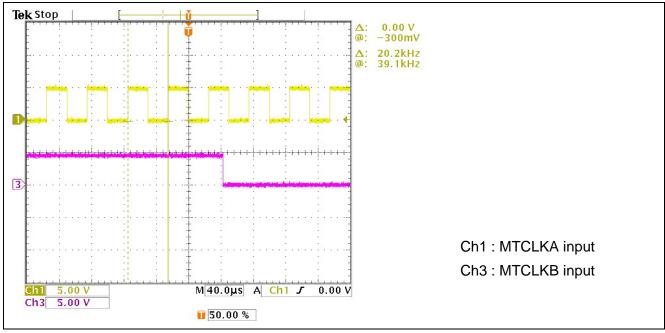

Fig. 4-3 shows an example of operation in phase counting mode 3, and variable A in sample code summarizes the TCNT up-count/down-count conditions.

Figure 4-3 MTCLKA and MTCLKB input for encoder pulse

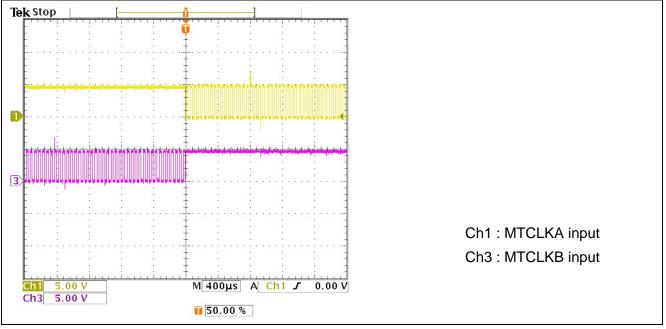

Fig. 4-4 shows an example of operation in phase counting mode 4, and variable A in sample code summarizes the TCNT up-count/down-count conditions.

Figure 4-4 MTCLKA and MTCLKB input for encoder pulse

# 5. Conclusion

We can use Multi-Function Timer Pulse Unit 3 for Phase Counting Mode control.

#### Website and Support

Renesas Electronics Website <u>http://www.renesas.com/</u>

Inquiries

http://www.renesas.com/inquiry

All trademarks and registered trademarks are the property of their respective owners.

# **Revision Record**

|      |               | Descript | ion                  |

|------|---------------|----------|----------------------|

| Rev. | Date          | Page     | Summary              |

| 1.00 | October 1. 11 | _        | First edition issued |

|      |               |          |                      |

|      |               |          |                      |

|      |               |          |                      |

|      |               |          |                      |

|      |               |          |                      |

|      |               |          |                      |

|      |               |          |                      |

# General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at

- which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal.

Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to a product with a different part number, confirm that the change will not lead to problems.

— The characteristics of an MPU or MCU in the same group but having a different part number may differ in terms of the internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

#### Notice

All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application categorized as "Specific" of nor which it is not intended without the prior written consent of Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronics appliances; machine tools;

- personal electronic equipment; and industrial robots. "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

Refer to "http://www.renesas.com/" for the latest and detailed information

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Renesse Electronics America Inc.

2880 Scott Boilevard Santa Clara, CA 95050-2554, U.S.A.

Tei: +1-409-588-0000, Fax: +14-08-588-6130

Renesse Electronics Canada Limited

1011 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada

Tei: +1-905-888-5441, Fax: +1-905-898-3220

Renesse Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tei: +44-1628-585-100, Fax: +444-1628-585-900

Renesse Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germany

Tei: +49-211-65030, Fax: +449-211-6503-1327

Renesse Electronics (China) Co., Ltd.

Th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China

Tei: +49-214-55030, Fax: +480-2835-7670

Renesse Electronics (Shanghai) Co., Ltd.

Unit 204, 205, AzIA Center, No. 1233 Luijazui Ring Rd., Pudong District, Shanghai 200120, China

Tei: +49-21-5877-1818, Fax: +852-1887-7858 / -7898

Renesse Electronics Hong Kong Limited

Unit 101-103, 16/FL, Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tei: +862-24175-9900, Fax: +862 2-8175-9670

Renesse Electronics Taiwan Co., Ltd.

137, No. 363, Fu Shing North Road, Taipei, Taiwan

Tei: +862-24175-9900, Fax: +863 2-4175-9870

<t