# **RL78/I1E**

### R01AN2819JJ0100 Rev.1.00 2015.11.09

# アナログ特性評価用サンプルコード仕様書

# 要旨

本ドキュメントは、RL78/I1E (R5F11CCC)用サンプルコードの仕様を説明します。

# 動作確認デバイス

RL78/I1E (R5F11CCC)

# 目次

| 1.  | 仕様2                  |

|-----|----------------------|

| 2.  | ハードウエア説明             |

| 3.  | API 関数一覧6            |

| 4.  | API 定義8              |

| 5.  | アナログ・フロントエンド関連 API26 |

| 6.  | フラッシュ・メモリ関連 API41    |

| 7.  | UART 通信関連 API43      |

| 8.  | フリーランタイマ関連 API46     |

| 9.  | キー判定関連 API47         |

| 10. | サンプルコード動作仕様53        |

| 11. | 設定変更手順66             |

| 12  | API 使用時の注音事項 70      |

### 1. 仕様

### 1.1 概要

$\triangle \Sigma$  A/D の制御としては、A/D 変換、ゲイン誤差測定、オフセット調整、自動ゲイン調整等の処理を行います。

# 1.2 動作確認条件

サンプルコードは、以下の条件で動作を確認しています。

表 1-1 動作条件一覧

| 項目                     | 内容                                       |  |  |

|------------------------|------------------------------------------|--|--|

| 評価ボード                  | ・RL78/I1E アナログ評価ボード [RTK50011CCC00000BR] |  |  |

|                        | ・RL78/I1E CPU ボード [FB-R5F11CCC-TB]       |  |  |

| 使用マイコン                 | R5F11CCC (RL78/I1E) 36ピン                 |  |  |

| 動作周波数                  | 32MHz                                    |  |  |

| 動作電圧                   | 5.0V                                     |  |  |

| 統合開発環境 (CS+ for CA,CX) | V3.01.00 [19 Aug 2015]                   |  |  |

| C コンパイラ (CS+)          | CA78K0R                                  |  |  |

|                        | V5.00.00.02 [03 Jul 2014]                |  |  |

| RL78/I1E コードライブラリ(CS+) | V1.02.00.06 [12 Aug 2015] <sup>注1</sup>  |  |  |

| データ・フラッシュ・ライブラリ        | RL78 ファミリ データ・フラッシュ・ライブラリ Type04         |  |  |

|                        | Ver.1.05                                 |  |  |

注 1: CS+用のコードライブラリはコード生成プラグインに内包されています。本ドキュメントでは「CS+ Code\_Generator for RL78\_78K V2.05.00」で動作確認を行っております。

# 2. ハードウエア説明

# 2.1 ハードウエアリソース一覧

表 2-1、表 2-2 に本サンプルコードで使用する周辺ハードウェアの設定を示します。

表 2-1 ハードウェアリソース一覧 (1/2)

| スと・ハ・・フェック 元(112)<br>田田悠色 |                                      |                               |  |  |

|---------------------------|--------------------------------------|-------------------------------|--|--|

| 周辺機能                      |                                      | 設定                            |  |  |

| クロック発生回路                  | 動作モード                                | 高速メイン・モード 2.7(V) ≦VDD≦5.5(V)  |  |  |

| └クロック                     | メインシステムクロック(fMAIN)                   | 高速オンチップオシレータクロック(fHOCO)       |  |  |

|                           | 24 ビットΔ Σ A/D コンバータの動                | 高速オンチップオシレータクロック(fHOCO)       |  |  |

|                           | 作クロック(fDSAD)ソースの設定                   | <del></del>                   |  |  |

|                           | RTC の動作クロック(fRTC)ソース<br>の設定          | 高速オンチップオシレータクロック(fHOCO)       |  |  |

|                           | 高速オンチップ・オシレータ・ク<br>ロック(fHOCO)設定      | 32(MHz)                       |  |  |

|                           | 高速システム・クロック(fMX)設定                   | なし                            |  |  |

|                           | 24 ビットΔ Σ A/D コンバータの動作クロック(fDSAD)の設定 | fHOCO 32(MHz)                 |  |  |

|                           | RTC,インターバル・タイマ/タイマ<br>RJ 動作クロック      | fIL 15(kHz)                   |  |  |

|                           | CPU と周辺クロック(fCLK)                    | fHOCO 32000(kHz)              |  |  |

| ポート機能                     | Port13                               | P13.7 (INTP)                  |  |  |

| タイマ・アレイ・ユ                 | チャネル 0                               | インターバル・タイマ                    |  |  |

| ニット                       | インターバル時間                             | 10(ms)                        |  |  |

| └ユニット1                    |                                      | カウント開始時に INTTM10 割り込みを発生する    |  |  |

|                           | 割り込み                                 | タイマ·チャネル 0 のカウント完了で割り込み<br>発生 |  |  |

|                           |                                      | レベル 3(低優先順位)                  |  |  |

| タイマ・アレイ・ユ                 | チャネル 1                               | インターバル・タイマ                    |  |  |

| ニット                       | 動作モード設定                              | 16 ビット                        |  |  |

| └ユニット1                    | インターバル・タイマ設定                         | 100(us)                       |  |  |

|                           | 割り込み                                 | タイマ·チャネル1のカウント完了で割り込み<br>発生   |  |  |

|                           |                                      | レベル 3(低優先順位)                  |  |  |

| ウォッチドッグ・タ<br>イマ           | ウォッチドッグ・タイマ動作設定                      | 使用しない                         |  |  |

| PGA+ΔΣA/Dコン               | 使用マルチプレクサ設定                          | マルチプレクサ 0 差動入力モード             |  |  |

| バータ                       |                                      | その他マルチプレクサ使用しない               |  |  |

|                           | SBIAS 出力電圧                           | 2.0V                          |  |  |

|                           | 断線検知                                 | 使用しない                         |  |  |

|                           | Δ Σ A/D コンバータ動作モード設定                 | 通常動作                          |  |  |

|                           | Δ Σ A/D コンバータ開始トリガ設定                 | ソフトウェアトリガ                     |  |  |

|                           | オートスキャンモード設定                         | シングルスキャン                      |  |  |

|                           | 割り込み設定                               | Δ Σ A/D の変換割り込み許可(INTDSAD)    |  |  |

|                           |                                      | レベル 3(低優先順位)                  |  |  |

|                           |                                      | Δ Σ A/D のスキャン割り込み許可(INTDSADS) |  |  |

|                           |                                      | レベル 3(低優先順位)                  |  |  |

|                           | <u>l</u>                             | (1-12220141-)                 |  |  |

表 2-2 ハードウェアリソース一覧 (2/2)

|                |                         | 設定                           |  |

|----------------|-------------------------|------------------------------|--|

| PGA+Δ Σ A/D コン | ゲイン設定 G <sub>SET1</sub> | 1 倍                          |  |

| バータ            | ゲイン設定 G <sub>SET2</sub> | 8倍                           |  |

| └マルチプレクサ 0     | オフセット調整電圧設定             | 16 (0mV)                     |  |

|                | オーバ・サンプリング比             | 256                          |  |

|                | A/D 変換回数                | PGA0CTL2 レジスタの設定値で 1~8092 回を |  |

|                | ハロ 交換回数                 | 指定                           |  |

|                |                         | 1 (1 回)                      |  |

|                | 平均化処理                   | 平均化処理を行なわない                  |  |

| シリアル           | チャネル 1                  | UARTO 送信/受信機能                |  |

| ∟SAU0          | データ・ビット長                | 8ビット                         |  |

| └チャネル          | データ転送方向                 | LSB                          |  |

| シリアル           | パリティ                    | パリティなし                       |  |

| SAU0           | ストップ・ビット長               | 1 ビット                        |  |

| UART1          | -                       | -                            |  |

|                | 受信データ・レベル               | 標準 1,000,000/hms)            |  |

| 文语             | 転送レート                   | 1000000(bps)                 |  |

|                | 割り込み                    | 受信完了割り込み設定(INTSR1)           |  |

|                |                         | レベル 3(低優先順位)                 |  |

|                | コールバック機能                | 受信完了                         |  |

| シリアル           | 転送モード                   | 連続転送モード                      |  |

| └SAU0          | データ・ビット長                | 8 ビット                        |  |

| └UART1         | データ転送方向                 | LSB                          |  |

| └送信            | パリティ                    | パリティなし                       |  |

|                | ストップ・ビット長               | 1 ビット                        |  |

|                | 送信データ・レベル               | 標準                           |  |

|                | 転送レート                   | 1000000(bps)                 |  |

|                | 割り込み                    | 送信完了割り込み設定(INTST1)           |  |

|                |                         | レベル 3(低優先順位)                 |  |

|                | コールバック機能                | 送信完了                         |  |

| データ・トランス       | DTC ベースアドレス             | 0xffd00                      |  |

| ファ・コントロール      | コントロールデータ 0(DTCD0)      | UART1 受信                     |  |

|                | コントロールデータ 1(DTCD1)      | UART1 送信                     |  |

| データ・トランス       | 転送モード設定                 | ノーマル・モード                     |  |

| ファ・コントロール      | 転送データ・サイズ設定             | 8ビット                         |  |

| └DTCD0         | 転送元アドレス                 | 0xFF46(固定)                   |  |

|                | 転送先アドレス                 | 0xF900(加算)                   |  |

|                | 転送回数                    | 1                            |  |

|                | ブロックサイズ                 | 1                            |  |

| データ・トランス       | 転送モード設定                 | ノーマル・モード                     |  |

| ファ・コントロール      | 転送データ・サイズ設定             | 8 ビット                        |  |

| └DTCD1         | 転送元アドレス                 | 0xF910(加算)                   |  |

|                | 転送先アドレス                 | 0xFF44(固定)                   |  |

|                | 転送回数                    | 1                            |  |

|                | ブロックサイズ                 | 1                            |  |

| 割り込み           | INT10                   | INTP0 使用                     |  |

| └外部割り込み        |                         | 立下りエッジ検出                     |  |

|                |                         | レベル 3(低優先順位)                 |  |

|                |                         | レ・バンの(医度元順位)                 |  |

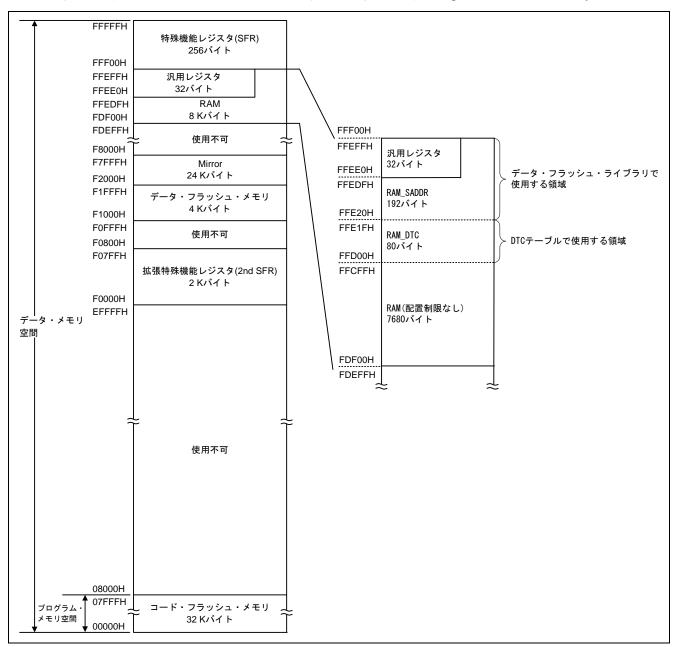

# 2.2 メモリアドレス空間

本サンプルコードで使用しているメモリアドレス空間を図2.1に示します。

データ・フラッシュ・ライブラリおよび DTC テーブルでは、RAM 上の固定番地の領域を確保する必要があります。設定は、リンク・ディレクティブ・ファイル (\*.dr) を作成し CS+への登録を行います。リンク・ディレクティブ・ファイルの詳細は「4.7 リンク・ディレクティブ・ファイル」を参照してください。

図 2.1 本サンプルコードで使用しているメモリアドレス空間

# 3. API 関数一覧

# 3.1 アナログ・フロントエンド関連

表 3-1 にアナログ・フロントエンド関連の API 関数一覧を示します。

ソースファイルは、r\_rl78\_ile\_common.c を参照してください。

表 3-1 アナログ・フロントエンド関連 API 関数一覧

| 関数名                             | 概要                                               |  |  |

|---------------------------------|--------------------------------------------------|--|--|

| R_I1E_Variable_Initialize       | サンプルコード使用変数初期化処理                                 |  |  |

| R_I1E_RingBuffer_Initialize     | DSAD リングバッファ初期化関数                                |  |  |

| R_I1E_AFE_Calibration           | AFE モジュール校正実行関数                                  |  |  |

| R_I1E_PGA_DSAD_GetResult_1Shot  | 24 ビット Δ Σ A/D コンバータ・指定 ch 1 ショット差動入力 A/D 変換実行関数 |  |  |

| R_I1E_PGA_DSAD_GainRegSet       | 24 ビットΔ Σ A/D コンバータ・ゲイン設定関数                      |  |  |

| R_I1E_PGA_DSAD_OffsetRegSet     | 24 ビットΔ Σ A/D コンバータオフセット設定関数                     |  |  |

| R_I1E_PGA_DSAD_OsrRegSet        | 24 ビット Δ Σ A/D コンバータ・OSR 設定関数                    |  |  |

| R_I1E_PGA_DSAD_SettingRegGet    | オートスキャンモード、各入力マルチプレクサ設定保持変数格納関数                  |  |  |

| R_I1E_PGA_DSAD_SettingRegSet    | DSAD 設定に構造体変数情報を設定                               |  |  |

| R_I1E_PGA_DSAD_CorrectValue     | PGA オフセット誤差補正適用値取得関数                             |  |  |

| R_I1E_PGA_DSAD_GetValue         | 24 ビットΔ Σ A/D コンバータ・変換値取得関数                      |  |  |

| R_I1E_PGA_DSAD_AutoGainInit     | PGA 自動ゲイン用変数初期化                                  |  |  |

| R_I1E_PGA_DSAD_AutoGainBufCheck | 24 ビットΔΣA/Dコンバータ変換完了後 PGA 自動ゲイン調整検査処理関数          |  |  |

| R_I1E_PGA_DSAD_AutoGainExecute  | 24 ビットΔ Σ A/D コンバータ・PGA 自動ゲイン調整関数                |  |  |

| R_I1E_PGA_DSAD_OffsetAdjustment | PGA オフセット調整実行関数                                  |  |  |

| R_I1E_PGA_DSAD_DisconnCheck     | 断線検知チェック関数                                       |  |  |

| R_I1E_AFE_Stop                  | RL78/I1E AFE 停止処理関数                              |  |  |

| R_I1E_AFE_ReStart               | RL78/I1E AFE 再始動処理関数                             |  |  |

| R_I1E_CAMP_Calibration          | コンフィギュラブル・アンプ トリミング実行関数                          |  |  |

# 3.2 フラッシュ・メモリ関連

表 3-2 にフラッシュ・メモリ関連の API 関数一覧を示します。

ソースファイルは、r\_rl78\_ile\_common.c を参照してください。

表 3-2 フラッシュ・メモリ関連 API 関数一覧

| 関数名                | 概要                      |  |  |

|--------------------|-------------------------|--|--|

| R_I1E_FlashCheck   | データフラッシュ・メモリ格納データチェック関数 |  |  |

| R_I1E_FlashRewrite | データフラッシュ・メモリ格納データ上書き関数  |  |  |

【注】 R\_FlashXXXX の名前の関数については、別途「データフラッシュライブラリ Type04」の関連ドキュメントをご参照ください。

# 3.3 UART 通信関連

表 3-3 に UART 通信関連の API 関数一覧を示します。

ソースファイルは、r\_rl78\_i1e\_common.c を参照してください。

#### 表 3-3 UART 通信関連 API 関数一覧

| 関数名                  | 概要                                            |  |

|----------------------|-----------------------------------------------|--|

| R_I1E_UartSend       | PC 送信処理設定関数(ASCII)。[1 回の送信で 256byte までの制限付き]  |  |

| R_I1E_UartSendBinary | PC 送信処理設定関数(Binary)。[1 回の送信で 256byte までの制限付き] |  |

| R_I1E_UartReceive    | PC からの受信処理(DTC0 使用)。[1 回の受信で 256byte までの制限付き] |  |

#### 3.4 フリーランタイマ関連

表 3-4 にフリーランタイマ関連の API 関数一覧を示します。

ソースファイルは、r\_rl78\_common\_util.c を参照してください。

表 3-4 フリーランタイマ関連 API 関数一覧

| 関数名                    | 概要                   |

|------------------------|----------------------|

| R_TAU_FreeRunTimerInit | フリーランタイマ・設定初期化関数     |

| R_TAU_FreeRunTimerStop | フリーランタイマ・停止関数        |

| R_GetTickCount         | フリーランタイマ・現在カウント値取得関数 |

| R_CmpTickCount         | フリーランタイマ・カウント値比較関数   |

# 3.5 キー判定関連

表 3-5 にキー判定関連の API 関数一覧を示します。

ソースファイルは、r\_keyscan.c を参照してください。

表 3-5 キー判定関連 API 関数一覧

| 関数名                | 概要              |  |  |

|--------------------|-----------------|--|--|

| R_KEY_Scan         | キースキャン処理        |  |  |

| R_KEY_Initialize   | キー情報初期化         |  |  |

| R_KEY_Get          | キー情報取得 (指定キーのみ) |  |  |

| R_KEY_GetAll       | キー情報取得 (全キー)    |  |  |

| R_KEY_WaitOneClick | 指定キー押下待ち        |  |  |

### 4. API 定義

本章では各 API 関数で使用する定義について示します。

#### 4.1 コード生成機能の定義

本サンプルコードでは CS+のコード生成機能で生成されるヘッダファイル[r\_cg\_macrodriver.h]をインクルードし、以下の型を用いています。

| 定義        | 値              |

|-----------|----------------|

| int8_t    | signed char    |

| uint8_t   | unsigned char  |

| int16_t   | signed short   |

| uint16_t  | unsigned short |

| int32_t   | signed long    |

| uint32_t  | unsigned long  |

| MD_STATUS | unsigned short |

表 4-1 型定義一覧

本サンプルコードに含まれる API(Application Program Interface;以下 API)関数は、一部を除き、共通した型でステータス値を返します。ユーザーアプリケーションでは、この返り値を判断し、正常であれば処理の続行、エラーであれば訂正処理を行う必要があります。

表 4-2 本サンプルコードで使用する MD\_STATUS 型の戻り値一覧

| 型名        | マクロ名        | 定数值 | 内容        |

|-----------|-------------|-----|-----------|

| MD_STATUS | MD_OK       | 00H | 正常終了      |

|           | MD_ERROR    | 80H | エラー       |

|           | MD_ARGERROR | 81H | パラメータ・エラー |

#### 4.2 ユーザー環境依存設定用マクロ宣言

本 API ではユーザー環境、使用条件に依存する部分をマクロ宣言にて定義しています。ご使用の環境に応じて各定義を変更してください。

#### (a) r cg main.c

表 4-3 ユーザー環境依存設定用マクロ宣言一覧

| マクロ宣言              | デフォルト設定値               | 入力範囲 | 内容                           |

|--------------------|------------------------|------|------------------------------|

| D_BULK_NUM         | 488U                   | 1 以上 | BULKSTART コマンドから BULKEND コマン |

|                    |                        |      | ドまでの転送データの総数を指定              |

| D_BULK_COMMAND_NUM | 20U <sup>注 1</sup>     | 1 以上 | 1回のBULKコマンド毎の転送データ数を指定       |

| D_STREAMHEADER     | (ヘッダ文字列) <sup>注2</sup> |      | STREAMHEADER 送信文字列定義         |

注 1 送信バッファサイズ ( D\_DSAD\_VALUE\_BUFFER\_SIZE ) に収まる範囲で設定してください 注 2 STREAM 転送のヘッダ送信の項を参照してください

#### (b) r\_rl78\_i1e\_common.h

表 4-4 ユーザー環境依存設定用マクロ宣言一覧

| マクロ宣言                        | デフォルト設定値          | 入力範囲                      | 内容                                 |

|------------------------------|-------------------|---------------------------|------------------------------------|

| D_MCU_CLOCK_MHZ              | 32U               | uint8_t <sup>注 1</sup>    | CPU と周辺クロック周波数の定義。 <sup>注1注2</sup> |

|                              |                   |                           | API 内部で使用するソフトウェアウエイト              |

|                              |                   |                           | の大まかな時間算出に使用します。                   |

|                              |                   |                           | (単位:MHz)                           |

| D_FLASH_MEMORY_DATA_USE      | 1U                | 0U,1U                     | フラッシュ・メモリデータ使用設定                   |

|                              |                   |                           | 0:使用しない                            |

|                              |                   |                           | 1:使用する                             |

| D_FLASH_FORCE_WRITING        | 0U                | 0U,1U                     | フラッシュデータ強制書き込み設定                   |

|                              |                   |                           | 0:強制書き換えしない。                       |

|                              |                   |                           | (フラッシュ値無効時のみ書き換える)                 |

|                              |                   |                           | 1:強制書き換えする                         |

| D_DSAD_CORRECT_USE           | 1U                | 0U,1U                     | PGA 誤差測定有効化設定                      |

|                              |                   |                           | 0:PGA 誤差測定無効                       |

|                              |                   |                           | 1:PGA 誤差測定有効                       |

| D_DSAD_CORRECT_MPXn          | D_PGA_DSAD_MP     | MPX0- MPX4 <sup>注 3</sup> | PGA 誤差測定で使用する入力マルチプレ               |

|                              | X0                |                           | クサ番号 <sup>注 3</sup>                |

| D_DSAD_VALUE_BUFFER_SIZE     | 256U              | uint16_t                  | DSAD 変換値格納バッファサイズ                  |

| D_DSAD_AUTO_GAIN_USE         | 1U                | 0U,1U                     | PGA 自動ゲイン調整有効化設定                   |

|                              |                   |                           | 0:PGA 自動ゲイン調整無効                    |

|                              |                   |                           | 1:PGA 自動ゲイン調整有効                    |

| D_DSAD_AUTO_GAIN_TRIGGER_SEC | 5U <sup>注 4</sup> | uint8_t                   | PGA 自動ゲイン調整タイミング(単位:秒)             |

| D_GAIN_ERROR_REFERENCE_mV    | 10.0F             | float                     | PGA ゲイン誤差測定基準電圧(単位:mV)             |

| D_DISCONNECTION_CHECK_COUNT  | 3U <sup>注 1</sup> | uint8_t                   | 断線チェック回数(1 回以上)                    |

| D_DISCONNECTION_THRESHOLD_mV | 10.0F             | float                     | 断線判定電圧(単位:mV)                      |

| D_UART_SEND_USE              | 1U                | 0U,1U                     | UART 送信有効化設定                       |

|                              |                   |                           | 0:UART 送信無効                        |

|                              |                   |                           | 1:UART 送信有効                        |

| D_UART_SEND_BUFFER_SIZE      | 256U              | Max.256                   | PC 送信用送信バッファサイズ                    |

- 【注1】0より大きな値を指定してください

- 【注2】使用するマイコンの CPU クロックの設定値を指定してください

- 【注 3】入力マルチプレクサ番号の define 宣言値を指定してください

D\_PGA\_DSAD\_MPX0 ··· 入力マルチプレクサ 0

D\_PGA\_DSAD\_MPX1 ··· 入力マルチプレクサ 1

D\_PGA\_DSAD\_MPX2 ··· 入力マルチプレクサ 2

D PGA DSAD MPX3 … 入力マルチプレクサ3

【注 4】実際の設定は CPU クロック周波数を基にしたカウンタ値を求める式が付加されます。 (5U\*D\_MCU\_CLOCK\_MHZ\*1000000)

# (c) r\_keyscan.h

表 4-5 ユーザー環境依存設定用マクロ宣言一覧

| マクロ宣言           | デフォルト設定値           | 入力範囲                | 内容                     |

|-----------------|--------------------|---------------------|------------------------|

| DEF_KEY_ACTIVE  | DEF_KEY_ACTIVE_LOW | DEF_KEY_ACTIVE_LOW, | SW 有効レベル               |

|                 |                    | DEF_KEY_ACTIVE_HIGH |                        |

| KEY_SCAN_NORM   | 10U                | uint8_t             | 単押し判定時間(単位:10ms)       |

| KEY_SCAN_LONG   | 100U               | uint8_t             | 長押し判定時間(単位:10ms)       |

| KEY_SCAN_DEAD   | 5U                 | uint8_t             | キー状態変更後の不感帯期間(単位:10ms) |

| KEY_SCAN_NOT    | 5U                 | uint8_t             | 非アクティブ期間(単位:10ms)      |

| KEY_SCAN_DOUBLE | 50U                | uint8_t             | ダブルクリック判定有効期間(単位:10ms) |

# (d) r\_cg\_userdefine.h

表 4-6 ユーザー環境依存設定用マクロ宣言一覧

| マクロ宣言            | デフォルト設定値 | 入力範囲       | 内容              |

|------------------|----------|------------|-----------------|

| D_DEBUG_LED_USE  | 0U       | 0U,1U      | デバッグ用 LED 使用設定  |

|                  |          |            | OU:使用しない        |

|                  |          |            | 1U:使用する         |

| D_DEBUG_LED_PORT | P1.5     | (出力ポート) 注1 | デバッグ用 LED ポート設定 |

【注 1】プルアップされた LED と接続しているデジタル出力ポートを指定してください

# 4.3 マクロ宣言

本節では API で定義されているマクロ宣言について示します。

# (a) r\_cg\_main.c

表 4-7 マクロ宣言一覧

| マクロ宣言                 | 値                                 | 内容              |

|-----------------------|-----------------------------------|-----------------|

| D_BULK_SPLIT_NUM      | D_BULK_NUM / _DSAD_VALUE_BUF_SIZE | BULK 分割数        |

| D_BULK_SPLIT_MOD      | D_BULK_NUM %D_DSAD_VALUE_BUF_SIZE | BULK 分割余り       |

| D_NO_ERROR            | 0x00U                             | エラー無し           |

| D_OVER_FLOW_ERROR     | 0x02U                             | オーバフロエラー        |

| D_DISCONNECTION_ERROR | 0x80U                             | 断線エラー           |

| D_ON_OFF_COMMAND      | @0¥r¥n                            | ON/OFF コマンド     |

| D_COMMAND_SIZE        | 4U                                | PC 通信用受信コマンドサイズ |

# (b) r\_rl78\_i1e\_common.h

表 4-8 マクロ宣言一覧

| マクロ宣言                          | 値                                          | 内容                   |

|--------------------------------|--------------------------------------------|----------------------|

| D_MCU_VOLTAGE_MODE             | OU                                         | フラッシュ・メモリ電圧モード       |

|                                |                                            | (フルスピード・モード)[固定]     |

| D_PGA_DSAD_MPX0                | 0x00U                                      | 入力マルチプレクサ 0          |

| D_PGA_DSAD_MPX1                | 0x01U                                      | 入力マルチプレクサ 1          |

| D_PGA_DSAD_MPX2                | 0x02U                                      | 入力マルチプレクサ 2          |

| D_PGA_DSAD_MPX3                | 0x03U                                      | 入力マルチプレクサ3           |

| D_DSAD_AUTO_GAIN_TRIGGER_COUNT | D_DSAD_AUTO_GAIN_TRIGGER_SEC *             | PGA 自動ゲイン調整タイミング     |

|                                | D_MCU_CLOCK_MHZ * 1000000                  | カウンタ値                |

| D_GAIN_ERROR_REFERENCE_LSB     | (int32_t)((0x800000L *                     | PGA ゲイン誤差測定基準電圧      |

|                                | D_GAIN_ERROR_REFERENCE_mV / 0.8            | (単位:LSB)             |

|                                | / 1000L)                                   |                      |

| D_DISCONNECTION_THRESHOLD_LSB  | (int32_t)(0x800000L *                      | 断線チェック判定電圧(単位:LSB)   |

|                                | D_DISCONNECTION_THRESHOLD_mV /             |                      |

|                                | 0.8 / 1000L)                               |                      |

| D_UART_SEND_BUFFER_NUMBER      | 2U                                         | PC 通信用送信バッファ本数       |

| D_FLASH_SUCCESS                | OU                                         | フラッシュ・メモリ処理成功        |

| D_FLASH_MATCH                  | OU                                         | フラッシュ・メモリと RAM に差異なし |

| D_FLASH_MISSMATCH              | 1U                                         | フラッシュ・メモリと RAM に差異あり |

| D_FLASH_INVALID                | 2U                                         | フラッシュ・メモリデータ無効       |

| D_FLASH_FAILURE                | 6U                                         | フラッシュ・メモリ処理エラー       |

| D_FLASH_DATA_STRUCT_SIZE       | sizeof(str_flash_data_t) / sizeof(uint8_t) | フラッシュ格納変数用構造体全体サイ    |

|                                |                                            | ズ (単位:byte)          |

| D_FLASH_DATA_CHECKSUM_SIZE     | 2U                                         | チェックサムサイズ (単位:byte)  |

| D_CAMP_CH_NUMBER               | 3U                                         | コンフィギュラブル・アンプのチャン    |

|                                |                                            | ネル数                  |

# $(c) \quad r\_rl78\_i1e\_common.c \\$

# 表 4-9 マクロ宣言一覧

| マクロ宣言                    | 値            | 内容                                                     |

|--------------------------|--------------|--------------------------------------------------------|

| D_DSAD_VALEU_MAX         | (1L<<23) - 1 | Δ Σ A/D コンバータへの入力電圧 最大値: +800 mV/(G <sub>TOTAL</sub> ) |

| D_DSAD_VALEU_MIN         | -1*(1L<<23)  | Δ Σ A/D コンバータへの入力電圧 最小値: -800 mV/(G <sub>TOTAL</sub> ) |

| D_DSAD_AUTO_GAIN_MAX_POS | 0U           | PGA 自動ゲイン調整用配列添え字 最大値添え字                               |

| D_DSAD_AUTO_GAIN_MIN_POS | 1U           | PGA 自動ゲイン調整用配列添え字 最小値添え字                               |

# ${\rm (d)} \quad r\_rl78\_common\_util.h$

表 4-10 マクロ宣言一覧

| マクロ宣言              | 値                                   | 内容                   |

|--------------------|-------------------------------------|----------------------|

| D_MCU_FREQUENCY_HZ | (D_MCU_CLOCK_MHZ * 1000000U)        | フリーランタイマ用定義          |

|                    |                                     | MCU 動作クロック周波数(単位:Hz) |

| D_WAIT10S          | (D_MCU_FREQUENCY_HZ * 10U - 1U)     | フリーランタイマ用カウンタ値:10s   |

| D_WAIT3S           | (D_MCU_FREQUENCY_HZ * 3U - 1U)      | フリーランタイマ用カウンタ値:3s    |

| D_WAIT1S           | (D_MCU_FREQUENCY_HZ * 1U - 1U)      | フリーランタイマ用カウンタ値:1s    |

| D_WAIT500MS        | (D_MCU_FREQUENCY_HZ / 2U - 1U)      | フリーランタイマ用カウンタ値:500ms |

| D_WAIT100MS        | (D_MCU_FREQUENCY_HZ / 10U - 1U)     | フリーランタイマ用カウンタ値:100ms |

| D_WAIT10MS         | (D_MCU_FREQUENCY_HZ / 100U - 1U)    | フリーランタイマ用カウンタ値:10ms  |

| D_WAIT5MS          | (D_MCU_FREQUENCY_HZ / 200U - 1U)    | フリーランタイマ用カウンタ値:5ms   |

| D_WAIT1MS          | (D_MCU_FREQUENCY_HZ / 1000U - 1U)   | フリーランタイマ用カウンタ値:1ms   |

| D_WAIT100US        | (D_MCU_FREQUENCY_HZ / 10000U - 1U)  | フリーランタイマ用カウンタ値:100us |

| D_WAIT10US         | (D_MCU_FREQUENCY_HZ / 100000U - 1U) | フリーランタイマ用カウンタ値:10us  |

# (e) r\_keyscan.h

# 表 4-11 マクロ宣言一覧

| マクロ宣言               | 値  | 内容            |

|---------------------|----|---------------|

| DEF_KEY_ACTIVE_LOW  | OU | ポート有効レベル=LOW  |

| DEF_KEY_ACTIVE_HIGH | 1U | ポート有効レベル=HIGH |

### 4.4 型宣言

本項では API で定義されている独自型について示します。

### 4.4.1 ユーザー環境依存設定用列挙体

表 4-12 に示す列挙体は、「4.5 ユーザー環境依存設定グローバル定数」で記載されている定数と共に用いられ、その設定に従って変更する必要があります。詳細は「4.5 ユーザー環境依存設定グローバル定数」を参照ください。

#### (a) r\_keyscan.h

表 4-12 キー設定情報格納グローバル変数指定用列挙体

| 型名      | デフォルト定義        | 内容                                                                                                                                                                                                                                  |

|---------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e_key_t | SW_MODE_CHANGE | スカポート番号などのキー設定情報が格納されているグローバル変数構造体配列の添え字を指し示す列挙体です。キー情報取得関数の呼び出し時に使用します。<br>ユーザーがキーを追加する場合は、ユニークな ENUM 値を追加してください。<br>(例)<br>SW_MODE_CHANGE = 0x00U,<br>SW_GAIN_UP, // 以降、追加キー<br>SW_GAIN_DOWN,<br>SW_OFFSET_UP,<br>SW_OFFSET_DOWN, |

|         | SW_TYPE_MAX    | 本定義によりキー設定情報が格納されているグローバル変数構造体配列のサイズを<br>決定していますので、名称の変更・削除・列挙体の最後尾からの移動はしないでくだ<br>さい。                                                                                                                                              |

注:変更時は必ず上記列挙体の設定とグローバル変数構造体配列の要素を一致させてください。

#### 4.4.2 列挙体

本節では API で定義されている列挙体宣言について示します。

#### (a) r\_cg\_main.c

表 4-13 BULK フォーマットデータ生成制御用列挙体

| 型名               | マクロ名                 | 内容                    |

|------------------|----------------------|-----------------------|

|                  | E_BULKDATA_BULKSTART | BULKSTART フォーマットデータ生成 |

| e_bulk_control_t | E_BULKDATA_BULK      | BULK フォーマットデータ生成      |

|                  | E_BULKDATA_BULKEND   | BULKEND フォーマットデータ生成   |

表 4-14 通信コマンド生成制御用列挙体

| 型名                     | マクロ名           | 内容                       |

|------------------------|----------------|--------------------------|

|                        | E_STREAMHEADER | STREAMHEADER フォーマットデータ生成 |

| e_communication_data_t | E_STREAM       | STREAM フォーマットデータ生成       |

|                        | E_BULK         | BULK フォーマットデータ生成         |

|                        | E_BINARY       | BINARY フォーマットデータ生成       |

# 表 4-15 通信コマンド判定用列挙体

| 型名                     | マクロ名             | 内容          |

|------------------------|------------------|-------------|

|                        | E_ON_OFF_COMMAND | ON/OFF コマンド |

| e_communication_data_t | E_COMMAND_NONE   | コマンド無し判定用   |

#### 表 4-16 測定制御用列挙体

| 型名                      | マクロ名                 | 内容         |

|-------------------------|----------------------|------------|

|                         | E_TRANSMISSION_START | シリアル送信開始   |

| e_measurement_control_t | E_DATA_GENERATION    | 測定値送信データ生成 |

|                         | E_ERROR_CHECK        | ERROR チェック |

|                         | E_WAIT               | 動作無し       |

# 表 4-17 MCU 状態判定用列挙体

| 型名            | マクロ名       | 内容       |

|---------------|------------|----------|

| e_mcu_state_t | E_MCU_HALT | HALT ₹—ド |

|               | E_MCU_RUN, | 動作中      |

#### (b) r\_rl78\_i1e\_common.h

#### 表 4-18 入力マルチプレクサ指定用列挙体

| 型名               | マクロ名               | 値     | 内容                       |

|------------------|--------------------|-------|--------------------------|

|                  | E_PGA_DSAD_MPX0    | 0x00U | 入力マルチプレクサ 0              |

|                  | E_PGA_DSAD_MPX1    | 0x01U | 入力マルチプレクサ 1              |

|                  | E_PGA_DSAD_MPX2    | 0x02U | 入力マルチプレクサ 2              |

| e_pga_dsad_mpx_t | E_PGA_DSAD_MPX3    | 0x03U | 入力マルチプレクサ3               |

|                  | E_PGA_DSAD_MPX4    | 0x04U | 入力マルチプレクサ 4 -> 内蔵温度センサ固定 |

|                  | E_PGA_DSAD_MPX_MAX | 0x05U | 入力マルチプレクサ最大判定            |

# 表 4-19 入力モード指定用列挙体

| 型名                      | マクロ名                    | 値     | 内容            |

|-------------------------|-------------------------|-------|---------------|

| a man dand Sand made to | E_PGA_DSAD_DIFF_INPUT   | 0x00U | 差動入力モード       |

| e_pga_dsad_input_mode_t | E_PGA_DSAD_SINGLE_INPUT | 0x01U | シングル・エンド入力モード |

# 表 4-20 Δ Σ A/D 変換許可/停止指定用列挙体

| 型名                 | マクロ名           | 値     | 内容        |

|--------------------|----------------|-------|-----------|

|                    | E_PGA_DSAD_OFF | 0x01U | A/D 変換を停止 |

| e_pga_dsad_onoff_t | E_PGA_DSAD_ON  | 0x00U | A/D 変換を許可 |

表 4-21 PGA ゲイン設定指定用列挙体

|                   |                        | 1     | ,                                                     |

|-------------------|------------------------|-------|-------------------------------------------------------|

| 型名                | マクロ名                   | 値     | 内容                                                    |

|                   | E_PGA_DSAD_GAIN_1_1_1  | 0x00U | $G_{SET1} = x1, G_{SET2} = x1, G_{TOTAL} = x1$        |

|                   | E_PGA_DSAD_GAIN_2_1_2  | 0x04U | $G_{SET1} = x2$ , $G_{SET2} = x1$ , $G_{TOTAL} = x2$  |

|                   | E_PGA_DSAD_GAIN_3_1_3  | 0x08U | $G_{SET1} = x3$ , $G_{SET2} = x1$ , $G_{TOTAL} = x3$  |

|                   | E_PGA_DSAD_GAIN_4_1_4  | 0x0CU | $G_{SET1} = x4, G_{SET2} = x1, G_{TOTAL} = x4$        |

|                   | E_PGA_DSAD_GAIN_8_1_8  | 0x10U | $G_{SET1} = x8, G_{SET2} = x1, G_{TOTAL} = x8$        |

|                   | E_PGA_DSAD_GAIN_1_2_2  | 0x01U | $G_{SET1} = x1, G_{SET2} = x2, G_{TOTAL} = x 2$       |

|                   | E_PGA_DSAD_GAIN_2_2_4  | 0x05U | $G_{SET1} = x2$ , $G_{SET2} = x2$ , $G_{TOTAL} = x 4$ |

|                   | E_PGA_DSAD_GAIN_3_2_6  | 0x09U | $G_{SET1} = x3$ , $G_{SET2} = x2$ , $G_{TOTAL} = x6$  |

|                   | E_PGA_DSAD_GAIN_4_2_8  | 0x0DU | $G_{SET1} = x4$ , $G_{SET2} = x2$ , $G_{TOTAL} = x 8$ |

| a man dand main t | E_PGA_DSAD_GAIN_8_2_16 | 0x11U | $G_{SET1} = x8$ , $G_{SET2} = x2$ , $G_{TOTAL} = x16$ |

| e_pga_dsad_gain_t | E_PGA_DSAD_GAIN_1_4_4  | 0x02U | $G_{SET1} = x1, G_{SET2} = x4, G_{TOTAL} = x 4$       |

|                   | E_PGA_DSAD_GAIN_2_4_8  | 0x06U | $G_{SET1} = x2, G_{SET2} = x4, G_{TOTAL} = x 8$       |

|                   | E_PGA_DSAD_GAIN_3_4_12 | 0x0AU | $G_{SET1} = x3$ , $G_{SET2} = x4$ , $G_{TOTAL} = x12$ |

|                   | E_PGA_DSAD_GAIN_4_4_16 | 0x0EU | $G_{SET1} = x4$ , $G_{SET2} = x4$ , $G_{TOTAL} = x16$ |

|                   | E_PGA_DSAD_GAIN_8_4_32 | 0x12U | $G_{SET1} = x8, G_{SET2} = x4, G_{TOTAL} = x32$       |

|                   | E_PGA_DSAD_GAIN_1_8_8  | 0x03U | $G_{SET1} = x1$ , $G_{SET2} = x8$ , $G_{TOTAL} = x 8$ |

|                   | E_PGA_DSAD_GAIN_2_8_16 | 0x07U | $G_{SET1} = x2$ , $G_{SET2} = x8$ , $G_{TOTAL} = x16$ |

|                   | E_PGA_DSAD_GAIN_3_8_24 | 0x0BU | $G_{SET1} = x3, G_{SET2} = x8, G_{TOTAL} = x24$       |

|                   | E_PGA_DSAD_GAIN_4_8_32 | 0x0FU | $G_{SET1} = x4$ , $G_{SET2} = x8$ , $G_{TOTAL} = x32$ |

|                   | E_PGA_DSAD_GAIN_8_8_64 | 0x13U | $G_{SET1} = x8$ , $G_{SET2} = x8$ , $G_{TOTAL} = x64$ |

# 表 4-22 オフセット電圧設定指定用列挙体

| 型名                  | マクロ名                      | 値     | 内容                             |

|---------------------|---------------------------|-------|--------------------------------|

|                     | E_PGA_DSAD_OFFSET_164p06  | 0x1FU | 164.06/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_153p13  | 0x1EU | 153.13/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_142p19  | 0x1DU | 142.19/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_131p25  | 0x1CU | 131.25/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_120p31  | 0x1BU | 120.31/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_109p38  | 0x1AU | 109.38/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_98p44   | 0x19U | 98.44/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_87p50   | 0x18U | 87.50/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_76p56   | 0x17U | 76.56/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_65p63   | 0x16U | 65.63/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_54p69   | 0x15U | 54.69/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_43p75   | 0x14U | 43.75/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_32p81   | 0x13U | 32.81/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_21p88   | 0x12U | 21.88/G <sub>SET1</sub> [mV]   |

|                     | E_PGA_DSAD_OFFSET_10p94   | 0x11U | 10.94/G <sub>SET1</sub> [mV]   |

| e_pga_dsad_offset_t | E_PGA_DSAD_OFFSET_0p00    | 0x10U | 0.00/G <sub>SET1</sub> [mV]    |

|                     | E_PGA_DSAD_OFFSET_M10p94  | 0x0FU | -10.94/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M21p88  | 0x0EU | -21.88/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M32p81  | 0x0DU | -32.81/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M43p75  | 0x0CU | -43.75/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M54p69  | 0x0BU | -54.69/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M65p63  | 0x0AU | -65.63/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M76p56  | 0x09U | -76.56/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M87p50  | 0x08U | -87.50/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M98p44  | 0x07U | -98.44/G <sub>SET1</sub> [mV]  |

|                     | E_PGA_DSAD_OFFSET_M109p38 | 0x06U | -109.38/G <sub>SET1</sub> [mV] |

|                     | E_PGA_DSAD_OFFSET_M120p31 | 0x05U | -120.31/G <sub>SET1</sub> [mV] |

|                     | E_PGA_DSAD_OFFSET_M131p25 | 0x04U | -131.25/G <sub>SET1</sub> [mV] |

|                     | E_PGA_DSAD_OFFSET_M142p19 | 0x03U | -142.19/G <sub>SET1</sub> [mV] |

|                     | E_PGA_DSAD_OFFSET_M153p13 | 0x02U | -153.13/G <sub>SET1</sub> [mV] |

|                     | E_PGA_DSAD_OFFSET_M164p06 | 0x01U | -164.06/G <sub>SET1</sub> [mV] |

#### 表 4-23 OSR 設定指定用列挙体

| 型名               | マクロ名                | 値     | 内容              |

|------------------|---------------------|-------|-----------------|

| _                | E_PGA_DSAD_OSR_64   | 0x00U | 15625.000 [sps] |

|                  | E_PGA_DSAD_OSR_128  | 0x01U | 7812.500 [sps]  |

|                  | E_PGA_DSAD_OSR_256  | 0x02U | 3906.250 [sps]  |

| e_pga_dsad_osr_t | E_PGA_DSAD_OSR_512  | 0x03U | 1953.125 [sps]  |

|                  | E_PGA_DSAD_OSR_1024 | 0x04U | 976.563 [sps]   |

|                  | E_PGA_DSAD_OSR_2048 | 0x05U | 488.281 [sps]   |

# 表 4-24 Δ Σ A/D 変換回数算出方法の指定用列挙体

| 型名                      | マクロ名                         | 値     | 内容                                    |

|-------------------------|------------------------------|-------|---------------------------------------|

|                         | E_PGA_DSAD_COUNT_CALCULATION | 0x00U | PGAxCTL2 レジスタの設定値で 1~8032 回<br>を指定    |

| e_pga_dsad_count_mode_t | E_PGA_DSAD_COUNT_LINEAR      | 0x01U | PGAxCTL2 レジスタの設定値で 1~255 回を<br>リニアに指定 |

#### 表 4-25 平均化処理の動作選択指定用列挙体

| 型名                             | マクロ名                           | 値     | 内容                      |

|--------------------------------|--------------------------------|-------|-------------------------|

|                                | E_PGA_DSAD_DO_NOT_AVERAGE_1    | 0x00U | 平均化処理を行わない              |

|                                | E_PGA_DSAD_DO_NOT_AVERAGE_2    | 0x01U | 平均化処理を行わない              |

| e_pga_dsad_average_operation_t | E DOA DOAD AVEDAGE INT AN ADO  | 0x02U | 平均化処理を行い、INTDSADを1回のA/D |

| e_pga_usau_average_operation_t | E_PGA_DSAD_AVERAGE_INT_AN_ADC  |       | 変換ごとに発生する               |

|                                | E DOA DOAD AVEDAGE INT LIDDATE | 0x03U | 平均化処理を行い、INTDSAD を平均値更  |

|                                | E_PGA_DSAD_AVERAGE_INT_UPDATE  |       | 新ごとに発生する                |

# 表 4-26 平均するデータ数の選択指定用列挙体

| 型名                          | マクロ名                  | 値     | 内容          |

|-----------------------------|-----------------------|-------|-------------|

| e_pga_dsad_average_number_t | E_PGA_DSAD_AVERAGE_8  | 0x00U | 平均するデータ数8   |

|                             | E_PGA_DSAD_AVERAGE_16 | 0x01U | 平均するデータ数 16 |

|                             | E_PGA_DSAD_AVERAGE_32 | 0x02U | 平均するデータ数 32 |

|                             | E_PGA_DSAD_AVERAGE_64 | 0x03U | 平均するデータ数 64 |

# 表 4-27 $\Delta$ $\Sigma$ A/D 変換(AUTOSCAN)の開始/停止指定用列挙体

| 型名                      | マクロ名             | 値     | 内容 |

|-------------------------|------------------|-------|----|

|                         | E_PGA_DSAD_STOP  | 0x00U | 停止 |

| e_pga_dsad_start_stop_t | E_PGA_DSAD_START | 0x01U | 開始 |

# 表 4-28 オートスキャンのモード指定用列挙体

| 型名                         | マクロ名                  | 値     | 内容           |

|----------------------------|-----------------------|-------|--------------|

|                            | E_PGA_DSAD_CONTINUOUS | 0x00U | 連続スキャンモード    |

| e_pga_dsad_autoscan_mode_t | E_PGA_DSAD_SINGLE     | 0x01U | シングル・スキャンモード |

#### 表 4-29 PGA 自動ゲイン調整処理戻り値指定用列挙体

| 型名                   | マクロ名                      | 値     | 内容            |

|----------------------|---------------------------|-------|---------------|

|                      | E_AUTO_GAIN_NO_ADJUSTMENT | 0x00U | PGA 自動ゲイン調整なし |

| e_auto_gain_return_t | E_AUTO_GAIN_ADJUSTMENT    | 0x01U | PGA 自動ゲイン調整実施 |

### 表 4-30 断線検知処理戻り値指定用列挙体

| 型名                       | マクロ名                      | 値           | 内容   |

|--------------------------|---------------------------|-------------|------|

| a diamental matrix t     | E_DISCONNECTION_NO_DETECT | 0x00U 非断線状態 |      |

| e_disconnection_return_t | E_DISCONNECTION_DETECT    | 0x01U       | 断線状態 |

# (c) r\_keyscan.h

表 4-31 キー状態指定用列挙体

| 型名             | マクロ名               | 内容                  |

|----------------|--------------------|---------------------|

|                | E_KEY_OFF          | キーオフ状態              |

|                | E_KEY_OFF_TO_ON    | キーオフからキー短押し状態に遷移    |

|                | E_KEY_ON_NORM      | キー短押し状態             |

| e_key_status_t | E_KEY_NORM_TO_LONG | キー短押し状態からキー長押し状態に遷移 |

|                | E_KEY_ON_LONG      | キー長押し状態             |

|                | E_KEY_LONG_TO_LONG | キー長押し状態からキー長押し状態に遷移 |

|                | E_KEY_DOUBLE_CLICK | キーダブルクリック状態         |

# 4.4.3 構造体

本項では API で定義されている構造体宣言について示します。

### (a) r\_cg\_main.c

表 4-32 測定データ格納変数用構造体

| 構造体型名 | measurement_data_t   |             |                  |  |  |

|-------|----------------------|-------------|------------------|--|--|

| 概要    | 測定データ格納変数用の定義。       |             |                  |  |  |

|       | 型                    | 名称          | 内容               |  |  |

|       | uint32_t             | count       | Δ Σ A/D 変換回数カウンタ |  |  |

| メンバ変数 | str_pga_dsad_value_t | dsad_value  | Δ Σ A/D 変換値構造体変数 |  |  |

|       | e_mcu_state_t        | mcu_state   | MCU の動作状態        |  |  |

|       | uint8_t              | error_state | エラー状態            |  |  |

# 表 4-33 BULK 転送データ格納変数用構造体

| 構造体型名     | bulk_data_t                                      |                     |                     |  |  |  |  |

|-----------|--------------------------------------------------|---------------------|---------------------|--|--|--|--|

| 概要        | BULK 転送データ格納変数用                                  | BULK 転送データ格納変数用の定義。 |                     |  |  |  |  |

|           | 型                                                | 型 名称 内容             |                     |  |  |  |  |

|           | uint16_t                                         | send_count          | BULK 転送送信回数カウンタ     |  |  |  |  |

| J きょうぎ 米佐 | e_bulk_control_t                                 | control             | BULK 転送制御           |  |  |  |  |

| メンハ変数     | メンバ変数<br>int32_t buf[D_BULK_BUFFER_SIZE] BULK 転送 |                     |                     |  |  |  |  |

|           | uint16_t                                         | str_count           | BULK 転送データ用バッファカウンタ |  |  |  |  |

|           | uint16_t                                         | split_count         | BULK 転送分割送信回数カウンタ   |  |  |  |  |

# $(b) \quad r\_rl78\_i1e\_common.h$

#### 表 4-34 Δ Σ A/D 変換情報格納変数用構造体

| 構造体型名 | str_pga_dsad_setting_t         |                        |                 |  |  |  |

|-------|--------------------------------|------------------------|-----------------|--|--|--|

| 概要    | PGA、ΔΣA/Dの各制御レジスタ設定情報格納変数用の定義。 |                        |                 |  |  |  |

|       | 型                              | 名称                     | 内容              |  |  |  |

|       | e_pga_dsad_onoff_t             | dsad_onoff             | A/D 変換 有効/無効フラグ |  |  |  |

|       | e_pga_dsad_input_mode_t        | dsad_input_mode        | 入力モード           |  |  |  |

|       | e_pga_dsad_offset_t            | dsad_offset            | オフセットレジスタ設定値    |  |  |  |

| メンバ変数 | e_pga_dsad_osr_t               | dsad_osr               | オーバー・サンプリング・レート |  |  |  |

| アンハ友奴 | e_pga_dsad_gain_t              | dsad_gain              | ゲイン             |  |  |  |

|       | uint8_t                        | dsad_count             | オートスキャン回数カウンタ   |  |  |  |

|       | e_pga_dsad_count_mode_t        | dsad_count_mode        | A/D 変換回数算出方法指定  |  |  |  |

|       | e_pga_dsad_average_operation_t | dsad_average_operation | 平均化処理の動作選択      |  |  |  |

|       | e_pga_dsad_average_number_t    | dsad_average_number    | 平均するデータ数の選択     |  |  |  |

# 表 4-35 ΔΣA/D 変換値格納バッファ用構造体

| 構造体型名 | str_pga_dsad_value_t                  |             |                      |  |  |

|-------|---------------------------------------|-------------|----------------------|--|--|

| 概要    | Δ Σ A/D 変換値と、ゲイン、オフセット等、各種情報格納変数用の定義。 |             |                      |  |  |

|       | 型                                     | 名称          | 内容                   |  |  |

|       | uint32_t                              | count       | 測定番号カウンタ値            |  |  |

|       | uni_long_t                            | adc_value   | A/D 変換値(右詰め 24bit)   |  |  |

|       | uint8_t                               | ch          | Ch 番号                |  |  |

| メンバ変数 | uint8_t                               | overflow    | オーバーフローフラグ           |  |  |

| アンハ麦奴 | uint8_t                               | gain_set_1  | 前段ゲイン倍率              |  |  |

|       | uint8_t                               | gain_set_2  | 後段ゲイン倍率              |  |  |

|       | uint8_t                               | gain_total  | トータルゲイン倍率            |  |  |

|       | e_pga_dsad_offset_t                   | offset_reg  | オフセットレジスタ設定値         |  |  |

|       | int32_t                               | adc_correct | A/D 変換補正値(右詰め 24bit) |  |  |

# 表 4-36 フラッシュ格納変数用構造体

| 構造体型名 | str_flash_data_t            |                                                                                                           |                |  |  |  |

|-------|-----------------------------|-----------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| 概要    | フラッシュ格納変数用の定義。              |                                                                                                           |                |  |  |  |

|       | 型                           | 名称                                                                                                        | 内容             |  |  |  |

|       | int32_t                     | gain_real[5U] 実ゲイン設定値                                                                                     |                |  |  |  |

|       |                             | G <sub>SET1</sub> x 固定 G <sub>SET2</sub> = G <sub>SET1</sub> [x1x2x3x4x8] x G <sub>SET2</sub> x 100(固定小数) |                |  |  |  |

| メンバ変数 | int32_t                     | offset_factor[5U][32U] PGA オフセット誤差補正値                                                                     |                |  |  |  |

|       |                             | オフセット 31 段階 x 前段ゲイン 5 段階 = 155 個保持                                                                        |                |  |  |  |

|       | [m][n] m はゲイン設定、n はオフセット設定値 |                                                                                                           |                |  |  |  |

|       | uint16_t                    | checksum                                                                                                  | チェックサム値(16bit) |  |  |  |

# (c) r\_keyscan.h

# 表 4-37 キー情報設定変数用構造体

| 構造体型名 | key_setting_t |                |                            |  |  |  |

|-------|---------------|----------------|----------------------------|--|--|--|

| 概要    | キー情報設定変数用の定義  | キー情報設定変数用の定義。  |                            |  |  |  |

|       | 型 名称 内容       |                |                            |  |  |  |

|       | uint8_t *     | p_port_addr    | SW 端子に接続しているポートレジスタのアドレス   |  |  |  |

| メンバ変数 | uint8_t       | port_bit_num   | SW 端子に接続しているポートレジスタのビット番号  |  |  |  |

|       | uint8_t       | multiple_group | 同時押し許可判別用グループ番号/同番号の同時押しを認 |  |  |  |

|       |               |                | めない                        |  |  |  |

# 4.4.4 共用体

本項では API で定義されている共用体宣言について示します。

#### (a) r\_rl78\_i1e\_common.h

表 4-38 signed long/unsigned long 読み出し用共用体

| 構造体型名 | uni_long_t                  |    |       |               |  |  |

|-------|-----------------------------|----|-------|---------------|--|--|

| 概要    | signed/unsigned 読み出し用共用体定義。 |    |       |               |  |  |

|       | 型 ビット数 名称 内容                |    |       |               |  |  |

| メンバ変数 | int32_t 32 LONG signed long |    |       |               |  |  |

|       | uint32_t                    | 32 | uLONG | unsigned long |  |  |

### 表 4-39 $\Delta \Sigma A/D$ コンバータ変換結果レジスタ C 読み出し用共用体

| 構造体型名 | uni_pga_dsad_conversion_result_t                    |   |    |           |  |  |

|-------|-----------------------------------------------------|---|----|-----------|--|--|

| 概要    | $\Delta$ $\Sigma$ A/D コンバータ変換結果レジスタ $C$ 読み出し用共用体定義。 |   |    |           |  |  |

|       | 型 ビット数 名称 内容                                        |   |    |           |  |  |

|       | uint8_t 8 BYTE 8bit access                          |   |    |           |  |  |

| メンバ変数 | BIT 4 - 未使用                                         |   |    |           |  |  |

|       | 1 overflow Overflow Flag                            |   |    |           |  |  |

|       |                                                     | 3 | ch | Ch number |  |  |

# 表 4-40 $\Delta \Sigma A/D$ コンバータ変換結果レジスタ読み出し用共用体

| 構造体型名 | uni_pga_dsad_value_t |                                  |   |         |                         |

|-------|----------------------|----------------------------------|---|---------|-------------------------|

| 概要    | Δ Σ A/D ⊐ :          | Δ Σ A/D コンバータ変換結果レジスタ読み出し用共用体定義。 |   |         |                         |

|       | 型 ビット数 名称 内容         |                                  |   |         |                         |

|       | uint32_t             | uint32_t                         |   | LONG    | 32bit access            |

|       | uint16_t             |                                  |   | WORD[2] | 16bit access            |

| メンバ変数 | BYTE                 | uni_pga_dsad_conversion_result_t | 8 | dsad_c  | Δ Σ A/D コンバータ変換結果レジスタ C |

|       | uint8_t              |                                  | 8 | dsad_l  | Δ Σ A/D コンバータ変換結果レジスタ L |

|       |                      | uint8_t                          | 8 | dsad_m  | Δ Σ A/D コンバータ変換結果レジスタ M |

|       |                      | uint8_t                          | 8 | dsad_h  | Δ Σ A/D コンバータ変換結果レジスタ H |

# 表 4-41 PGAxCTL0 レジスタ、ゲイン設定用共用体

| 構造体型名 | uni_pga_dsad_gain_t            |      |            |                   |

|-------|--------------------------------|------|------------|-------------------|

| 概要    | PGAxCTL0 レジスタ、ゲイン設定読み出し用共用体定義。 |      |            |                   |

|       | 型                              | ビット数 | 名称         | 内容                |

|       | uint8_t                        | 8    | BYTE       | 8bit access       |

| メンバ変数 | GAIN_BIT                       | 2    | gain_set_2 | G <sub>SET2</sub> |

|       |                                | 3    | gain_set_1 | G <sub>SET1</sub> |

|       |                                | 3    | =          | 未使用               |

# 表 4-42 PGAxCTL0 レジスタ制御用共用体

| 構造体型名 | uni_reg_pgaxctl0_t     |   |      |             |

|-------|------------------------|---|------|-------------|

| 概要    | PGAxCTL0 レジスタ制御用共用体定義。 |   |      |             |

|       | 型 ビット数 名称 内容           |   |      |             |

| メンバ変数 | uint8_t                | 8 | BYTE | 8bit access |

| ノンハ友奴 | PGAxCTL0_BIT           | 5 | gain | GAIN        |

|       |                        | 3 | osr  | OSR         |

#### 表 4-43 PGAxCTL1 レジスタ制御用共用体

| 構造体型名 | uni_reg_pgaxctl1_t     |      |            |                   |

|-------|------------------------|------|------------|-------------------|

| 概要    | PGAxCTL1 レジスタ制御用共用体定義。 |      |            |                   |

|       | 型                      | ビット数 | 名称         | 内容                |

|       | uint8_t                | 8    | BYTE       | 8bit access       |

| メンバ変数 | PGAxCTL1_BIT           | 5    | offset     | offset            |

| アンハ麦奴 |                        | 1    | -          | 未使用               |

|       |                        | 1    | pga3tsel   | コンフィギュラブル・アンプ自己補正 |

|       |                        | 1    | input_mode | AINSEL            |

# 表 4-44 PGAxCTL2 レジスタ制御用共用体

| 構造体型名 | uni_reg_pgaxctl2_t     |   |      |             |

|-------|------------------------|---|------|-------------|

| 概要    | PGAxCTL2 レジスタ制御用共用体定義。 |   |      |             |

|       | 型 ビット数 名称 内容           |   |      |             |

| メンバ変数 | uint8_t                | 8 | BYTE | 8bit access |

| アンハ亥奴 | PGAxCTL2_BIT           | 5 | low  | offset      |

|       |                        | 3 | high | 未使用         |

### 表 4-45 PGAxCTL3 レジスタ制御用共用体

| 構造体型名 | uni_reg_pgaxctl3_t     |   |            |                        |

|-------|------------------------|---|------------|------------------------|

| 概要    | PGAxCTL3 レジスタ制御用共用体定義。 |   |            |                        |

|       | 型 ビット数 名称 内容           |   |            |                        |

|       | uint8_t                | 8 | BYTE       | 8bit access            |

| メンバ変数 | PGAxCTL3_BIT           | 2 | pgaxave0_1 | PGAXAV[1:0]平均化するデータの選択 |

| メンハ変数 |                        | 2 | pgaxave3_2 | PGAXAV[3:2]平均化処理の動作選択  |

|       |                        | 3 | -          | 未使用                    |

|       |                        | 1 | pgaxctm    | A/D 変換回数指定モード選択        |

# 表 4-46 DSADCTL レジスタ制御用共用体

| 構造体型名 | uni_reg_pgaxctl3_t    |      |            |                          |

|-------|-----------------------|------|------------|--------------------------|

| 概要    | DSADCTL レジスタ制御用共用体定義。 |      |            |                          |

|       | 型                     | ビット数 | 名称         | 内容                       |

|       | uint8_t               | 8    | BYTE       | 8bit access              |

| メンバ変数 | DSADCTL_BIT           | 5    | dsadbmp4_0 | 入力マルチプレクサ n からの信号(n=4-0) |

| トンハ変数 |                       | 1    | dsadscm    | オートスキャンモードの選択            |

|       |                       | 1    | -          | 未使用                      |

|       |                       | 1    | dsadtst    | A/D 変換(AUTOSCAN)の制御      |

# 4.5 ユーザー環境依存設定グローバル定数

# 4.5.1 キー設定情報格納グローバル変数

本項で示す  $r_{\text{keyscan.h}}$  ファイルにある定数を変更することにより、ユーザーが使用するハードウエア構成  $(I/O \, \, \text{ぱ-h})$ に対応させることができます。

#### (a) r\_keyscan.h

表 4-47 キー設定情報格納グローバル変数用構造体

| 構造体型名 | key_setting_t       |                |                              |  |  |

|-------|---------------------|----------------|------------------------------|--|--|

| 概要    | キー設定情報格納グローバル変数用構造体 |                |                              |  |  |

|       | 型                   | 名称             | 内容                           |  |  |

| メンバ変数 | uint8_t *           | p_port_addr    | SW に接続しているポートレジスタのアドレス       |  |  |

| ノンハ変数 | uint8_t             | port_bit_num   | SW に接続しているポートレジスタのビット番号      |  |  |

|       | uint8_t             | multiple_group | 同時押し許可判別用グループ番号(同番号の同時押しは無効) |  |  |

#### (b) 記述例

#### ケース 1

RL78/I1EのP13.7を「SW\_MODE\_CHANGE」としてキー登録を行う。(本サンプルコードの既定値)

```

typedef enum {

SW_MODE_CHANGE = 0x00U,

SW_TYPE_MAX

} e_key_t;

const key_setting_t g_con_key_setting[SW_TYPE_MAX] = {

/* ポート ビット番号 グループ */

/* SW_MODE_CHANGE */ {&P13, 7U, 0U},

};

```

#### ケース 2

RL78/IIE の P12.1 を「SW\_GAIN\_UP」、P12.0 を「SW\_GAIN\_DOWN」としてキー登録を行い、グループ 1 として同一グループ設定(同時押し無効)とする。また、P1.2 を「SW\_OFFSET\_UP」、P1.5 を「SW\_OFFSET\_DOWN」としてキー登録を行い、グループ 2 として同一グループ設定(同時押し無効)とする。

```

typedef enum

SW_GAIN_UP = 0x00U,

SW_GAIN_DOWN,

SW_OFFSET_UP,

SW_OFFSET_DOWN,

SW_TYPE_MAX

} e_key_t;

const key_setting_t g_con_key_setting[SW_TYPE_MAX] =

{

ポート ビット番号 グループ */

/*

/* SW_GAIN_UP

*/ {&P12, 1U,

1U},

/* SW_GAIN_DOWN

*/ {&P12, OU,

1U},

/* SW OFFSET UP

*/ {&P1, 2U,

2U},

/* SW_OFFSET_DOWN */ {&P1, 5U,

2U},

};

```

# 4.6 グローバル変数

本節では API で定義されているグローバル変数について示します。

#### (a) r\_cg\_main.c

表 4-48 r\_cg\_main.c グローバル変数一覧

| 型名          | 値           | 内容             |

|-------------|-------------|----------------|

| bulk_data_t | g_bulk_data | BULK 転送データ格納変数 |

# $(b) \quad r\_rl78\_i1e\_common.c$

表 4-49 r\_rl78\_i1e\_common.c グローバル変数一覧

| 変数名                        | 型名                         | 内容                               |

|----------------------------|----------------------------|----------------------------------|

| g_flash_value              | str_flash_data_t           | データ・フラッシュ格納データ構造体                |

| g_dsad_autoscan_mode       | e_pga_dsad_autoscan_mode_t | オートスキャンモード設定                     |

| g_dsad_setting             | str_pga_dsad_setting_t     | 各入力マルチプレクサ設定保持変数                 |

| g_camp_trimming            | uint8_t                    | コンフィギュラブル・アンプトリミング設定値格納変数        |

| g_dsad_value               | str_pga_dsad_value_t       | DSAD 変換値格納バッファ                   |

| g_dsad_value_write_pos     | uint16_t                   | DSAD 変換値格納バッファ書き込み位置             |

| g_dsad_value_read_pos      | uint16_t                   | DSAD 変換値格納バッファ読み出し位置             |

| g_dsad_value_user_read_pos | uint16_t                   | DSAD 変換値格納バッファユーザ読み出し位置          |

| g_dsad_measurement_count   | uint32_t                   | DSAD 変換測定番号カウンタ                  |

| g_i1e_uart_send_buffer     | int8_t                     | PC 送信用の送信バッファ(UART への転送は DTC 使用) |

| g_buffer_number            | uint8_t                    | PC 送信用の送信バッファの格納先番号              |

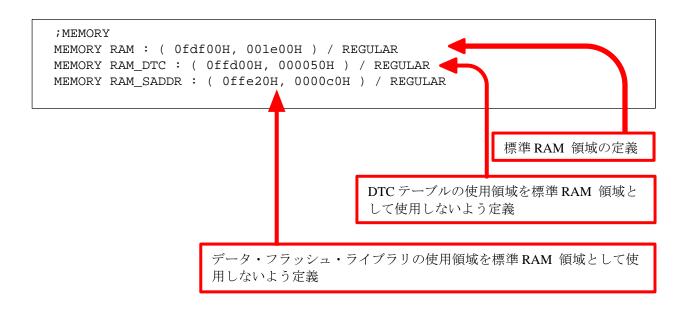

# 4.7 リンク・ディレクティブ・ファイル

リンク・ディレクティブ・ファイルによって、データ・フラッシュ・ライブラリおよび DTC テーブルで使用する RAM 領域を使用しないように設定を行います。

本サンプルコードで使用するリンク・ディレクティブ・ファイル「SampleCode.dr」の概要を以下に記載します。

# 5. アナログ・フロントエンド関連 API

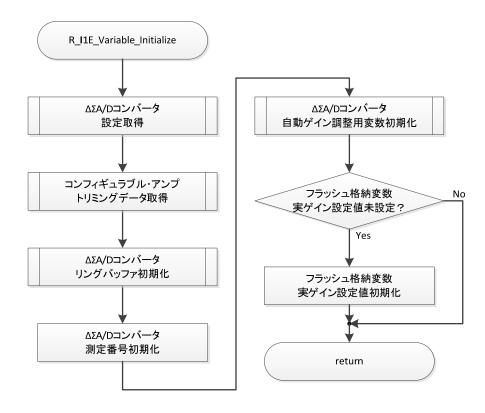

# 5.1 サンプルコード使用変数初期化処理

#### void R\_I1E\_Variable\_Initialize(void)

説明 サンプルコード使用変数初期化処理

引数 なし

グローバル変数 g\_dsad\_autoscan\_mode:

オートスキャンモード設定

g\_dsad\_setting[]:

各入力マルチプレクサ設定保持変数

g\_camp\_trimming:

コンフィギュラブル・アンプ n トリミング設定値

g\_flash\_value:

データ・フラッシュ格納データ構造体

gs\_con\_gain\_set\_1\_size:

前段ゲインの倍率要素数

gs\_con\_gain\_set\_1[]:

前段ゲインの倍率

SFR

なし

戻り値

なし

処理内容  $\Delta \Sigma A/D$  コンバータの各種設定を取得する。

コンフィギュラブル・アンプのトリミングデータを取得する。

ΔΣA/D コンバータ変換値リングバッファを初期化する。

ΔΣA/D コンバータ変換測定番号カウンタを初期化する。(0 クリア)

PGA 自動ゲイン調整用変数を初期化する。

フラッシュ格納用構造体の実ゲイン設定値配列が設定されていない場合、初期化する。

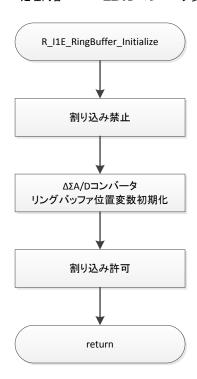

# 5.2 DSAD リングバッファ初期化関数

# void R\_I1E\_RingBuffer\_Initialize(void)

説明 DSAD リングバッファ初期化関数

引数 なし

グローバル変数 g\_dsad\_value\_write\_pos:

DSAD 変換値格納バッファ書き込み位置

g\_dsad\_value\_read\_pos:

DSAD 変換値格納バッファ読み出し位置

g\_dsad\_value\_user\_read\_pos:

DSAD 変換値格納バッファユーザ読み出し位置

SFR なし 戻り値 なし

処理内容  $\Delta\Sigma A/D$  コンバータ変換値格納リングバッファの書き込み位置/読み出し位置記憶変数を初期化する。

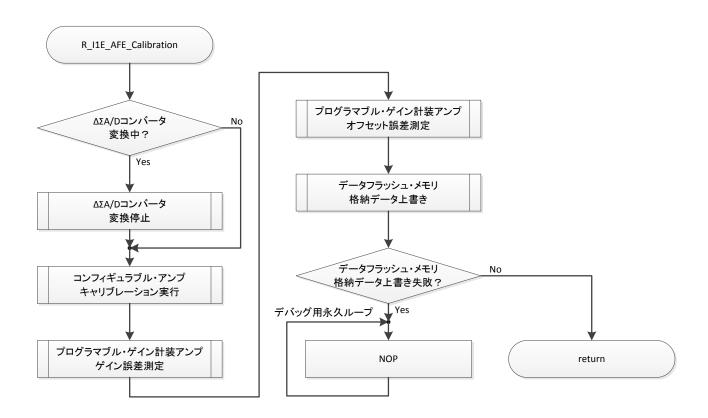

# 5.3 AFE モジュール校正実行関数

### void R\_I1E\_AFE\_Calibration(void)

説明 AFE モジュール校正実行関数

引数 なし

グローバル変数 g\_camp\_trimming:

コンフィギュラブル・アンプ n トリミング設定値

g\_flash\_value:

データ・フラッシュ格納データ構造体

SFR なし 戻り値 なし

処理内容 コンフィギュラブル・アンプのオフセット・キャリブレーションを実行し、結果を g\_camp\_trimming に格納する。

プログラマブル・ゲイン計装アンプのゲイン誤差を測定し、フラッシュ格納用構造体の実ゲイン設定値配列に格

納する。

プログラマブル・ゲイン計装アンプのオフセット誤差を測定し、フラッシュ格納用構造体のオフセット誤差補正

値配列に格納する。

フラッシュ・メモリに取得したデータを書き込みする。

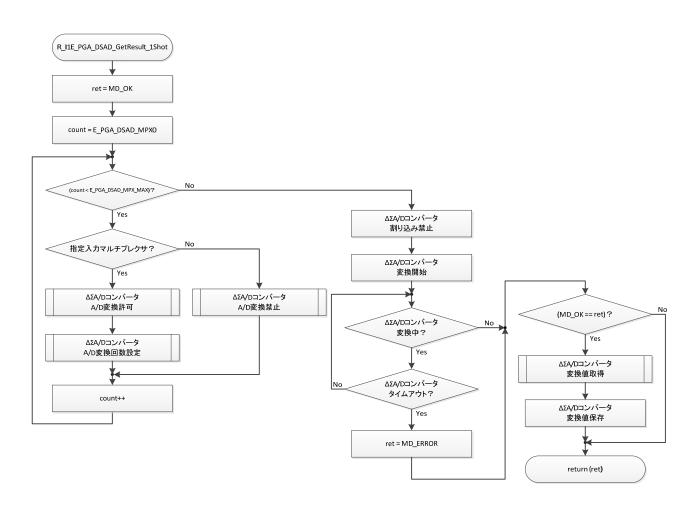

# 5.4 24 ビット Δ Σ A/D コンバータ・指定 ch 1 ショット差動入力 A/D 変換実行関数

# MD\_STATUS R\_I1E\_PGA\_DSAD\_GetResult\_1Shot

(e\_pga\_dsad\_mpx\_t dsad\_mpx, int32\_t \*p\_dsad\_value)

説明 24 ビット ΔΣA/D コンバータ・指定 ch 1 ショット差動入力 A/D 変換実行関数

引数 dsad\_mpx:

24 ビット ΔΣΑ/D コンバータ 入力マルチプレクサ番号

\*p\_dsad\_value:

24 ビット ΔΣA/D コンバータ 24 ビット A/D 値 格納ポインタ

グローバル変数 なし

SFR DSADIF:

ΔΣA/D 変換 変換完了割り込み要求フラグ

DSADSIF:

ΔΣA/D 変換 スキャン完了割り込み要求フラグ

DSADMK:

ΔΣA/D 変換 変換完了割り込みマスクフラグ

DSADSMK:

ΔΣA/D 変換 スキャン完了割り込みマスクフラグ

DSADST:

A/D 変換(AUTOSCAN)の制御

戻り値 MD STATUS:

MD\_OK

MD\_ERROR

処理内容  $\Delta\Sigma$ A/D コンバータで入力マルチプレクサ指定チャネルからの入力により A/D 変換を行い、 $^*$ p\_dsad\_value に結果

を格納する。

A/D 変換がタイムアウトした場合は MD\_ERROR を返す。

# 5.5 24 ビット Δ Σ A/D コンバータ・ゲイン設定関数

void R\_I1E\_PGA\_DSAD\_GainRegSet(e\_pga\_dsad\_mpx\_t dsad\_mpx, e\_pga\_dsad\_gain\_t dsad\_gain)

説明 24 ビット ΔΣΑ/D コンバータ・ゲイン設定関数

引数 dsad\_mpx:

24 ビット ΔΣΑ/D コンバータ 入力マルチプレクサ番号

dsad\_gain:

24 ビット ΔΣΑ/D コンバータ ゲイン設定値

グローバル変数 なし

SFR PGAxCTL0:

入力マルチプレクサ x(x=0~4) 設定レジスタ 0

戻り値 なし

処理内容 ΔΣΑ/D コンバータ入力マルチプレクサの指定チャネル用プログラマブル・ゲイン計装アンプゲインレジスタに指

定値を設定する。

# 5.6 24 ビットΔ Σ A/D コンバータオフセット設定関数

void R I1E PGA DSAD OffsetRegSet

(e\_pga\_dsad\_mpx\_t dsad\_mpx, e\_pga\_dsad\_offset\_t dsad\_offset)

説明 24 ビット  $\Delta\Sigma$ A/D コンバータオフセット設定関数

引数 dsad\_mpx:

24 ビット ΔΣΑ/D コンバータ 入力マルチプレクサ番号

dsad offset:

24 ビット ΔΣΑ/D コンバータ オフセット設定値

グローバル変数 なし

SFR PGAxCTL1:

入力マルチプレクサ x(x=0~4) 設定レジスタ 1

戻り値 なし

処理内容 ΔΣΑ/D コンバータ入力マルチプレクサの指定チャネル用オフセット電圧レジスタに指定値を設定する。

#### 5.7 24 ビットΔ Σ A/D コンバータ・OSR 設定関数

void R\_I1E\_PGA\_DSAD\_OsrRegSet(e\_pga\_dsad\_mpx\_t dsad\_mpx, e\_pga\_dsad\_osr\_t dsad\_osr)

説明 24 ビット ΔΣA/D コンバータ・OSR 設定関数

引数 dsad mpx:

24 ビット ΔΣΑ/D コンバータ 入力マルチプレクサ番号

osr:

24 ビット ΔΣA/D コンバータ OSR 設定値

グローバル変数 なし

SFR PGAxCTL0:

入力マルチプレクサ x(x=0~4) 設定レジスタ 0

戻り値 なし

処理内容  $\Delta\Sigma A/D$  コンバータ入力マルチプレクサの指定チャネル用オーバ・サンプリング比レジスタに指定値を設定する。

# 5.8 オートスキャンモード、各入力マルチプレクサ設定保持変数格納関数

void R\_I1E\_PGA\_DSAD\_SettingRegGet

(e\_pga\_dsad\_autoscan\_mode\_t \*dsad\_autoscan, str\_pga\_dsad\_setting\_t dsad\_setting[])

説明 オートスキャンモード、各入力マルチプレクサ設定保持変数格納関数

引数 \*dsad\_autoscan:

オートスキャンモード設定

dsad\_setting[]:

24 ビット ΔΣΑ/D コンバータ設定値

グローバル変数 gs\_gain\_set\_2:

後段ゲインの倍率

SFR

なし

戻り値

なし

処理内容 ΔΣΑ/D コンバータのオートスキャンモード設定を取得し、\*dsad\_autoscan に格納する。

$\Delta\Sigma$ A/D コンバータ全入力マルチプレクサ用の各種設定を取得し、 $dsad\_setting[]$ 配列に格納する。

PGA 誤差測定で使用する入力マルチプレクサ用のプログラマブル・ゲイン計装アンプの後段ゲイン倍率を取得

し、グローバル変数 gs\_gain\_set\_2 に格納する。

### 5.9 DSAD 設定に構造体変数情報を設定

void R\_I1E\_PGA\_DSAD\_SettingRegSet

(e\_pga\_dsad\_autoscan\_mode\_t dsad\_autoscan, str\_pga\_dsad\_setting\_t dsad\_setting[])

説明 DSAD 設定に構造体変数情報を設定

引数 dsad\_autoscan:

オートスキャンモード設定

dsad\_setting[]:

24 ビット ΔΣΑ/D コンバータ設定値

グローバル変数 なし SFR なし 戻り値 なし

処理内容  $\Delta\Sigma A/D$  コンバータのオートスキャンモードを指定のモードに設定する。

$\Delta\Sigma$ A/D コンバータ全入力マルチプレクサ用の各種設定を dsad\_setting[]配列で指定される値に設定する。

#### 5.10 PGA オフセット誤差補正適用値取得関数

int32\_t R\_I1E\_PGA\_DSAD\_CorrectValue(str\_pga\_dsad\_value\_t \*p\_value)

説明 PGA オフセット誤差補正適用値取得関数

引数 \*p\_value:

24 ビット ΔΣΑ/D コンバータ 変換値ポインタ

グローバル変数 g\_flash\_value:

データ・フラッシュ格納データ構造体

SFR なし 戻り値 int32\_t:

PGA オフセット誤差適用値。p\_value >adc\_correct にも同値格納。

処理内容 指定された A/D 変換情報格納用構造体に格納されたデータを元にオフセット誤差適用値を計算し、これを返す。

同時に指定された構造体のメンバ adc\_correct にも算出された値を格納する。

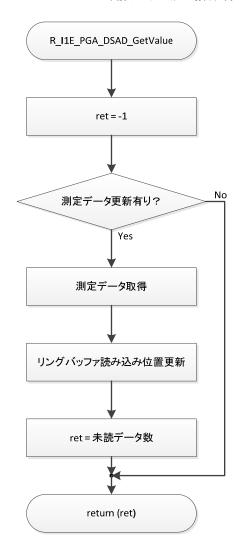

# 5.11 24 ビット Δ Σ A/D コンバータ・変換値取得関数

# int16\_t R\_I1E\_PGA\_DSAD\_GetValue(str\_pga\_dsad\_value\_t \*p\_value)

説明 24 ビット  $\Delta\Sigma$ A/D コンバータ・変換値取得関数

引数 \*p\_value:

24 ビット ΔΣΑ/D コンバータ 変換値ポインタ

グローバル変数 g\_dsad\_value\_write\_pos:

DSAD 変換値格納バッファ書き込み位置

g\_dsad\_value\_user\_read\_pos:

DSAD 変換値格納バッファユーザ読み出し位置

g\_dsad\_value[]:

DSAD 変換値格納バッファ

SFR なし 戻り値 int16\_t:

0以上:データ読み出し完了+未読データ数

1:バッファエンプティ

処理内容 ΔΣΑ/D コンバータ変換値リングバッファから\*p\_value にデータをコピーし、リングバッファ読み出し位置を更新

する。

データの読み出しが正常に行われた場合、読み出し後の未読データ数を返す。(0~)

未読データが無い場合、何もせずに-1を返す。

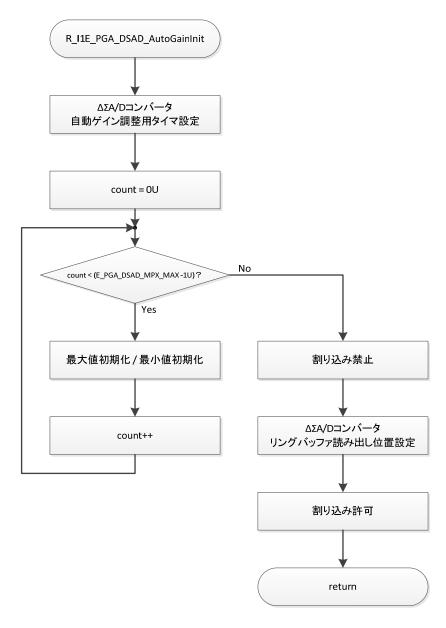

# 5.12 PGA 自動ゲイン用変数初期化

# void R\_I1E\_PGA\_DSAD\_AutoGainInit(void)

説明 PGA 自動ゲイン用変数初期化

引数 なし

グローバル変数 gs\_dsad\_auto\_gain\_buffer[]:

PGA 自動ゲイン調整用バッファ

g\_dsad\_value\_write\_pos:

DSAD 変換値格納バッファ書き込み位置

g\_dsad\_value\_read\_pos:

DSAD 変換値格納バッファ読み出し位置

SFR なし 戻り値 なし

処理内容 PGA 自動ゲイン調整用変数を初期化する。

# 5.13 24 ビットΔ Σ A/D コンバータ変換完了後 PGA 自動ゲイン調整検査処理関数

# e\_auto\_gain\_return\_t R\_I1E\_PGA\_DSAD\_AutoGainBufCheck(void)

説明 24 ビット ΔΣΑ/D コンバータ変換完了後 PGA 自動ゲイン調整検査処理関数

引数 なし

グローバル変数 g\_dsad\_value\_write\_pos:

DSAD 変換値格納バッファ書き込み位置

g\_dsad\_value\_read\_pos:

DSAD 変換値格納バッファ読み出し位置

g\_dsad\_value[]:

DSAD 変換値格納バッファ gs\_dsad\_current\_gain\_set1[]: 現在の前段ゲイン値

gs\_dsad\_auto\_gain\_buffer[]: PGA 自動ゲイン調整用バッファ

SFR なし

戻り値 e\_auto\_gain\_return\_t:

E\_AUTO\_GAIN\_NO\_ADJUSTMENT PGA ゲイン調整なし E\_AUTO\_GAIN\_ADJUSTMENT PGA ゲイン調整あり

処理内容  $\Delta\Sigma A/D$  コンバータの測定結果から最大値/最小値を更新し、この値からゲインが適切でないと判断される場合、 PGA ゲインの自動調整を行う。

R\_I1E\_PGA\_DSAD\_AutoGainBufCheck E\_AUTO\_GAIN\_NO\_ADJUSTMENT 測定データ更新有り? Yes 温度センサ用チャネル以外? Yes 前段ゲイン値更新 オーバーフロー発生? Yes 最大値<取得値? ΔΣΑ/Dコンバータ・ゲイン-1ダウン (結果はretに格納) Yes 最大値更新 ゲイン調整実行有り? Yes 最小值>取得值? ΔΣΑ/Dコンバータ 自動ゲイン用変数初期化 Yes 最小值更新 リングバッファ読み出し位置更新 return (ret)

# 5.14 24 ビット Δ Σ A/D コンバータ・PGA 自動ゲイン調整関数

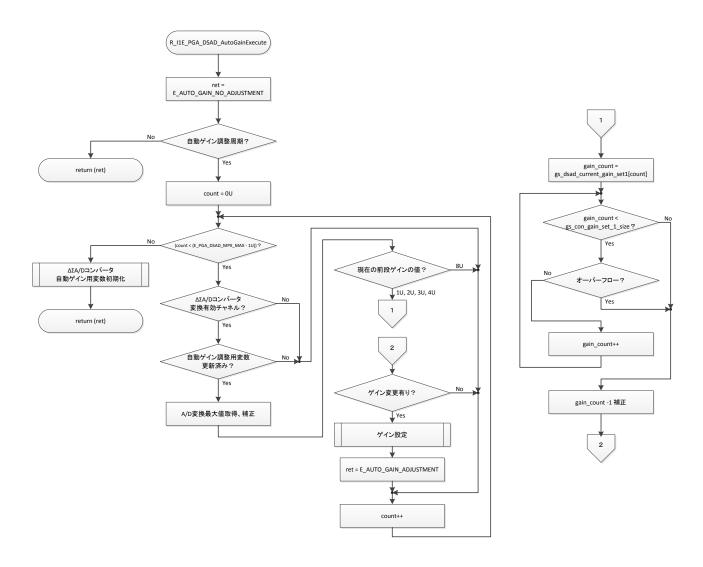

# e\_auto\_gain\_return\_t R\_I1E\_PGA\_DSAD\_AutoGainExecute(void)

説明 24 ビット  $\Delta\Sigma$ A/D コンバータ・PGA 自動ゲイン調整関数

引数 なし

グローバル変数 gs\_dsad\_auto\_gain\_timer:

PGA 自動ゲイン調整用タイマ

g\_dsad\_setting[]:

24 ビット ΔΣΑ/D コンバータ設定値

gs\_dsad\_auto\_gain\_buffer[]: PGA 自動ゲイン調整用バッファ

gs\_dsad\_current\_gain\_set1[]: 現在の前段ゲイン値

gs\_con\_gain\_set\_1\_size: 前段ゲインの倍率数

SFR なし

戻り値 e\_auto\_gain\_return\_t:

E\_AUTO\_GAIN\_NO\_ADJUSTMENT PGA ゲイン調整なし E\_AUTO\_GAIN\_ADJUSTMENT PGA ゲイン調整あり

処理内容  $\Delta\Sigma A/D$  コンバータの指定入力マルチプレクサにおいて PGA 自動ゲイン調整を行う。

# 5.15 PGA オフセット調整実行関数

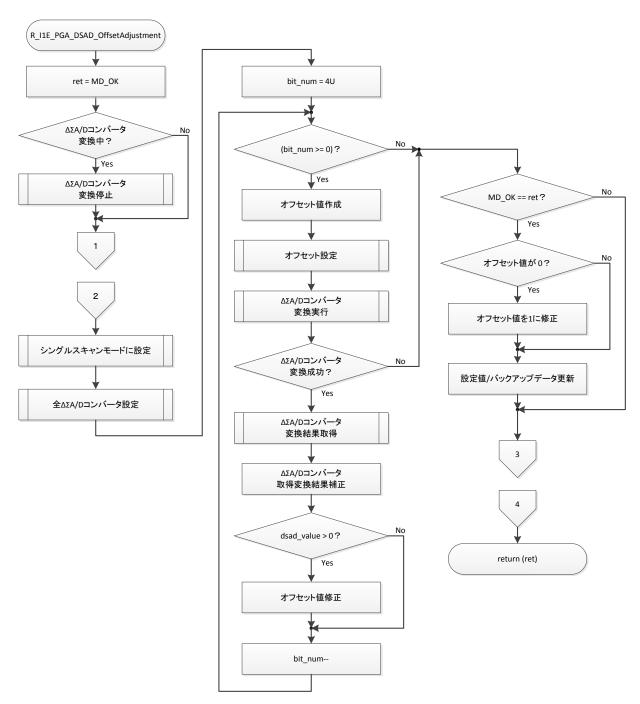

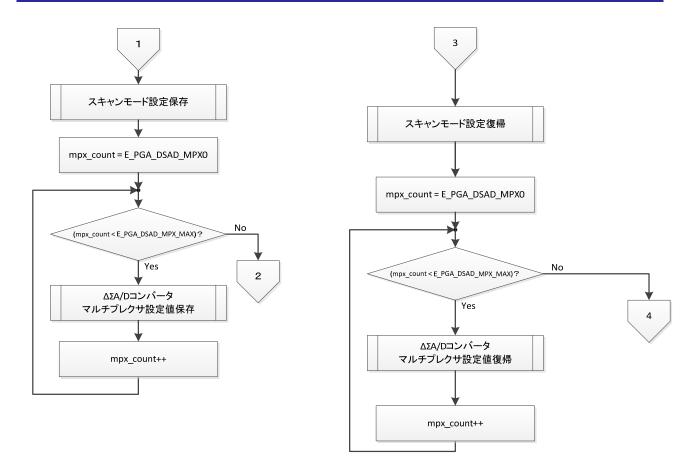

# MD\_STATUS R\_I1E\_PGA\_DSAD\_OffsetAdjustment(e\_pga\_dsad\_mpx\_t dsad\_mpx)

説明 PGA オフセット調整実行関数

引数 dsad\_mpx:

24 ビット ΔΣΑ/D コンバータ 入力マルチプレクサ番号

グローバル変数 なし SFR なし

戻り値 MD\_STATUS:

MD\_OK MD\_ERROR

処理内容 ΔΣΑ/D コンバータの指定入力マルチプレクサにおいてプログラマブル・ゲイン計装アンプのオフセット調整を行

い、結果をフラッシュ格納用構造体のオフセット誤差補正値配列に格納する。

オフセット調整に失敗した場合、MD\_ERROR を返す。

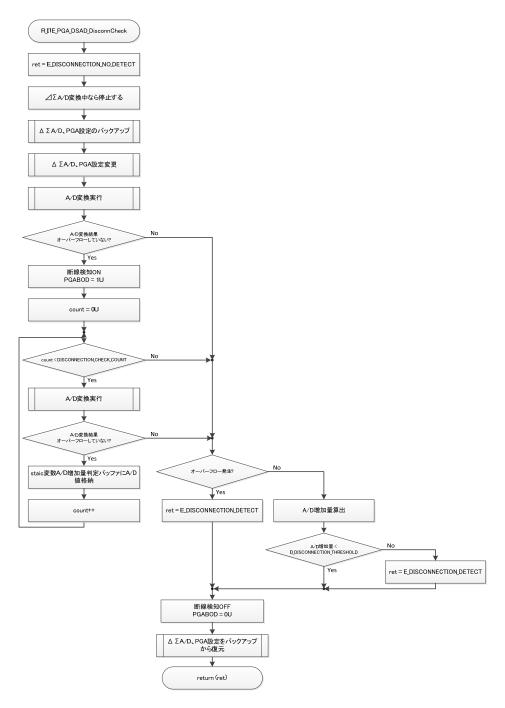

## 5.16 断線検知チェック関数

## e\_disconnection\_return\_t R\_I1E\_PGA\_DSAD\_DisconnCheck(e\_pga\_dsad\_mpx\_t dsad\_mpx)

説明 断線検知チェック関数

引数 dsad\_mpx:

24 ビット ΔΣΑ/D コンバータ 入力マルチプレクサ番号

グローバル変数 なし SFR なし

戻り値 e\_disconnection\_return\_t:

E\_DISCONNECTION\_NO\_DETECT 非断線状態 E\_DISCONNECTION\_DETECT 断線状態

処理内容  $\Delta\Sigma A/D$  コンバータの指定入力マルチプレクサにおいて断線検知を行う。

断線を検知した場合、E\_DISCONNECTION\_DETECT を返す。

## 5.17 RL78/I1E AFE 停止処理関数

## void R\_I1E\_AFE\_Stop(void)

説明 RL78/I1E AFE 停止処理関数

引数 なし グローバル変数 なし SFR PERO:

周辺イネーブル・レジスタ 0

AFEPWS:

アナログ・フロントエンド電源選択レジスタ

AFEPON:

AFE 基準電源 (ABGR) 部の電源制御レジスタ

PFR1·

周辺イネーブル・レジスタ 1

AFEEN:

AFE 電源・クロック制御部入力クロック供給の制御レジスタ

戻り値 なし

処理内容 アナログ・フロントエンドを停止状態にする。

## 5.18 RL78/I1E AFE 再始動処理関数

#### void R I1E AFE ReStart(void)

説明 RL78/I1E AFE 再始動処理関数

引数 なし グローバル変数 なし SFR AFEEN:

AFE 電源・クロック制御部入力クロック供給の制御レジスタ

AFEPON:

AFE 基準電源(ABGR)部の電源制御レジスタ

AFESTAT:

AFE 基準電源 (ABGR) 部の電源状態

AFECKS:

アナログ・フロントエンド・クロック選択レジスタ

PGAEN:

PGA および 24 ビット ΔΣΑ/D コンバータの入力クロック供給の制御

DSADMR:

ΔΣA/D コンバータ・モード・レジスタ

PGAPON:

プログラマブル・ゲイン計装アンプ(PGA)部の電源制御

PGASTAT:

プログラマブル・ゲイン計装アンプ(PGA)部の電源状態

戻り値 なし

処理内容 アナログ・フロントエンドを使用可能状態にする。

# 5.19 コンフィギュラブル・アンプ トリミング実行関数

void R\_I1E\_CAMP\_Calibration(uint8\_t \*camp\_trimming)

説明 コンフィギュラブル・アンプ トリミング実行関数

引数 \*camp\_trimming:

コンフィギュラブル・アンプ n トリミング設定値

グローバル変数 なし

SFR AMPOCAL:

コンフィギュラブル・アンプ 0 トリミング・レジスタ

AMP1CAL:

コンフィギュラブル・アンプ 1 トリミング・レジスタ

AMP2CAL:

コンフィギュラブル・アンプ 2 トリミング・レジスタ

戻り値 なし

処理内容 コンフィギュラブル・アンプの入力オフセットトリミングを行い、\*camp\_trimming に結果を格納する。

## 6. フラッシュ・メモリ関連 API

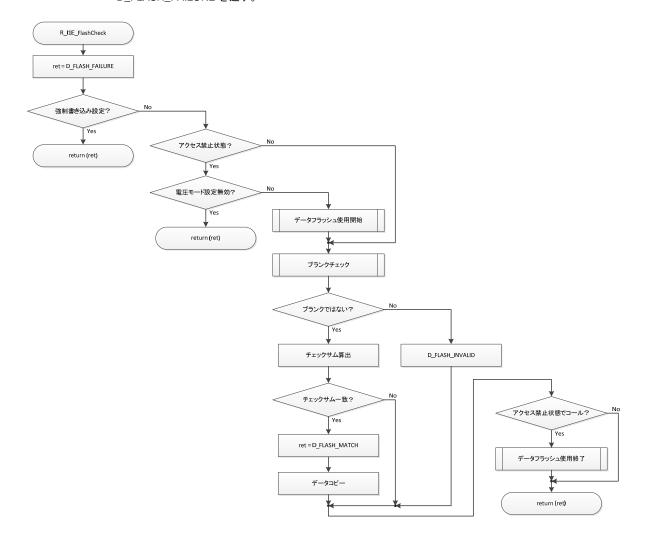

## 6.1 データフラッシュ・メモリ格納データチェック関数

## uint8\_t R\_I1E\_FlashCheck(void)

説明 データフラッシュ・メモリ格納データチェック関数

引数 なし

グローバル変数 g\_flash\_value:

データ・フラッシュ格納データ構造体

SFR DFLCTL:

データ・フラッシュ・コントロール・レジスタ

戻り値 uint8\_t:

D\_FLASH\_MATCH D\_FLASH\_FAILURE D\_FLASH\_INVALID

処理内容 データ・フラッシュの特定ブロックがブランクではなかった場合、かつ、データ・フラッシュに書き込まれて

いるデータとチェックサムに齟齬がなかった場合、フラッシュ格納用構造体にデータを読み出し、

D\_FLASH\_MATCH を返す。

データ・フラッシュの特定ブロックがブランクだった場合は、データの読み出しは行わずに D\_FLASH\_INVALID

を返す。

データ・フラッシュに記録されているデータが異常だった場合、データ・フラッシュへのアクセスができなかった場合、及び、フラッシュデータ強制書き込み設定の場合、フラッシュ格納用構造体への読み出しは行わずに D\_FLASH\_FAILURE を返す。

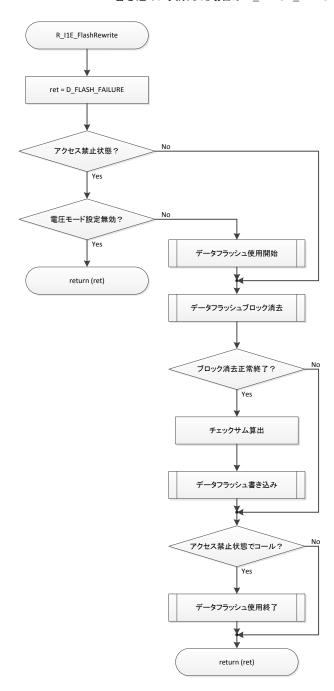

## 6.2 データフラッシュ・メモリ格納データ上書き関数

## uint8\_t R\_I1E\_FlashRewrite(str\_flash\_data\_t \*p\_flash\_value)

説明 データフラッシュ・メモリ格納データ上書き関数

引数 \*p\_flash\_value:

フラッシュ・メモリ書き込みデータ格納バッファポインタ

グローバル変数 なし

SFR DFLCTL:

データ・フラッシュ・コントロール・レジスタ

戻り値 uint8 t:

D\_FLASH\_SUCCESS

D\_FLASH\_FAILURE

処理内容データ・フラッシュの特定ブロックに指定データとチェックサムの上書きを行う。

書き込みに失敗した場合は D\_FLASH\_FAILURE を返す。

## 7. UART 通信関連 API

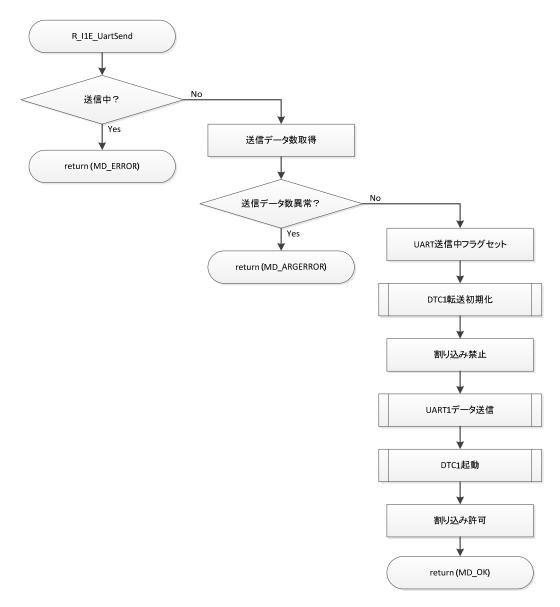

# 7.1 PC 送信処理設定関数(ASCII)。[1 回の送信で 256byte までの制限付き]

## MD\_STATUS R\_I1E\_UartSend(int8\_t \*p\_send\_data)

説明 PC 送信処理設定関数(ASCII)。[1 回の送信で 256byte までの制限付き]

引数 \*p\_send\_data:

送信バッファアドレス

グローバル変数 g\_tx\_in\_process\_flag:

UART 送信中フラグ

SFR なし

戻り値 MD\_STATUS:

MD\_OK MD\_ERROR MD\_ARGERROR

処理内容 データ・トランスファ・コントローラのコントロールデータ 1 を使用し、UART1 より指定文字列の送信を行う。

既に送信中の場合、何もせずに MD\_ERROR を返す。

指定文字列サイズが不正な場合、何もせずに MD\_ARGERROR を返す。

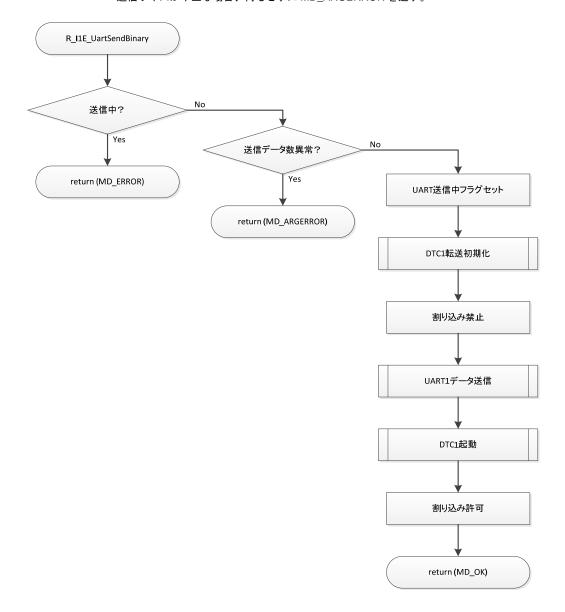

# 7.2 PC 送信処理設定関数(Binary)。[1 回の送信で 256byte までの制限付き]

## MD\_STATUS R\_I1E\_UartSendBinary(int8\_t \*p\_send\_data, uint16\_t send\_length)

説明 PC 送信処理設定関数(Binary)。[1 回の送信で 256byte までの制限付き]

引数 \*p\_send\_data:

送信バッファアドレス

send\_length: 送信サイズ

グローバル変数 g\_tx\_in\_process\_flag:

UART 送信中フラグ

SFR なし

戻り値 MD\_STATUS:

MD\_OK MD\_ERROR MD\_ARGERROR

処理内容 データ・トランスファ・コントローラのコントロールデータ 1 を使用し、UART1 より指定バイト数の送信を行

う。

既に送信中の場合、何もせずに MD\_ERROR を返す。

送信サイズが不正な場合、何もせずに MD\_ARGERROR を返す。

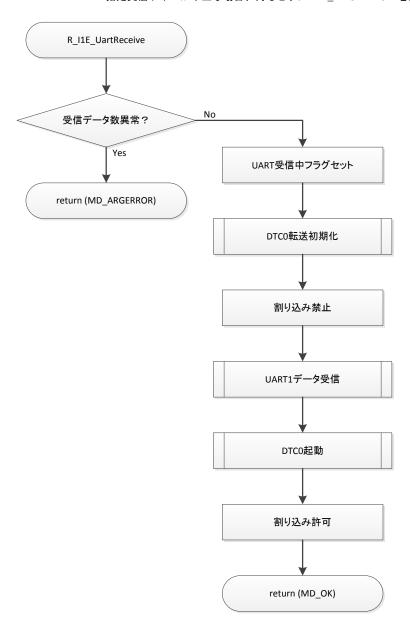

# 7.3 PC からの受信処理(DTC0 使用)。[1 回の受信で 256byte までの制限付き]

## MD\_STATUS R\_I1E\_UartReceive(int8\_t \*p\_receive\_data, uint8\_t receive\_length)

説明 PC からの受信処理(DTC0 使用)。[1 回の受信で 256byte までの制限付き]

引数 \*p\_receive\_data:

受信バッファアドレス

receive\_length:

指定受信サイズ

グローバル変数 g\_rx\_in\_process\_flag:

UART 受信中フラグ

SFR なし

戻り値 MD\_STATUS:

$\mathsf{MD}_\mathsf{OK}$

MD\_ARGERROR

処理内容 データ・トランスファ・コントローラのコントロールデータ 0 を使用し、UART1 より指定バイト数の受信を行

つ。

指定受信サイズが不正な場合、何もせずに MD\_ARGERROR を返す。

## 8. フリーランタイマ関連 API

### 8.1 フリーランタイマ・設定初期化関数

## void R\_TAU\_FreeRunTimerInit(void)

説明 フリーランタイマ・設定初期化関数

引数 なし グローバル変数 なし SFR TDR11:

タイマ・データ・レジスタ 11

戻り値 なし

処理内容

フリーランタイマの設定を初期化し、タイマ動作を開始する。

## 8.2 フリーランタイマ・停止関数

## void R\_TAU\_FreeRunTimerStop(void)

説明 フリーランタイマ・停止関数

引数 なし グローバル変数 なし SFR なし 戻り値 なし

処理内容 フリーランタイマを停止する。

## 8.3 フリーランタイマ・現在カウント値取得関数

## uint32\_t R\_GetTickCount(void)

説明 フリーランタイマ・現在カウント値取得関数

引数 なし

グローバル変数 g\_freerun\_timer:

フリーランタイマカウンタ変数

SFR TCR11:

タイマ・カウンタ・レジスタ 11

戻り値 uint32\_t:

32bit のフリーランタイマ値

処理内容 フリーランタイマの現在のカウント値を取得し、これを返す。

## 8.4 フリーランタイマ・カウント値比較関数

# int32\_t R\_CmpTickCount(uint32\_t freerun\_counter)

説明 フリーランタイマ・カウント値比較関数

引数 freerun\_counter:

比較対象のタイマ・カウント値

グローバル変数 なし SFR なし

> 戻り値 int32\_t: 0 未満 : 未経過状態

> > 0 以上: 経過状態

処理内容

フリーランタイマの現在のカウント値と指定のカウント値を比較し、結果を返す。

## 9. キー判定関連 API

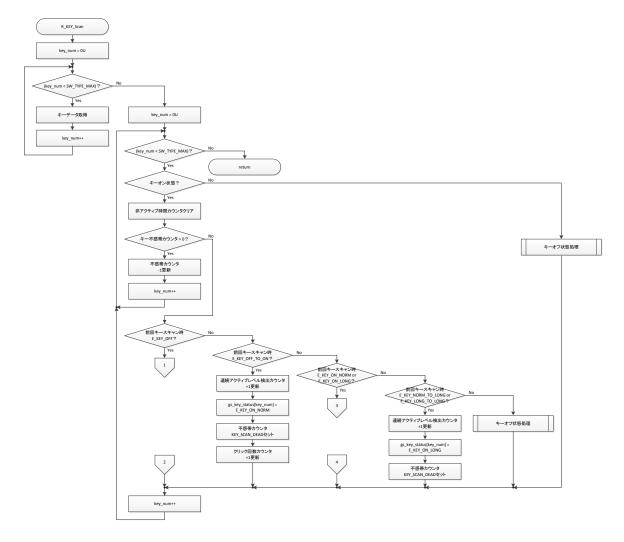

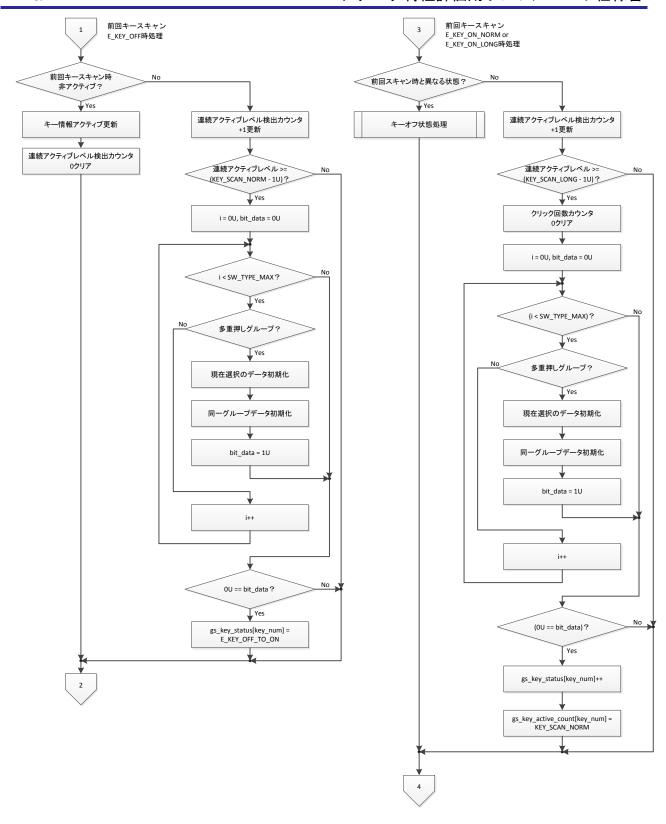

## 9.1 キースキャン処理

## void R\_KEY\_Scan(void)

説明 キースキャン処理

引数 なし

グローバル変数 g\_con\_key\_setting[]:

ユーザー設定キー情報

gs\_key\_status[]:

キー情報配列

gs\_key\_setting\_old: 最終キー情報

gs\_key\_active\_count[]:

連続アクティブレベル検出回数カウンタ配列

gs\_key\_dead\_zone\_count[]:

スイッチ状態変更後の不感帯カウンタ配列

gs\_key\_non\_active\_count[]:

連続非アクティブレベル検出回数カウンタ配列

gs\_key\_click\_count[]:

クリック回数カウンタ配列

SFR

なし

戻り値

なし

処理内容キー入力として設定されたポートの入力状態を確認し、各キー情報を更新する。

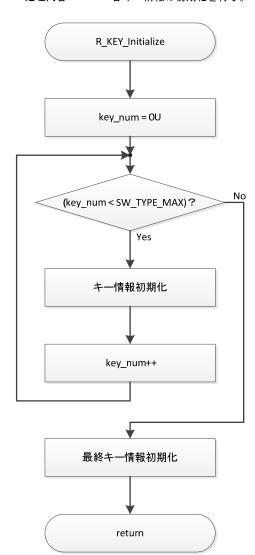

## 9.2 キー情報初期化

## void R\_KEY\_Initialize(void)

説明 キー情報初期化

引数 なし

グローバル変数 gs\_key\_setting\_old:

最終キー情報

gs\_key\_active\_count[]:

連続アクティブレベル検出回数カウンタ配列

gs\_key\_dead\_zone\_count[]:

スイッチ状態変更後の不感帯カウンタ配列

gs\_key\_non\_active\_count[]:

連続非アクティブレベル検出回数カウンタ配列

gs\_key\_click\_count[]:

クリック回数カウンタ配列

gs\_key\_status[]:

キー情報配列

SFR なし 戻り値 なし

処理内容 各キー情報の初期化を行う。

# 9.3 キー情報取得 (指定キーのみ)

## e\_key\_status\_t R\_KEY\_Get(e\_key\_t const key)

説明 キー情報取得 (指定キーのみ)

引数 key:

e\_key\_t で設定した SW 名

グローバル変数 gs\_key\_status[]:

キー情報配列

SFR なし

戻り値 e\_key\_status\_t:

E\_KEY\_OFF 0 The key is not pushed

E\_KEY\_OFF\_TO\_ON 1 The key was pushed ( off to normal push )

E\_KEY\_ON\_NORM 2 The key was pushed ( normal push )

E\_KEY\_NORM\_TO\_LONG 3 The key was pushed ( normal to long push )

E\_KEY\_ON\_LONG 4 The key was pushed ( push and hold )

E\_KEY\_LONG\_TO\_LONG 5 The key was pushed ( long to long push )

E\_KEY\_DOUBLE\_CLICK 6 The key was double pushed

処理内容 指定されたキーの情報を取得し、これを返す。

※この関数は既に取得されたキー情報を返すだけなので、事前に R\_KEY\_Scan()の実行が必要。

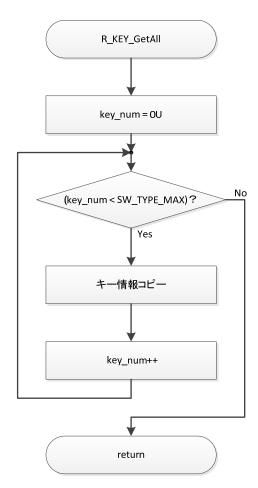

# 9.4 キー情報取得 (全キー)

# void R\_KEY\_GetAll(e\_key\_status\_t \* p\_status)

説明 キー情報取得 (全キー)

引数 p\_status:

キー情報配列ポインタ

グローバル変数 gs\_key\_status[]:

キー情報配列

SFR なし 戻り値 なし

処理内容全てのキー情報を指定されたキー情報配列に格納する。

※この関数は既に取得されたキー情報をコピーするだけなので、事前に R\_KEY\_Scan()の実行が必要。

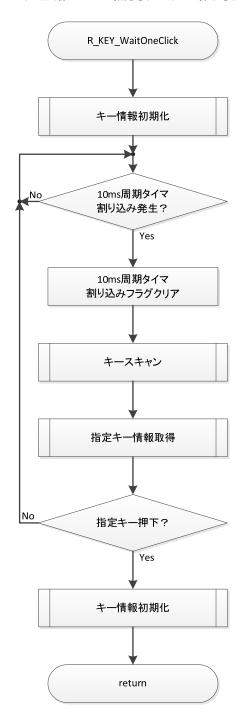

## 9.5 指定キー押下待ち

## void R\_KEY\_WaitOneClick(e\_key\_t const key)

説明 指定キー押下待ち

引数 key:

e\_key\_t で設定した SW 名

グローバル変数 g\_10ms\_timer\_flag:

10ms タイマ周期フラグ

SFR なし 戻り値 なし

処理内容 指定されたキーが押下されるまでループして待つ。

## 10. サンプルコード動作仕様

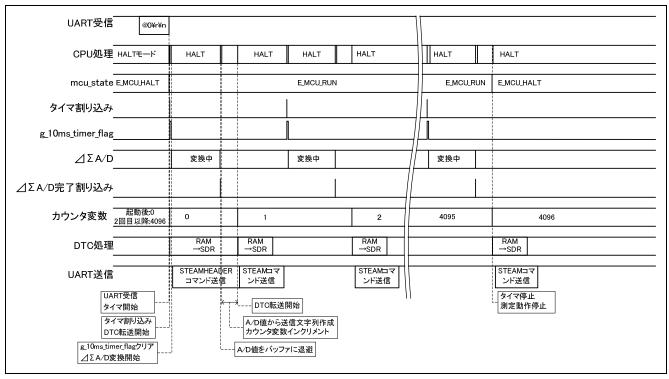

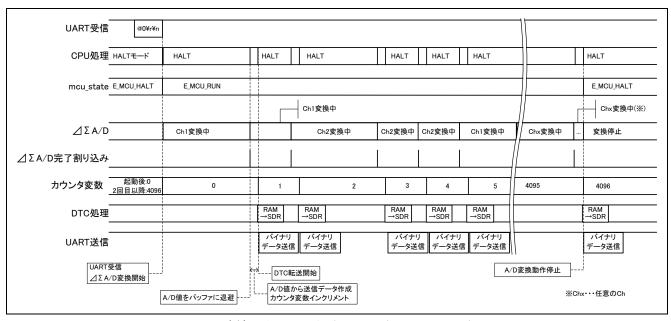

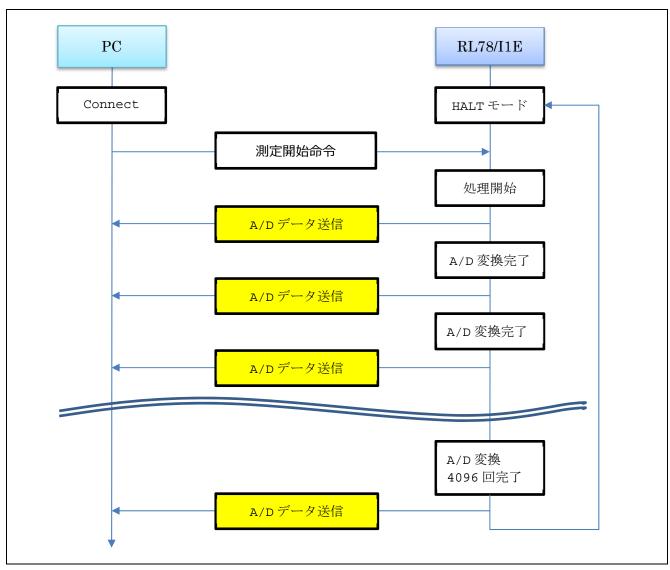

本サンプルコードでは24bit  $\Delta$   $\Sigma$  A/D コンバータ動作を周期的に行い、シリアル・アレイ・ユニット (UART1) を介して PC ヘデータを送信します。 CS+のコード生成で24bit  $\Delta$   $\Sigma$  A/D コンバータのオートスキャンのモードを選択することで、A/D 変換の間欠動作または連続動作となります。

メイン関数の動作説明および PC へ送信する通信仕様について以下に示します。

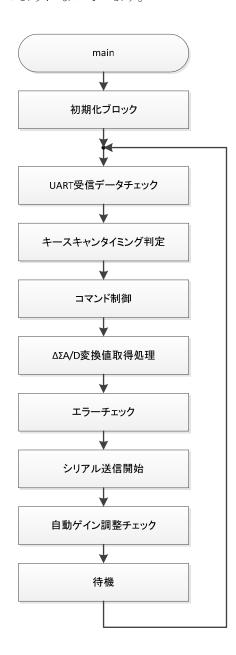

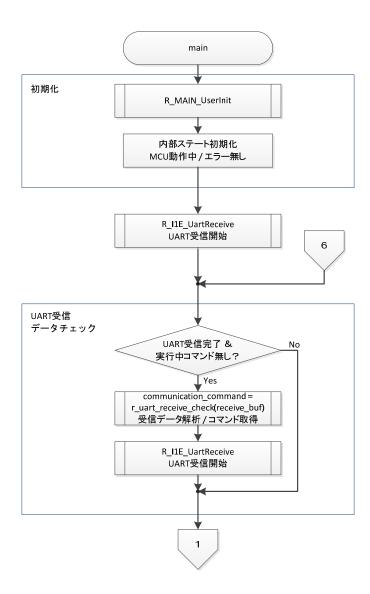

### 10.1 メイン関数動作説明

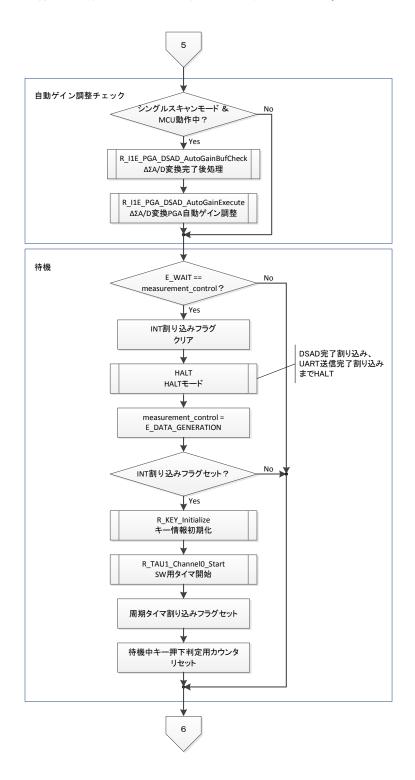

メイン関数内の初期化後の処理は大きく分けて9つのブロックで構成されており、以下のフローチャートのようになっています。

## 10.1.1 UART 受信データチェックブロック

UART 受信データチェックブロックでは UART からのデータ受信状態の確認と受信時のコマンド解析、取得、及び UART の受信再開処理を行います。

UART のデータ受信自体はデータ・トランスファ・コントローラにより行われており、このブロックはデータ受信が完了していた場合にのみ実行されます。

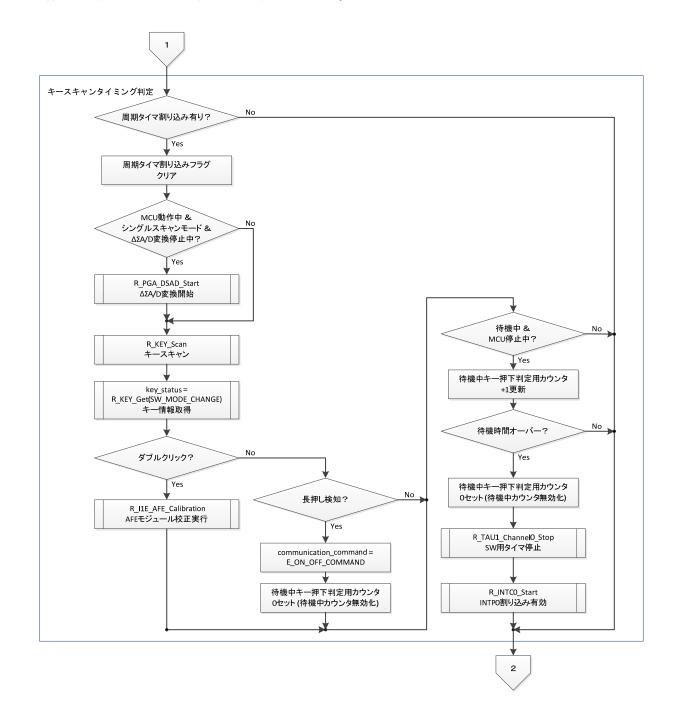

### 10.1.2 キースキャンタイミング判定ブロック

キースキャンタイミング判定ブロックでは周期タイマ割り込みのタイミングで以下の処理を行います。

- シングル・スキャンモード時、 $\Delta\Sigma$ A/D 変換の間欠実行。

- キー入力情報の取得。

- 取得したキー入力情報に合わせた各種処理。

- ▶ ダブルクリック ⇒AFE モジュール校正実行。

- ▶ 長押し ⇒A/D 変換 ON/OFF トグル処理。

- 待機中の有効キー入力監視と、一定時間キー入力が無かった場合のキー入力無効化。

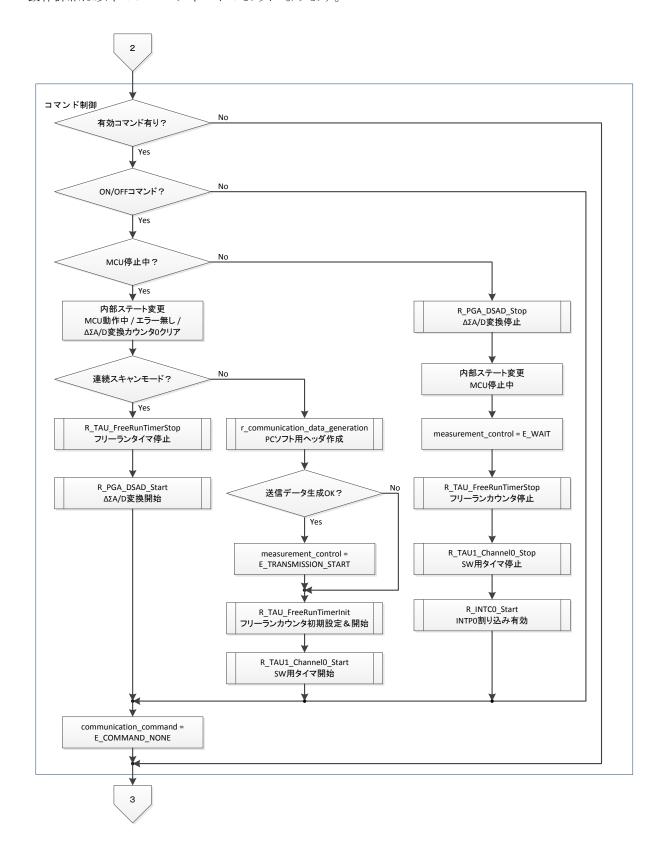

## 10.1.3 コマンド制御ブロック

コマンド制御ブロックでは受信したコマンドに合わせた各種処理を行います。

本サンプルでは ON/OFF コマンドのみ用意されています。

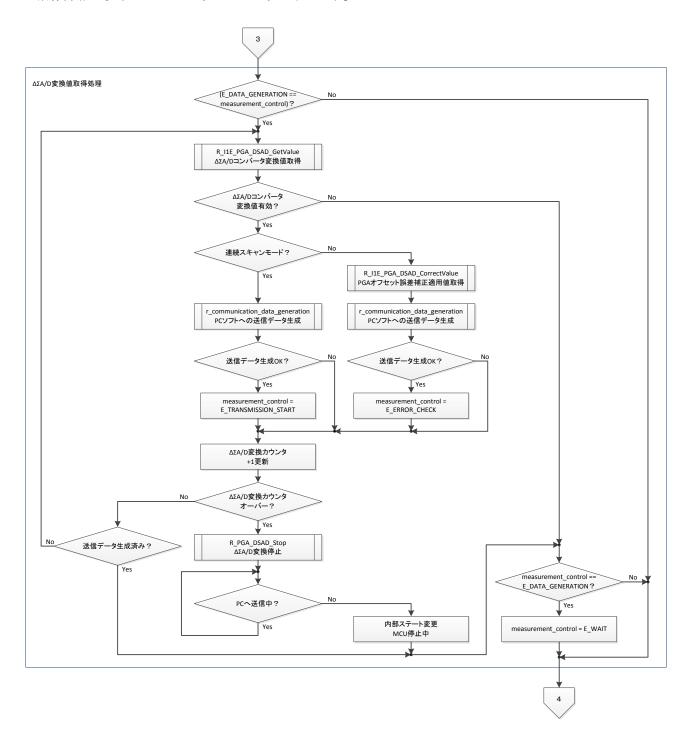

## 10.1.4 $\Delta\Sigma A/D$ 変換値取得処理ブロック

$\Delta\Sigma$ A/D 変換値取得処理ブロックではスキャンモードに応じた PC への送信データ生成を行います。また、送信データ数のカウントも行っており、一定数の A/D 変換が行われると、 $\Delta\Sigma$ A/D 変換の停止処理も行います。動作詳細は以下のフローチャートのようになります。

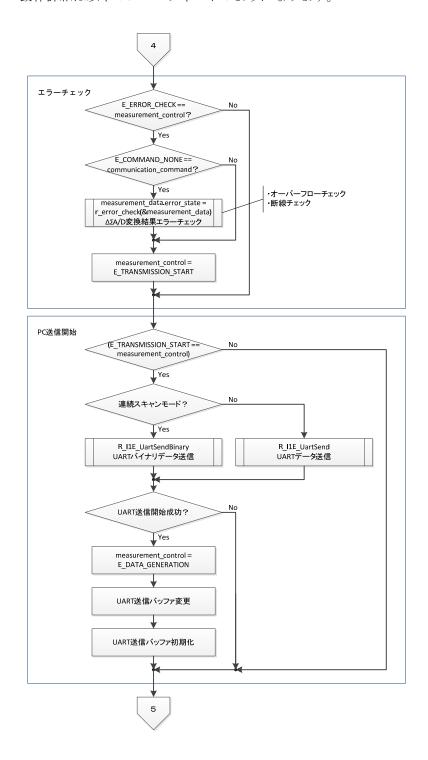

### 10.1.5 エラーチェックブロック

エラーチェックブロックでは  $\Delta\Sigma$ A/D 変換結果のエラーチェックを行います。

#### 10.1.6 シリアル送信ブロック

シリアル送信ブロックではスキャンモードに合わせた方法(Binary/ASCII)でPCへの送信を開始します。データの送信自体はデータ・トランスファ・コントローラが行っており、このブロックでは送信の開始処理のみ行います。

また、このブロックでは送信バッファの管理も行っており、データ送信の開始に成功した場合、データを 格納する送信バッファの変更処理を行います。

## 10.1.7 PGA 自動ゲイン調整チェックブロック

PGA 自動ゲイン調整チェックブロックでは、シングル・スキャンモードで動作している場合に PGA 自動ゲイン調整についての各種処理を行います。

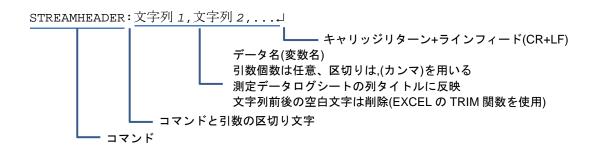

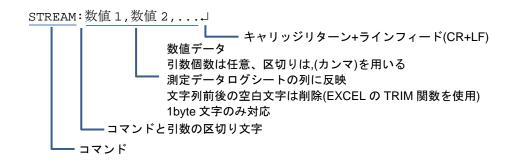

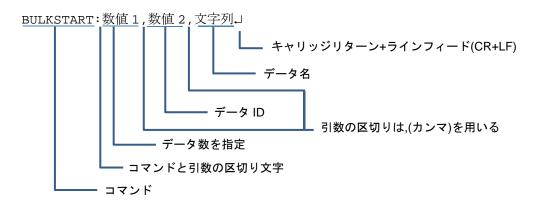

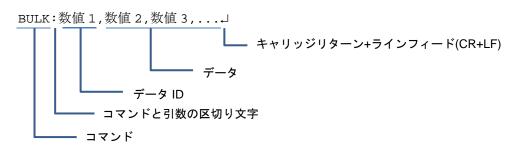

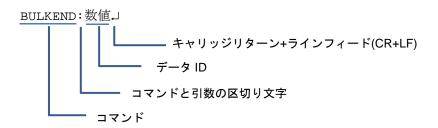

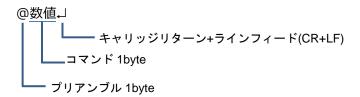

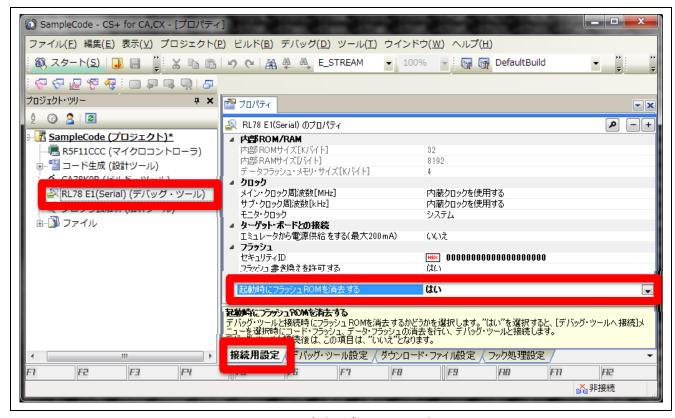

### 10.1.8 待機ブロック