# RL78/G1E Group

R01AN1055EJ0110 Rev.1.10 Sep. 30, 2013

# **Example of Measurement Using a Current Sensor**

#### Introduction

This application note describes how to measure a physical quantity (illuminance) based on the current value output from a current sensor, by using the configurable amplifier, A/D converter, and D/A converter incorporated in the RL78/G1E (R5F10FMx).

In this application note, the photodiode BS520E0F (made by Sharp Corporation) is used as the current sensor.

## **Operation Verified Devices**

RL78/G1E (R5F10FMx (x = C, D, or E))

When this application note is applied to other microcontrollers, make the necessary changes according to the specifications of the microcontroller and verify them thoroughly.

# Contents

| 1. | Sp  | ecificatio | ons                                                                                     | 3    |

|----|-----|------------|-----------------------------------------------------------------------------------------|------|

| 2. | Co  | onditions  | for Verifying Operation                                                                 | 4    |

| 3. | Re  | elated Ap  | plication Notes                                                                         | 4    |

| 4. | На  | ardware    |                                                                                         | 5    |

|    | 4.1 | Hardw      | are Configuration Example                                                               | 5    |

|    | 4.2 | Function   | ons Used                                                                                | 6    |

|    | 4.3 | Pins U     | sed                                                                                     | 7    |

| 5. | De  | escription | of Features                                                                             | 8    |

|    | 5.1 | Curren     | t Sensor                                                                                |      |

|    |     | 5.1.1      | Overview of current sensors                                                             |      |

|    |     | 5.1.2      | Overview of photodiode (BS520E0F)                                                       | 9    |

|    | 5.2 | Config     | urable Amplifier (Used As a Transimpedance Amplifier)                                   | 10   |

|    |     | 5.2.1      | Example of general amplifier and signal converter                                       | . 10 |

|    |     | 5.2.2      | Example of amplifier and signal converter configured by using a configurable amplifier. |      |

|    | 5.3 | A/D Co     | onverter                                                                                | . 12 |

|    |     | 5.3.1      | Overview of A/D converter incorporated in RL78/G1E (R5F10FMx)                           | . 12 |

|    |     | 5.3.2      | Connecting the configurable amplifier (used as a transimpedance amplifier)              |      |

|    |     |            | to the A/D converter                                                                    | .12  |

|    | 5.4 | ,          | Arithmetic Operation)                                                                   |      |

|    | 5.5 | LCD M      | lodule                                                                                  | . 14 |

| 6. | An  | alog Blo   | ck of RL78/G1E (R5F10FMx)                                                               | . 15 |

|    | 6.1 | Overvi     | ew of Analog Block of RL78/G1E (R5F10FMx)                                               | . 15 |

|    | 6.2 | Function   | ons of Analog Block of RL78/G1E (R5F10FMx)                                              | 16   |

|    |     | 6.2.1      | Configurable amplifier                                                                  |      |

|    |     | 6.2.2      | Reference voltage generator and variable output voltage regulator                       |      |

|    |     | 6.2.3      | D/A converter                                                                           |      |

|    |     | 6.2.4      | SPI                                                                                     |      |

|    | 6.3 | Setting    | s of SPI Control Registers of RL78/G1E (R5F10FMx)                                       | 26   |

| 7. | Mi  | crocontro  | oller Block of RL78/G1E (R5F10FMx)                                                      | . 33 |

|    | 7.1 | Function   | ons Assigned to the Microcontroller Block of the RL78/G1E (R5F10FMx)                    | . 33 |

|    | 7.2 | Function   | ons of the Microcontroller Block of the RL78/G1E (R5F10FMx)                             | . 34 |

|    |     | 7.2.1      | High-speed on-chip oscillator (clock generator)                                         | . 34 |

|    |     | 7.2.2      | SPI control                                                                             | 36   |

|    |     | 7.2.3      | A/D converter                                                                           | 41   |

|    |     | 7.2.4      | Timer array unit 0                                                                      | 43   |

|    |     | 7.2.5      | LCD module control                                                                      | 45   |

|    | 7.3 | Softwa     | ıre                                                                                     | 46   |

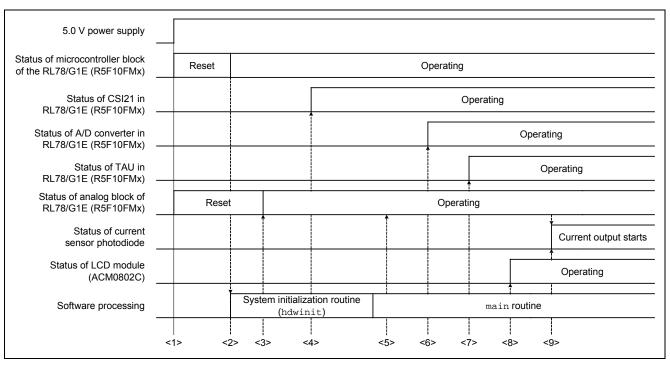

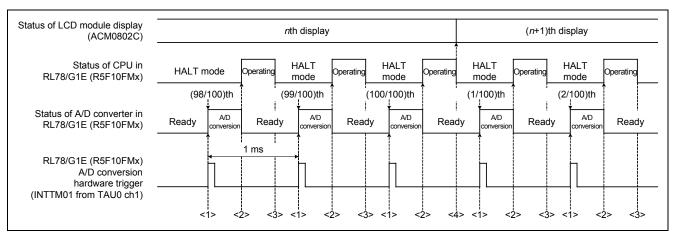

|    |     | 7.3.1      | Timing charts                                                                           | 46   |

|    |     | 7.3.2      | Register settings specified for the microcontroller block of the RL78/G1E (R5F10FMx).   | 48   |

|    |     | 7.3.3      | Functions                                                                               |      |

|    |     | 7.3.4      | Function specifications                                                                 | 71   |

|    |     | 7.3.5      | RAM variables                                                                           |      |

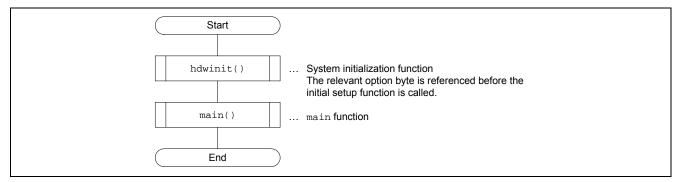

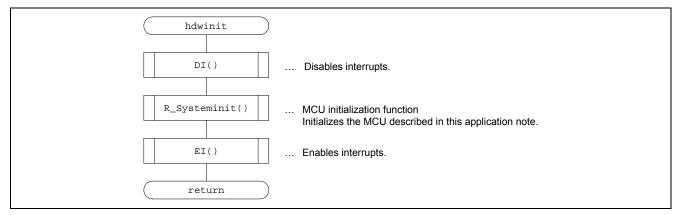

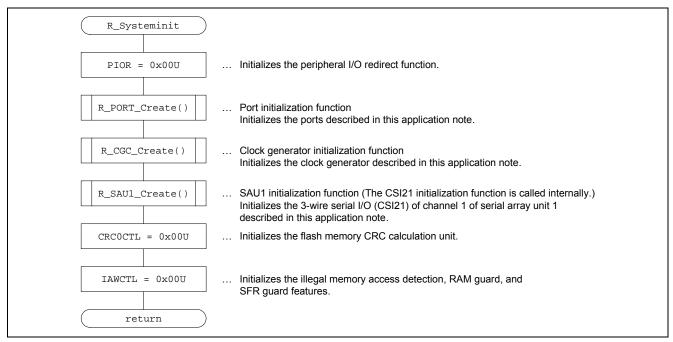

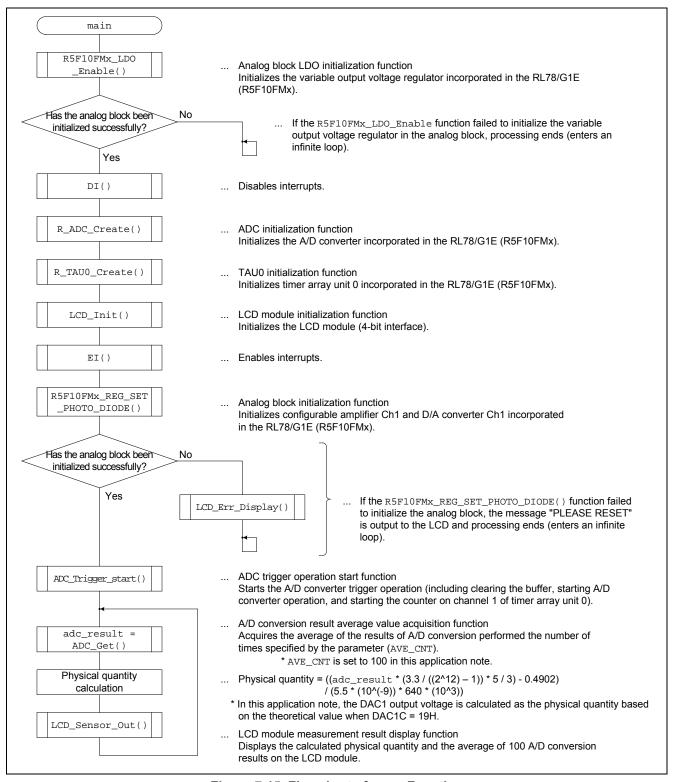

|    |     | 7.3.6      | Flowcharts                                                                              | . 80 |

|    |     | 7.3.7      | Source files and changes applied to the code output from the code generator             | . 88 |

# 1. Specifications

This application note describes how a current sensor is used by providing an example of a system in which the RL78/G1E (R5F10FMx) is used to measure the illuminance based on the current output from a photodiode (BS520E0F).

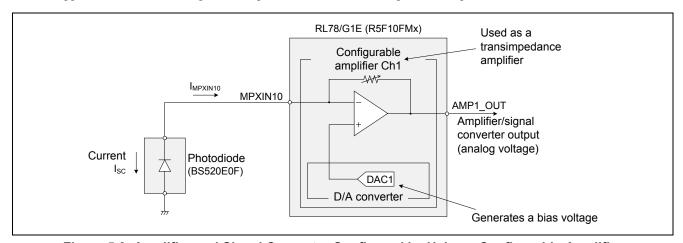

In this application note, a case is presented in which a current output from a photodiode is converted to a voltage and then amplified by using the configurable amplifier (used as a transimpedance amplifier) incorporated in the RL78/G1E (R5F10FMx).

The converted and amplified voltage is further converted to a digital value by using the A/D converter incorporated in the RL78/G1E (R5F10FMx).

The illuminance is calculated from the obtained digital value, and the result is displayed on the LCD module (ACM0802C) connected to the RL78/G1E (R5F10FMx).

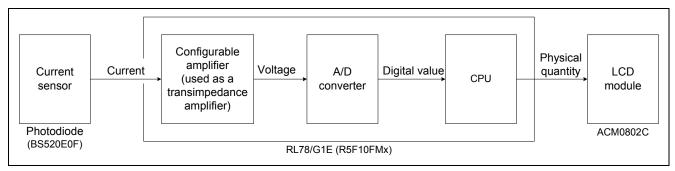

Figure 1.1 shows a block diagram, and Table 1.1 shows the elements included in the block diagram.

Figure 1.1 Block Diagram

Table 1.1 Description of the Elements in the Block

| Element                  | Function                                                    | Description                                                                                                                 |

|--------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Photodiode<br>(BS520E0F) | Current sensor                                              | Outputs a current in accordance with the illuminance.                                                                       |

| RL78/G1E<br>(R5F10FMx)   | Configurable amplifier (used as a transimpedance amplifier) | Converts the current output from a photodiode to a voltage and amplifies it.                                                |

|                          | A/D converter                                               | Converts the analog voltage output from the configurable amplifier (used as a transimpedance amplifier) to a digital value. |

|                          | CPU                                                         | Calculates the physical quantity (illuminance) from the digital value converted by the A/D converter.                       |

| ACM0802C                 | LCD module                                                  | Displays the physical quantity (illuminance) calculated by the CPU.                                                         |

# 2. Conditions for Verifying Operation

The operation of the sample code shown in this application note has been verified under the conditions shown below.

**Table 2.1 Conditions for Verifying Operation**

| Item                    | Description                                                            |  |  |

|-------------------------|------------------------------------------------------------------------|--|--|

| Microcontroller used    | RL78/G1E (R5F10FME)                                                    |  |  |

| Operating frequency     | High-speed on-chip oscillator (high-speed OCO) clock: 32 MHz           |  |  |

|                         | CPU/peripheral hardware clock: 32 MHz                                  |  |  |

| Operating voltage       | VDD, DVDD, AVDD1, AVDD2, AVDD3, and LCD module power supply: 5.0 V     |  |  |

|                         | AVDD: 3.3 V                                                            |  |  |

|                         | LVD detection voltage (VLVIH): 4.06 V when rising, 3.98 V when falling |  |  |

| External devices used   | Photodiode (BS520E0F)                                                  |  |  |

|                         | LCD module (ACM0802C-NLW-BBH)                                          |  |  |

| Integrated development  | CubeSuite+ V1.01.01 [31 Jan 2012] made by Renesas Electronics          |  |  |

| environment             |                                                                        |  |  |

| C compiler (build tool) | CA78K0R V1.30 made by Renesas Electronics                              |  |  |

# 3. Related Application Notes

Related application notes are shown below. Also refer to these documents when using this application note.

- RL78/G13 Initialization (R01AN0451E) Application Note

- RL78/G13 Timer Array Unit (Interval Timer) (R01AN0456E) Application Note

- RL78/G13 Serial Array Unit for 3-Wire Serial I/O (Master Transmission/Reception) (R01AN0460E) Application Note

#### 4. Hardware

# 4.1 Hardware Configuration Example

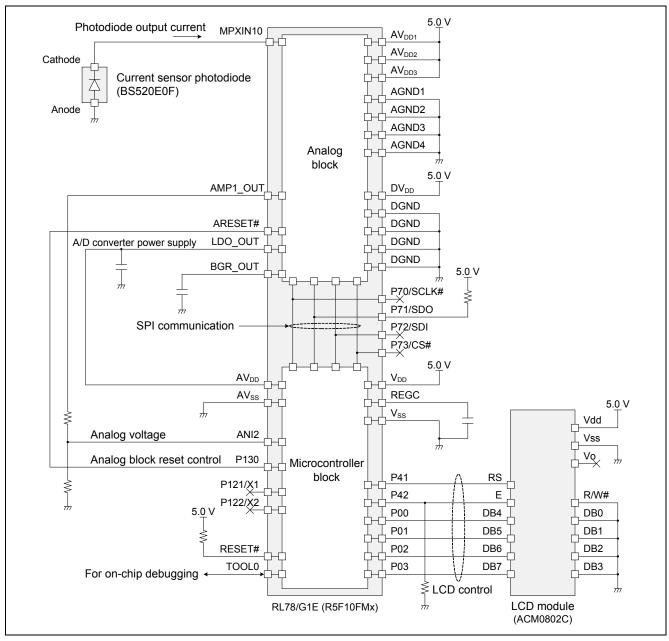

**Figure 4.1** shows an example of the hardware configuration described in this application note.

Figure 4.1 Hardware Configuration

Caution This circuit diagram is simplified to show an overview of the circuit connection. When designing an actual circuit, connect pins appropriately so as to satisfy the electrical specifications. (Connect unused input-only ports individually to VDD or Vss via a resistor.)

# 4.2 Functions Used

**Table 4.1** shows the RL78/G1E (R5F10FMx) peripheral functions used in this application note and their applications.

Table 4.1 RL78/G1E (R5F10FMx) Peripheral Functions and Their Applications

|                       | 8/G1E (R5F10FMx) Peripheral                    | Application                                                                                                          |  |  |

|-----------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| block                 | Configurable amplifier                         | Used as a transimpedance amplifier that converts the current output from a photodiode to a voltage and amplifies it. |  |  |

| Analog b              | D/A converter                                  | Generates a bias voltage for the configurable amplifier (used as a transimpedance amplifier).                        |  |  |

| A                     | Variable output voltage regulator              | Generates the power supply voltage for the A/D converter.                                                            |  |  |

|                       | SPI                                            | Controls SPI communication with the microcontroller block of the RL78/G1E (R5F10FMx).                                |  |  |

| lock                  | A/D converter                                  | Converts the voltage output from the configurable amplifier (used as a transimpedance amplifier) to a digital value. |  |  |

| Microcontroller block | Serial array unit 1 (channel 1: CSI21)         | Controls SPI communication with the analog block by using the 3-wire serial I/O function.                            |  |  |

| ntr                   | I/O ports                                      | Controls the analog block and external LCD module.                                                                   |  |  |

| 000                   | Timer array unit 0 (channel 1)                 | Generates a hardware trigger signal for the A/D converter.                                                           |  |  |

| lici                  | Timer array unit 0 (channel 3)                 | Generates the wait time used by software.                                                                            |  |  |

| 2                     | High-speed on-chip oscillator (high-speed OCO) | Generates the 32 MHz clock used as the main system clock.                                                            |  |  |

# 4.3 Pins Used

**Table 4.2** shows the RL78/G1E (R5F10FMx) pins used in this application note and their features.

Table 4.2 RL78/G1E (R5F10FMx) Pins Used and Their Features

| Pin Name | I/O    | Description                                                                                                                                                                                                                                                                            |

|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPXIN10  | Input  | This is an inverted input pin of the configurable amplifier Ch1 (used as a transimpedance amplifier) in the analog block. The output signal from photodiode is input to this pin.                                                                                                      |

| AMP1_OUT | Output | This is an output pin of the configurable amplifier Ch1 (used as a transimpedance amplifier) in the analog block. This pin is connected to the ANI2 pin of the A/D converter in the microcontroller block via a resistor divider.                                                      |

| ANI2     | Input  | This is an analog input pin of the A/D converter in the microcontroller block. This pin is connected to the AMP1_OUT pin in the analog block via a resistor divider which steps down the output voltage from the AMP1_OUT pin. The output voltage stepped down is to be A/D converted. |

| P130     | Output | P130 is an output-only pin in the microcontroller block. This pin is connected to the ARESET# pin in the analog block and is used to control the analog reset feature of the analog block.                                                                                             |

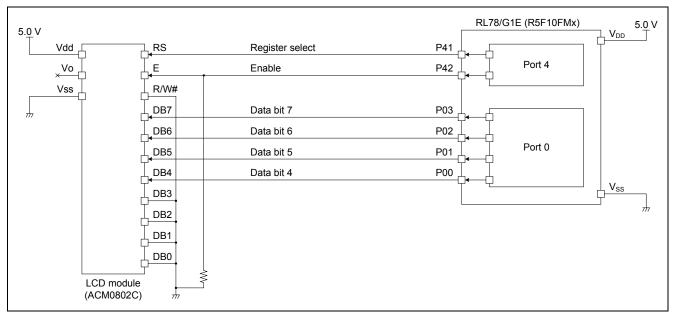

| P41      | Output | P41 is an output pin in the microcontroller block. This pin is connected to the RS pin in the LCD module and is used to control the LCD module display.                                                                                                                                |

| P42      | Output | P42 is an output pin in the microcontroller block. This pin is connected to the E pin in the LCD module and is used to control the LCD module display.                                                                                                                                 |

| P00      | Output | P00 is an output pin in the microcontroller block. This pin is connected to the DB4 pin in the LCD module. This pin is used to control the LCD module display.                                                                                                                         |

| P01      | Output | P01 is an output pin in the microcontroller block. This pin is connected to the DB5 pin in the LCD module and is used to control the LCD module display.                                                                                                                               |

| P02      | Output | P02 is an output pin in the microcontroller block. This pin is connected to the DB6 pin in the LCD module and is used to control the LCD module display.                                                                                                                               |

| P03      | Output | P03 is an output pin in the microcontroller block. This pin is connected to the DB7 pin in the LCD module and is used to control the LCD module display.                                                                                                                               |

# 5. Description of Features

#### 5.1 Current Sensor

This section provides an overview of typical current sensors and the characteristics and operation of the photodiode BS520E0F (made by Sharp Corporation).

#### 5.1.1 Overview of current sensors

The following devices typically output a current signal:

#### Photodiode

A photodiode generates a current by using the photovoltaic effect, which is effected by electrons being excited when a p-n junction is exposed to light. The current is electrically linear to the illuminance.

#### ■ Current transformer (clamp type)

When an electric current flows into a conductor wire, a magnetic field is produced according to Ampère's circuital law. By coiling the conductor around the core, electric current flows in the coil according to the magnetic flux. A current transformer is used to measure this current to obtain the value of the current flowing through the conductor indirectly.

#### ■ Electrochemical sensor

Electrochemical sensors apply an electrode reaction that causes electric current to flow according to the amount of charge produced at the interface between the measured object and an electrode. The type and density of the measured object can be determined or measured based on the type of electrode and the amount of current.

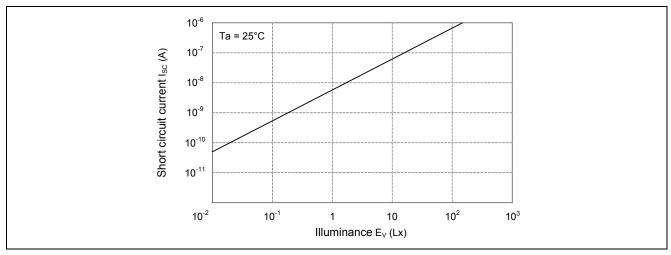

#### 5.1.2 Overview of photodiode (BS520E0F)

An overview of the photodiode BS520E0F is shown below.

The following shows the electrical characteristics extracted from the datasheet of the photodiode BS520E0F that were referenced when studying the product in this application note. Before using the product, be sure to download the latest datasheet from the Sharp website.

Specifications of photodiode BS520E0F

The extracted electrical characteristics of the photodiode BS520E0F (measurement temperature = 25°C) are shown in Table 5.1.

Table 5.1 Photodiode BS520E0F Extracted Electrical Characteristics

| Parameter             | Symbol | Conditions                     | MIN. | TYP. | MAX. | Unit |

|-----------------------|--------|--------------------------------|------|------|------|------|

| Short circuit current | Isc    | Ev = 100 Lx                    | 400  | 550  | 650  | nA   |

| Dark current          | ld     | V <sub>R</sub> = 1 V, RH ≤ 65% | _    | 3.0  | 10   | pА   |

Figure 5.1 Short Circuit Current Isc (A) vs. Illuminance Ev (Lx)

# 5.2 Configurable Amplifier (Used As a Transimpedance Amplifier)

This section shows how a current signal output from the current sensor is amplified by using two different methods: a general amplifier and signal converter, and an amplifier and signal converter that are configured by using the configurable amplifier of the RL78/G1E (R5F10FMx).

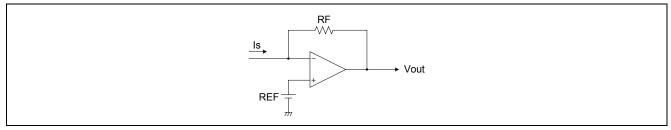

# 5.2.1 Example of general amplifier and signal converter

The photodiode outputs an electric current. To amplify the current signal and convert it to a voltage signal, a transimpedance amplifier is used. A general transimpedance amplifier is shown in **Figure 5.2**.

Figure 5.2 General Transimpedance Amplifier

The output voltage is obtained by using the following formula:

$$V_{OUT} = -RF \times I_S + REF$$

... Formula 1

# 5.2.2 Example of amplifier and signal converter configured by using a configurable amplifier

**Figure 5.3** shows an example of an amplifier and signal converter that are configured by using the configurable amplifier incorporated in the RL78/G1E (R5F10FMx).

In this application note, the configurable amplifier is used as a transimpedance amplifier.

Figure 5.3 Amplifier and Signal Converter Configured by Using a Configurable Amplifier

As a Transimpedance Amplifier

AMP1\_OUT (V), the voltage output from configurable amplifier Ch1 (used as a transimpedance amplifier), is expressed as shown in *Formula 1*, where RF ( $\Omega$ ) is the feedback resistance of the transimpedance amplifier and IMPXINIO (A) is the current input to the transimpedance amplifier.

$$AMP1\_OUT = -RF \times I_{MPXIN10} + DACI$$

... Formula 2

DAC1: D/A converter Ch1 output voltage (V)

The direction of IMPXIN10 and the short circuit current is reversed. Therefore, IMPXIN10 is expressed as shown in the formula below where the short circuit current is Isc:

$$I_{MPXINI0} = -I_{SC}$$

... Formula 3

When the configurable amplifier of the RL78/G1E (R5F10FMx) is used as a transimpedance amplifier, the output voltage ranges from AGND1 + 0.03 V to AVDD1 - 0.03 V (Typ.). In this example, therefore, DAC1 is set to 0.5 V so that AMP1 OUT will be 0.5 V when the illuminance is 0 (Lx). Assuming RF = 640 k $\Omega$ , Formula 2 is expressed as follows:

$$AMP1_OUT = 640k \times I_{SC} + 0.5$$

... Formula 4

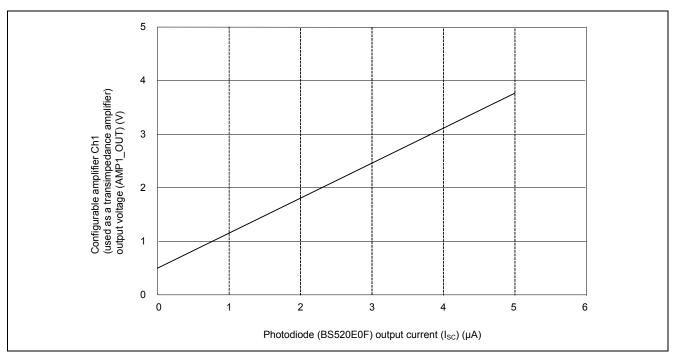

**Figure 5.4** shows the relationship between the current output from the photodiode BS520E0F and the voltage output from configurable amplifier Ch1 (used as a transimpedance amplifier) incorporated in the RL78/G1E (R5F10FMx).

Figure 5.4 Photodiode Output Current (Isc) vs. Transimpedance Amplifier (AMP1\_OUT) Output Voltage

#### 5.3 A/D Converter

This section describes the A/D converter incorporated in the RL78/G1E (R5F10FMx), which is used to convert the photodiode output current signal amplified and converted by the configurable amplifier (used as a transimpedance amplifier) to a digital value.

## 5.3.1 Overview of A/D converter incorporated in RL78/G1E (R5F10FMx)

The A/D converter incorporated in the RL78/G1E (R5F10FMx) is used to convert an analog input to a digital value. Seventeen analog input channels are available for analog input. 12-bit resolution or 8-bit resolution can be selected.

The settings specified for the A/D converter incorporated in the RL78/G1E (R5F10FMx) are shown below.

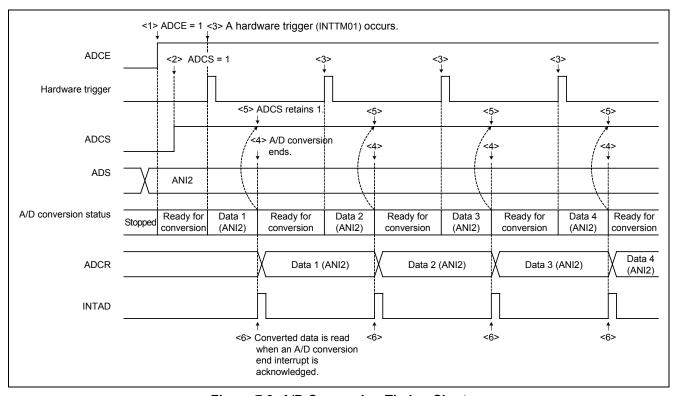

■ Trigger mode: Hardware trigger no-wait mode

■ Channel selection mode: Select mode

■ Conversion mode: One-shot conversion mode

Analog input pin: ANI2Conversion resolution: 12 bits

Reference voltage:  $AV_{DD} = 3.3 \text{ V}, AV_{SS} = 0 \text{ V}$

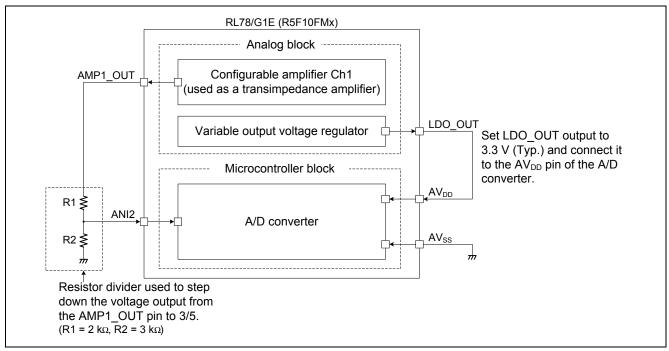

# 5.3.2 Connecting the configurable amplifier (used as a transimpedance amplifier) to the A/D converter

The maximum power supply voltage of the A/D converter incorporated in the RL78/G1E (R5F10FMx) is 3.6 V. The power supply voltage used in this application note is 5.0 V, so a stepped down voltage must be supplied to the A/D converter. To achieve this, the output voltage from the variable output voltage regulator in the analog block is set to be 3.3 V (Typ.), which is supplied to the AVDD pin.

Connect the output pin (AMP1\_OUT) of configurable amplifier Ch1 (used as a transimpedance amplifier) in the analog block to the ANI2 analog input pin of the A/D converter. Note that the analog voltage output from configurable amplifier Ch1 (used as a transimpedance amplifier) in the analog block is 0 to 5 V. To make the output voltage from AMP1\_OUT lower than AVDD, therefore, step down it to 0 to 3 V by using a resistor divider and input it to the ANI2 analog input pin of the A/D converter.

**Figure 5.5** shows the connection between configurable amplifier Ch1 (used as a transimpedance amplifier) and the A/D converter incorporated in the RL78/G1E (R5F10FMx).

Figure 5.5 Connection Between Configurable Amplifier Ch1 (Used As a Transimpedance Amplifier) and A/D Converter

# 5.4 CPU (Arithmetic Operation)

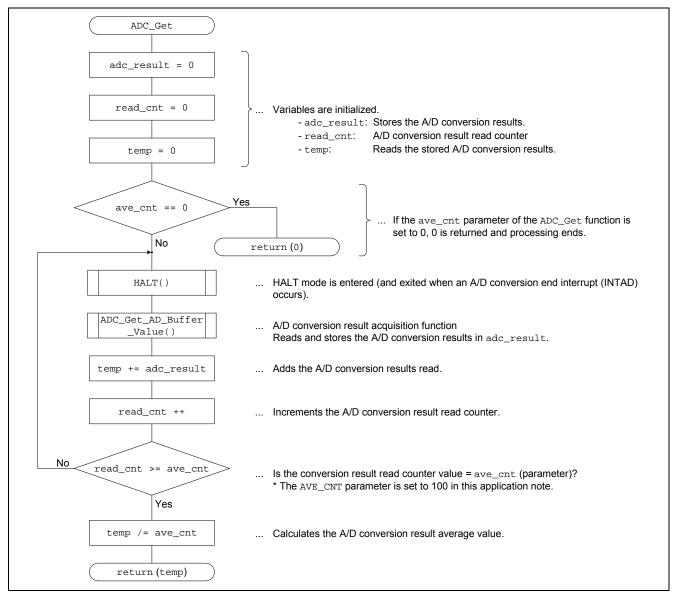

This section describes how the CPU calculates the physical quantity (illuminance) based on the A/D conversion result.

The analog voltage input to the ANI2 pin, which is calculated from the A/D conversion result (stored in the 12-bit A/D conversion result register (ADCR)) is expressed as shown in the formula below:

$$ANI2 = \frac{AD\_conversion\_value}{2^{12} - 1} \times AV_{DD} \qquad \qquad ... \quad \text{Formula 5}$$

AVDD: Power supply voltage input to the A/D converter (V)

ANI2: Voltage input to analog input pin 2 of the A/D converter (V)

Because the analog voltage output from the AMP1\_OUT pin is divided by using the resistor divider and then input to the ANI2 pin, the AMP1\_OUT pin voltage (V) is expressed as shown in the formula below (see *Figure 5.5*):

$$AMP1\_OUT = ANI2 \times \frac{R1 + R2}{R2}$$

... Formula 6

The current output from the photodiode (Isc (A)), which is calculated from the voltage output from the AMP1\_OUT pin in *Formula 2*, is expressed as shown in the formula below:

$$I_{SC} = \frac{AMP1\_OUT - DAC1}{RF}$$

... Formula 7

DAC1: D/A converter Ch1 output voltage (V)

RF: Feedback resistance of configurable amplifier Ch1 (used as a transimpedance amplifier)  $(\Omega)$

The photodiode output current and the illuminance are proportional. Based on the typical value prescribed in the datasheet, therefore, the physical quantity (illuminance (Lx)), which is calculated from the photodiode output current, is expressed as shown in the formula below:

$$Lx = \frac{I_{SC}}{5.5 \times 10^{-9}}$$

... Formula 8

If, from Formula 5, Formula 6, Formula 7, and Formula 8 above, AVDD = 3.3 V, RF = 640 k $\Omega$ , R1 = 2 k $\Omega$ , R2 = 3 k $\Omega$ , and DAC1 = 0.4902 V<sup>Note 1</sup>, the relationship between the illuminance and the A/D conversion value is expressed as shown in the formula Note 2 below:

$$Lx = \left(\frac{\frac{AD\_conversion\_value}{2^{12} - 1} \times 3.3 \times \frac{2k + 3k}{3k} - 0.4902}{5.5 \times 10^{-9} \times 640k}\right) \qquad ... \quad \text{Formula 9}$$

**Note 1** This is the voltage output from D/A converter Ch1 when DAC control register 1 (DAC1C) for D/A converter Ch1 is set to 19H (DAC1 =  $2.5 \times 2 \times 25/255 = 0.4902$  V). For how to calculate the value, see the *RL78/G1E Hardware User's Manual*.

**Note 2** The set values used in *Formula 9* are reference values. The user needs to evaluate the system to determine the actual values.

#### 5.5 LCD Module

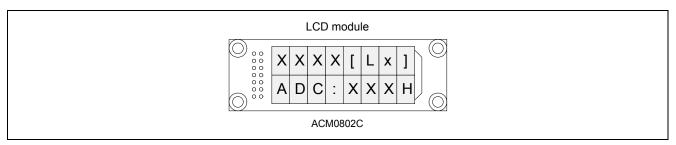

This section describes the contents displayed in the LCD module (ACM0802C).

(1) Specifications of the LCD module

Model name: ACM0802C-NLW-BBH

Manufacturer: AZ Displays, Inc.

Number of displayed characters: 8 characters × 2 lines

■ Power supply voltage: 5 V

(2) Displaying the calculation result (physical quantity)

**Figure 5.6** shows how the calculation result is displayed on the LCD module. The calculation result is displayed as a left-justified four-digit integer on the upper line. The unit is displayed as Lx. The averaged A/D conversion value is displayed in three-digit hexadecimal on the bottom line.

Figure 5.6 LCD Module Display Format

# 6. Analog Block of RL78/G1E (R5F10FMx)

This section describes the functions used in the analog block of the RL78/G1E (R5F10FMx).

# 6.1 Overview of Analog Block of RL78/G1E (R5F10FMx)

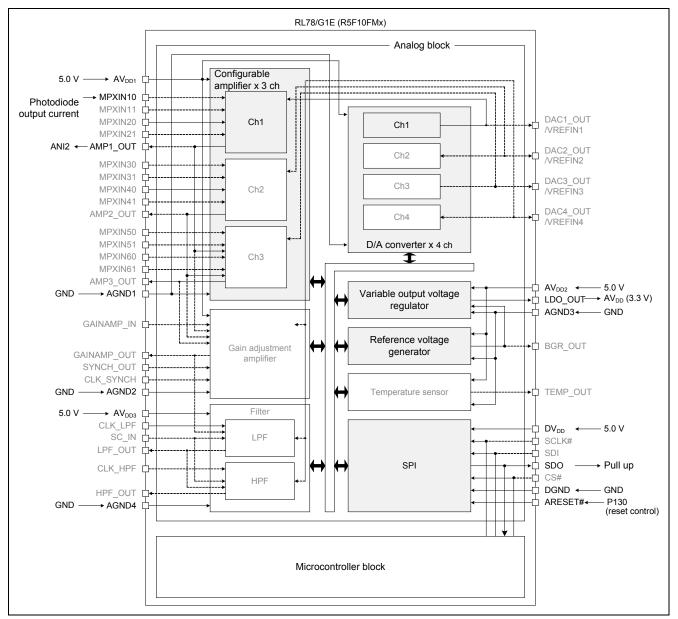

The analog block of the RL78/G1E (R5F10FMx) has on-chip circuits such as configurable amplifiers, a gain adjustment amplifier, a filter circuit, D/A converters, and a temperature sensor, allowing the R5F10FMx to be used as an analog front-end circuit for processing very small sensor signals.

The block diagram of the analog block of the RL78/G1E (R5F10FMx) is shown below. The blocks described in the following sections are shaded.

Figure 6.1 Block Diagram of Analog Block of RL78/G1E (R5F10FMx)

# 6.2 Functions of Analog Block of RL78/G1E (R5F10FMx)

This section describes the analog block of the RL78/G1E (R5F10FMx) used in this application note in detail.

# 6.2.1 Configurable amplifier

In this application note, configurable amplifier Ch1 is used as a transimpedance amplifier.

#### (1) Overview of configurable amplifier features

The RL78/G1E (R5F10FMx) has three on-chip configurable amplifier channels.

By specifying settings in the SPI control registers, the configurable amplifiers can be used to realize the following features:

**Table 6.1 Overview of Configurable Amplifier**

| Description         | Overview                                                                                        |

|---------------------|-------------------------------------------------------------------------------------------------|

| Non-inverting       | The gain can be specified between 10 dB and 40 dB in 18 steps.                                  |

| amplifier           | Four operating modes are available.                                                             |

|                     | Includes a power-off feature.                                                                   |

|                     | * Single-channel operation                                                                      |

| Inverting amplifier | • The gain can be specified between 6 dB and 40 dB in 18 steps of 2 dB each.                    |

|                     | Four operating modes are available.                                                             |

|                     | Includes a power-off feature.                                                                   |

|                     | * Single-channel operation                                                                      |

| Differential        | • The gain can be specified between 6 dB and 40 dB in 18 steps of 2 dB each.                    |

| amplifier           | Four operating modes are available.                                                             |

|                     | Includes a power-off feature.                                                                   |

|                     | * Single-channel operation                                                                      |

| Transimpedance      | • The feedback resistance can be specified between 20 k $\Omega$ and 640 k $\Omega$ in 6 steps. |

| amplifier           | Four operating modes are available.                                                             |

|                     | Includes a low-current mode.                                                                    |

|                     | * Single-channel operation                                                                      |

| Instrumentation     | • The gain can be specified between 20 dB and 54 dB in 18 steps of 2 dB each.                   |

| amplifier           | Four operating modes are available.                                                             |

|                     | Includes a power-off feature.                                                                   |

|                     | * On-chip configurable amplifier × 3 ch                                                         |

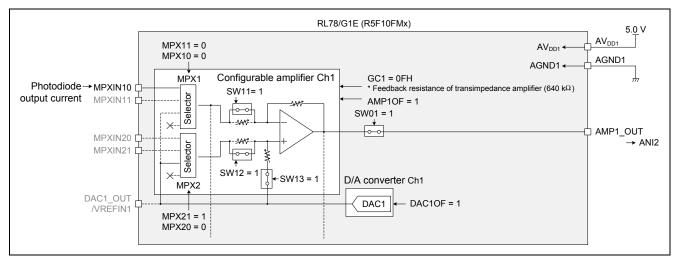

(2) Settings specified when using a configurable amplifier channel as a transimpedance amplifier

The settings specified when using a configurable amplifier channel as a transimpedance amplifier are as follows.

- Connect the current output from the photodiode (BS520E0F) to the inverted input source (MPXIN10) of configurable amplifier Ch1.

- Specify the settings as shown below when using configurable amplifier Ch1 as a transimpedance amplifier (feedback resistance:  $640 \text{ k}\Omega$ ).

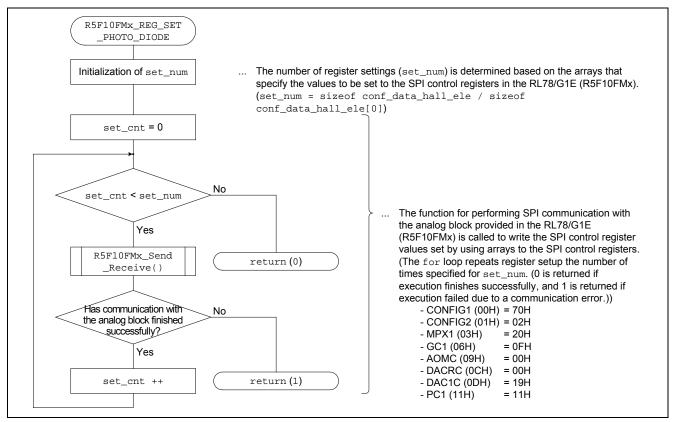

- <1> Set SW11 to 1, SW12 to 1, and SW13 to 1 in configuration register 1 (CONFIG1).

- <2> Set MPX11 to 0 and MPX10 to 0 in MPX setting register 1 (MPX1) to specify the MPXIN10 pin as the source of inverted input to configurable amplifier Ch1.

- <3> Set MPX21 to 1 and MPX20 to 0 in MPX setting register 1 (MPX1) to specify the D/A converter Ch1 output signal or the VREFIN1 pin as the source of non-inverted input to configurable amplifier Ch1.

- <4> Set CC1 to 0 and CC0 to 0 in the AMP operation mode control register (AOMC) to specify high-speed mode as the operating mode of configurable amplifier channels Ch1 to Ch3.

- <5> Set gain control register 1 (GC1) to 0FH to specify 640 k $\Omega$  as the feedback resistance (Typ.) of configurable amplifier Ch1 (used as a transimpedance amplifier).

- <6> Set SW01 to 1 in configuration register 2 (CONFIG2).

- <7> Set AMP1OF to 1 in power control register 1 (PC1) to start operation of configurable amplifier Ch1 (used as a transimpedance amplifier).

Figure 6.2 shows a block diagram of configurable amplifier Ch1 when used as a transimpedance amplifier.

Figure 6.2 Block Diagram of Configurable Amplifier Ch1 (Used As a Transimpedance Amplifier)

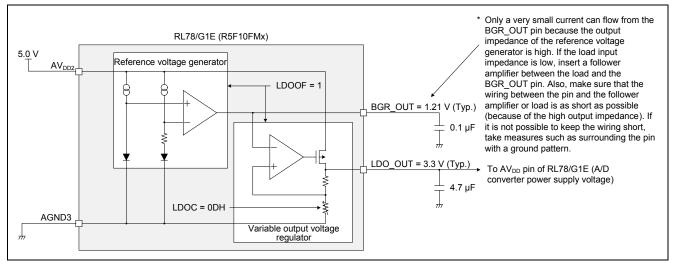

#### 6.2.2 Reference voltage generator and variable output voltage regulator

The RL78/G1E (R5F10FMx) has an on-chip reference voltage generator channel and variable output voltage regulator channel. The variable output voltage regulator is a series regulator that generates 3.3 V (default) from a supplied voltage of 5 V. In this application note, the voltage output from the variable output voltage regulator (LDO\_OUT) is connected to the AV<sub>DD</sub> pin in the RL78/G1E (R5F10FMx) and used as a voltage of 3.3 V supplied to the A/D converter.

- (1) Overview of variable output voltage regulator features

- Output voltage range: 2.0 to 3.3 V (Typ.)

- Output current: 15 mA (Max.)

- Includes a power-off feature.

- (2) Overview of reference voltage generator features

- Output reference voltage: 1.21 V (Typ.)

- Includes a power-off feature.

- (3) Settings specified for reference voltage generator and variable output voltage regulator

Specify the settings for the reference voltage generator and variable output voltage regulator as shown below.

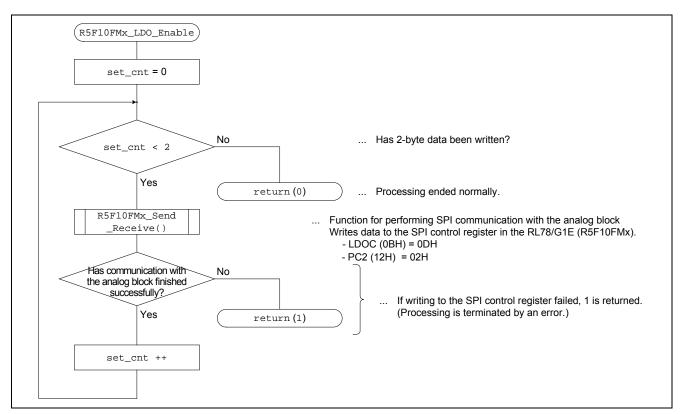

- <1> Set the LDO control register (LDOC) to 0DH to specify 3.3 V as the voltage output from the variable output voltage regulator.

- <2> Set LDOOF to 1 in power control register 2 (PC2) to start operation of the reference voltage generator and variable output voltage regulator.

Figure 6.3 shows a block diagram of the reference voltage generator and variable output voltage regulator.

Figure 6.3 Block Diagram of Reference Voltage Generator and Variable Output Voltage Regulator

(4) Notes on using reference voltage generator

Observe the following points when using the reference voltage generator:

Only a very small current can flow from the BGR\_OUT pin because the output impedance of the reference voltage generator is high. If the load input impedance is low, insert a follower amplifier between the load and the BGR\_OUT pin. Also, make sure that the wiring between the pin and the follower amplifier or load is as short as possible. If it is not possible to keep the wiring short, take measures such as surrounding the pin with a ground pattern.

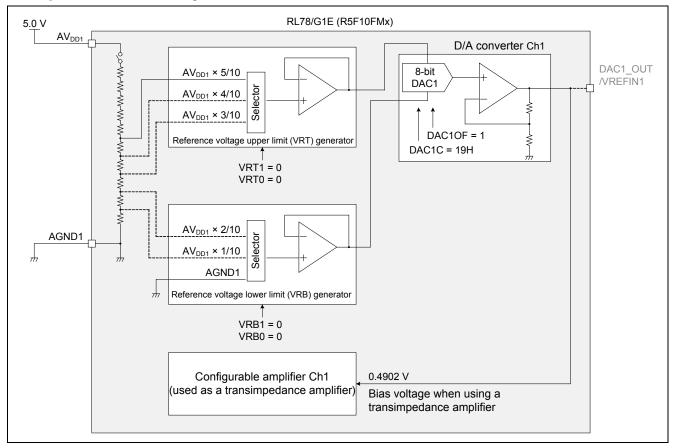

#### 6.2.3 D/A converter

The RL78/G1E (R5F10FMx) has four on-chip 8-bit D/A converter channels. In this application note, D/A converter Ch1 is used to generate a bias voltage for configurable amplifier Ch1 (used as a transimpedance amplifier).

#### (1) Overview of D/A converter features

- 8-bit resolution × 4 ch

- R-2R ladder method

- Analog output voltage: (reference voltage upper limit reference voltage lower limit)  $\times$  2  $\times$  m/255 + 2  $\times$  reference voltage lower limit

- (m: Value set to DACnC register)

- Controls the reference voltage for the configurable amplifiers, gain adjustment amplifier, high-pass filter, and low-pass filter

- Includes a power-off feature.

- Conversion speed (settling time): 100 μs (Max.)

- Voltage resolution: 19.608 mV

- \* Reference voltage upper limit =  $AV_{DD1} \times 5/10$

- \* Reference voltage lower limit = AGND1

- \*  $AV_{DD1} = 5.0 \text{ V}$

#### (2) Settings specified for D/A converter

- In this application note, the reference voltage upper limit for the D/A converter (VRT) is set to AVDD1 × 5/10, and the reference voltage lower limit for the D/A converter (VRB) is set to AGND1. The voltage output from D/A converter channels Ch1 to Ch4 therefore ranges from AGND1 to AVDD1 (0 to 5 V).

- Specify the settings for the D/A converter as shown below.

- <1> Set VRT1 to 0 and VRT0 to 0 in the DAC reference voltage control register (DACRC) to specify "AVDD1 × 5/10" as the reference voltage upper limit (VRT) for D/A converter channels Ch1 to Ch4.

- <2> Set VRB1 to 0 and VRB0 to 0 in the DAC reference voltage control register (DACRC) to specify AGND1 as the reference voltage lower limit (VRB) for D/A converter channels Ch1 to Ch4.

- <3> Specify the output analog voltage value by using DAC control registers 1 to 4 (DAC1C to DAC4C) corresponding to the D/A converter used.

- \* In this application note, D/A converter Ch1 is used to generate a bias voltage for configurable amplifier Ch1 (used as a transimpedance amplifier). For the bias voltage, set the DAC1C register to 19H to specify 0.4902 V as the voltage output from the DAC1\_OUT pin so that the voltage output from the AMP1\_OUT pin of configurable amplifier Ch1 (used as a transimpedance amplifier) is set to 0.5 V when the illuminance detected by the photodiode is 0 Lx. (Note that the value set to the DAC1C register is a reference value. The user needs to evaluate the system to determine the actual values.)

- <4> Set DAC1OF to 1 in power control register 1 (PC1) to start operation of this channel. Set all the other bits to 0. (DAC4OF = 0, DAC3OF = 0, DAC2OF = 0, and DAC1OF = 1.)

Figure 6.4 shows a block diagram of D/A converter Ch1.

Figure 6.4 Block Diagram of D/A Converter Ch1

#### (3) Notes on using the D/A converter

Observe the following points when using the D/A converter:

- Only a very small current can flow from the DACn\_OUT pin because the output impedance of the D/A converter is high. If the load input impedance is low, insert a follower amplifier between the load and the DACn\_OUT pin. Also, make sure that the wiring between the pin and the follower amplifier or load is as short as possible. If it is not possible to keep the wiring short, take measures such as surrounding the pin with a ground pattern.

- If inputting an external reference power supply to the VREFINn pin, be sure to set the DACnOF bit to 0.

**Remark**: n = 1 to 4

#### 6.2.4 SPI

The SPI is used to allow control from external devices by using clocked communication via four lines: a serial clock line (SCLK#), two serial data lines (SDI and SDO), and a slave selection input line (CS#).

#### (1) Overview of SPI features

- Data transmission/reception:

- 16-bit data unit

- MSB first

- The SPI pins SCLK#, SDI, and SDO, which are located in the analog block of the RL78/G1E (R5F10FMx), are connected to the corresponding pins in the 3-wire serial I/O function block (CSI21) of channel 1 of serial array unit 1 in the microcontroller block inside the package. The CS# pin is connected to the P73 pin in the microcontroller block inside the package.

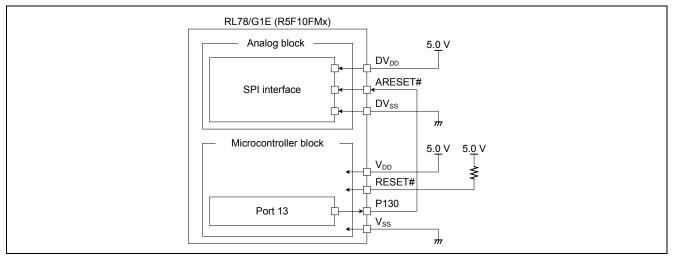

- The RL78/G1E (R5F10FMx) has an on-chip analog reset feature. A reset can be generated in the following two ways:

- By inputting an external reset signal to the ARESET# pin

- By generating an internal reset by writing 1 to the RESET bit of the reset control register (RC)

- In this application note, the ARESET# pin in the RL78/G1E (R5F10FMx) is connected to the P130 pin in the microcontroller block to control the analog reset feature.

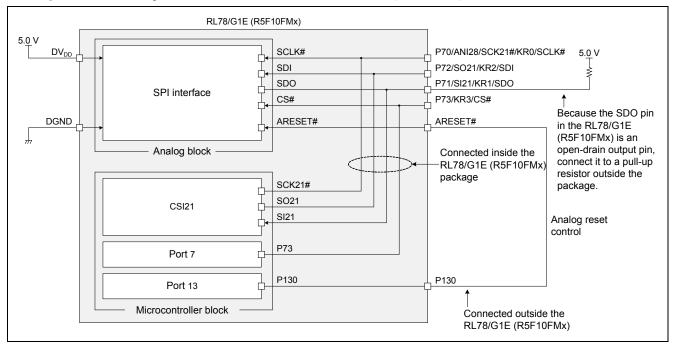

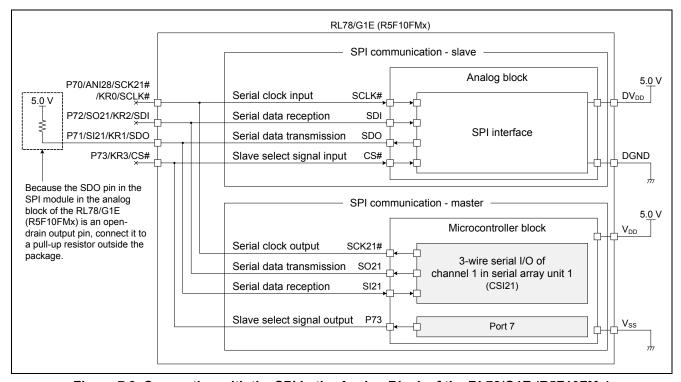

**Figure 6.5** shows the pin connections of the SPI in the RL78/G1E (R5F10FMx).

Figure 6.5 SPI Configuration Example

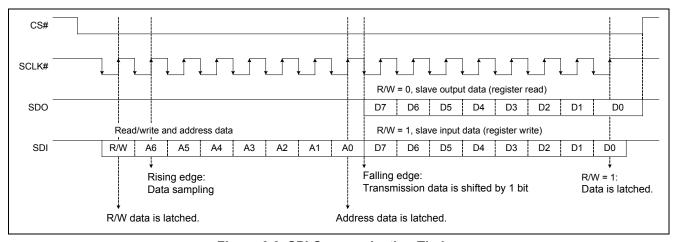

#### (2) SPI communication

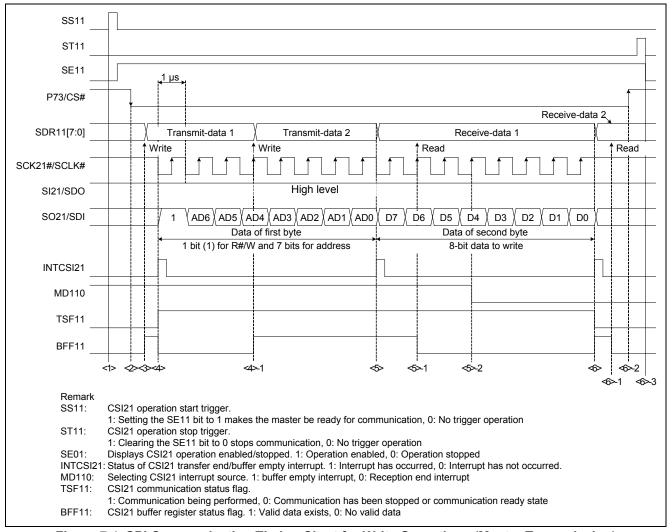

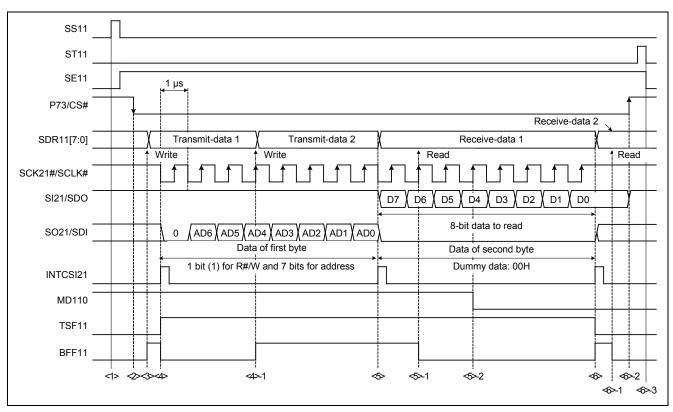

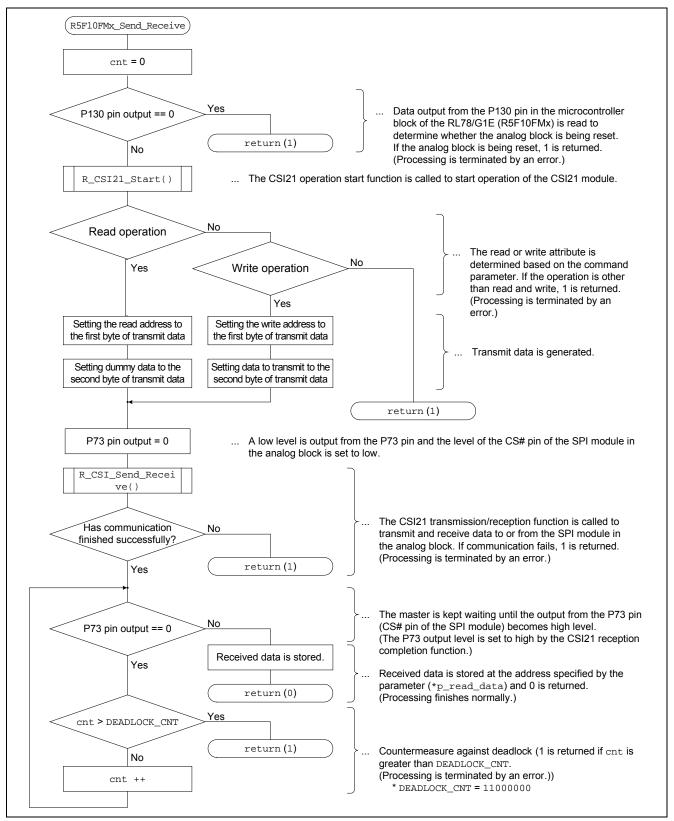

The SPI transmits and receives data in 16-bit units. Data can be transmitted and received when CS# is low. Data is transmitted one bit at a time in synchronization with the falling edge of the serial clock, and is received one bit at a time in synchronization with the rising edge of the serial clock. When the R/W bit is 1, data is written to the SPI control register in accordance with the address/data setting when the rising edge of the 16th SCLK# signal is detected after the fall of CS#. When the R/W bit is 0, the data is output from the register in accordance with the address/data setting, in synchronization with the 9th and later falling edges of SCLK# following the fall of CS#.

In this application note, the SPI in the analog block of the RL78/G1E (R5F10FMx) and CSI21 in the microcontroller block, to which the SPI is connected inside the RL78/G1E (R5F10FMx) chip, are used to perform SPI communication. A 32 MHz clock generated by the high-speed on-chip oscillator is used as the main system clock for the RL78/G1E (R5F10FMx), and 1 MHz is selected as the operating clock for SPI communication. The slave select input (CS#) pin for the SPI is controlled by using the P73 pin in the RL78/G1E (R5F10FMx).

Figure 6.6 shows the SPI communication timing.

Figure 6.6 SPI Communication Timing

(3) SPI control registers

**Table 6.2** shows the SPI control registers.

**Table 6.2 SPI Control Registers**

| Address | SPI Contro                       | R/W                                       | After Reset |                     |

|---------|----------------------------------|-------------------------------------------|-------------|---------------------|

| 00H     | CONFIG1                          | Configuration register 1                  | R/W         | 00H                 |

| 01H     | CONFIG2                          | Configuration register 2                  | R/W         | 00H                 |

| 03H     | MPX1                             | MPX setting register 1                    | R/W         | 00H                 |

| 04H     | MPX2                             | MPX setting register 2                    | R/W         | 00H                 |

| 05H     | MPX3                             | MPX setting register 3                    | R/W         | 00H                 |

| 06H     | GC1                              | Gain control register 1                   | R/W         | 00H                 |

| 07H     | GC2                              | Gain control register 2                   | R/W         | 00H                 |

| 08H     | GC3                              | Gain control register 3                   | R/W         | 00H                 |

| 09H     | AOMC                             | AMP operation mode control register       | R/W         | 00H                 |

| 0AH     | GC4                              | Gain control register 4                   | R/W         | 00H                 |

| 0BH     | LDOC                             | LDO control register                      | R/W         | 0DH                 |

| 0CH     | DACRC                            | RC DAC reference voltage control register |             | 00H                 |

| 0DH     | DAC1C                            | 1C DAC control register 1                 |             | 80H                 |

| 0EH     | DAC2C                            | DAC control register 2                    | R/W         | 80H                 |

| 0FH     | DAC3C                            | C3C DAC control register 3                |             | 80H                 |

| 10H     | DAC4C DAC control register 4     |                                           | R/W         | 80H                 |

| 11H     | 11H PC1 Power control register 1 |                                           | R/W         | 00H                 |

| 12H     | 12H PC2 Power control register 2 |                                           | R/W         | 00H                 |

| 13H     | RC                               | Reset control register                    | R/W         | 00H <sup>Note</sup> |

**Note** When generating an internal reset by writing 1 to the RESET bit of the reset control register, the reset control register is not initialized.

#### (4) Analog reset feature

The RL78/G1E (R5F10FMx) has an on-chip analog reset feature. A reset can be generated in the following two ways:

- By inputting an external reset signal to the ARESET# pin

- By generating an internal reset by writing 1 to the RESET bit of the reset control register (RC)

There are no functional differences between an external and an internal reset: both types serve to initialize Note the SPI control registers.

If a low-level signal is input to the ARESET# pin or if 1 is written to the RESET bit of the reset control register (RC), the analog circuits enter the statuses shown in **Table 6.3**. The statuses of the SPI control registers after a reset has been acknowledged are shown in **Table 6.4**.

A reset is generated by inputting a low-level signal to the ARESET# pin. The reset is subsequently canceled by inputting a high-level signal to this pin.

When generating an internal reset by writing 1 to the RESET bit of the reset control register, the reset occurs <sup>Note</sup> after 1 is written to the RESET bit, and is subsequently canceled by writing 0 to the same bit.

In this application note, the ARESET# pin in the RL78/G1E (R5F10FMx) is connected to the P130 pin in the microcontroller block to control the analog reset feature.

**Note** When generating an internal reset by writing 1 to the RESET bit of the reset control register, the reset control register is not initialized.

Caution When generating an external reset, input a low-level signal to the ARESET# pin for at least 10 µs.

Table 6.3 Statuses During an Analog Reset Period

| Function Block                    | By Inputting an External Reset Signal to the ARESET# Pin | By Generating an Internal<br>Reset by Writing 1 to the<br>RESET Bit of the Reset Control<br>Register (RC) |  |  |

|-----------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Configurable amplifier            | Operation                                                | on stops.                                                                                                 |  |  |

| Gain adjustment amplifier         | Operation stops.                                         |                                                                                                           |  |  |

| D/A converter                     | Operation stops.                                         |                                                                                                           |  |  |

| Low-pass filter                   | Operation stops.                                         |                                                                                                           |  |  |

| High-pass filter                  | Operation stops.                                         |                                                                                                           |  |  |

| Temperature sensor                | Operation stops.                                         |                                                                                                           |  |  |

| Variable output voltage regulator | Operation stops.                                         |                                                                                                           |  |  |

| Reference voltage generator       | Operation stops.                                         |                                                                                                           |  |  |

| SPI                               | Operation stops.                                         | Operation enabled                                                                                         |  |  |

Table 6.4 Statuses of SPI Control Registers After an Analog Reset Is Acknowledged

| Address SPI Control R            |                                  | l Register                             | Status After an Analog Reset Is Acknowledged |

|----------------------------------|----------------------------------|----------------------------------------|----------------------------------------------|

| 00H                              | CONFIG1                          | Configuration register 1               | 00H                                          |

| 01H                              | CONFIG2                          | Configuration register 2               | 00H                                          |

| 03H                              | MPX1                             | MPX setting register 1                 | 00H                                          |

| 04H                              | MPX2                             | MPX setting register 2                 | 00H                                          |

| 05H                              | MPX3                             | MPX setting register 3                 | 00H                                          |

| 06H                              | GC1                              | Gain control register 1                | 00H                                          |

| 07H                              | GC2                              | Gain control register 2                | 00H                                          |

| 08H                              | 08H GC3 Gain control register 3  |                                        | 00H                                          |

| 09H                              | AOMC                             | AMP operation mode control register    | 00H                                          |

| 0AH                              | GC4                              | Gain control register 4                | 00H                                          |

| 0BH                              | BH LDOC LDO control register     |                                        | 0DH                                          |

| 0CH                              | DACRC                            | DAC reference voltage control register | 00H                                          |

| 0DH                              | DAC1C                            | DAC control register 1                 | 80H                                          |

| 0EH                              | DAC2C                            | DAC control register 2                 | 80H                                          |

| 0FH DAC3C DAC control register 3 |                                  | DAC control register 3                 | 80H                                          |

| 10H                              | 10H DAC4C DAC control register 4 |                                        | 80H                                          |

| 11H                              | 11H PC1 Power control register 1 |                                        | 00H                                          |

| 12H                              | PC2                              | Power control register 2               | 00H                                          |

| 13H                              | 13H RC Reset control register    |                                        | 00H <sup>Note</sup>                          |

**Note** When generating an internal reset by writing 1 to the RESET bit of the reset control register, the reset control register is not initialized.

# 6.3 Settings of SPI Control Registers of RL78/G1E (R5F10FMx)

This section describes the settings of the SPI control registers used in this application note. This section omits descriptions of the SPI control registers not used in this application note. (They are used with their default values.) For details, see the *RL78/G1E Hardware User's Manual*.

Caution For how to specify the register settings, see the RL78/G1E Hardware User's Manual.

# (1) Configuration register 1 (CONFIG1)

This register is used to turn on or off the SW11, SW12, and SW13 switches of configurable amplifier Ch1.

| Address: 00H | After res | set: OUH R | d/vv Set va | alue: /UH |   |      |      |      |

|--------------|-----------|------------|-------------|-----------|---|------|------|------|

| Symbol       | 7         | 6          | 5           | 4         | 3 | 2    | 1    | 0    |

| CONFIG1      | 0         | SW11       | SW12        | SW13      | 0 | SW21 | SW22 | SW23 |

| Set value    | 0         | 1          | 1           | 1         | 0 | 0    | 0    | 0    |

|   | SW11 | Control of SW11 |

|---|------|-----------------|

| Γ | 0    | Turn off SW11.  |

| I | 1    | Turn on SW11.   |

| SW12 | Control of SW12 |

|------|-----------------|

| 0    | Turn off SW12.  |

| 1    | Turn on SW12.   |

| SW13 | Control of SW13 |

|------|-----------------|

| 0    | Turn off SW13.  |

| 1    | Turn on SW13.   |

#### (2) Configuration register 2 (CONFIG2)

This register is used to turn on or off the SW01 switch of configurable amplifier Ch1.

| Address: 01H | After res | set: 00H | R/W Se | t value: 02H |   |      |      |      |

|--------------|-----------|----------|--------|--------------|---|------|------|------|

| Symbol       | 7         | 6        | 5      | 4            | 3 | 2    | 1    | 0    |

| CONFIG2      | 0         | SW31     | SW32   | SW33         | 0 | SW02 | SW01 | SW00 |

| Set value    | 0         | 0        | 0      | 0            | 0 | 0    | 1    | 0    |

| SW01 | Control of SW01 |

|------|-----------------|

| 0    | Turn off SW01.  |

| 1    | Turn on SW01.   |

# (3) MPX setting register 1 (MPX1)

This register is used to control MPX1 and MPX2.

This register is used to select the signal input to configurable amplifier Ch1.

Address: 03H After reset: 00H R/W Set value: 20H Symbol 5 3 2 7 6 4 1 0 MPX1 MPX11 MPX10 MPX21 MPX20 MPX31 MPX30 MPX41 MPX40 Set value 0 0

| MPX11 | MPX10 | Source of configurable amplifier Ch1 inverted input |

|-------|-------|-----------------------------------------------------|

| 0     | 0     | MPXIN10 pin                                         |

| 0     | 1     | MPXIN11 pin                                         |

| 1     | 0     | D/A converter Ch1 output signal or VREFIN1 pin      |

| 1     | 1     | Leave open                                          |

| MPX21 | MPX20 | Source of configurable amplifier Ch1 non-inverted input |

|-------|-------|---------------------------------------------------------|

| 0     | 0     | MPXIN20 pin                                             |

| 0     | 1     | MPXIN21 pin                                             |

| 1     | 0     | D/A converter Ch1 output signal or VREFIN1 pin          |

| 1     | 1     | Leave open                                              |

#### (4) Gain control register 1 (GC1)

This register is used to specify the gain and feedback resistance of configurable amplifier Ch1.

The value to specify depends on the configuration of configurable amplifier Ch1. In this application note, the configurable amplifier is used as a transimpedance amplifier.

| Address: 06H | After res | set: 00H | R/W S | Set value: 0FH |        |        |        |        |

|--------------|-----------|----------|-------|----------------|--------|--------|--------|--------|

| Symbol       | 7         | 6        | 5     | 4              | 3      | 2      | 1      | 0      |

| GC1          | 0         | 0        | 0     | AMPG14         | AMPG13 | AMPG12 | AMPG11 | AMPG10 |

| Set value    | 0         | 0        | 0     | 0              | 1      | 1      | 1      | 1      |

| AMPG14 | AMPG13 | AMPG12       | AMPG11             | AMPG10 | Feedback resistance of transimpedance amplifier (Typ.) |  |  |

|--------|--------|--------------|--------------------|--------|--------------------------------------------------------|--|--|

| 0      | 0      | 0            | 0                  | 0      | 20 kΩ                                                  |  |  |

| 0      | 0      | 0            | 0                  | 1      |                                                        |  |  |

| 0      | 0      | 0            | 1                  | 0      |                                                        |  |  |

| 0      | 0      | 0            | 1                  | 1      | 40 kΩ                                                  |  |  |

| 0      | 0      | 1            | 0                  | 0      |                                                        |  |  |

| 0      | 0      | 1            | 0                  | 1      |                                                        |  |  |

| 0      | 0      | 1            | 1                  | 0      | 80 kΩ                                                  |  |  |

| 0      | 0      | 1            | 1                  | 1      |                                                        |  |  |

| 0      | 1      | 0            | 0                  | 0      |                                                        |  |  |

| 0      | 1      | 0            | 0                  | 1      | 160 kΩ                                                 |  |  |

| 0      | 1      | 0            | 1                  | 0      |                                                        |  |  |

| 0      | 1      | 0            | 1                  | 1      |                                                        |  |  |

| 0      | 1      | 1            | 0                  | 0      | 320 kΩ                                                 |  |  |

| 0      | 1      | 1            | 0                  | 1      |                                                        |  |  |

| 0      | 1      | 1            | 1                  | 0      |                                                        |  |  |

| 0      | 1      | 1            | 1                  | 1      | 640 kΩ                                                 |  |  |

| 1      | 0      | 0            | 0                  | 0      |                                                        |  |  |

| 1      | 0      | 0            | 0                  | 1      |                                                        |  |  |

|        | Ot     | her than abo | Setting prohibited |        |                                                        |  |  |

## (5) AMP operation mode control register (AOMC)

This register is used to specify the operating mode of configurable amplifier channels Ch1 to Ch3.

| Address: 09H | After res | set: 00H | R/W Set | value: 00H |   |   |     |     |

|--------------|-----------|----------|---------|------------|---|---|-----|-----|

| Symbol       | 7         | 6        | 5       | 4          | 3 | 2 | 1   | 0   |

| AOMC         | 0         | 0        | 0       | 0          | 0 | 0 | CC1 | CC0 |

| Set value    | 0         | 0        | 0       | 0          | 0 | 0 | 0   | 0   |

| CC1 | CC0 | Operating mode of configurable amplifier channels Ch1 to Ch3 |

|-----|-----|--------------------------------------------------------------|

| 0   | 0   | High-speed mode                                              |

| 0   | 1   | Mid-speed mode 2                                             |

| 1   | 0   | Mid-speed mode 1                                             |

| 1   | 1   | Low-speed mode                                               |

# (6) LDO control register (LDOC)

This register is used to specify the output voltage of the variable output voltage regulator.

| Address: 0BH | After res | set: 0DH | R/W Set v | alue: 0DH |      |      |      |      |

|--------------|-----------|----------|-----------|-----------|------|------|------|------|

| Symbol       | 7         | 6        | 5         | 4         | 3    | 2    | 1    | 0    |

| LDOC         | 0         | 0        | 0         | 0         | LDO3 | LDO2 | LDO1 | LDO0 |

| Set value    | 0         | 0        | 0         | 0         | 1    | 1    | 0    | 1    |

| LDO3 | LDO2       | LDO1     | LDO0 | Output voltage of variable output voltage regulator (Typ.) |

|------|------------|----------|------|------------------------------------------------------------|

| 0    | 0          | 0        | 0    | 2.0 V                                                      |

| 0    | 0          | 0        | 1    | 2.1 V                                                      |

| 0    | 0          | 1        | 0    | 2.2 V                                                      |

| 0    | 0          | 1        | 1    | 2.3 V                                                      |

| 0    | 1          | 0        | 0    | 2.4 V                                                      |

| 0    | 1          | 0        | 1    | 2.5 V                                                      |

| 0    | 1          | 1        | 0    | 2.6 V                                                      |

| 0    | 1          | 1        | 1    | 2.7 V                                                      |

| 1    | 0          | 0        | 0    | 2.8 V                                                      |

| 1    | 0          | 0        | 1    | 2.9 V                                                      |

| 1    | 0          | 1        | 0    | 3.0 V                                                      |

| 1    | 0          | 1        | 1    | 3.1 V                                                      |

| 1    | 1          | 0        | 0    | 3.2 V                                                      |

| 1    | 1          | 0        | 1    | 3.3 V                                                      |

|      | Other that | an above | •    | Setting prohibited                                         |

#### (7) DAC reference voltage control register (DACRC)

This register is used to specify the upper (VRT) and lower (VRB) limits of the reference voltage for D/A converter channels Ch1 to Ch4.

When selecting the upper limit of the reference voltage, use bits 3 and 2. When selecting the lower limit of the reference voltage, use bits 1 and 0.

| Address: 0CH | After res | set: 00H | R/W Set | value: 00H |      |      |      |      |

|--------------|-----------|----------|---------|------------|------|------|------|------|

| Symbol       | 7         | 6        | 5       | 4          | 3    | 2    | 1    | 0    |

| DACRC        | 0         | 0        | 0       | 0          | VRT1 | VRT0 | VRB1 | VRB0 |

| Set value    | 0         | 0        | 0       | 0          | 0    | 0    | 0    | 0    |

| VRT1 | VRT0 | Upper limit of reference voltage (Typ.) |

|------|------|-----------------------------------------|

| 0    | 0    | AV <sub>DD1</sub> × 5/10                |

| 0    | 1    | AV <sub>DD1</sub> × 4/10                |

| 1    | 0    | AV <sub>DD1</sub> × 3/10                |

| 1    | 1    | AV <sub>DD1</sub> × 5/10                |

| VRB1 | VRB0 | Upper limit of reference voltage (Typ.) |

|------|------|-----------------------------------------|

| 0    | 0    | AGND1                                   |

| 0    | 1    | AV <sub>DD1</sub> × 1/10                |

| 1    | 0    | AV <sub>DD1</sub> × 2/10                |

| 1    | 1    | AGND1                                   |

# (8) DAC control register 1 (DAC1C)

This register is used to specify the analog voltage to be output to the DAC1\_OUT pin.

The DAC1\_OUT output signal is used to generate a bias voltage for configurable amplifier Ch1 (used as a transimpedance amplifier).

| Address: 0DI | H After res | set: 80H F | R/W Set | value: 19H |       |       |       |       |

|--------------|-------------|------------|---------|------------|-------|-------|-------|-------|

| Symbol       | 7           | 6          | 5       | 4          | 3     | 2     | 1     | 0     |

| DAC1C        | DAC17       | DAC16      | DAC15   | DAC14      | DAC13 | DAC12 | DAC11 | DAC10 |

| Set value    | 0           | 0          | 0       | 1          | 1     | 0     | 0     | 1     |

#### ■ DAC1 OUT output voltage

= ((reference voltage upper limit – reference voltage lower limit)  $\times$  2  $\times$  m/255) + 2  $\times$  reference voltage lower limit

=

$$((AV_{DD1} \times 5/10 - AGND1) \times 2 \times 25/255) + 2 \times AGND1$$

$$= ((2.5 \text{ V} - 0 \text{ V}) \times 2 \times 25/255) + 2 \times 0 \text{ V}$$

= 0.4902 V

- \*  $AV_{DD1} = 5.0 \text{ V}$

- \* AGND1 = 0 V

- \* m (DAC1C register value) = 25 (19H)

- The value set to the DAC1C register is a reference value. The user needs to evaluate the system to determine the actual values.

#### (9) Power control register 1 (PC1)

This register is used to enable or disable operation of the configurable amplifier and D/A converter. Use this register to stop unused functions to reduce power consumption and noise.

When using one of D/A converter channels Ch1 to Ch4, be sure to set the control bit that corresponds to the channel (bits 7 to 4) to 1.

When using one of configurable amplifier channels Ch1 to Ch3, be sure to set the control bit that corresponds to the channel (bits 2 to 0) to 1.

| Address: 11 | H After res | set: 00H | R/W Se | t value: 11H |   |        |        |        |

|-------------|-------------|----------|--------|--------------|---|--------|--------|--------|

| Symbol      | 7           | 6        | 5      | 4            | 3 | 2      | 1      | 0      |

| PC1         | DAC4OF      | DAC3OF   | DAC2OF | DAC10F       | 0 | AMP3OF | AMP2OF | AMP10F |

| Set value   | 0           | 0        | 0      | 1            | 0 | 0      | 0      | 1      |

| DAC40F | Operation of D/A converter Ch4         |

|--------|----------------------------------------|

| 0      | Stop operation of D/A converter Ch4.   |

| 1      | Enable operation of D/A converter Ch4. |

| DAC3OF | Operation of D/A converter Ch3         |

|--------|----------------------------------------|

| 0      | Stop operation of D/A converter Ch3.   |

| 1      | Enable operation of D/A converter Ch3. |

| DAC2OF | Operation of D/A converter Ch2         |

|--------|----------------------------------------|

| 0      | Stop operation of D/A converter Ch2.   |

| 1      | Enable operation of D/A converter Ch2. |

|   | DAC10F | Operation of D/A converter Ch1         |

|---|--------|----------------------------------------|

|   | 0      | Stop operation of D/A converter Ch1.   |

| Ī | 1      | Enable operation of D/A converter Ch1. |

| Α | MP3OF | Operation of configurable amplifier Ch3         |

|---|-------|-------------------------------------------------|

|   | 0     | Stop operation of configurable amplifier Ch3.   |

|   | 1     | Enable operation of configurable amplifier Ch3. |

| AMP2OF | Operation of configurable amplifier Ch2         |

|--------|-------------------------------------------------|

| 0      | Stop operation of configurable amplifier Ch2.   |

| 1      | Enable operation of configurable amplifier Ch2. |

| AMP10F | Operation of configurable amplifier Ch1         |

|--------|-------------------------------------------------|

| 0      | Stop operation of configurable amplifier Ch1.   |

| 1      | Enable operation of configurable amplifier Ch1. |

#### (10) Power control register 2 (PC2)

This register is used to enable or disable operation of the gain adjustment amplifier, the low-pass filter, the high-pass filter, the variable output voltage regulator, the reference voltage generator, and the temperature sensor. Use this register to stop unused functions to reduce power consumption and noise.

When using the gain adjustment amplifier, be sure to set bit 4 to 1.

When using the low-pass filter, be sure to set bit 3 to 1.

When using the high-pass filter, be sure to set bit 2 to 1.

When using the variable output voltage regulator and reference voltage generator, be sure to set bit 1 to 1.

When selecting the signal to be input to the temperature sensor, be sure to set bit 0 to 1.

| Address: 12H | After res | set: 00H | R/W Set | value: 02H |       |       |       |        |

|--------------|-----------|----------|---------|------------|-------|-------|-------|--------|

| Symbol       | 7         | 6        | 5       | 4          | 3     | 2     | 1     | 0      |

| PC2          | 0         | 0        | 0       | GAINOF     | LPFOF | HPFOF | LDOOF | TEMPOF |

| Set value    | 0         | 0        | 0       | 0          | 0     | 0     | 1     | 0      |

|   | GAINOF | Operation of gain adjustment amplifier             |

|---|--------|----------------------------------------------------|

|   | 0      | Stop operation of the gain adjustment amplifier.   |

| Ī | 1      | Enable operation of the gain adjustment amplifier. |

| LPFOF | Operation of low-pass filter             |

|-------|------------------------------------------|

| 0     | Stop operation of the low-pass filter.   |

| 1     | Enable operation of the low-pass filter. |

| HPFOF | Operation of high-pass filter             |

|-------|-------------------------------------------|

| 0     | Stop operation of the high-pass filter.   |

| 1     | Enable operation of the high-pass filter. |

| LDOOF | Operation of variable output voltage regulator and reference voltage generator             |

|-------|--------------------------------------------------------------------------------------------|

| 0     | Stop operation of the variable output voltage regulator and reference voltage generator.   |

| 1     | Enable operation of the variable output voltage regulator and reference voltage generator. |

| TEMPOF | Operation of temperature sensor             |

|--------|---------------------------------------------|

| 0      | Stop operation of the temperature sensor.   |

| 1      | Enable operation of the temperature sensor. |

# 7. Microcontroller Block of RL78/G1E (R5F10FMx)

This section describes the functions and software used by the microcontroller block of the RL78/G1E (R5F10FMx).

# 7.1 Functions Assigned to the Microcontroller Block of the RL78/G1E (R5F10FMx)

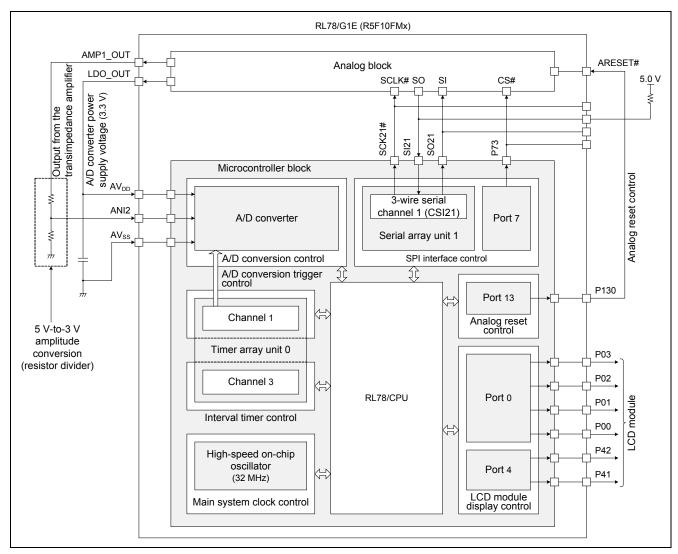

**Figure 7.1** shows the function blocks in the microcontroller block of the RL78/G1E (R5F10FMx), and **Table 7.1** shows the assigned roles.

Figure 7.1 Function Blocks in the Microcontroller Block of the RL78/G1E (R5F10FMx)

Table 7.1 Functions Assigned to the Microcontroller Block of the RL78/G1E (R5F10FMx)

| Functions Block                | Assigned Role                                                                                                                                            |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSI21                          | Control the communication with the SPI in the analog block of the RL78/G1E                                                                               |

| Port 7 (P73)                   | (R5F10FMx).                                                                                                                                              |

| A/D converter                  | Controls A/D conversion of the voltage (AMP1_OUT) output from configurable amplifier Ch1 (used as a transimpedance amplifier) and input to the ANI2 pin. |

| Port 13 (P130)                 | Controls the analog reset feature.                                                                                                                       |

| Timer array unit 0 (channel 1) | Controls the hardware trigger signal for the A/D converter.                                                                                              |

| Timer array unit 0 (channel 3) | Controls the interval timer for generating the wait time used by software.                                                                               |

| Port 0 (P00 to P03)            | Control the LCD module display.                                                                                                                          |

| Port 4 (P41, P42)              | Control the LCD module display.                                                                                                                          |

| High-speed on-chip oscillator  | Generates the 32 MHz clock selected as the main system clock.                                                                                            |

# 7.2 Functions of the Microcontroller Block of the RL78/G1E (R5F10FMx)

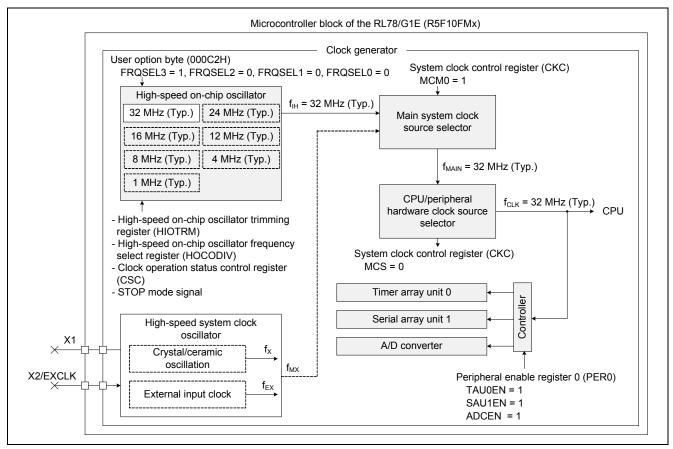

## 7.2.1 High-speed on-chip oscillator (clock generator)

In this application note, a 32 MHz clock generated by the high-speed on-chip oscillator (high-speed OCO) is used as the main system clock. The clock generator features are described below.

- Select 32 MHz as the high-speed on-chip oscillator frequency by using FRQSEL[3:0] of the user option byte (000C2H).

- By setting the user option byte (000C2H), after a reset period ends, the CPU starts operating on the high-speed on-chip oscillator clock (fiH = 32 MHz (Typ.)). Oscillation can be stopped by executing the STOP instruction or by setting the HIOSTOP bit of the clock operation status control register (CSC).

- Select the high-speed on-chip oscillator clock (fiн = 32 MHz (Typ.)) as the main system clock (fmain) by using the MCM0 bit of the system clock control register (CKC).

- Enable clock input to timer array unit 0, serial array unit 1, and the A/D converter by using peripheral enable register 0 (PER0). In this application note, clock input to unused peripheral functions is stopped to reduce power consumption and noise.

- The high-speed on-chip oscillator frequency specified by the user option byte (000C2H) can be changed by using the high-speed on-chip oscillator frequency select register (HOCODIV). In this application note, the high-speed on-chip oscillator frequency is not changed.

- The accuracy of the high-speed on-chip oscillator can be adjusted by using the high-speed on-chip oscillator trimming register (HIOTRM). In this application note, the accuracy of the high-speed on-chip oscillator is not changed.

**Figure 7.2** shows a block diagram of the clock generator incorporated in the RL78/G1E (R5F10FMx) that is used in this application note.

Figure 7.2 Block Diagram of the Clock Generator in the RL78/G1E (R5F10FMx)

#### 7.2.2 SPI control

Communication with the SPI in the analog block of the RL78/G1E (R5F10FMx) is executed by using the 3-wire serial I/O (CSI21) of channel 1 of serial array unit 1 and the P73 pin of port 7 together.

#### (1) Connection with the SPI in the analog block of the RL78/G1E (R5F10FMx)

The SPI in the analog block of the RL78/G1E (R5F10FMx), CSI21 in the microcontroller block, and the P73 pin are connected in the RL78/G1E (R5F10FMx) package. Because the serial data transmission pin (SDO) in the SPI in the analog block of the RL78/G1E (R5F10FMx) is an open-drain output pin, a pull-up resistor is externally connected to the P71/SI21/KR1/SDO pin of the RL78/G1E (R5F10FMx).

Figure 7.3 shows the pin connections of the SPI of the RL78/G1E (R5F10FMx).

Figure 7.3 Connection with the SPI in the Analog Block of the RL78/G1E (R5F10FMx)

#### (2) 3-wire serial I/O (CSI21) of channel 1 of serial array unit 1 incorporated in the RL78/G1E (R5F10FMx)

In this application note, channel 1 of serial array unit 1 incorporated in the RL78/G1E (R5F10FMx) is used for 3-wire serial I/O (CSI21).

The 3-wire serial I/O function transmits and receives data in synchronization with the serial clock (SCK#) output from the master. This is a clocked communication interface that uses three communication lines: one for the serial clock (SCK#) and two for the transmission and reception of serial data (SO and SI).