R01AN6027EJ0100

Rev.1.0

# RH850 Series CAN Configuration (CAN FD Mode)

# Summary

This document describes an example of a procedure for setting CAN Configuration using the RH850 series. Please refer to the notes in the latest user's manual hardware edition for the settings of each register.

# **Operation Confirmed Devices**

This document applies to the RH850 series.

The variables described in the text are as follows.

|                                                       | Variable | Target MCU |              |             |

|-------------------------------------------------------|----------|------------|--------------|-------------|

|                                                       | variable | RH850/E2x  | RH850/E1M-S2 | RH850/P1M-E |

| RS-CAN FD channel number                              | m        | 0~4        | 0~3          | 0~2         |

| GAFLIDj, GAFLMj, GAFLP0j,<br>GAFLP1j Register numbers | j        | 0~15       | 0~15         | 0~15        |

| Transmit/Receive FIFO buffer number                   | k        | 0~14       | 0~11         | 0~8         |

| Receive FIFO buffer number                            | х        | 0~7        | 0~7          | 0~7         |

| Receive buffer number                                 | q        | 0~79       | 0~63         | 0~47        |

| Transmit buffer number                                | р        | 0~79       | 0~63         | 0~47        |

| RAM test number                                       | r        | 0~63       | 0~63         | 0~63        |

| GAFLCFGi、GTINTSTSi<br>register number                 | i        | 0          | 0            | 0           |

| Number of each status register                        | у        | 0~2        | 0,1          | 0,1         |

#### Table 1-1 Target Devices and Variables

The functions marked with " $\star$ " in the text are applicable to cases where 2 or more channels are installed. In the text, CFD is omitted from the register names.

# Contents

| 1.  | CAN Configuration                                     | 3  |

|-----|-------------------------------------------------------|----|

| 2.  | CAN State (Mode) Transition1                          | 0  |

| 3.  | Communication Speed1                                  | 9  |

| 4.  | Global Function2                                      | 23 |

| 5.  | Receive Rule Table                                    | 30 |

| 6.  | Buffer, FIFO Buffer                                   | 39 |

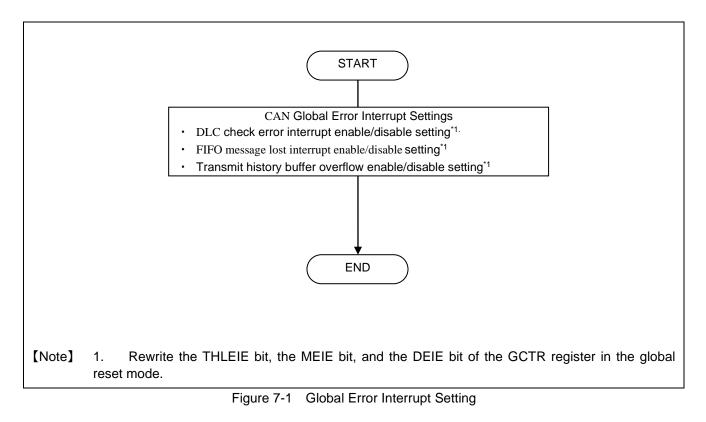

| 7.  | Global Error Interrupt5                               | 50 |

| 8.  | Channel Function5                                     | 52 |

| 9.  | CAN-related Interrupt6                                | 30 |

| 10. | Transmitter Delay Compensation (Only in CAN FD Mode)6 | 52 |

| 11. | Precautions for Processing Flow6                      | 33 |

| 12. | Appendix                                              | 35 |

# 1. CAN Configuration

In CAN configuration, set the functions required for CAN communication. Perform the configuration when resets MC, detects BUS failures, starts and restarts CAN communication after WAKEUP.

The stats available when performing CAN configuration are shown below. For CAN State (Mode), refer to "Section

- 2, CAN State (Mode) Transition".

- After CAN module enable (the CAN0EN bit in the PER2 register is "1")

- Global reset mode

- Channel reset mode

- Channel halt mode

The required functions when setting CAN configuration are shown below. For details of each process, refer to the following chapters.

- CAN state (mode) transition

- Communication speed

- Global function

- Receive rule table

- Buffer

- Global error interrupt

- Channel function

# 1.1 CAN Configuration after CAN Module Enable

# 1.1.1 CAN Configuration after CAN Module Enable

Perform the initialization of entire RS-CANFD modules after resetting MCU.

# 1.1.2 Setting Procedures of CAN Configuration after CAN Module Enable

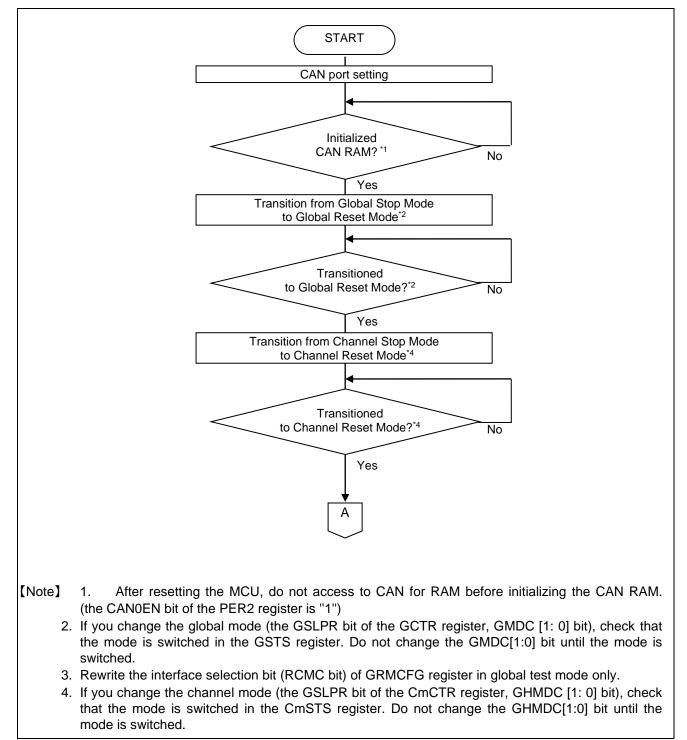

Figure 1-1 and Figure 1-2 shows the procedure of CAN Configuration after CAN Module Enable

Figure 1-1 Procedure of CAN Configuration after resetting MCU 1/2

Figure 1-2 Procedure of CAN Configuration after resetting MCU 2/2

# 1.2 CAN Configuration after Global Reset Mode

## 1.2.1 CAN Configuration after Global Reset Mode

Perform the initialization of CAN configuration after global reset mode transition.

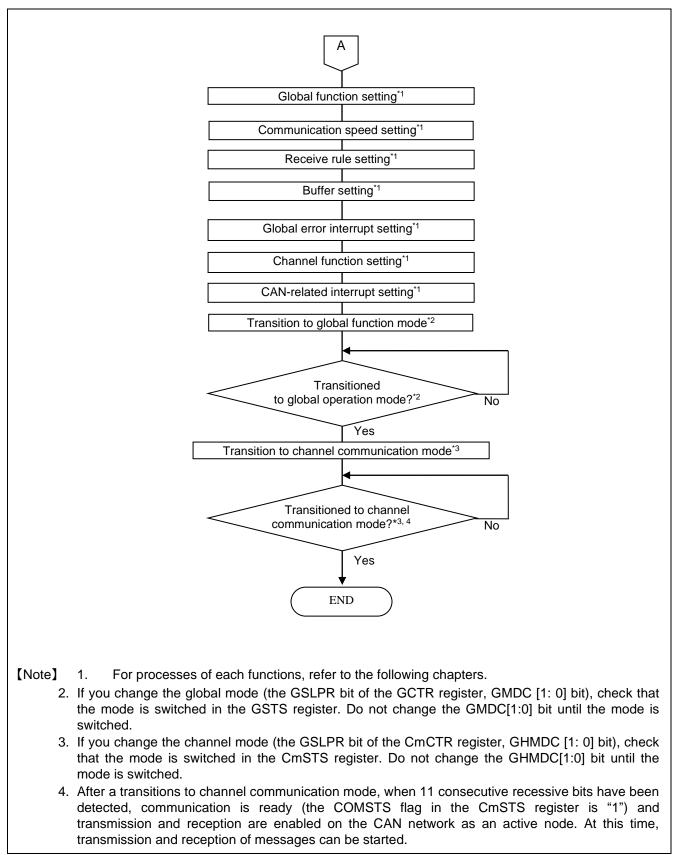

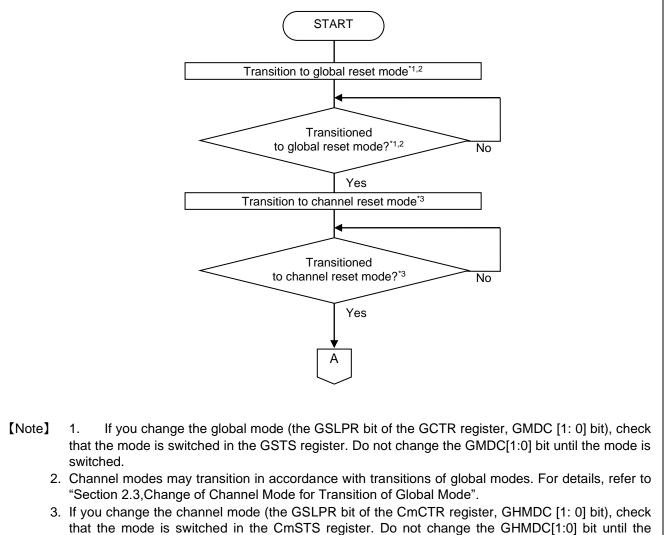

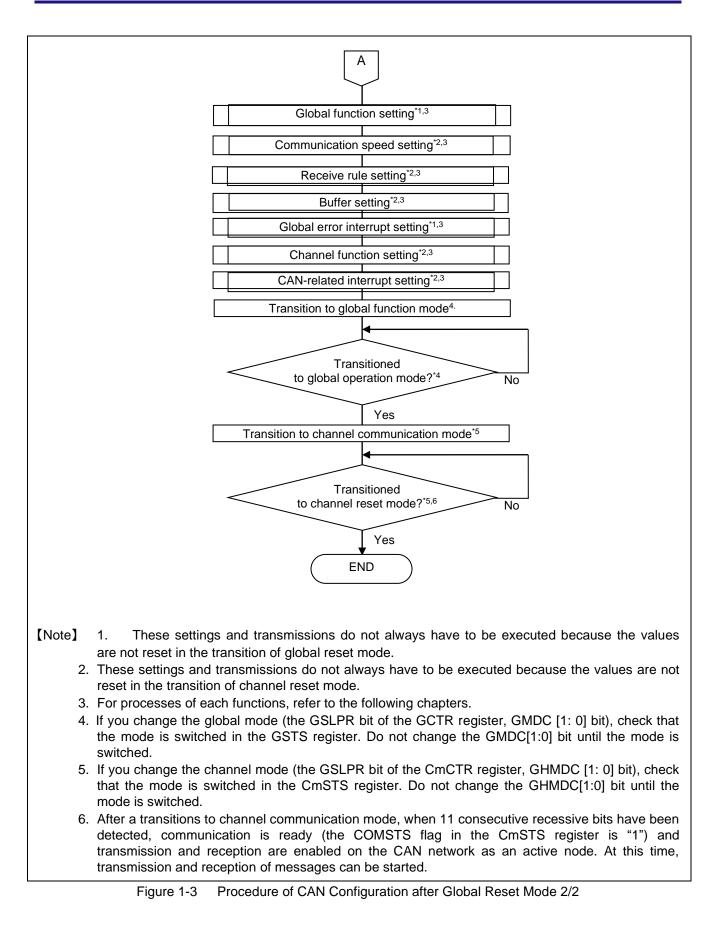

# 1.2.2 Setting Procedures of CAN Configuration after Global Reset Mode

Figure 1-3 and Figure 1-4 shows the procedure of CAN configuration after global reset mode.

mode is switched.

Figure 1-2 Procedure of CAN Configuration after Global Reset Mode 1/2

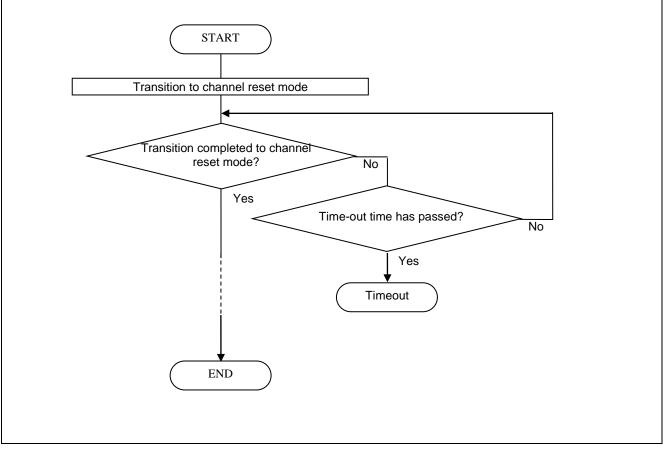

# 1.3 CAN Configuration after Channel Reset Mode

## 1.3.1 CAN Configuration after Channel Reset Mode

Perform the initialization of CAN configuration after channel reset mode transition.

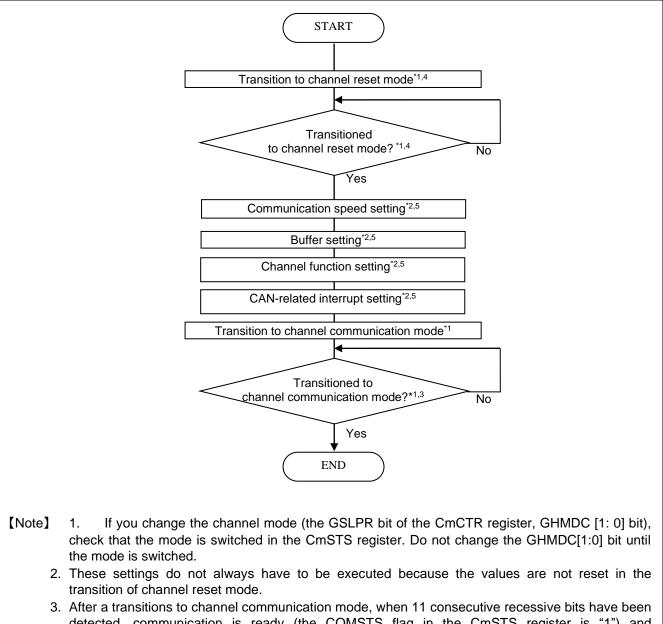

# 1.3.2 Setting Procedures of CAN Configuration after Channel Reset Mode

Figure 1-5 shows the procedure of CAN configuration after channel reset mode.

- 3. After a transitions to channel communication mode, when 11 consecutive recessive bits have been detected, communication is ready (the COMSTS flag in the CmSTS register is "1") and transmission and reception are enabled on the CAN network as an active node. At this time, transmission and reception of messages can be started.

- 4. To channel reset mode is transitioned before communication is completed. To allow transition to channel reset mode after communication is completed, confirm that communication has been completed and transition to channel halt mode has been completed, and then transition to channel reset mode.

- 5. For processes of each functions, refer to the following chapters.

Figure 1-4 Procedure of CAN Configuration after Channel Reset Mode

# 1.4 CAN Configuration after Channel Halt Mode

# 1.4.1 CAN Configuration after Channel Halt Mode

Perform the initialization of CAN configuration after channel halt mode transition.

# 1.4.2 Setting Procedures of CAN Configuration after Channel Halt Mode

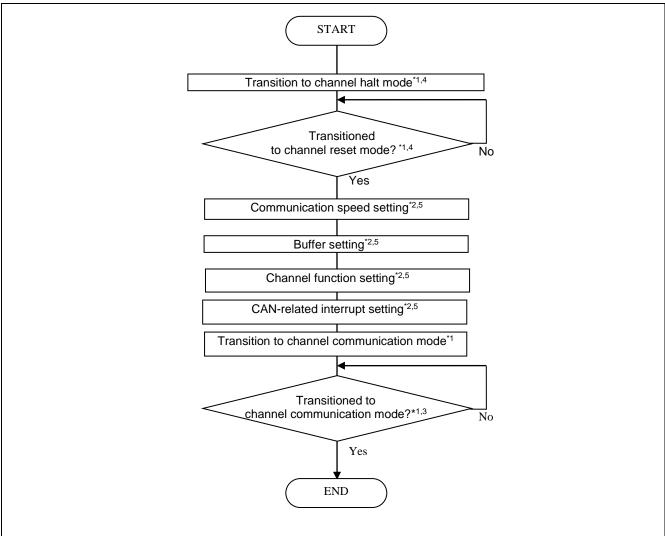

Figure 1-6 shows the procedure of CAN configuration after channel halt mode.

- [Note] 1. If you change the channel mode (the GSLPR bit of the CmCTR register, GHMDC [1: 0] bit), check that the mode is switched in the CmSTS register. Do not change the GHMDC[1:0] bit until the mode is switched.

- 2. These settings do not always have to be executed because the values are not reset in the transition of channel reset mode.

- 3. After a transitions to channel communication mode, when 11 consecutive recessive bits have been detected, communication is ready (the COMSTS flag in the CmSTS register is "1") and transmission and reception are enabled on the CAN network as an active node. At this time, transmission and reception of messages can be started.

- 4. While the CAN bus is locked to the dominant level (BLF flag in the CmERFLL register is "1"), transition to channel halt mode is not made. In that case, enter channel reset mode.

- 5. For processes of each functions, refer to the following chapters.

Figure 1-5 Procedure of CAN Configuration after Channel Halt Mode

# 2. CAN State (Mode) Transition

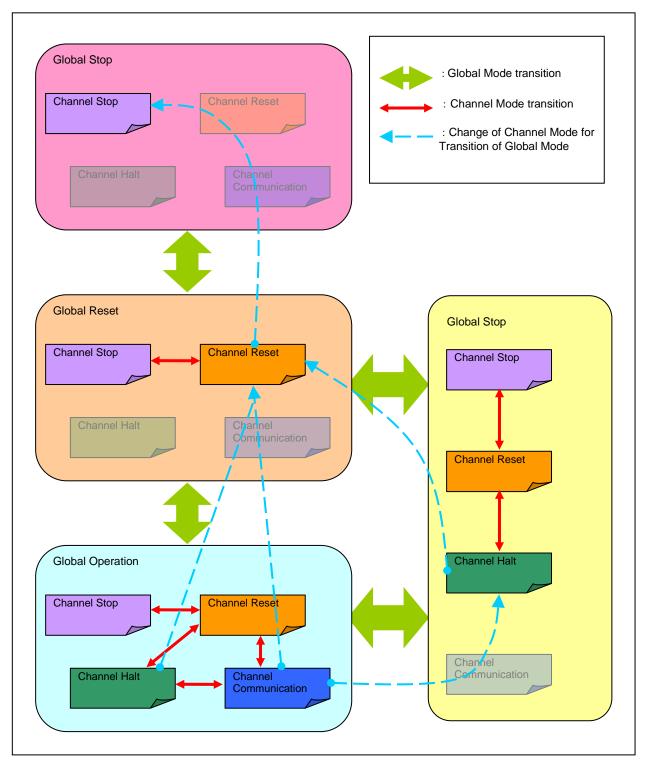

RS-CANFD module has the state of entire channels (here after called Global) and each channel (mode). The states RS-CANFD module has are shows below.

- Global Mode

- Global stop mode Global reset mode Global test mode Global operation mode

- Channel Mode Channel stop mode Channel reset mode Channel halt mode Channel communication mode

# 2.1 Global Mode

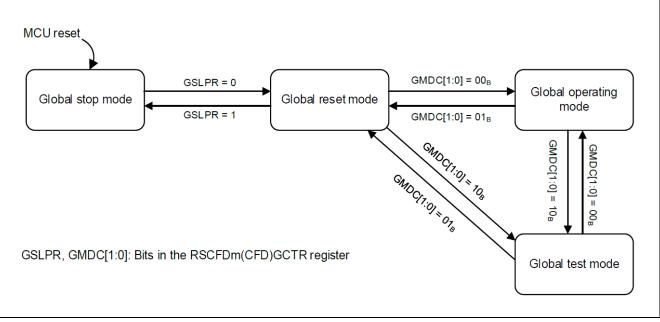

This is the mode of entire RS-CANFD mode. Figure 2-1 shows the transition of global mode.

Channel modes may transition in accordance with transitions of global modes. For details, refer to "Section 2.3, Change of Channel Mode for Transition of Global Mode".

Figure 2-1 Transitions of Global Mode

## 2.1.1 Global Stop Mode

This mode stop RS-CANFD module clocks. CAN clock do not runt and therefore power consumption is reduced. CAN registers can be read, but writing data to them is prohibited. Register values are retained.

## 2.1.2 Global Reset Mode

This mode performs settings for entire RS-CANFD module. When the RS-CANFD module transitions to global reset mode, some registers are initialized. Table 2-2 and Table 2-3 show the list of the registers to be initialized.

#### 2.1.3 Global Test Mode

This mode performs settings for test-related resisters. When the RS-CANFD module transitions to global test mode, all CAN communications are disabled.

#### 2.1.4 Global Operation Mode

This mode operates entire RS-CANFD module. When do a communication using each channel, transition to global operation mode is required.

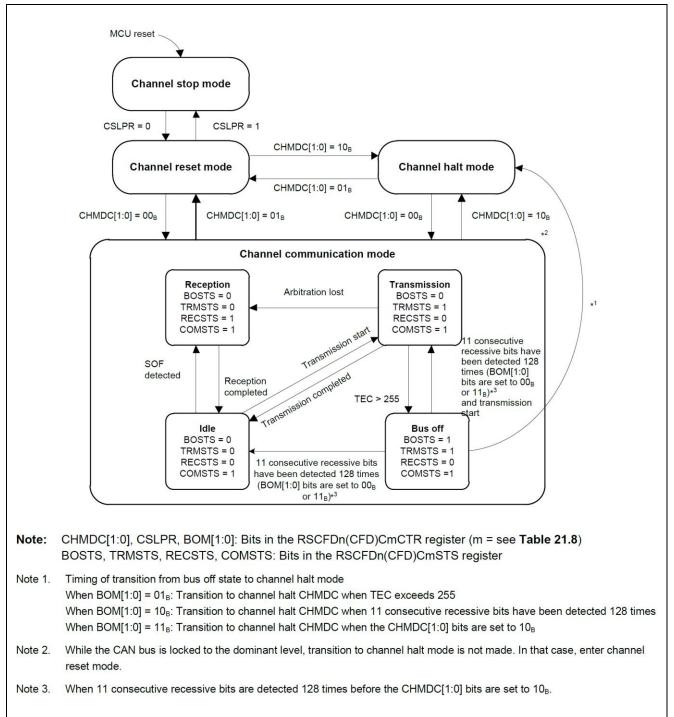

# 2.2 Channel Mode

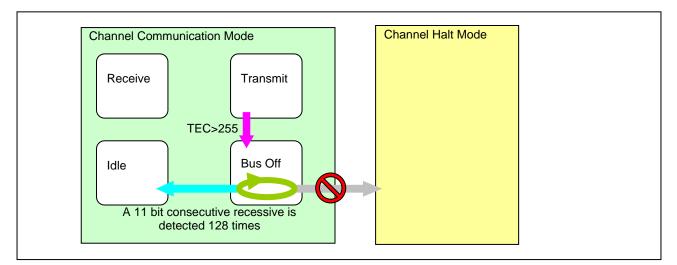

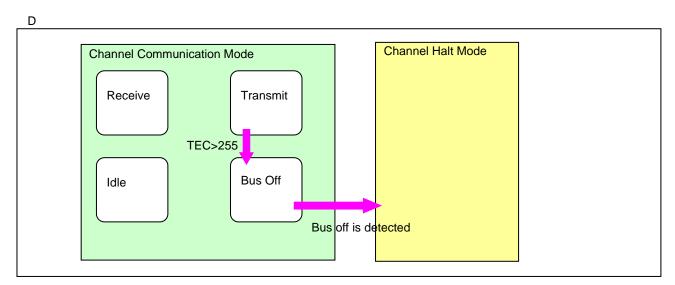

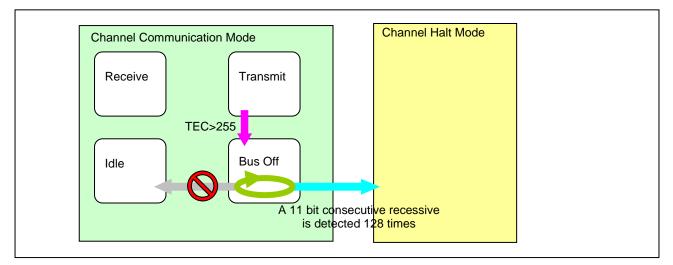

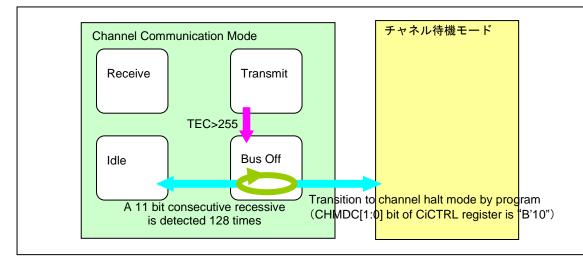

These modes is each of the channels. Figure 2-2 Shows a channel mode transition chart.

Figure 2-2 Transitions of Channel Mode

## 2.2.1 Channel Stop Mode

This mode stop RS-CANFD module clocks. CAN clock do not runt and therefore power consumption is reduced. CAN registers can be read, but writing data to them is prohibited. Register values are retained.

## 2.2.2 Channel Reset Mode

This mode performs settings for channel. When a transitions to channel reset mode, some channel-related registers are initialized. Table 2-2 shows the list of the registers to be initialized.

#### 2.2.3 Channel Halt Mode

This mode performs settings for test-related resisters of the channel. When a channel transitions to channel halt mode, corresponding CAN communication of the channel stops.

## 2.2.4 Channel Communication Mode

This mode perform CAN communication. Each cannel waits following communication states during CAN communication.

#### • Idle

Neither reception nor transmission is in progress.

• Reception

Receiving a message sent from another node.

• Transmission

Transmitting a message.

• Bus off

Isolated from CAN communication.

# 2.3 Change of Channel Mode for Transition of Global Mode

Channel modes may transition in accordance with transitions of global modes. Table 2-1 and figure 2-3 show the transitions of channel modes depending on the global mode setting.

| Table 2-1 | Transitions of Channel Modes Depending on Global Mode Setting |

|-----------|---------------------------------------------------------------|

|-----------|---------------------------------------------------------------|

|                                | Channel Mode after setting |               |               |                          |

|--------------------------------|----------------------------|---------------|---------------|--------------------------|

| Channel Mode<br>before Setting | Global Operating           | Global Test   | Global Reset  | Global Stop              |

| Channel communication          | Channel communication      | Channel halt  | Channel reset | Transition<br>prohibited |

| Channel halt                   | Channel halt               | Channel halt  | Channel reset | Transition<br>prohibited |

| Channel reset                  | Channel reset              | Channel reset | Channel reset | Channel stop             |

| Channel stop                   | Channel stop               | Channel stop  | Channel stop  | Channel stop             |

[Note] **Bold** : The positions are transitioned channel mode depending on the transition of global mode. *Red* : Restriction

Figure 2-3 Transitions of Global Mode and Channel Mode

| CFSTSk registerCFMC[7:0]、CFFLL、CFEMP、CFMLT、CFRXIF、CFTISTS registerCFkTXIFTMCp registerTMOM、TMTAR、TMTRTMSTSp registerTMTARM、TMTRM、TMTRF[1:0]、TMTSTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S、COMSTS、(ESIF)、<br>R、AERR、FERR、SERR、<br>BEF                                                                         |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| CmSTS registerREC[7:0], TEC[7:0]CmERFL registerCRCREG[14:0], ADERR, B0ERR, B1ERR, CERF<br>ALF, BLF, OVLF, BORF, BOEF, EPF, EWF,CmFDCTR registerEOCCLR, SOCCLRCmFDSTS registerSOC[7:0], EOC[7:0], SOCO, EOCO, TDCVF, TCmFDCRC registerCRCREG[20:0]CFCCk registerWhen transmit/receive FIFO buffer is in transmit modeCFSTSk registerCFKTXIFTMCp registerCFkTXIFTMCp registerTMTARSTSp (Bits of corresponding channel are initia<br>mode.)TMTARSTSy registerTMTARSTSp (Bits of corresponding channel are initia                                                                                                                                                     | R、AERR、FERR、SERR、<br>BEF                                                                                             |  |  |

| CMERFL registerALF、BLF、OVLF、BORF、BOEF、EPF、EWF、CmFDCTR registerEOCCLR、SOCCLRCmFDSTS registerSOC[7:0]、EOC[7:0]、SOCO、EOCO、TDCVF、TCmFDCRC registerCRCREG[20:0]CFCCk registerWhen transmit/receive FIFO buffer is in transmit modeCFSTSk registerWhen transmit/receive FIFO buffer is in transmit modeCFTISTS registerCFKC[7:0]、CFFLL、CFEMP、CFMLT、CFRXIF、CFTISTS registerCFkTXIFTMCp registerTMTARM、TMTRM、TMTRF[1:0]、TMTSTSTMTRSTSy registerTMTRSTSp (Bits of corresponding channel are initia mode.)TMTARSTSy registerTMTARSTSp (Bits of corresponding channel are initia                                                                                             | BEF                                                                                                                  |  |  |

| CmFDSTS registerSOC[7:0]、EOC[7:0]、SOCO、EOCO、TDCVF、TCmFDCRC registerCRCREG[20:0]CFCCk registerWhen transmit/receive FIFO buffer is in transmit modeCFSTSk registerWhen transmit/receive FIFO buffer is in transmit modeCFSTSk registerCFMC[7:0]、CFFLL、CFEMP、CFMLT、CFRXIF、CFTISTS registerCFkTXIFTMCp registerTMOM、TMTAR、TMTRTMSTSp registerTMTARM、TMTRM、TMTRF[1:0]、TMTSTSTMTRSTSy registerTMTRSTSp (Bits of corresponding channel are initia mode.)TMTARSTSy registerTMTARSTSp (Bits of corresponding channel are initia                                                                                                                                           | DCR[6:0]、                                                                                                            |  |  |

| CmFDCRC register         CRCREG[20:0]           CFCCk register         When transmit/receive FIFO buffer is in transmit model           CFSTSk register         When transmit/receive FIFO buffer is in transmit model           CFTISTS register         CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF,           CFTISTS register         CFkTXIF           TMCp register         TMOM, TMTAR, TMTR           TMSTSp register         TMTARM, TMTRM, TMTRF[1:0], TMTSTS           TMTRSTSy register         TMTARSTSp (Bits of corresponding channel are initia mode.)           TMTARSTSy register         TMTARSTSp (Bits of corresponding channel are initia mode.) | DCR[6:0]、                                                                                                            |  |  |

| CFCCk registerWhen transmit/receive FIFO buffer is in transmit modelCFSTSk registerWhen transmit/receive FIFO buffer is in transmit modelCFSTSk registerCFMC[7:0]、CFFLL、CFEMP、CFMLT、CFRXIF、CFTISTS registerCFkTXIFTMCp registerTMOM、TMTAR、TMTRTMSTSp registerTMTARM、TMTRM、TMTRF[1:0]、TMTSTSTMTRSTSy registerTMTRSTSp (Bits of corresponding channel are initia<br>mode.)TMTARSTSy registerTMTARSTSp (Bits of corresponding channel are initia                                                                                                                                                                                                                     |                                                                                                                      |  |  |

| CFSTSk register       When transmit/receive FIFO buffer is in transmit mode.)         CFSTSk register       CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF,         CFTISTS register       CFkTXIF         TMCp register       TMOM, TMTAR, TMTR         TMSTSp register       TMTARM, TMTRM, TMTRF[1:0], TMTSTS         TMTRSTSy register       TMTRSTSp (Bits of corresponding channel are initia mode.)         TMTARSTSy register       TMTARSTSp (Bits of corresponding channel are initia                                                                                                                                                                           |                                                                                                                      |  |  |

| CFSTSk register       CFMC[7:0], CFFLL, CFEMP, CFMLT, CFRXIF,         CFTISTS register       CFkTXIF         TMCp register       TMOM, TMTAR, TMTR         TMSTSp register       TMTARM, TMTRM, TMTRF[1:0], TMTSTS         TMTRSTSy register       TMTRSTSp (Bits of corresponding channel are initia mode.)         TMTARSTSy register       TMTARSTSp (Bits of corresponding channel are initia                                                                                                                                                                                                                                                                 | de or gateway mode : CFE                                                                                             |  |  |

| TMCp register       TMOM、TMTAR、TMTR         TMSTSp register       TMTARM、TMTRM、TMTRF[1:0]、TMTSTS         TMTRSTSy register       TMTRSTSp (Bits of corresponding channel are initia mode.)         TMTARSTSy register       TMTARSTSp (Bits of corresponding channel are initia mode.)                                                                                                                                                                                                                                                                                                                                                                            | When transmit/receive FIFO buffer is in transmit mode or gateway mode :<br>CFMC[7:0]、CFFLL、CFEMP、CFMLT、CFRXIF、CFTXIF |  |  |

| TMSTSp register       TMTARM、TMTRM、TMTRF[1:0]、TMTSTS         TMTRSTSy register       TMTRSTSp (Bits of corresponding channel are initia mode.)         TMTARSTSy register       TMTARSTSp (Bits of corresponding channel are initia                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      |  |  |

| TMTRSTSy register       TMTRSTSp (Bits of corresponding channel are initia mode.)         TMTARSTSy register       TMTARSTSp (Bits of corresponding channel are initia mode.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |  |  |

| TMTRSTSy register     mode.)       TMTARSTSy register     TMTARSTSp (Bits of corresponding channel are init)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TMTRSTSp (Bits of corresponding channel are initialized in channel reset mode.)                                      |  |  |

| niode:)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | alized in channel reset                                                                                              |  |  |

| TMTCSTSy register TMTCSTSp(Bits of corresponding channel are initial mode.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ized in channel reset                                                                                                |  |  |

| TMTASTSy register TMTASTSp(Bits of corresponding channel are initial mode.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TMTASTSp(Bits of corresponding channel are initialized in channel reset mode.)                                       |  |  |

| TXQCCm register TXQE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |  |  |

| TXQSTSm register TXQIF、TXQFLL、TXQEMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |  |  |

| THLCCm register THLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      |  |  |

| THLSTSm register THLMC[4:0]、THLIF、THLELT、THLFLL、THLEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                    |  |  |

| GTINTSTS0 register TSIFm、TAIFm、TQIFm、CFTIFm、THIFm (m=0-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                      |  |  |

| Table 2-2 F | Registers Initialized in Global Reset Mode or Channel Reset Mode |

|-------------|------------------------------------------------------------------|

|-------------|------------------------------------------------------------------|

Note: Bits and flags in parentheses exist only in registers in CAN FD mode.

| レジスタ          | ビット/フラグ                                                                      |

|---------------|------------------------------------------------------------------------------|

| CiCTRLレジスタ    | CHMDC[1:0]                                                                   |

| CiCTRHレジスタ    | CTMS[1:0]、CTME                                                               |

| CiSTSLレジスタ    | CHLTSTS、EPSTS、BOSTS、TRMSTS、RECSTS、COMSTS                                     |

| CiSTSHレジスタ    | REC[7:0]、TEC[7:0]                                                            |

| CiERFLLレジスタ   | ADERR、B0ERR、B1ERR、CERR、AERR、FERR、SERR、ALF、BLF、OVLF、<br>BORF、BOEF、EPF、EWF、BEF |

| CiERFLHレジスタ   | CRCREG[14:0]                                                                 |

| CFCCLkレジスタ    | 送受信FIFOバッファが送信モード:CFE                                                        |

| CFSTSkレジスタ    | 送受信FIFOバッファが送信モード : CFMC[5:0]、CFTXIF、CFRXIF、CFMLT、<br>CFFLL、CFEMP            |

| TMCpレジスタ      | TMOM、TMTAR、TMTR                                                              |

| TMSTSpレジスタ    | TMTARM、TMTRM、TMTRF[1:0]、TMTSTS                                               |

| TMTRMSxx レジスタ | TMTRSTSp                                                                     |

CAN Configuration (CAN FD Mode)

# **RH850 Series**

| TMTCSTSxxレジスタ | TMTCSTSp                              |

|---------------|---------------------------------------|

| TMTASTSxxレジスタ | TMTASTSp                              |

| THLCCiレジスタ    | THLE                                  |

| THLSTSiレジスタ   | THLMC[3:0]、THLIF、THLELT、THLFLL、THLEMP |

| CGTISRレジスタ    | TSIFi、TAIFi、CFTIFi、THIFi              |

|                               | Table 2-3 Registers Initialized in Global Reset Mode                                              |  |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| Registers                     | Bit/Flag                                                                                          |  |  |  |  |

| GSTS register                 | GHLTSTS                                                                                           |  |  |  |  |

| GERFL register                | EEF0、EEF1、EEF2、EEF3、(CMPOF)、THLES、MES、DEF                                                         |  |  |  |  |

| GTSC register                 | TS[15:0]                                                                                          |  |  |  |  |

| RMNDy register                | RMNSq                                                                                             |  |  |  |  |

| RFCCx register                | RFE                                                                                               |  |  |  |  |

| RFSTSx register               | RFMC[7:0]、RFIF、RFMLT、RFFLL、RFEMP                                                                  |  |  |  |  |

| CFCCk register                | When transmit/receive is in receive mode : CFE                                                    |  |  |  |  |

| CFSTSk register               | When transmit/receive FIFO is in receive mode : CFMC[7:0], CFFLL, CFEMP, CFTXIF, CFRXIF, CFMLT    |  |  |  |  |

| FESTS register                | CFkEMP、RFxEMP                                                                                     |  |  |  |  |

| FFSTS register                | CFkFLL、RFxFLL                                                                                     |  |  |  |  |

| FMSTS register                | CFkMLT、RFxMLT                                                                                     |  |  |  |  |

| RFISTS register               | RFxIF                                                                                             |  |  |  |  |

| CFRISTS register              | CFkRXIF                                                                                           |  |  |  |  |

| CDTCT register                | CFDMAEm、RFDMAEx                                                                                   |  |  |  |  |

| CDTSTS register               | CFDMASTSm、RFDMASTSx                                                                               |  |  |  |  |

| GTSTCFG register              | RTMPS[6:0]、C0ICBCE、C1ICBCE、C2ICBCE、C3ICBCE                                                        |  |  |  |  |

| GTSTCTR register              | RTME、ICBCTME                                                                                      |  |  |  |  |

| Note: Bits and flags in paren | Note: Bits and flags in parentheses exist only in registers in CAN FD mode.                       |  |  |  |  |

| CiCTRL register               | CHMDC[1:0]                                                                                        |  |  |  |  |

| CiCTRH register               | CTMS[1:0]、CTME                                                                                    |  |  |  |  |

| CiSTSL register               | CHLTSTS、EPSTS、BOSTS、TRMSTS、RECSTS、COMSTS                                                          |  |  |  |  |

| CiSTSH register               | REC[7:0]、TEC[7:0]                                                                                 |  |  |  |  |

| CiERFLL register              | ADERR、B0ERR、B1ERR、CERR、AERR、FERR、SERR、ALF、BLF、OVLF、<br>BORF、BOEF、EPF、EWF、BEF                      |  |  |  |  |

| CiERFLH register              | CRCREG[14:0]                                                                                      |  |  |  |  |

| CFCCLk register               | When transmit/receive FIFO buffer is in tramsmit mode : CFE                                       |  |  |  |  |

| CFSTSk register               | When transmit/receive FIFO buffer is in transmit mode : CFMC[5:0]、CFTXIF、CFRXIF、CFMLT、CFFLL、CFEMP |  |  |  |  |

| TMCp register                 | TMOM、TMTAR、TMTR                                                                                   |  |  |  |  |

| TMSTSp register               | TMTARM、TMTRM、TMTRF[1:0]、TMTSTS                                                                    |  |  |  |  |

| TMTRMSxx register             | TMTRSTSp                                                                                          |  |  |  |  |

| TMTCSTSxx register            | TMTCSTSp                                                                                          |  |  |  |  |

| TMTASTSxx register            | TMTASTSp                                                                                          |  |  |  |  |

| THLCCi register               | THLE                                                                                              |  |  |  |  |

| THLSTSi register              | THLMC[3:0]、THLIF、THLELT、THLFLL、THLEMP                                                             |  |  |  |  |

| CGTISR register               | TSIFi、TAIFi、CFTIFi、THIFi                                                                          |  |  |  |  |

| GSTS register                 | GHLTSTS                                                                                           |  |  |  |  |

| GERFLL register               | THLES、MES、DEF                                                                                     |  |  |  |  |

| GTSC register                 | TS[15:0]                                                                                          |  |  |  |  |

| レジスタ        | ビット/フラグ                                                            |

|-------------|--------------------------------------------------------------------|

| GSTSレジスタ    | GHLTSTS                                                            |

| GERFLLレジスタ  | THLES、MES、DEF                                                      |

| GTSCレジスタ    | TS[15:0]                                                           |

| RMNDn レジスタ  | RMNSn                                                              |

| RFCCmレジスタ   | RFE                                                                |

| RFSTSmレジスタ  | RFMC[5:0]、RFIF、RFMLT、RFFL、RFELL                                    |

| CFCCLkレジスタ  | 送受信FIFOが受信モード時:CFE                                                 |

| CFSTSkレジスタ  | 送受信FIFOバッファが受信モード時 : CFMC[5:0]、CFFLL、CFEMP、CFTXIF、<br>CFRXIF、CFMLT |

| RFMSTSレジスタ  | RFmMLT                                                             |

| CFMSTSレジスタ  | CFkMLT                                                             |

| RFISTSレジスタ  | RFmIF                                                              |

| CFISTSレジスタ  | CFkIF                                                              |

| GTSTCFGレジスタ | RTMPS[2:0]                                                         |

| GTSTCTRレジスタ | RTME                                                               |

## 3. Communication Speed

Set the communication speed for CAN communication. You need to perform the following settings to determine CAN communication speed.

- Bit Timing Setting

- Communication Speed Setting

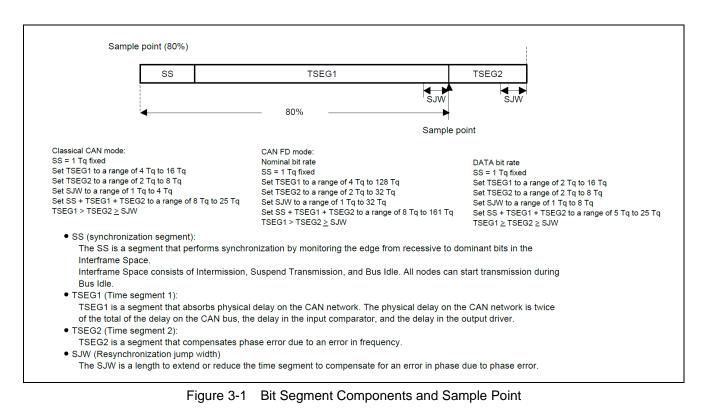

## 3.1 CAN Bit Timing Setting

In this CAN bit timing setting of RS-CANFD module, one bit of a communication frame consists of three segments. Figure 3-1 shows segments of bits and sample point.

In these segments, Time Segment 1(called TSEG1 hereafter) and Time Segment 2 (called TSEG2 hereafter) indicate the sample point. Also, it can be changed the timing for sampling by changing the values of segments. FD mode has 2 types of bit rate (nominal bit rate and data bit rate) and be sett for each of them.

This minimum protection area unit of timing setting is called 1 Time Quanta (called Tq hereafter), also it is consisted by inputted clock frequency and baud rate prescaler division value to RS-CANFD module.

# 3.2 Communication Speed Setting

Communication speed is consisted by CAN clock (fCAN) that is clock source of RS-CANFD module , baud rate prescaler division value, and Tq count per bit. fCAN is available for use clkc or clk xincan. For fCAN setting, refer to "Section 4.5, CAN clock source setting".

Table 3-1 and 3-2 show the main formula and example of communication speed. Table 3-3 shows example of bit timing setting.

| Formula of          | fCAN                                                                |          |                     |

|---------------------|---------------------------------------------------------------------|----------|---------------------|

| Communication Speed | Nominal Bit Rate Prescaler Division Ration $\times$ Tq count of 1 b |          | count of 1 bit time |

| fCAN                | 40MHz 20MHz 10MHz                                                   |          | 10MHz               |

| Comm                |                                                                     |          |                     |

| Speed               |                                                                     |          |                     |

| 1Mbps               | 10Tq(4)                                                             | 10Tq(2)  | 10Tq(1)             |

|                     | 20Tq(2)                                                             | 20Tq(1)  |                     |

| 500Kbps             | 10Tq(8)                                                             | 10Tq(4)  | 10Tq(2)             |

|                     | 20Tq(4)                                                             | 20Tq(2)  | 20Tq(1)             |

| 250Kbps             | 10Tq(16)                                                            | 10Tq(8)  | 10Tq(4)             |

|                     | 20Tq(8)                                                             | 20Tq(4)  | 20Tq(2)             |

| 125Kbps             | 10Tq(32)                                                            | 10Tq(16) | 10Tq(8)             |

|                     | 20Tq(16)                                                            | 20Tq(8)  | 20Tq(4)             |

| 83.3Kbps            | 8Tq(60)                                                             | 8Tq(30)  | 8Tq(15)             |

|                     | 10Tq(48)                                                            | 10Tq(24) | 10Tq(12)            |

|                     | 12Tq(40)                                                            | 12Tq(20) | 12Tq(10)            |

|                     | 15Tq(32)                                                            | 15Tq(16) | 15Tq(8)             |

|                     | 16Tq(30)                                                            | 16Tq(15) | 20Tq(6)             |

|                     | 20Tq(24)                                                            | 20Tq(12) | 24Tq(5)             |

|                     | 24Tq(20)                                                            | 24Tq(10) |                     |

| 33.3Kbps            | 8Tq(150)                                                            | 8Tq(75)  | 10Tq(30)            |

|                     | 10Tq(120)                                                           | 10Tq(60) | 12Tq(25)            |

|                     | 12Tq(100)                                                           | 12Tq(50) | 15Tq(20)            |

|                     | 15Tq(80)                                                            | 15Tq(40) | 20Tq(15)            |

|                     | 20Tq(60)                                                            | 20Tq(30) |                     |

|                     | 24Tq(50)                                                            | 24Tq(25) |                     |

Table 3-1

Example of Communication Speed setting (Nominal Bit Rate)

Note: Values in ( ) are baud rate prescaler division values.

| Table 3-2 | Example of Communication | Speed | Setting (Data Bit Rate) |  |

|-----------|--------------------------|-------|-------------------------|--|

|-----------|--------------------------|-------|-------------------------|--|

| Formula of          |         | fCAN                                                       |         |  |  |

|---------------------|---------|------------------------------------------------------------|---------|--|--|

| Communication Speed |         | Data Bit Prescaler Divison Ration × Tq count of 1 bit time |         |  |  |

| fCAN                | 40MHz   | 20MHz                                                      |         |  |  |

| Comm                |         |                                                            |         |  |  |

| Speed               |         |                                                            |         |  |  |

| 5Mbps               | 8Tq(1)  |                                                            | なし      |  |  |

| 2Mbps               | 20Tq(1) |                                                            | 10Tq(1) |  |  |

Note: Values in () are baud rate prescaler division values.

| 1 Bit |    | Setting Va | Sample Point |     |                |

|-------|----|------------|--------------|-----|----------------|

| I DIL | SS | TSEG1      | TSEG2        | SJW | Percentage (%) |

| 5Tq   | 1  | 2          | 2            | 1   | 60.00          |

| 8Tq   | 1  | 4          | 3            | 1   | 62.50          |

| ory   | 1  | 5          | 2            | 1   | 75.00          |

| 10Tq  | 1  | 6          | 3            | 1   | 70.00          |

| iuiq  | 1  | 7          | 2            | 1   | 80.00          |

| 16Ta  | 1  | 10         | 5            | 1   | 68.75          |

| 16Tq  | 1  | 11         | 4            | 1   | 75.00          |

|       | 1  | 12         | 7            | 1   | 65.00          |

| 20Tq  | 1  | 13         | 6            | 1   | 70.00          |

|       | 1  | 15         | 4            | 3   | 80.00          |

| 247.4 | 1  | 15         | 8            | 1   | 66.66          |

| 24Tq  | 1  | 16         | 7            | 1   | 70.83          |

| 50Tq  | 1  | 39         | 10           | 4   | 80.00          |

| Table 3-3 | Example of Bit Timing Setting |

|-----------|-------------------------------|

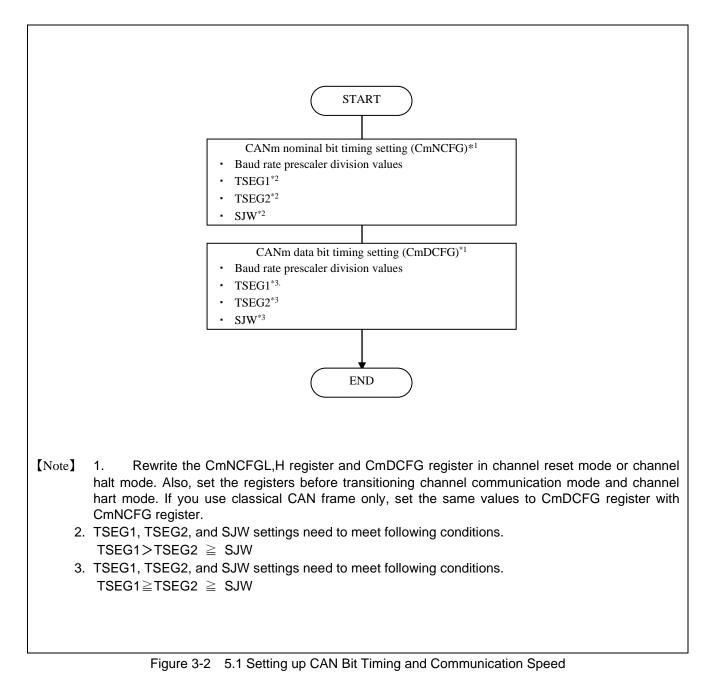

# 3.3 CAN Bit Timing and Communication Speed Setting Procedures

Figure 3-2 shows setting procedures of CAN bit timing and communication speed.

Perform these settings during CAN configuration.

Refer to "Section 1, CAN Configuration" for procedure of CAN configuration.

## 4. Global Function

Set the following functions that are common to entire RS-CANFD Module (all channels).

- Transmit priority setting

- DLC check setting

- DLC replacement function setting

- Mirror function setting

- CAN clock source setting

- Timestamp clock setting

- Interval timer prescaler setting

# 4.1 Transmit Priority Setting

Set the transmit priority when the transmit request is requested from multiple transmit buffer in the same channel.

It is not able to set the transmit priority for each channel because the transmit priority is common to entire channels.

You can choose following two of judgment methods.

#### • ID priority

The messages are transmitted according to the priority of stored message IDs. Priority of IDs conforms to the CAN bus arbitration specification defined in the CAN specification.

Targets of priority determination are IDs of messages placed in transmit buffers, transmit/receive FIFO buffers (set to transmit mode or gateway mode<sup> $\star$ </sup>), and transmit queues.

When transmit/receive FIFO buffers is used, the oldest message in a FIFO buffer becomes a target of priority determination.

When a message is being transmitted from a transmit/receive FIFO buffer, the next message in the same FIFO buffer becomes a target of priority determination.

When transmit queues are used, all messages in transmit queues are targets of priority determination. When the same ID is set for two or more buffers, the buffer with a lower number takes precedence.

#### • Transmit buffer number priority

the message in the transmit buffer whose number is the lowest among buffers having transmit requests are transmitted first.

When transmit/receive FIFO buffers is linked to transmit buffers, transmit priority is determined according to the linked transmit buffer numbers.

When messages are retransmitted due to an arbitration-lost or an error, transmit priority determination is made again whichever transmit priority is selected.

[Note] 1. It is prohibited to select when using transmit queue. Select the ID priority.

# 4.2 DLC Check Setting

Set the ability and disability of DLC check function.

When the DLC check function is enabled, DLC filter processing is performed for messages that pass through the acceptance filter processing.

When the DLC check function is disenabled, DLC check is not performed after performing acceptance filter processing.

In DLC check, when the DLC value in a message is equal to or larger than the DLC value set in the receive rule, the message passes through the DLC filter processing. When the DLC value of the received message is smaller than that of the receive rule, the message does not pass through the DLC filter processing. In this case, the message is not stored in the receive buffer or the FIFO buffer and a DLC error is present.

Please refer to "Section 5, Receive Rule Table" for the receive rule.

## 4.3 DLC Replacement Function

Set the ability and disability of DLC replacement function.

DLC replacement is effective only when DLC check function is enabled.

When DLC replacement is enabled, the DLC value of the receive rule is stored in the buffer instead of the DLC value of the received message. In this case, a value of "00'H" is written to data bytes that are larger than the DLC value of the receive rule.

When DLC replacement is enabled, the DLC value of the received message is stored in the buffer. In this case, all

the data bytes in the received message are stored in the buffer.

Please refer to "Section 5, Receive Rule Table" for the receive rule.

| GCFGL           | Register                         | Received message DLC                                                                  | Received N          | lessage       |

|-----------------|----------------------------------|---------------------------------------------------------------------------------------|---------------------|---------------|

| DCE Bit         | DRE Bit                          | ✓ Receive rule DLC                                                                    | Processing          | Stored DLC    |

| 0<br>(DLC check | 0<br>(DLC replacement            | Received message DLC<br><received dlc<="" rule="" td=""><td></td><td></td></received> |                     |               |

| disabled)       | is disabled)                     | Received message DLC                                                                  |                     |               |

|                 |                                  | ≧Received rule DLC                                                                    |                     |               |

|                 |                                  | Received rule DLC=0                                                                   |                     |               |

|                 |                                  |                                                                                       | Stored to buffer*1  | Received      |

|                 | 1                                | Received message DLC                                                                  |                     | message DLC   |

|                 | (DLC replacement                 | < Received rule DLC                                                                   |                     |               |

|                 | is enabled)                      | Received message DLC                                                                  |                     |               |

|                 |                                  | ≧Received rule DLC                                                                    |                     |               |

|                 |                                  | Received rule DLC=0                                                                   |                     |               |

|                 |                                  |                                                                                       |                     |               |

| 1               | 0                                | Received message DLC                                                                  | Discard (DLC error) | —             |

| (DLC check is   | (DLC replacement                 | <received dlc<="" rule="" td=""><td></td><td></td></received>                         |                     |               |

| enable)         | is disabled)                     | Received message DLC                                                                  | Stored to buffer    | Received      |

|                 |                                  | ≧Received rule DLC                                                                    |                     | message DLC   |

|                 |                                  | Received rule DLC=0                                                                   | Stored to buffer    | Received      |

|                 |                                  |                                                                                       |                     | message DLC   |

|                 | 1                                | Received message DLC                                                                  | Discard (DLC error) | —             |

|                 | (DLC replacement                 | <received dlc<="" rule="" td=""><td></td><td></td></received>                         |                     |               |

|                 | is enabled) Received message DLC |                                                                                       | Stored to buffer    | Received rule |

|                 |                                  | $\geq$ Received rule DLC                                                              |                     | DLC*2         |

|                 |                                  | Received rule DLC=0                                                                   | Stored to buffer    | Received      |

|                 |                                  |                                                                                       |                     | message DLC   |

| Table 4-1 | DLC Filter Processing and DLC Replacement Processing |

|-----------|------------------------------------------------------|

|-----------|------------------------------------------------------|

[Note] 1.DLC check itself is not performed.

2. "00'H" is written to data bytes that are larger than the DLC of the receive rule.

# 4.4 Mirror Function Setting

Set the ability and disability of mirror function.

The mirror function allows reception of own transmitted messages. When the mirror function is in use, receive rules for which mirror function is unused are applied to the data processing for messages received from other CAN nodes. When own transmitted messages are received, receive rules for which mirror function is unused are used for data processing.

Please refer to "Section 5, Receive Rule Table" for the receive rule.

| MME Bit of<br>GCFGL Register  | GAFLLB Bit of<br>GAFLDHj Register | Message Targeted for Data Processing of Receive rule |

|-------------------------------|-----------------------------------|------------------------------------------------------|

| 0                             | 0                                 | Message received from other CAN node                 |

| (Mirror function is disabled) | 1                                 | No targeted message                                  |

| 1                             | 0                                 | Message transmitted from other CAN node              |

| (Mirror function is enabled)  | 1                                 | Own transmitted message transmitted                  |

#### Table 4-2 DLC Filter Processing and DLC Replacement Processing

# 4.5 CAN Clock Source Setting

Set the CAN clock (fCAN) which is clock source of CAN clock source in DCS bit of GCFG register. The clocks enabled as CAN clock source are shown below.

- clk\_xincan

- clkc

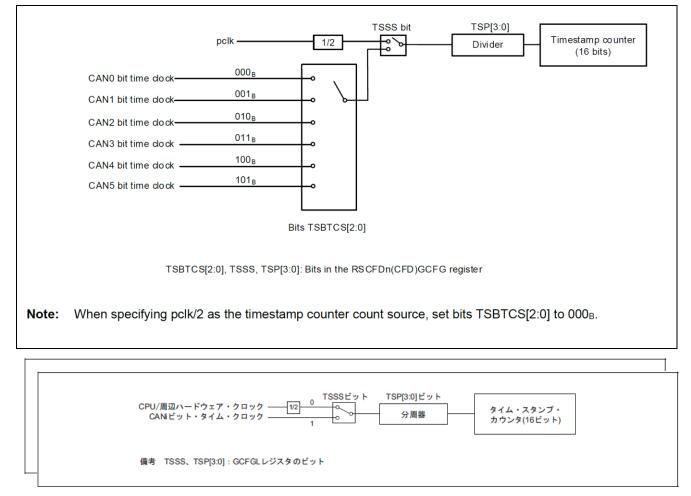

# 4.6 Timestamp Clock Setting

Set the clock source and the Division Ration for using timestamp clock.

The timestamp counter is a 16-bit free-running counter used for recording the message reception time and transmission time. The timestamp counter value is fetched at the SOF (Start of Frame)<sup>\*1</sup> of the message and is then stored in a receive buffer or a FIFO buffer together with the message ID and data during data reception.

You can select the following clocks for using timestamp.

- pclk/2

- CANm nominal time clock

When the nominal CANm bit time clock is used as a clock source, the timestamp counter stops when the corresponding channel transitions to channel reset mode or channel halt mode. When pclk/2 is used as a clock source, the timestamp function is not affected by channel mode.

Figure 4-1 show the timstop function block diagram.

Figure 4-1 Timestamp Function Block Diagram

[Note] 1. Start Of Frame Field represent start of frame

# 4.7 Interval Timer Prescaler Setting

Set the prescaler value when pclk is selected as an interval timer count source.

Please refer to "Section 6.4.3, Interval Timer Counter Setting" for interval timer function.

# 4.8 Global Function Setting

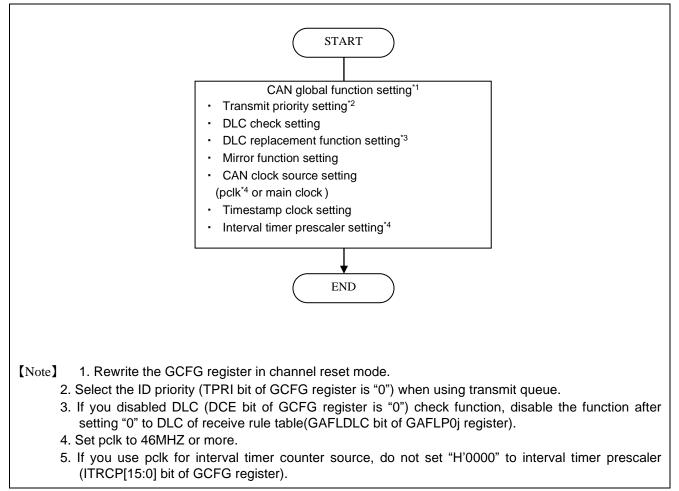

Figure 4-2 show global function setting procedures.

Perform these settings during CAN configuration.

Prese refer to "Section 1, CAN Configuration" for CAN configuration setting procedure.

Figure 4-2 Global Function Setting Procedure

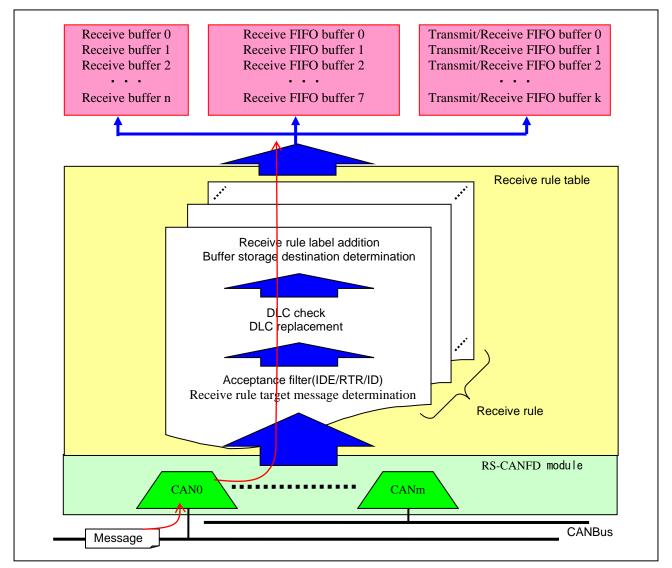

# 5. Receive Rule Table

Set receive rule table for filtering received message.

Data processing using the receive rule table store selected messages to the specified buffer. Data processing includes acceptance filter processing, DLC filter processing, routing processing, label addition processing, and mirror function processing.

Following setting is required for receive rule.

- Receive rule setting

- IDE/RTR/ID setting

- Receive rule target message setting

- IDE mask/RTR mask/ID mask setting

- DLC check setting

- Receive rule label setting

- Stored buffer setting

Figure 5-1 Filtering Image by Receive Rule Table

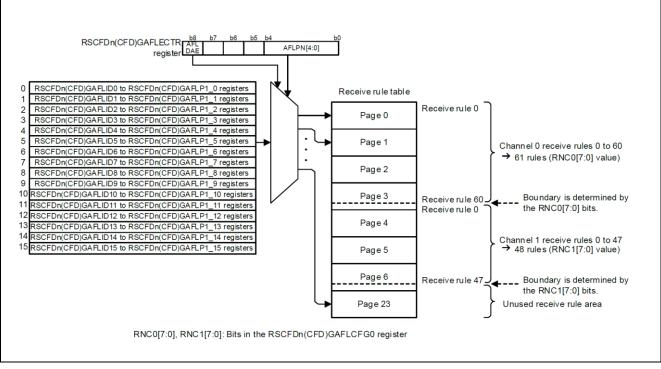

## 5.1 Receive Rules Setting

Set the receive rules for each channel.

The receive rules are  $64 \times$  channels in entire module, and the maximum channel unable to register channel rules to a channel are 128.

Check processes begin with the lowest channel rule number in ascending order. When all the bits to be compared in a received message match the bits set in the receive rule or when all the receive rules are compared without any match, filter processing stops. When there is no matching receive rule, the received message is not stored in the receive buffer or FIFO buffer.

The restrictions of receive rules can be registered are shown below.

- Restriction of receive rules for each channel

- CAN0 receive rules  $\leq 64 \times$  channels

- •

- CANm receive rules  $\leq 64 \times$  channels

- Restriction of all receive channels CAN0 receive rules + • • • +CANm receive rules ≤64 × channels

Figure 5-2 shows the receive rules registration diagram when channel 0,1 is used.

Figure 5-2 Receive Rule Registration (in the case of setting channel 0 and 1)

# 5.2 IDE/RTR/ID Setting

Set the ID format (standard ID or extended ID), frame format(data frame or remote frame), and receive ID of the received message.

# 5.3 Receive Rule Target Message Setting

When you set the transmitted message from another CAN node (GAFLLB bit of GAFLIDHj register is "0"), data processing to be performed using the receive rule when a message transmitted from another CAN node is received. When you set the own transmitted message using mirror function (GAFLLB bit is "1"), data processing to be

performed using the receive rule when the own transmitted message is received.

Please refer to "Section 4.4, Mirror Function Setting" for mirror function.

# 5.4 IDE Mask/RTR Mask/ID Mask Setting

Set the mask value that is set in IDE/RTR/ID.

The bit that is not masked in IDE mask/RTR mask/ID mask becomes effective by acceptance filter.

# 5.5 DLC Check Counter Value Setting

Set DLC value of the receive rule which is compared with DLC value of received message when DLC check is

allowed DLC.

Please refer to "Section 4.2, DLC check setting" for DLC check.

# 5.6 Routing Processing

When the payload length of the received message exceeds the payload storage size of the storage buffer, the CMPOF flag in the GERFL register is set to 1 (payload overflow) and the processing is handled according to the CMPOC bit in the GCFG register. When the CMPOC bit is "0", the received message which exceeds the payload storage size is not stored in the buffer. When the CMPOC bit is "1", the received message is stored in the buffer with payloads exceeding the storage size being discarded.

# 5.7 Receive Rule Label Setting

Set added 12-bit label information when message that passed through filter processing is stored to buffer.

It is possible to set label voluntary, and it is able to freely use received message label by program. For example, if

you set the receiving channel number to the label, it is possible to check which channel the message with same ID in the receive FIFO buffer was received.

# 5.8 Store Buffer Setting

Set the buffer stored the message that passed through filter processing.

Buffers be unable to select as storage destination are shown below.

- Receive buffer q (For 1 receive rule, 1 buffer is selectable.)

- Receive FIFO buffer q

- Transmit/Receive FIFO buffer k (receive mode)

Maximum 2 store buffer is selectable for 1 receive rule. However, It is only possible to select 1 buffer as storage destination. (For example, it is not possible to store to receive buffer 0 and 1.)

Example of maximum storage destination)

- Max 2 buffer = (Receive FIFO buffer x) : 1 piece

- + receive buffer q : 1 piece

- Max 2 buffer = (Receive FIFO buffer + Transmit/Receive FIFO buffer k) : 2 piece

Unable/ Disable setting example)

$\circ$  : Store to receive buffer 0, receive FIFO buffer 2, and receive FIFO buffer 3

×: Store to receive buffer 0, receive buffer 1, and receive FIFO buffer 2 \* Disable to store 2 receive buffer.

# 5.9 Receive Rule Usage Example

Receive rule usage example are shown below.

- Example. 1

- Example of each register is shown when below messages are received.

- ID format : Standard ID

- Message format : Data frame

- Mirror Function : Massage receive from another CAN node

: 010h

- Receive ID : 120h,121h,122h,123h

- DLC : Receive message DLC  $\geq 6$

- Label

- Storage destination buffer : Receive buffer 3, Receive FIFO buffer 0, 1, 2

|             |       | GAFLIDE/GAFLIDEM | GAFLRTR/GAFLRTRM | GAFLLB | GAFLID/GAFLIDM  |            |            |            |  |  |

|-------------|-------|------------------|------------------|--------|-----------------|------------|------------|------------|--|--|

| GAFLIDLj,Hj |       | 0                | 0                | 0      | B'00000         | B'00000000 | B'0000001  | B'00100000 |  |  |

| GAFLMLj,Hj  |       | 1                | 1                | —      | B'00000         | B,00000000 | B'00000111 | B'11111100 |  |  |

|             | H'120 |                  |                  |        | В'              | В'         | B'001      | B'00100000 |  |  |

| Receivable  | H'121 | 0                | 0                | 0      | B' B'001 B'0010 |            |            |            |  |  |

| message     | H'122 | 0                | 0                | 0      | В'              | В'         | B'001      | B'00100010 |  |  |

|             | H'123 |                  |                  |        | В'              | В'         | B'001      | B'00100011 |  |  |

|          | GAFLDLC | GAFLPTR | GAFLRMV | GAFLRMDP | GAFLFDP  |

|----------|---------|---------|---------|----------|----------|

| GAFLP0Hj | 6       | H'010   | —       | —        | _        |

| GAFLP0Lj | Ι       | _       | 1       | 3        | B' 00011 |

#### • Example. 2

- Example of each register is shown when below messages are received.

- ID format : Standard ID

- Message format : Remote frame, Data frame

- Mirror Function : Massage receive from another CAN node

:130h

- Receive ID : 130h

- DLC : Unused DLC check

- Label

- Storage destination buffer : Receive FIFO buffer 4, 6, Transmit/Receive FIFO buffer 1, 2

|             |              | GAFLIDE/GAFLIDEM | GAFLRTR/GAFLRTRM | GAFLLB | GAFLID/GA | FLIDM      |            |            |

|-------------|--------------|------------------|------------------|--------|-----------|------------|------------|------------|

| GAFLIDLj,Hj |              | 0                | 0                | 0      | B'00000   | B'00000000 | B'00000001 | B'00110000 |

| GAFLMLj,Hj  |              | 1                | 0                | -      | B'00000   | B'00000000 | B'00000111 | B'11111111 |

| Receivable  | H'130 (Data) | 0                | 0                | 0      | В'        | В'         | B'001      | B'00110000 |

| Message     | H'130 (Rmt)  | 0                | 1                | 0      | В'        | В'         | B'001      | B'00110000 |

|          | GAFDLC | GAFLPTR | GAFLRMV | GAFLRMDP | GAFLFDP |

|----------|--------|---------|---------|----------|---------|

| GAFLP0Hj | 0      | H'130   | —       | —        | _       |

| GAFLP0Lj |        | —       | 0       | 0        | B'10001 |

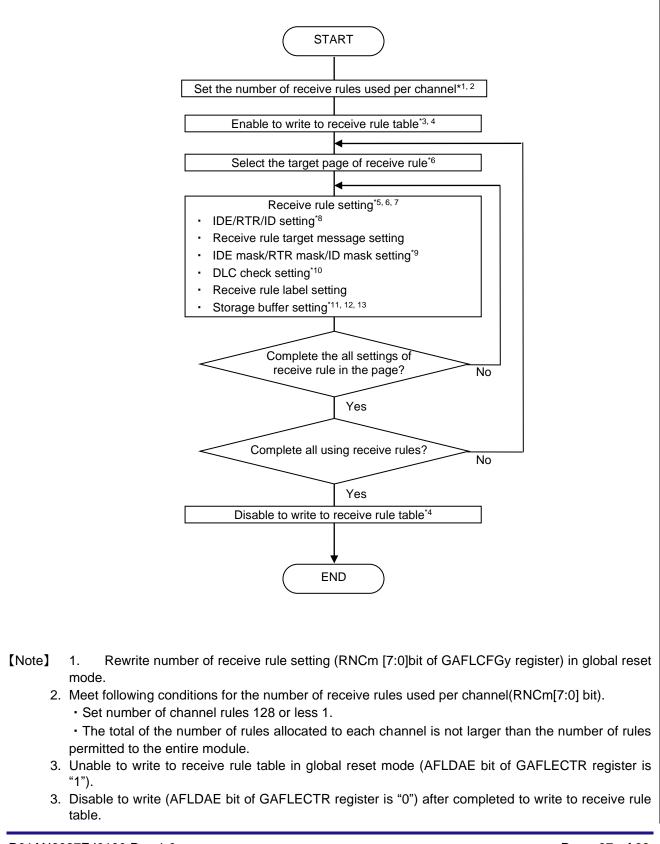

# 5.10 Receive Rule Table Setting Procedures

Figure 5-3 show receive rule table setting procedures.

Set these settings during CAN configuration.

Please refer to "section 1, CAN Configuration" for CAN configuration processing.

- 4. Do not set the page more than number of pages that can be set in module to setting target page.

- 5. Rewrite receive rule(GAFLIDj register, GAFLMj register, GAFLP0j register, GAFLP1j register) in the condition enabled to write to receive rule table and global reset mode.

- 6. Set receive rule continusly for each cahnnel. It is diabled to share and set alternately with another channel.

- In standard ID, set standard ID values to b10~b0 ID(GAFLID[28:0] bit of GAFLIDj register), and set "0" to b28~b11.

- If IDE bit is not compared (GAFLIDEM bit of GAFLMj register is "0"), set "do not compared all bit" (all GAFLIDEM[28:0] bit of GAFLMj register is "0").

- 9. It is effective if DLC check function is allowed(DCE bit of GCFG register is "1").

- 10.Maximum 8 FIFO buffers can be selected. However, maximum 7 buffers can be selected if the message is stored to receive buffer (GAFLRMV bit of GAFLP0j register is "1").

- 11.Only select transmit/receive buffer set to receive FIFO buffer and receive mode, or gateway mode\*.

- 12. If you select receive buffer as storage destination, enable to receive buffer (GAFLRMV bit is "1"), and set the number smaller than the number used receive buffer (Setting values to NRXMBm[7:0] bit of RMNBy register).

Figure 5-3 Receive Rule Table Setting Processing

# 6. Buffer, FIFO Buffer

Set buffer used in transmit/ receive and FFO buffer. Following buffer and FIFO buffer setting are required.

- Receive buffer setting

- Receive FIFO buffer setting

- Transmit/Receive FIFO buffer setting

- Transmit buffer setting

- Transmit qeue

- Transmit history buffer setting

- Payload strage size

The restriction of settable number of buffers to receive buffer, receive FIFO buffer, and transmit/receive FIFO buffer are showed below.

Receive buffer  $\times$  (12+Payload strage size) +Total (Stage number  $\times$  (12+Payload strage size) ) of Receive FIFO buffer x +Total (Stage number  $\times$  (12+Payload strage size) ) of Transmit/Receive FIFO buffer k  $\leq$ 7168 byte

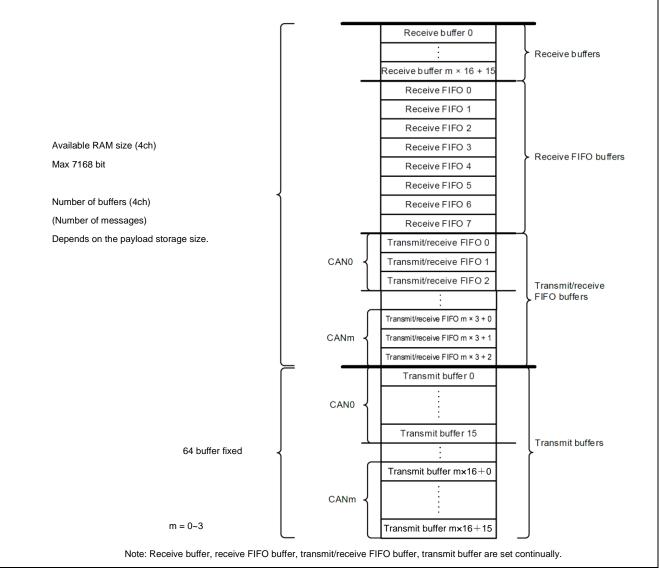

Figure 6-1 shows buffer configuration.

Figure 6-1 Buffer Configuration

## 6.1 Receive Buffer Setting

Set number of buffer assigned to buffer and payload size abled to store to per buffer. It is possible to assign buffers of  $0\sim16\times$  number of channels to receive buffer. Receive buffer is not able to use if "0" is set to number of receive buffer.

There is no setting of related interrupt because there is no interrupt of related receive buffer.

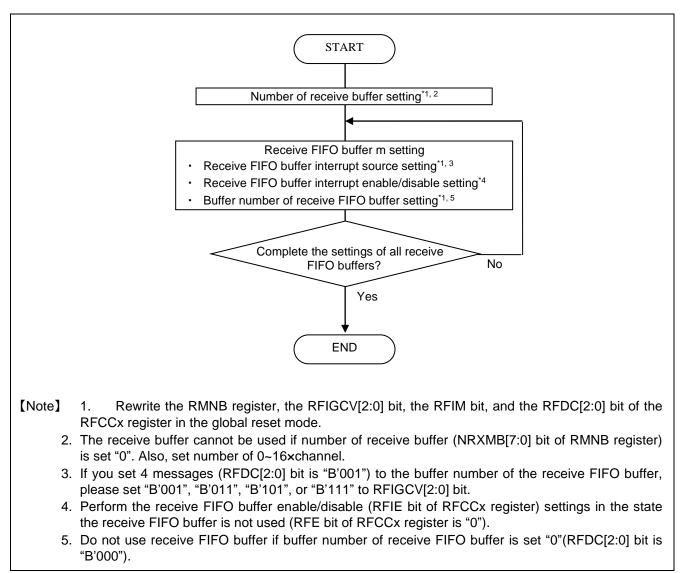

# 6.2 Receive FIFO Buffer Setting

Required settings used for receive FIFO buffer are showed below.

- Number of buffers and payload size setting

- Interrupt enable/disable setting, and interrupt source setting

#### 6.2.1 Number of Buffers setting

Set number of buffer assigned to FIFO buffer and payload size.

There are 8 receive buffers, and maximum 128 buffers can be assigned.

Number of buffers assigned to receive FIFO buffer are able to select from 0<sup>\*1</sup>, 4, 8, 16, 32, 48, 64, 128.

#### 6.2.2 Interrupt enable/disable Setting, and Interrupt Source Setting

Set interrupt enable/disable setting, and interrupt source setting.

When you use receive FIFO interrupt, interrupt source able to select below.

- Receive FIFO interrupt occur (RFM bit of RFCCx register is "0") when RFIGCV[2.0] bit of RFCCx register meet following conditions.

- When the message stored to receive FIFO buffer is 1/8 full.<sup>\*2</sup>

- When the message stored to receive FIFO buffer is 2/8 full.

- When the message stored to receive FIFO buffer is 3/8 full.<sup>\*2</sup>

- When the message stored to receive FIFO buffer is 4/8 full.

- When the message stored to receive FIFO buffer is 5/8 full.\*2

- When the message stored to receive FIFO buffer is 6/8 full.

- When the message stored to receive FIFO buffer is 7/8 full.<sup>\*2</sup>

- When receive FIFO buffer is full.

- Receive FIFO interrupt occurs every time when a message reception is completed (RFIM bit of RFCCx register is "1").

- [Note] 1. If you do not use receive FIFO buffer, set 0 message (RFDC[2:0] bit of RFCCx register is "B'000") to buffer number of receive FIFO buffer.

- 2. Do not set if you set 4 messages (RFDC[2:0] bit is "B'001") to buffer number of receive FIFO buffer.

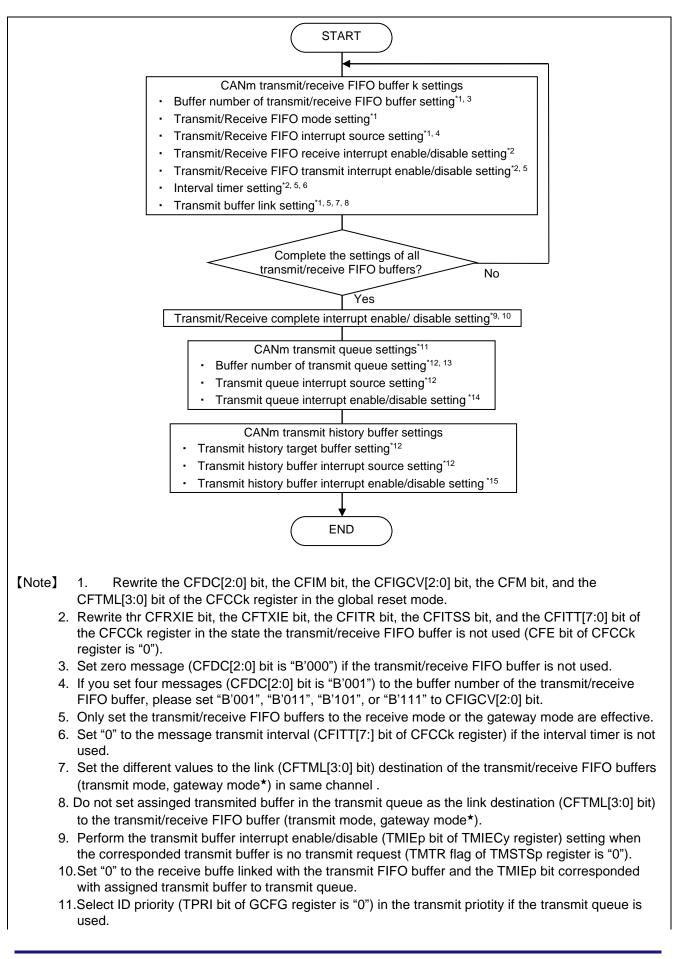

#### 6.3 Transmit/Receive FIFO Buffer Setting

Required settings for using transmit/receive FIFO is shown below.

- Number of buffers setting

- Interrupt enable/disable setting, and interrupt source setting

- Transmit/Receive FIFO mode setting

- Interval timer counter setting (Transmit mode, gateway mode<sup>★</sup>)

- Transmit buffer link setting (Transmit mode, gateway mode<sup> $\star$ </sup>) •

#### 6.3.1 Number of buffers setting

There are three transmit/receive FIFO buffers for each channel, and maximum 128 buffers are assigned. Number of buffers assigned to transmit/receive FIFO buffer are able to select from 0\*1, 4, 8, 16, 32, 48, 64, 128.

#### 6.3.2 Interrupt Enable/Disable Setting, and Interrupt Source Setting

Set interrupt enable/disable setting, and interrupt source setting of each transmit/receive FIFO buffer. Table 6-1 shows settable interrupt source for each transmit/receive FIFO mode.

| Transmit/Receive<br>FIFO Mode | CFIM Bit of<br>CFCCLk<br>Register | Interrupt Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Mode                  | 0                                 | When receive message is met condition set in CFIGCV[2:0] bit of CFCCLK register, receive complete interrupt of transmit/receive FIFO is occurred.<br>CFIGCV[2:0] bit setting<br>$000_B$ : When the message stored to receive FIFO buffer is 1/8 full. <sup>*2</sup><br>$001_B$ : When the message stored to receive FIFO buffer is 2/8 full.<br>$010_B$ : When the message stored to receive FIFO buffer is 3/8 full. <sup>*2</sup><br>$011_B$ : When the message stored to receive FIFO buffer is 3/8 full. <sup>*2</sup><br>$011_B$ : When the message stored to receive FIFO buffer is 4/8 full.<br>$100_B$ : When the message stored to receive FIFO buffer is 5/8 full. <sup>*2</sup><br>$101_B$ : When the message stored to receive FIFO buffer is 6/8 full.<br>$110_B$ : When the message stored to receive FIFO buffer is 7/8 full. <sup>*2</sup><br>$111_B$ : When the message stored to receive FIFO buffer is 7/8 full. <sup>*2</sup> |

|                               | 1                                 | Receive complete interrupt of transmit/receive FIFO is occurred when a message reception is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Transmit Mada                 | 0                                 | Receive complete interrupt of transmit/receive FIFO is occurred when buffer becomes empty by completed message transmit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Transmit Mode                 | 1                                 | Receive complete interrupt of transmit/receive FIFO is occurred when a message transmit is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 6-1 Transmit/Receive FIFO Buffer interrupt source

If you do not use transmit/receive FIFO buffer, set 0 message (CFDC[2:0] bit of CFCCLk register is "B'000") to buffer number of transmit/receive FIFO buffer. 2. Do not set if you set 4 messages (RFDC[2:0] bit is "B'001") to buffer number of transmit/receive

FIFO buffer.

Transmit/Receive FIFO transmit complete interrupt becomes occurrence source of CANm transmit interrupt. The

occurrence sources of CANm transmit interrupt are shown below.

CANm transmit complete interrupt

CANm transmit abort interrupt

CANm transmit/receive FIFO transmit comlete interrupt

CANm transmit qeue interrupt

CANm transmit history interrupt

#### 6.3.3 Transmit/Receive FIFO Mode Setting

Set transmit/receive FIFO buffer mod. It is possible to select receive mode or transmit mode.

Receive modeOperate as receive FIFO.Transmit mode

Operate as transmit FIFO.

#### 6.3.4 Interval Timer Counter Setting

Set counter source of interval timer counter and transmission interval. The interval timer counter is effective in transmit mode and gateway mode<sup>\*</sup>.