# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# R8C/35C Group

# A/D Converter (Single Sweep Mode Using DTC)

### 1. Abstract

This document describes the setting method and an application example of the A/D converter in single sweep mode and data transfer controller (DTC) in normal mode.

### 2. Introduction

The application example described in this document applies to the following MCU and parameters.

• MCU : R8C/35C Group

• VCC/AVCC, VREF : 5 V

•  $\phi$  AD : 20 MHz (f1)

This application note can be used with other R8C Family MCUs which have the same special function registers (SFRs) as the R8C/35C Group. Check the manual for any modifications to functions. Careful evaluation is recommended before using the program described in this application note.

# 3. Application Example

# 3.1 Program Outline

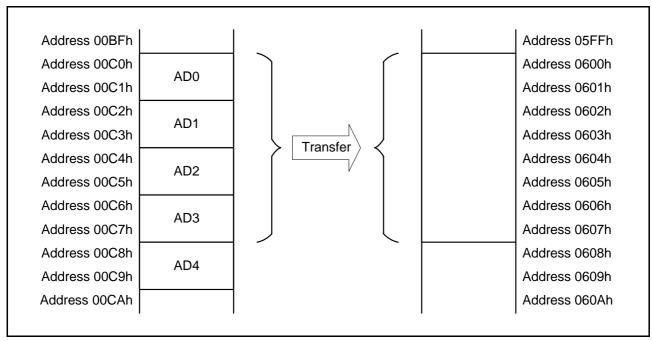

In this sample program, DTC is activated by an A/D conversion interrupt and transfers the A/D conversion result stored in the registers (AD0 register (addresses 00C0h - 00C1h) to AD3 register (addresses 00C6h - 00C7h)) to the on-chip memory (addresses 0600h - 0607h).

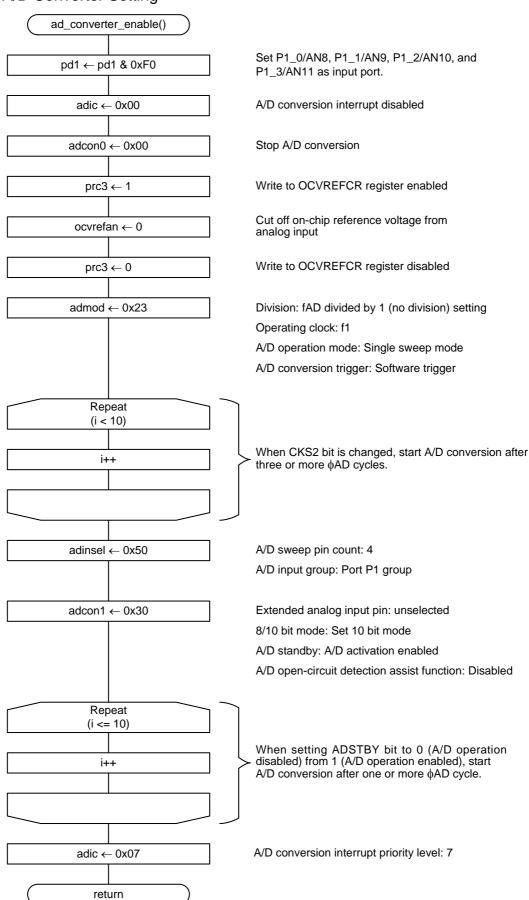

Table 3.1 lists the settings for the A/D converter, and Table 3.2 lists the settings for the DTC. Figure 3.1 shows the contents of the data transfer.

Table 3.1 A/D Converter Settings

| Function                                   | Setting                                                |

|--------------------------------------------|--------------------------------------------------------|

| Operating clock   AD                       | fAD (= f1) divided by 1 (no division)                  |

| Operating mode                             | Single sweep mode                                      |

| A/D conversion start condition             | Software trigger                                       |

| Resolution                                 | 10 bits                                                |

| A/D sweep pin count                        | 4                                                      |

| Analog input pin                           | AN8 to AN11 (AD0 register to AD3 register)             |

| On-chip reference voltage to analog input  | On-chip reference voltage and analog input are cut off |

| A/D open-circuit detection assist function | Disabled                                               |

| Extended analog input pin                  | Not selected                                           |

# Table 3.2 DTC Settings

| Function                                                   | Setting                                 |

|------------------------------------------------------------|-----------------------------------------|

| DTC activation source                                      | A/D conversion interrupt                |

| Control data                                               | Control data 0 (address 2C40h to 2C47h) |

| Transfer mode                                              | Normal mode                             |

| Source address control                                     | Fixed                                   |

| Destination address control                                | Fixed                                   |

| Chain transfer                                             | Disabled                                |

| Size of the data block to be transferred by one activation | 8 bytes                                 |

| Number of times of DTC data transfers                      | 1                                       |

| Transfer source address for data transfer                  | 00C0h (address in the AD0 register)     |

| Transfer destination address for data transfer             | 0600h (address in on-chip memory)       |

Figure 3.1 Data Transfer Contents

# 3.2 Advantage of Using DTC

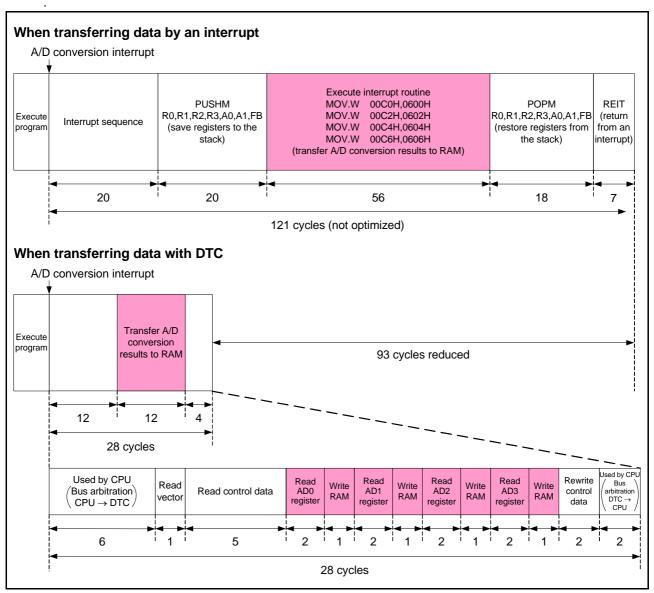

Figure 3.2 compares the numbers of execution cycles required for DTC with those required for data transfer by an interrupt process.

In this application example, while data transfer by an interrupt requires 121 cycles, DTC requires only 28 cycles–about 76.9 percent shorter than an interrupt.

Figure 3.2 Numbers of Data Transfer Cycles

# 3.3 Pins and Memory

#### 3.3.1 Pins

#### Table 3.3 Pins and Their Functions

| Pin Name  | I/O   | Function              |

|-----------|-------|-----------------------|

| P1_0/AN8  | Input | AN8 analog input pin  |

| P1_1/AN9  | Input | AN9 analog input pin  |

| P1_2/AN10 | Input | AN10 analog input pin |

| P1_3/AN11 | Input | AN11 analog input pin |

# 3.3.2 Memory

## Table 3.4 Memory

| Memory                  | Size      | Remarks                                                                                                              |

|-------------------------|-----------|----------------------------------------------------------------------------------------------------------------------|

| ROM                     | 271 bytes | In the rej05b1337_src.c module                                                                                       |

| RAM                     | 16 bytes  | In the rej05b1337_src.c module                                                                                       |

| Maximum user stack      | 9 bytes   | main function: 3 bytes mcu_init function: 6 bytes ad_converter_enable function: 6 bytes dtc_enable function: 3 bytes |

| Maximum interrupt stack | 18 bytes  | ad_converter_int function: 18 bytes                                                                                  |

Memory size varies depending on the C compiler version and compile options. The above applies to the following conditions:

C compiler: M16C/60, 30, 20, 10, and Tiny and R8C/Tiny Series Compiler V.5.45 Release 00

Compile option: -c -finfo  $(see\ Note)$  -dir "(CONFIGDIR)" -R8C Note: -c -finfo cannot be used for the R8C/Tiny-only Free-version.

### 4. Setup

This section shows the initial setting procedures and values to set the example described in 3. Application Example. Refer to the R8C/35C Group Hardware Manual for details on individual registers.

## 4.1 Setting System Clock

(1) Enable writing to registers CM0, CM1, CM3, OCD, FRA0, FRA1, FRA2, and FRA3.

#### Protect Register (PRCR)

Address 000Ah

| Bit           | b7 | b6 | b5 | b4 | b3   | b2   | b1   | b0   |

|---------------|----|----|----|----|------|------|------|------|

| Symbol        | _  | _  | _  | _  | PRC3 | PRC2 | PRC1 | PRC0 |

| Setting Value | _  | _  | _  | _  |      | _    | _    | 1    |

| Bit | Symbol | Bit Name      | Function                                                                                       | R/W |

|-----|--------|---------------|------------------------------------------------------------------------------------------------|-----|

| b0  | PRC0   | Protect bit 0 | Enables writing to registers CM0, CM1, CM3, OCD, FRA0, FRA1, FRA2, and FRA3.  1: Write enabled | R/W |

(2) Start the low-speed on-chip oscillator (OCO).

### System Clock Control Register 1 (CM1)

Address 0007h

| Bit           | b7   | b6   | b5 | b4   | b3   | b2   | b1   | b0   |   |

|---------------|------|------|----|------|------|------|------|------|---|

| Symbol        | CM17 | CM16 | _  | CM14 | CM13 | CM12 | CM11 | CM10 |   |

| Setting Value | _    | _    | _  | 0    | _    | _    | _    |      | • |

| Ĺ | Bit | Symbol | Bit Name                                     | Function                           | R/W |

|---|-----|--------|----------------------------------------------|------------------------------------|-----|

|   | b4  | CM14   | Low-speed on-chip oscillator stop bit (1, 2) | 0: Low-speed on-chip oscillator on | R/W |

#### Notes:

- 1. When the OCD2 bit is set to 0 (XIN clock selected), the CM14 bit can be set to 1 (low-speed on-chip oscillator off). When the OCD2 bit is set to 1 (on-chip oscillator clock selected), the CM14 bit is set to 0 (low-speed on-chip oscillator on). It remains unchanged even if 1 is written to it.

- 2. To use the voltage monitor 1 interrupt or voltage monitor 2 interrupt (when the digital filter is used), set the CM14 bit to 0 (low-speed on-chip oscillator on).

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the CM1 register.

(3) Set the divide ratio of the high-speed OCO.

# High-Speed On-Chip Oscillator Control Register 2 (FRA2)

Address 0025h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2    | b1    | b0    |

|---------------|----|----|----|----|----|-------|-------|-------|

| Symbol        | _  | _  | _  | _  | _  | FRA22 | FRA21 | FRA20 |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0     | 0     | 0     |

| Bit | Symbol | Bit Name      | Function                                                                              | R/W |  |

|-----|--------|---------------|---------------------------------------------------------------------------------------|-----|--|

| b0  | FRA20  |               | Division selection                                                                    | R/W |  |

| b1  | FRA21  | switching bit | These bits select the division ratio for the high-<br>speed on-chip oscillator clock. | R/W |  |

| b2  | FRA22  | switching bit | b2 b1 b0<br>0 0 0: Divide-by-2 mode                                                   |     |  |

| b3  | _      |               |                                                                                       |     |  |

| b4  | _      |               |                                                                                       |     |  |

| b5  | _      | Reserved bits | Set to 0.                                                                             | R/W |  |

| b6  | _      |               |                                                                                       |     |  |

| b7  | _      |               |                                                                                       |     |  |

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the FRA2 register.

# (4) Start the high-speed OCO.

High-Speed On-Chip Oscillator Control Register 0 (FRA0)

Address 0023h

| Bit           | b7 | b6 | b5 | b4 | b3    | b2 | b1    | b0    |

|---------------|----|----|----|----|-------|----|-------|-------|

| Symbol        | _  | _  | _  | _  | FRA03 | _  | FRA01 | FRA00 |

| Setting Value | _  | _  |    |    |       |    |       | 1     |

| Bit | Symbol | Bit Name                                 | Function                            | R/W |

|-----|--------|------------------------------------------|-------------------------------------|-----|

| b0  | FRA00  | High-speed on-chip oscillator enable bit | 1: High-speed on-chip oscillator on | R/W |

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the FRA0 register.

(5) Wait until oscillation stabilizes.

(6) Select the high-speed OCO.

#### High-Speed On-Chip Oscillator Control Register 0 (FRA0)

Address 0023h

| Bit           | b7 | b6 | b5 | b4 | b3    | b2 | b1    | b0    |   |

|---------------|----|----|----|----|-------|----|-------|-------|---|

| Symbol        | _  | _  | _  | _  | FRA03 | _  | FRA01 | FRA00 | Ì |

| Setting Value | _  | _  | _  | _  | _     | _  | 1     | _     |   |

| Bit | Symbol | Bit Name                                     | Function                                  | R/W |

|-----|--------|----------------------------------------------|-------------------------------------------|-----|

| b1  | FRA01  | High-speed on-chip oscillator select bit (1) | 1: High-speed on-chip oscillator selected | R/W |

#### Note:

- 1. Change the FRA01 bit in the following conditions.

- FRA00 = 1 (high-speed on-chip oscillator on)

- The CM14 bit in the CM1 register = 0 (low-speed on-chip oscillator on)

- Bits FRA22 to FRA20 in the FRA2 register:

All division mode can be set when VCC = 3.0 V to 5.5 V 000b to 111b

Divide ratio of 4 or more when VCC = 2.7 V to 5.5 V 010b to 111b (divide-by-4 or more) Divide ratio of 8 or more when VCC = 2.2 V to 5.5 V 110b to 111b (divide-by-8 or more)

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the FRA0 register.

(7) Set the system clock division select bit 1.

System Clock Control Register 1 (CM1)

Address 0007h

| Bit           | b7   | b6   | b5 | b4   | b3   | b2   | b1   | b0   |

|---------------|------|------|----|------|------|------|------|------|

| Symbol        | CM17 | CM16 | _  | CM14 | CM13 | CM12 | CM11 | CM10 |

| Setting Value | 0    | 0    | _  | _    | _    | _    | _    |      |

| Bit | Symbol | Bit Name                               | Function              | R/W |

|-----|--------|----------------------------------------|-----------------------|-----|

| b6  | CM16   | System clock division select bit 1 (1) | b7 b6                 | R/W |

| b7  | CM17   | System clock division select bit 1 V   | 0 0: No division mode | R/W |

#### Note:

1. When the CM06 bit is set to 0 (bits CM16 and CM17 enabled), bits CM16 and CM17 are enabled.

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the CM1 register.

(8) Set the system clock division select bit 0.

# System Clock Control Register 0 (CM0)

Address 0006h

| Bit           | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0 |

|---------------|------|------|------|------|------|------|------|----|

| Symbol        | CM07 | CM06 | CM05 | CM04 | CM03 | CM02 | CM01 | _  |

| Setting Value | _    | 0    | _    | _    | _    | _    | _    | _  |

| Bit | Symbol | Bit Name                            | Function                                      | R/W |

|-----|--------|-------------------------------------|-----------------------------------------------|-----|

| b6  | CM06   | CPU clock division select bit 0 (1) | 0: Bits CM16 and CM17 in CM1 register enabled | R/W |

#### Note:

1. When the MCU enters stop mode, the CM06 bit is set to 1 (divide-by-8 mode).

Set the PRC0 bit in the PRCR register to 1 (write enabled) before rewriting the CM0 register.

(9) Disable writing to registers CM0, CM1, CM3, OCD, FRA0, FRA1, FRA2, and FRA3.

# Protect Register (PRCR)

Address 000Ah

| Bit           | b7 | b6 | b5 | b4 | b3   | b2   | b1   | b0   |  |

|---------------|----|----|----|----|------|------|------|------|--|

| Symbol        | _  | _  | _  | _  | PRC3 | PRC2 | PRC1 | PRC0 |  |

| Setting Value | _  | _  | _  | _  | _    | _    | _    | 0    |  |

| Bit | Symbol | Bit Name      | Function                                                                                        | R/W |

|-----|--------|---------------|-------------------------------------------------------------------------------------------------|-----|

| b0  | PRC0   | Protect bit 0 | Enables writing to registers CM0, CM1, CM3, OCD, FRA0, FRA1, FRA2, and FRA3.  0: Write Disabled | R/W |

# 4.2 Setting A/D Converter (Single Sweep Mode)

(1) Set P1\_0 (AN8), P1\_1 (AN9), P1\_2 (AN10), and P1\_3 (AN11) as input ports.

### Port P1 Direction Register (PD1)

Address 00E3h

| Bit           | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Symbol        | PD1_7 | PD1_6 | PD1_5 | PD1_4 | PD1_3 | PD1_2 | PD1_1 | PD1_0 |  |

| Setting Value | _     | _     | _     | _     | 0     | 0     | 0     | 0     |  |

| Bit | Symbol | Bit Name                | Function                                    | R/W |  |  |

|-----|--------|-------------------------|---------------------------------------------|-----|--|--|

| b0  | PD1_0  | Port P1_0 direction bit |                                             | R/W |  |  |

| b1  | PD1_1  | Port P1_1 direction bit | 0: Input mode (functions as an input port)  | R/W |  |  |

| b2  | PD1_2  | Port P1_2 direction bit | o. Input mode (functions as all input port) |     |  |  |

| b3  | PD1_3  | Port P1_3 direction bit |                                             | R/W |  |  |

The PD1 register selects whether I/O ports are used for input or output. Each bit in the PD1 register corresponds to one port.

#### (2) Disable A/D conversion interrupt.

### Interrupt Control Register (ADIC)

Address 004Eh

| Bit           | b7 | b6 | b5 | b4 | b3 | b2    | b1    | b0    |  |

|---------------|----|----|----|----|----|-------|-------|-------|--|

| Symbol        | _  | _  | _  | _  | IR | ILVL2 | ILVL1 | ILVL0 |  |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0     | 0     | 0     |  |

| Bit | Symbol | Bit Name                                 | Function                                          | R/W        |  |  |  |

|-----|--------|------------------------------------------|---------------------------------------------------|------------|--|--|--|

| b0  | ILVL0  |                                          |                                                   | R/W        |  |  |  |

| b1  | ILVL1  | Interrupt priority level select bit      | b2 b1 b0<br>  0 0 0: Level 0 (interrupt disabled) | R/W        |  |  |  |

| b2  | ILVL2  |                                          |                                                   | R/W        |  |  |  |

| b3  | IR     | Interrupt request bit                    | 0: No interrupt requested                         | R/W<br>(1) |  |  |  |

| b4  | _      |                                          |                                                   |            |  |  |  |

| b5  | _      | Nothing is assigned. If necessary, set t | o 0.                                              | _          |  |  |  |

| b6  | _      | When read, the content is undefined.     |                                                   |            |  |  |  |

| b7  |        |                                          |                                                   |            |  |  |  |

#### Note:

1. Only 0 can be written to the IR bit. Do not write 1 to this bit.

Rewrite the interrupt control register when an interrupt request corresponding to the register is not generated.

(3) Stop A/D conversion.

# A/D Control Register 0 (ADCON0)

Address 00D6h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0   |

|---------------|----|----|----|----|----|----|----|------|

| Symbol        | _  | _  | _  | _  | _  | _  | _  | ADST |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    |

| Bit | Symbol | Bit Name                               | Function                           | R/W |  |  |  |  |

|-----|--------|----------------------------------------|------------------------------------|-----|--|--|--|--|

| b0  | ADST   | A/D conversion start flag              | 0: Stop A/D conversion             | R/W |  |  |  |  |

| b1  | _      |                                        |                                    |     |  |  |  |  |

| b2  | _      |                                        |                                    |     |  |  |  |  |

| b3  | _      |                                        |                                    |     |  |  |  |  |

| b4  | _      | Nothing is assigned. If necessary, set | to 0. When read, the content is 0. | _   |  |  |  |  |

| b5  | _      |                                        |                                    |     |  |  |  |  |

| b6  | _      |                                        |                                    |     |  |  |  |  |

| b7  | _      |                                        |                                    |     |  |  |  |  |

ADST Bit (A/D conversion start flag)

Conditions for setting this bit to 1:

When A/D conversion starts or during A/D conversion.

Condition for setting this bit to 0:

When A/D conversion stops.

(4) Enable writing to the OCVREFCR register.

### Protect Register (PRCR)

Address 000Ah

| Bit           | b7 | b6 | b5 | b4 | b3   | b2   | b1   | b0   |

|---------------|----|----|----|----|------|------|------|------|

| Symbol        |    | _  | _  | _  | PRC3 | PRC2 | PRC1 | PRC0 |

| Setting Value | _  | _  | _  | _  | 1    | _    | _    | _    |

| Bit | Symbol | Bit Name      | Function                                                                                    | R/W |

|-----|--------|---------------|---------------------------------------------------------------------------------------------|-----|

| b3  | PRC3   | Protect bit 3 | Enables writing to registers OCVREFCR, VCA2, VD1LS, VW0C, VW1C, and VW2C.  1: Write enabled | R/W |

(5) Cut off on-chip reference voltage from the analog input.

### On-Chip Reference Voltage Control Register (OCVREFCR)

Address 0026h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0       |

|---------------|----|----|----|----|----|----|----|----------|

| Symbol        | _  | _  | _  | _  | _  | _  | _  | OCVREFAN |

| Setting Value | _  | _  | _  | _  | _  | _  | _  | 0        |

| Bit | Symbol                     | Bit Name                                | Function                                                  | R/W   |

|-----|----------------------------|-----------------------------------------|-----------------------------------------------------------|-------|

| b0  |                            | On-chip reference voltage to            | 0: On-chip reference voltage and analog input are cut off | R/W   |

|     | 30 I ( )( )( )( )EE ( )( ) | analog input connect bit <sup>(1)</sup> | o. On one relevence voltage and analog input are out on   | 10,00 |

#### Note:

1. When on-chip reference voltage is used as analog input, first set the ADEX0 bit in the ADCON1 register to 1 (on-chip reference voltage selected) and then set the OCVREFAN bit to 1 (on-chip reference voltage and analog input are connected).

When on-chip reference voltage is not used as analog input, first set the OCVREFAN bit to 0 (on-chip reference voltage and analog input are cut off) and then set the ADEX0 bit to 0 (extended analog input pin not selected).

Set the PRC3 bit in the PRCR register to 1 (write enabled) before rewriting the OCVREFCR register. If the contents of the OCVREFCR register are rewritten during A/D conversion, the conversion result is undefined.

(6) Disable writing to OCVREFCR register.

Protect Register (PRCR)

Address 000Ah

| Bit           | b7 | b6 | b5 | b4 | b3   | b2   | b1   | b0   |

|---------------|----|----|----|----|------|------|------|------|

| Symbol        | _  | _  | _  | _  | PRC3 | PRC2 | PRC1 | PRC0 |

| Setting Value | _  | _  | _  | _  | 0    | _    | _    |      |

| Bit | Symbol | Bit Name      | Function                                                                                     | R/W |

|-----|--------|---------------|----------------------------------------------------------------------------------------------|-----|

| b3  | PRC3   | Protect bit 3 | Enables writing to registers OCVREFCR, VCA2, VD1LS, VW0C, VW1C, and VW2C.  0: Write disabled | R/W |

(7) Set the A/D mode register.

# A/D Mode Register (ADMOD)

Address 00D4h

| Bit           | b7     | b6     | b5  | b4  | b3  | b2   | b1   | b0   |  |

|---------------|--------|--------|-----|-----|-----|------|------|------|--|

| Symbol        | ADCAP1 | ADCAP0 | MD2 | MD1 | MD0 | CKS2 | CKS1 | CKS0 |  |

| Setting Value | 0      | 0      | 1   | 0   | 0   | 0    | 1    | 1    |  |

| Bit | Symbol | Bit Name                           | Function                                                            | R/W |  |  |

|-----|--------|------------------------------------|---------------------------------------------------------------------|-----|--|--|

| b0  | CKS0   | Division select bit                | b1 b0                                                               | R/W |  |  |

| b1  | CKS1   | DIVISION SEIECE DIE                | 1 1: fAD divided by 1 (no division)                                 |     |  |  |

| b2  | CKS2   | Clock source select bit (1)        | 0: Select f1                                                        | R/W |  |  |

| b3  | MD0    |                                    |                                                                     | R/W |  |  |

| b4  | MD1    | A/D operating mode select bit      | b5 b4 b3<br>1 0 0: Single sweep mode                                |     |  |  |

| b5  | MD2    |                                    |                                                                     |     |  |  |

| b6  | ADCAP0 | A/D conversion trigger select bit  | b7 b6<br>0 0: A/D conversion start by software trigger (ADST bit in | R/W |  |  |

| b7  | ADCAP1 | TAY D CONVENSION INGGER SELECT DIT | the ADCON0 register)                                                |     |  |  |

#### Note:

1. When the CKS2 bit is changed, wait for 3  $\phi$ AD cycles or more before starting A/D conversion.

If the ADMOD register is rewritten during A/D conversion, the conversion result is undefined.

(8) Wait for three or more  $\phi AD$  cycles.

(9) Set the A/D input select register.

# A/D Input Select Register (ADINSEL)

Address 00D5h

| Bit           | b7      | b6      | b5    | b4    | b3 | b2  | b1  | b0  |

|---------------|---------|---------|-------|-------|----|-----|-----|-----|

| Symbol        | ADGSEL1 | ADGSEL0 | SCAN1 | SCAN0 | _  | CH2 | CH1 | CH0 |

| Setting Value | 0       | 1       | 0     | 1     | 0  | 0   | 0   | 0   |

| Bit | Symbol  | Bit Name                        | Function                                      | R/W |  |

|-----|---------|---------------------------------|-----------------------------------------------|-----|--|

| b0  | CH0     |                                 |                                               | R/W |  |

| b1  | CH1     | Analog input pin select bits    | Refer to Table 4.1 Analog Input Pin Selection | R/W |  |

| b2  | CH2     |                                 |                                               | R/W |  |

| b3  | _       | Reserved bit                    | Set to 0.                                     | R/W |  |

| b4  | SCAN0   | A/D sweep pin count select bits | b5 b4                                         | R/W |  |

| b5  | SCAN1   | A/D sweep pin count select bits | 0 1: 4 pins                                   | R/W |  |

| b6  | ADGSEL0 | A/D input group select bits     | b7 b6                                         | R/W |  |

| b7  | ADGSEL1 | TOUP Select bits                | 0 1: Port P1 group selected                   |     |  |

If the ADINSEL register is rewritten during A/D conversion, the conversion result is undefined.

Table 4.1 Analog Input Pin Selection

| Bits CH2 to CH0 | Bits ADGSEL1, ADGSEL0 = 00b | Bits ADGSEL1, ADGSEL0 = 01b |

|-----------------|-----------------------------|-----------------------------|

| 000b            | AN0                         | AN8                         |

| 001b            | AN1                         | AN9                         |

| 010b            | AN2                         | AN10                        |

| 011b            | AN3                         | AN11                        |

| 100b            | AN4                         |                             |

| 101b            | AN5                         | Do not set.                 |

| 110b            | AN6                         | Do not set.                 |

| 111b            | AN7                         |                             |

(10) Set A/D control register 1.

### A/D Control Register 1 (ADCON1)

Address 00D7h

| Bit           | b7      | b6      | b5     | b4   | b3 | b2 | b1 | b0    |

|---------------|---------|---------|--------|------|----|----|----|-------|

| Symbol        | ADDDAEL | ADDDAEN | ADSTBY | BITS |    |    | _  | ADEX0 |

| Setting Value | 0       | 0       | 1      | 1    | 0  | 0  | 0  | 0     |

| Bit | Symbol  | Bit Name                                                             | Function                                  | R/W |  |  |

|-----|---------|----------------------------------------------------------------------|-------------------------------------------|-----|--|--|

| b0  | ADEX0   | Extended analog input pin select bit (1)                             | 0: Extended analog input pin not selected | R/W |  |  |

| b1  | _       |                                                                      |                                           |     |  |  |

| b2  | _       | Reserved bits                                                        | Set to 0.                                 | R/W |  |  |

| b3  | _       |                                                                      |                                           |     |  |  |

| b4  | BITS    | 8/10-bit mode select bit                                             | 1: 10-bit mode                            | R/W |  |  |

| b5  | ADSTBY  | A/D standby bit (2)                                                  | 1: A/D operation enabled                  | R/W |  |  |

| b6  |         | A/D open-circuit detection assist function enable bit <sup>(3)</sup> | 0: Disabled                               | R/W |  |  |

| b7  | ADDDAEL | A/D open-circuit detection assist method select bit <sup>(3)</sup>   | 0: Discharge before conversion            | R/W |  |  |

#### Notes:

- 1. When on-chip reference voltage is used as analog input, first set the ADEX0 bit to 1 (on-chip reference voltage selected) and then set the OCVREFAN bit in the OCVREFCR register to 1 (on-chip reference voltage and analog input are connected).

- When on-chip reference voltage is not used as analog input, first set the OCVREFAN bit to 0 (on-chip reference voltage and analog input are cut off) and then set the ADEX0 bit to 0 (extended analog input pin not selected).

- 2. When the ADSTBY bit is changed from 0 (A/D operation stops) to 1 (A/D operation enabled), wait for 1 φAD cycle or more before starting A/D conversion.

- 3. To enable the A/D open-circuit detection assist function, select the conversion start state with the ADDDAEL bit after setting the ADDDAEN bit to 1 (enabled).

- The conversion result with an open circuit varies with external circuits. Careful evaluation should be performed according to the system before using this function.

If the ADCON1 register is rewritten during A/D conversion, the conversion result is undefined.

(11) Wait one or more  $\phi AD$  cycles.

(12) Set the A/D conversion interrupt priority level.

# Interrupt Control Register (ADIC)

Address 004Eh

| Bit           | b7 | b6 | b5 | b4 | b3 | b2    | b1    | b0    |

|---------------|----|----|----|----|----|-------|-------|-------|

| Symbol        | _  | _  | _  | _  | IR | ILVL2 | ILVL1 | ILVL0 |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 1     | 1     | 1     |

| Bit | Symbol | Bit Name                                     | Function                     | R/W        |  |  |  |

|-----|--------|----------------------------------------------|------------------------------|------------|--|--|--|

| b0  | ILVL0  |                                              |                              | R/W        |  |  |  |

| b1  | ILVL1  | Interrupt priority level select bit          | b2 b1 b0<br>1 1 1 1: Level 7 | R/W        |  |  |  |

| b2  | ILVL2  |                                              |                              |            |  |  |  |

| b3  | IR     | Interrupt request bit                        | 0: No interrupt requested    | R/W<br>(1) |  |  |  |

| b4  | _      |                                              |                              |            |  |  |  |

| b5  | _      | Nothing is assigned. If necessary, set to 0. |                              |            |  |  |  |

| b6  | _      | When read, the content is undefined.         |                              |            |  |  |  |

| b7  | _      |                                              |                              |            |  |  |  |

#### Note:

1. Only 0 can be written to the IR bit. Do not write 1 to this bit.

Rewrite the interrupt control register when an interrupt request corresponding to the register is not generated.

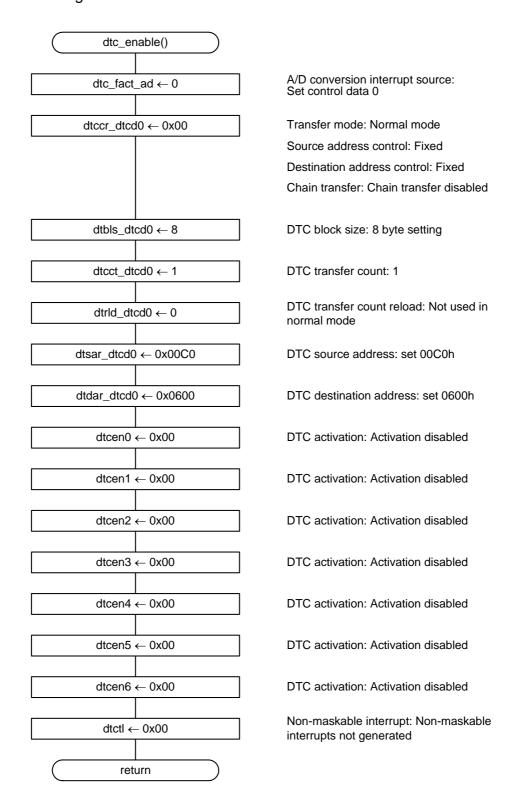

# 4.3 Setting DTC (Normal Mode)

(1) Set the DTC control data number in the DTC vector address (address 2C09h) which is assigned to the A/D conversion interrupt. In this program, set 0 to address 2C09h to use control data 0.

### DTC Vector Address for A/D Conversion Interrupt

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |   |

|---------------|----|----|----|----|----|----|----|----|---|

| Symbol        | _  | _  | _  | _  | _  | _  | _  | _  | 1 |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | - |

| Bit     | Function                                                                                    | Setting Range | R/W |

|---------|---------------------------------------------------------------------------------------------|---------------|-----|

| b7 - b0 | Stores the data from 00000000b to 00010111b, and selects one control data out of 24 groups. | 00h - 17h     | R/W |

(2) Set the DTC control register allocated for control data 0. Set "Normal mode" for the transfer mode, "Fixed" for the source address, "Fixed" for the destination address, and "Disabled" for the chain transfer.

### DTC Control Register (DTCCR)

#### Address 2C40h

| Bit           | b7 | b6 | b5     | b4   | b3    | b2    | b1     | b0   |

|---------------|----|----|--------|------|-------|-------|--------|------|

| Symbol        | _  | _  | RPTINT | CHNE | DAMOD | SAMOD | RPTSEL | MODE |

| Setting Value | 0  | 0  | _      | 0    | 0     | 0     | _      | 0    |

| Bit | Symbol | Bit Name                             | Function                    | R/W   |

|-----|--------|--------------------------------------|-----------------------------|-------|

| b0  | MODE   | Transfer mode select bit             | 0: Normal mode              | R/W   |

| b1  | RPTSEL | Repeat area select bit (1)           |                             | R/W   |

| b2  | SAMOD  | Source address control bit (2)       | 0: Fixed                    | R/W   |

| b3  | DAMOD  | Destination address control bit (2)  | 0: Fixed                    | R/W   |

| b4  | CHNE   | Chain transfer enable bit            | 0: Chain transfers disabled | R/W   |

| b5  | RPTINT | Repeat mode interrupt enable bit (1) |                             | R/W   |

| b6  | _      | Reserved bits                        | Set to 0.                   | R/W   |

| b7  |        | 110001100 510                        | 001.10 0.                   | 10,00 |

#### Notes:

- 1. This bit is valid when the MODE bit is 1 (repeat mode).

- 2. Settings of bits SAMOD and DAMOD are invalid for the repeat area.

(3) Set the DTC block size register allocated for control data 0. In this program, set 8 in this register to transfer 8-byte data once.

#### DTC Block Size Register (DTBLS)

#### Address 2C41h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |   |

|---------------|----|----|----|----|----|----|----|----|---|

| Symbol        | _  | _  | _  | _  | _  | _  | _  | _  | l |

| Setting Value | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |   |

|    | Bit   | Function                                                                           | Setting Range             | R/W |

|----|-------|------------------------------------------------------------------------------------|---------------------------|-----|

| b7 | to b0 | These bits specify the size of the data block to be transferred by one activation. | 00h to FFh <sup>(1)</sup> | R/W |

#### Note:

1. When the DTBLS register is set to 00h, the block size is 256 bytes.

(4) Set the DTC transfer count register allocated for control data 0. In this program, set 1 in this register to transfer 8-byte data once.

### DTC Transfer Count Register (DTCCT)

#### Address 2C42h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |   |

|---------------|----|----|----|----|----|----|----|----|---|

| Symbol        | _  | _  | _  | _  | _  | _  | _  | _  | 1 |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | • |

| Bit      | Function                                                      | Setting Range             | R/W |

|----------|---------------------------------------------------------------|---------------------------|-----|

| b7 to b0 | These bits specify the number of times of DTC data transfers. | 00h to FFh <sup>(1)</sup> | R/W |

#### Note:

1. When the DTCCT register is set to 00h, the number of transfer times is 256. Each time the DTC is activated, the DTCCT register is decremented by 1.

(5) Set the DTC transfer count reload register allocated for control data 0. As normal mode does not use this register, set 0.

### DTC Transfer Count Reload Register (DTRLD)

#### Address 2C43h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---------------|----|----|----|----|----|----|----|----|

| Symbol        | _  | _  | _  | _  | _  | _  | _  | _  |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit      | Function                                                              | Setting Range             | R/W |

|----------|-----------------------------------------------------------------------|---------------------------|-----|

| b7 to b0 | This register value is reloaded to the DTCCT register in repeat mode. | 00h to FFh <sup>(1)</sup> | R/W |

#### Note:

1. Set the initial value for the DTCCT register.

(6) Set the DTC source address register allocated for control data 0. In this program, set the source address 00C0h.

# DTC Source Address Register (DTSAR)

| Address :     | 2C44h |     |     |     |     |     |    |    |

|---------------|-------|-----|-----|-----|-----|-----|----|----|

| Bit           | b7    | b6  | b5  | b4  | b3  | b2  | b1 | b0 |

| Symbol        |       | 1   | 1   | _   | _   | 1   | 1  | _  |

| Setting Value | 1     | 1   | 0   | 0   | 0   | 0   | 0  | 0  |

| Bit           | b15   | b14 | b13 | b12 | b11 | b10 | b9 | b8 |

| Symbol        | _     | _   | _   | _   | _   | _   | _  | _  |

| Setting Value | 0     | 0   | 0   | 0   | 0   | 0   | 0  | 0  |

| Bit       | Function                                                        | Setting Range  | R/W |

|-----------|-----------------------------------------------------------------|----------------|-----|

| b15 to b0 | These bits specify a transfer source address for data transfer. | 0000h to FFFFh | R/W |

(7) Set the DTC destination register allocated for control data 0. In this program, set the destination address 0600h.

# DTC Destination Register (DTDAR)

#### Address 2C46h

| Bit           | b7  | b6  | b5  | b4  | b3  | b2  | b1 | b0 |

|---------------|-----|-----|-----|-----|-----|-----|----|----|

| Symbol        | _   | _   | _   | _   | _   | _   | _  | _  |

| Setting Value | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  |

| Bit           | b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8 |

| Symbol        | _   | _   | _   | _   | _   | _   | _  | _  |

| Setting Value | 0   | 0   | 0   | 0   | 0   | 1   | 1  | 0  |

| Bit       | Function                                                             | Setting Range  | R/W |

|-----------|----------------------------------------------------------------------|----------------|-----|

| b15 to b0 | These bits specify a transfer destination address for data transfer. | 0000h to FFFFh | R/W |

(8) Set the DTC activation enable registers. Set all DTC activation source to "Activation disabled".

#### DTC Activation Enable Registers (DTCENi) (i = 0 to 6)

${\sf Address} \begin{array}{l} {\sf 0088h~(DTCEN0),~0089h~(DTCEN1),~008Ah~(DTCEN2),~008Bh~(DTCEN3),~008Ch~(DTCEN4),} \\ {\sf 008Dh~(DTCEN5),~008Eh~(DTCEN6)} \end{array}$

| Bit           | b7      | b6      | b5      | b4      | b3      | b2      | b1      | b0      |

|---------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Symbol        | DTCENi7 | DTCENi6 | DTCENi5 | DTCENi4 | DTCENi3 | DTCENi2 | DTCENi1 | DTCENi0 |

| Setting Value | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Bit | Symbol  | Bit Name                   | Function               | R/W |  |

|-----|---------|----------------------------|------------------------|-----|--|

| b0  | DTCENi0 |                            |                        | R/W |  |

| b1  | DTCENi1 |                            |                        | R/W |  |

| b2  | DTCENi2 |                            |                        | R/W |  |

| b3  | DTCENi3 |                            | 0: Activation disabled | R/W |  |

| b4  | DTCENi4 | DTC activation enable bits | 1: Activation enabled  | R/W |  |

| b5  | DTCENi5 |                            |                        | R/W |  |

| b6  | DTCENi6 |                            |                        |     |  |

| b7  | DTCENi7 |                            |                        | R/W |  |

i = 0 to 6

The DTCENi register enables/disables DTC activation using by interrupt sources. Table 4.2 shows the correspondences between bits DTCENi0 to DTCENi7 (i = 0 to 6) and interrupt sources.

Table 4.2 Correspondences Between Bits DTCENi0 to DTCENi7 (i = 0 to 6) and Interrupt Sources

| Register | DTCENi7 Bit                                            | DTCENi6 Bit                                            | DTCENi5 Bit                                            | DTCENi4 Bit                                            | DTCENi3 Bit                                            | DTCENi2 Bit                                            | DTCENi1 Bit                                            | DTCENi0 Bit                                            |

|----------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| DTCEN0   | INT0                                                   | INT1                                                   | INT2                                                   | INT3                                                   | INT4                                                   | 1                                                      |                                                        |                                                        |

| DTCEN1   | Key input                                              | A/D<br>conversion                                      | UART0 reception                                        | UART0<br>transmission                                  | UART1 reception                                        | UART1<br>transmission                                  | UART2 reception                                        | UART2<br>transmission                                  |

| DTCEN2   | SSU/I <sup>2</sup> C bus<br>receive data<br>full       | SSU/I <sup>2</sup> C bus<br>transmit data<br>empty     | Voltage<br>Monitor 2/<br>Comparator<br>A2              | Voltage<br>Monitor 1/<br>Comparator<br>A1              | I                                                      | ı                                                      | Timer RC<br>input-<br>capture/<br>compare-<br>match A  | Timer RC<br>input-<br>capture/<br>compare-<br>match B  |

| DTCEN3   | Timer RC<br>input-<br>capture/<br>compare-<br>match C  | Timer RC<br>input-<br>capture/<br>compare-<br>match D  | Timer RD0<br>input-<br>capture/<br>compare-<br>match A | Timer RD0<br>input-<br>capture/<br>compare-<br>match B | Timer RD0<br>input-<br>capture/<br>compare-<br>match C | Timer RD0<br>input-<br>capture/<br>compare-<br>match D | Timer RD1<br>input-<br>capture/<br>compare-<br>match A | Timer RD1<br>input-<br>capture/<br>compare-<br>match B |

| DTCEN4   | Timer RD1<br>input-<br>capture/<br>compare-<br>match C | Timer RD1<br>input-<br>capture/<br>compare-<br>match D | _                                                      | _                                                      | _                                                      | _                                                      | _                                                      | _                                                      |

| DTCEN5   | _                                                      | _                                                      | Timer RE                                               | _                                                      |                                                        |                                                        |                                                        |                                                        |

| DTCEN6   | _                                                      | Timer RA                                               | _                                                      | Timer RB                                               | Flash<br>memory<br>ready status                        | _                                                      | _                                                      | _                                                      |

(9) Set the DTC activation control register. Disable DTC activation when a non-maskable interrupt (an interrupt by the watchdog timer, oscillation stop detection, voltage monitor 1, or voltage monitor 2) is generated.

#### DTC Activation Control Register (DTCTL)

| Add | lress | 00 | 80 | )h |

|-----|-------|----|----|----|

|     |       |    |    |    |

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1   | b0 |   |

|---------------|----|----|----|----|----|----|------|----|---|

| Symbol        | _  | _  | _  | _  | _  | _  | NMIF | _  | 1 |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0  | - |

| Bit | Symbol | Bit Name                                        | Function                                                                 | R/W |  |  |

|-----|--------|-------------------------------------------------|--------------------------------------------------------------------------|-----|--|--|

| b0  | _      | Reserved bit                                    | Set to 0.                                                                | R/W |  |  |

| b1  | NMIF   | Non-maskable interrupt generation bit (1)       | 0: Non-maskable interrupts not generated                                 | R/W |  |  |

| b2  | _      |                                                 |                                                                          | _   |  |  |

| b3  | _      |                                                 |                                                                          |     |  |  |

| b4  | _      | Nothing is assigned. If necessary set to 0      | othing is assigned. If necessary set to 0. When read, the content is 0.  |     |  |  |

| b5  | _      | Two timing is assigned. If fleedssary, set to c | othing is assigned. If necessary, set to 0. When read, the content is 0. |     |  |  |

| b6  | _      |                                                 |                                                                          |     |  |  |

| b7  | _      |                                                 |                                                                          |     |  |  |

#### Note:

1. This bit is set to 0 when the read result is 1 and 0 is written to the same bit. This bit remains unchanged even if the read result is 0 and 0 is written to the same bit. This bit remains unchanged if 1 is written to it.

The DTCTL register controls DTC activation when a non-maskable interrupt (an interrupt by the watchdog timer, oscillation stop detection, voltage monitor 1, or voltage monitor 2) is generated.

#### Non-Maskable Interrupt Generation Bit (NMIF Bit)

The NMIF bit is set to 1 when a watchdog timer interrupt, an oscillation stop detection interrupt, a voltage monitor 1 interrupt, or a voltage monitor 2 interrupt is generated.

When the NMIF bit is 1, the DTC is not activated even if the interrupt which enables DTC activation is generated. If the NMIF bit becomes 1 during DTC transfer, the transfer continues until it is completed.

# 4.4 Starting A/D Conversion

- (1) Confirm that DTC activation with A/D conversion enable bit has been disabled (dtcen 16 = 0).

- (2) Set the DTC transfer count register allocated for control data 0. In this program, set 1 to transfer 8-byte data once.

### DTC Transfer Count Register (DTCCT)

Address 2C42h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |   |

|---------------|----|----|----|----|----|----|----|----|---|

| Symbol        | _  | _  | _  | _  |    | _  | _  | _  | 1 |

| Setting Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | - |

| Bit      | Function                                                      | Setting Range             | R/W |

|----------|---------------------------------------------------------------|---------------------------|-----|

| b7 to b0 | These bits specify the number of times of DTC data transfers. | 00h to FFh <sup>(1)</sup> | R/W |

#### Note:

- 1. When the DTCCT register is set to 00h, the number of transfer times is 256. Each time the DTC is activated, the DTCCT register is decremented by 1.

- (3) Use A/D conversion interrupt source to enable DTC activation.

#### DTC Activation Enable Registers (DTCEN1)

Address 0089h

| Bit           | b7      | b6      | b5      | b4      | b3      | b2      | b1      | b0      |

|---------------|---------|---------|---------|---------|---------|---------|---------|---------|

| Symbol        | DTCEN17 | DTCEN16 | DTCEN15 | DTCEN14 | DTCEN13 | DTCEN12 | DTCEN11 | DTCEN10 |

| Setting Value | _       | 1       | _       | _       | _       | _       | _       | _       |

| Bit | Symbol     | Bit Name                                                | Function              | R/W |

|-----|------------|---------------------------------------------------------|-----------------------|-----|

| b6  | 11)1(.FN16 | DTC activation with A/D conversion interrupt enable bit | 1: Activation enabled | R/W |

(4) Start A/D conversion.

### A/D Control Register 0 (ADCON0)

Address 00D6h

| Bit           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0   |

|---------------|----|----|----|----|----|----|----|------|

| Symbol        | _  | _  | _  | _  | _  | _  |    | ADST |

| Setting Value | _  | _  | _  | _  | _  | _  | _  | 1    |

| Bit | Symbol | Bit Name                  | Function                | R/W |

|-----|--------|---------------------------|-------------------------|-----|

| b0  | ADST   | A/D conversion start flag | 1: Start A/D conversion | R/W |

ADST Bit (A/D conversion start flag)

Conditions for setting to 1:

When A/D conversion starts and during A/D conversion.

Condition for setting to 0:

When A/D conversion stops.

# 5. Function Table and Flowchart

# 5.1 Function Table

| Declaration       | void mcu_init(void)                              | roid mcu_init(void) |          |  |  |  |

|-------------------|--------------------------------------------------|---------------------|----------|--|--|--|

| Outline           | System clock setting                             | ystem clock setting |          |  |  |  |

| Argument          | Argument name                                    |                     | Meaning  |  |  |  |

| Argument          | None                                             |                     | -        |  |  |  |

| Variable (global) | Variable name                                    |                     | Contents |  |  |  |

| variable (global) | None                                             |                     | -        |  |  |  |

| Returned value    | Туре                                             | Value               | Meaning  |  |  |  |

| Returned value    | None                                             | _                   | -        |  |  |  |

| Function          | Set system clock (high-speed on-chip oscillator) |                     |          |  |  |  |

| Declaration                             | void ad_converter_                    | void ad_converter_enable(void) |          |  |  |

|-----------------------------------------|---------------------------------------|--------------------------------|----------|--|--|

| Outline                                 | A/D convertor setti                   | A/D convertor setting          |          |  |  |

| A = = = = = = = = = = = = = = = = = = = | Argument name                         |                                | Meaning  |  |  |

| Argument                                | None                                  |                                | -        |  |  |

| Variable (global)                       | Variable name                         |                                | Contents |  |  |

| Variable (global)                       | None                                  |                                | -        |  |  |

| Returned value                          | Туре                                  | Value                          | Meaning  |  |  |

| Returned value                          | None                                  | _                              | -        |  |  |

| Function                                | Set A/D converter (single sweep mode) |                                |          |  |  |

| Declaration       | void dtc_enable(voi   | void dtc_enable(void) |          |  |  |  |

|-------------------|-----------------------|-----------------------|----------|--|--|--|

| Outline           | DTC setting           | DTC setting           |          |  |  |  |

| Argument          | Argument name         |                       | Meaning  |  |  |  |

| Argument          | None                  |                       | -        |  |  |  |

| Variable (global) | Variable name         |                       | Contents |  |  |  |

| Variable (global) | None                  |                       | -        |  |  |  |

| Returned value    | Туре                  | Value                 | Meaning  |  |  |  |

|                   | None                  | _                     | -        |  |  |  |

| Function          | Set DTC (normal mode) |                       |          |  |  |  |

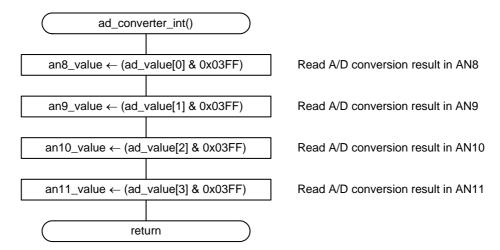

| Declaration       | void ad_converter_int(void)                                                                                                                                                                                                    |                          |           |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|--|--|

| Outline           | A/D conversion inter                                                                                                                                                                                                           | A/D conversion interrupt |           |  |  |

| Argument          | Argument name                                                                                                                                                                                                                  |                          | Meaning   |  |  |

| Argument          | None                                                                                                                                                                                                                           |                          | _         |  |  |

|                   | Variable name                                                                                                                                                                                                                  |                          | Contents  |  |  |

|                   | unsigned short ad_value[4]                                                                                                                                                                                                     |                          | Reference |  |  |

| Variable (global) | unsigned short an8_value                                                                                                                                                                                                       |                          | Setting   |  |  |

| Variable (global) | unsigned short an9_value                                                                                                                                                                                                       |                          | Setting   |  |  |

|                   | unsigned short an10_value                                                                                                                                                                                                      |                          | Setting   |  |  |

|                   | unsigned short an11_value                                                                                                                                                                                                      |                          | Setting   |  |  |

| Returned value    | Type                                                                                                                                                                                                                           | Value                    | Meaning   |  |  |

| Returned value    | None                                                                                                                                                                                                                           | _                        | _         |  |  |

| Function          | This interrupt process takes place after A/D conversion is completed. (This interrupt starts when DTC transfer is completed.) A/D conversion values in AN8 to AN11, which are transferred from DTC, are set to each parameter. |                          |           |  |  |

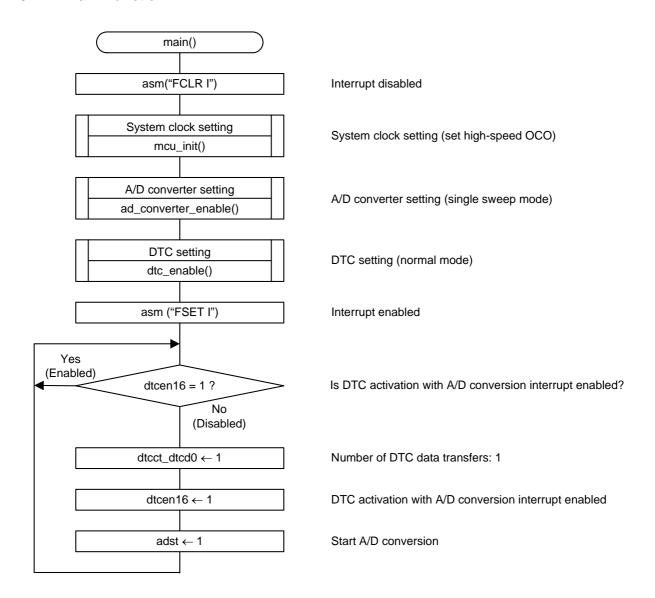

# 5.2 Flow Chart

## 5.2.1 Main Function

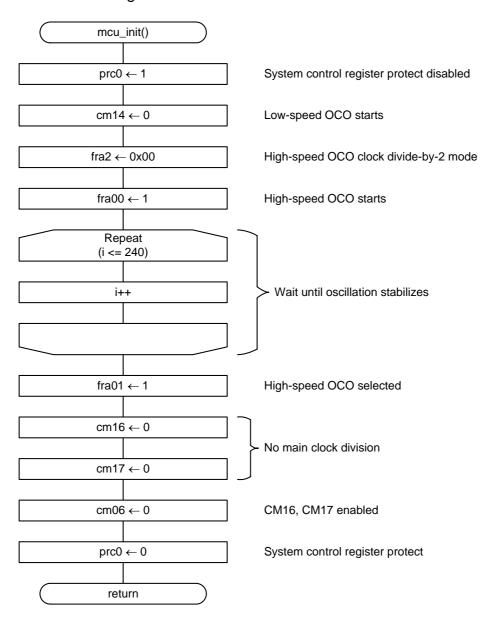

# 5.2.2 System Clock Setting Process

# 5.2.3 A/D Converter Setting

# 5.2.4 DTC Setting

# 5.2.5 A/D Conversion Interrupt

# 6. Sample Programming Code

A sample program can be downloaded from the Renesas Technology website. To download, click "Application Notes" in the left-hand side menu of the R8C/Tiny Series page.

### 7. Reference Documents

Hardware Manual

R8C/35C Group Hardware Manual Rev.0.10

The latest version can be downloaded from the Renesas Technology website.

Technical Update/Technical News

The latest information can be downloaded from the Renesas Technology website.

# Website and Support

Renesas Technology website http://www.renesas.com/

Inquiries http://www.renesas.com/inquiry csc@renesas.com

| REVISION HISTORY | R8C/35C Group                               |

|------------------|---------------------------------------------|

| REVISIONTIISTORT | A/D Converter (Single Sweep Mode Using DTC) |

| Rev. | Date         | Description |                      |

|------|--------------|-------------|----------------------|

|      |              | Page        | Summary              |

| 1.00 | Oct 26, 2009 | -           | First Edition issued |

All trademarks and registered trademarks are the property of their respective owners

Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

© 2009. Renesas Technology Corp., All rights reserved. Printed in Japan.