# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

## **POWER CONSUMPTION OPTIMIZATION IN NEC ELECTRONICS MICROCONTROLLERS**

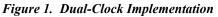

Application Note August 2003 Introduction For embedded microcontroller applications that are battery-powered, it is important to minimize power consumption to maximize battery life. In conventional microcontroller designs, this need dictates the use of a system clock with slower speed. Advanced microcontroller architectures employ low-power modes instead. NEC Electronics collectively refers to these low-power modes as the *standby function*. Several modes within the standby function provide shutdown methods for unused internal circuitry. NEC Electronics' microcontroller architecture improves low-power operation by providing a special clock prescaling to the CPU and separately to each integrated peripheral device. Users can switch in real time between different clock settings to achieve an optimal ratio of system performance versus power consumption. To further reduce power consumption and enhance functionality, NEC Electronics has integrated two independent clocks into its microcontrollers, the primary high-speed main clock and a secondary 32.768-kHz subsystem clock, each with its own set of standby modes. The main clock operates all parts of the microcontroller, while the subsystem clock is dedicated to the CPU, a real-time clock (also called a watch timer), and LCD controller (if present). NEC Electronics provides dual oscillators for applications needing the ability to operate from a low-speed, very low-power-consuming clock source and then switch to a high-speed clock for time-critical functions. Security systems, data acquisition systems, and real-time control systems are good examples of these applications. The main clock structure has two standby modes: halt and stop. The addition of a subsystem clock offers two complementary modes: subclock operation and subclock halt. This document describes NEC Electronics' dual-clock architecture, illustrated in Table 1

| Clock Source | Mode               | Description                                                                                                                    |

|--------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Main         | Halt               | CPU clock is OFF and peripheral clocks are ON                                                                                  |

|              | Stop               | Main clock is OFF and the rest of the microcontroller, except for the interrupt controller, is OFF                             |

| Subsystem    | Subclock operation | Main clock is OFF; subsystem oscillator clocks the CPU, real-<br>time clock, and an LCD controller, if present                 |

|              | Subclock halt      | Main clock is OFF and CPU clock halted (OFF); the subsystem clock pulses the real-time clock and an LCD controller, if present |

and later in Figure 1, and how to use the clocks to optimize power consumption.

#### Table 1. Standby Functions in NEC Electronics Microcontrollers

Note: Operating current is shown for the µPD78064 at 3 volts and 5 MHz.

### Tracking the Time of Day

Some battery-powered applications require the microcontroller to keep track of the time of day, a good example of a low-power application. For this purpose, many NEC Electronics microcontrollers contain a watch timer (real-time clock) that updates the time of day every one-half second. The watch timer, driven by a 32.768-kHz subsystem clock, must be ON for the microcontroller to continually track the time of day in real time.

The CPU can use either the main clock or the subsystem clock to update the time of day. This application note explains both options and shows how subsystem clock operation uses less current than main clock operation.

# NEC

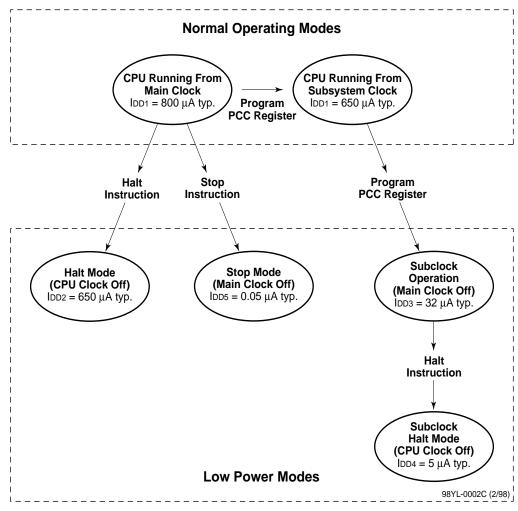

Main Clock OperationWhen the time of day is updated by the CPU using the main clock, executing a stop<br/>instruction puts the microcontroller into stop mode and turns OFF the main clock. The<br/>watch timer uses the subsystem clock and continues to run, and issues an interrupt every<br/>0.5 second, at which time the main crystal is started and an interrupt service routine<br/>increases the time count by 0.5 second. After the time is updated, the microcontroller<br/>returns to stop mode and waits for the next watch timer interrupt (Figure 2).

#### Figure 2. Time-of-Day Update Using the Main Clock

Subsystem Clock Operation

Alternatively, the time can be updated by the CPU using the subsystem clock. In this case, the microcontroller must be put into subclock halt mode using this procedure.

1.

Switch to the subsystem clock by setting bit CSS of the Processor Clock Control (PCC) register to logic 1.

2.

Verify that the CPU clock source is switched to the subsystem clock and that bit CLS of the PCC register is set to logic 1.

3.

Enter subclock operation by shutting off the main oscillator and setting bit MCC of the PCC register to logic 1.

4. Enter subclock halt mode by executing a halt instruction.

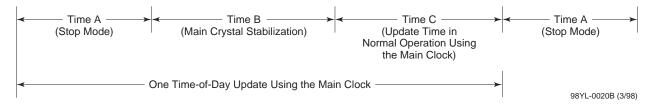

When the watch timer generates a 0.5-second interrupt, the microcontroller exits subclock halt mode and enters subclock operation, whereby the subsystem clock is connected to the CPU and the CPU updates the time of day by 0.5 second. During this time, the microcontroller's main clock is OFF. After the time of day is updated, a halt instruction must be executed to disconnect the subsystem clock from the CPU. As shown in Figure 3, the microcontroller waits for the next watch timer interrupt to update the time of day. Note that because the subsystem clock is always oscillating, 'TIME B' is zero (0).

#### Figure 3. Time-of-Day Update Using the Subsystem Clock

### Example Operating Current Calculation

This section explains how to calculate operating current for NEC microcontrollers. The example uses data pertaining to the  $\mu$ PD78064 and is based on these assumptions:

- 1. It takes 500 CPU clock periods to update the time of day.

- 2. The main clock has a ceramic resonator with a stabilization time of 3 ms.

- 3. The oscillator stabilization time select (OSTS) register allows a range of different wait times to be selected to match the crystal resonator.

- 4. The oscillation stabilization wait time closest to 3 ms, 3.28 ms, is selected.

- 5. Maximum main clock frequency (fx) for the  $\mu$ PD78064 is 5.00 MHz.

- 6. The current specified in the data sheet = internal prescaler setting of fxx/16.

- 7. The CPU cycle period for  $fxx/16 = 3.2 \,\mu s$ .

- 8. Therefore, TIME c in Figure 2 is  $500 \times (3.2 \ \mu s) = 1.6 \ ms.$

|                    |                                         | IDD at 3 Volts |          |

|--------------------|-----------------------------------------|----------------|----------|

| Mode               | Clocks                                  | Typical        | Maximum  |

| Normal operation   | Main and subclocks ON                   | 800 μA         | 2,400 µA |

| Halt mode          | Main and subclocks ON; clock to CPU OFF | 650 μA         | 1,950 µA |

| Stop mode          | Main clock OFF                          | 0.05 μA        | 10 µA    |

| Subclock operation | Main clock OFF and subclock to CPU ON   | 32 µA          | 64 µA    |

| Subclock halt      | Main clock OFF and subclock to CPU OFF  | 5 μΑ           | 15 μA    |

#### Table 2. µPD78064 Specifications

Table 3 shows this information as it appears on the auto-calculate worksheet, a program especially developed by NEC Electronics America to calculate power consumption for NEC Electronics microcontrollers. The worksheet is available at <a href="https://www.necelam.com/docs/files/power\_a1%204.xls">www.necelam.com/docs/files/power\_a1%204.xls</a>.

|                                      |                             |         | ameters (mA)          |                           |

|--------------------------------------|-----------------------------|---------|-----------------------|---------------------------|

|                                      |                             | Typical | Maximum               |                           |

| Main clock operation                 | I <sub>DD1</sub>            | 0.80    | 2.40                  |                           |

| Main clock halt mode                 | I <sub>DD2</sub>            | 0.65    | 1.95                  |                           |

| Subclock operation                   | I <sub>DD3</sub>            | 0.032   | 0.064                 |                           |

| Subclock operation at 2 volts        | I <sub>DD3</sub> at 2 volts | 0.024   | 0.048                 |                           |

| Subclock halt mode                   | I <sub>DD4</sub>            | 0.005   | 0.015                 |                           |

| Subclock halt mode at 2 volts        | I <sub>DD4</sub> at 2 volts | 0.0025  | 0.0125                |                           |

| Stop mode                            | I <sub>DD5</sub>            | 0.00005 | 0.010                 |                           |

| CPU clock divided internally; main   | 16                          | 2       | < Subclock divided by |                           |

| Default oscillation frequency        |                             | 5       | 3.28                  | < Osc. stabilization time |

| Enter number of CPU clocks here ===> |                             |         | 500                   |                           |

Table 3. Example of Auto-Calculate Worksheet Data Input (µPD78064 at 3 Volts)

# <u>NEC</u>

| Main Clock<br>Operating Current      |             | Standby current = $I_{DD Total} = (I_{DD TIME A}) + (I_{DD TIME B}) + (I_{DD TIME C})$ , where halt mode current is noted as 'TIME B.' See Figure 2.                                                                                                                                                                          |

|--------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |             | TIME A + TIME B + TIME C = $500 \text{ ms}$<br>TIME A = $500 \text{ ms} - \text{TIME B} - \text{TIME C}$<br>TIME A = $500 \text{ ms} - 3.28 \text{ ms} - 1.60 \text{ ms} = 495.12 \text{ ms}$                                                                                                                                 |

|                                      |             | % of time a = 495.12 ms / 500 ms x (100) = 99.02%<br>% of time b = 3.28 ms / 500 ms x (100) = 0.66%<br>% of time c = 1.60 ms / 500 ms x (100) = 0.32%                                                                                                                                                                         |

|                                      |             | Typical current = $I_{DD Typ} = (I_{DD Typ TIME A}) + (I_{DD Typ TIME B}) + (I_{DD Typ TIME C})$                                                                                                                                                                                                                              |

|                                      |             | $\begin{split} I_{\text{DD Typ}} &= 99.02\% \ /100 \ \text{x} \ (0.005 \ \mu\text{A}) + 0.6\% \ / \ 100 \ \text{x} \ (0.65 \ \text{mA}) + 0.32\% \ / \ 100 \ \text{x} \ (0.8 \ \text{mA}) \\ I_{\text{DD Typ}} &= 4.95 \ \mu\text{A} + 4.26 \ \mu\text{A} + 2.56 \ \mu\text{A} = \underline{11.77 \ \mu\text{A}} \end{split}$ |

|                                      |             | $Maximum current = I_{DD Max} = (I_{DD Max TIME A}) + (I_{DD Max TIME B}) + (I_{DD Max TIME C})$                                                                                                                                                                                                                              |

|                                      |             | $I_{\rm DD\ Max} = 99.02\% \ / \ 100\ x\ (15\ \mu A) + 0.66\% \ / \ 100\ x\ (1.95\ m A) + 0.32\% \ / \ 100\ x\ (2.4\ m A)$<br>$I_{\rm DD\ Max} = 14.85\ \mu A + 12.78\ \mu A + 7.68\ \mu A = \underline{35.31\ \mu A}$                                                                                                        |

| Subsystem Clock<br>Operating Current | acti<br>sub | CPU is inactive during halt mode. The interrupt generated by the watch timer vates the CPU, which is immediately connected to the subsystem clock. Since the system crystal is always oscillating, 'TIME B' is equal to zero. See Figure 3. Therefore, the ulation formula is modified as follows:                            |

|                                      |             | $\begin{split} I_{\text{DD Total}} = (I_{\text{DD TIME A}}) + (I_{\text{DD TIME B}}) + (I_{\text{DD TIME C}}) = (I_{\text{DD TIME A}}) + 0 + (I_{\text{DD TIME C}}) = (I_{\text{DD TIME A}}) + (I_{\text{DD TIME C}}) \end{split}$                                                                                            |

|                                      |             | Cycle time = 2 x (1/32.768 kHz) = 61 µs                                                                                                                                                                                                                                                                                       |

|                                      |             | TIME A + TIME C = 500 ms<br>TIME C = 500 CPU clocks = 500 x (61 $\mu$ s) = 31.52 ms<br>TIME A = 500 ms - TIME C = 500 - 31.52 = 469.48 ms                                                                                                                                                                                     |

|                                      |             | % of time a = 469.48 ms / 500 ms x (100) = 93.90%<br>% of time b = 0%<br>% of time c = 61 ms / 500 ms x (100) = 6.10%                                                                                                                                                                                                         |

|                                      |             | Typical current = $I_{DD Typ} = (I_{DD Typ} TIME A) + (I_{DD Typ} TIME C)$                                                                                                                                                                                                                                                    |

|                                      |             | $I_{DD Typ}$ = 93.90% / 100 x (2.5 μA) + 6.10% / 100 x (5 μA)<br>$I_{DD Typ}$ = 4.69 μA + 1.95 μA = <u>6.65 μA</u>                                                                                                                                                                                                            |

|                                      |             | Maximum current = $I_{DD Max} = (I_{DD Max} TIME A) + (I_{DD Max} TIME C)$                                                                                                                                                                                                                                                    |

|                                      |             | $I_{\text{DD Max}} = 93.90\% / 100 \text{ x} (12.5 \mu\text{A}) + 6.10\% / 100 \text{ x} (15 \mu\text{A})$ $I_{\text{DD Max}} = 14.08 \mu\text{A} + 3.91 \mu\text{A} = \underline{17.99 \mu\text{A}}$                                                                                                                         |

Both the typical and maximum operating currents using the subsystem clock are less than those using the main system clock.

|                                    |      | Main Syst | em Clock | Subsyste | m Clock     |

|------------------------------------|------|-----------|----------|----------|-------------|

|                                    |      | 5,000,0   | 000 Hz   | 32,768   | 8 kHz       |

| Subroutine execution time interval | ms   |           | 500.00   |          | 500.00      |

| Oscillation stabilization time     | ms   |           | 4.00     |          | Subclock or |

| Min. CPU cycle time (set by PCC)   | μs   |           | 3.20     |          | 61.04       |

| Clock cycles needed by subroutine  | each |           | 500.00   |          | 500.00      |

| Time required by subroutine        | ms   |           | 1.60     |          | 30.52       |

| Overall sleep time                 | ms   |           | 494.40   |          | 469.4       |

| ·                                  |      | Main Syst | em Clock | Subsyste | m Clock     |

| Sleep time (subhalt mode)          | %    |           | 98.88    |          | 93.9        |

| Oscillation stabilization time     | %    |           | 0.80     |          | 0.0         |

| Microcontroller is active          | %    |           | 0.32     |          | 6.1         |

| Total                              | %    |           | 100.00   |          | 100.0       |

| ·                                  |      | Тур.      | Max.     | Тур.     | Max         |

| Sleep time (subhalt mode)          | μΑ   | 4.94      | 14.83    | 4.69     | 14.03       |

| Oscillation stabilization time     | μΑ   | 5.20      | 15.60    | 0.00     | 0.0         |

| Microcontroller active             | μΑ   | 2.56      | 7.68     | 1.95     | 3.9         |

| Total                              | μΑ   | 12.70     | 38.11    | 6.65     | 17.9        |

Table 4 shows how this information is displayed on the auto-calculate worksheet.

| Table 4. Current Consumption Results From | n the Auto-Calculate Worksheet |

|-------------------------------------------|--------------------------------|

|                                           |                                |

### Effect of Crystal Stabilization Time on IDD

The resonator's stabilization time has a profound effect on overall input current consumption. The original calculation example used a resonator stabilization time of 3.28 ms. The calculations shown in Table 5 are based on a stabilization time of 10 ms and stabilization wait time of 13.1 ms, resulting in a substantial increase in power consumption. As demonstrated here, the shorter the oscillation stabilization time, the lower the overall power consumption. The subsystem clock is clearly advantageous over the fastest (and most expensive) crystal resonators.

|                              | Mair    | Main Clock |          |  |

|------------------------------|---------|------------|----------|--|

| Power Consumption            | 3.28 ms | 13.1 ms    | Subclock |  |

| I <sub>DD</sub> Typical (mA) | 11.77   | 24.45      | 6.65     |  |

| I <sub>DD</sub> Maximum (mA) | 35.31   | 73.36      | 17.99    |  |

#### Table 5. Oscillation Stabilization Times Versus Subsystem Clock at 500 Cycles

### Effect of CPU Cycles on IDD

The larger the current ratio of main clock oscillation to subsystem clock operation, the better the power savings. To prove this hypothesis, Table 6 compares power consumption at 250, 500, and 5000 cycles.

|                      | 250 Cycles |          | 500 Cycles |          | 5000 Cycles |          |

|----------------------|------------|----------|------------|----------|-------------|----------|

| Power Consumption    | Main       | Subclock | Main       | Subclock | Main        | Subclock |

| Typical current (mA) | 10.50      | 5.82     | 11.77      | 6.65     | 34.67       | 21.48    |

| Maximum current (mA) | 31.50      | 16.50    | 35.31      | 17.99    | 104.00      | 44.91    |

# NEC

|                             | The subsystem clock clearly uses less power than the main clock. A shorter program also lowers the average input current.                                                                                                                                                                                                                                                            |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | It is important to pay attention to the maximum number of clock cycles required by a program, because the subsystem clock is much slower than the main clock and processing power is reduced when the subsystem clock is used. If the program is too long, it may be impossible to run it using the subsystem clock. This problem could be solved, however, by optimizing the code.  |

|                             | Another potential problem arises when attempting to execute a very long subroutine.<br>Therefore, with some specific microcontrollers, the power savings becomes negligible as<br>the number of CPU cycles increases. Always perform this initial calculation in order to<br>design a power-optimized system.                                                                        |

|                             | Note: NEC Electronics onstantly improves power consumption reduction techniques, and newest microcontrollers have more optimized main clock operation.                                                                                                                                                                                                                               |

| Auto-Calculate<br>Worksheet | The auto-calculate worksheet in Table 7 demonstrates the results obtained for the µPD78064 applying the same assumptions used in the earlier calculations. The auto-calculate program is available at <u>www.necelam.com/docs/files/power_a1%204.xls</u> . To use the program, you must have Microsoft <sup>®</sup> Excel <sup>™</sup> software installed on your personal computer. |

|                             | 1. Read the instructions on page 1 of worksheet 1.                                                                                                                                                                                                                                                                                                                                   |

|                             | 2. From the <b>Tools</b> menu, click <b>Macro</b> .                                                                                                                                                                                                                                                                                                                                  |

|                             | 3. Scroll through the list of part numbers and select one.                                                                                                                                                                                                                                                                                                                           |

|                             | 4. Click <b>Run</b> .                                                                                                                                                                                                                                                                                                                                                                |

|                             |                                                                                                                                                                                                                                                                                                                                                                                      |

The program automatically calculates current consumption and displays typical and maximum specifications, as shown in Table 7.

#### Table 7. Auto-Worksheet Calculations for the µPD78064 at 3 Volts

|                                               |                       |        | Input Paran          | neters (mA) | ]                                             |

|-----------------------------------------------|-----------------------|--------|----------------------|-------------|-----------------------------------------------|

|                                               |                       |        | Тур.                 | Max.        |                                               |

| Main clock operation                          | I <sub>DD1</sub>      |        | 0.80                 | 2.40        |                                               |

| Main clock halt mode                          | I <sub>DD2</sub>      |        | 0.65                 | 1.95        |                                               |

| Subclock operation                            | I <sub>DD3</sub>      |        | 0.032                | 0.064       |                                               |

| Subclock operation at 2 volts                 | I <sub>DD3</sub> (2V) |        | 0.024                | 0.048       |                                               |

| Subclock halt mode                            | I <sub>DD4</sub>      |        | 0.005                | 0.015       |                                               |

| Subclock halt mode at 2 volts                 | I <sub>DD4</sub> (2V) |        | 0.0025               | 0.0125      |                                               |

| Stop mode                                     | I <sub>DD5</sub>      |        | 0.00005              | 0.010       |                                               |

| CPU clock is divided internally; main divided |                       |        | 16                   | 2           | <subclock by<="" divided="" td=""></subclock> |

| Default oscillation frequency                 |                       |        | 5                    | 3.28        | <osc. stabilization="" td="" time<=""></osc.> |

| Enter the number of CPU clock cycles here =   | :==>                  |        | 50                   | 00          |                                               |

|                                               |                       | Main   | Clock (5,000,000 Hz) | Subsyster   | n Clock (32,768 kHz                           |

| Subroutine execution time interval            | ms                    |        | 500.00               |             | 500.00                                        |

| Oscillation stabilization time                | ms                    | 3.28   |                      | Subclock    |                                               |

| Mininimum CPU cycle time (set by PCC)         | μs                    | 3.20   |                      | 61.         |                                               |

| Clock cycles required by subroutine           | each                  | 500.00 |                      | 500.0       |                                               |

| Time required by subroutine                   | ms                    | 1.60   |                      | 30.5        |                                               |

| Overall sleep time                            | ms                    | 495.12 |                      | 469.48      |                                               |

| c1 / 11 1. 1.                                 | 0(                    |        | 00.02                |             | 93.90                                         |

| Sleep time (subhalt mode)                     | %                     |        | 99.02                |             |                                               |

| Oscillation stabilization time                | %                     |        | 0.66                 | 0.          |                                               |

| Microcontroller active                        | %                     |        | 0.32                 |             | 6.10                                          |

| Total                                         | %                     |        | 100.00               |             | 1000.00                                       |

| al                                            |                       | Typ.   | Max.                 | Тур.        | Max                                           |

| Sleep time (subhalt mode)                     | μΑ                    | 4.95   | 14.85                | 4.69        | 14.08                                         |

| Oscillation stabilization time                | μΑ                    | 4.26   | 12.78                | 0.00        | 0.0                                           |

| Microcontroller active                        | μΑ                    | 2.56   | 7.68                 | 1.95        | 3.9                                           |

| Total                                         | μΑ                    | 11.77  | 35.31                | 6.65        | 17.99                                         |

| Power savings SUB versus main clock           | %                     |        |                      | 43.52       | 49.05                                         |

| Scratch pad. Enter the comparison data below  | N.                    |        |                      |             |                                               |

| Compared to CPU clock cycles (µA)             | 250                   | 10.50  | 31.50                | 5.82        | 16.5                                          |

| Compared to CPU clock cycles (%)              | 250                   |        |                      | 44.53       | 47.63                                         |

A given device's default parameters are entered into the worksheet when you select that device. You will need to vary the number of instructions to find the optimum current. Also, the program makes assumptions about voltage, CPU clock division rate, oscillator frequency, and number of CPU cycles. You can only modify the number of CPU cycles for a specific application in order to generate the best power consumption model.

Power consumption information for each part in the matrix was checked at the time of this document's publication. To verify accuracy, please refer to the latest published data sheet for your specific device. For any device not shown in the matrix, please request the latest data from NEC Electronics and manually enter those numbers in the Input Parameters box. The worksheet program will calculate the results, but without saving the data in the password-protected data base.

# NEC

#### For literature, call **1-800-366-9782** 7 a.m. to 6 p.m. Pacific time or fax your request to **1-800-729-9288** or visit our web site at **www.necelam.com**

#### **NEC Electronics America, Inc.**

CORPORATE HEADQUARTERS 2880 Scott Boulevard Santa Clara, CA 95050-2554

TEL 408-588-6000

The information in this document is current as of July 2003. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc. for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information. No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document. NEC Electronics does not assume any liability arising from the use of such NEC Electronics products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others. Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information in the design of customers products. No IEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products. NEC Electronics products developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its guality grade, as indicated below. Customer must incorporate sufficient safety measures in their duality grade of each NEC Electronics product before using it in a particular appli

"NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

"NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).