# **HiPerClockS<sup>™</sup> Application Note**

High Speed LVCMOS Driver Termination

Design Guide

This application note provides general design guide for high speed LVCMOS driver termination. To handle high speed LVCMOS drivers, general rules for high-speed digital board design must be carefully followed. Improper handling of the termination will cause signal reflection, clock ringing and lead to system failure. Proper termination is required to ensure signal integrity and Electro-Magnetic Interference (EMI) reduction. There are many different termination schemes for single ended LVCMOS drivers. This application note discusses parallel termination, AC termination and series termination. The following termination approaches are only general recommendations under ideal conditions. Board designers should consult with their signal integrity engineers and verify through simulations in their system environment.

## **Parallel Termination**

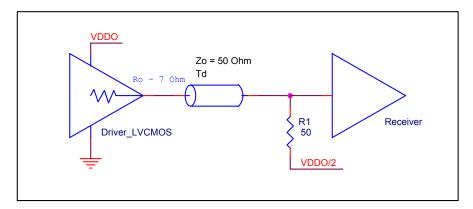

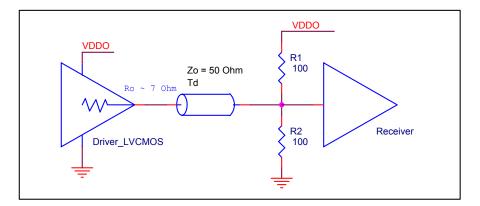

The standard termination of an LVCMOS driver in a  $Z_0$ =50 ohm transmission line environment is shown in Figure 1. The driver is terminated with 50 Ohm pull down to VTT=V<sub>DDO</sub>/2 at the receiver end. The LVCMOS clock buffer characterization set up is terminated in similar manner using split power supplies approach (See test condition in data sheet of an LVCMOS driver). In actual applications, the equivalent parallel termination shown in Figure 2 can be used. The LVCMOS parallel termination has the same effect as the standard LVCMOS shown in Figure 1. The parallel termination shown in Figure 2 can eliminate the need of VTT=V<sub>DDO</sub>/2 power supply (or reference voltage). The power dissipation calculation is described in a separate application note.

Figure 1 LVCMOS Driver Standard Termination

Figure 2 LVCMOS Parallel Termination

# **HiPerClockS<sup>™</sup> Application Note**

High Speed LVCMOS Driver Termination

Design Guide

## **AC Termination**

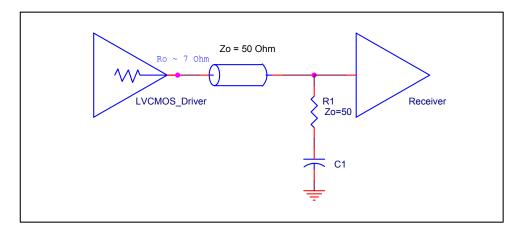

The LVCMOS driver AC termination in a 50-ohm transmission line environment is shown in Figure 3. The majority of load current is drawn during transient region (i.e. rising edge and falling edge). This termination consumes less power than the parallel termination. The proper value of capacitor C1 depends on the trace delay and capacitance of the transmission line. Some software tools such as Hyperlynx provides a feature of calculating the transmission line capacitance by entering the trace information [1].

Figure 3 AC Termination

# **Series Termination**

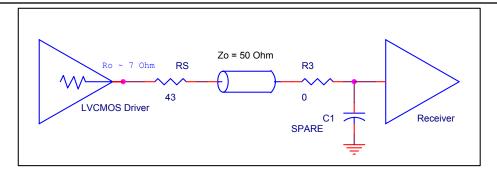

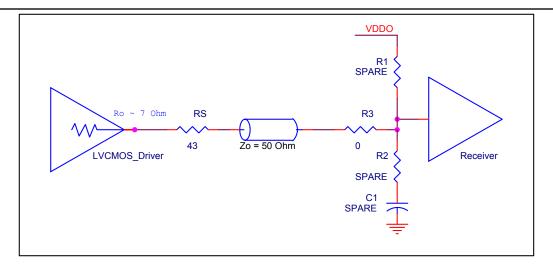

Series termination is a popular termination scheme for LVCMOS drivers. Figure 4 shows a simple series termination for LVCMOS drivers with output impedance of 7 Ohm. The Power Dissipation of this termination scheme is described in a separate document.

The typical output impedance  $R_0$  of a HiPerClockS<sup>TM</sup> LVCMOS driver is approximately 7 ohms. (Some parts might have different Ro value. Refer to data sheet for the output impedance). The closest series resistor value,  $R_S$ , can be calculated as follows

$$R_S = Z_O - R_O = 43$$

ohms

In the Figure 4, the footprint for optional series resistor R3 or optional capacitor C1 at the receiver input is recommend for adjusting edge rate or overshoot if necessary.

# **HiPerClockS<sup>™</sup> Application Note**High Speed LVCMOS Driver Termination

High Speed LVCMOS Driver Termination Design Guide

Figure 4 One to One LVCMOS Series Termination

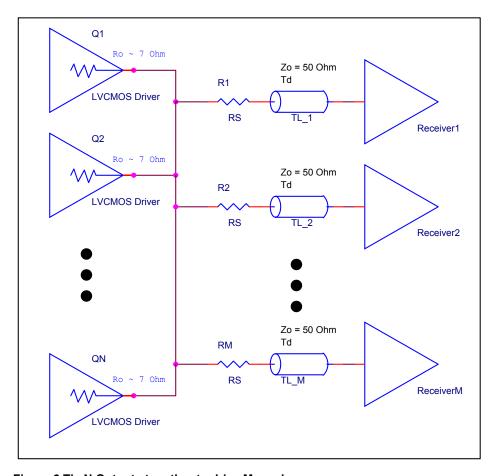

When the number of drivers is not equal to number of receivers as shown in Figure 6, the series resistor value  $R_S$  is calculated as follows:

$$R_S = Z_O - (R_O \times M)/(N)$$

Number of driver = N Number of receiver = M

This configuration assumes that all the trace delays and load conditions are equally matched.

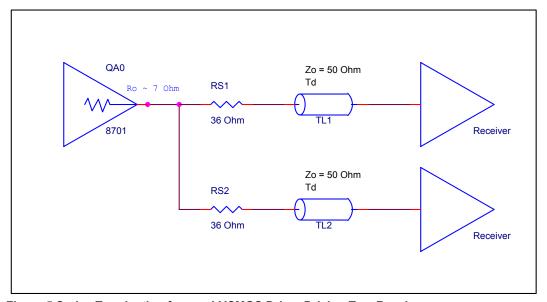

For example, one driver driving 2 receivers as shown in Figure 5, with N=1and M=2, the series resistor is calculated to be  $R_{\rm S}$  = 36 Ohms. The trace delays Td on TL1 are equal. The loading conditions on both receivers should also be equal.

Figure 5 Series Termination for one LVCMOS Driver Driving Two Receiver

For 5 drivers driving 6 receivers, the closest series resistor can be calculated as follows:

N=5, N=6,  $Z_O$ =50 Ohms,  $R_O$  =7 Ohm

# **HiPerClockS<sup>™</sup> Application Note**

High Speed LVCMOS Driver Termination

Design Guide

$$R_S = 50 - (7 \times 6)/5 = 41.6 \text{ Ohm}$$

The result above is straight from calculations. The closest available resistor value should be chosen.

Figure 6 Tie N Outputs together to drive M receivers

# PC Board Layout With Option of Multi Termination Schemes

For signal integrity, take the necessary precaution and follow the high-speed digital design rules as much as possible. In most cases, the board design cannot fully comply the high-speed design rules due to constrains on the board environment, e.g. space available, cost etc. There is always some unknown parameters or interference in the system environment. The signal quality can only be optimized through the experiment during prototype phase. One termination scheme may work better then the other. While capturing a schematic for PC Board layout, if there is space available, it is recommended to provide options to choose different termination schemes on the prototype board. Figure 7 shows an example schematic for a PC board footprint that provides an option of choosing various types of terminations.

# **HiPerClockS<sup>™</sup> Application Note**High Speed LVCMOS Driver Termination

Design Guide

Figure 7 P.C. Board layout provides footprint to choose various termination options

Written by: Ming Lim

Any comment, please send e-mail to ming@icst.com

#### References:

[1] Kaufer, Steve, Crisafulli, Kellee, Terminating Trace on High-Speed PCBs, Printed Circuit Design, March 1998

[2] Dr. Johnson, Howard, Dr. Graham, Martin, High-Speed Digital Design, A Handbook of Black Magic, Prentice Hall, 1993

## **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.