# Modular Baseband Design Enabling a Low Cost, Reusable Wireless Infrastructure Application Note - 415

### **Notes**

# Introduction

Over the last decade wireless base station designers have made major strides in their constant struggle to reduce cost, power and footprint. For these designers the goal for 3G base station development is simple: To achieve ten times the bandwidth at one tenth the cost.

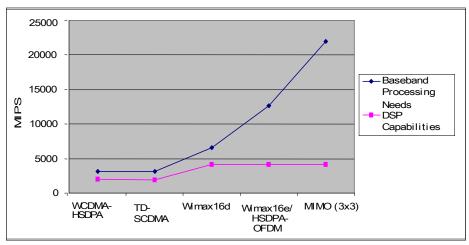

The processing power required to handle baseband algorithms continues to increase with new wireless protocols. As shown in figure 1, conventional digital signal processors (DSPs) may not have enough MIPS power to perform baseband processing, resulting in the need for hardware acceleration to supplement the DSPs<sup>2</sup>. A typical architecture may consist of a cluster of DSPs and hardware accelerator blocks on the baseband card where multiple channels are processed.

Figure 1: MIPS requirements for different wireless protocols

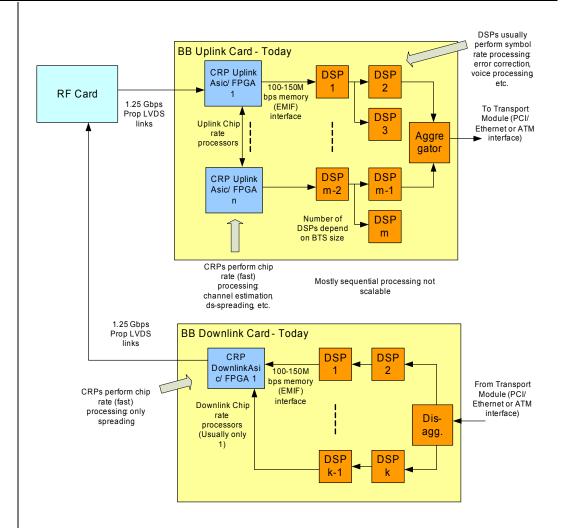

Today's base station typically relies on a sequential processing scheme, and every block and processing is time aligned <sup>1</sup>. The architecture often looks like figure 2. One chip-rate processor (CRP) interfaces to the time-sliced backplane and receives "samples" from the RF card.

In CDMA-related systems (such as WCDMA, CDMA2000) samples are converted to chips and eventually to symbols before transitioning to the DSP, often via the parallel memory interface. The DSP performs the "symbol-rate processing" such as error correction and voice/data channel processing.

In orthogonal frequency division multiplexing (OFDM) systems (such as 802.16x, WiMAX), the CRP is replaced by the OFDM PHY, which performs synchronization and FFT before handing symbols to the DSPs. DSPs perform similar operations to the CDMA architecture.

This architecture is not very scalable as ASIC and DSP processing allocations are fixed at the time of design, and are tightly coupled with the selection of the hardware. As a result, some DSPs and CRPs might be underutilized in some base stations, but this inefficiency is allowed to exist because it is very difficult to shift resources from one processing block to another during run time.

Figure 2: Today's typical base band card architecture

It is also not easy to have the same architecture for pico base station, micro and macro base station, as it is a challenge to scale algorithms developed for the CRPs and DSPs in a given application. For a small performance increment, a whole new group of CRPs and DSPs may need to be added.

In some architectures, one of the CRPs interfaces to the backplane (RF card) and the rest of the CRPs talk to the first CRP (uplink card). This requires a different design for the backplane interface CRP, as one cannot replicate the same design to the subordinate CRPs without reducing their effectiveness and thus decreasing the return on investment for developing the CRPs.

The memory interface between the CRPs and DSPs can also be a problem for the system software. The bi-directional nature of a standard memory interface can make it harder to fully utilize this interconnect. Usually baseband algorithms are sensitive to non- deterministic delay, which may be introduced using a bi-directional interface.

# **Emerging Standards to the Rescue**

In recent years the industry has thrown its support behind a number of standards-based efforts to promote modularity at the system and network levels, allowing for cost-effective reuse of engineering efforts and scalable architectures.

One of the best examples of this trend is the Open Base Station Architecture Initiative (OBSAI). OBSAI defines modular base station architecture with standardized interfaces between each module in the base station<sup>3</sup>.

Six months after OBSAI was launched, a competing standard, Common Public Radio Interface (CPRI) was announced. Far simpler than OBSAI, CPRI focuses on the UMTS base station by dividing it into a RF and control block connected via a standard digital interface<sup>4</sup>.

To address the needs of network equipment manufacturers and service providers at the chassis level, the PCI Industrial Computer Manufacturers Group (PCI-MG) has defined a standard chassis form factor called the Advanced Telecom Computing Architecture (ATCA)<sup>5</sup>.

DSP blades in wireless base station applications need highly simplified, high-speed interconnects for data transfer and protocol management. These computationally-intense embedded applications require the system to quickly move data between signal processors in a tightly-coupled DSP farm. The serial RapidIO (sRIO)<sup>6</sup> specifications, developed as an open standard, was expressly designed to address the needs of high-performance embedded systems.

The sRIO standard complements the modularity benefits that standards like OBSAI, CPRI and ATCA bring at the chassis and system levels by extending those advantages to the board level. Neither OBSAI nor CPRI define the linecard interface in a base station design.

Moreover, sRIO's highly tuned support for DSP clusters allows equipment designers to develop very flexible and scaleable architectures in a cost-efficient manner that simply cannot be replicated in FPGA or ASIC-based designs. For example, using sRIO a base station designer can build a DSP-intensive system for macro cell applications allowing the rapid deployment of new technology to support wide areas of coverage, and then reuse much of the original design in scaled-down solutions for micro or pico-cellular environments that deliver the desired saturation and density in the most cost-effective manner.

Most importantly, sRIO simplifies inter-processor communications by integrating control and data traffic, offloading simple and time-consuming tasks from the processor, and differentiating between high- and low-priority data traffic.

# **Putting it all together**

Then the next question is: How do we put all of these together for base station development? What is missing to get a complete baseband card design?

Before looking into next-generation architectures, let's look at the algorithm-protocol partitioning for the base stations.

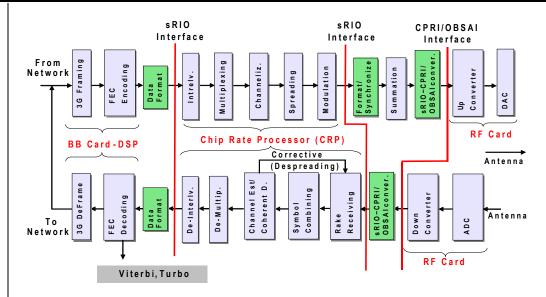

Figure 3: Algorithm-protocol partitioning for CDMA based systems

The light blue blocks are mathematical operations needed for CDMA based (UMTS, CDMA2000, etc.) baseband transceiver. An ideal baseband card has a cluster of DSPs and hardware accelerator blocks (or CRPs) in the form of FPGAs or ASICs. Figure 3 shows partitioning of algorithms to DSP and CRPs. There might be multiple DSPs and CRPs depending on the processing requirements for the baseband card, therefore these blocks need to be connected. A similar partition and observation can be made for OFDM-based algorithms.

Serial RIO and CPRI/OBSAI interfaces are also shown in Figure 3 designated with red lines. Serial RIO is used to connect multiple processing blocks on the baseband card, as shown in figure 4. These interfaces are also shown on figure 3 with algorithm partitioning. Note the green blocks next to the interfaces are necessary for data formatting between the interface and algorithms such as sign extension, packetization of samples/symbols, and multiple-packet alignment (from multiple CRPs) before summation. These functions have to be performed by one of the neighboring devices to this interface. The question is: What is the ideal architecture to handle this partitioning?

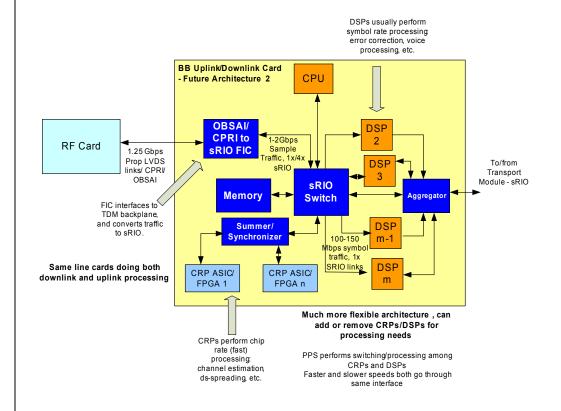

Figure 4: Ideal Baseband Architecture

Figure 4 shows a close-to-ideal architecture for next-generation baseband cards. A fabric interface component (FIC) translates CPRI/OBSAI to sRIO, and the rest of the baseband card interface is sRIO, but a regular sRIO switch will not be enough to handle special operations needed. There are 2 distinct traffic flows on the baseband card:

- Between the FIC and CRPs: High-speed traffic (spread samples) with deterministic timing. Latency on this link needs to be deterministic to support timing requirements in the base station. Packets are multicast to multiple CRPs on uplink, summed on downlink.

- Between CRPs and DSPs: Much more flexible in latency, lower bandwidth (symbols) traffic, as well as control and maintenance packets.

A regular sRIO switch needs to be supported with a summer and synchronizer device, which aligns packets from multiple CRPs, sums them on the uplink, and multicasts them to CRPs on the uplink.

Different devices and algorithms work on different sample and symbol sizes. For example, CPRI defines sample size ranging from 8 bits to 40 bits. Processors like to work on sample sizes 8, 16 or 32. Also different algorithms want samples in specific order (I-Q together or separate, over-samples together with regular samples or separate, etc.) therefore these data formatting operations need to be performed in the CRP and the DSP. Depending on selection of DSP and CRP, there are a lot of combinations of these operations that system designer need to be aware of, and processors might spend a lot of MIPS to do these operations.

Baseband card sizes can be small to large depending on the system. Micro-TCA form factor can be close enough for all different cards in the base station. This will give designers the means to build a large and varied selection of interchangeable modules to meet the needs of telecommunications equipment manufacturers.

This architecture also supports flexible and scalable base station designs.

- Flexible: Exchanging CRPs with OFDM PHYs; the same design can be used for both CDMA and OFDM based systems

- 2) Scalable: Number of CRPs and DSPs can be changed easily to adapt the same design for pico to macro base stations. Traffic and processing power can also be shifted from one device to another at run time since the architecture is not tightly coupled with algorithms anymore.

## **Conclusion**

The development of 3G wireless networks is at a crossroads. Subscribers expect higher levels of service at lower cost. Yet the bandwidth and performance requirements implicit in delivering triple-play services will demand increasingly sophisticated and complex base station designs.

The key to meeting those needs while lowering costs will lie in the adoption of modular, standards-based architectures. By embracing emerging industry standards such as ATCA, OBSAI and CPRI and leveraging the high degree of design flexibility and adaptability in DSP-based arrays using the sRIO interface, base station designers can deliver high performance next-generation wireless services at a cost structure users will embrace.

#### References:

- [1] Bertan Tezcan et al, "Advantages of Packet Switched Communication in Next-Generation Wireless Basestation Equipment", GSPx, September 2004

- [2] Andsers Nilsson, et al, "An Accelerator Architecture for Programmable Multi-Standard Baseband Processor", WNET, 2004

- [3] www.obsai.com

- [4] <u>www.cpri.info</u>

- [5] <u>www.atca.org</u>

- [6] www.rapidio.org

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.