# M16C/6C Group

Supplement for Serial Interface UARTi (i = 0 to 5)

R01AN0421EJ0100 Rev.1.00 Mar. 09, 2011

# 1. Abstract

This document is a supplement for serial interface UARTi (i = 0 to 5) specifications in the M16C/6C Group.

# 2. Introduction

This document includes modifications to the serial interface UARTi specifications in Technical Update: TN-16C-A201A/E "Specification Modifications in M16C/65, M16C/64A, M16C/63 and M16C/6C Groups", and supplemental information for the Serial Interface UARTi chapter in the M16C/6C Group User's Manual: Hardware. Use this document to verify changes made to the specifications. A previous version of the chapter from the hardware

manual is attached at the end for comparison.

When making a program using I<sup>2</sup>C mode, refer to application notes listed below.

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

# 3. Supplement Content and Modifications to Specifications

# 3.1 Clock Synchronous Serial I/O Mode, UART Mode

The description for "Transmit/Receive Circuit Initialization" in the previous version of the hardware manual is correct, but not clear enough. The description has been rewritten as shown below.

Processing When Terminating Communication or When an Error Occurs

When communication is terminated in clock synchronous serial I/O mode or UART mode, or when a communication error occurs, use the following procedure to reset communication:

- (1) Set the TE bit in the UiC1 register to 0 (transmission disabled) and the RE bit to 0 (reception disabled).

- (2) Set bits SMD2 to SMD0 in the UiMR register to 000b (serial interface disabled).

- (3) Set bits SMD2 to SMD0 in the UiMR register to one of the following:

- 001b (clock synchronous serial I/O mode)

- 100b (UART mode, character length is 7 bits)

- 101b (UART mode, character length is 8 bits)

- 110b (UART mode, character length is 9 bits)

- (4) Set the TE bit in the UiC1 register to 1 (transmission enabled) and the RE bit to 1 (reception enabled).

# 3.2 I<sup>2</sup>C Mode

This section describes the modifications made to the specifications. I<sup>2</sup>C mode function descriptions have been revised. Refer to 4. "Special Mode 1 (I<sup>2</sup>C Mode)" for details on major changes.

#### 3.2.1 UiSMR4 Register

Bits in the UiSMR4 register are used in I<sup>2</sup>C mode. To set these bits to 1, preset the IICM bit in the UiSMR register to 1 (I<sup>2</sup>C mode). Do not set these bits to 1 when the IICM bit is 0.

Bits STAREQ, RSTAREQ, STPREQ, STSPSEL, and SCLHI are used in master mode of I<sup>2</sup>C mode. Set the STSPSEL bit to 1 (select start condition/stop condition generate circuit) after setting the STARREQ, RSTAREQ, or STPREQ bit to 1 (start).

Bits ACKD, ACKC, and SWC9 are used in slave mode of I<sup>2</sup>C mode.

#### 3.2.2 UiBRG Register

Set the UiBRG register to a value of 03h or greater in I<sup>2</sup>C mode.

#### 3.2.3 UiSMR3 Register

Set the CKPH bit in the UiSMR3 register to 1 (with clock delay) in I<sup>2</sup>C mode.

#### 3.2.4 Additional Notes

Notes listed below have been added.

# 3.2.4.1 Low/High-level Input Voltage and Low-level Output Voltage

The low-level input voltage, high-level input voltage, and low-level output voltage differ from the I<sup>2</sup>C-bus specification.

Refer to the recommended operating conditions for I/O ports which share the pins with SCL and SDA.

I<sup>2</sup>C-bus specification High level input voltage ( $V_{IH}$ ) = min. 0.7  $V_{CC}$ Low level input voltage ( $V_{II}$ ) = max. 0.3  $V_{CC}$

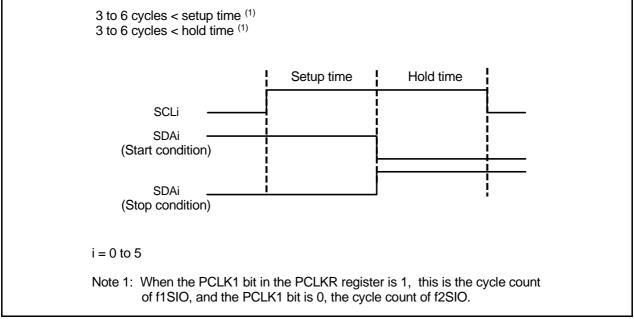

# 3.2.4.2 Setup and Hold Times When Generating a Start/Stop Condition

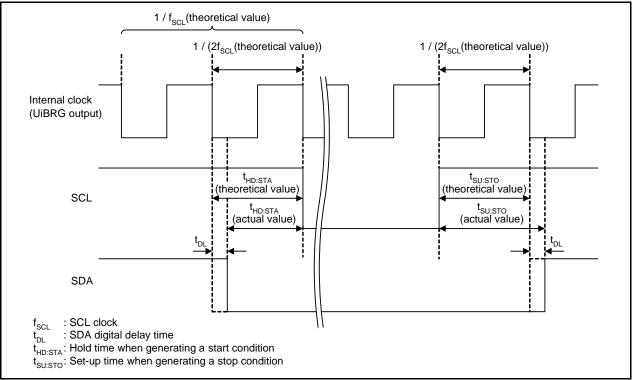

When generating a start condition, the hold time ( $t_{HD}$ :STA) is a half cycle of the SCL clock. When generating a stop condition, the setup time ( $t_{SU}$ :STO) is a half cycle of the SCL clock.

When the SDA digital delay function is enabled, take delay time into consideration.

The following shows a calculation example of hold and setup times when generating a start/stop condition.

Calculation example when setting 100 kbps

- UiBRG count source: f1 = 20 MHz

- UiBRG register setting value: n = 100 1

- SDA digital delay setting value: DL2 to DL0 are 101b (5 or 6 cycles of UiBRG count source)

$f_{SCI}$  (theoretical value) = f1 / (2(n+1)) = 20 MHz / (2 × (99 + 1)) = 100 kbps

$t_{DL}$  = delay cycle count / f1 = 6 / 20 MHz = 0.3  $\mu$ s

$t_{HD:STA}$  (theoretical value) = 1 / (2 $f_{SCL}$  (theoretical value)) = 1 / (2 × 100 kbps) = 5  $\mu$ s

$t_{\text{SU:STO}}$  (theoretical value) = 1 / (2 $f_{\text{SCL}}$  (theoretical value)) = 1 / (2 × 100 kbps) = 5 µs

$f_{HD:STA}$  (actual value) =  $t_{HD:STA}$  (theoretical value) -  $t_{DL}$  = 5 µs - 0.3 µs = 4.7 µs

$f_{SU:STO}$  (actual value) =  $t_{SU:STO}$  (theoretical value) +  $t_{DL}$  = 5 µs + 0.3 µs = 5.3 µs

# 3.2.4.3 Restrictions on the Bit Rate When Using the UiBRG Count Source

In I<sup>2</sup>C mode, set the UiBRG register to a value of 03h or greater.

A maximum of three UiBRG count source cycles are necessary until the internal circuit acknowledges the SCL clock level. The connectable I<sup>2</sup>C-bus bit rate is one third or less than the UiBRG count source speed. If a value between 00h to 02h is set to the UiBRG register, bit slippage may occur.

#### 3.2.4.4 Restart Condition in Slave Mode

When a restart condition is detected in slave mode, the successive processes may not be executed correctly. In slave mode, do not use a restart condition.

#### 3.2.4.5 Requirements to Start Transmission/Reception in Slave Mode

When transmission/reception is started in slave mode and the TXEPT bit in the UiC0 register is 1 (no data present in transmit register), meet the last requirement when the external clock is high.

Requirements to start transmission (in no particular order):

- The TE bit in the UiC1 register is 1 (transmission enabled).

- The TI bit in the UiC1 register is 0 (data present in the UiTB register).

- •Requirements to start reception (in no particular order):

- The RE bit in the UiC1 register is 1 (reception enabled).

- The TE bit in the UiC1 register is 1 (transmission enabled).

- The TI bit in the UiC1 register is 0 (data present in the UiTB register).

#### 3.3 Special Mode 2

Use special mode 2 in master mode. Do not use special mode 2 in slave mode (external clock). Set the CKDIR bit in the UiMR register to 0 (internal clock) in special mode 2.

However, slave mode can be used under certain conditions. An application note for this is being prepared. Serial Interface Special Mode 2 (Slave Transmission) (REJ05B1472-0100)

# 4. Special Mode 1 (I<sup>2</sup>C Mode)

# 4.1 Detecting Start and Stop Conditions

Start and stop conditions are detected by their respective detectors.

Whether a start or a stop condition has been detected is determined.

A start condition detect interrupt request is generated when the SDAi pin changes state from high to low while the SCLi pin is in the high state. A stop condition detect interrupt request is generated when the SDAi pin changes state from low to high while the SCLi pin is in the high state.

Because the start and stop condition detect interrupts share the interrupt control register and vector, check the BBS bit in the UiSMR register to determine which interrupt source is requesting the interrupt.

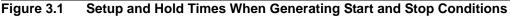

To detect a start or stop condition, both the set-up and hold times require at least six cycles of the BRGi count source as shown in Figure 4.1. To meet the condition for the Fast-mode specification, the BRGi count source must be at least 10 MHz.

Figure 4.1 Detecting Start and Stop Conditions

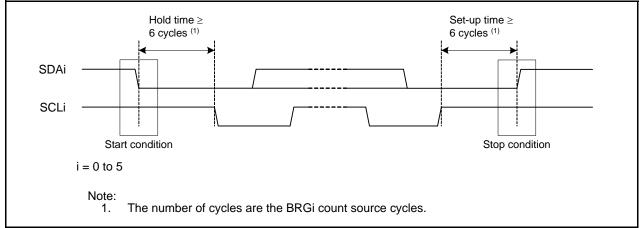

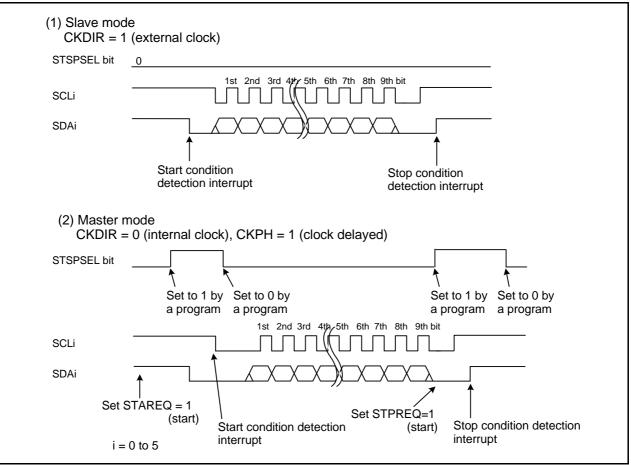

# 4.2 Generating Start and Stop Conditions

A start condition is generated by setting the STAREQ bit in the UiSMR4 register (i = 0 to 5) to 1 (start).

A restart condition is generated by setting the RSTAREQ bit in the UiSMR4 register to 1 (start). A stop condition is generated by setting the STPREQ bit in the UiSMR4 register to 1 (start).

The output procedure is described below.

- (1) Set the STAREQ bit, RSTAREQ bit or STPREQ bit to 1 (start).

- (2) Set the STSPSEL bit in the UiSMR4 register to 1 (output).

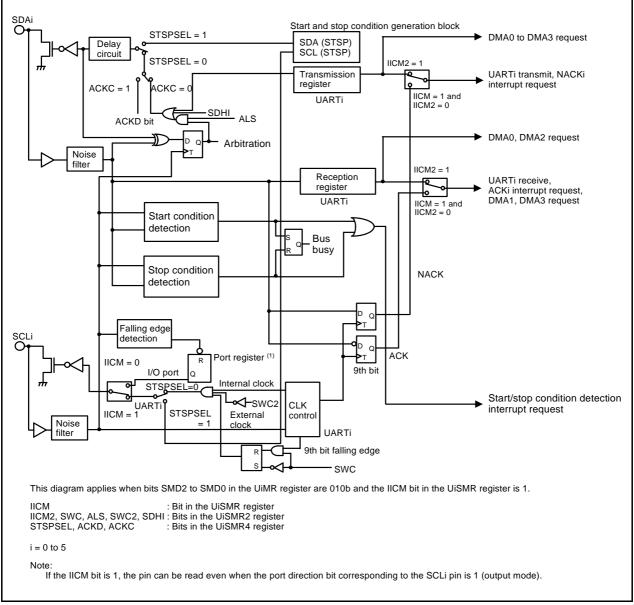

The functions of the STSPSEL bit are shown in Table 4.1 and Figure 4.2.

| Function                                                       | STSPSEL = 0                                                                                                                                                                | STSPSEL = 1                                                                          |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Output of pins SCLi and<br>SDAi                                | Output of transmit/receive clock and<br>data<br>Output of start/stop condition is<br>accomplished by a program using<br>ports (not automatically generated in<br>hardware) | Output of a start/stop condition<br>according to bits STAREQ,<br>RSTAREQ, and STPREQ |

| Start/stop condition<br>Interrupt request<br>generation timing | Detection of start/stop condition                                                                                                                                          | Completion of generating start/stop condition                                        |

#### 4.3 Arbitration

The MCU determines whether the transmit data matches data input to the SDAi pin on the rising edge of SCLi. If it does not match the input data, arbitration takes place at the SDAi pin by stopping data output.

The ABC bit in the UiSMR register (i = 0 to 5) determines the update timing for the ABT bit in the UiRB register. When the ABC bit is 0 (update per bit), the ABT bit becomes 1 as soon as a data discrepancy is detected. If not detected, the ABT bit becomes 0. When the ABC bit is 1 (update per byte), the ABT bit becomes 1 on the falling edge of the eighth bit of SCLi if any discrepancy is detected. In this ABC bit setting, the ABT bit should be set to 0 to start the next 1-byte transmission/reception.

When the ALS bit in the UiSMR2 register is set to 1 (SDA output stop enabled), an arbitration lost occurs. As soon as the ABT bit becomes 1, the SDAi pin becomes high-impedance.

#### 4.4 SCL Control and Clock Synchronization

Data transmission/reception in I<sup>2</sup>C mode uses the transmit/receive clock. The clock speed increase makes it difficult to secure the required time for ACK generation and data transmit procedure. The I<sup>2</sup>C mode supports a function of wait-state insertion to secure this required time and a function of clock synchronization with a wait-state inserted by other devices.

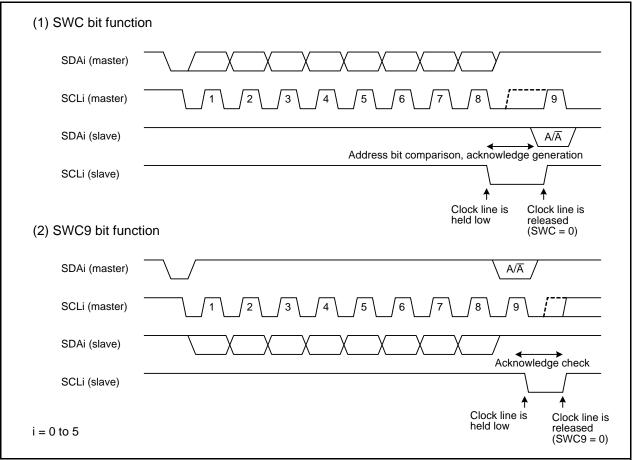

The SWC bit in the UiSMR2 register (i = 0 to 5) is used to insert a wait-state for ACK generation. When the SWC bit is set to 1 (the SCLi pin is held low after the eighth bit of SCLi is received), the SCLi pin is held low on the falling edge of the eighth bit of SCLi. When the SWC bit is set to 0 (no wait-state/wait-state cleared), the SCLi line is released.

When the SWC2 bit in the UiSMR2 register is set to 1 (the SCLi pin is held low), the SCLi pin is forced low even during transmission or reception. When the SWC2 bit is set to 0 (transmit/receive clock is output at the SCLi pin), the SCLi line is released to output the transmit/receive clock.

The SWC9 bit in the UiSMR4 register is used to insert a wait-state for checking received acknowledge bits. While the CKPH bit in the UiSMR3 register is 1 (clock delayed), when the SWC9 bit is set to 1 (the SCLi pin is held low after the ninth bit of the SCLi is received), the SCLi pin is held low on the falling edge of the ninth bit of SCLi. When the SWC9 bit is set to 0 (no wait-state/wait-state cleared), the SCLi line is released.

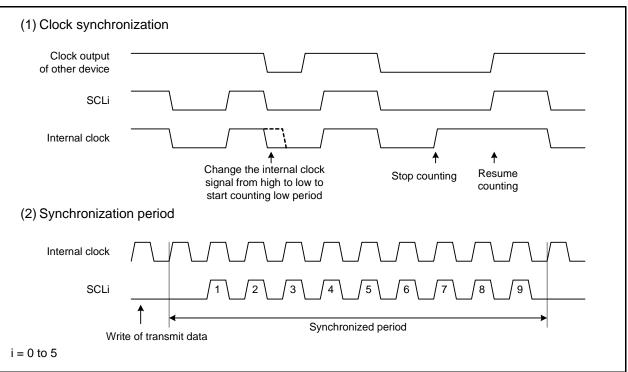

Figure 4.4 Inserting Wait-states Using Bits SWC and SWC9

The CSC bit in the UiSMR2 register synchronizes an internally generated clock with the clock applied to the SCLi pin. For example, if a wait-state is inserted from other devices, the two clocks are not synchronized. While the CSC bit is 1 (clock synchronization enabled) and the internal clock is held high, when a high at the SCLi pin changes to low, the internal clock becomes low in order to reload the UiBRG register value and resume counting. While the SCLi pin is held low, when the internal clock changes from low to high, the count is stopped until the SCLi pin becomes high. That is, the UARTi transmit/receive clock is the logical AND of the internal clock and SCLi. The synchronized period starts from one clock prior to the first synchronized clock and ends when the ninth clock is completed. The CSC bit can be set to 1 only when the CKDIR bit in the UiMR register is set to 0 (internal clock selected).

The SCLHI bit in the UiSMR4 register is used to leave the SCLi pin open when another master generates a stop condition while the master is performing a transmit/receive operation. While the SCLHI bit is set to 1 (output stopped), the SCLi pin is open (the pin is high-impedance) when a stop condition is detected and the clock output is stopped.

Figure 4.5 Clock Synchronization

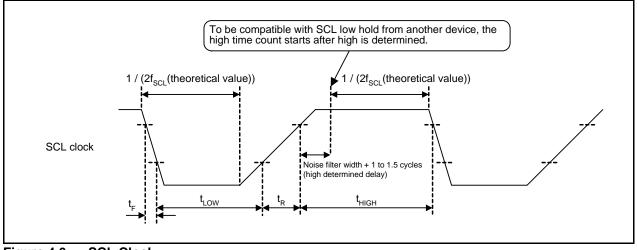

#### 4.5 SCL Clock Frequency

The SCL clock duty generated in I<sup>2</sup>C mode is 50%. The low-level width of the SCL clock is 1.25  $\mu$ s when the I<sup>2</sup>C-bus setting is Fast-mode maximum SCL clock (400 kbps). This value does not satisfy the Fast-mode I<sup>2</sup>C-bus specification (f<sub>LOW</sub> = minimum 1.3  $\mu$ s). Set the SCL clock to 384.6 kbps or less to satisfy the SCL clock low-level width of 1.3  $\mu$ s or more.

When the clock synchronous function (Figure 4.5 "Clock Synchronization") is enabled, there is a sampling delay of the noise filter plus 1 to 1.5 cycles of UiBRG count source.

There is also a delay of the SCL clock when high is determined and the SCL clock high width is extended. Therefore, the actual SCL clock becomes slower than SCL clock bit rate setting.

To calculate the effective value of SCL clock, take the SCL clock rise time  $(t_R)$  into consideration.

The following is an example of an SCL clock calculation.

Example of an effective value of SCL clock calculation at 384.6 kbps

- UiBRG count source: f1 = 20 MHz

- UiBRG register setting value: n = 26 1

- SCL clock rise time:  $t_{R} = 100 \text{ ns}$

- SCL clock fall time:  $t_F = 0$  ns

- Noise filter width:  $t_{NF} = 100 \text{ ns}^{(1)}$

- Sampling delay:  $t_{SD} = 1$  cycle

$$\begin{split} &f_{SCL} \ (\text{theoretical value}) = \text{f1} / (2(n + 1)) = 20 \ \text{MHz} / (2(25 + 1)) = 384.6 \ \text{kbps} \\ &t_{LOW} = 1 / (2f_{SCL} \ (\text{theoretical value})) = 1 / (2 \times 384.6 \ \text{kbps}) = 1.3 \ \mu\text{s} \\ &t_{\text{HIGH}} = 1 / (2f_{SCL} \ (\text{theoretical value})) + t_{\text{NF}} + (t_{SD} \times 1 / \text{f1}) \\ &= 1 / (2 \times 384.6 \ \text{kbps}) + 100 \ \text{ns} + (1 \times 1 / 20 \ \text{MHz}) \\ &= 1.45 \ \mu\text{s} \\ &f_{SCL} \ (\text{actual value}) = 1 / (t_{\text{F}} + t_{\text{LOW}} + t_{\text{R}} + t_{\text{HIGH}}) = 1 / (0 \ \text{ns} + 1.3 \ \mu\text{s} + 100 \ \text{ns} + 1.45 \ \mu\text{s}) \approx 350.8 \ \text{kbps} \end{split}$$

Note:

1. Maximum 200 ns.

#### 4.6 SDA Output Control

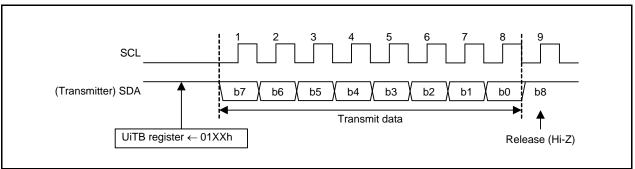

When transmitting byte data, the SDAi pin outputs transmit data for the first to eighth bits, and it is released to receive an acknowledgement for the ninth bit.

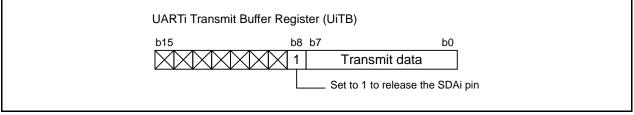

In I<sup>2</sup>C mode, set 9-bit data to the UiTB register. In 9-bit data, set the transmit data to bits b7 to b0 and set b8 to 1. By setting the UFORM bit in the UiC0 register to 1 (MSB first) and 9-bit data to the UiTB register, transmit data is output from the SDAi pin in the following order: b7, b6, b5, b4, b3, b2, b1, b0 and b8. As b8 is 1, the SDAi pin becomes high-impedance at the ninth bit and an acknowledgment can be received.

Figure 4.7 UiTB Register Setting (SDA Output)

Figure 4.8 Byte Data Transmission

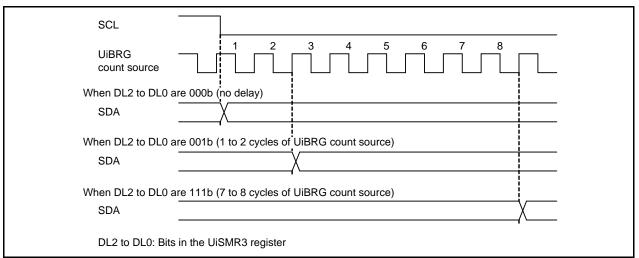

Set bits DL2 to DL0 in the UiSMR3 register to add no delays or a delay of one to eight UiBRG count source clock cycles to SDAi output.

Setting the SDHI bit in the UiSMR2 register to 1 (SDA output disabled) forcibly places the SDAi pin in a highimpedance state. Do not write to the SDHI bit at the rising edge of the UARTi transfer clock as the ABT bit may inadvertently become 1 (detected).

#### 4.7 SDA Digital Delay

When transferring data with the  $I^2C$ -bus, change the data while the SCL clock is low. When SDA is changed while the SCL clock is a high, the change is recognized as one of the corresponding conditions (see 3.2.4.2 "Setup and Hold Times When Generating a Start/Stop Condition").

This function delays output from the SDAi pin. By delaying the change of the SDA, the data can be changed while the SCL clock is low. This function is enabled by setting bits DL2 to DL0 in the UiSMR3 register to 001b to 111b, and disabled by setting them to 000b.

Figure 4.9 SDA Output Selection by Setting Bits DL2 to DL0

#### 4.8 SDA Input

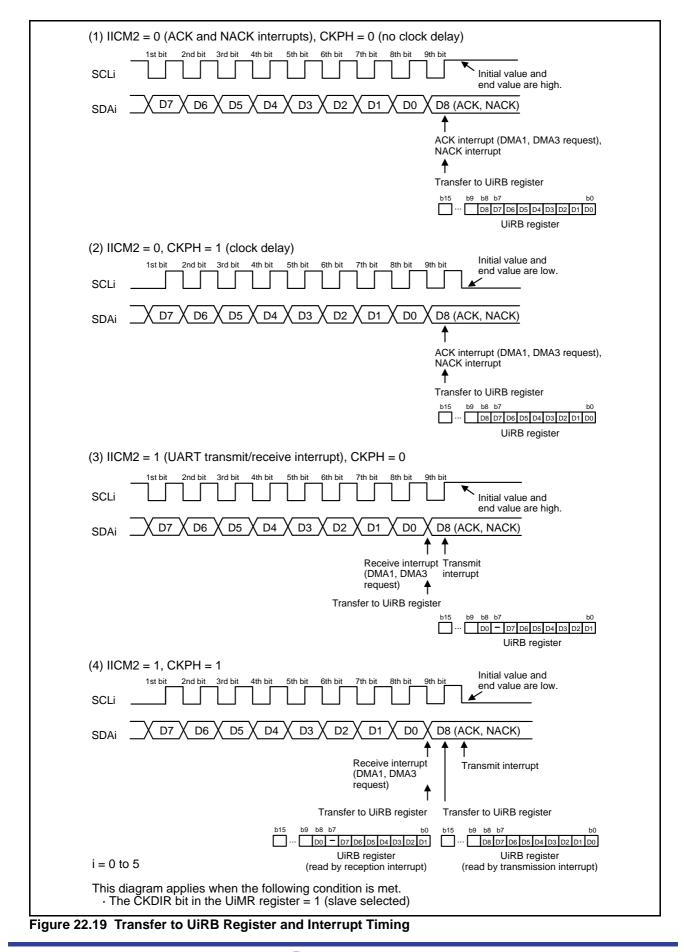

When the IICM2 bit in the UiSMR2 register (i = 0 to 5) is set to 0, the first 8 bits of received data (D7 to D0) are stored in bits 7 to 0 in the UiRB register and the ninth bit (ACK/NACK) is stored in bit 8.

When the IICM2 bit is 1, the first to seventh bits (D7 to D1) of the received data are stored in bits 6 to 0 in the UiRB register and the eighth bit (D0) is stored in bit 8 in the UiRB register. Even when the IICM2 bit is 1, if the CKPH bit in the UiSMR3 register is 1, the same data as when the IICM2 bit is 0 can be read. To read the data, read the UiRB register after the rising edge of ninth bit of the corresponding clock pulse.

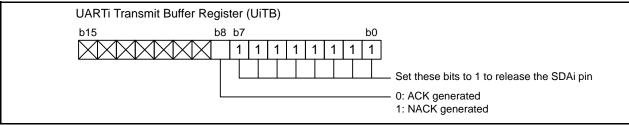

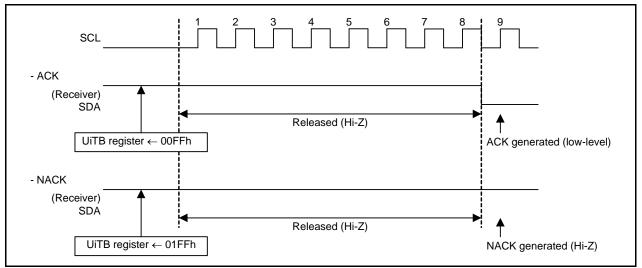

When receiving byte data, the SDAi pin is released for the first to eighth bits to receive data, and an acknowledgment is generated for the ninth bit. NACK is generated when the last byte data is received in master mode, or when the slave address does not match in slave mode. In all other cases, ACK is generated.

In I<sup>2</sup>C mode, set 9-bit data to the UiTB register. In 9-bit data, set FFh to b7 to b0 to release the SDAi pin and set b8 to 0 to generate ACK or 1 to generate NACK.

By setting 00FFh or 01FFh as 9-bit data to the UiTB register, the SDAi pin becomes high-impedance for the first to eighth bits, and data can be received. ACK or NACK is generated at the ninth bit.

Read the received data from the UiRB register. When the clock delay function is used, data transfer to the UiRB register occurs twice and each UiRB register value is different.

Figure 4.11 Byte Data Reception

# 4.9 ACK and NACK

When data is to be received in master mode, ACK is output after 8 bits are received by setting the UiTB register to 00FFh as dummy data. When the STSPSEL bit in the UiSMR4 register (i = 0 to 5) is set to 0 (serial I/O circuit selected) and the ACKC bit is set to 1 (ACK data output), the value of the ACKD bit is output at the SDAi pin. If the IICM2 bit is 0, a NACK interrupt request is generated when the SDAi pin is held high at the rising edge of the ninth bit of SCLi. An ACK interrupt request is generated when the SDAi pin is held low.

If the DMA request source is "UARTi receive interrupt request or ACK interrupt request", the DMA transfer is activated when ACK is detected.

# 4.10 Initialization of Transmission/Reception

Select the external clock as the transmit/receive clock when using this function.

If a start condition is detected while the STAC bit in the UiSMR2 register is 1 (initialize the circuit if the start condition is detected), the serial interface operates as follows:

- The transmit shift register is initialized, and the UiTB register value is transferred to the transmit shift register. Doing so starts the data transmission when the next clock pulse is applied. However, the UARTi output value does not change until the first bit of data is output synchronously with the input clock. It remains the same as when a start condition was detected.

- The receive shift register is initialized, and the serial interface starts receiving data when the next clock pulse is applied.

- The SWC bit becomes 1 (hold the SCLi pin low after the eighth bit of SCLi is received). Consequently, the SCLi pin is pulled low at the falling edge of the ninth clock pulse.

When UARTi transmission/reception is started using this function, the TI bit does not change.

When the UARTi initializing function is used in slave mode, UARTi is initialized automatically when a start condition is detected. Therefore, an interrupt is unnecessary for detecting a start condition.

# 5. Reference Documents

M16C/6C Group User's Manual: Hardware Rev.2.00 (R01UH0138EJ0200)

Application Notes Application notes indicated in 2. "Introduction" and application notes for other modes have been prepared.

The latest versions can be downloaded from the Renesas Electronics website.

Reference: the previous version of the UARTi document The previous version of UARTi document is attached at the end of this document.

# Website and Support

Renesas Electronics website http://www.renesas.com/

Inquiries http://www.renesas.com/inquiry

| Revision History | M16C/6C Group<br>Supplement for Serial Interface UARTi (i = 0 to 5) |

|------------------|---------------------------------------------------------------------|

| -                |                                                                     |

| Rev.   | Date       |      | Description          |

|--------|------------|------|----------------------|

| ittev. | Date       | Page | Summary              |

| 1.00   | 2011.03.09 | _    | First edition issued |

|        |            |      |                      |

All trademarks and registered trademarks are the property of their respective owners.

### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or otherwise.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which is not intended without the prior written consent of Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- \*Specific\*: Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

SALES OFFICES

Refer to "http://www.renesas.com/" for the latest and detailed information

**Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc.

2880 Scott Boulevard Santa Clara, CA 95050-2554, U.S.A.

Tel: +1-408-588-6000, Fax: +1-408-588-6130

Renesas Electronics Canada Limited

1101 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada

Tel: +1-905-898-5441, Fax: +1-905-898-3220

Renesas Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tel: +4-902-585-100, Fax: +44+1628-585-900

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Disseldorf, Germany

Tel: +49-211-65030, Fax: +449-211-6503-1327

Renesas Electronics China) Co., Ltd.

Th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China

Tel: +86-10-8235-7679

Renesas Electronics Changhai) Co., Ltd.

Unit 204, 205, AZIA Center, No. 1233 Lujiazui Bing Rd., Pudong District, Shanghai 200120, China

Tel: +862-869-7818, Fax: +862-16887-7858 / -7886

Renesas Electronics Hong Kong Limited

Unit 101-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +886-24175-9600

Renesas Electronics Singapore Pte. Ltd.

1 harbourfront Avenue, 406-10, keppel Bay Tower, Singapore 098632

Tel: +862-24175-9600, Fax: +868 2-46175-9670

Renesas Electr

# 22. Serial Interface UARTi (i = 0 to 5)

### 22.1 Introduction

Each UARTi has a dedicated timer to generate a transmit/receive clock, so it operates independently of the others.

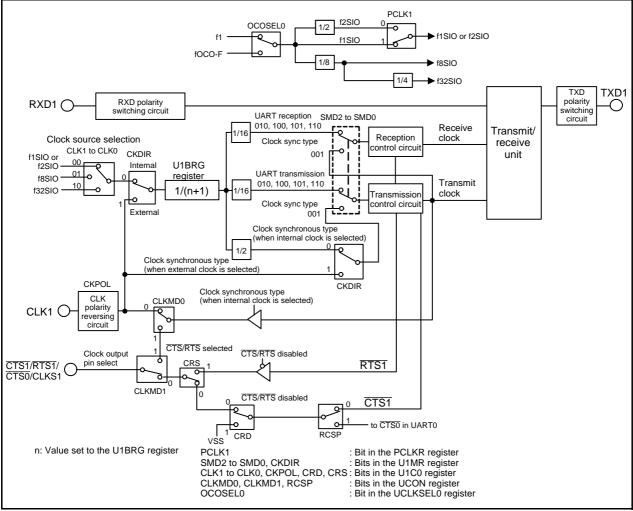

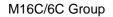

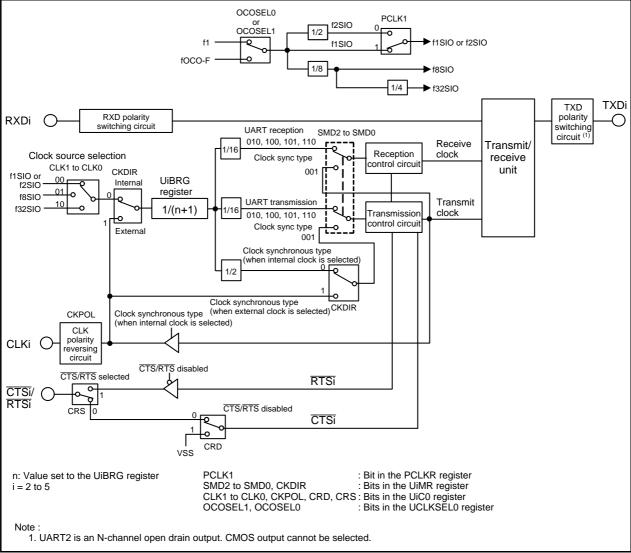

Table 22.1 lists Specifications of UARTi (i = 0 to 5), Table 22.2 lists Specification Difference in UART0 to UART5, Figure 22.1 to Figure 22.3 show UARTi Block Diagram, and Figure 22.4 shows UARTi Transmit/ Receive Unit Block Diagram.

Table 22.1 Specifications of UARTi (i = 0 to 5)

| Item             | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operational mode | <ul> <li>Clock synchronous serial I/O mode</li> <li>Clock asynchronous serial I/O mode (UART mode)</li> <li>Special mode 1 (I<sup>2</sup>C mode)</li> <li>Special mode 2 The simplified I<sup>2</sup>C-bus interface is supported.</li> <li>Special mode 3 (bus collision detection function, IE mode) A 1-byte wave of the UART mode approximates 1-bit of the IEBus.</li> <li>Special mode 4 (SIM mode) UART2 is available. The SIM interface is supported.</li> </ul> |

#### Table 22.2 Specification Difference in UART0 to UART5

| Mode                                              | UART0  | UART1   | UART2     | UART3  | UART4   | UART5         |

|---------------------------------------------------|--------|---------|-----------|--------|---------|---------------|

| Clock synchronous serial I/O mode                 | Avai   | lable   | Available | Avai   | lable   | Available     |

| Clock asynchronous serial I/O mode<br>(UART mode) | Avai   | lable   | Available | Avai   | lable   | Available     |

| Special mode 1 (I <sup>2</sup> C mode)            | Avai   | lable   | Available | Avai   | lable   | Available     |

| Special mode 2                                    | Avai   | lable   | Available | Avai   | lable   | Available     |

| Special mode 3 (IE mode)                          | Avai   | lable   | Available | Avai   | lable   | Available     |

| Special mode 4 (SIM mode)                         | Not av | ailable | Available | Not av | ailable | Not available |

| Memory expansion mode or<br>microprocessor mode   |        | Can be  | used      | Do no  | ot use  | Can be used   |

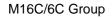

Figure 22.1 UART0 Block Diagram

Figure 22.2 UART1 Block Diagram

Figure 22.3 Block Diagram of UART2 to UART5

Figure 22.4 UARTi Transmit/Receive Unit Block Diagram

#### 22.2 Registers

Table 22.3 and Table 22.4 list registers associated with UART0 to UART5.

Set the OCOSEL0 or OCOSEL1 bit in the UCLKSEL0 register before setting other registers associated with UART0 to UART5. After changing the OCOSEL0 or OCOSEL1 bit, set other registers associated with UART0 to UART5 again.

Refer to "Registers Used and Settings" in each mode for the settings of registers and bits.

| Address        | Register                                  | Symbol   | Reset Value |

|----------------|-------------------------------------------|----------|-------------|

| 0012h          | Peripheral Clock Select Register          | PCLKR    | 0000 0011b  |

| 0244h          | UARTO Special Mode Register 4             | U0SMR4   | 00h         |

| 0245h          | UARTO Special Mode Register 3             | U0SMR3   | 000X 0X0Xb  |

| 0246h          | UARTO Special Mode Register 2             | U0SMR2   | X000 0000b  |

| 0247h          | UARTO Special Mode Register               | U0SMR    | X000 0000b  |

| 0248h          | UART0 Transmit/Receive Mode Register      | U0MR     | 00h         |

| 0249h          | UART0 Bit Rate Register                   | U0BRG    | XXh         |

| 024Ah<br>024Bh | UART0 Transmit Buffer Register            | U0TB     | XXh<br>XXh  |

| 024Ch          | UART0 Transmit/Receive Control Register 0 | U0C0     | 0000 1000b  |

| 024Dh          | UART0 Transmit/Receive Control Register 1 | U0C1     | 00XX 0010b  |

| 024Eh<br>024Fh | UART0 Receive Buffer Register             | UORB     | XXh<br>XXh  |

| 0250h          | UART Transmit/Receive Control Register 2  | UCON     | X000 0000b  |

| 0252h          | UART Clock Select Register                | UCLKSEL0 | X0h         |

| 0254h          | UART1 Special Mode Register 4             | U1SMR4   | 00h         |

| 0255h          | UART1 Special Mode Register 3             | U1SMR3   | 000X 0X0Xb  |

| 0256h          | UART1 Special Mode Register 2             | U1SMR2   | X000 0000b  |

| 0257h          | UART1 Special Mode Register               | U1SMR    | X000 0000b  |

| 0258h          | UART1 Transmit/Receive Mode Register      | U1MR     | 00h         |

| 0259h          | UART1 Bit Rate Register                   | U1BRG    | XXh         |

| 025Ah<br>025Bh | UART1 Transmit Buffer Register            | U1TB     | XXh<br>XXh  |

| 025Ch          | UART1 Transmit/Receive Control Register 0 | U1C0     | 0000 1000b  |

| 025Dh          | UART1 Transmit/Receive Control Register 1 | U1C1     | 00XX 0010b  |

| 025Eh<br>025Fh | UART1 Receive Buffer Register             | U1RB     | XXh<br>XXh  |

| 0264h          | UART2 Special Mode Register 4             | U2SMR4   | 00h         |

| 0265h          | UART2 Special Mode Register 3             | U2SMR3   | 000X 0X0Xb  |

| 0266h          | UART2 Special Mode Register 2             | U2SMR2   | X000 0000b  |

| 0267h          | UART2 Special Mode Register               | U2SMR    | X000 0000b  |

| 0268h          | UART2 Transmit/Receive Mode Register      | U2MR     | 00h         |

| 0269h          | UART2 Bit Rate Register                   | U2BRG    | XXh         |

| 026Ah          | LIAPT2 Transmit Buffor Posicitor          |          | XXh         |

| 026Bh          | UART2 Transmit Buffer Register            | U2TB     | XXh         |

| 026Ch          | UART2 Transmit/Receive Control Register 0 | U2C0     | 0000 1000b  |

| 026Dh          | UART2 Transmit/Receive Control Register 1 | U2C1     | 0000 0010b  |

| 026Eh<br>026Fh | UART2 Receive Buffer Register             | U2RB     | XXh<br>XXh  |

| 0284h          | UART5 Special Mode Register 4             | U5SMR4   | 00h         |

| 0285h          | UART5 Special Mode Register 3             | U5SMR3   | 000X 0X0Xb  |

#### Table 22.3 Register Structure (1/2)

| Address        | Register                                  | Symbol | Reset Value |

|----------------|-------------------------------------------|--------|-------------|

| 0286h          | UART5 Special Mode Register 2             | U5SMR2 | X000 0000b  |

| 0287h          | UART5 Special Mode Register               | U5SMR  | X000 0000b  |

| 0288h          | UART5 Transmit/Receive Mode Register      | U5MR   | 00h         |

| 0289h          | UART5 Bit Rate Register                   | U5BRG  | XXh         |

| 028Ah<br>028Bh | UART5 Transmit Buffer Register            | U5TB   | XXh<br>XXh  |

| 028Ch          | UART5 Transmit/Receive Control Register 0 | U5C0   | 0000 1000b  |

| 028Dh          | UART5 Transmit/Receive Control Register 1 | U5C1   | 0000 0010b  |

| 028Eh<br>028Fh | UART5 Receive Buffer Register             | U5RB   | XXh<br>XXh  |

| 0294h          | UART4 Special Mode Register 4             | U4SMR4 | 00h         |

| 0295h          | UART4 Special Mode Register 3             | U4SMR3 | 000X 0X0Xb  |

| 0296h          | UART4 Special Mode Register 2             | U4SMR2 | X000 0000b  |

| 0297h          | UART4 Special Mode Register               | U4SMR  | X000 0000b  |

| 0298h          | UART4 Transmit/Receive Mode Register      | U4MR   | 00h         |

| 0299h          | UART4 Bit Rate Register                   | U4BRG  | XXh         |

| 029Ah<br>029Bh | UART4 Transmit Buffer Register            | U4TB   | XXh<br>XXh  |

| 029Ch          | UART4 Transmit/Receive Control Register 0 | U4C0   | 0000 1000b  |

| 029Dh          | UART4 Transmit/Receive Control Register 1 | U4C1   | 0000 0010b  |

| 029Eh<br>029Fh | UART4 Receive Buffer Register             | U4RB   | XXh<br>XXh  |

| 02A4h          | UART3 Special Mode Register 4             | U3SMR4 | 00h         |

| 02A5h          | UART3 Special Mode Register 3             | U3SMR3 | 000X 0X0Xb  |

| 02A6h          | UART3 Special Mode Register 2             | U3SMR2 | X000 0000b  |

| 02A7h          | UART3 Special Mode Register               | U3SMR  | X000 0000b  |

| 02A8h          | UART3 Transmit/Receive Mode Register      | U3MR   | 00h         |

| 02A9h          | UART3 Bit Rate Register                   | U3BRG  | XXh         |

| 02AAh<br>02ABh | UART3 Transmit Buffer Register            | U3TB   | XXh<br>XXh  |

| 02ACh          | UART3 Transmit/Receive Control Register 0 | U3C0   | 0000 1000b  |

| 02ADh          | UART3 Transmit/Receive Control Register 1 | U3C1   | 0000 0010b  |

| 02AEh<br>02AFh | UART3 Receive Buffer Register             | U3RB   | XXh<br>XXh  |

# Table 22.4 Register Structure (2/2)

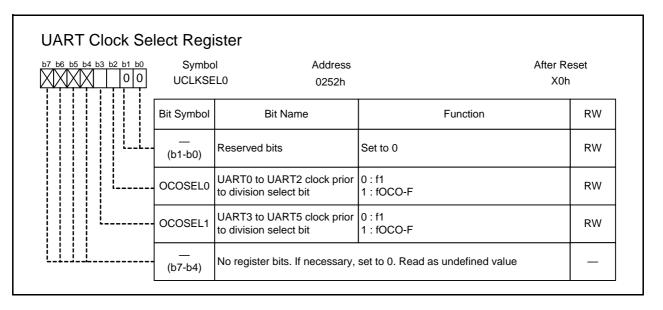

# 22.2.1 UART Clock Select Register (UCLKSEL0)

OCOSEL0 (UART0 to UART2 clock prior to division select bit) (b2) OCOSEL1 (UART3 to UART 5 clock prior to division select bit) (b3)

Set bits OCOSEL0 and OCOSEL1 while transmission/reception of UART0 to UART5 stops. Set the OCOSEL0 or OCOSEL1 bit before setting other registers associated with UART0 to UART5. After changing the OCOSEL0 or OCOSEL1 bit, set other registers associated with UART0 to UART5 again.

# 22.2.2 Peripheral Clock Select Register (PCLKR)

| b7     b6     b5     b4     b3     b2     b1     b0       0     0     0     0     0     0 | Symbol<br>PCLKR | Addre<br>0012                                                                                                                                            |                                                                         | After Reset<br>0000 0011b |

|-------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------|

|                                                                                           | Bit Symbol      | Bit Name                                                                                                                                                 | Function                                                                | RW                        |

|                                                                                           | PCLK0           | Timers A, B and S clock select bit<br>(clock source for timers A, B and S,<br>the dead time timer, and muliti-<br>master I <sup>2</sup> C-bus interface) | 0: f2TIMAB / f2IIC / f2TIMS<br>1: f1TIMAB / f1IIC / f1TIMS              | RW                        |

|                                                                                           | PCLK1           | SI/O clock select bit<br>(clock source for UART0 to<br>UART5)                                                                                            | 0: f2SIO<br>1: f1SIO                                                    | RW                        |

|                                                                                           | <br>(b4-b2)     | Reserved bits                                                                                                                                            | Set to 0                                                                | RW                        |

|                                                                                           | PCLK5           | Clock output function<br>extension bit<br>(valid in single-chip mode)                                                                                    | 0: Selected by bits CM01 to CM00<br>in the CM0 register<br>1: Output f1 | RW                        |

|                                                                                           | <br>(b7-b6)     | Reserved bits                                                                                                                                            | Set to 0                                                                | RW                        |

Set the PRC0 bit in the PRCR register to 1 (write enabled) before the PCLKR register is rewritten.

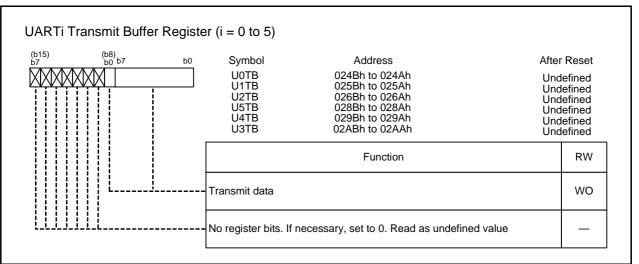

# 22.2.3 UARTi Transmit Buffer Register (UiTB) (i = 0 to 5)

Use MOV instruction to write to this register.

When character bit is 9 bits long, write in 16-bit units, or write in 8-bit units in the order of high-order bytes to low-order bytes.

# 22.2.4 UARTi Receive Buffer Register (UiRB) (i = 0 to 5)

| 5) (b8)<br>b0 b7 b0 | Symt<br>UOR<br>U1R<br>U2R<br>U5R<br>U4R<br>U3R | B 024F<br>B 025F<br>B 026F<br>B 026F<br>B 028F<br>B 029F | ddress<br>h to 024Eh<br>h to 025Eh<br>h to 026Eh<br>h to 028Eh<br>h to 029Eh<br>ih to 02AEh | After Reset<br>Undefined<br>Undefined<br>Undefined<br>Undefined<br>Undefined<br>Undefined |

|---------------------|------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                     | Bit Symbol                                     | Bit Name                                                 | Function                                                                                    | RW                                                                                        |

|                     | <br>(b7-b0)                                    |                                                          | Receive data (D7 to D0)                                                                     | RO                                                                                        |

|                     | (b8)                                           |                                                          | Receive data (D8)                                                                           | RO                                                                                        |

|                     | <br>(b10-b9)                                   | No register bits. If necessary                           | set to 0. Read as undefined value                                                           | _                                                                                         |

|                     | АВТ                                            | Arbitration lost detect flag                             | 0 : Not detected<br>1 : Detected                                                            | RW                                                                                        |

| <br>     <br>       | OER                                            | Overrun error flag                                       | 0 : No overrun error<br>1 : Overrun error found                                             | RO                                                                                        |

|                     | FER                                            | Framing error flag                                       | 0 : No framing error<br>1 : Framing error found                                             | RO                                                                                        |

|                     | PER                                            | Parity error flag                                        | 0 : No parity error<br>1 : Parity error found                                               | RO                                                                                        |

|                     | SUM                                            | Error sum flag                                           | 0 : No error<br>1 : Error found                                                             | RO                                                                                        |

When bits SMD2 to SMD0 in the UiMR register is 100b, 101b or 110b, read in 16-bit units, or read in 8bit units in the order of high-order bytes to low-order bytes.

Bits FER and PER arranged in the high-order bytes become 0 when the lower bytes of the UiRB register are read.

If an overrun error occurs, the receive data of the UiRB register will be undefined.

#### ABT (Arbitration lost detect flag) (b11)

The ABT bit is set to 0 by a program. (It remains unchanged even if 1 is written.)

#### OER (Overrun error flag) (b12)

Condition to become 0:

- Bits SMD2 to SMD0 in the UiMR register are 000b (serial interface disabled).

- The RE bit in the UiC1 register is 0 (reception disabled).

Condition to become 1:

• The RI bit in the UiC1 register is 1 (data present in UiRB register), and the last bit of the next data is received.

#### FER (Framing error flag) (b13)

The FER bit is disabled when bits SMD2 to SMD0 are set to 001b (clock synchronous serial I/O mode) or to 010b (I<sup>2</sup>C mode). The read value is undefined.

Condition to become 0:

- Bits SMD2 to SMD0 in the UiMR register are 000b (serial interface disabled).

- The RE bit in the UiC1 register is 0 (reception disabled).

- The lower bytes of the UiRB register are read.

Condition to become 1:

• The set number of stop bits is not detected.

(detected when the received data is transferred from the UARTi receive register to the UiRB register.)

#### PER (Parity error flag) (b14)

The PER bit is disabled when bits SMD2 to SMD0 are set to 001b (clock synchronous serial I/O mode) or to 010b (I<sup>2</sup>C mode). The read value is undefined. Condition to become 0:

• Bits SMD2 to SMD0 in the UiMR register are 000b (serial interface disabled).

- The RE bit in the UiC1 register is 0 (reception disabled).

- The lower bytes of the UiRB register are read.

Condition to become 1:

• The number of 1s of the parity bit and character bit does not match the set value of the PRY bit in the UiMR register.

(detected when the received data is transferred from the UARTi receive register to the UiRB register.)

# SUM (Error sum flag) (b15)

The SUM bit is disabled when bits SMD2 to SMD0 are set to 001b (clock synchronous serial I/O mode) or to 010b (I<sup>2</sup>C mode). The read value is undefined.

Condition to become 0:

- Bits SMD2 to SMD0 in the UiMR register are 000b (serial interface disabled).

- The RE bit in the UiC1 register is 0 (reception disabled).

- All of bits PER, FER and OER are 0 (no error).

Condition to become 1:

• More than one of bits PER, FER or OER is 1 (error found).

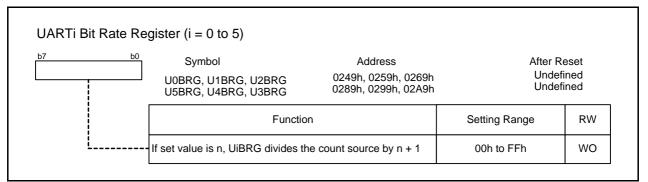

# 22.2.5 UARTi Bit Rate Register (UiBRG) (i = 0 to 5)

Write to the UiBRG register while serial interface is neither transmitting nor receiving. Use MOV instruction to write to the UiBRG register.

Write to the UiBRG register after setting bits CLK1 to CLK0 in the UiC0 register.

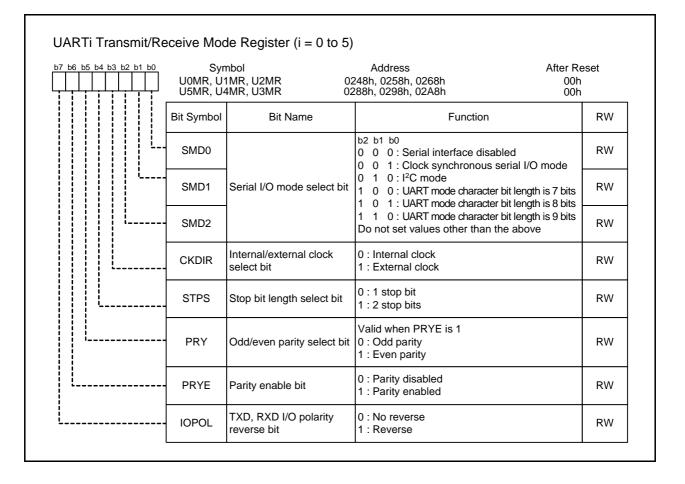

# 22.2.6 UARTi Transmit/Receive Mode Register (UiMR) (i = 0 to 5)

# 22.2.7 UARTi Transmit/Receive Control Register 0 (UiC0) (i = 0 to 5)

| 6 b5 b4 b3 b2 b1 b0 | Symbo      |                              |                                                                                                                                                                                                                                                                                      | er Reset<br>00 1000b |

|---------------------|------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                     | ,          |                              | .,                                                                                                                                                                                                                                                                                   | 00 1000b             |

|                     | Bit Symbol | Bit Name                     | Function                                                                                                                                                                                                                                                                             | RW                   |

|                     | CLK0       | UiBRG count source select    | b1 b0<br>0 0 : f1SIO or f2SIO selected<br>0 1 : f8SIO selected                                                                                                                                                                                                                       | RW                   |

|                     | CLK1       | bit                          | 1 0 : f32SIO selected<br>1 1 : Do not set                                                                                                                                                                                                                                            | RW                   |

|                     | CRS        | CTS/RTS function select bit  | Valid when CRD is 0<br>0 : CTS function selected<br>1 : RTS function selected                                                                                                                                                                                                        | RW                   |

|                     | TXEPT      | Transmit register empty flag | <ul> <li>0 : Data present in transmit register<br/>(transmission in progress)</li> <li>1 : No data present in transmit register<br/>(transmission completed)</li> </ul>                                                                                                              | RO                   |

| <u> </u>            | CRD        | CTS/RTS disable bit          | 0 : CTS/RTS function enabled<br>1 : CTS/RTS function disabled                                                                                                                                                                                                                        | RW                   |

|                     | NCH        | Data output select bit       | <ul> <li>0 : Pins TXDi/SDAi and SCLi are CMO:<br/>output</li> <li>1 : Pins TXDi/SDAi and SCLi are N-cha<br/>open-drain output</li> </ul>                                                                                                                                             | P\//                 |

|                     | CKPOL      | CLK polarity select bit      | <ul> <li>0: Transmit data is output at the falling<br/>edge of transmit/receive clock and<br/>receive data is input at the rising ed</li> <li>1: Transmit data is output at the rising<br/>edge of transmit/receive clock and<br/>receive data is input at the falling ed</li> </ul> | RW                   |

|                     | UFORM      | Bit order select bit         | 0 : LSB first<br>1 : MSB first                                                                                                                                                                                                                                                       | RW                   |

#### CLK1 to CLK0 (UiBRG count source select bit) (b1-b0)

When bits CLK1 to CLK0 are 00b (f1SIO or f2SIO selected), select f1SIO or f2SIO by the PCLK1 bit in the PCLKR register.

Set bits CLK1 to CLK0 after setting registers UCLKSEL0 and PCLKR.

If bits CLK1 to CLK0 are changed, set the UiBRG register.

# CRS (CTS/RTS function select bit) (b2)

CTS1/RTS1 can be used when the CLKMD1 bit in the UCON register is 0 (CLK output is only from CLK1) and the RCSP bit in the UCON register is 0 (CTS0/RTS0 not separated).

# CRD (CTS/RTS disable bit) (b4)

When the CRD bit is 1 (CTS/RTS function disabled), the CTSi/RTSi pin can be used as an I/O port.

#### NCH (Data output select bit) (b5)

TXD2/SDA2 and SCL2 are N-channel open drain outputs. They cannot be set to CMOS output. Nothing is assigned in the NCH bit in the U2C0 register. If necessary, set to 0.

This function is used to set P-channel transistor of the COMS output buffer always off, but not to change pins TXDi/SDAi and SCLi to open drain output completely.

Check electrical characteristics for the input voltage range.

#### UFORM (Bit order select bit) (b7)

The UFORM bit is enabled when bits SMD2 to SMD0 in the UiMR register are 001b (clock synchronous serial I/O mode), or 101b (UART mode, 8-bit character data).

Set the UFORM bit to 1 when bits SMD2 to SMD0 are 010b (I<sup>2</sup>C mode), and to 0 when bits SMD2 to SMD0 are 100b (UART mode, 7-bit character data) or 110b (UART mode, 9-bit character data).

# 22.2.8 UARTi Transmit/Receive Control Register 1 (UiC1) (i = 0 to 5)

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbol<br>U0C1, U10                                                      | Addre:<br>1 024Dh, 0                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | After Reset<br>00XX 0010b                                                      |

|-------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|                         | Bit Symbol                                                               | Bit Name                                                                                                                                                                                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RW                                                                             |

|                         | TE                                                                       | Transmit enable bit                                                                                                                                                                                                   | 0 : Transmission disabled<br>1 : Transmission enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RW                                                                             |

|                         | TI                                                                       | Transmit buffer empty flag                                                                                                                                                                                            | 0 : Data present in UiTB register<br>1 : No data present in UiTB register                                                                                                                                                                                                                                                                                                                                                                                                                                              | RO                                                                             |

|                         | RE                                                                       | Receive enable bit                                                                                                                                                                                                    | 0 : Reception disabled<br>1 : Reception enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RW                                                                             |

|                         | RI                                                                       | Receive complete flag                                                                                                                                                                                                 | 0 : No data present in UiRB register<br>1 : Data present in UiRB register                                                                                                                                                                                                                                                                                                                                                                                                                                              | RO                                                                             |

|                         | <br>(b5-b4)                                                              | No register bits. If necessary,                                                                                                                                                                                       | set to 0. Read as undefined value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                              |

|                         | UiLCH                                                                    | Data logic select bit                                                                                                                                                                                                 | 0 : No reverse<br>1 : Reverse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RW                                                                             |

|                         | UiERE                                                                    | Error signal output enable bit                                                                                                                                                                                        | 0 : Output disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RW                                                                             |

|                         | t/Receive<br>Symbol                                                      | e Control Register 1                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | After Reset                                                                    |

|                         | Symbol                                                                   | Addre                                                                                                                                                                                                                 | (i = 2 to 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | After Reset                                                                    |

|                         | Symbol<br>U2C1<br>U5C1, U                                                | Addre:<br>026Dr<br>J4C1, U3C1 028Dr                                                                                                                                                                                   | (i = 2 to 5)<br>ss<br>h, 029Dh, 02ADh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | After Reset<br>0000 0010b<br>0000 0010b                                        |

|                         | Symbol<br>U2C1                                                           | Addre<br>026Dr                                                                                                                                                                                                        | (i = 2 to 5)<br>ss<br>h, 029Dh, 02ADh<br>Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | After Reset<br>0000 0010b                                                      |

|                         | Symbol<br>U2C1<br>U5C1, U                                                | Addre:<br>026Dr<br>J4C1, U3C1 028Dr                                                                                                                                                                                   | (i = 2 to 5)<br>ss<br>h, 029Dh, 02ADh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | After Reset<br>0000 0010b<br>0000 0010b                                        |

|                         | Symbol<br>U2C1<br>U5C1, U<br>Bit symbol                                  | Addre:<br>026Dr<br>J4C1, U3C1 028Dr<br>Bit Name                                                                                                                                                                       | (i = 2 to 5)<br>ss<br>h, 029Dh, 02ADh<br>Function<br>0 : Transmission disabled                                                                                                                                                                                                                                                                                                                                                                                                                                         | After Reset<br>0000 0010b<br>0000 0010b<br>RW                                  |

|                         | Symbol<br>U2C1<br>U5C1, U<br>Bit symbol<br>TE                            | Addre<br>026Dr<br>028Dr<br>Bit Name<br>Transmit enable bit                                                                                                                                                            | (i = 2 to 5)<br>ss<br>b, 029Dh, 02ADh<br>Function<br>0 : Transmission disabled<br>1 : Transmission enabled<br>0 : Data present in UiTB register                                                                                                                                                                                                                                                                                                                                                                        | After Reset<br>0000 0010b<br>0000 0010b<br>RW<br>RW                            |

|                         | Symbol<br>U2C1<br>U5C1, U<br>Bit symbol<br>TE<br>TI                      | Addre:<br>026Dr<br>028Dr<br>Bit Name<br>Transmit enable bit<br>Transmit buffer empty flag                                                                                                                             | (i = 2 to 5)<br>ss<br>h, 029Dh, 02ADh<br>Function<br>0 : Transmission disabled<br>1 : Transmission enabled<br>0 : Data present in UiTB register<br>1 : No data present in UiTB register<br>0 : Reception disabled                                                                                                                                                                                                                                                                                                      | After Reset<br>0000 0010b<br>0000 0010b<br>RW<br>RW<br>RW<br>RO<br>RO          |

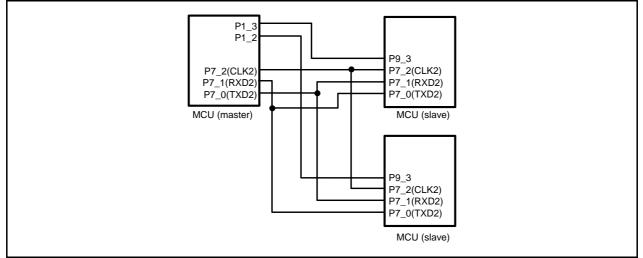

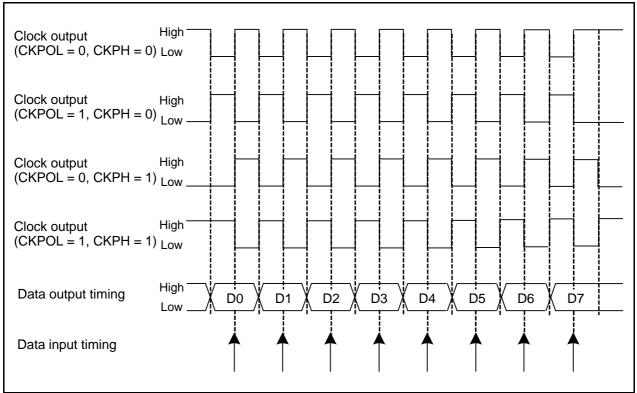

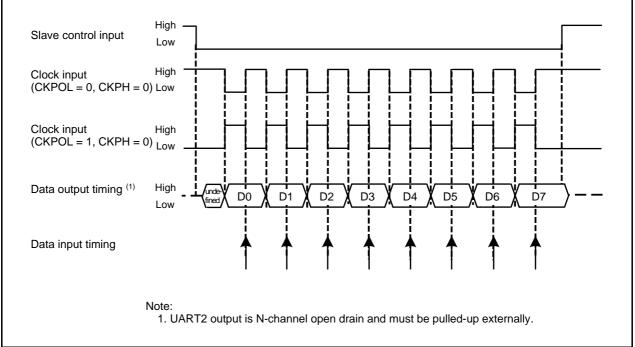

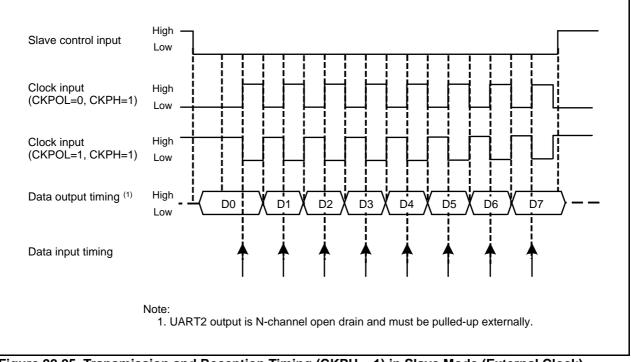

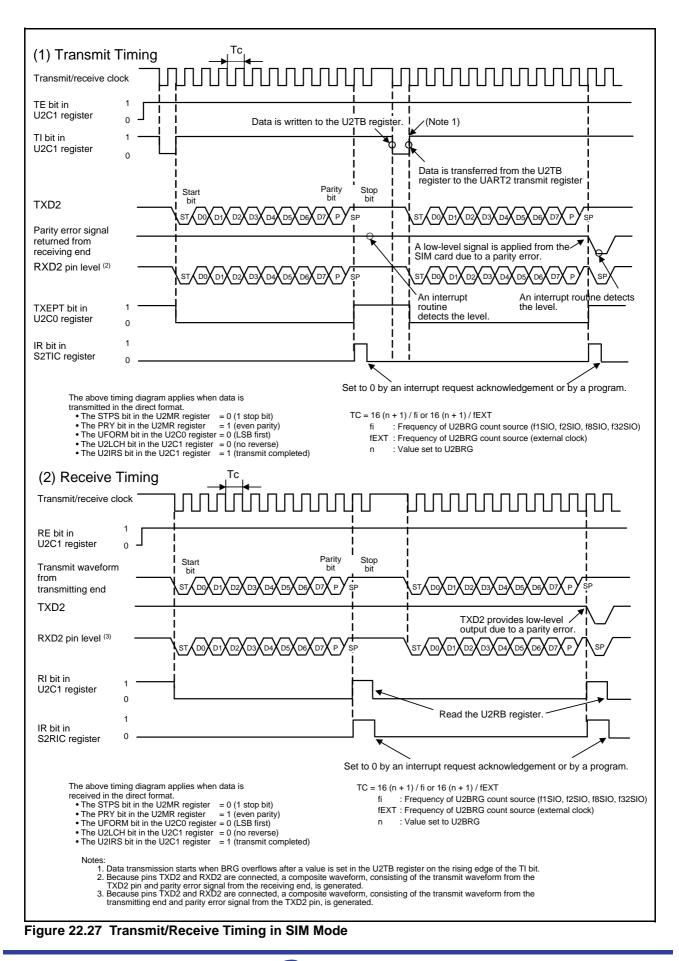

|                         | Symbol<br>U2C1<br>U5C1, U<br>Bit symbol<br>TE<br>TI<br>RE                | Addre:<br>026Dr<br>028Dr<br>Bit Name<br>Transmit enable bit<br>Transmit buffer empty flag<br>Receive enable bit                                                                                                       | (i = 2 to 5)<br>ss<br>h, 029Dh, 02ADh<br>Function<br>0 : Transmission disabled<br>1 : Transmission enabled<br>0 : Data present in UiTB register<br>1 : No data present in UiTB register<br>0 : Reception disabled<br>1 : Reception enabled<br>0 : No data present in UiRB register                                                                                                                                                                                                                                     | After Reset<br>0000 0010b<br>0000 0010b<br>RW<br>RW<br>RO<br>RO<br>RW          |