# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **H8S Family**

Example of Reprogramming On-Chip Flash Memory in the User Boot Mode "SCI (Clock Synchronous Mode)"

### Introduction

This Application Note is a compilation of sample reprogramming operations performed on the on-chip flash memory (user MAT) of the H8S/2556, 2552 or 2506 group MCU when operated in the user boot mode through clock synchronous communication using a serial communications interface (hereafter called SCI).

# **Target Device**

H8S/2500 Series H8S/2556 Group MCU

#### **Contents**

| 1. | Specifications                    | 2  |

|----|-----------------------------------|----|

| 2. | Description of Software Operation | 4  |

| 3. | Description of Registers          | 5  |

| 4. | Flowchart                         | 19 |

| 5. | Memory Map                        | 28 |

| 6. | Program Listings                  | 29 |

# 1. Specifications

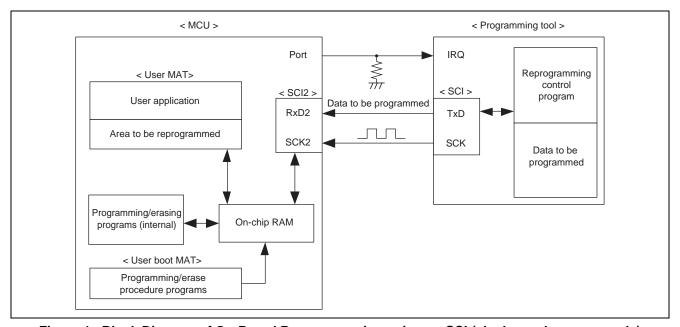

In this sample task, the H8S/2556 is started up in the user boot mode. Once the flash memory's EB10 through EB12 (3 blocks in all) have been erased, a signal requesting the transmission of data to be programmed is transmitted, and then the data received in response is programmed to the three blocks from EB10 through EB12. A serial communications interface (hereafter called SCI) and clock synchronous modes are used. To be more precise, the MCU uses the SCI2.

Figure 1 shows a block diagram of an on-board programming using the SCI (clock synchronous mode).

Figure 1 Block Diagram of On-Board Reprogramming using an SCI (clock synchronous mode)

#### 1.1 Operation Mode

User-boot-mode pin settings are shown as follows.

Table 1 Pin Settings

| Pin | Level |

|-----|-------|

| RES | 1     |

| MD0 | 1     |

| MD1 | 0     |

| MD2 | 0     |

# 1.2 Software Development Environment

For software development of this sample task, High-performance Embedded Workshop 3 (HEW3) Ver. 3.01.06.001 is used. For programming the software in the user boot mode, flash development tool kit (FDT) 2.0 is used.

### 1.3 Interface Specifications

The SCI interface specifications are shown below.

Table 2 Interface Specifications

| Item                | MCU                                 | Programming Tool      |

|---------------------|-------------------------------------|-----------------------|

| Channel used        | Channel 2 (SCI2) for reception only | For transmission only |

| Clock (SCK)         | Input                               | Output                |

| Communications mode | Clock synchronous                   |                       |

| Baud rate           | 1 Mbps                              |                       |

## 1.4 Control Specifications

The control specifications are shown below.

**Table 3 Control Specifications**

| Control                         | MCU                       | Programming Tool   |

|---------------------------------|---------------------------|--------------------|

| Programming data request signal | Port PJ0 (pin 53: output) | IRQ (falling edge) |

# 1.5 Description of Control Signal Behavior

In this sample task, a port is used for the programming data request signals. (Any interrupts are inhibited during flash-memory programming/erasing operations.)

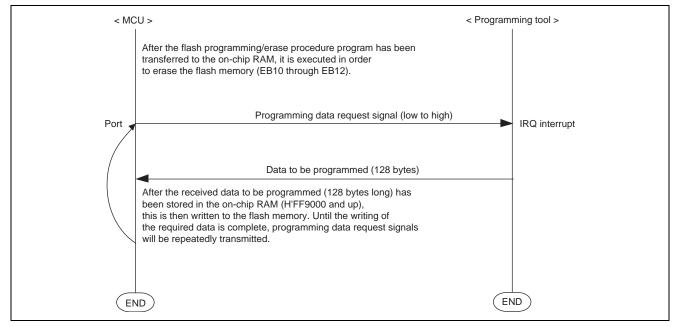

Figure 2 shows a series of control operations that take place up until the flash memory reprogramming is complete.

Please note that, no error handling procedure is defined. The programming tool used in this sample task is designed with the assumption that the reprogramming operation has ended normally in the absence of any programming data request signal from the MCU within a predetermined time period following transmission of a reprogramming start signal.

Figure 2 Control Operation

# 2. Description of Software Operation

This section provides an explanation of the software operations implemented in this sample task.

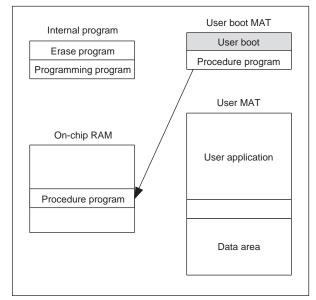

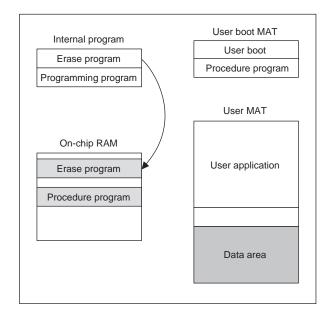

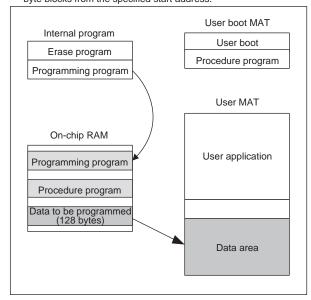

(1) Following system startup, the user boot program transfers the flash memory erase and write procedure programs into the onchip RAM, from where the procedure programs are then executed.

(2) The procedure program in the on-chip RAM then downloads the Internal program (for erasing) into the on-chip RAM, which subsequently erases the flash memory in the specified block area.

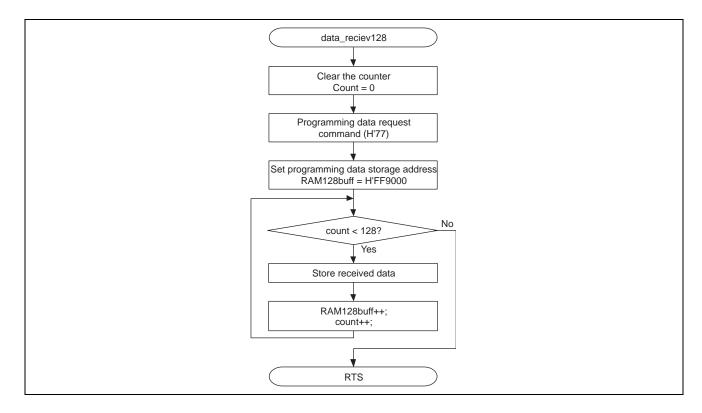

(3) The procedure program in the on-chip RAM downloads the Internal program (programming program) into the on-chip RAM, stores the programming data received from the programming tool into the on-chip RAM on a single occasion, and writes the data in 128byte blocks from the specified start address.

Figure 3 Description of Software Operation

### 3. Description of Registers

The registers and parameters for controlling flash memory units are described below.

In order to enable access to a register controlling flash memory other than RAMER (RAM emulation register), the SYSCR2's FLSHE bit must be set to 1 in a mode where the on-chip flash memory is operational. However, when FLSHE = 1, certain TPU control registers (H'FFFE80 to H'FFFEB1) become inaccessible. Always clear the FLSHE bit to 0 before accessing TPU registers.

### 3.1 Programming/Erase Interface Registers

This section describes the programming/erase interface registers. All are 8-bit registers allowing byte access only. These registers, save the FLER section of the FCCS register, are initialized upon power-on reset, as well as upon entering hardware standby, software standby mode, or watch modes, respectively. The FLER bit, however, is not initialized upon entering software standby or watch modes.

#### 3.1.1 Flash-Code-Control Status Register (FCCS) Initial value: H'80

The FCCS consists of a monitor bit for checking for errors during the programming/erasing of flash memory, and a bit for requesting download of an internal program.

Table 4 Flash-Code-Control Status Register (FCCS) Initial Value

|      | Bit  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Name | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7    | _    | R   | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |      |     | The value read from this bit is always 1. Always set this bit to 1 when writing as                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |      |     | well.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6, 5 | _    | R   | Reserved bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |      |     | The value read from these bits are always 0. Always set these bits to 0 when writing as well.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4    | FLER | R   | Flash memory error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |      |     | This is a bit for indicating that an error has occurred during flash memory programming/erase processing. If FLER = 1 is set to 1, the flash memory enters the error protection state. This bit is initialized at power-on reset or transition to the hardware standby mode. When FLER becomes 1, a high voltage will be applied inside the flash memory. Therefore, in order to prevent possible damage to the flash memory, release a reset after a reset input period of 100 $\mu$ s, which is longer than usual.  0: Flash memory is operating normally. |

|      |      |     | Programming/erase protection (error protection) on the flash memory is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |      |     | [Clearing condition] Cleared at the time of power-on reset or transition to the hardware standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |      |     | <ol> <li>Indicates that an error has occurred during flash memory programming or<br/>erase operation. Programming/erase protection (error protection) on the<br/>flash memory is enabled.</li> </ol>                                                                                                                                                                                                                                                                                                                                                         |

| 3 to | _    | R   | Reserved bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1    |      |     | The value read from these bits are always 0. Always set these bits to 0 when writing as well.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 4 Flash-Code-Control Status Register (FCCS) Initial Value (cont)

|     | Bit  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name | R/W  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0   | SCO  | (R)/ | Source program copy operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| O O | 300  | W W  | This is a request bit to download the internal programming/erase program into the on-chip RAM. If 1 is written to this bit, the internal program selected by the FPCS or FECS register will be automatically downloaded into the on-chip RAM area specified by the FTDAR register. In order to write 1 to this bit, it is necessary to clear the RAM emulation state, write H'A5 to the FKEY register, and execute the downloaded program on the on-chip RAM.  Immediately after writing 1 to this bit, always execute four NOP instructions.  Note that, when downloading is completed, this bit is cleared to zero and thus it is impossible to read a 1 state from this bit.  O: Downloads the internal programming/erase program to the on-chip RAM.  [Clearing condition] Cleared when a download completes.  1: Generates a request to download the internal programming/erase program into the on-chip RAM.  [Setting condition] The bit is set when 1 is written with all of the following conditions being satisfied.  (1) H'A5 has been written in the FKEY register.  (2) The code is being executed in the on-chip RAM. |

|     |      |      | (3) Not in the RAM emulation mode. (That is, the RAMS bit of RAMER is 0.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# 3.1.2 Flash Program Code Select Register (FPCS) Initial value: H'00

FPCS is a register to select/unselect the internal programming program to be downloaded.

Table 5 Flash Program Code Select Register (FPCS) Initial Value

|        | Bit  |     |                                                                                               |

|--------|------|-----|-----------------------------------------------------------------------------------------------|

| Bit    | Name | R/W | Description                                                                                   |

| 7 to 1 | _    | R   | Reserve bits                                                                                  |

|        |      |     | The value read from these bits are always 0. Always set these bits to 0 when writing as well. |

| 0      | PPVS | R/W | Program pulse verify                                                                          |

|        |      |     | Selects the programming program.                                                              |

|        |      |     | 0: Does not select the internal programming program.                                          |

|        |      |     | [Clearing condition] Cleared when a transfer completes.                                       |

|        |      |     | 1: Selects the internal programming program.                                                  |

### 3.1.3 Flash Erase Code Select Register (FECS) Initial value: H'00

FECS is a register to select/deselect the internal erase program to be downloaded.

#### Table 6 Flash Erase Code Select Register (FECS) Initial Value

|        | Bit  |     |                                                                                            |

|--------|------|-----|--------------------------------------------------------------------------------------------|

| Bit    | Name | R/W | Description                                                                                |

| 7 to 1 | _    | R   | Reserved bit                                                                               |

|        |      |     | The value read from this bit is always 0. Always set these bits to 0 when writing as well. |

| 0      | EPVB | R/W | Erase pulse verify block                                                                   |

|        |      |     | Selects the erase program.                                                                 |

|        |      |     | 0: Does not select the internal erase program.                                             |

|        |      |     | [Clearing condition] Cleared when a transfer completes.                                    |

|        |      |     | 1: Selects the internal erase program.                                                     |

## 3.1.4 Flash Key Code Register (FKEY) Initial Value: H'00

FKEY is a register for software protection that permits the download of an internal program and the programming/erasing of the flash memory. Unless a key code is entered before writing 1 to the SCO bit for downloading an internal program or before executing the downloaded programming/erase program, such processing cannot be performed.

Table 7 Flash Key Code Register (FKEY) Initial Value

|     | Bit  |     |                                                                                                                                       |

|-----|------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name | R/W | Description                                                                                                                           |

| 7   | K7   | R/W | Key code                                                                                                                              |

| 6   | K6   | R/W | Writing to the SCO bit is only enabled when H'A5 has been written into this                                                           |

| 5   | K5   | R/W | register. If any value other than H'A5 is written in the FKEY register, writing 1 to                                                  |

| 4   | K4   | R/W | the SCO bit is not allowed and, therefore, a program cannot be downloaded to                                                          |

| 3   | K3   | R/W | the on-chip RAM. Only after H'5A has been written, the programming/erasing of                                                         |

| 2   | K2   | R/W | the flash memory becomes possible. Even if an internal programming/erase                                                              |

| 1   | K1   | R/W | program is executed with any value other than H'A5 written in the FKEY register,                                                      |

| 0   | K0   | R/W | the flash memory cannot be programmed or erased.                                                                                      |

|     |      |     | H'A5: Enables writing to the SCO bit. (Any value other than H'A5 would not allow setting of the SCO bit.)                             |

|     |      |     | H'5A: Enables flash memory programming/erasing. (Any value other than H'5A would cause the software protection state to be retained.) |

|     |      |     | H'00: Initial value                                                                                                                   |

## 3.1.5 Flash MAT Select Register (FMATS) Initial Value: H'AA\*

FMATS is a register that specifies the selection of either the user or the user boot MAT respectively.

Table 8 Flash Mat Select Register (FMATS) Initial value

|     | Bit  |     |                                                                                           |

|-----|------|-----|-------------------------------------------------------------------------------------------|

| Bit | Name | R/W | Description                                                                               |

| 7   | MS7  | R/W | MAT select                                                                                |

| 6   | MS6  | R/W | A value other than H'AA specifies the selection of the user MAT, while H'AA               |

| 5   | MS5  | R/W | written in this register specifies the selection of the user boot MAT. BY writing a       |

| 4   | MS4  | R/W | value to FMATS, MAT switching is effected.                                                |

| 3   | MS3  | R/W | H'AA: Selects the user boot MAT.                                                          |

| 2   | MS2  | R/W | (A value other than H'AA specifies the selection of the user MAT.)                        |

| 1   | MS1  | R/W | This is the initial value when startup is done in the user boot mode.                     |

| 0   | MS0  | R/W | H'00: This is the initial value when startup is done in a mode other than user boot mode. |

|     |      |     | (The user MAT is selected.)                                                               |

|     |      |     | [Programmable condition] The code is being executed within the on-chip RAM.               |

Note \*The initial value is H'AA when in the user boot mode; H'00 otherwise.

## 3.1.6 Flash Transfer Destination Address Register (FTDAR) Initial Value: H'00

FTDAR is a register used to specify the destination address on the on-chip RAM to which the internal program is to be downloaded. Make the setting of this register before writing 1 to the SCO bit in the FCCS register.

Table 9 Flash Transfer Destination Address Register (FTDAR) Initial value

|     | Bit  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Name | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7   | TDER | R/W | Transfer destination address setting error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     |      |     | When an error has occurred in the download start address specification using the bits from TDA6 to TDA0, 1 is set to this bit. Concerning evaluation of a potential error in the address specification, a check is made of the value in bits TDA6 to TDA0 to determine whether it falls within the range between H'00 to H'07 when a program is downloaded with the FCCS register's SCO bit set to 1. Before setting the SCO bit to 1, set the FTDAR value to between H'00 to H'07 in addition to setting this bit to 0.  0: The value set to bits TDA6 to TDA0 is normal.  1: The value set to bits TDA6 to TDA0 is outside the range of H'00 to H'07, |

|     |      |     | meaning that download has been aborted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6   | TDA6 | R/W | Transfer destination address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | TDA5 | R/W | Specifies the download start address. Using a setting value within the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | TDA4 | R/W | permissible range of H'00 to H'07, the download start address on the on-chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3   | TDA3 | R/W | RAM can be specified in increments of 4 kilobytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2   | TDA2 | R/W | H'00: Sets the download start address to H'FF9000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1   | TDA1 | R/W | H'01: Sets the download start address to H'FFA000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0   | TDA0 | R/W | H'02: Sets the download start address to H'FFB000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |     | H'03: Sets the download start address to H'FFC000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |     | H'04: Sets the download start address to H'FFD000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |     | H'05: Sets the download start address to H'FFE000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |     | H'06: Sets the download start address to H'FF8000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |     | H'07: Sets the download start address to H'FF7000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |      |     | H'08 - H'FF: Must not be set. If any of these values are set, the TDER bit becomes 1 during the download operation and the download operation of the internal program is aborted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### 3.1.7 System Control Register (SYSCR2) Initial Value: H'00\*

The SYSCR2 register controls register access.

Table 10 System Control Register (SYSCR2) Initial Value

|        | Bit   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Name  | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7 to 4 | _     | _   | Reserved bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |       |     | Write 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3      | FLSHE | R/W | Flash memory control register enable                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |       |     | Writes 0 to control the CPU access made by the flash memory control register. Setting the FLSHE bit to 1 enables read/programming of the flash memory control register. Clearing the FLSHE bit to 0 deselects the flash memory control register. At this time, the contents of the flash memory control register are retained.  0: Flash control logic unit which controls H'FFFFA4 to H'FFFFAF is disabled.  1: Flash control logic unit which controls H'FFFFA4 to H'FFFFAF is enabled. |

| 2      | _     | _   | Reserved bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        |       |     | Write 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1,0    | _     | R/W | Reserved bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |       |     | Write 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Note \*The initial values of bits 7 to 4 and 2 are undefined. The initial values of other bits are 0.

# 3.2 Programming/Erase Interface Parameters

Programming/erase interface parameters are used for specifying operating frequency, user branch destination address, programming data storing address, blocks to be erased, and so on of an internal program that has been downloaded as well as exchanging processing and operation results. For these parameters, the CPU's general registers (ER0, ER1) and on-chip RAM areas are used. Initial values at the time of power-on reset and hardware standby remain undefined.

During download, initialization, or the execution of an internal program, the values of the CPU registers other than that of R0L are saved. In R0L, the value returned as the result of processing is written. Since the stack area is used for saving the values of registers other than that of the R0L, always ensure this is allocated prior to any processing. (The maximum usable size of the stack area is 128 bytes.)

Programming/erase interface parameters are used in the following four types of processing:

- 1. Download control

- 2. Pre-programming/erase operation initialization

- 3. Programming operation

- 4. Erase operation

Different parameters are used for different types of processing. The following table shows which parameters are used for which types of operation.

Note that the FPFR parameter values are returned as the result of the initialization, programming and erase operations. However, the meanings of individual bits vary depending on the type of processing performed.

Table 11 Parameters and Modes in which They are Used

| Parameter Name                                   | Abbr.  | Down-<br>load | Initializa-<br>tion | Pro-<br>gramming | Erase | R/W | Initial<br>Value | Assigned<br>to  |

|--------------------------------------------------|--------|---------------|---------------------|------------------|-------|-----|------------------|-----------------|

| Download pass /fail result                       | DPFR   | Used          |                     |                  |       | R/W | Undefined        | On-chip<br>RAM* |

| Flash pass/fail result                           | FPFR   |               | Used                | Used             | Used  | R/W | Undefined        | CPU's<br>R0L    |

| Flash program erase frequency control            | FPEFEQ |               | Used                |                  |       | R/W | Undefined        | CPU's<br>ER0    |

| Flash user branch address set parameter          | FUBRA  |               | Used                |                  |       | R/W | Undefined        | CPU's<br>ER1    |

| Flash multi-<br>purpose address<br>area          | FMPAR  |               |                     | Used             |       | R/W | Undefined        | CPU's<br>ER1    |

| Flash multi-<br>purpose data<br>destination area | FMPDR  |               |                     | Used             |       | R/W | Undefined        | CPU's<br>ER0    |

| Flash erase block select                         | FEBS   |               |                     |                  | Used  | R/W | Undefined        | CPU's<br>ER0    |

Note \*A single byte in the download destination start address specified by the FTDAR register.

#### 3.2.1 Download Control

The internal program is automatically downloaded by setting the SCO bit to 1. The area on the on-chip RAM into which the program is downloaded is a 2-kilobyte area from the start address specified by the FTDAR register. Download control is set by means of the programming/erase interface registers, and a return value is passed as the DPFR parameter.

(1) Download Pass/Fail Parameter (DPFR: 1 byte of start address on the on-chip RAM specified by the FTDAR register)

This is a value returned as the result of a download. The success or otherwise of the download can be assessed by the value of this parameter. Since it is difficult to verify whether the setting of the SCO bit to 1 was successful, set the single-byte start address on the on-chip RAM specified in the FTDAR register prior to download (that is, before setting the SCO bit to 1) to a specification other than the download return value (for example, to H'FF), to ensure positive verification.

Table 12 Download Pass/Fail Result Parameter

|        | Bit  |     |                                                                                                                                                                                                                                                                                                                                                                            |

|--------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Name | R/W | Description                                                                                                                                                                                                                                                                                                                                                                |

| 7 to 3 | _    | _   | Reserve bits                                                                                                                                                                                                                                                                                                                                                               |

|        |      |     | Value 0 is returned.                                                                                                                                                                                                                                                                                                                                                       |

| 2      | SS   | R/W | Source select error detection bit                                                                                                                                                                                                                                                                                                                                          |

|        |      |     | As a downloadable program, only one type of internal program can be specified. If none or multiple types are selected, or a program is selected without mapping, an error occurs.                                                                                                                                                                                          |

|        |      |     | 0: Program to be downloaded is correctly selected.                                                                                                                                                                                                                                                                                                                         |

|        |      |     | <ol> <li>Download error. (Multiple programs selected or program selected without<br/>mapping.)</li> </ol>                                                                                                                                                                                                                                                                  |

| 1      | FK   | R/W | Flash key register error detection bit                                                                                                                                                                                                                                                                                                                                     |

|        |      |     | This is a bit returning the result following checking of whether or not the FKEY register value is H'A5.                                                                                                                                                                                                                                                                   |

|        |      |     | 0: FKEY register setting is correct. (FKEY = H'A5)                                                                                                                                                                                                                                                                                                                         |

|        |      |     | 1: FKEY register setting value error. (The FKEY value is not H'A5.)                                                                                                                                                                                                                                                                                                        |

| 0      | SF   | R/W | Success/fail bit                                                                                                                                                                                                                                                                                                                                                           |

|        |      |     | This is a bit that specifies whether downloading has successfully completed. By reading back the program that has been downloaded to the on-chip RAM, a check is made to determine whether it has been successfully transferred to the on-chip RAM, and the result of this check is returned.  0: Download of an internal program has been completed successfully (without |

|        |      |     | error).                                                                                                                                                                                                                                                                                                                                                                    |

|        |      |     | 1: Download of an internal program has failed. (An error has occurred.)                                                                                                                                                                                                                                                                                                    |

#### 3.2.2 Programming/Erase Initialization

An internal program to be downloaded includes an initialization module.

The programming/erase operation requires the application of pulses of a given time width, and the required pulse width is created by a wait loop using the CPU instructions. Accordingly, it is necessary to set the operating frequency of the CPU.

It is the initialization program that makes settings such as the programming/erase program parameters of the downloaded program.

(1) Flash Programming/Erasing Frequency Parameter (FPEFEQ: CPU's general register ER0) This parameter is used to set the operating frequency of the CPU.

Table 13 Flash Programming/Erasing Frequency Parameter

|         | Bit    |     |                                                                                                                                                            |

|---------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Name   | R/W | Description                                                                                                                                                |

| 31 to   | F31 to | R/W | Reserve bits                                                                                                                                               |

| 16      | F16    |     | These bits should be cleared to 0.                                                                                                                         |

| 15 to 0 | F15 to | R/W | Frequency setting bits                                                                                                                                     |

|         | F0     |     | Set the CPU operating frequency. Calculate the settable value as follows:                                                                                  |

|         |        |     | <ul> <li>Round off the operating frequency in MHz to two decimal places.</li> </ul>                                                                        |

|         |        |     | <ul> <li>Multiply the value by 100, convert the obtained value to binary form, and<br/>write it to the FPEFEQ parameter (general register ER0).</li> </ul> |

|         |        |     | As a concrete example, when the CPU's operating frequency is 25.000 MHz, calculations are as follows:                                                      |

|         |        |     | Round off 25.000 at the third decimal place to obtain 25.00.                                                                                               |

|         |        |     | Convert 25.00 $\times$ 100 = 2500 into binary form to obtain B'0000, 1001, 1100, 0100 (H'09C4), and set it to ER0.                                         |

<sup>(2)</sup> Flash User Branch Address Setting Parameter (FUBRA: CPU's general register ER1)

This parameter sets the user branch destination address. The specified user program can be executed in units of a predetermined amount of processing during programming/erase operations.

| Table 1/ | Flash User  | Branch | Addrass | Satting | Parameter |

|----------|-------------|--------|---------|---------|-----------|

| Table 14 | riasii User | Drancn | Address | Setting | Parameter |

|         | Bit  |     |                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Name | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

| 31 to 0 | UA31 | R/W | User branch destination address                                                                                                                                                                                                                                                                                                                                                                                       |

|         | to   |     | When no user branching is required, set address 0 (H'00000000).                                                                                                                                                                                                                                                                                                                                                       |

|         | UA16 |     | A user branch destination must be within the RAM space other than the area occupied by the internal program transferred, or the external bus space. Proceed with caution to avoid branching to an area without execution code, which would cause a runaway, and avoid corrupting the internal program area or a stack area. In the event of a program runaway, flash memory values are not guaranteed.                |

|         |      |     | During user-branched processing, do not download, initialize, or invoke any programming/erase program routines of the internal program.                                                                                                                                                                                                                                                                               |

|         |      |     | Programming/erasing subsequent to the user branch routine cannot be otherwise guaranteed. In addition, do not modify the prepared data to be written. Likewise, do not rewrite the programming/erase interface register or make a transition to the RAM emulation mode during user branched processing. After completing the user-branch processing, return to the programming/erase program by the RTS instructions. |

<sup>(3)</sup> Flash Pass/Fail Parameter (FPFR: CPU's general register R0L)

This section describes the FPFR as a return value, indicating the result of initialization.

Table 15 Flash Pass/Fail Parameter

|        | Bit  |     |                                                                                                                                                                                                                                                                                                          |

|--------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Name | R/W | Description                                                                                                                                                                                                                                                                                              |

| 7 to 3 | _    | _   | Reserve bits                                                                                                                                                                                                                                                                                             |

|        |      |     | Value 0 is returned.                                                                                                                                                                                                                                                                                     |

| 2      | BR   | R/W | User branch error detection bit                                                                                                                                                                                                                                                                          |

|        |      |     | Returns the result of a check performed to determine whether or not the specified user branch destination address is outside the storage area of a programming/erase-related programs that have been downloaded.  0: User branch address setting is normal.  1: User branch address setting is abnormal. |

| 1      | FQ   | R/W | Frequency error detection bit                                                                                                                                                                                                                                                                            |

|        |      |     | Returns the result of a check determining whether or not the specified CPU operating frequency is within the supported range.  0: Operating frequency setting is normal.                                                                                                                                 |

|        |      |     | 1: Operating frequency setting is abnormal.                                                                                                                                                                                                                                                              |

| 0      | SF   | R/W | Success/fail bit                                                                                                                                                                                                                                                                                         |

|        |      |     | This is a bit that is returned to indicate whether or not initialization has been successfully terminated.  0: Initialization terminated successfully (without error).  1: Initialization terminated abnormally (and resulted in error).                                                                 |

|        |      |     | i. initialization terminated abnormally (and resulted in error).                                                                                                                                                                                                                                         |

H8S/Family

#### 3.2.3 Programming Operation

To perform programming of the flash memory, it is necessary to pass the programming destination address on the user MAT to the downloaded programming program in addition to the data to be programmed.

- 1. Set the start address of the programming destination on the user MAT to general register ER1. This parameter is called FMPAR (flash multi-purpose address area parameter). Since programming data is always in 128-byte units, the programming start address boundary on the user MAT should always have lower 8 bits (A7 to A0) of either H'00 or H'80.

- 2. Ensure that programming data to be programmed to the user MAT is ready in a continuous area. The programming data must be in a continuous space accessible by the CPU's MOV.B instruction and outside the on-chip flash memory space. Even if the data you wish to program is less than 128 bytes long, prepare programming data a full 128 bytes by padding with dummy code (H'FF). Set the start address of the area storing the prepared programming data to general register ERO. This parameter is called FMPDR (flash multi-purpose data destination area parameter).

- (1) Flash Multi-Purpose Address Area Parameter (FMPAR: CPU's general register ER1)

Sets the programming destination start address on the user MAT.

When the address of any area outside the flash memory space is set, an error will occur.

In addition, the programming destination start address must be within a 128-byte boundary. Any address outside this boundary also will result in an error, which will be reflected in the WA bit of the FPFR parameter.