### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### H8SX Family

### Flash Memory Reprogramming in the User Boot Mode for H8SX/1657F

### Introduction

This application note describes the reprogramming of flash memory (the user MAT) via a clock synchronous communications interface in the use boot mode of H8SX/1657F, and mainly concerns the slave side. That is, unless otherwise specified, the descriptions are related to the slave side.

### **Target Device**

H8SX/1657F

### Contents

| 1. | Specification                                                                                     | 2  |

|----|---------------------------------------------------------------------------------------------------|----|

| 2. | Applicable Conditions                                                                             | 7  |

| 3. | Description of Functions Used                                                                     | 8  |

| 4. | Description of Operation                                                                          | 11 |

| 5. | Description of Software for Normal Program on the Receive Side (Slave)                            | 19 |

| 6. | Description of Software for Programming/Erasing Procedure Program on the Slave Side               | 26 |

| 7. | Description of Software for the Clock Synchronous Serial Communications Program on the Slave Side | 46 |

# RENESAS

### 1. Specification

### 1.1 Outline

Specifications, which are highly reliable for users to reprogram the on-chip flash memory, are provided for H8SX/1657F. The use starts by downloading the erasing or programming module to the RAM and then calls subroutines to erase/program the flash memory.

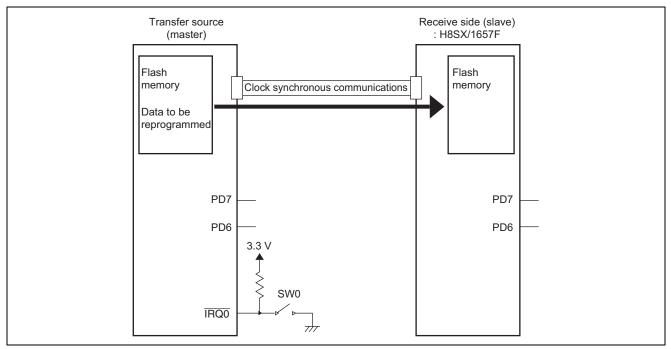

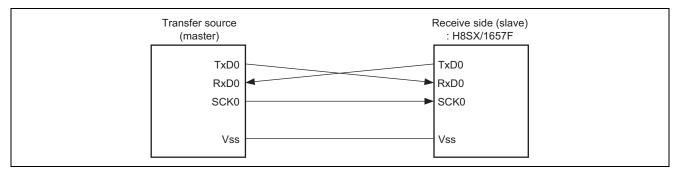

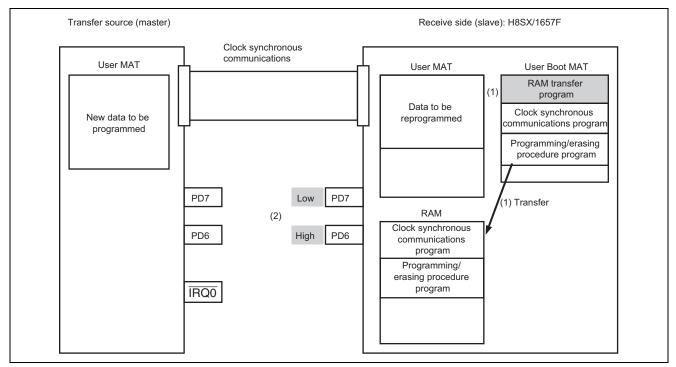

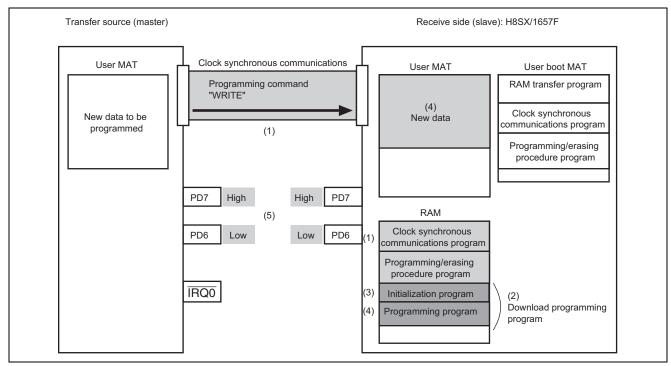

In this sample task, data for reprogramming are placed in the flash memory on the master side and sent to the slave side by clock synchronous communications. The following procedure is then applied to reprogram the flash memory on the slave side. A sample configuration for on-board reprogramming is illustrated in figure 1, and the connections for clock synchronous communications between the master and slave are illustrated in figure 2.

- Power-on resets are applied, and the slave boots up in the user boot mode and the master boots up in the user mode.

- When master side switch 0 (SW0) is turned on, the master side sends the erase command to the slave side, and the slave side erases its own flash memory.

- The master side sends the data to be reprogrammed from its own flash memory to the slave side. The data for reprogramming are transferred in clock synchronous mode via serial communications interface (SCI) 0. The data is transmitted from the master side and received on the slave side.

- The slave programs the received data for reprogramming to its own flash memory.

- On both the master and slave sides, PD7 is low and PD6 is high while the flash memory is being reprogrammed, and PD7 is high and PD6 is low on completion of reprogramming.

Figure 1 Sample Configuration for On-Board Reprogramming

Figure 2 Connections for Clock Synchronous Communications between the Master and Slave

### 1.2 User Boot Mode

Set the mode pin for the user boot mode (MD1 = 0, MD0 = 1), and performs a start from reset.

The RAM transfer program, clock synchronous communications program, and programming/erasing procedure program must be written to the user MAT in advance.

### **1.3** Specification for Communications

The specification for communications between the master and slave in this sample task are listed below.

### 1.3.1 Type of Communications

### Table 1 Type of Communications

| Item          | Setting                          |

|---------------|----------------------------------|

| Transfer rate | 2.5 Mbps                         |

| Туре          | Clock synchronous communications |

| Data bit      | 8 bits (1 byte)                  |

### 1.3.2 Communications Command

### Table 2 Communications commands

| Command Name                  | Constant Name | Command Data |  |

|-------------------------------|---------------|--------------|--|

| Erase                         | ERASE         | H'11         |  |

| Write                         | WRITE         | H'12         |  |

| Read status                   | STATUSREAD    | H'13         |  |

| 128-byte transmission request | TRS128        | H'14         |  |

### 1.3.3 State Indicator

### Table 3State Indicator

| Statue Name                  | Constant Name | Status Data |  |

|------------------------------|---------------|-------------|--|

| Normal                       | OK            | H'00        |  |

| Erase command error          | ER_ECMD       | H'C1        |  |

| Erase download error         | ER_EDWNLD     | H'C2        |  |

| Erase initialization error   | ER_EINIT      | H'C3        |  |

| Erase error                  | ER_ERASE      | H'C4        |  |

| Program command error        | ER_WCMD       | H'A1        |  |

| Program download error       | ER_WDWNLD     | H'A2        |  |

| Program initialization error | ER_WINIT      | H'A3        |  |

| Program error                | ER_WRITE      | H'A4        |  |

### 1.3.4 Specifying Blocks to be Erased

The erase command "ERASE" is sent from the master to the slave and is immediately followed by an indicator of the block numbers of blocks to be erased. The communications format for block erasure is given in table 4. Block settings are made in a 4-byte (32-bit) unit where bits 19 to 0 correspond to blocks 19 to 0. Since bits 31 to 20 are not used, always set them to 0. An example of the data transmitted to erase block 19 is given in table 5.

### Table 4 Correspondence of Blocks to be Erased

| Bit      | Erased Block | Setting | Description                               |

|----------|--------------|---------|-------------------------------------------|

| 31 to 20 | No used      | 0 fixed | Not used.                                 |

|          |              |         | Set 0.                                    |

| 19 to 0  | EB19 to EB0  | 0/1     | 0: The corresponding block is not erased. |

|          |              |         | 1: The corresponding block is erased.     |

### Table 5 Example of Data for Transmission to Erase Block 19

|      | 1st Byte                 | 2nd Byte    | 3rd Byte | 4th Byte        | 5th Byte |

|------|--------------------------|-------------|----------|-----------------|----------|

| Item | Erase Command<br>(ERASE) | Erase block |          |                 |          |

| Byte | H'11                     | H'00        | H'08     | H'00            | H'00     |

| Bit  | 00010001                 | 000000000   | 00001000 | 0 0 0 0 0 0 0 0 | 00000000 |

|      | MSB LSB                  | MSB LSB     | MSB LSB  | MSB LSB         | MSB LSB  |

Note: The data is transmitted in byte units, with the LSB first.

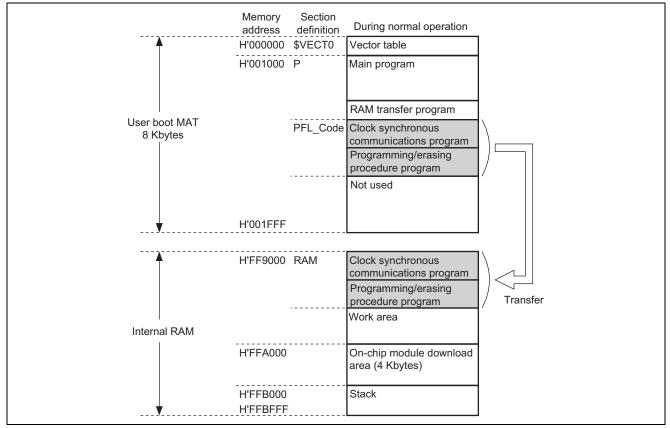

### 1.4 Memory Map

The memory map for this sample task is given as figure 3.

Figure 3 Memory Map

### 2. Applicable Conditions

### Table 6 Applicable Conditions

| Item                      | Description                                                           |

|---------------------------|-----------------------------------------------------------------------|

| Operating Frequency       | Input clock: 17.5 MHz                                                 |

|                           | System clock (I                                                       |

|                           | Peripheral module clock (Ρφ): 35 MHz                                  |

|                           | External bus clock (Βφ): 35 MHz                                       |

| Operating mode            | Mode 1 (MD2 = 0, MD1 = 0, MD0 = 1)                                    |

| On-board programming mode | User boot mode                                                        |

| Development tool          | High-performance Embedded Workshop Ver.4.01.01                        |

| C/C++ compiler            | H8S, H8/300 Series C/C++ Compiler Ver.6.01.02                         |

|                           | (manufactured by Renesas Technology)                                  |

| Compiler options          | -cpu = h8sxa:24:md, -code = machinecode, -optimize = 1, -regparam = 3 |

|                           | -speed = (register, shift, struct, expression)                        |

### Table 7 Section Setting

| Address  | Section Name | Description                                                 |

|----------|--------------|-------------------------------------------------------------|

| H'001000 | Р            | Program area                                                |

|          | PFL_Code     | Areas for storing programming/erasing procedure program     |

| H'FF9000 | RAM          | Area for transferring programming/erasing procedure program |

### 3. Description of Functions Used

### 3.1 User Boot Mode

### 3.1.1 User MAT and User Boot MAT

The on-chip flash memory consists of the two memory units (memory MATs) listed in table 8. Both are allocated to the same address. The user boot mode is an arbitrary boot program that suits the user system, and the user MAT can be programmed/erased.

When the CPU's operating mode setting is for the user boot mode and it is started from a reset, processing starts from the execution start address contained in the reset vector. At this time the target memory MAT is the user boot MAT (FMATS = H'AA). If the user MAT is actually to be erased/programmed, the user boot MAT must be replaced by the user MAT in the memory map when the erasing/programming is to be done. This switching should be executed by code in RAM.

### Table 8 Memory MATs

| Memory MAT    | Activation                                                          | Amount of Memory Used |

|---------------|---------------------------------------------------------------------|-----------------------|

| User MAT      | Activates when a power-on reset is performed in the user mode.      | 768 Kbytes            |

| User Boot MAT | Activates when a power-on reset is performed in the user boot mode. | 8 Kbytes              |

### 3.1.2 Downloading the On-Chip Program

Programming/erasing of the flash memory on this LSI is done by first downloading the on-chip module for either programming/erasing to the on-chip RAM and then running the individual program.

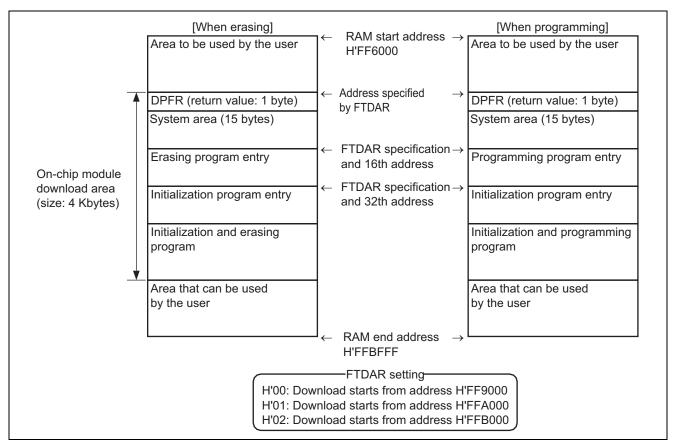

The destination address for downloading is determined by the setting of the download destination specification register (FTDAR). For the RAM address map after downloading, refer to figure 4. As the figure shows, the on-chip RAM area is the destination for downloading of programming/erasing programs. The corresponding program must be downloaded to the RAM area indicated by FTDAR prior to the required processing.

During programming/erasing, take care to ensure that the download area does not overlap with an area in use by the user.

Figure 4 Normal Operation

### 3.2 Block Configuration

Erase blocks of the user MAT are listed in table 9.

### Table 9 User MAT Erase Blocks

| Block | Unit of Erasure | Addresses            |

|-------|-----------------|----------------------|

| EB0   | 4 Kbytes        | H'000000 to H'000FFF |

| EB1   | 4 Kbytes        | H'001000 to H'001FFF |

| EB2   | 4 Kbytes        | H'002000 to H'002FFF |

| EB3   | 4 Kbytes        | H'003000 to H'003FFF |

| EB4   | 4 Kbytes        | H'004000 to H'004FFF |

| EB5   | 4 Kbytes        | H'005000 to H'005FFF |

| EB6   | 4 Kbytes        | H'006000 to H'006FFF |

| EB7   | 4 Kbytes        | H'007000 to H'007FFF |

| EB8   | 32 Kbytes       | H'008000 to H'00FFFF |

| EB9   | 64 Kbytes       | H'010000 to H'01FFFF |

| EB10  | 64 Kbytes       | H'020000 to H'02FFFF |

| EB11  | 64 Kbytes       | H'030000 to H'03FFFF |

| EB12  | 64 Kbytes       | H'040000 to H'04FFFF |

| EB13  | 64 Kbytes       | H'050000 to H'05FFFF |

| EB14  | 64 Kbytes       | H'060000 to H'06FFFF |

| EB15  | 64 Kbytes       | H'070000 to H'07FFFF |

| EB16  | 64 Kbytes       | H'080000 to H'08FFFF |

| EB17  | 64 Kbytes       | H'090000 to H'09FFFF |

| EB18  | 64 Kbytes       | H'0A0000 to H'0AFFFF |

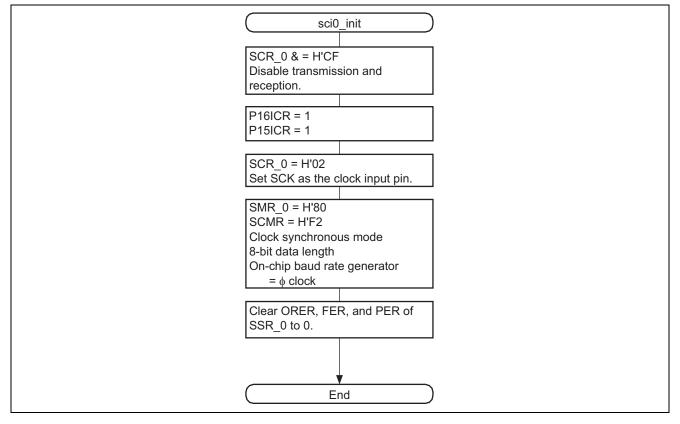

### 3.3 Serial Communications Interface

The SCI operates in the clock synchronous mode. It is used for command-related communications between the master and slave to transfer the data for reprogramming.

### 4. Description of Operation

### 4.1 User MAT Reprogramming Procedure

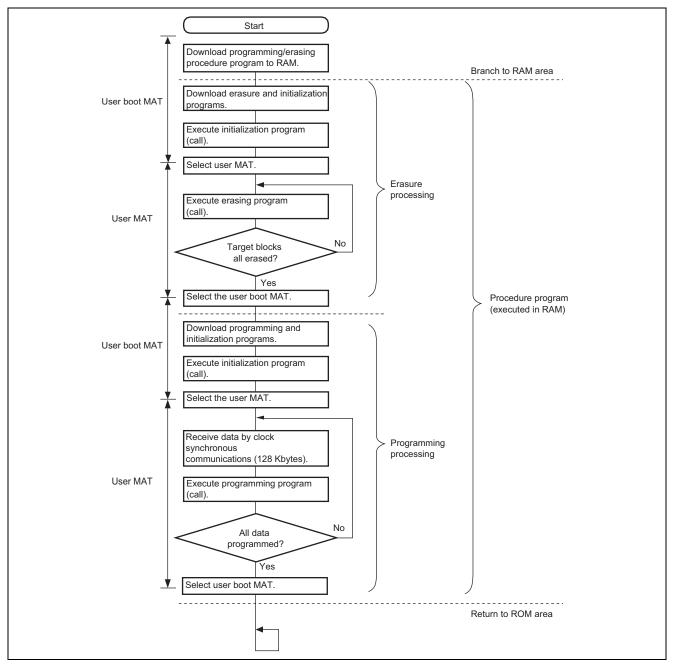

User MAT reprogramming procedure in the user boot mode is given in figure 5. In the user boot mode, the user boot MAT is accessible in the flash memory area, but the user MAT is hidden behind it. Therefore, user MAT must be chosen on the occasion of a reprogramming to user MAT. During programming of the user MAT, the user boot MAT is hidden, and the user MAT is being programmed, so the procedure program must be executed from an area other than the flash-memory area. After programming, the memory MATs are switched back to their initial mapping.

### 4.2 **Operational Overview**

### 4.2.1 Start of On-Board Reprogramming

(1) A power-on reset is applied to the slave side with the mode pins set for the user boot mode, the RAM transfer program in the user boot mode MAT on the slave side is activated, and the programming/erasing procedure program is transferred to the on-chip RAM.

(2) Here, PD7 is low and PD6 is high on the slave side.

Figure 6 Start of On-Board Reprogramming

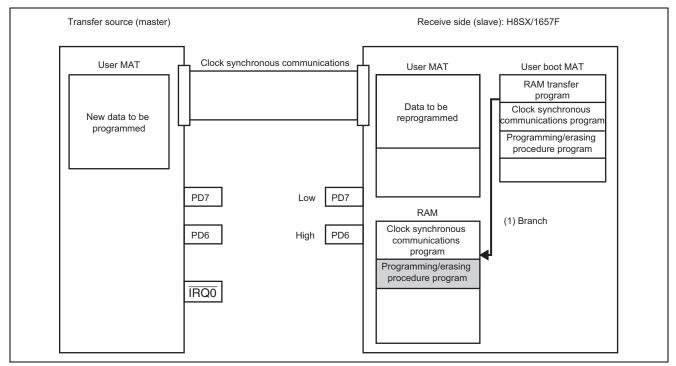

### 4.2.2 Activating the Programming/Erasing Procedure Program

(1) After the transfer programs have been loaded to RAM, control branches to the programming/erasing procedure program in RAM.

Figure 7 Activation of Programming/Erasing Procedure Program

# RENESAS

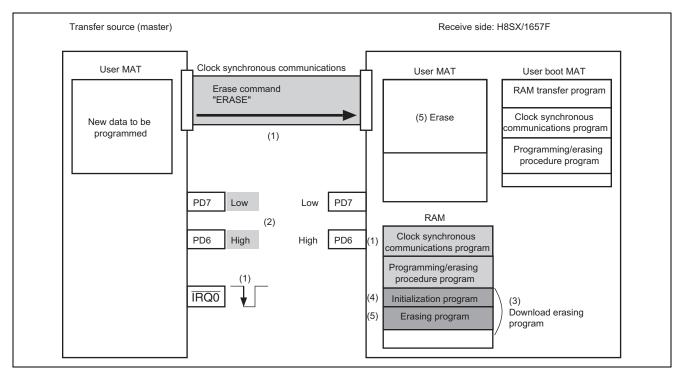

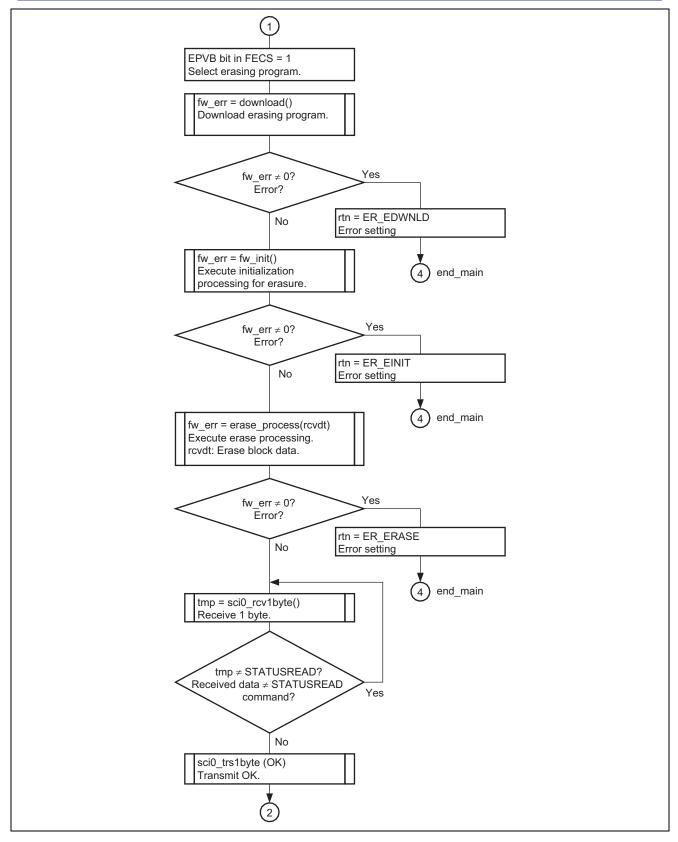

### 4.2.3 Erasing User MAT

- (1) When a low level input on the  $\overline{IRQ0}$  pin as a trigger, the master sends the erasing command, "ERASE".

- (2) At this time, PD7 is low and PD6 is high on the master side.

- (3) Registers for controlling the flash memory are set (both the EPVB bit of the FECS register and the SCO bit of the FCCS register to 1), and the initialization program and erasure program are downloaded.

- (4) The initialization program is executed.

- (5) The erasing program is executed, and the target block foe erasure on the user MAT is erased.

Figure 8 Erasing User MAT

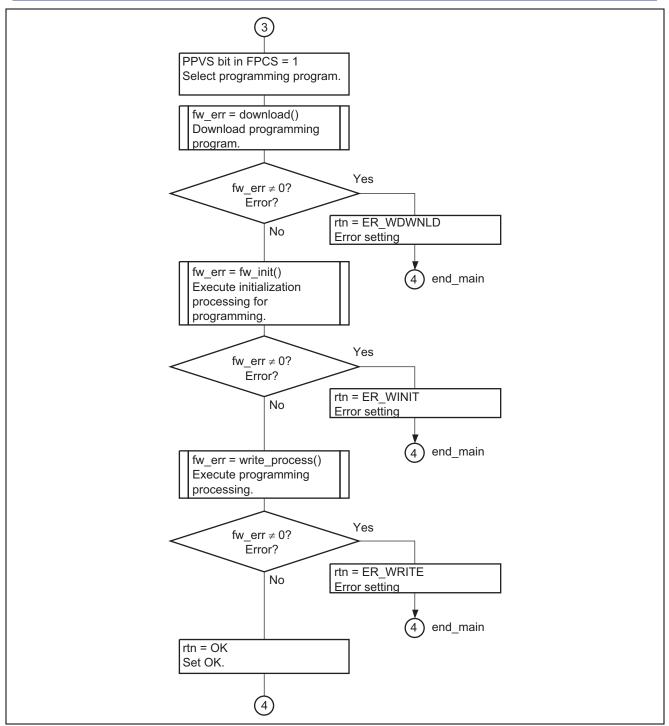

### 4.2.4 Programming User MAT

**I**

- (1) The master sends the programming command "WRITE".

- (2) Registers for controlling the flash memory are set (Both the PPVS bit of the FPCS register and the SCO bit of the FCCS register to 1), and initialization program and the programming program are downloaded.

- (3) The initialization program is executed.

- (4) The following a. and b. are repeated until all data on the master side is programmed on the slave side.

- a. The receive side (slave) receives 128 bytes of new data from the transfer source (master).

- b. The receive side (slave) executes the programming program, and writes 128 bytes of data to the user MAT.

- (5) On completion of programming, PD7 is high and PD6 is low on both the master and slave sides.

Figure 9 Programming User MAT

### 4.3 Sequence Diagram

### 4.3.1 Erasure Processing

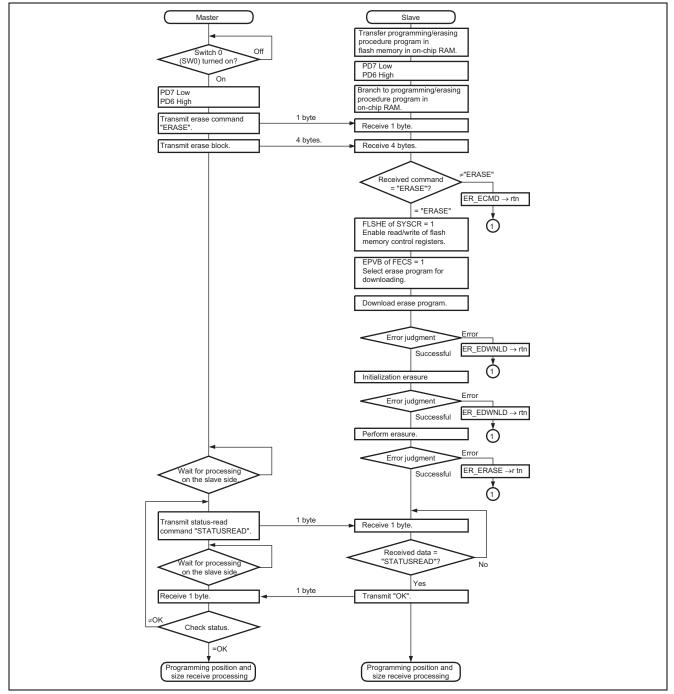

Figure 10 Erasure Processing

### 4.3.2 **Processing to Receive the Position and Range for Programming**

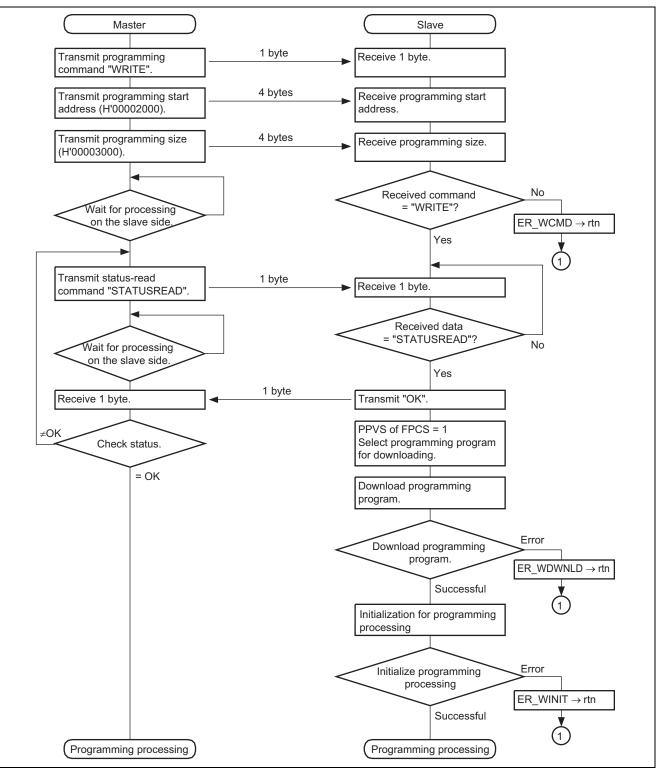

Figure 11 Processing to Receive the Position and Range for Programming

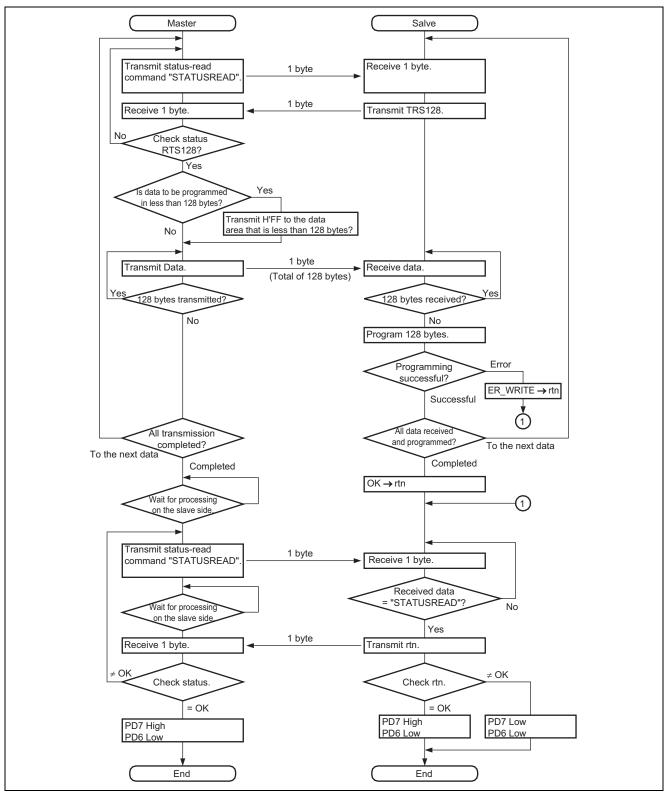

### 4.3.3 Programming Processing

### 5. Description of Software for Initialization Program on the Receive Side (Slave)

### 5.1 List of Functions

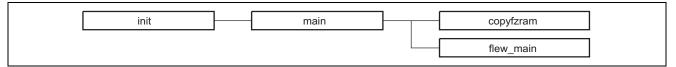

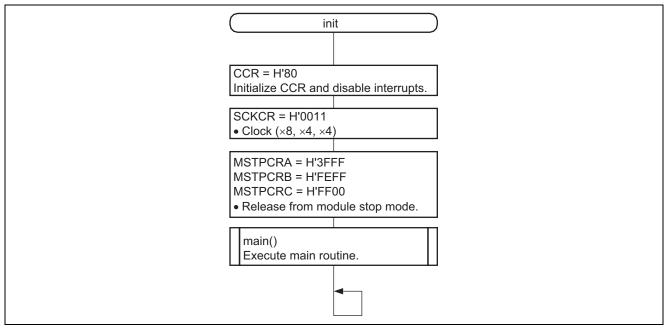

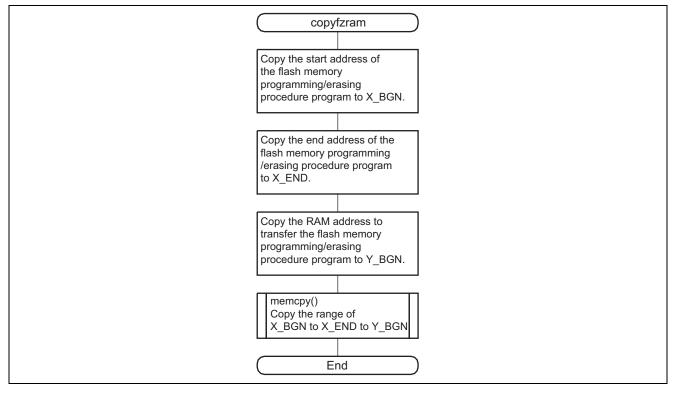

The initialization program (main.c) on the receive side is used to transfer the programming/erasing procedure program to the on-chip RAM. A list of functions used in the initialization program on the receive side is given in table 10, and the hierarchical structure of calls is given in figure 13.

| Table 10 | Functions in the Initialization Program on the Receive Side (Slave) |  |

|----------|---------------------------------------------------------------------|--|

|----------|---------------------------------------------------------------------|--|

| Function Name | Description                                                                                   |

|---------------|-----------------------------------------------------------------------------------------------|

| init          | Initialization routine                                                                        |

|               | Releases from the module stop mode, makes clock settings, and calls the main                  |

|               | function.                                                                                     |

| main          | Main routine                                                                                  |

|               | Transfers the programming/erasing procedure from the user MAT to the on-chip RAM.             |

| copyfzram     | Transfers the programming/erasing procedure program from the user MAT to the on-<br>chip RAM. |

| flew_main     | Programming/erasing procedure program in the user MAT.                                        |

Figure 13 Initialization Program on the Slave Side

### 5.2 Description of Functions

### 5.2.1 init Function

### 1. Functional overview

Initialization routine, releases the module stop mode, sets the clock, and calls the main function.

### 2. Arguments

None

3. Return value

None

4. Internal registers used

The internal registers used in this sample task are described below. Note that the settings shown below are

not the initial values but the values used in this sample task.

• Mode control register (MDCR) Number of bits: 16 Address: H'FFFDC0

| Bit | Bit Name | Setting    | R/W | Description                                                                                                     |

|-----|----------|------------|-----|-----------------------------------------------------------------------------------------------------------------|

| 11  | MDS3     | Undefined* | R   | Mode Select 3 to 0                                                                                              |

| 10  | MDS2     | Undefined* | R   | These bits indicate the operating mode selected by the                                                          |

| 9   | MDS1     | Undefined* | R   | mode pins (MD1 and MD0; see table 11). When MDCR is                                                             |

| 8   | MDS0     | Undefined* | R   | read, the signal levels input on pins MD2 to MD0 are latched into these bits. The latch is released by a reset. |

Note: \* Determined by the settings on pins MD1 and MD0.

### Table 11 Values of bits MDS3 to MDS0

| MCU            | Mode Pi | ins |     | MDCR |      |      |      |

|----------------|---------|-----|-----|------|------|------|------|

| Operating Mode | MD2     | MD1 | MD0 | MDS3 | MDS2 | MDS1 | MDS0 |

| 1              | 0       | 0   | 1   | 1    | 1    | 0    | 1    |

| 2              | 0       | 1   | 0   | 1    | 1    | 0    | 0    |

| 4              | 1       | 0   | 0   | 0    | 0    | 1    | 0    |

| 5              | 1       | 0   | 1   | 0    | 0    | 0    | 1    |

| 6              | 1       | 1   | 0   | 0    | 1    | 0    | 1    |

| 7              | 1       | 1   | 1   | 0    | 1    | 0    | 0    |

| • Sy | stem clock control register (SCKCR) | Number of bits: 16 | Address: H'FFFDC4 |

|------|-------------------------------------|--------------------|-------------------|

|------|-------------------------------------|--------------------|-------------------|

| Bit | Bit Name | Setting | R/W | Description                                                     |

|-----|----------|---------|-----|-----------------------------------------------------------------|

| 10  | ICK2     | 0       | R/W | System Clock (I                                                 |

| 9   | ICK1     | 0       |     | These bits select the frequency of the system clock provided to |

| 8   | ICK0     | 1       |     | the CPU, DMAC, and DTC.                                         |

|     |          |         |     | 000: Input clock × 2                                            |

| 6   | PCK2     | 0       | R/W | Peripheral Module Clock (P                                      |

| 5   | PCK1     | 0       |     | These bits select the frequency of the peripheral module clock. |

| 4   | PCK0     | 1       |     | 001: Input clock × 2                                            |

| 2   | BCK2     | 0       | R/W | External Bus Clock (B                                           |

| 1   | BCK1     | 0       |     | These bits select the frequency of the external bus clock.      |

| 0   | BCK0     | 1       |     | 001: Input clock × 2                                            |

## RENESAS

- MSTPCRA, MSTPCRB, and MSTPCRC control the module stop mode. Setting a bit to 1 makes the corresponding module enter the module stop mode, while clearing the bit to 0 releases the module from module stop state.

- Module stop control register A (MSTPCRA) Number of bits: 16 Address: H'FFFDC8

| Bit | Bit Name | Setting | R/W | Description                                                                                                                                                                                                                                                                                                                           |

|-----|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | ACSE     | 0       | R/W | All-Module-Clock-Stop Mode Enable<br>Enables/disables all-module-clock-stop mode for reducing<br>current drawn by stopping the operation of bus controller and<br>I/O ports when the CPU executes the SLEEP instruction after<br>the module stop mode has been set for all of the on-chip<br>peripheral modules controlled by MSTPCR. |

|     |          |         |     | 0: Disables all-module-clock-stop mode 1: Enables all-module-clock-stop mode                                                                                                                                                                                                                                                          |

| 13  | MSTPA13  | 1       | R/W | DMA controller (DMAC)                                                                                                                                                                                                                                                                                                                 |

| 12  | MSTPA12  | 1       | R/W | Data transfer controller (DTC)                                                                                                                                                                                                                                                                                                        |

| 4   | MSTPA4   | 1       | R/W | A/D converter (unit 1)                                                                                                                                                                                                                                                                                                                |

| 3   | MSTPA3   | 1       | R/W | A/D converter (unit 0)                                                                                                                                                                                                                                                                                                                |

| 1   | MSTPA1   | 1       | R/W | 16-bit timer pulse unit (TPU channels 11 to 6)                                                                                                                                                                                                                                                                                        |

| 0   | MSTPA0   | 1       | R/W | 16-bit timer pulse unit (TPU channels 5 to 0)                                                                                                                                                                                                                                                                                         |

• Module stop control register B (MSTPCRB) Number of bits: 16 Address: H'FFFDCA

| Bit | Bit Name | Setting | R/W | Description                               |

|-----|----------|---------|-----|-------------------------------------------|

| 15  | MSTPB15  | 1       | R/W | Programmable pulse generator (PPG)        |

| 12  | MSTPB12  | 1       | R/W | Serial communications interface_4 (SCI_4) |

| 11  | MSTPB11  | 0       | R/W | Serial communications interface_3 (SCI_3) |

• Module stop control register C (MSTPCRC) Number of bits: 16 Address: H'FFFDCC

| Bit      | Bit Name | Setting  | R/W | Description                                      |

|----------|----------|----------|-----|--------------------------------------------------|

| 10       | MSTPC10  | 1        | R/W | Synchronous serial communications unit 2 (SSU_2) |

| 9        | MSTPC9   | 1        | R/W | Synchronous serial communications unit 1 (SSU_1) |

| 8        | MSTPC8   | 1        | R/W | Synchronous serial communications unit 0 (SSU_0) |

| 2        | MSTPC2   | 0        | R/W | On-chip RAM_2 (H'FF6000 to H'FF7FFF)             |

| 1        | MSTPC1   | 0        | R/W | On-chip RAM_1 (H'FF8000 to H'FF9FFF)             |

| 0        | MSTPC0   | 0        | R/W | On-chip RAM_0 (H'FFA000 to H'FFBFFF)             |

| <u> </u> |          | <b>v</b> |     |                                                  |

### 5. Flowchart

### 5.2.2 main Function

- 1. Functional overview

- Branches to programming/erasing procedure program

2. Arguments

None

3. Return value

None

4. Internal registers used

The internal registers used in this sample task are described below. Note that the settings shown below are not the initial values but the values used in this sample task.

| • Por | • Port D data direction register (PDDDR) |         | DDDR) | Number of bits: 8 Address: H'FFFB8C |

|-------|------------------------------------------|---------|-------|-------------------------------------|

| Bit   | Bit Name                                 | Setting | R/W   | Description                         |

| 7     | PD7DDR                                   | 1       | R/W   | 0: Sets PD7 as an input pin.        |

|       |                                          |         |       | 1: Sets PD7 as an output pin.       |

| 6     | PD6DDR                                   | 1       | R/W   | 0: Sets PD6 as an input pin.        |

|       |                                          |         |       | 1: Sets PD6 as an output pin.       |

• Port D data register (PDDR) Number of bits: 8 Address: H'FFFF5C

In this sample task, the PD7 and PD6 pins are used for output pins of flash reprogramming.

| Bit | Bit Name | Setting   | R/W | Description                        |

|-----|----------|-----------|-----|------------------------------------|

| 7   | PD7DR    | Undefined | R/W | 0: PD7 pin is set to a low level.  |

|     |          |           |     | 1: PD7 pin is set to a high level. |

| 6   | PD6DR    | Undefined | R/W | 0: PD6 pin is set to a low level.  |

|     |          |           |     | 1: PD6 pin is set to a high level. |

### 5. Flowchart

### 5.2.3 copyfzram Function

### 1. Functional overview

Transfers the programming/erasing procedure program to the on-chip RAM.

2. Arguments

None

3. Return value

None

4. Internal registers used

None

#### 5. Flowchart

### 5.2.4 flew\_main Function

1. Functional overview

Calls the main routine of the programming/erasing procedure program.

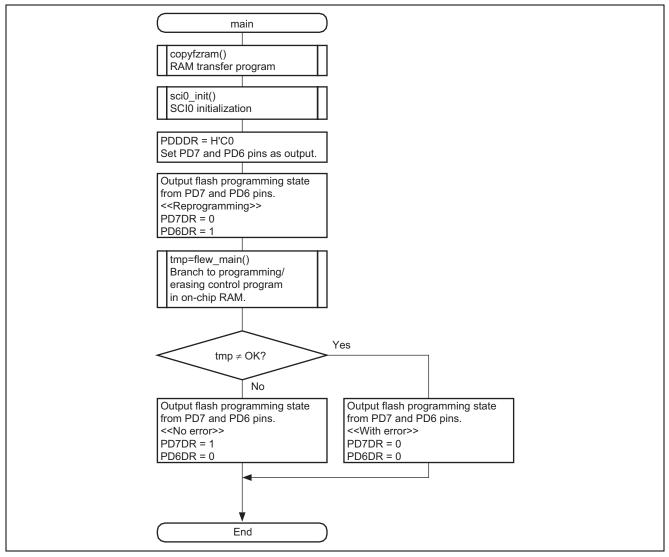

## 6. Description of Software for Programming/Erasing Procedure Program on the Slave Side

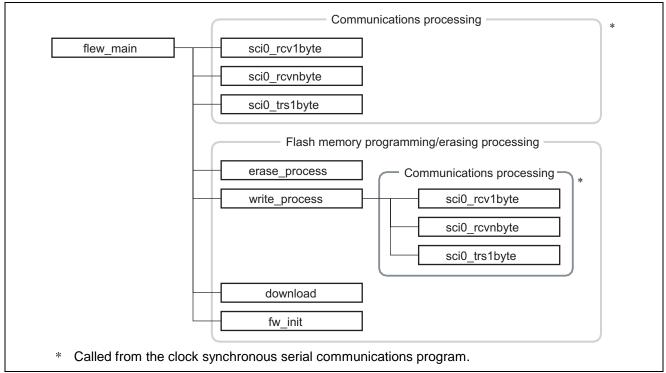

### 6.1 List of Functions

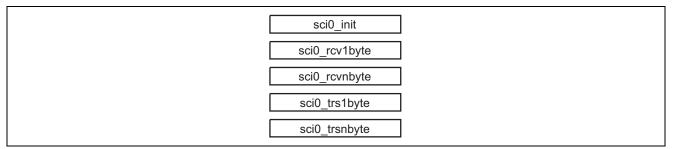

Programming/erasing procedure program (fwrite.c) performs erasing block units, receives flash memory programming data, and performs programming to flash memory. A list of functions for the routines used in the programming/erasing procedure program is given in table 12. The hierarchical structure is shown in figure 14.

| Table 12 | List of Functions for | r Programming/Erasing Procedure P | rogram |

|----------|-----------------------|-----------------------------------|--------|

|----------|-----------------------|-----------------------------------|--------|

| Function Name | Description                                                |

|---------------|------------------------------------------------------------|

| flew_main     | Main processing of flash memory erasing/programming        |

| erase_process | Erases flash memory                                        |

| write_process | Programs flash memory                                      |

| download      | Downloads on-chip modules                                  |

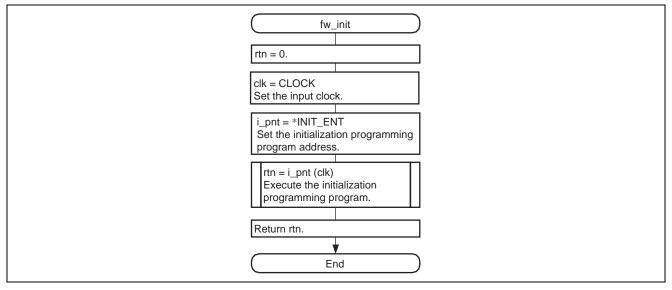

| fw_init       | Initialization before flash memory erasing and programming |

Figure 14 Programming/Erasing Procedure Program

#### 6.2 **Description of Functions**

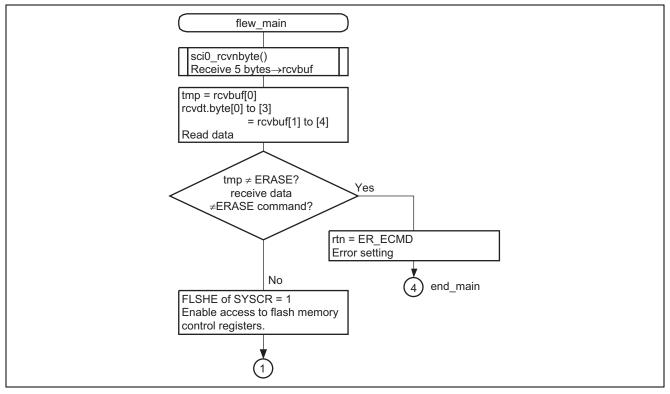

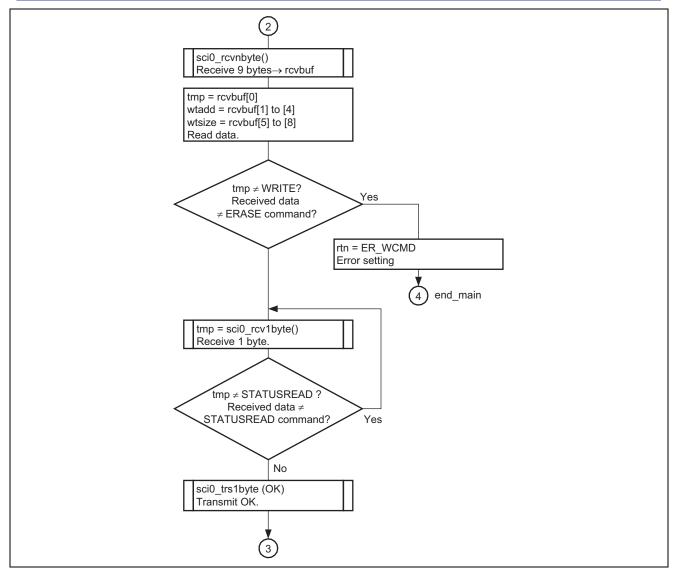

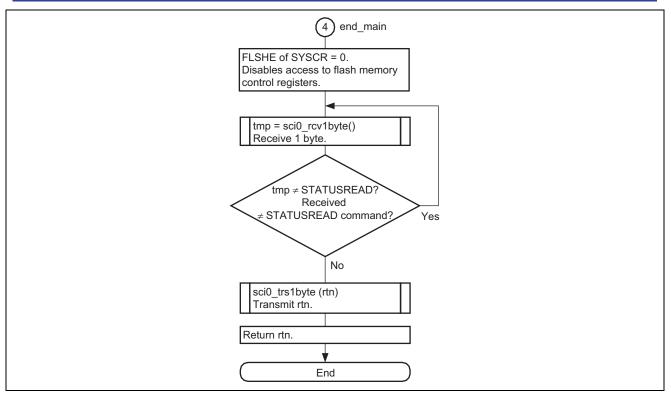

#### 6.2.1 flew\_main Function

### 1. Functional overview

Main processing of flash memory erasing/programming

| $\mathbf{r}$ | Argumonto |

|--------------|-----------|

| <i>L</i> .   | Arguments |

None

| 3. | Return | value |  |

|----|--------|-------|--|

|----|--------|-------|--|

| 5. Return value |              |  |

|-----------------|--------------|--|

| Туре            | Description  |  |

| unsigned char   | Error status |  |

### 4. Internal registers used

The internal registers used in this sample task are described below. Note that the settings shown below are not the initial values but the values used in this sample task.

### • System control register (SYSCR) Number of bits: 16 Address: H'FFFDC2

| Bit    | Bit Name         | Setting        | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------|------------------|----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7      | FLSHE            | 1              | R/W       | <ul> <li>Flash Memory Control Register Enable</li> <li>Controls accesses by the CPU to the flash memory control registers. Setting this bit to 1 enables read from/write to the flash memory control registers. Clearing this bit to 0 disables the flash memory control registers. At this time, the contents of the flash memory control registers are retained.</li> <li>0: Disables the flash memory control registers.</li> <li>1: Enables the flash memory control registers.</li> </ul> |  |

| • Flas | sh program cod   | e select regi  | ster (FPC | S) Number of bits: 8 Address: H'FFFDE9                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Bit    | Bit Name         | Setting        | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0      | PPVS             | 1              | R/W       | Program Pulse Verify                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|        |                  |                |           | Selects the programming program to be downloaded.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|        |                  |                |           | 0: Does not select programming program.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|        |                  |                |           | [Clearing condition]                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|        |                  |                |           | Completion of transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|        |                  |                |           | 1: Selects programming program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| • Flag | sh erase code se | elect register | (FFCS)    | Number of bits: 8 Address: H'FFFDEA                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Bit    | Bit Name         | Setting        | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0      | EPVB             | 1              | R/W       | Erase Pulse Verify Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Ŭ      | 2 0              | •              |           | Selects the erasing program to be downloaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|        |                  |                |           | 0: Does not select erasing program.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|        |                  |                |           | [Clearing condition]                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|        |                  |                |           | Completion of transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|        |                  |                |           | 1: Selects erasing program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|        |                  |                |           | ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

### 5. Flowchart

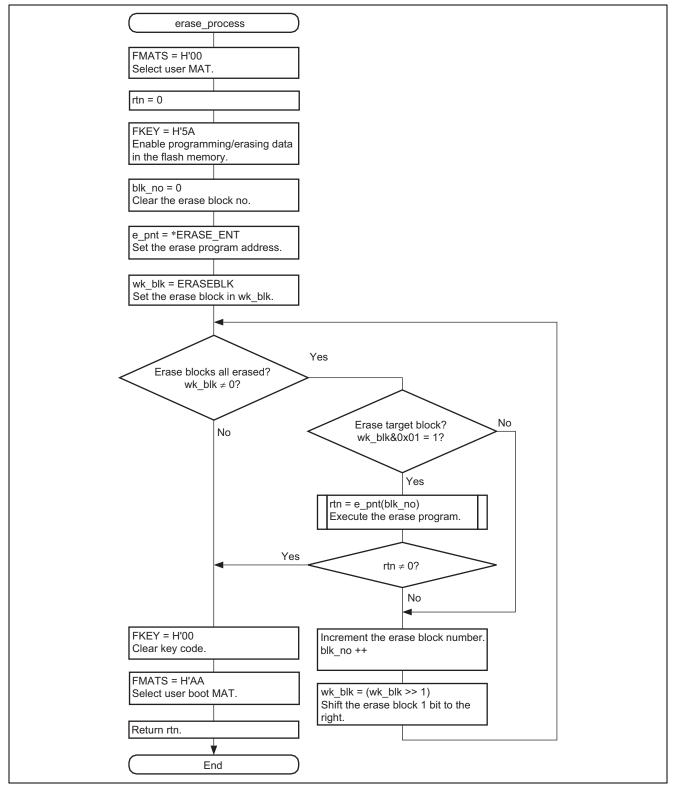

### 6.2.2 erase\_process Function

1. Functional overview

Erase flash memory.

#### 2. Arguments

| unsigned long ERASEBLK Erases block. | Туре          | Variable Name | Description   |

|--------------------------------------|---------------|---------------|---------------|

|                                      | unsigned long | ERASEBLK      | Erases block. |

3. Return value

| Туре          | Description                          |  |  |  |

|---------------|--------------------------------------|--|--|--|

| unsigned char | Flash pass and fail parameter (FPFR) |  |  |  |

|               | Return value of the erase result.    |  |  |  |

### 4. Internal registers used

The internal registers used in this sample task are described below. Note that the settings shown below are not the initial values but the values used in this sample task.

| ٠ | Flash key code register (FKEY) | Number of bits: 8 | Address: H'FFFDEC |

|---|--------------------------------|-------------------|-------------------|

|---|--------------------------------|-------------------|-------------------|

| Bit | Bit Name                                                                                                        | Setting | R/W                                                                                                                                                                                        | Description                                                                                                                                       |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | K7                                                                                                              | 0       | R/W                                                                                                                                                                                        | Key Code                                                                                                                                          |  |  |  |

| 6   | K6                                                                                                              | 1       | R/W                                                                                                                                                                                        | When H'A5 is written to FKEY, writing to the SCO bit in FCCS is                                                                                   |  |  |  |

| 5   | K5                                                                                                              | 0       | R/W enabled. When a value other than H'A5 is written, the SC                                                                                                                               |                                                                                                                                                   |  |  |  |

| 4   | K4                                                                                                              | 1       | R/W                                                                                                                                                                                        | connet be get to 1. Therefore, the on ship program connet be                                                                                      |  |  |  |

| 3   | K3                                                                                                              | 1       | R/W                                                                                                                                                                                        | programming/erasing of the flash memory can be executed.                                                                                          |  |  |  |

| 2   | K2                                                                                                              | 0       | R/WWhen a value other than H'5A is written, even if the<br>programming/erasing program is executed,<br>programming/erasing cannot be performed.R/Wprogramming/erasing cannot be performed. |                                                                                                                                                   |  |  |  |

| 1   | K1                                                                                                              | 1       |                                                                                                                                                                                            |                                                                                                                                                   |  |  |  |

| 0   | K0                                                                                                              | 0       |                                                                                                                                                                                            | programming/erasing cannot be performed.                                                                                                          |  |  |  |

|     | H'A5: Writing to the SCO bit is enabled. (The SCO bit cannot be set to 1 when FKEY is a value other than H'A5.) |         |                                                                                                                                                                                            |                                                                                                                                                   |  |  |  |

|     |                                                                                                                 |         |                                                                                                                                                                                            | H'5A: Programming/erasing of the flash memory is enabled.<br>(When FKEY is a value other than H'5A, the software<br>protection state is entered.) |  |  |  |

|     |                                                                                                                 |         |                                                                                                                                                                                            | H'00: Initial value                                                                                                                               |  |  |  |

• Flash MAT select register (FMATS) Number of bits: 8 Address: H'FFFEAD

| Bit | Bit Name | Setting | R/W | Description                                                   |

|-----|----------|---------|-----|---------------------------------------------------------------|

| 7   | MS7      | 0       | R/W | MAT Selection                                                 |

| 6   | MS6      | 0       | R/W | The memory MATs can be switched by writing a value to         |

| 5   | MS5      | 0       | R/W | FMATS.                                                        |

| 4   | MS4      | 0       | R/W | When H'AA is written to FMATS, the user boot MAT is selected. |

| 3   | MS3      | 0       | R/W | When a value other than H'AA is written, the user MAT is      |

| 2   | MS2      | 0       | R/W | selected. In the user boot mode:                              |

| 1   | MS1      | 0       | R/W | H'AA: The user boot MAT is selected.                          |

| 0   | MS0      | 0       | R/W | A value other than H'AA: The user MAT is selected.            |

• Flash pass and fail parameter (FPFR) (CPU general register R0L) Return value of the erase results

| Bit | Bit Name | Setting   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | MD       | Undefined | R/W | Erasing Mode Related Setting Error Detect<br>Detects the error protection state and returns the result. When<br>the error protection state is entered, this bit is set to 1.<br>Whether the error protection state is entered or not can be<br>performed with the FLER bit of the FCCS register.<br>0: Normal operation (FLER = 0)<br>1: Error protection state, and programming cannot be<br>performed (FLER = 1) |

| 5   | EE       | Undefined | R/W | <ul> <li>Erasing Execution Error Detect</li> <li>Writes 1 to this bit when the specified data could not be written because the user MAT was not erased. If this is set to 1, there is a high possibility that the user MAT has been written partially. In this case, after removing the error factor, erase the user MAT.</li> <li>0: Erasure has ended normally.</li> </ul>                                       |

|     |          |           |     | 1: Erasure has ended abnormally.                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | FK       | Undefined | R/W | <ul> <li>Flash Key Register Error Detect</li> <li>Checks the FKEY value (H'A5) before programming starts, and returns the results.</li> <li>0: FKEY setting is normal (H'5A).</li> <li>1: FKEY setting is abnormal (a value other than H'5A).</li> </ul>                                                                                                                                                           |

| 3   | EB       | Undefined | R/W | <ul> <li>Erase Block Selection Error Detect</li> <li>Checks whether the specified erase block number is in the block range of user MAT and returns the result.</li> <li>0: Setting of erase block number is normal.</li> <li>1: Setting of erase block number is abnormal.</li> </ul>                                                                                                                              |

| 0   | SF       | Undefined | R/W | Success/Fail<br>Indicates the erasure results.<br>0: Erasure ended normally (no error).<br>1: Erasure ended abnormally (error occurred).                                                                                                                                                                                                                                                                           |

• Flash erase block select parameter (FEBS) (CPU general register ER0)

Sets the erase block number in the range from 0 to 19. Number 0 corresponds to block EB0 and number 19 corresponds to block EB19. An error occurs when a number other than 0 to 19 is set.

Setting: blk\_no

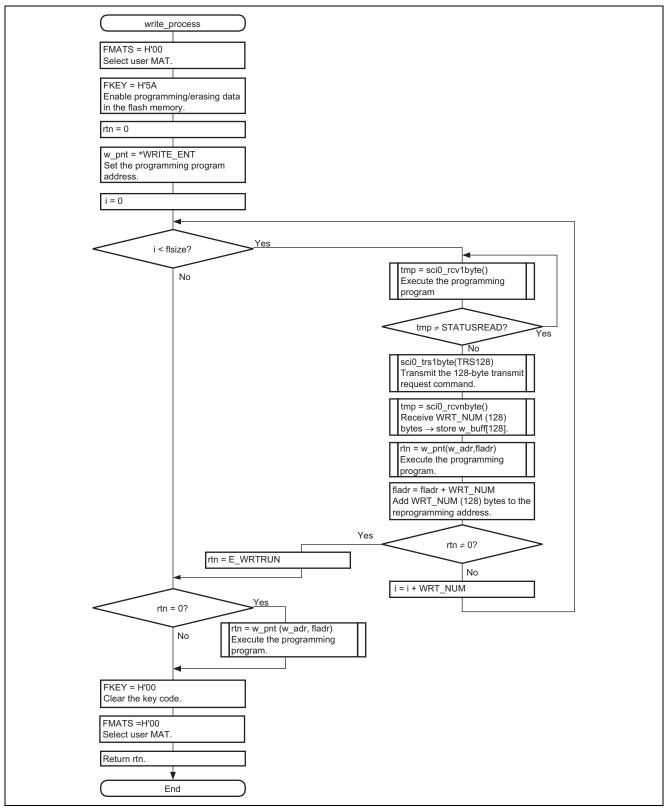

### 6.2.3 write\_process Function

1. Functional overview

Programs flash memory.

#### 2. Arguments

| Туре          | Variable Name | Description                 |

|---------------|---------------|-----------------------------|

| unsigned long | fladr         | Reprogramming start address |

| unsigned long | flsize        | Reprogramming size          |

#### 3. Return value

| Туре          | Description                             |

|---------------|-----------------------------------------|

| unsigned char | Flash pass and fail parameter (FPFR)    |

| Ū             | Return value of the programming result. |

#### 4. Internal registers used

The internal registers used in this sample task are described below. Note that the settings shown below are not the initial values but the values used in this sample task.

| Bit | Bit Name | Setting | R/W | Description                                                                                                                                       |

|-----|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | K7       | 0       | R/W | Key code                                                                                                                                          |

| 6   | K6       | 1       | R/W | When H'A5 is written to FKEY, writing to the SCO bit in FCCS is                                                                                   |

| 5   | K5       | 0       | R/W | enabled. When a value other than H'A5 is written, the SCO bit                                                                                     |

| 4   | K4       | 1       | R/W | cannot be set to 1. Therefore, the on-chip program cannot be                                                                                      |

| 3   | K3       | 1       | R/W | downloaded to the on-chip RAM. Only When H'5A is written, programming/erasing of the flash memory can be executed.                                |

| 2   | K2       | 0       | R/W | When a value other than H'5A is written, even if the                                                                                              |

| 1   | K1       | 1       | R/W | programming/erasing program is executed,                                                                                                          |

| 0   | K0       | 0       | R/W | programming/erasing cannot be performed.                                                                                                          |

|     |          |         |     | H'A5: Writing to the SCO bit is enabled. (The SCO bit cannot be set to 1 when FKEY is a value other than H'A5.)                                   |

|     |          |         |     | H'5A: Programming/erasing of the flash memory is enabled.<br>(When FKEY is a value other than H'5A, the software<br>protection state is entered.) |

|     |          |         |     | H'00: Initial value                                                                                                                               |

| Bit | Bit Name | Setting | R/W | Description                                                                                |

|-----|----------|---------|-----|--------------------------------------------------------------------------------------------|

| 7   | MS7      | 0       | R/W | MAT Selection                                                                              |

| 6   | MS6      | 0       | R/W | The memory MATs can be switched by writing a value to                                      |

| 5   | MS5      | 0       | R/W | FMATS.                                                                                     |

| 4   | MS4      | 0       | R/W | When H'AA is written to FMATS, the user boot MAT is selected.                              |

| 3   | MS3      | 0       | R/W | When a value other than H'AA is written, the user MAT is                                   |

| 2   | MS2      | 0       | R/W | selected. In the user boot mode:                                                           |

| 1   | MS1      | 0       | R/W | H'AA: The user boot MAT is selected.<br>A value other than H'AA: The user MAT is selected. |

| 0   | MS0      | 0       | R/W | A value other than n AA. The user MAT is selected.                                         |

• Flash pass and fail parameter (FPFR) (CPU general register R0L) Return value of the erase results

| Bit | Bit Name | Setting   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|----------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | MD       | Undefined | R/W | Programming Mode Related Setting Error Detect<br>Detects the error protection state and returns the result. When<br>the error protection state is entered, this bit is set to 1.<br>Whether the error protection state is entered or not can be<br>performed with the FLER bit of the FCCS register.<br>0: Normal operation (FLER = 0)                                                                                                                                                                                             |

|     |          |           |     | <ol> <li>Error protection state, and programming cannot be<br/>performed (FLER = 1)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5   | EE       | Undefined | R/W | Programming Execution Error Detect<br>Writes 1 to this bit when the specified data could not be written<br>because the user MAT was not erased. If this is set to 1, there<br>is a high possibility that the user MAT has been written<br>partially. In this case, after removing the error factor, erase the<br>user MAT.                                                                                                                                                                                                         |

|     |          |           |     | 0: Erasure has ended normally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |           |     | 1: Erasure has ended abnormally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | FK       | Undefined | R/W | <ul> <li>Flash Key Register Error Detect</li> <li>Checks the FKEY value (H'A5) before programming starts, and returns the results.</li> <li>0: FKEY setting is normal (H'5A).</li> <li>1: EKEX setting is apparent (a value other than H'5A).</li> </ul>                                                                                                                                                                                                                                                                           |

| 2   | WD       | Undefined | R/W | 1: FKEY setting is abnormal (a value other than H'5A).<br>Write Data Address Detect                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ζ   | WD       | Undenned  | N/W | <ul> <li>When an address belet</li> <li>When an address not in the flash memory area is specified as the start address of the storage destination for the program data, an error occurs.</li> <li>0: Setting of the start address of the storage destination for the program data is normal.</li> <li>1: Setting of the start address of the storage destination for the program data is abnormal.</li> </ul>                                                                                                                      |

| 1   | WA       | Undefined | R/W | <ul> <li>Write Address Error Detect</li> <li>When the following items are specified as the start address of the programming destination, an error occurs.</li> <li>An area other than flash memory</li> <li>The specified address is not aligned with the 128-byte boundary.<br/>(lower eight bits of the address are other than H'00 and H'80)</li> <li>0: Setting of the start address of the programming destination is normal.</li> <li>1: Setting of the start address of the programming destination is abnormal.</li> </ul> |

| 0   | SF       | Undefined | R/W | Success/Fail<br>Indicates the program results.<br>0: Programming ended normally (no error).<br>1: Programming ended abnormally (error occurred).                                                                                                                                                                                                                                                                                                                                                                                   |

• Flash multipurpose address area parameter (FMPAR) (CPU general register ER1)

ENESAS

FMPAR sets the start address of the programming destination on the user MAT.

When an address in an area other than the flash memory is set, or the start address of the programming destination is not aligned with the 128-byte boundary, an error occurs. The error occurrence is indicated by the WA bit of the FPFR register.

| Bit        | Bit Name         | Setting                      | R/W | Description                                                                                                                                                                                                                                                                                                                 |

|------------|------------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to<br>0 | MOA31 to<br>MOA0 | fladr<br>(local<br>variable) | R/W | Sets the start address of the programming destination on the user MAT. Consecutive 128-byte programming is executed starting from the specified start address of the user MAT. Therefore, the specified start address of the programming destination becomes a 128-byte boundary, and MOA6 to MOA0 are always cleared to 0. |

• Flash multipurpose data destination parameter (FMPDR)

(CPU general register ER0)

FMPDR sets the start address in the area which stores the data to be programmed in the user MAT. When the storage destination for the program data is in flash memory, an error occurs. The error occurrence is indicated by the WD bit in FPFR.

| Bit        | Bit Name         | Setting                      | R/W | Description                                                                                                                                                                                 |

|------------|------------------|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to<br>0 | MOD31 to<br>MOD0 | fladr<br>(local<br>variable) | R/W | Sets the start address of the area which stores the program data<br>for the user MAT. Consecutive 128-byte data is programmed to<br>the user MAT starting from the specified start address. |

### 6.2.4 download Function

1. Functional overview

Downloads the on-chip modules.

2. Arguments None

3. Return value

| Туре          | Description                                    |

|---------------|------------------------------------------------|

| unsigned char | Download pass and fail result parameter (DPFR) |

|               | Return value of the download result.           |

4. Internal registers used

The internal registers used in this sample task are described below. Note that the settings shown below are not the initial values but the values used in this sample task.

| • | Flash key code register (FKEY) | Number of bits: 8 | Address: H'FFFDEC |

|---|--------------------------------|-------------------|-------------------|

|---|--------------------------------|-------------------|-------------------|

| Bit | Bit Name | Setting | R/W | Description                                                                                                                                       |

|-----|----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | K7       | 1       | R/W | Key Code                                                                                                                                          |

| 6   | K6       | 0       | R/W | When H'A5 is written to FKEY, writing to the SCO bit in FCCS is                                                                                   |

| 5   | K5       | 1       | R/W | enabled. When a value other than H'A5 is written, the SCO bit                                                                                     |

| 4   | K4       | 0       | R/W | cannot be set to 1. Therefore, the on-chip program cannot be                                                                                      |

| 3   | K3       | 0       | R/W | downloaded to the on-chip RAM. Only When H'5A is written, programming/erasing of the flash memory can be executed.                                |

| 2   | K2       | 1       | R/W | When a value other than H'5A is written, even if the                                                                                              |