### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

### M16C/80 Group

### Explanation of boot loader

#### 1.0 Abstract

This application note describes the communication protocol specifications of the boot loader and the rewrite program prepared by the user.

#### **2.0 Introduction**

The explanation of this issue is applied to the following condition: Applicable MCU: M16C/80 group

#### 3.0 Contents

#### 3.1 Overview of Bootloader

External ROM version of M16C/80 group with built-in bootloader (hereinafter referred to as "M16C/80 bootloader) contains firmware (hereinafter referred to as "bootloader") which downloads a boot program (hereinafter referred to as "rewrite program") to the microcontroller for reprogramming of the external Flash memory. Table 3.1.1 shows the product list of M16C/80 bootloader.

With a serial writer or personal computer, a rewrite program is downloaded to the internal RAM on the microcontroller for execution via serial communications with M16C/80 bootloader. Besides the said down-load function, the bootloader has another optional function, flash memory control function. This is to repro-gram a certain type of external flash memories (\*1).

The download and flash memory control functions are described in <u>3.2 Overview of bootloader mode 1 (clock</u> <u>synchronized)</u> and <u>3.3 Overview of boot loader mode 2 (clock asynchronized)</u>

\*1: Mitsubishi flash memory M5M29GB/T160BVP, M5M29GB/T320BVP and MCMs combined with the these flash memories only.

#### 3.1.1 Bootloader Mode

When a reset is released by applying an "H" level to CNVss pin, M16C/80 bootloader starts the operation in the microprocessor mode. On the other hand, when a reset is released by applying an "L" level to CNVss pin, M16C/80 bootloader starts the operation in the bootloader program and this mode is called "bootloader mode."

#### Table 3.1.1 Product List

As of Oct., 2001

| Type No      | ROM capacity | RAM capacity | Package type | Remarks                   |

|--------------|--------------|--------------|--------------|---------------------------|

| M30800SFP-BL |              | 10 Kbytes    | 100P6S-A     | External ROM version with |

| M30800SGP-BL |              |              | 100P6Q-A     | built-in bootloader       |

| M30802SGP-BL |              |              | 144P6Q-A     |                           |

| M30803SFP-BL |              | 24 Kbytes    | 100P6S-A     |                           |

| M30803SGP-BL |              |              | 100P6Q-A     |                           |

| M30805SGP-BL |              |              | 144P6Q-A     |                           |

#### 3.1.2 Overview of Bootloader Mode

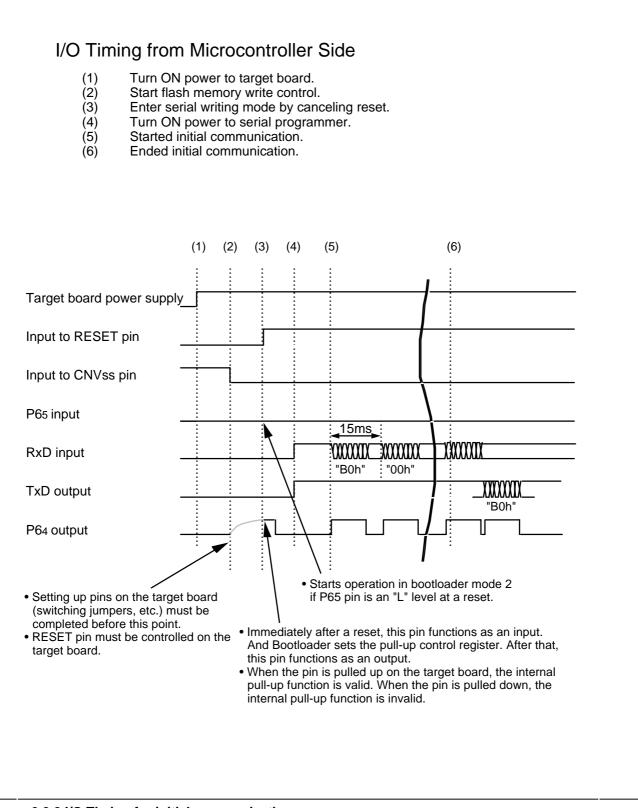

There are two bootloader modes: Bootloader mode 1, which is clock synchronized, and Bootloader mode 2, which is asynchronized. Communications with external devices are performed using a serial programmer (\*1).

These bootloader modes start when a reset is released by applying an "L" level to CNVss. Inputs/outputs of serial data are transferred in 8-bit units with UART1. The bootloader switches between mode 1 (clock synchronized) and mode 2 (clock asynchronized) according to the level of the SCLK pin when the reset is released.

To use bootloader mode 1 (clock synchronized), apply an "H" level to the SCLK pin and release the reset. The operation uses four UART1 pins CLK1, RxD1, TxD1 and RTS1. The CLK1 pin becomes the transfer clock input pin SCLK and inputs an external transfer clock. The TxD1 pin becomes TxD. This pin is for CMOS output. The RTS1 pin becomes BUSY output and outputs an "L" level when ready for reception and an "H" when reception starts.

To use bootloader mode 2 (clock asynchronized), apply an "L" level to the SCLK pin and release the reset. The operation uses two UART1 pins RxD1 and TxD1 as RxD and TxD.

The bootloader switches whether to enable or disable the built-in pull-up function according to the level of the BUSY pin when the reset is released. Immediately after being reset, if an "L" level is applied to the BUSY pin, then the pull-up function become disable, and if an "H" then enable. Table 3.1.2 shows pin functions, and Figure 3.1.1 to 3.1.3 show pin connections for bootloader mode.

\*1: Bootloader mode 1 (clock synchronized) can be used with PC card type flash memory programmer (M3A-0655G01/02) and Sunny Giken serial writer Multi Flash Write. Bootloader mode 2 (clock asynchronized) can be used with M16C Flash Starter (M3A-0806).

Note: Users are usually required to develop a serial writer together with a rewrite program.

#### Table 3.1.2 Pin functions

| Pin                    | Name                      | I/O | Description                                                                                                  |

|------------------------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------|

| Vcc, Vss               | Power input               |     | Apply 4.2V to 5.5V(*1) to Vcc pin and 0V to Vss pin                                                          |

| CNVss                  | CNVss                     | I   | Connect to Vss pin                                                                                           |

| RESET                  | RESET input               | I   | RESET input pin. While reset is "L" level, a 20 cycle or longer clock must be input to XIN pin.              |

| XIN                    | Clock input               | I   | Connect a ceramic resonator or crystal oscillator between X IN                                               |

| Хоит                   | Clock output              | 0   | and $X_{OUT}$ pins. To input an externally generated clock, input it to $X_{IN}$ pin and open $X_{OUT}$ pin. |

| BYTE                   | BYTE input                | I   | Connect this pin to Vcc or Vss.                                                                              |

| AVcc, AVss             | Analog power supply input | I   | Connect AVss to Vss and AVcc to Vcc, respectively.                                                           |

| Vref                   | Reference voltage input   | I   | Enter the reference voltage for A-D converter from this pin.                                                 |

| P00 to P07             | Input port P0             | I/O | Connect to memory or input "H" or "L" level signal or open.                                                  |

| P10 to P17             | Input port P1             | I/O | Connect to memory or input "H" or "L" level signal or open.                                                  |

| P20 to P27             | Input port P2             | I/O | Connect to memory or input "H" or "L" level signal or open.                                                  |

| P30 to P37             | Input port P3             | I/O | Connect to memory or input "H" or "L" level signal or open.                                                  |

| P40 to P47             | Input port P4             | I/O | Connect to memory or input "H" or "L" level signal or open.                                                  |

| P50 to P52             | Input port P5             | I/O | Connect to memory or input "H" or "L" level signal or open.                                                  |

| P53 to P54             | Input port P5             |     | Input "H" or "L" level signal or open.                                                                       |

| P55                    | HOLD input                |     | Input "H" level signal.                                                                                      |

| P56                    | Input port P5             |     | Input "H" or "L" level signal or open.                                                                       |

| P57                    | RDY input                 |     | Input "H" level signal.                                                                                      |

| P60 to P63             | Input port P6             | I   | Input "H" or "L" level signal or open.                                                                       |

| P64/RTS1               | BUSY output (*2)          | 0   | Boot loader mode 1: BUSY signal output.<br>Boot loader mode 2: Monitors the program operation check.         |

| P65/CLK1               | SCLK input                | 1   | Boot loader mode 1: Serial clock input.<br>Boot loader mode 2: Input "L" level signal.                       |

| P66/RxD1               | RxD input                 | 1   | Serial data input pin.                                                                                       |

| P67/TxD1               | TxD output                | 0   | Serial data output pin.                                                                                      |

| P70 to P77             | Input port P7             | I   | Input "H" or "L" level signal or open.                                                                       |

| P80 to P84<br>P86, P87 | Input port P8             | I   | Input "H" or "L" level signal or open.                                                                       |

| P85                    | NMI input                 |     | Connect this pin to Vcc.                                                                                     |

| P90 to P97             | Input port P9             | I   | Input "H" or "L" level signal or open.                                                                       |

| P100 to P107           | Input port P10            | I   | Input "H" or "L" level signal or open.                                                                       |

| P110 to P114           | Input port P11            | I   | Input "H" or "L" level signal or open.                                                                       |

| P120 to p127           | Input port P12            | I   | Input "H" or "L" level signal or open.                                                                       |

| P130 to P137           | Input port P13            | I   | Input "H" or "L" level signal or open.                                                                       |

| P140 to P146           | Input port P14            | I   | Input "H" or "L" level signal or open.                                                                       |

| P150 to P157           | Input port P15            | I   | Input "H" or "L" level signal or open.                                                                       |

\*1: When using at 4.2 V or lower, max. operating frequency is 10MHz.

\*2: For further information, please refer to "BUSY Pin Function".

• Shading indicates pins used in bootloader mode.

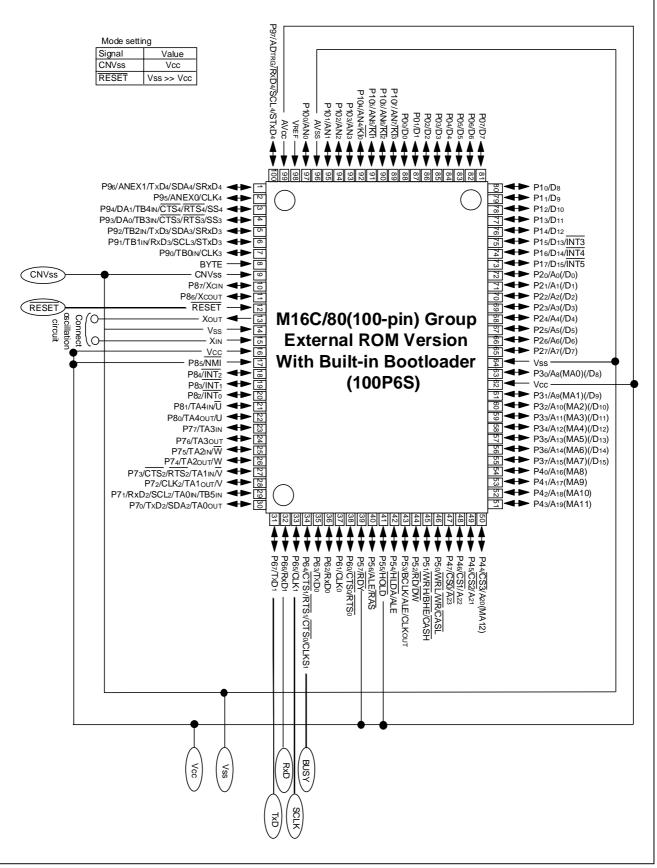

Figure 3.1.1 Pin connections for bootloader mode (100P6S)

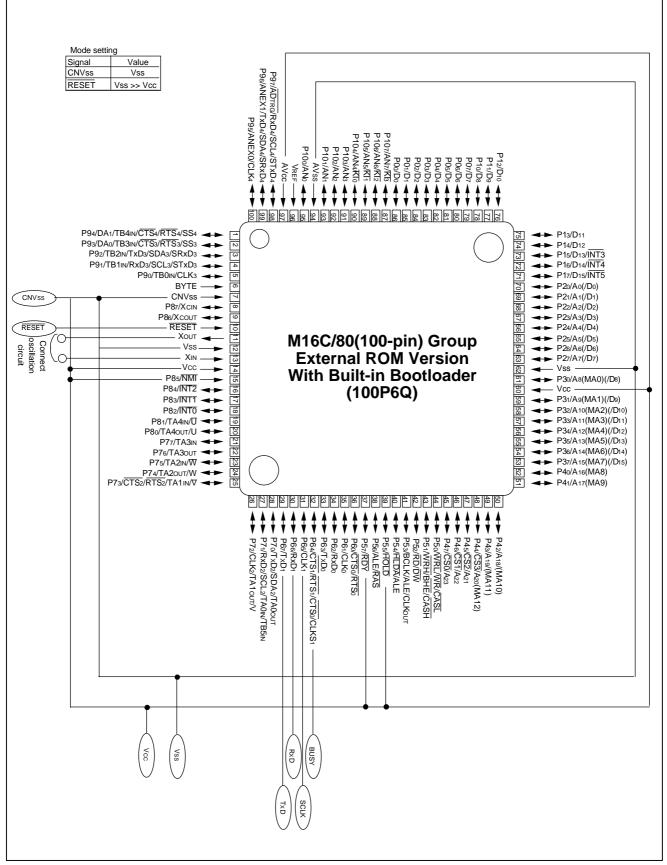

Figure 3.1.2 Pin connections for bootloader mode (100P6Q)

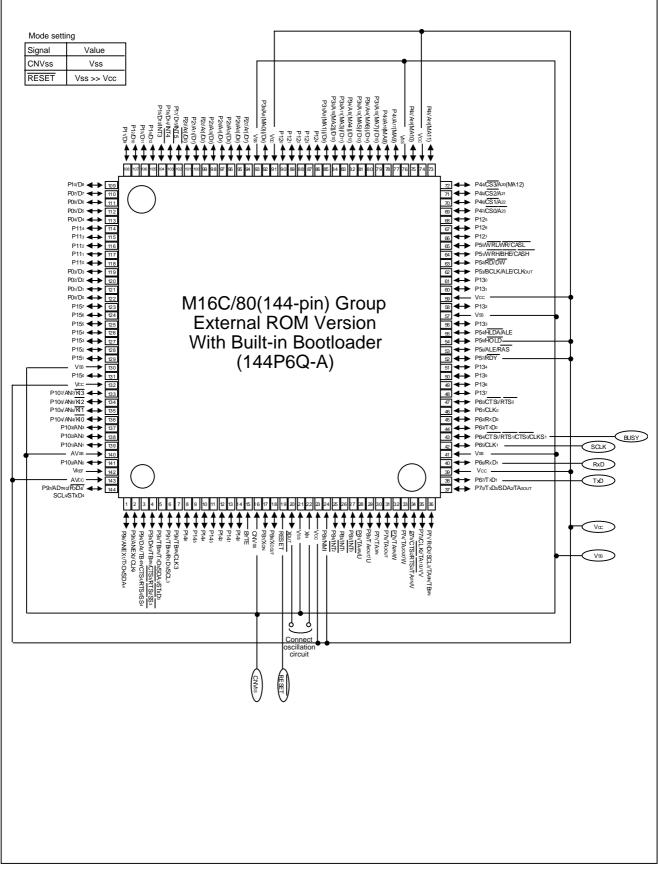

Figure 3.1.3 Pin connections for bootloader mode (144P6Q)

#### 3.1.3 BUSY Pin Description

Immediately after being reset, the BUSY(P6\_4/RTS1) pin functions as an input. And the bootloader selects whether to enable or disable the built-in pull-up function according to the level of BUSY pin at this moment. (On user's target board, please use a pull-up or pull-down of the BUSY pin to select enabling or disabling the pull-up function.) Immediately after being reset, if an "L" level is applied to the BUSY pin, the pull-up function is disabled, and if an "H" then enabled. After the selection, the BUSY pin functions as an output.

Table 3.1.3 shows pull-up pins when the internal pull-up function becomes enabled.

| Pull-up pin              | Setting of pull-up control register |

|--------------------------|-------------------------------------|

| P0 to P3 (Note)          | PUR0 = 0FF16                        |

| P4, P5 (Note)            | PUR1 = 0F16                         |

| P6 to P9 (P8_5 excluded) | PUR2 = 0FF16                        |

| P10 to P13               | PUR3 = 0FF16                        |

| P14, 15                  | PUR4 = 0F16                         |

#### Table 3.1.3 Pull-up pins and settings for internal pull-up function

Note: Before changing to microprocessor mode, please set the value of the P0 to P5 pull-up control registers, which function as bus, to "0" for disabling internal pull-up function.

#### 3.2 Overview of bootloader mode 1 (clock synchronized)

In bootloader mode 1, software commands, addresses and data are input and output between the MCU and serial programmer (\*1) using 4-wire clock-synchronized serial I/O (UART1). Bootloader mode 1 is engaged by releasing the reset with the SCLK pin "H" level.

In reception, software commands, addresses and program data are synchronized with the rise of the transfer clock that is input to the SCLK pin, and are then input to the MCU via the RxD pin. In transmission, the read data and status are synchronized with the fall of the transfer clock, and output from the TxD pin.

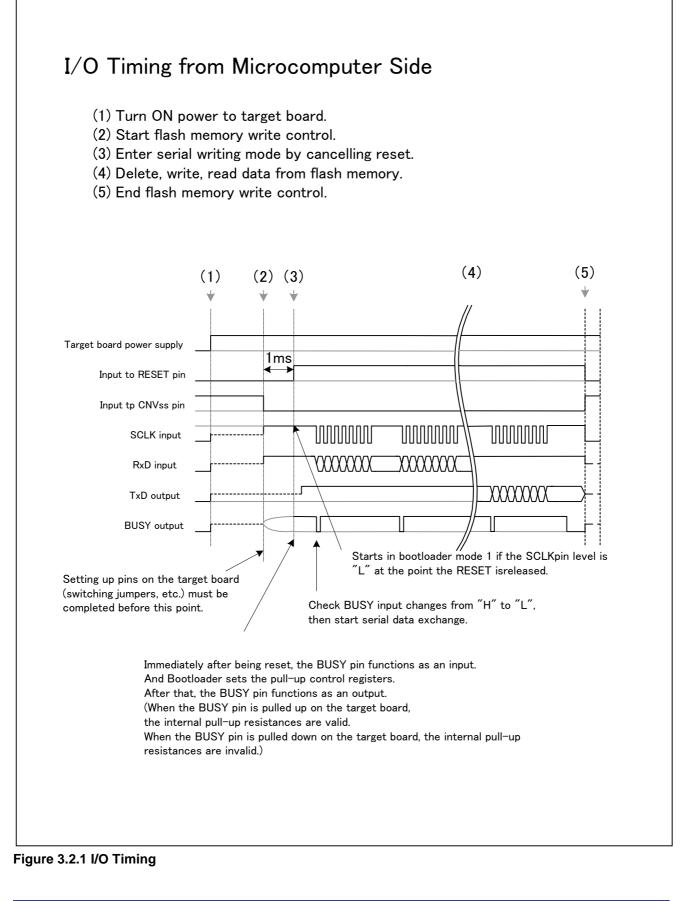

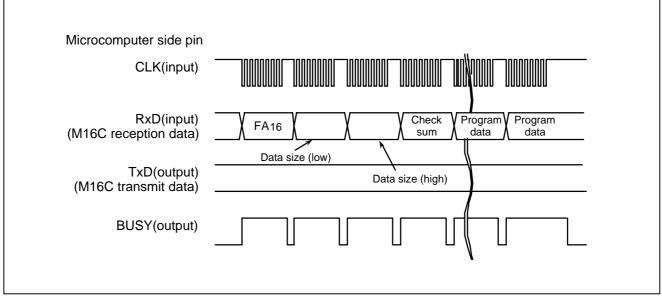

The TxD pin is for CMOS output. Transfer is in 8-bit units with LSB first. When busy, such as during transmission, reception, software command execution, the BUSY pin is "H" level. Accordingly, always start the next transfer after the BUSY pin is "L" level.(refer to figure 3.2.1 I/O Timing)

Bootloader mode 1 supports the download and the flash memory control functions. Here following are explained these function.

\*1: MAEC PC card type flash memory programmer and Sunny Giken Multi Flash Writer can be used for the serial programmer

MAEC-MCU-M16C-95-0302-R1.0

#### 3.2.1 Download Function

#### **Functional Description**

The download function of M16C/80 Bootloader is to download a rewrite program (\*1) to the internal RAM in the microcomputer using serial communications and then let the processing jump to the ad-dress in the RAM where the downloaded program has been located.

\*1: The rewrite program should be prepared by the user according to the following notes.

- The rewrite program should have two functions: (1) control function to write, erase and read to/from the external flash and (2) communication function to communicate with a serial writer.

- When using a stack in the rewrite program, please setup the stack pointer within the program.

- When the download is completed, the microcomputer starts the operation in single chip mode. Please change the processor mode from the single chip mode to microprocessor mode using the rewrite program before starting controls such as writing or erasing to the external flash memory.

- Please do not use any interrupts in the rewrite program.

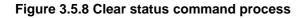

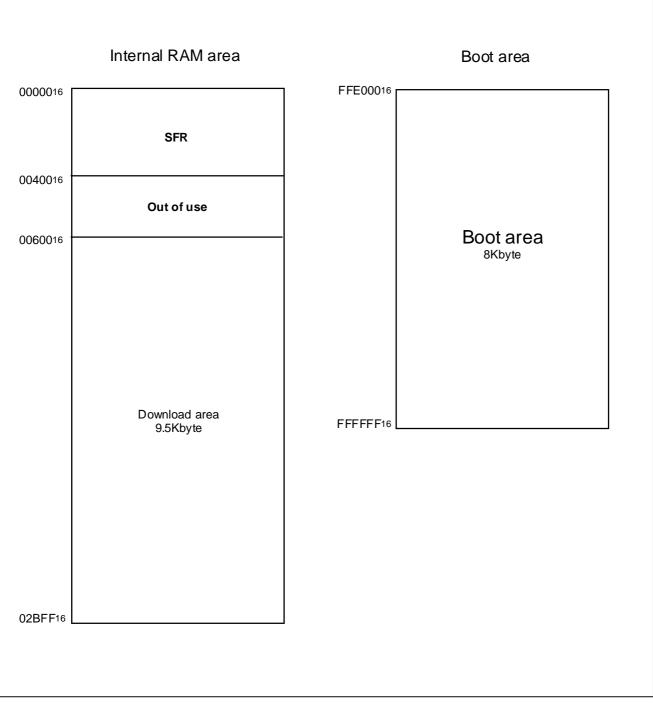

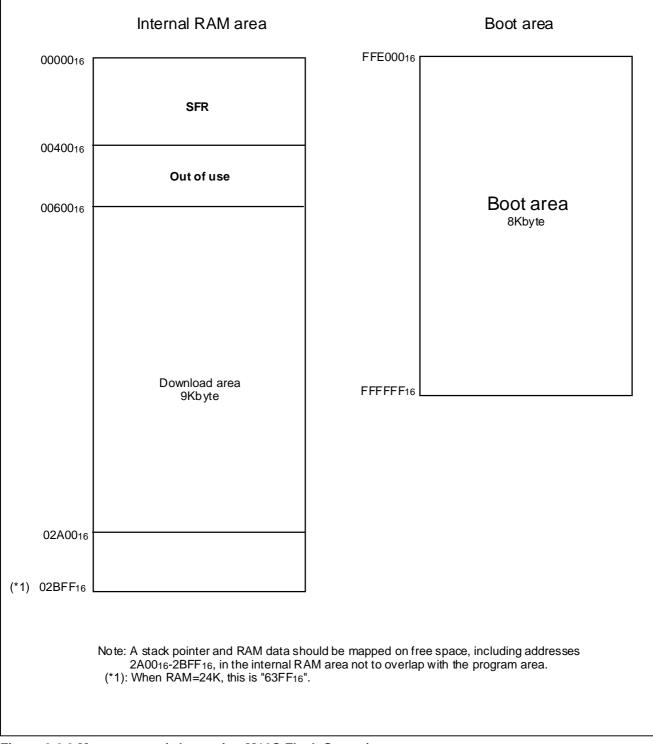

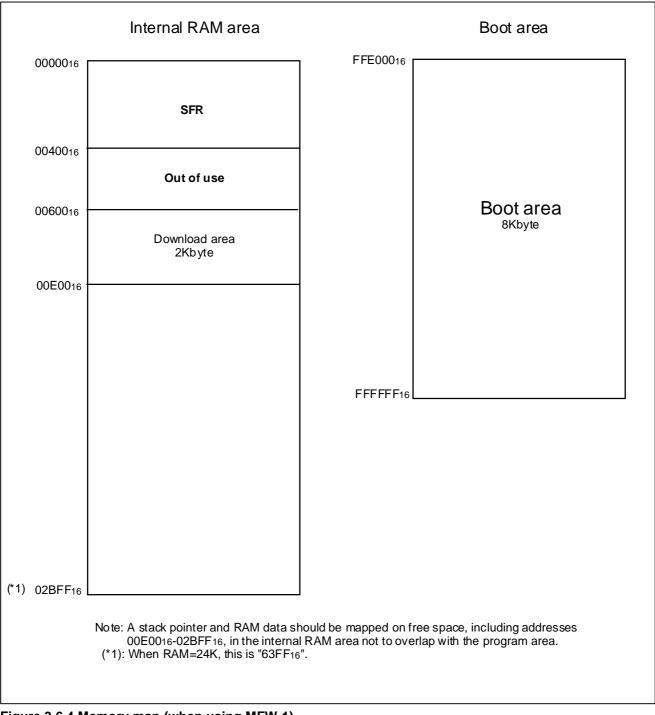

- Please refer to the memory map of the Appendix 1 for the details of download area.

#### Software commands

Table 3.2.1 lists the software commands for bootloader mode 1.

|   | Control command              | 1st byte<br>transfer | 2nd byte                  | 3rd byte                  | 4th byte                  | 5th byte                  | 6th byte                             |                                          |

|---|------------------------------|----------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------------------|------------------------------------------|

| 1 | Download function            | FA <sub>16</sub>     | Size<br>(low)             | Size<br>(high)            | Check-<br>sum             | Data<br>input             | To<br>required<br>number<br>of times |                                          |

| 2 | Download result output       | FA <sub>16</sub>     | Data<br>output            |                           |                           |                           |                                      |                                          |

| 3 | Version data output function | FB <sub>16</sub>     | Version<br>data<br>output | Version<br>data<br>output | Version<br>data<br>output | Version<br>data<br>output | Version<br>data<br>output            | Version<br>data<br>output to<br>9th byte |

#### Table 3.2.1 Software commands for download (Boot loader mode 1)

Note 1: Shading indicates transfer from microcomputer to serial programmer. All other data is transferred from the serial programmer to the microcomputer.

#### Download

This command downloads a rewrite program to the internal RAM. The program as downloaded is stored in the internal RAM from address 60016 onward.

After a reset, the downloaded program is held in the internal RAM. Execute the download command as explained here following.

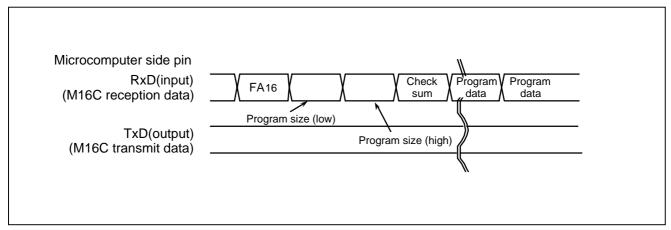

- (1) Transfer the "FA16" command code serially with the 1st byte.

- (2) Transfer the program size serially with the 2nd and 3rd bytes, as follows: low order size with the 2nd byte, and high-order size with the 3rd byte.

- (3) Transfer the check sum serially with the 4th byte. The check sum is added to all data sent with the 5th byte onward.

- (4) The program to execute is sent with the 5th byte onward. The size of the program to be transferred will vary depending on the internal RAM size. (Please refer to "<u>3.6 Memory Map</u>" about the size of the rewrite program.)

When all data has been transferred, the microcomputer automatically executes the download result output command.

Figure 3.2.2 Timing for download

#### Download Result Output

After downloaded, the transferred check sum value from the serial programmer and the check sum value obtained by received data are compared. When the check sum values are matched, "FA16" and "0016"(success) are sent back, and then the processing jumps to the beginning of the downloaded program to execute it. When the values are not matched, "FA16" and "0116"(failure) are sent back and boot program stored in the microcomputer is transferred to RAM again, then this program is executed. (Return to the original state)

When the Download Function has been completed, the bootloader (microcomputer) outputs the execution result as explained here following.

(1) When the Download Function has been completed, output the "FA16" command code with the 1st byte.

(2) Output the download result code ("0016" : success / "0116" : failure) with the 2nd byte.

| Microcomputer side pin              |           |

|-------------------------------------|-----------|

| CLK(input)                          |           |

| RxD(input)<br>(M16C reception data) |           |

| TxD(output)<br>(M16C transmit data) | FA16 data |

| BUSY(output)                        |           |

|                                     |           |

Figure 3.2.3 The timing of download result

#### **Version Information Output Command**

This command outputs the version information data of bootloader.

Execute the version information output command as explained here following.

- (1) Transfer the "FB16" command code serially with the 1st byte.

- (2) The version information will be output serially from the 2nd byte to the 9th byte. This data is composed of 8 ASCII code characters (\*1).

\*1: Version data format is 8 characters by ASCII code,

"VER. X. XX" (X:number).

It is output from "V".

| Microcomputer side pin<br>CLK(input) |      |

|--------------------------------------|------|

| RxD(input)<br>(M16C reception data)  | FB16 |

| TxD(output)<br>(M16C transmit data)  |      |

| BUSY(output)                         |      |

|                                      | "    |

Figure 3.2.4 Timing for version information output

#### 3.2.2 Flash Memory Control Function

#### **Functional Description**

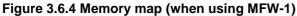

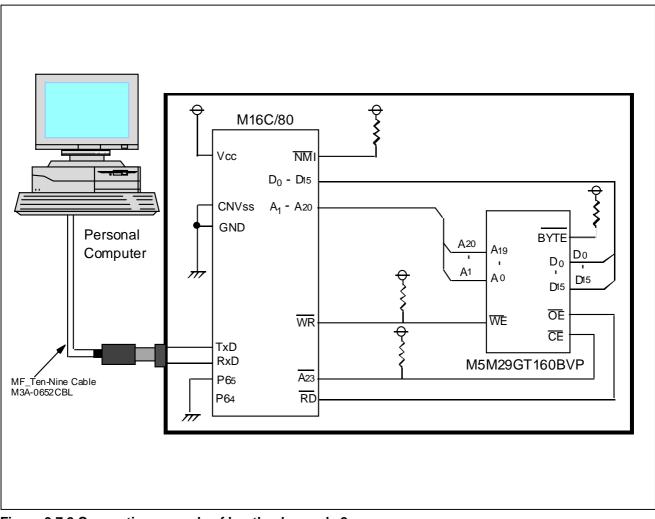

If an external flash memory is M5M29GB/T160BVP, M5M29GB/T320BVP (made by MITSUBISHI) or MCM with these flash memories, the M16C/80 Bootloader is able to execute writing and erasing without rewrite program. (A connection example is shown in "<u>3.7 Connection example of bootloader</u>")

The M16C/80 Bootloader writes and erases a program to flash memory by communicating commands and data with serial programmer.

#### **Software Commands**

The following table lists the flash memory control commands and I/O data. When only an external flash memory is M5M29GB/T160BVP, M5M29GB/T320BVP or MCM with these flash memories, the user is able to use these commands.

|   | Control command           | 1st byte<br>transfer | 2nd byte                | 3rd byte                 | 4th byte                   | 5th byte       | 6th byte       |                                 |

|---|---------------------------|----------------------|-------------------------|--------------------------|----------------------------|----------------|----------------|---------------------------------|

| 1 | Page read                 | FF16                 | Address<br>(middle)     | Address<br>(high)        | Data<br>output             | Data<br>output | Data<br>output | Data<br>output to<br>259th byte |

| 2 | Page program              | 4116                 | Address<br>(middle)     | Address<br>(high)        | Data<br>input              | Data<br>input  | Data<br>input  | Data input<br>to 259th<br>byte  |

| 3 | Block erase               | 2016                 | Address<br>(middle)     | Address<br>(high)        | D016                       |                |                |                                 |

| 4 | Erase all unlocked blocks | A716                 | D016                    |                          |                            |                |                |                                 |

| 5 | Read status register      | 7016                 | SRD<br>output           | SRD1<br>output           |                            |                |                |                                 |

| 6 | Clear status register     | 5016                 |                         |                          |                            |                |                |                                 |

| 7 | Read lock bit status      | 7116                 | Address<br>(middle)     | Address<br>(high)        | Lock bit<br>data<br>output |                |                |                                 |

| 8 | Lock bit program          | <b>77</b> 16         | Address<br>(middle)     | Address<br>(high)        | D016                       |                |                |                                 |

| 9 | Read check data           | FD16                 | Data<br>output<br>(low) | Data<br>output<br>(high) |                            |                |                |                                 |

Note 1: Shading indicates transfer from microcomputer to serial programmer. All other data is transferred from the serial programmer to the microcomputer.

Note 2: SRD refers to status register data, and SRD1 refers to status register 1 data.

#### **Page Read Command**

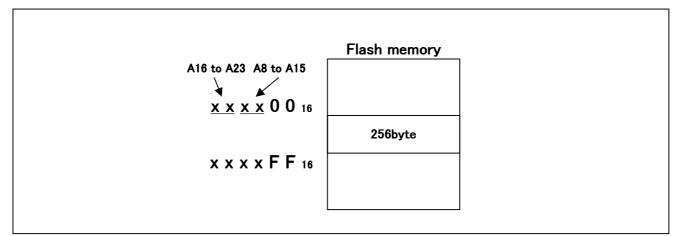

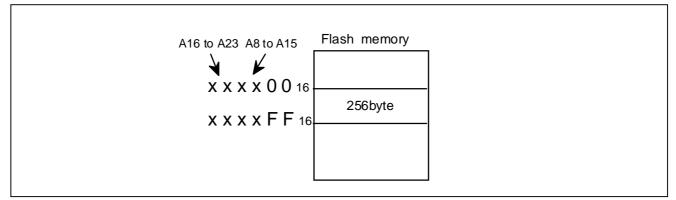

This command reads the specified page (256 bytes) in the flash memory sequentially one byte at a time. The read area is set with a high address (A16 to A23) and middle address (A8 to A15), targeting the 256 bytes from xxxx0016 to xxxxFF16. (Refer to Figure 3.2.5)

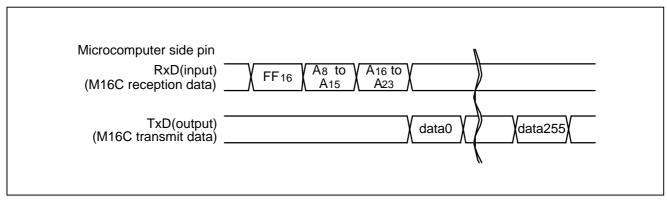

Execute the page read command as explained here following.

- (1) Transfer the "FF16" command code serially with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23 with the 2nd and 3rd bytes respectively.

- (3) From the 4th byte onward, data (Do–D7) for the page (256 bytes) specified with addresses A8 to A23 will be output sequentially from the smallest address first in sync with the fall of the clock.

Figure 3.2.5 The designation of the address and command applicable area

Figure 3.2.6 Timing for page read

#### Page Program Command

This command writes the specified page (256 bytes) in the flash memory sequentially one byte at a time. The area to be written to is set using a high address (A16 to A23) and middle address (A8 to A15), targeting the page between xxxx0016 and xxxxFF16.

Execute the page program command as explained here following.

- (1) Transfer the "4116" command code with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23 with the 2nd and 3rd bytes respectively.

- (3) From the 4th byte onward, as write data (D0–D7) for the page (256 bytes) specified with addresses A8 to A23 is input sequentially from the smallest address first, that page is automatically written.

When reception setup for the next 256 bytes ends, the BUSY signal changes from the "H" to the "L" level. The result of the page program can be known by reading the status register. For more information, see the section on the <u>Read Status Register Command</u>.

Each block can be write-protected with the lock bit. For more information, see the section on the Lock Bit Program Command. Additional writing is not allowed with already programmed pages.

Figure 3.2.7 Timing for the page program

#### **Block Erase Command**

Г

This command erases the data in the specified block. Execute the block erase command as explained here following.

- (1) Transfer the "2016" command code serially with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23 with the 2nd and 3rd bytes respectively.

- (3) Transfer the verify command code "D016" with the 4th byte. With the verify command code, the erase operation will start for the specified block in the flash memory.

When block erasing ends, the BUSY signal changes from the "H" to the "L" level. After block erase ends, the result of the block erase operation can be known by reading the status register. For more information, see the section on the <u>Read Status Register Command</u>.

Each block can be erase-protected with the lock bit. For more information, see the section on the Lock Bit Program Command.

| Microcomputer side pin<br>SCLK(input) |                                                                                                                                                                                |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxD(input)<br>(M16C reception data)   | $ \begin{array}{c c} 2016 \end{array} \begin{array}{c} A8 & to \\ A15 \end{array} \begin{array}{c} A16 & to \\ A23 \end{array} \begin{array}{c} D016 \end{array} \end{array} $ |

| TxD(output)<br>(M16C transmit data)   |                                                                                                                                                                                |

| BUSY(output)                          |                                                                                                                                                                                |

|                                       |                                                                                                                                                                                |

Figure 3.2.8 Timing for block erasing

#### **Erase All Unlocked Blocks Command**

This command erases the content of all blocks. Execute the erase all unlocked blocks command as explained here following.

- (1) Transfer the "A716" command code serially with the 1st byte.

- (2) Transfer the verify command code "D016" with the 2nd byte. With the verify command code, the erase operation will start and continue for all blocks in the flash memory.

When block erasing ends, the BUSY signal changes from the "H" to the "L" level. The result of the erase operation can be known by reading the status register. For more information, see the section on the <u>Read</u> <u>Status Register Command</u>.

Each block can be erase-protected with the lock bit. For more information, see the section on the Lock Bit Program Command.

| Microcomputer side pin<br>SCLK(input) |           |

|---------------------------------------|-----------|

| RxD(input)<br>(M16C reception data)   | A716 D016 |

| TxD(output)<br>(M16C transmit data)   |           |

| BUSY(output)                          |           |

Figure 3.2.9 Timing for erasing all unlocked blocks

#### **Read Status Register Command**

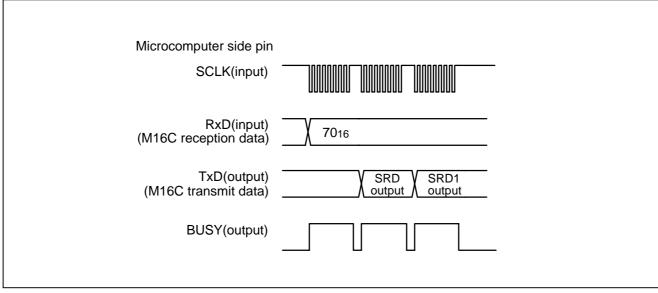

This command reads status information. Execute the read status register command as explained here following.

- (1) Transfer the "7016" command code serially with the 1st byte.

- (2) Output the contents of the status register (SRD) specified with the 2nd byte and the contents of status register 1 (SRD1) specified with the 3rd byte.

Details of "status register", refer to a section of the Status Register(SRD).

Details of "status register 1", refer to a section of the Status Register 1(SRD1).

Figure 3.2.10 Timing for reading the status register

#### Status Register (SRD)

The status register indicates operating status of the flash memory and status such as whether an erase operation or a program ended successfully or in error. It can be read by executing the read status register command (7016). Also, the status register becomes "8016" by executing the clear status register command (5016).

After being reset, the status register outputs "8016" by executing the read status register command.

Table 3.2.3 gives the definition of each status register bit.

| SRD0 bits  | Status name                      | Definition          |                     |  |  |  |

|------------|----------------------------------|---------------------|---------------------|--|--|--|

| SKD0 bits  | Status name                      | "1"                 | "0"                 |  |  |  |

| SR7 (bit7) | Write state machine (WSM) status | Ready               | Busy                |  |  |  |

| SR6 (bit6) | Reserved                         | -                   | -                   |  |  |  |

| SR5 (bit5) | Erase status                     | Terminated in error | Terminated normally |  |  |  |

| SR4 (bit4) | Program status                   | Terminated in error | Terminated normally |  |  |  |

| SR3 (bit3) | Block status after program       | Terminated in error | Terminated normally |  |  |  |

| SR2 (bit2) | Reserved                         | -                   | -                   |  |  |  |

| SR1 (bit1) | Reserved                         | -                   | -                   |  |  |  |

| SR0 (bit0) | Reserved                         | -                   | -                   |  |  |  |

#### Table 3.2.3 Status register (SRD)

#### Write State Machine (WSM) Status (SR7)

The write state machine (WSM) status indicates the operating status of the flash memory. When power is turned on, "1" (ready) is set for it. The bit is set to "0" (busy) during an auto write or auto erase operation, but it is set back to "1" when the operation ends.

#### Erase Status (SR5)

The erase status reports the operating status of the auto erase operation. If an erase error occurs, it is set to "1". If the clear status register command is executed, the erase status is set to "0".

#### Program Status (SR4)

The program status reports the operating status of the auto write operation. If a write error occurs, it is set to "1". If the clear status register command is executed, the program status is set to "0".

#### **Block Status After Program (SR3)**

If excessive data is written, "1" is set for the block status after-program at the end of the page write operation. The block status after-program becomes "0" by executing the clear status register command.

If "1" is written for any of the SR5, SR4 or SR3 bits, the page program, block erase, erase all unlocked blocks and lock bit program commands are not accepted. Before executing these commands, execute the clear status register command (5016).

#### Status Register 1 (SRD1)

Status register 1 indicates the status of serial communications, results from check sum comparisons. It can be read after the SRD by executing the read status register command (7016). Also, bit SR9 of the status register 1 becomes "0" by executing the clear status register command (5016).

Table 3.2.4 gives the definition of each status register 1 bit.

#### Table 3.2.4 Status register 1 (SRD1)

| SRD0 bits  | Chatwa nome               | Definition       |                  |  |  |

|------------|---------------------------|------------------|------------------|--|--|

| SRD0 bits  | Status name               | "1"              | "0"              |  |  |

| SR7 (bit7) | Boot update completed bit | Update completed | Not update       |  |  |

| SR6 (bit6) | Reserved                  | -                | -                |  |  |

| SR5 (bit5) | Reserved                  | -                | -                |  |  |

| SR4 (bit4) | Check sum match bit       | Match            | Mismatch         |  |  |

| SR3 (bit3) | Reserved                  | -                | -                |  |  |

| SR2 (bit2) | Reserved                  | -                | -                |  |  |

| SR1 (bit1) | Data receive time out     | Time out         | Normal operation |  |  |

| SR0 (bit0) | Reserved                  | -                | -                |  |  |

#### Boot Update Completed Bit (SR15)

This flag indicates whether the rewrite program was downloaded to the internal RAM or not, using the download function. After the rewrite program is transferred serially using the download function, this bit is set to "1".

#### Check Sum Consistency Bit (SR12)

This flag indicates whether the check sum matches or not when a rewrite program is downloaded for execution using the download function.

#### Data Reception Time Out (SR9)

This flag indicates when a time out error is generated during data reception. If this flag is set during data reception, the received data is discarded and the microcomputer returns to the command wait state.

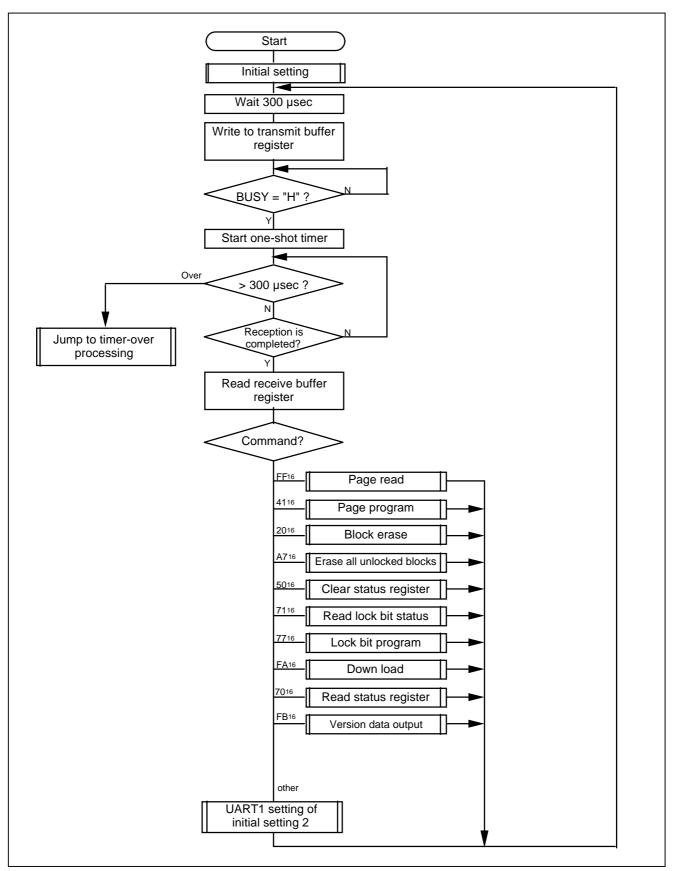

#### **Clear Status Register Command**

This command clears the bits (SR3–SR5, SR9) which are set to "1" when the operation of the status register or status register 1 ends in error. When the "5016" command code is sent serially with the 1st byte, the aforementioned bits are set to "0". When the clear status register operation ends, the BUSY signal changes from the "H" to the "L" level.

| Microcomputer side pin<br>SCLK(input) |      |

|---------------------------------------|------|

| RxD(input)<br>(M16C reception data)   | 5016 |

| TxD(output)<br>(M16C transmit data)   |      |

| BUSY(output)                          |      |

|                                       |      |

Figure 3.2.11 Timing for clearing the status register

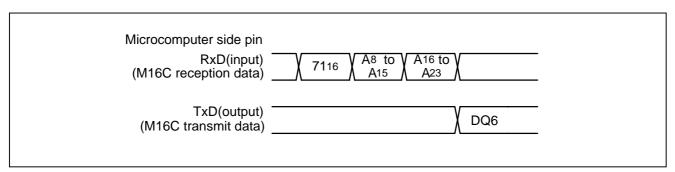

#### Read Lock Bit Status Command

This command reads the lock bit status of the specified block. Execute the read lock bit status command as explained here following. Write the highest address of specified block for addresses A8 to A23. Each block can be locked or unlocked.

locked : Erase and Writing is not possible unlocked : Erase and Writing is possible

- (1) Transfer the "7116" command code with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23, which are the highest address in the specified block with the 2nd and 3rd bytes respectively.

- (3) The lock bit data is output with the 4th byte. The 6th bit of the output data shows the status. "1" indicates that the block is unlocked, "0" that it is locked.

| $\begin{array}{c c} & A8 & to \\ \hline & A15 \\ \hline & A15 \\ \hline & A23 \\ \hline \end{array}$ |

|------------------------------------------------------------------------------------------------------|

| DQ6                                                                                                  |

|                                                                                                      |

|                                                                                                      |

Figure 3.2.12 Timing for reading lock bit status

#### Lock Bit Program Command

This command writes "0" (lock) for the lock bit of the specified block. Execute the lock bit program command as explained here following. Write the highest address of specified block for addresses A8 to A23.

- (1) Transfer the "7716" command code serially with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23, which are the highest address in the specified block with the 2nd and 3rd bytes respectively.

- (3) Transfer the verify command code "D016" with the 4th byte. With the verify command code, "0" is written for the lock bit of the specified block.

When writing ends, the BUSY signal changes from the "H" to the "L" level. Lock bit status can be read with the read lock bit status command.

If the user want to make effective the contents of the lock bit, the user need make the write protect pin of the flash memory an "L" level. If the user want to make ineffective the contents of the lock bit, the user need make the write protect pin of the flash memory an "H" level. Details of the write protect pin, refer to the data sheet of flash memory (Refer to M5M29GB/T160BVP, M5M29GB/T320BVP data sheets).

The lock bit returns to "1" (unlocked) by setting the write protect pin of the flash memory to "H" level first and then executing the block erase or erase all unlocked blocks command.

| Microcomputer side pin<br>SCLK(input) |                                                                                                                                                                                                                                                |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxD(input)<br>(M16C reception data)   | $\begin{array}{c c} \hline \end{array} \begin{array}{c} 7716 \\ \hline \end{array} \begin{array}{c} A8 \\ A15 \\ \hline \end{array} \begin{array}{c} A16 \\ A23 \\ \hline \end{array} \begin{array}{c} D016 \\ \hline \end{array} \end{array}$ |

| TxD(output)<br>(M16C transmit data)   |                                                                                                                                                                                                                                                |

| BUSY(output)                          |                                                                                                                                                                                                                                                |

|                                       |                                                                                                                                                                                                                                                |

Figure 3.2.13 Timing for lock bit program

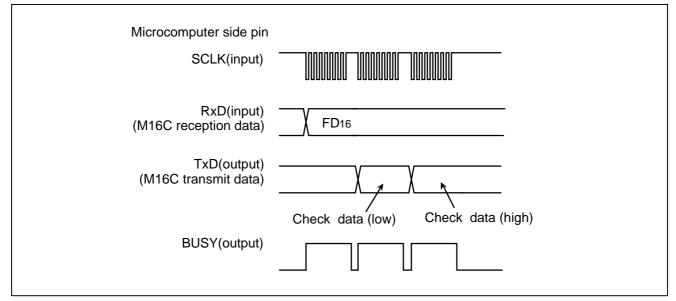

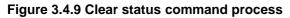

#### Read Check Data

This command reads the check data that confirms that the write data, which the serial programmer sent with the page program command, was successfully received by the microcontroller. After reading out the 2-byte check data, the check data becomes "000016". Execute the Read Check Data command as explained here following.

#### Table 3.2.5 Formula of check data

| Check data form | Calculation method                                     |

|-----------------|--------------------------------------------------------|

| CRC operation   | CRC code is obtained using M16C CRC operation circuit. |

(1) Transfer the "FD16" command code serially with the 1st byte.

(2) The check data (low) is output with the 2nd byte and the check data (high) with the 3rd.

To use this read check data command, first execute the command and then set the check data to "000016". Next, execute the page program command the required number of times. After that, when the read check command is executed again, the check data for all of the written data that was sent with the page program command during this time is read.

Figure 3.2.14. Timing for read check data

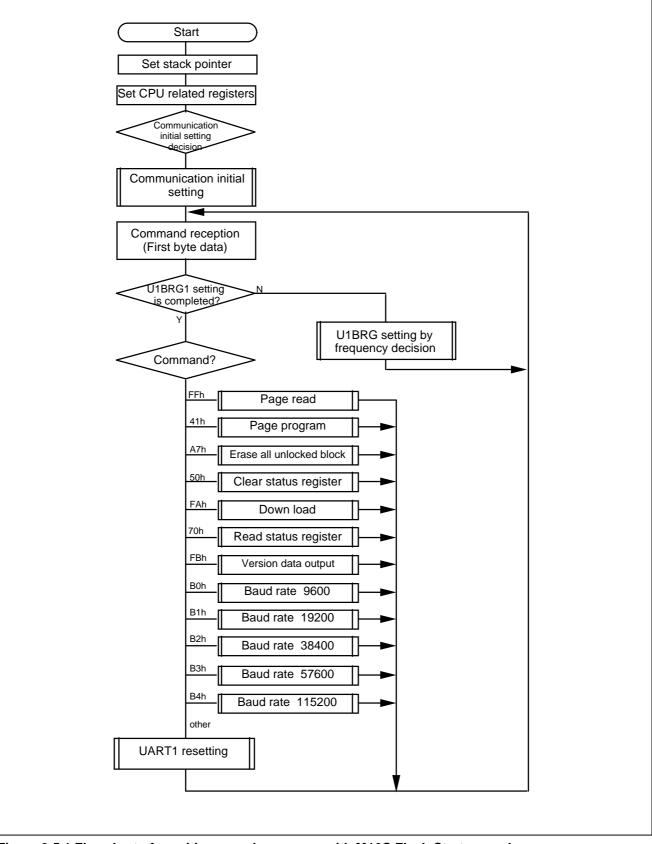

#### 3.3 Overview of boot loader mode 2 (clock asynchronized)

In boot loader mode 2, software commands, addresses and data are input and output between the MCU and serial programmer (\*1) using 2-wire clock-asynchronized serial I/O (UART1). To use this mode, the main clock input oscillation frequency should be no fewer than 2MHz, nor more than 20MHz. Bootloader mode 2 is engaged by applying an "L" level to the P65 pin to release the reset.

The TxD pin is for CMOS output. Data transfer is in 8-bit units with LSB first, 1 stop bit and parity OFF. After the reset is released, connections can be established at 9,600 bps. And then the baud rate can also be changed from 9,600 bps to 19,200, 38,400, 57,600 or 115,200 bps.

Here following are explained initial communications with serial programmer, how frequency is identified, and two functions (Download function and Flash memory control function) supported by bootloader mode 2.

\*1: M16C FlashStart can be used as the serial programmer.

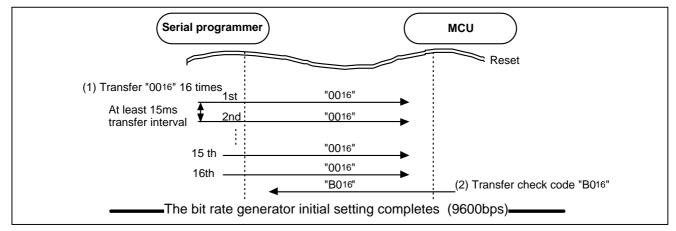

#### 3.3.1 Initial communications with serial programmer

After a reset, the bit rate generator is adjusted to 9,600 bps by establishing initial communications with serial programmer.

- (1) Adjust the bit rate to 9,600 bps first, then transmit "0016" from a serial programmer 16 times at transfer intervals of a minimum 15 ms. (The MCU sets the bit rate generator so that "0016" can be successfully received.)

- (2) The MCU outputs the "B016" check code and initial communications end successfully (\* 2). Figure 3.3.1 shows a protocol of initial communication with a serial programmer. Figure 3.3.2 shows a I/O timing of initial communication.

- \*2. If the serial programmer cannot receive "B016" successfully, change the input oscillation frequency of the main clock.

Figure 3.3.1 Serial programmer and initial communication

Figure 3.3.2 I/O Timing for initial communication

#### 3.3.2 Main clock input oscillation frequency and baud rate

Desired baud rate cannot be attained with some main clock input oscillation frequencies. Table 3.3.1 gives the main clock input oscillation frequency and the baud rate that can be attained for.

| Main clock input<br>operation frequency<br>(MHz) | Baud rate<br>9,600bps   | Baud rate<br>19,200bps | Baud rate<br>38,400bps | Baud rate<br>57,600bps | Baud rate<br>115,200bps |

|--------------------------------------------------|-------------------------|------------------------|------------------------|------------------------|-------------------------|

| 20MHz                                            | $\checkmark$            | $\checkmark$           | $\checkmark$           | $\checkmark$           | $\checkmark$            |

| 16MHz                                            | $\checkmark$            | $\checkmark$           | $\checkmark$           | $\checkmark$           | $\checkmark$            |

| 12MHz                                            | $\checkmark$            | $\checkmark$           | $\checkmark$           | $\checkmark$           | _                       |

| 10MHz                                            | $\checkmark$            | $\checkmark$           | $\checkmark$           | $\checkmark$           | -                       |

| 8MHz                                             | $\checkmark$            | $\checkmark$           | $\checkmark$           | $\checkmark$           | -                       |

| 7.3728MHz                                        | $\checkmark$            | $\checkmark$           | $\checkmark$           | $\checkmark$           | $\checkmark$            |

| 6MHz                                             | $\checkmark$            | $\checkmark$           | $\checkmark$           | I                      | -                       |

| 5MHz                                             | $\checkmark$            | $\checkmark$           | $\checkmark$           | I                      | -                       |

| 4.5MHz                                           | $\checkmark$            | $\checkmark$           | $\checkmark$           | $\checkmark$           | -                       |

| 4.194304MHz                                      | $\checkmark$            | $\checkmark$           | $\checkmark$           | -                      | -                       |

| 4MHz                                             | $\checkmark$            | $\checkmark$           | -                      | -                      | -                       |

| 3.58MHz                                          | $\checkmark$            | $\checkmark$           | $\checkmark$           |                        | $\sim$                  |

| 2MHz                                             | $\overline{\checkmark}$ | -                      | -                      | -                      | _                       |

$\sqrt{}$  :Communications possible

- :Communications not possible

#### 3.3.3 Download Function

#### **Functional Description**

The download function of M16C/80 Bootloader is to download a rewrite program (\*1) to internal RAM in the microcomputer using serial communications and then let the processing jump to the address in the RAM where the downloaded program has been located.

\*1: The rewrite program should be prepared by the user according to the following notes.

- The rewrite program should have two functions: (1) control function to write, erase and read to/from the external flash and (2) communication function to communicate with a serial writer.

- When using a stack in the rewrite program, please setup the stack pointer within the program.

- When the download is completed, the microcomputer starts the operation in single chip mode. Please change the processor mode from the single chip mode to microprocessor mode using the rewrite program before starting controls such as writing or erasing to the external flash memory.

- Please do not use any interrupts in the rewrite program.

- For the download area, please refer to the memory map of the Appendix 1.

#### Software commands

Table 3.3.2 lists the software commands for bootloader mode 2.

|   |                              |                      |                           |                           | -                         |                           | -                                    |                                          |

|---|------------------------------|----------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------------------|------------------------------------------|

|   | Control command              | 1st byte<br>transfer | 2nd byte                  | 3rd byte                  | 4th byte                  | 5th byte                  | 6th byte                             |                                          |

| 1 | Download function            | FA16                 | Size<br>(low)             | Size<br>(high)            | Check-<br>sum             | Data<br>input             | To<br>required<br>number<br>of times |                                          |

| 2 | Download result output       | FA <sub>16</sub>     | Data<br>input             |                           |                           |                           |                                      |                                          |

| 3 | Version data output function | FB16                 | Version<br>data<br>output | Version<br>data<br>output | Version<br>data<br>output | Version<br>data<br>output | Version<br>data<br>output            | Version<br>data<br>output to<br>9th byte |

| 4 | Baud rate 9600               | B016                 | <b>B0</b> 16              |                           |                           |                           |                                      |                                          |

| 5 | Baud rate 19200              | B116                 | <b>B1</b> 16              |                           |                           |                           |                                      |                                          |

| 6 | Baud rate 38400              | B216                 | <b>B2</b> 16              |                           |                           |                           |                                      |                                          |

| 7 | Baud rate 57600              | B316                 | <b>B3</b> 16              |                           |                           |                           |                                      |                                          |

| 8 | Baud rate 115200             | B416                 | <b>B4</b> 16              |                           |                           |                           |                                      |                                          |

| Table 3.3.2 Software commands for download | (Boot loader mode 2) |

|--------------------------------------------|----------------------|

|--------------------------------------------|----------------------|

Note: Shading indicates transfer from microcomputer to serial programmer. All other data is transferred from the serial programmer to the microcomputer.

#### Download

This command downloads a rewrite program to the internal RAM. The program as downloaded is stored in the internal RAM from address 60016 onward.

After a reset, the downloaded program is held in the internal RAM.

Execute the download command as explained here following.

- (1) Transfer the "FA16" command code serially with the 1st byte.

- (2) Transfer the program size serially with the 2nd and 3rd bytes, as follows: low order size with the 2nd byte, and high-order size with the 3rd byte.

- (3) Transfer the check sum serially with the 4th byte. The check sum is added to all data sent with the 5th byte onward.

- (4) The program to execute is sent with the 5th byte onward. The size of the program to be transferred will vary depending on the internal RAM size. (Please refer to "<u>3.6 Memory Map</u>" about the size of the rewrite program.)

When all data has been transferred, the microcomputer automatically executes the download result output command.

Figure 3.3.3 Timing for download

#### **Download Result Output**

After downloaded, the transferred check sum value from the serial programmer and the check sum value obtained by received data are compared. When the check sum values are matched, "FA16" and "0016"(success) are sent back, and then the processing jumps to the beginning of the downloaded program to execute it. When the values are not matched, "FA16" and "0116"(failure) are sent back and boot program stored in the microcomputer is transferred to RAM again, then this program is executed. (Return to the original state)

When the Download Function has been completed, the bootloader (microcomputer) outputs the execution result as explained here following.

- (1) When the Download Function has been completed, output the "FA16" command code with the 1st byte.

- (2) Output the download result code ("0016" : success / "0116" : failure) with the 2nd byte.

| Microcomputer side pin              |             |

|-------------------------------------|-------------|

| RxD(input)                          |             |

| (M16C reception data)               |             |

| TxD(output)<br>(M16C transmit data) | FA16 Result |

Figure 3.3.4 The timing of download result

#### **Version Information Output Command**

This command outputs the version information data of bootloader.

Execute the version information output command as explained here following.

- (1) Transfer the "FB16" command code serially with the 1st byte.

- (2) The version information will be output serially from the 2nd byte to the 9th byte. This data is composed of 8 ASCII code characters (\*1).

\*1: Version data format is 8 characters by ASCII code,

"VER. X. XX" (X: number).

It is output from "V".

| Microcomputer side pin                  | N    |

|-----------------------------------------|------|

| RxD(input)<br>(M16C reception data)     | FB16 |

| TxD(output) 「<br>(M16C transmit data) 」 |      |

Figure 3.3.5 Timing for version information output

## Baud Rate 9600

This command changes baud rate to 9,600 bps. Execute it as follows.

- (1) Transfer the "B016" command code serially with the 1st byte.

- (2) After the "B016" check code is output with the 2nd byte, change the baud rate to 9,600 bps.

| Microcomputer side pin<br>RxD(input) <sup>-</sup><br>(M16C reception data) _ | B016 |  |

|------------------------------------------------------------------------------|------|--|

| TxD(output)<br>(M16C transmit data) _                                        | B016 |  |

Figure 3.3.6 Timing of baud rate 9600

#### Baud Rate 19200

This command changes baud rate to 19,200 bps. Execute it as follows.

- (1) Transfer the "B116" command code serially with the 1st byte.

- (2) After the "B116" check code is output with the 2nd byte, change the baud rate to 19,200 bps.

| Microcomputer side pin<br>RxD(input) -<br>(M16C reception data) | B116 |  |

|-----------------------------------------------------------------|------|--|

| TxD(output) <sup>–</sup><br>(M16C transmit data) _              | B116 |  |

#### Figure 3.3.7 Timing of baud rate 19200

## Baud Rate 38400

This command changes baud rate to 38,400 bps. Execute it as follows.

- (1) Transfer the "B216" command code serially with the 1st byte.

- (2) After the "B216" check code is output with the 2nd byte, change the baud rate to 38,400 bps.

| Microcomputer side pin<br>RxD(input) <sup>–</sup><br>(M16C reception data) _ | B216 |  |

|------------------------------------------------------------------------------|------|--|

| TxD(output)<br>(M16C transmit data) _                                        | B216 |  |

Figure 3.3.8 Timing of baud rate 38400

### Baud Rate 57600

This command changes baud rate to 57,600 bps. Execute it as follows.

- (1) Transfer the "B316" command code serially with the 1st byte.

- (2) After the "B316" check code is output with the 2nd byte, change the baud rate to 57,600 bps.

| Microcomputer side pin<br>RxD(input)<br>(M16C reception data) | B316 |  |

|---------------------------------------------------------------|------|--|

| TxD(output)<br>(M16C transmit data)                           | B316 |  |

Figure 3.3.9 Timing of baud rate 57600

## Baud Rate 115200

This command changes baud rate to 115,200 bps. Execute it as follows.

- (1) Transfer the "B416" command code serially with the 1st byte.

- (2) After the "B416" check code is output with the 2nd byte, change the baud rate to 19,200 bps.

| Microcomputer side pin                  |      |

|-----------------------------------------|------|

| RxD(input) —<br>(M16C reception data) _ | B416 |

| TxD(output) —<br>(M16C transmit data) _ | B416 |

Figure 3.3.10 Timing of baud rate 115200

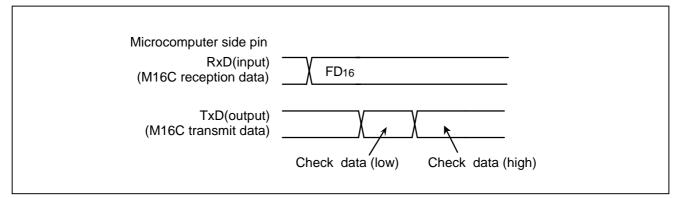

## 3.3.4 Flash Memory Control Function

### **Functional Description**

If an external flash memory is <u>M5M29GB/T160BVP</u>, <u>M5M29GB/T320BVP</u> (made by <u>MITSUBISHI</u>) or <u>MCM</u> with these flash memories, the <u>M16C/80</u> Bootloader is able to execute writing and erasing without rewrite program. (A connection example is shown in "<u>3.7 Connection example of bootloader</u>")

The M16C/80 Bootloader writes and erases a program to flash memory by communicating commands and data with serial programmer.

### **Software Commands**

The following table lists the flash memory control commands and I/O data.

When only an external flash memory is M5M29GB/T160BVP, M5M29GB/T320BVP or MCM with these flash memories, the user is able to use these commands.

Commands from 10 to 14 are the commands for clock asynchronous communication control.

About these commands, refer to the section of Bootloader mode 2 Download function.

|    | Control command           | 1st byte<br>transfer | 2nd byte                | 3rd byte                 | 4th byte                   | 5th byte       | 6th byte       |                                 |

|----|---------------------------|----------------------|-------------------------|--------------------------|----------------------------|----------------|----------------|---------------------------------|

| 1  | Page read                 | FF <sub>16</sub>     | Address<br>(middle)     | Address<br>(high)        | Data<br>output             | Data<br>output | Data<br>output | Data<br>output to<br>259th byte |

| 2  | Page program              | 41 <sub>16</sub>     | Address<br>(middle)     | Address<br>(high)        | Data<br>input              | Data<br>input  | Data<br>input  | Data<br>input to<br>259th byte  |

| 3  | Block erase               | 20 <sub>16</sub>     | Address<br>(middle)     | Address<br>(high)        | D0 <sub>16</sub>           |                |                |                                 |

| 4  | Erase all unlocked blocks | A7 <sub>16</sub>     | D0 <sub>16</sub>        |                          |                            |                |                |                                 |

| 5  | Read status register      | 70 <sub>16</sub>     | SRD<br>output           | SRD1<br>output           |                            |                |                |                                 |

| 6  | Clear status register     | 50 <sub>16</sub>     |                         |                          |                            |                |                |                                 |

| 7  | Read lock bit status      | 71 <sub>16</sub>     | Address<br>(middle)     | Address<br>(high)        | Lock bit<br>data<br>output |                |                |                                 |

| 8  | Lock bit program          | 77 <sub>16</sub>     | Address<br>(middle)     | Address<br>(high)        | D0 <sub>16</sub>           |                |                |                                 |

| 9  | Read check data           | FD <sub>16</sub>     | Data<br>output<br>(low) | Data<br>output<br>(high) |                            |                |                |                                 |

| 10 | Baud rate 9600            | B0 <sub>16</sub>     | B0 <sub>16</sub>        |                          |                            |                |                |                                 |

| 11 | Baud rate 19200           | B1 <sub>16</sub>     | B1 <sub>16</sub>        |                          |                            |                |                |                                 |

| 12 | Baud rate 38400           | B2 <sub>16</sub>     | B2 <sub>16</sub>        |                          |                            |                |                |                                 |

| 13 | Baud rate 57600           | B3 <sub>16</sub>     | B3 <sub>16</sub>        |                          |                            |                |                |                                 |

| 14 | Baud rate 115200          | B4 <sub>16</sub>     | B4 <sub>16</sub>        |                          |                            |                |                |                                 |

Note 1: Shading indicates transfer from microcomputer to serial programmer. All other data is transferred from the serial programmer to the microcomputer.

Note 2: SRD refers to status register data. SRD1 refers to status register 1 data.

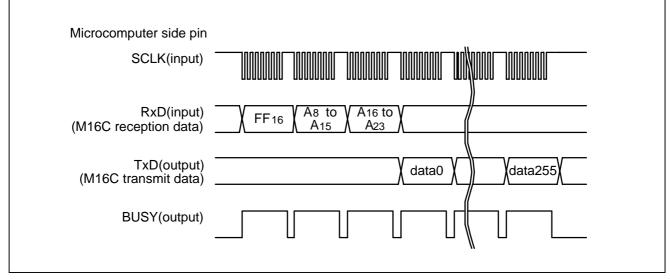

## Page Read Command

This command reads the specified page (256 bytes) in the flash memory sequentially one byte at a time. The read area is set with a high address (A16 to A23) and middle address (A8 to A15), targeting the 256 bytes from xxxx0016 to xxxxFF16. (Refer to Figure 3.3.11)

Execute the page read command as explained here following.

- (1) Transfer the "FF16" command code serially with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23 with the 2nd and 3rd bytes respectively.

- (3) From the 4th byte onward, data (D0–D7) for the page (256 bytes) specified with addresses A8 to A23 will be output sequentially from the smallest address first in sync with the fall of the clock.

Figure 3.3.11 The designation of the address and command applicable area

Figure 3.3.12 Timing for page read

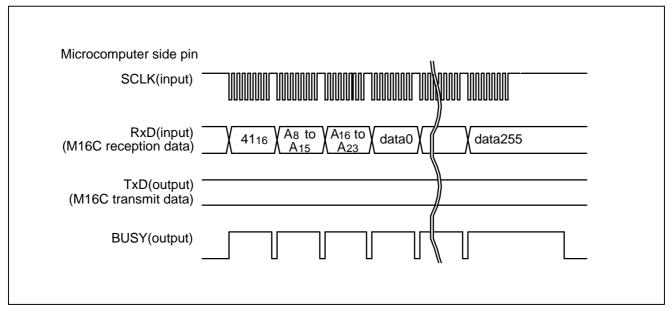

## Page Program Command

This command writes the specified page (256 bytes) in the flash memory sequentially one byte at a time. The area to be written to is set using a high address (A16 to A23) and middle address (A8 to A15), targeting the page between xxxx0016 and xxxxFF16.

Execute the page program command as explained here following.

- (1) Transfer the "4116" command code with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23 with the 2nd and 3rd bytes respectively.

- (3) From the 4th byte onward, as write data (D0–D7) for the page (256 bytes) specified with addresses A8 to A23 is input sequentially from the smallest address first, that page is automatically written.

The result of the page program can be known by reading the status register. For more information, see the section on the Read Status Register Command.

Each block can be write-protected with the lock bit. For more information, see the section on the Lock Bit Program Command. Additional writing is not allowed with already programmed pages.

| Microcomputer side pin<br>RxD(input)<br>(M16C reception data)<br>TxD(output)<br>(M16C transmit data) | $\begin{array}{c c} 41_{16} & A_8 & to \\ A_{15} & A_{23} \\ \end{array} & data0 \\ \end{array} & data255 \\ \end{array}$ |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| TxD(output)<br>(M16C transmit data)                                                                  |                                                                                                                           |

Figure 3.3.13 Timing for the page program

## **Block Erase Command**

This command erases the data in the specified block. Execute the block erase command as explained here following.

- (1) Transfer the "2016" command code serially with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23 with the 2nd and 3rd bytes respectively.

- (3) Transfer the verify command code "D016" with the 4th byte. With the verify command code, the erase operation will start for the specified block in the flash memory.

After block erase ends, the result of the block erase operation can be known by reading the status register. For more information, see the section on the Read Status Register Command.

Each block can be erase-protected with the lock bit. For more information, see the section on the LockBit Program Command.

| Microcomputer side pin<br>RxD(input)<br>(M16C reception data) | $20_{16} \begin{pmatrix} A_8 & to \\ A_{15} \end{pmatrix} \begin{pmatrix} A_{16} & to \\ A_{23} \end{pmatrix} D0_{16}$ |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| TxD(output)<br>(M16C transmit data)                           |                                                                                                                        |

Figure 3.3.14 Timing for block erasing

### **Erase All Unlocked Blocks Command**

This command erases the content of all blocks. Execute the erase all unlocked blocks command as explained here following.

- (1) Transfer the "A716" command code serially with the 1st byte.

- (2) Transfer the verify command code "D016" with the 2nd byte. With the verify command code, the erase operation will start and continue for all blocks in the flash memory.

The result of the erase operation can be known by reading the status register. For more information, see the section on the Read Status Register Command.

Each block can be erase-protected with the lock bit. For more information, see the section on the Lock Bit Program Command.

| Microcomputer side pin<br>RxD(input)<br>(M16C reception data) | A716 D016 |  |

|---------------------------------------------------------------|-----------|--|

| TxD(output)<br>(M16C transmit data)                           |           |  |

Figure 3.3.15 Timing for erasing all unlocked blocks

## **Read Status Register Command**

This command reads status information. Execute the read status register command as explained here following.

- (1) Transfer the "7016" command code serially with the 1st byte.

- (2) Output the contents of the status register (SRD) specified with the 2nd byte and the contents of status register 1 (SRD1) specified with the 3rd byte.

Details of "status register", refer to section "<u>Status Register(SRD)</u>" of bootloader mode 1.

Details of "status register 1", refer to section "Status Register 1(SRD1)" of bootloader mode 1.

| Microcomputer side pin<br>RxD(input)<br>(M16C reception data) | 7016                      |  |

|---------------------------------------------------------------|---------------------------|--|

| TxD(output)<br>(M16C transmit data)                           | SRD SRD1<br>output output |  |

Figure 3.3.16 Timing for reading the status register

### **Clear Status Register Command**

This command clears the bits (SR3–SR5, SR9) which are set to "1" when the operation of the status register or status register 1 ends in error. When the "5016" command code is sent serially with the 1st byte, the aforementioned bits are set to "0".

| Microcomputer side pin<br>RxD(input)<br>(M16C reception data) | 5016 |

|---------------------------------------------------------------|------|

| TxD(output)<br>(M16C transmit data)                           |      |

Figure 3.3.17 Timing for clearing the status register

### Read Lock Bit Status Command

This command reads the lock bit status of the specified block. Execute the read lock bit status command as explained here following. Write the highest address of the specified block for addresses A8 to A23. Each block can be locked or unlocked.

locked : Erase and Writing is not possible unlocked : Erase and Writing is possible

- (1) Transfer the "7116" command code with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23, which are the highest addresses in the specified block with the 2nd and 3rd bytes respectively.

- (3) The lock bit data is output with the 4th byte. The 6th bit of the output data shows the status. "1" indicates that the block is unlocked, "0" that it is locked.

Figure 3.3.18 Timing for reading lock bit status

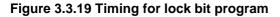

## Lock Bit Program Command

This command writes "0" (lock) for the lock bit of the specified block. Execute the lock bit program command as explained here following. Write the highest address of the specified block for addresses A8 to A23. Each block can be locked or unlocked.

- (1) Transfer the "7716" command code serially with the 1st byte.

- (2) Transfer addresses A8 to A15 and A16 to A23, which are the highest address in the specified block and with the 2nd and 3rd bytes respectively.

- (3) Transfer the verify command code "D016" with the 4th byte. With the verify command code, "0" is written for the lock bit of the specified block.

Lock bit status can be read with the read lock bit status command.

If the user want to make effective the contents of the lock bit, the user need make the write protect pin of the flash memory an "L" level. If the user want to make ineffective the contents of the lock bit, the user need make the write protect pin of the flash memory an "H" level. Details of the write protect pin, refer to the data sheet of flash memory (Refer to M5M29GB/T160BVP, M5M29GB/T320BVP data sheets).

The lock bit returns to "1" (unlocked) by setting the write protect pin of the flash memory to "H" level first and then executing the block erase or erase all unlocked blocks command.

| Microcomputer side pin<br>RxD(input)<br>(M16C reception data) | $\begin{array}{c c} \hline \end{array} & \begin{array}{c} A8 & to \\ A15 \\ \end{array} & \begin{array}{c} A16 & to \\ A23 \\ \end{array} & \begin{array}{c} D016 \\ \end{array} \end{array}$ |  |