## Guide for Connecting an External MCU with the SPI

R01AN3969EJ0100 Rev.1.00 Sep. 11, 2017

## Outline

In industrial networks, the migration from the fieldbus systems for serial communications to industrial Ethernet is ongoing. This application note provides information to assist in conformance with the major industrial Ethernet protocol, EtherCAT<sup>®</sup>, by connecting an external MCU, on which the industrial application runs, with an SPI of an EC-1.

- The SPI as the standard serial communications interface is used for connection of an external MCU with the EC-1. The external MCU and EC-1 operate in SPI master mode and SPI slave mode, respectively. This allows connection with various MCUs which support SPI master mode.

- The SPI interface is conformant with the specifications defined in the "EtherCAT slave controller connection library". Therefore, the physical and logical specifications of the SPI do not require further consideration.

- The EtherCAT communications program for the EC-1 is created by the EtherCAT slave stack code generation tool ("SSC Tool") from Beckhoff Automation GmbH, so customization suited to the specifications of the machinery under control is possible.

- The external MCU can access the registers, Process data RAM, and the extended SPI registers of the EtherCAT slave controller ("ESC") in the EC-1.

- The sample program runs on the EC-1 remote I/O board and the EC-1 communications board, and the extended SPI registers in the EC-1 are used for the sharing of data.

## Target Devices

EC-1

## Contents

| 1. Specifications                                               | 4  |

|-----------------------------------------------------------------|----|

| 2. Operating Environment                                        | 5  |

| 3. Hardware                                                     | 6  |

| 3.1 Example of the Hardware Configuration                       | 6  |

| 3.2 Pins                                                        | 7  |

| 4. SPI Interface                                                |    |

| 4.1 Example of the Software Configuration                       |    |

| 4.2 SPI Address Space                                           |    |

| 4.3 Extended SPI Registers                                      |    |

| 4.3.1 Device ID Register (DEVICEID)                             |    |

| 4.3.2 Revision Number Register (REVNO)                          |    |

| 4.3.3 Status Register (STATUS)                                  |    |

| 4.3.4 Control Register (CONTROL)                                | 11 |

| 4.3.5 Scratch Registers (SCRATCH0 to 9)                         |    |

| 4.3.6 Sequential Data Number Register (SQDATNUM)                |    |

| 4.3.7 Sequential Data Registers (SQDATA0 to 63)                 |    |

| 4.4 Format of SPI Packets                                       | 12 |

| 4.4.1 Commands                                                  | 12 |

| 4.4.2 RD Command                                                | 12 |

| 4.4.3 WR Command                                                | 13 |

| 4.4.4 SQRD Command                                              | 14 |

| 4.4.5 SQWR Command                                              | 15 |

| 4.4.6 DTRD Command                                              | 16 |

| 4.4.7 DTWR Command                                              | 17 |

| 4.5 Procedures for Access                                       | 19 |

| 4.5.1 Sequence for Reading the Registers                        | 19 |

| 4.5.2 Sequence for Writing to the Registers                     | 20 |

| 4.5.3 Sequence for Sequential Reading from the Process Data RAM | 21 |

| 4.5.4 Sequence for Sequential Writing to the Process Data RAM   | 23 |

| 4.5.5 Extended Registers: Sequence for Confirming Startup       | 24 |

| 4.5.6 Extended Registers: Software Reset Sequence               | 25 |

| 5. Software                                                     | 25 |

| 5.1 Operation in Outline                                        | 25 |

| 5.2 Procedure for Designing Software                            | 27 |

| 5.3 Interrupts                                                  |    |

| 5.4 Fixed-Width Integers                                        |    |

| 5.5 Constants and Error Codes                                   |    |

| 5.6 Structures and Unions                                       | 30 |

| 5.7 Global Variables                                            | 32 |

| 5.8 Functions                                                   | 32 |

| 5.9   | Specifications of the Functions                          |    |

|-------|----------------------------------------------------------|----|

| 5.9   | 9.1 Processing for the Initial Settings of the SPI Pins  |    |

| 5.9   | 9.2 Initialization Processing for SPI Control            |    |

| 5.9   | 9.3 Starting SPI Communications                          |    |

| 5.9   | 9.4 Stopping SPI Communications                          |    |

| 5.9   | 9.5 Processing for SPI Transfer                          |    |

| 6. Sa | Sample Program                                           |    |

| 6.1   | Overview                                                 |    |

| 6.2   | Hardware Configuration                                   |    |

| 6.3   | Software Configuration                                   |    |

| 6.4   | Configuration of Directories and Files                   |    |

| 6.4   | 4.1 Sample Program for the Remote I/O Board              |    |

| 6.4   | 4.2 Sample Program for the Communications Board          |    |

| 6.5   | Flowchart                                                |    |

| 6.6   | Shared Data                                              |    |

| 6.7   | Tutorial                                                 |    |

| 6.7   | 7.1 Preparation                                          |    |

| 6.7   | 7.2 Connection with TwinCAT <sup>®</sup>                 |    |

| 7. D  | Documents for Reference                                  | 45 |

| 7.1   | Related Documents                                        | 45 |

| 7.2   | Relationship between This Document and Related Documents |    |

| 8. W  | Vebsite and Support                                      | 46 |

## 1. Specifications

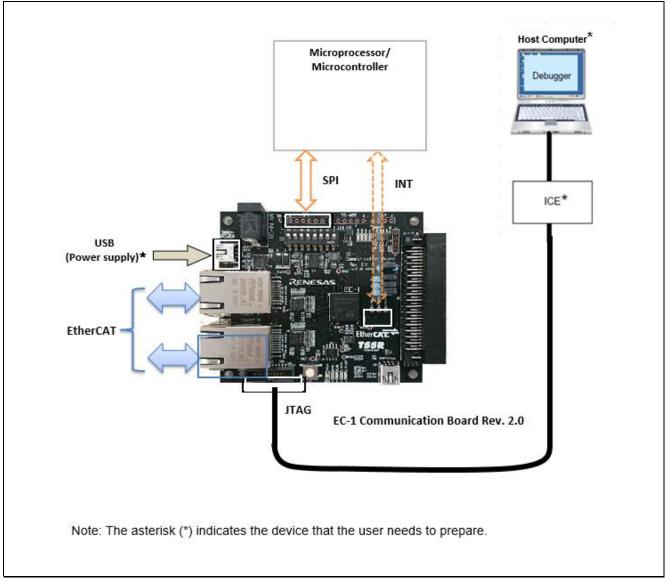

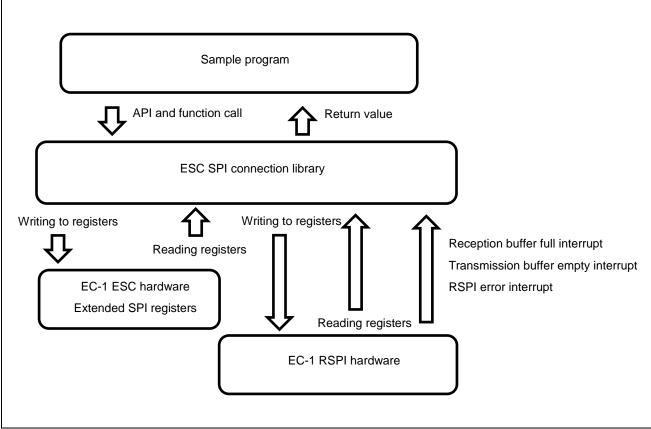

Table 1.1 lists the peripheral modules used and their applications. Figure 1.1 shows the operating environment of the sample program which includes the library.

| Table 1.1 | Peripheral Modules Used and Their Applications |

|-----------|------------------------------------------------|

|-----------|------------------------------------------------|

| Peripheral Module                 | Application                                                                                                                              |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| EtherCAT slave controller         | For use in EtherCAT communications                                                                                                       |

| EtherCAT interrupt output signals | CATIRQ, CATSYNC0, and CATSYNC1 are output to an external MCU.                                                                            |

| Ethernet MAC (ETHERC)             | For use in EtherCAT communications                                                                                                       |

| Peripheral interface (RSPI)       | For use in transfer to and from an external MCU (CH0 or CH1 is selectable)                                                               |

| Interrupt controller              | The reception buffer full, transmission buffer empty, and RSOI error interrupts are used as sources to generate interrupts for the RSPI. |

| Tightly coupled memory            | The ATCM is used as the program and variable area for the library.                                                                       |

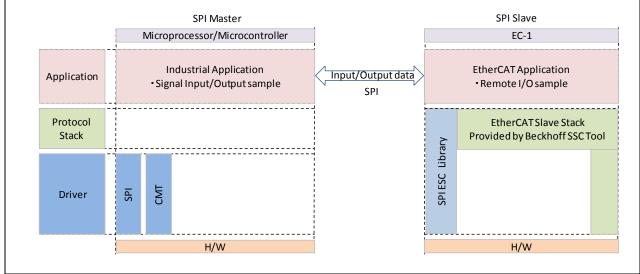

### Figure 1.1Operating Environment

Notes: - Use the EtherCAT IN port to connect an EtherCAT master.

- EtherCAT interrupt output signals are also connected when they are required by an external MCU.

## 2. Operating Environment

The library covered in this application note is for the environment below.

## Table 2.1 Operating Environment

| Item                    | Description                                                                     |

|-------------------------|---------------------------------------------------------------------------------|

| Board used              | EC-1 communications board                                                       |

|                         | EC-1 Communication Board Rev. 2.0                                               |

| CPU                     | EC-1                                                                            |

|                         | R9A06G043                                                                       |

| Operating frequency     | CPU clock (CPUCLK): 150 MHz                                                     |

|                         | System clock: 25 MHz                                                            |

| Operating voltage       | 3.3 V                                                                           |

| Operating mode          | SPI boot mode                                                                   |

| Devices used            | Serial flash memory                                                             |

|                         | W25Q32JVSFIM from Winbond                                                       |

|                         | • EEPROM                                                                        |

|                         | R1EX24016ASAS0 from Renesas Electronics                                         |

|                         | Ethernet PHY                                                                    |

|                         | LK105 from Texas Instruments                                                    |

| Communications protocol | EtherCAT®                                                                       |

| Integrated development  | Embedded Workbench® for ARM, version 7.70.1, from IAR Systems                   |

| environment             |                                                                                 |

| Emulator                | I-jet from IAR Systems                                                          |

| SSC Tool                | Slave Stack Code (SSC) Tool, version 5.11, from EtherCAT Technology Group (ETG) |

| Software PLC            | TwinCAT® 3 from Beckhoff Automation GmbH                                        |

## 3. Hardware

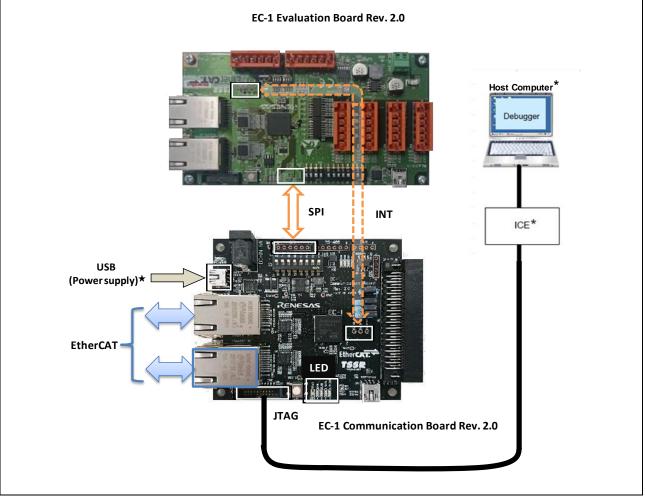

## 3.1 Example of the Hardware Configuration

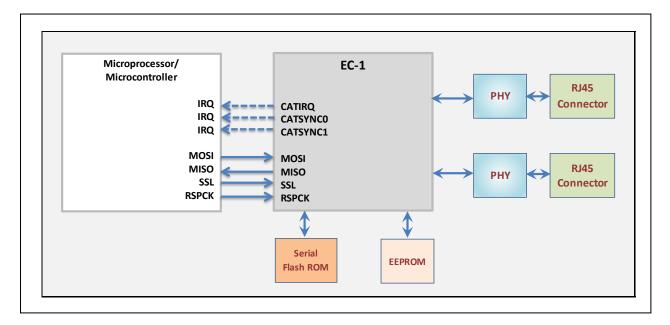

Figure 3.1 is an example of the hardware configuration where the EC-1 that incorporates the library is combined as an EtherCAT slave with an external MCU.

### Figure 3.1 Example of the Hardware Configuration of an EtherCAT Slave

The EtherCAT slave transfers data to and from the external MCU by using the four-wire SPI. The four signals are MOSI (Master Out Slave In), MISO (Master In Slave Out), SSL (Slave Select), and RSPCK (RSPI Clock).

The external MCU is the SPI master and the EC-1 is the SPI slave.

The EC-1 outputs CATIRQ, CATSYNC0, and CATSYNC1 as synchronous interrupt signals for EtherCAT.

Connect these signals if the external MCU is using synchronization of timing.

## 3.2 Pins

Table 3.1 lists the pins used and their functions.

| Table 3.1 | Pins | Used | and | Their | Functions |

|-----------|------|------|-----|-------|-----------|

|           |      |      |     |       |           |

| Pin Name    | I/O    | Description                                                 |

|-------------|--------|-------------------------------------------------------------|

| ETH_MDIO    | I/O    | Input and output of the management data signal              |

| ETH_MDC     | Output | Output of the management interface clock                    |

| ETH0_RXC    | I/O    | Input and output of the reception clock                     |

| ETH1_RXC    |        |                                                             |

| ETH0_RXER   | Input  | Input of the received data error signal                     |

| ETH1_RXER   |        |                                                             |

| ETH0_RXDV   | Input  | Input of the received data enable signal                    |

| ETH1_RXDV   |        |                                                             |

| ETH0_RXD0~3 | Input  | Input of the received data signal                           |

| ETH1_RXD0~3 |        |                                                             |

| ETH0_TXC    | Input  | Input of the 10 M/100 M transmission clock (2.5 MHz/25 MHz) |

| ETH1_TXC    |        |                                                             |

| ETH0_TXER   | Output | Output of the transmission error signal                     |

| ETH1_TXER   |        |                                                             |

| ETH0_TXEN   | Output | Output of the transmission enable signal                    |

| ETH1_TXEN   |        |                                                             |

| ETH0_TXD0~3 | Output | Output of the transmission data signal                      |

| ETH1_TXD0~3 |        |                                                             |

| ETH0_COL    | Input  | Input of the collision detection signal                     |

| ETH1_COL    |        |                                                             |

| ETH0_CRS    | Input  | Input of the carrier sense signal                           |

| ETH1_CRS    |        |                                                             |

| CLKOUT25M0  | Output | Output of the Ethernet PHY external clock                   |

| CLKOUT25M1  |        |                                                             |

| PHYLINK0    | Input  | Input of the PHY Link signal (for Ethernet Switch)          |

| PHYLINK1    |        |                                                             |

| ETH0_INT    | Input  | Input of the Ethernet PHY interrupt request signal          |

| ETH1_INT    |        |                                                             |

| CATI2CCLK   | Output | Output of the EtherCAT EEPROM I2C clock signal              |

| CATI2CDATA  | I/O    | Input and output of the EtherCAT EEPROM I2C data signal     |

| CATLINKACT1 | Output | Output of the EtherCAT Link/Activity LED signal             |

| CATLINKACT0 |        |                                                             |

| CATLEDRUN   | Output | Output of the EtherCAT RUN LED signal                       |

| CATLEDSTER  | Output | Output of the EtherCAT dual-color state LED signal          |

| CATLEDERR   | Output | Output of the EtherCAT error LED signal                     |

| CATIRQ      | Output | Output of EtherCAT IRQ                                      |

| CATSYNC0    | Output | Output of EtherCAT SYNC0                                    |

| CATSYNC1    | Output | Output of EtherCAT SYNC1                                    |

| RSPCK0      | Input  | Input of the RSPI clock                                     |

| MISO0       | Output | Output of RSPI slave send data                              |

| MOSI0       | Input  | Input of RSPI master send data                              |

| SSL00       | Input  | Input of the RSPI slave select signal                       |

## 4. SPI Interface

The EC-1 has two serial peripheral interfaces (RSPI).

The library allows the selection of channel 0 or 1 through parameters at the time of initialization.

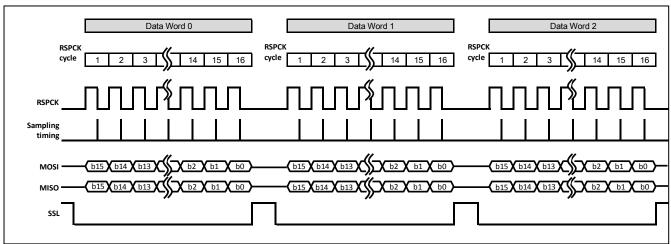

Table 4.1 lists the specifications of the SPI and Figure 4.1 is a timing chart of the SPI.

### Table 4.1SPI Specifications

| Item                     | Description                  |

|--------------------------|------------------------------|

| Method of communications | Four-wire SPI                |

| Transfer mode            | Slave mode                   |

| Method of communications | Full duplex                  |

| Signal sense             | SSL: Active low              |

|                          | RSPCK: Low in the idle state |

| Transfer frame           | 16 bits × 3 words            |

| Format                   | MSB first                    |

| Data sampling timing     | Falling edges of RSPCK       |

| Maximum transfer rate    | 18.75 Mbps                   |

Figure 4.1 Timing Chart of the SPI

## 4.1 Example of the Software Configuration

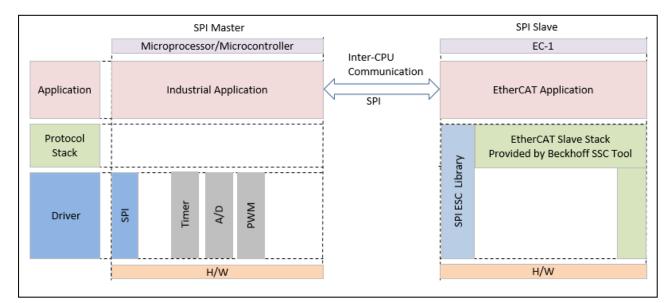

Figure 4.2 is an example of the software configuration where the EC-1 is combined as an EtherCAT slave with an external MCU.

### Figure 4.2 Example of the Software Configuration of an EtherCAT Slave

SSC Tool: Program generation tool for EtherCAT control from Beckhoff Automation GmbH

The external MCU operates as an SPI master and runs the industrial application, drivers for use with the industrial application, and a driver for access to the EC-1 through the SPI interface.

The EC-1 operates as an SPI slave and has the EtherCAT application, EtherCAT slave stack, and the ESC SPI connection library for access by the external MCU through the SPI interface.

Note that the procedure for access by the external MCU to the EC-1 through the SPI interface is described in section 4.5, Procedures for Access.

## 4.2 SPI Address Space

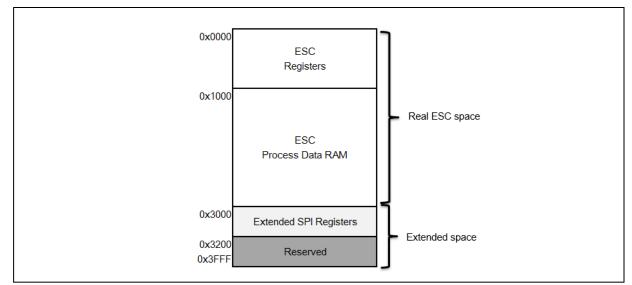

Figure 4.3 shows the address space for access by the external MCU to the EC-1 through the SPI interface. Of the total space of 16 Kbytes, the ESC of the EC1 is allocated to the 12 Kbytes from 0x0000 to 0x2FFF. The 512 bytes from 0x3000 to 0x31FF are allocated to the extended registers for SPI communications.

Figure 4.3 SPI Address Space

## 4.3 Extended SPI Registers

The extended SPI registers are accessible in 16- or 32-bit units.

Table 4.2 lists the extended SPI registers.

Note that R and W indicate the directions of access as seen from the external MCU.

### Table 4.2Extended SPI Registers

| Address                 | Register Name                              | Bit | R/W |

|-------------------------|--------------------------------------------|-----|-----|

| 0x3000                  | Device ID register (DEVICEID)              | 32  | R   |

| 0x3004                  | Revision number register (REVNO)           | 16  | R   |

| 0x3006                  | Status register (STATUS)                   | 16  | R   |

| 0x3008                  | Control register (CONTROL)                 | 16  | W   |

| 0x300A +2n*1            | Scratch registers (SCRATCH0 to 9)          | 16  | R/W |

| 0x301E                  | Sequential data number register (SQDATNUM) | 16  | R   |

| 0x3020+4n* <sup>2</sup> | Sequential data register (SQDATA0 to 63)   | 32  | R   |

| 0x3120-0x31FE           | Reserved                                   |     |     |

Note 1. n = 0 to 9 Note 2. n = 0 to 63

## 4.3.1 Device ID Register (DEVICEID)

| Address | Bit  | R/W | escription                                   |  |

|---------|------|-----|----------------------------------------------|--|

| 0x3000  | 31:0 | R   | The device ID can be read here.              |  |

|         |      |     | "EC-1" (0x45435E31) is stored in ASCII code. |  |

## 4.3.2 Revision Number Register (REVNO)

| Address | Bit  | R/W | Description                                         |

|---------|------|-----|-----------------------------------------------------|

| 0x3004  | 15:0 | R   | The version number of the library can be read here. |

|         |      |     | 15:8: Major part of the version number              |

|         |      |     | 7:0: Minor part of the version number               |

## 4.3.3 Status Register (STATUS)

| Address | Bit  | R/W | Description                                                                         |

|---------|------|-----|-------------------------------------------------------------------------------------|

| 0x3006  | 15:0 | R   | The error code which has occurred during operation of the library can be read here. |

|         |      |     | 0x0000: No error                                                                    |

|         |      |     | 0x0001: The previously received command is invalid.                                 |

|         |      |     | 0x0002: The word length specified in the previously received command is invalid.    |

|         |      |     | 0x0003: The address specified in the previously received command is invalid.        |

|         |      |     | 0x0004: The consecutive values that were previously received are invalid.           |

|         |      |     | 0x0005: The control register settings that were previously received are invalid.    |

|         |      |     | 0x0011: An overrun error occurred.                                                  |

|         |      |     | 0x0014: A mode fault error occurred.                                                |

|         |      |     | 0x0018: A parity error occurred (not used this time)                                |

## 4.3.4 Control Register (CONTROL)

| Address | Bit  | R/W | Description                                                                              |

|---------|------|-----|------------------------------------------------------------------------------------------|

| 0x3008  | 15:0 | W   | When a control code is set in this register, operation proceeds according to the control |

|         |      |     | code.                                                                                    |

|         |      |     | 0x0001: The error code of the status register is cleared and set to "no error" (0x0000). |

|         |      |     | 0x0080: The EC-1 is rebooted by the application of a software reset.                     |

## 4.3.5 Scratch Registers (SCRATCH0 to 9)

| Address | Bit  | R/W | Description                                                                                  |

|---------|------|-----|----------------------------------------------------------------------------------------------|

| 0x300A  | 15:0 | R/W | This is a 16-bit register for general use. It is also available for use in transferring data |

| +2n     |      |     | and state information to and from the external MCU.                                          |

Note: n =0 to 9

## 4.3.6 Sequential Data Number Register (SQDATNUM)

| Address | Bit  | R/W | Description                                                                        |

|---------|------|-----|------------------------------------------------------------------------------------|

| 0x301E  | 15:0 | R   | The number of transfers in the last R/W sequence to have been received can be read |

|         |      |     | here.                                                                              |

## 4.3.7 Sequential Data Registers (SQDATA0 to 63)

| Address | Bit  | R/W | Description                                                                        |

|---------|------|-----|------------------------------------------------------------------------------------|

| 0x3020  | 31:0 | R   | In the case of the SQRD command, this holds the data read from the DATAR register. |

| +4n     |      |     | In the case of the SQWR command, this holds the data for writing to the DATAWR     |

|         |      |     | register.                                                                          |

Note: n = 0 to 63

## 4.4 Format of SPI Packets

### 4.4.1 Commands

Table 4.3 lists the commands for access by the external MCU to the SPI address space in the EC-1.

For the sequence for access by using the command, see section 4.5.1, Sequence for Reading the Registers, to section 4.5.4, Sequence for Sequential Writing to the Process Data RAM.

| CMD [7:0] | Command | Function                                                            |

|-----------|---------|---------------------------------------------------------------------|

|           | Name    |                                                                     |

| 0x01      | RD      | This command is for reading the ESC and extended registers.         |

| 0x02      | WR      | This command is for writing to the ESC and extended registers.      |

| 0x03      | SQRD    | This command initiates sequential reading from the ESC.             |

| 0x04      | SQWR    | This command initiates sequential writing to the ESC.               |

| 0x05      | DTRD    | This command is for reading data from the sequential data register. |

| 0x06      | DTWR    | This command is for writing data to the sequential data register.   |

#### Table 4.3 SPI Commands

### 4.4.2 RD Command

This command is for reading of the ESC or extended registers in the EC-1 by the external MCU.

The length of the data and the address from which to read are specified.

1, 2, or 4 bytes are specifiable as lengths.

On receiving the RD command, the EC-1 reads the specified register and sends the results

|      |                                                                                            | Data V | Vord 0 | Data Word 1                           | Data Word 2 |

|------|--------------------------------------------------------------------------------------------|--------|--------|---------------------------------------|-------------|

|      | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 |        |        | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |             |

| MOSI |                                                                                            | RD     | LEN    | REGADR                                |             |

| MISO | Sts                                                                                        | RE     | EGADR  | D0                                    | D1          |

| Figure 4.4 Format of RD Command Packets |

|-----------------------------------------|

|-----------------------------------------|

| Word No. | Bit  | Name   | Description                                                                     |  |

|----------|------|--------|---------------------------------------------------------------------------------|--|

| 0        | 15:8 | RD     | RD command (0x01)                                                               |  |

|          | 7:0  | LEN    | These bits set the number of bytes to be read.                                  |  |

|          |      |        | Allowable settings are 1, 2, and 4 bytes.                                       |  |

| 1        | 15:0 | REGADR | These bits specify the addresses of the ESC or extended registers from which to |  |

|          |      |        | read.                                                                           |  |

|          |      |        | The specifiable address range is from 0x0000 to 0x3FFF.                         |  |

| 2        | 15:0 |        | These bits cannot be used with the RD command. The value is "don't care".       |  |

### Table 4.4RD Command Packets for MOSI (external MCU $\rightarrow$ EC-1)

## Table 4.5RD Command Packets for MISO (EC-1 $\rightarrow$ external MCU)

| Word No. | Bit   | Name   | Description                                                                         |

|----------|-------|--------|-------------------------------------------------------------------------------------|

| 0        | 15:14 | Sts    | Bit 15: ERROR                                                                       |

|          |       |        | Indicates the error state of the RD command.                                        |

|          |       |        | 1: An error has occurred.                                                           |

|          |       |        | 0: No error has occurred.                                                           |

|          |       |        | Bit 14: BUSY                                                                        |

|          |       |        | Indicates the state of execution of the RD command.                                 |

|          |       |        | 1: The command is being executed.                                                   |

|          |       |        | 0: End of the command                                                               |

|          | 13:0  | REGADR | These bits indicate the address of a register specified by the RD command.          |

| 1        | 15:0  | D0     | These bits indicate the results of reading the register specified by the RD command |

| 2        | 15:0  | D1     | while BUSY = 0.                                                                     |

|          |       |        | The data are flush left when the length of data is 1 or 2 bytes.                    |

## 4.4.3 WR Command

This command is for writing of the ESC or extended registers in the EC-1 by the external MCU.

The length of the data and the address to which to write are specified.

1, or 2 bytes are specifiable as lengths.

On receiving the WR command, the EC-1 writes to the specified register.

|      |       | Data V          | Vord 0          | Data Word 1                           | Data Word 2                           |

|------|-------|-----------------|-----------------|---------------------------------------|---------------------------------------|

|      | 15 14 | 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

| MOSI |       | WR LEN          |                 | REGADR                                | D0                                    |

| MISO | Sts   | REGADR          |                 |                                       |                                       |

#### Figure 4.5 Format of SPI Packets for the WR Command

#### Table 4.6WR Command Packets for MOSI (external MCU $\rightarrow$ EC-1)

| Word No. | Bit  | Name   | Description                                                                          |  |

|----------|------|--------|--------------------------------------------------------------------------------------|--|

| 0        | 15:8 | WR     | WR command (0x02)                                                                    |  |

|          | 7:0  | LEN    | These bits set the number of bytes for writing.                                      |  |

|          |      |        | Allowable settings are 1 and 2 bytes.                                                |  |

| 1        | 15:0 | REGADR | These bits specify the addresses of the ESC or extended registers to which to write. |  |

|          |      |        | The specifiable address range is from 0x0000 to 0x3FFF.                              |  |

| 2        | 15:0 | D0     | These bits set a value for writing to the register.                                  |  |

|          |      |        | The data are flush left when the length of data is 1 byte.                           |  |

| Word No. | Bit   | Name   | Description                                                                  |

|----------|-------|--------|------------------------------------------------------------------------------|

| 0        | 15:14 | Sts    | Bit 15: ERROR                                                                |

|          |       |        | Indicates the error state of the WR command.                                 |

|          |       |        | 1: An error has occurred.                                                    |

|          |       |        | 0: No error has occurred.                                                    |

|          |       |        | Bit 14: BUSY                                                                 |

|          |       |        | Indicates the state of execution of the WR command.                          |

|          |       |        | 1: The command is being executed.                                            |

|          |       |        | 0: End of the command                                                        |

|          | 13:0  | REGADR | These bits indicate the address of the register specified by the WR command. |

| 1        | 15:0  |        | These bits cannot be used with the WR command. The value is "don't care".    |

| 2        | 15:0  |        |                                                                              |

### Table 4.7 WR Command Packets for MISO (EC-1 $\rightarrow$ external MCU)

## 4.4.4 SQRD Command

This command is for the sequential reading of the Process Data RAM of the ESC in the EC-1 by the external MCU.

The length of data and the address where reading of the register is to start are specified.

Up to 255 bytes are specifiable as lengths.

On receiving an SQRD command, the EC-1 reads the specified registers and stores the results in the sequential data register.

The external MCU can read the results of reading from the sequential data register by issuing a DTRD command.

|      | Data Word 0 |                 |                 | Data Word 1                           | Data Word 2                         |

|------|-------------|-----------------|-----------------|---------------------------------------|-------------------------------------|

|      | 15 14       | 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |

| MOSI |             | SQRD            | LEN             | REGADR                                |                                     |

| MISO | Sts         | REGADR          |                 |                                       |                                     |

#### Figure 4.6 Format of SPI Packets for the SQRD Command

### Table 4.8SQRD Command Packets for MOSI (external MCU $\rightarrow$ EC-1)

| Word No. | Bit  | Name   | Description                                                                 |

|----------|------|--------|-----------------------------------------------------------------------------|

| 0        | 15:8 | SQRD   | SQRD command (0x03)                                                         |

|          | 7:0  | LEN    | These bits set the number of bytes for sequential reading.                  |

|          |      |        | Allowable settings are up to 255 bytes.                                     |

| 1        | 15:0 | REGADR | These bits specify the addresses of the ESC from which to read.             |

|          |      |        | The specifiable address range is from 0x0000 to 0x2FFF.                     |

| 2        | 15:0 |        | These bits cannot be used with the SQRD command. The value is "don't care". |

| Word No. | Bit   | Name   | Description                                                                    |

|----------|-------|--------|--------------------------------------------------------------------------------|

| 0        | 15:14 | Sts    | Indicates the error state of the SQRD command.                                 |

|          |       |        | 1: An error has occurred.                                                      |

|          |       |        | 0: No error has occurred.                                                      |

|          |       |        | Bit 14: BUSY                                                                   |

|          |       |        | Indicates the state of execution of the SQRD command.                          |

|          |       |        | 1: The command is being executed.                                              |

|          |       |        | 0: End of the command                                                          |

|          | 13:0  | REGADR | These bits indicate the address of the register specified by the SQRD command. |

| 1        | 15:0  | D0     | These bits cannot be used with the SQRD command. The value is "don't care".    |

| 2        | 15:0  | D1     |                                                                                |

### Table 4.9SQRD Command Packets for MISO (EC-1 $\rightarrow$ external MCU)

## 4.4.5 SQWR Command

This command is for the sequential writing of the Process Data RAM of the ESC in the EC-1 by the external MCU.

The length of data and the address where writing of the register is to start are specified.

Up to 255 bytes are specifiable as lengths.

The data for writing must have been stored in the sequential data register beforehand by issuing a DTWR command.

On receiving an SQWR command, the EC-1 writes data stored in the sequential data register to the ESC.

|      |       | Data \          | Nord 0          | Data Word 1                           | Data Word 2                           |

|------|-------|-----------------|-----------------|---------------------------------------|---------------------------------------|

|      | 15 14 | 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

| MOSI |       | SQWR            | LEN             | REGADR                                |                                       |

| MISO | Sts   | RI              | EGADR           |                                       |                                       |

### Figure 4.7 Format of SPI Packets for the SQWR Command

## Table 4.10 SQWR Command Packets for MOSI (external MCU $\rightarrow$ EC-1)

| Word No. | Bit  | Name   | Description                                                                 |

|----------|------|--------|-----------------------------------------------------------------------------|

| 0        | 15:8 | SQWR   | SQWR command (0x04)                                                         |

|          | 7:0  | LEN    | These bits set the number of bytes for sequential writing.                  |

|          |      |        | Allowable settings are up to 255 bytes.                                     |

| 1        | 15:0 | REGADR | These bits specify the addresses of the ESC to which to write.              |

|          |      |        | The specifiable address range is from 0x0000 to 0x2FFF.                     |

| 2        | 15:0 |        | These bits cannot be used with the SQWR command. The value is "don't care". |

| Word No. | Bit   | Name   | Description                                                                    |

|----------|-------|--------|--------------------------------------------------------------------------------|

| 0        | 15:14 | Sts    | Bit 15: ERROR                                                                  |

|          |       |        | Indicates the error state of the SQWR command.                                 |

|          |       |        | 1: An error has occurred.                                                      |

|          |       |        | 0: No error has occurred.                                                      |

|          |       |        | Bit 14: BUSY                                                                   |

|          |       |        | Indicates the state of execution of the SQWR command.                          |

|          |       |        | 1: The command is being executed.                                              |

|          |       |        | 0: End of the command                                                          |

|          | 13:0  | REGADR | These bits indicate the address of the register specified by the SQWR command. |

| 1        | 15:0  | D0     | These bits cannot be used with the SQWR command. The value is "don't care".    |

| 2        | 15:0  | D1     |                                                                                |

### Table 4.11 SQWR Command Packets for MISO (EC-1 $\rightarrow$ external MCU)

## 4.4.6 DTRD Command

This command is for reading the sequential data register by the external MCU.

Specify the length of data to be read. Specify four bytes for reading data other than the last of it. For example, to read 10 bytes, specify four bytes for the first and second DTRD commands and specify the remaining two bytes for the third DTRD command.

The EC-1 reads and transmits data from sequential data register 0 in order on receiving the DTRD command.

In the case above, it reads and transmits: four bytes from sequential data register 0 in response to the first DTRD command, four bytes from sequential data register 1 in response to the second DTRD command, and two bytes from sequential data register 2 in response to the third DTRD command.

|      |       | Data V          | Vord 0          | Data Word 1                           | Data Word 2                           |

|------|-------|-----------------|-----------------|---------------------------------------|---------------------------------------|

|      | 15 14 | 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

| MOSI |       | DTRD LEN        |                 |                                       |                                       |

| MISO | Sts   | RE              | EGADR           | D0                                    | D1                                    |

Figure 4.8 Format of SPI Packets for the DTRD Command

| Table 4.12 | DTRD Command Packets for MOSI (external MCU $\rightarrow$ EC-1) |

|------------|-----------------------------------------------------------------|

|------------|-----------------------------------------------------------------|

| Word No. | Bit  | Name | Description                                                                    |

|----------|------|------|--------------------------------------------------------------------------------|

| 0        | 15:8 | DTRD | DTRD command (0x05)                                                            |

|          | 7:0  | LEN  | These bits set the number of bytes to be read in response to the DTRD command. |

|          |      |      | Allowable settings are 1 to 4 bytes.                                           |

| 1        | 15:0 |      | These bits cannot be used with the DTRD command. The value is "don't care".    |

| 2        | 15:0 |      |                                                                                |

| Word No. | Bit   | Name   | Description                                                           |

|----------|-------|--------|-----------------------------------------------------------------------|

| 0        | 15:14 | Sts    | Bit 15: ERROR                                                         |

|          |       |        | Indicates the error state of the DTRD command.                        |

|          |       |        | 1: An error has occurred.                                             |

|          |       |        | 0: No error has occurred.                                             |

|          |       |        | Bit 14: BUSY                                                          |

|          |       |        | Indicates the state of execution of the DTRD command.                 |

|          |       |        | 1: The command is being executed.                                     |

|          |       |        | 0: End of the command                                                 |

|          | 13:0  | REGADR | These bits indicate the base address of the ESC register read.        |

| 1        | 15:0  | D0     | These bits indicate the results of reading the register.              |

| 2        | 15:0  | D1     | The data are flush left when the length of data is less than 4 bytes. |

### Table 4.13DTRD Command Packets for MISO (EC-1 $\rightarrow$ external MCU)

## 4.4.7 DTWR Command

This command is for writing data to the sequential data register by the external MCU.

Specify the length of data and the data for writing. Specify four bytes for writing data other than the last of it. For example, to write 10 bytes, specify four bytes for the first and second DTWR commands and specify the remaining two bytes for the third DTWR command.

The EC-1 writes the data which have been received from sequential data register 0 in order on receiving the DTWR command.

In the case above, it writes: four bytes to sequential data register 0 in response to the first DTWR command, four bytes to sequential data register 1 in response to the second DTWR command, and two bytes to sequential data register 2 in response to the third DTWR command.

|      | Data Word 0           |      |                 | Data Word 1                           | Data Word 2                         |

|------|-----------------------|------|-----------------|---------------------------------------|-------------------------------------|

|      | 15 14 13 12 11 10 9 8 |      | 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |

| MOSI |                       | DTWR | LEN             | D0                                    | D1                                  |

| MISO | Sts                   | RI   | EGADR           |                                       |                                     |

Figure 4.9

Format of SPI Packets for the DTWR Command

#### Table 4.14 DTWR Command Packets for MOSI (external MCU $\rightarrow$ EC-1)

| Word No. | Bit  | Name | Description                                                                     |

|----------|------|------|---------------------------------------------------------------------------------|

| 0        | 15:8 | DTWR | DTWR command (0x06)                                                             |

|          | 7:0  | LEN  | These bits set the number of bytes for writing in response to the DTWR command. |

|          |      |      | Allowable settings are 1 to 4 bytes.                                            |

| 1        | 15:0 | D0   | These bits set the data for writing to the register.                            |

| 2        | 15:0 | D1   | The data are flush left when the length of data is less than 4 bytes.           |

| Word No. | Bit   | Name   | Description                                                                            |

|----------|-------|--------|----------------------------------------------------------------------------------------|

| 0        | 15:14 | Sts    | Bit 15: ERROR                                                                          |

|          |       |        | Indicates the error state of the DTWR command.                                         |

|          |       |        | 1: An error has occurred.                                                              |

|          |       |        | 0: No error has occurred.                                                              |

|          |       |        | Bit 14: BUSY                                                                           |

|          |       |        | Indicates the state of execution of the DTWR command.                                  |

|          |       |        | 1: The command is being executed.                                                      |

|          |       |        | 0: End of the command                                                                  |

|          | 13:0  | REGADR | These bits indicate the base address of the sequential data register where data are to |

|          |       |        | be stored in response to the DTWR command.                                             |

| 1        | 15:0  | D0     | These bits cannot be used with the DTWR command. The value is "don't care".            |

| 2        | 15:0  | D1     |                                                                                        |

## Table 4.15DTWR Command Packets for MISO (EC-1 $\rightarrow$ external MCU)

### 4.5 **Procedures for Access**

The following describes the procedures for access to the ESC and extended SPI registers in the EC-1 by the external MCU through the SPI interface.

For the specifications of the SPI interface, see section 4, SPI Interface.

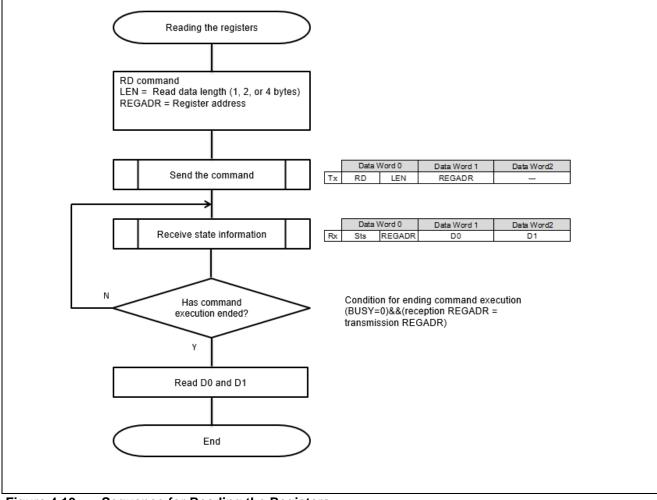

## 4.5.1 Sequence for Reading the Registers

Figure 4.10 shows the sequence for reading the ESC and extended SPI registers by using the RD command.

The results of reading can be acquired immediately in response to issuing each RD command.

1, 2, or 4 bytes of data can be read at a time.

Figure 4.10 Sequence for Reading the Registers

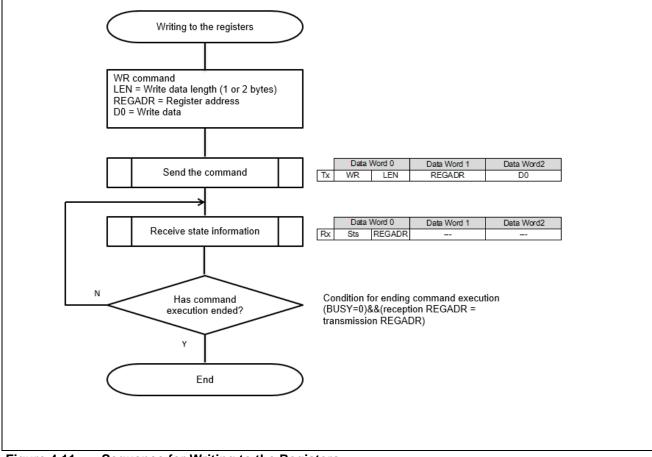

## 4.5.2 Sequence for Writing to the Registers

Figure 4.11 shows the sequence for writing to the ESC and extended SPI registers by using the WR command.

Data to be written can be reflected immediately in response to issuing each WR command.

1 or 2 bytes of data can be written at a time. Note that 4-byte writing is not allowed.

Figure 4.11 Sequence for Writing to the Registers

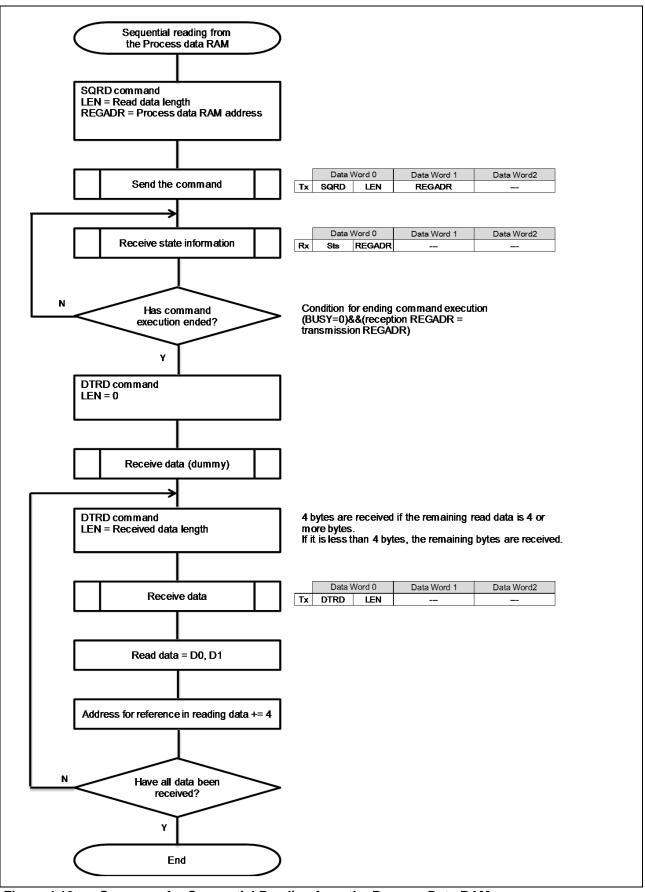

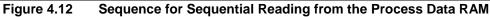

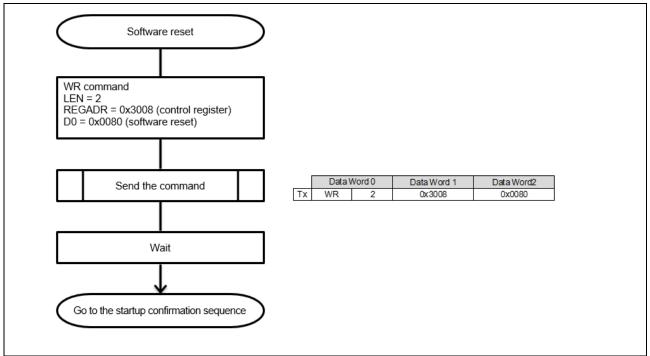

### 4.5.3 Sequence for Sequential Reading from the Process Data RAM

Figure 4.12 shows the sequence for sequential reading of data from the Process Data RAM of the ESC.

The SQRD and DTRD commands are used.

First, the address where the Process Data RAM starts and the data length (up to 255 bytes) to be read by using the SQRD command are specified.

Upon receiving the SQRD command, the EC-1 stores data in a sequential data register of the extended registers by reading the specified area of the Process Data RAM.

After that, issue a single DTRD command to dummy read the sequential data register. The data in the sequential data register are then acquired. In receiving data by using the DTRD command, confirming the completion of execution of the command is not required, so the continuous reception of data is possible.

### 4.5.4 Sequence for Sequential Writing to the Process Data RAM

Figure 4.13 shows the sequence for sequential writing of data to the process data RAM of the ESC.

The DTWR and SQWR commands are used.

First, all data to be written by using the DTWR command are stored in a sequential data register. In transmitting data by using the DTWR command, confirming the completion of execution of the command is not required, so the continuous transmission of data is possible.

After that, the address where the Process Data RAM starts and the data length (up to 255 bytes) are specified by using the SQWR command.

Upon receiving the SQWR command, the EC-1 writes data to the specified area of the Process Data RAM in a sequential data register of the extended registers.

Figure 4.13 Sequence for Sequential Writing to the Process Data RAM

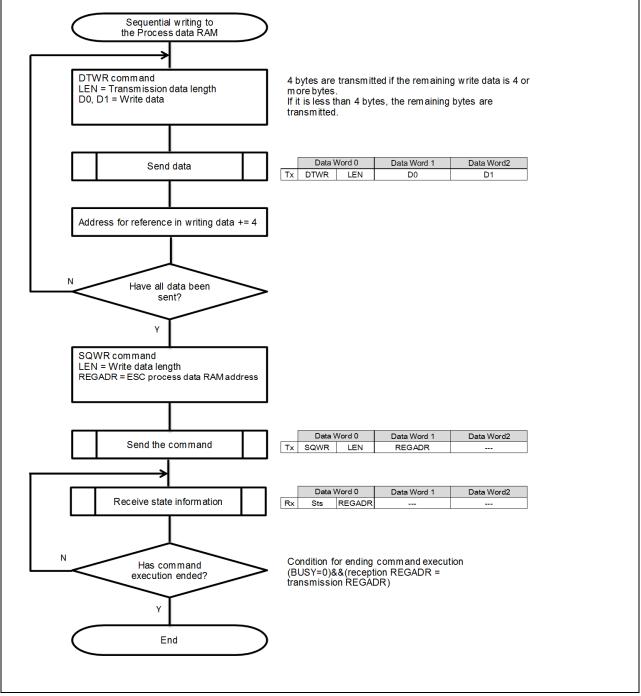

## 4.5.5 Extended Registers: Sequence for Confirming Startup

Before running the EtherCAT protocol, confirm that SPI communications with the EC-1 are trouble-free.

Figure 4.14 shows the sequence for confirming startup.

4 bytes of the device ID register (0x3000) among the extended registers are read by using the RD command. If 'EC-1' (0x45435E31) is read, communications are proceeding normally.

Figure 4.14 Sequence for Confirming Startup

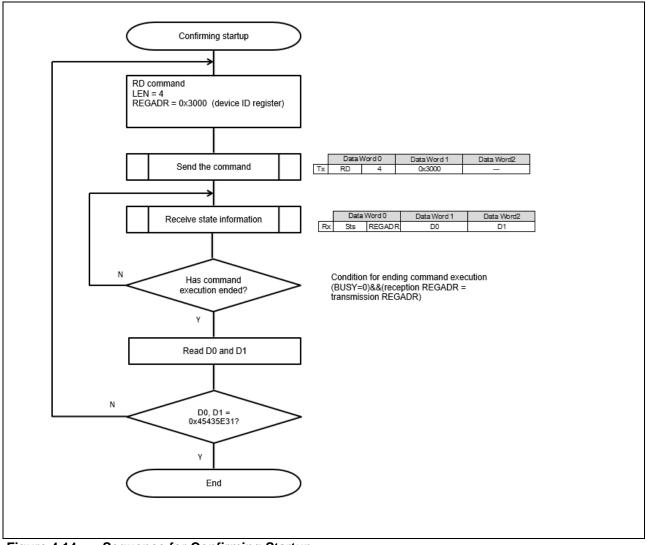

### 4.5.6 Extended Registers: Software Reset Sequence

Figure 4.15 shows the sequence for a software reset by the EC-1.

The WR command is used to write 2 bytes of code (0x0080) to apply a software reset through the control register (0x3008) among the extended registers.

The EC-1 executes a software reset immediately upon reception of the command.

SPI communications do not proceed while the EC-1 is being restarted. Wait and then execute the startup confirmation sequence.

Figure 4.15 Software Reset Sequence

## 5. Software

## 5.1 Operation in Outline

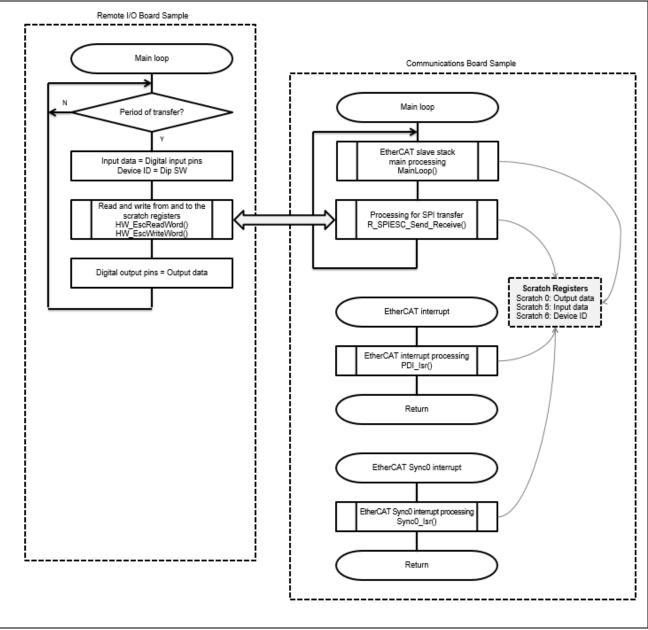

Table 5.1 gives an outline of the operation of the ESC SPI connection library. Figure 5.1 is a block diagram of the system.

Table 5.1Operation in Outline

| Function              | Outline                                                                                  |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------|--|--|--|

| Outline of Processing | Handles transfer to and from an external MCU as the SPI master and reads from and writes |  |  |  |

|                       | to the ESC and extended SPI registers.                                                   |  |  |  |

| RSPI settings         | Channel: CH0 or CH1 is selectable.                                                       |  |  |  |

|                       | SPI operation: Four-wire connection                                                      |  |  |  |

|                       | Transfer mode: Slave mode (transmission and reception)                                   |  |  |  |

|                       | Data length: 16 bits × 3 words                                                           |  |  |  |

|                       | Bit rate: Up to 18.75 Mbps                                                               |  |  |  |

| Interrupt sources     | Interrupt sources                                                                        |  |  |  |

|                       | RSPI reception buffer full interrupt                                                     |  |  |  |

|                       | RSPI transmission buffer empty interrupt                                                 |  |  |  |

|                       | RSPI error interrupt                                                                     |  |  |  |

Figure 5.1 Block Diagram of the System

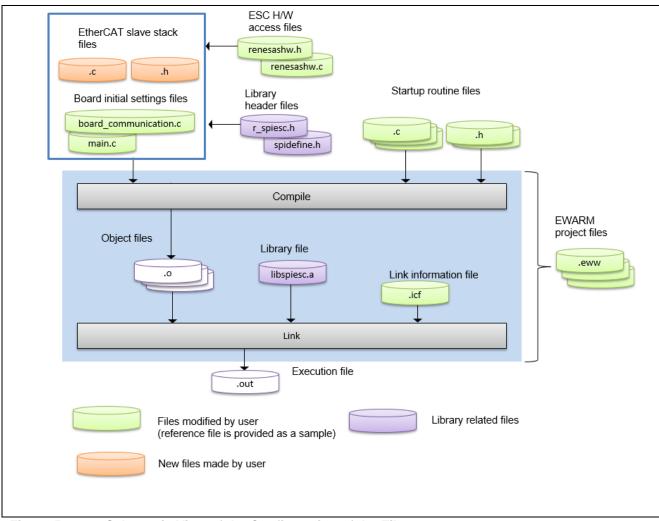

## 5.2 **Procedure for Designing Software**

Figure 5.2 is a schematic view of the configuration of the files.

In the sample program, the initial settings file for the board is for the EC-1 communications board. Modify the file according to the hardware environment you will actually be using.

Figure 5.2 Schematic View of the Configuration of the Files

## 5.3 Interrupts

Table 5.2 lists the interrupts used in the library.

### Table 5.2 Interrupts Used in the Library

| Interrupt Source (Source ID)                    | Priority | Processing in Outline                            |

|-------------------------------------------------|----------|--------------------------------------------------|

| RSPI reception buffer full interrupt (RSPI)     | 0        | Processing for completion of reception           |

| RSPI transmission buffer empty interrupt (SPTI) | 0        | Processing for completion of transmission        |

| RSPI error interrupt (SPEI)                     | 0        | Overrun, parity, and mode fault error processing |

## 5.4 Fixed-Width Integers

Table 5.3 lists the fixed-width integers used in the library.

### Table 5.3 Fixed-Width Integers Used in the Library

| Symbol Description |                                                           |  |  |

|--------------------|-----------------------------------------------------------|--|--|

| int8_t             | 8-bit signed integer (defined in the standard library)    |  |  |

| int16_t            | 16-bit signed integer (defined in the standard library)   |  |  |

| int32_t            | 32-bit signed integer (defined in the standard library)   |  |  |

| int64_t            | 64-bit signed integer (defined in the standard library)   |  |  |

| uint8_t            | 8-bit unsigned integer (defined in the standard library)  |  |  |

| uint16_t           | 16-bit unsigned integer (defined in the standard library) |  |  |

| uint32_t           | 32-bit unsigned integer (defined in the standard library) |  |  |

| uint64_t           | 64-bit unsigned integer (defined in the standard library) |  |  |

## 5.5 Constants and Error Codes

Table 5.4 to Table 5.8 list the constants and Table 5.9 lists the error codes used in the library.

#### Table 5.4 Constants Used in the Library (Initial Settings)

| Constant        | Setting | Description                                           |

|-----------------|---------|-------------------------------------------------------|

| SPIESC_CH0      | 0       | RSPI CH0 is selected.                                 |

| SPIESC_CH1      | 1       | RSPI CH1 is selected.                                 |

| SPIESC_LOG_NONE | 0       | Log output specification (not output)                 |

| SPIESC_LOG_DATA | 1       | Log output specification (output of transferred data) |

| SPIESC_LOG_MSG  | 2       | Log output specification (output of error code)       |

#### Table 5.5 Constants Used in the Library (Packet Settings)

| Constant          | Setting | Description                                                                                    |  |  |

|-------------------|---------|------------------------------------------------------------------------------------------------|--|--|

| SPI_PACKET 3      |         | Number of words of SPI communications packets                                                  |  |  |

| SPI_SQDATA_BYTE   | 4       | Maximum number of bytes which can be transferred at a time by using the DTRD and DTWR commands |  |  |

| SPI_SQDATA_BUFNUM | 64      | Number of the sequential data registers                                                        |  |  |

#### Table 5.6Constants Used in the Library (Commands)

| Constant     | Setting | Description  |

|--------------|---------|--------------|

| SPI_CMD_RD   | 0x0001  | RD command   |

| SPI_CMD_WR   | 0x0002  | WR command   |

| SPI_CMD_SQRD | 0x0003  | SQRD command |

| SPI_CMD_SQWR | 0x0004  | SQWR command |

| SPI_CMD_DTRD | 0x0005  | DTRD command |

| SPI_CMD_DTWR | 0x0006  | DTWR command |

### Table 5.7 Constants Used in the Library (Extended SPI Registers)

| Constant                | Setting | Description                                                                           |  |  |

|-------------------------|---------|---------------------------------------------------------------------------------------|--|--|

| SPIREG_MISC_BASE        | 0x3000  | Extended SPI register base address                                                    |  |  |

| SPIREG_DEVICEID1 0x3000 |         | Device ID register address (higher-order word)                                        |  |  |

| SPIREG_DEVICEID2        | 0x3002  | Device ID register address (lower-order word)                                         |  |  |

| SPIREG_REVNO            | 0x3004  | Revision number register address                                                      |  |  |

| SPIREG_STATUS           | 0x3006  | Status register address                                                               |  |  |

| SPIREG_CTRL             | 0x3008  | Control register address                                                              |  |  |

| SPIREG_SCRATCH0         | 0x300A  | Scratch 0 register address                                                            |  |  |

| SPIREG_SCRATCH1         | 0x300C  | Scratch 1 register address                                                            |  |  |

| SPIREG_SCRATCH2         | 0x300E  | Scratch 2 register address                                                            |  |  |

| SPIREG_SCRATCH3         | 0x3010  | Scratch 3 register address                                                            |  |  |

| SPIREG_SCRATCH4         | 0x3012  | Scratch 4 register address                                                            |  |  |

| SPIREG_SCRATCH5         | 0x3014  | Scratch 5 register address                                                            |  |  |

| SPIREG_SCRATCH6         | 0x3016  | Scratch 6 register address                                                            |  |  |

| SPIREG_SCRATCH7         | 0x3018  | Scratch 7 register address                                                            |  |  |

| SPIREG_SCRATCH8         | 0x301A  | Scratch 8 register address                                                            |  |  |

| SPIREG_SCRATCH9         | 0x301C  | Scratch 9 register address                                                            |  |  |

| SPIREG_SQDATANUM        | 0x301E  | Sequential data number register address                                               |  |  |

| SPIREG_SQDATA0          | 0x3020  | Sequential data register address                                                      |  |  |

| SPIREG_MISC_MAX16       | 0x311E  | Upper-limit on the address when access to an extended SPI register is in 16-bit units |  |  |

| SPIREG_MISC_MAX32       | 0x311C  | Upper-limit on the address when access to an extended SPI register is in 32-bit units |  |  |

#### Table 5.8 Constants Used in the Library (Control Code)

| Constant           | Setting | Description                 |  |

|--------------------|---------|-----------------------------|--|

| SPICTRLCODE_STSCLR | 0x0001  | The error code is cleared.  |  |

| SPICTRLCODE_RST    | 0x0080  | The EC-1 software is reset. |  |

### Table 5.9Error Codes Used in the Library

| Constant                       | Setting | Description                                         |

|--------------------------------|---------|-----------------------------------------------------|

| SPISTATUSCODE_NOERROR          | 0x0000  | No error has occurred.                              |

| SPISTATUSCODE_INVALID_CMD      | 0x0001  | Error in the received command                       |

| SPISTATUSCODE_INVALID_LENGTH   | 0x0002  | Erroneous word length in the received command       |

| SPISTATUSCODE_INVALID_ADDR     | 0x0003  | Erroneous address specified in the received command |

| SPISTATUSCODE_INVALID_SQDATA   | 0x0004  | Error in the sequence of the DTRD and DTWR commands |

| SPISTATUSCODE_INVALID_CTRLCODE | 0x0005  | Error in the control code                           |

| SPISTATUSCODE_COMERROR         | 0x0010  | Error in overall SPI communications                 |

| SPISTATUSCODE_OVRERROR         | 0x0011  | Overrun error                                       |

| SPISTATUSCODE_MODERROR         | 0x0012  | Mode fault error                                    |

Guide for Connecting an External MCU with the SPI

SPISTATUSCODE\_PERERROR 0x0014 Parity error

## 5.6 Structures and Unions

Table 5.10 to Table 5.13 list the structures and unions used in the library.

### Table 5.10Structures and Unions Used in the Library (1)

| Definitions of Structures<br>and Unions | Outline                                                                             | Definition File |

|-----------------------------------------|-------------------------------------------------------------------------------------|-----------------|

| spi_t                                   | Definition of the structure for setting SPI packets <ul> <li>MOSI member</li> </ul> | spidefine.h     |

|                                         | The external MCU (master) sets data for transmission.                               |                 |

|                                         | The EC-1 (slave) acquires data as received data.                                    |                 |

|                                         | MISO member                                                                         |                 |

|                                         | The EC-1 (slave) sets data for transmission.                                        |                 |

|                                         | The external MCU (master) acquires data as received data.                           |                 |

| T_SPIREG_STD16                          | Definition of the union for the 16-bit extended SPI registers                       | spidefine.h     |

| T_SPIREG_STD32                          | Definition of the union for the 32-bit extended SPI registers                       | spidefine.h     |

| T_SPIREG_STATUS                         | Definition of the union for the status register                                     | spidefine.h     |

| spi_misc_t                              | Definition of the structure for the extended SPI registers as a whole               | spidefine.h     |

### Table 5.11 Structures and Unions Used in the Library (2)

| Definitions of<br>Structures and Unions | Member      |             |                    | Description                                                 |

|-----------------------------------------|-------------|-------------|--------------------|-------------------------------------------------------------|

| spi_t                                   | union CMDRD | BIT         | uint32_t REGADR:14 | MISO REGADR setting                                         |

|                                         |             |             | uint32_t BUSY:1    | MISO Sts BUSY bit                                           |

|                                         |             |             |                    | 1: The command is being                                     |

|                                         |             |             |                    | executed.                                                   |

|                                         |             |             |                    | 0: End of the command                                       |

|                                         |             |             | uint32_t EEOR:1    | MISO Sts ERROR bit                                          |

|                                         |             |             |                    | 1: An error has occurred.                                   |

|                                         |             |             |                    | 0: No error has occurred.                                   |

|                                         |             |             | uintt32_t: 16      |                                                             |

|                                         |             | BYTE        | uint8_t B0         | MISO D1 higher-order byte                                   |

|                                         |             |             | uint8_t B1         | MISO D1 lower-order byte                                    |

|                                         |             |             | uint8_t B2         | MISO D0 higher-order byte                                   |

|                                         |             |             | uint8_t B3         | MISO D0 lower-order byte                                    |

|                                         |             | WORD        | uint16_t W0        | MISO D0                                                     |

|                                         |             |             | uint16_t W1        | MISO D1                                                     |

|                                         |             | uint32_t DW | ORD                | MISO D1/D0                                                  |

|                                         | CMDWR       | uint8_t CMD |                    | MOSI CMD setting                                            |

|                                         |             | uint8_t LEN |                    | MOSI LEN setting                                            |

|                                         |             | uint16_t RE | GADR               | MOSI REGADR setting                                         |

|                                         | T_SPIREG_ST | D32 DATARD  |                    | Read data setting for the RD and                            |

|                                         |             |             |                    | DTRD commands for MISO                                      |

|                                         | T_SPIREG_ST | D32 DATAWR  | 1                  | Write data setting for the WR and<br>DTWR commands for MOSI |

| Definitions of Member Description |                |                  | Description                            |  |

|-----------------------------------|----------------|------------------|----------------------------------------|--|

| Structures and Unions             |                |                  |                                        |  |

| union                             | BYTE           | uint8_t B0       | Generic definition of 16-bit registers |  |

| T_SPIREG_STD16                    |                |                  | Higher-order byte                      |  |

|                                   |                | uint8_t B1       | Lower-order byte                       |  |

|                                   | uint16_t WORD  |                  | Word                                   |  |

| union                             | BYTE           | uint8_t B0       | Generic definition of 32-bit registers |  |

| T_SPIREG_STD32                    |                |                  | Most significant byte                  |  |

|                                   |                | uint8_t B1       | Higher-order byte                      |  |

|                                   |                | uint8_t B2       | Lower-order byte                       |  |

|                                   |                | uint8_t B3       | Least-significant byte                 |  |

|                                   | WORD           | uint16_t W0      | Higher-order word                      |  |

|                                   |                | uint16_t W1      | Lower-order word                       |  |

|                                   | uint32_t DWORD |                  | Double word                            |  |

| union                             | BIT            | uint16_t ERROR:1 | Definition of the status register      |  |

| T_SPIREG_STATUS                   |                |                  | ERROR bit                              |  |

|                                   |                |                  | 1: An error has occurred.              |  |

|                                   |                |                  | 0: No error has occurred.              |  |

|                                   |                | uint16_t BUSY:1  | BUSY bit                               |  |

|                                   |                |                  | 1: The command is being executed.      |  |

|                                   |                |                  | 0: End of the command                  |  |

|                                   |                | uint16_t :14     |                                        |  |

|                                   | BYTE           | uint8_t B0       | Higher-order byte                      |  |

|                                   |                | uint8_t B1       | Lower-order byte                       |  |

|                                   | uint16_t WORD  |                  | Word                                   |  |

## Table 5.12 Structures and Unions Used in the Library (3)

## Table 5.13Structures and Unions Used in the Library (4)

| Definitions of<br>Structures and Unions | Member                      | Description                         |

|-----------------------------------------|-----------------------------|-------------------------------------|

| spi_misc_t                              | T_SPIREG_STD16 DEVICEID1    | Device ID register                  |

|                                         |                             | Higher-order word                   |

|                                         | T_SPIREG_STD16 DEVICEID2    | Device ID register                  |

|                                         |                             | Lower-order word                    |

|                                         | T_SPIREG_STD16 REVNO        | Revision number register            |

|                                         | T_SPIREG_STD16 STATUS       | Status register                     |

|                                         | T_SPIREG_STD16 CTRL         | Control register                    |

|                                         | T_SPIREG_STD16 SCRATCH [10] | Scratch registers (0 to 9)          |

|                                         | T_SPIREG_STD16 SQDATANUM    | Sequential data number register     |

|                                         | T_SPIREG_STD16 SQDATA [64]  | Sequential data registers (0 to 63) |

## 5.7 Global Variables

Table 5.14 lists the global variables used in the library.

### Table 5.14 Global Variables Used in the Library

| Туре        | Variable | Description                             | Function Used           |

|-------------|----------|-----------------------------------------|-------------------------|

| spi_t       | SPI      | Information of SPI packet data settings | R_SPIEsc_Create()       |

|             |          |                                         | R_SPIEsc_Send_Receive() |

| spi_,misc_t | SPIMISC  | Information of extended SPI registers   | R_SPIEsc_Create()       |

|             |          |                                         | R_SPIEsc_Send_Receive() |

## 5.8 Functions

Table 5.15 lists the functions in the library.

## Table 5.15 Library Functions

| Function              | Page Number |

|-----------------------|-------------|

| R_SPIEsc_Pin_Init     | 33          |

| R_SPIEsc_Create       | 33          |

| R_SPIEsc_Start        | 35          |

| R_SPIEsc_Stop         | 36          |

| R_SPIEsc_Send_Receive | 37          |

## 5.9 Specifications of the Functions

The following describes the specifications of the library functions.

### 5.9.1 **Processing for the Initial Settings of the SPI Pins**

### R\_SPIESC\_PinInit

#### (1) Outline

Initial settings for the pins for SPI communications

#### (2) C-Language Format

#### void R\_SPIESC\_PinInt (uint\_16t ch);

#### (3) Parameter

| I/O | F        | Parameter | Description                                    |

|-----|----------|-----------|------------------------------------------------|

| Ι   | uint16_t | ch        | RSPI channels to be used in SPI communications |

|     |          |           | SPIESC_CH0: Channel 0                          |

|     |          |           | RSPCK0, MISO0, MOSI0, and SSL00 are used.      |

|     |          |           | SPIESC_CH1: Channel 1                          |

|     |          |           | RSPCK1, MISO1, MOSI1, and SSL10 are used.      |

#### (4) Function

This function makes initial settings for the pins to be used in SPI communications.

#### (5) Return Value

None

Remark 1. When executing this API function, make sure that writing to the PFS register is enabled by using the write protection register (PWPR).

#### 5.9.2 Initialization Processing for SPI Control

### R\_SPIESC\_Create(uint16\_t log)

#### (1) Outline

Initialization processing for RSPI control

#### (2) C-Language Format

#### void R\_SPIESC\_Create(uint16\_t log);

### (3) Parameter

| I/O |          | Parameter | Description                                                            |

|-----|----------|-----------|------------------------------------------------------------------------|

| I   | uint16_t | log       | Specifies the log output for SPI communications.                       |

|     |          |           | SPIESC_LOG_NONE: A log is not output.                                  |

|     |          |           | SPIESC_LOG_DATA: A log of the transfer data is output.                 |

|     |          |           | SPIESC_LOG_MSG: A log of the error codes set in the status register in |

|     |          |           | response to errors is output.                                          |

The logical OR of SPIESC\_LOG\_DATA and SPIESC\_LOG\_MSG can be set.

### (4) Function

This function handles initialization which is required for control of SPI communications.