# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

# M16C/80 Group, M32C/8B Group Differences between M16C/80 and M32C/8B

# 1. Abstract

This document describes differences between the M16C/80 144-pin package and the M32C/8B 144-pin package. Refer to each device's hardware manual or software manual for details.

# 2. Introduction

The document described in this document applies to the following MCUs:

•MCUs: M16C/80 144-pin package M32C/8B 144-pin package

Refer to the latest hardware manuals and technical updates when using this application note.

# 3. Differences

# 3.1 Differences in Functions

Table 3.1 and Table 3.2 list differences in functions.

| Table 3.1 | Differences in | Functions | (1/2) |

|-----------|----------------|-----------|-------|

|           |                |           |       |

| Item                                                          |                                           | M16C/80                                                                                                                                                  | M32C/8B                                                                                                                                                                                                                                                                                                                                                                     |  |

|---------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Basic Instructio                                              | ons                                       | 106 instructions                                                                                                                                         | 108 instructions                                                                                                                                                                                                                                                                                                                                                            |  |

| Minimum Instruction Execution<br>Time                         |                                           | 50 ns (f(XIN) = 20 MHz)                                                                                                                                  | 31.3 ns (f(CPU) = 32 MHz, VCC = 3.0 to 5.5 V)                                                                                                                                                                                                                                                                                                                               |  |

| Power Supply (                                                | Channels                                  | 1 channel (VCC)                                                                                                                                          | 2 channels (VCC1, VCC2)                                                                                                                                                                                                                                                                                                                                                     |  |

| Supply Voltage                                                |                                           | •4.2 V to 5.5 V (f(XIN) = 20 MHz)<br>•2.7 V to 5.5 V (f(XIN) = 10 MHz)                                                                                   | •VCC1 = 3.0 V to 5.5 V<br>•VCC2 = 3.0 V to VCC1                                                                                                                                                                                                                                                                                                                             |  |

| Current Consumption                                           |                                           | •45 mA (VCC = 5 V, f(XIN) = 20 MHz)<br>•14 mA (VCC = 3.0 V, f(XIN) = 10 MHz)<br>•1.5 μA (VCC = 3.0 V, f(XCIN) = 32 kHz,<br>oscillation capability = Low) | •26 mA (32 MHz, VCC1 = VCC2 = 5 V)<br>•23 mA (32 MHz, VCC1 = VCC2 = 3.3 V<br>•110 $\mu$ A (approx. 1 MHz, VCC1 = VCC2<br>= 3.3 V, on-chip oscillator low-power<br>consumption mode $\rightarrow$ wait mode)<br>•8 $\mu$ A (approx. 32 kHz, VCC1 = VCC2 =<br>3.3 V, low-power consumption mode $\rightarrow$<br>wait mode)<br>•4 $\mu$ A (VCC1 = VCC2 = 3.3 V, stop<br>mode) |  |

| Clock Number of<br>Generation Circuits<br>Circuits            |                                           | 2 circuits:<br>•Main clock<br>•Sub clock                                                                                                                 | 4 circuits:<br>•Main clock<br>•Sub clock<br>•On-chip oscillator<br>•PLL frequency synthesizer                                                                                                                                                                                                                                                                               |  |

|                                                               | Maximum<br>Frequency of<br>the Main Clock | 20 MHz                                                                                                                                                   | 16 MHz                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                               | Oscillation Stop<br>Detection             | Not available                                                                                                                                            | Main clock oscillation stop detect function                                                                                                                                                                                                                                                                                                                                 |  |

|                                                               | System Clock<br>Protect<br>Function       | Not available                                                                                                                                            | Available                                                                                                                                                                                                                                                                                                                                                                   |  |

| Power Flash Memory<br>Consumption Low-speed<br>Control Access |                                           | Not available                                                                                                                                            | Available (flash memory version)                                                                                                                                                                                                                                                                                                                                            |  |

| Main Voltage<br>Regulator Stop<br>Function                    |                                           | Not available                                                                                                                                            | Available                                                                                                                                                                                                                                                                                                                                                                   |  |

| Power Supply \                                                | Voltage Detection                         | Not available                                                                                                                                            | Voltage monitor interrupt (optional) <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                         |  |

| Bus                                                           | Bus Wait States                           | No wait state to 3 wait states                                                                                                                           | 1 wait state to 7 wait states                                                                                                                                                                                                                                                                                                                                               |  |

|                                                               | Recovery Cycle                            | Not available                                                                                                                                            | Insertable                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                               | Page Mode<br>Control<br>Function          | Not available                                                                                                                                            | Available (ROMless version)                                                                                                                                                                                                                                                                                                                                                 |  |

| Watchdog<br>Timer                                             |                                           | •BCLK (main clock, sub clock)                                                                                                                            | <ul> <li>CPU clock (main clock, sub clock, PLL<br/>frequency synthesizer)</li> <li>On-chip oscillator clock</li> </ul>                                                                                                                                                                                                                                                      |  |

Note:

1. Please contact a Renesas sales office for optional features.

| lte                            | em                                | M16C/80                                                                                                                                                                                                                              | M32C/8B                                                                                                                                                                             |

|--------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMACII                         |                                   | Not available                                                                                                                                                                                                                        | Available                                                                                                                                                                           |

| Timer                          | Count Source                      | f1, f8, f32, fC32                                                                                                                                                                                                                    | f1, f8, f2n, fC32<br>(n = 0 to 15, no division only where n = 0)                                                                                                                    |

| Timer for Three-               | Count Source                      | f1, f8, f32, fC32                                                                                                                                                                                                                    | f1                                                                                                                                                                                  |

| Phase Motor                    | Dead Time                         | Enabled                                                                                                                                                                                                                              | Selectable from enabled and disabled                                                                                                                                                |

| Control                        | Dead Time<br>Trigger              | Fixed                                                                                                                                                                                                                                | Selectable                                                                                                                                                                          |

| Serial Interface               | Operating<br>Modes                | •(Clock synchronous mode, clock<br>asynchronous mode) × 2 channels<br>•(Clock synchronous mode, clock<br>asynchronous mode, l <sup>2</sup> C-bus, IEBus <sup>(1)</sup><br>(optional <sup>(2)</sup> ), SIM interface) × 3<br>channels | •(Clock synchronous mode, clock<br>asynchronous mode, I <sup>2</sup> C-bus, special<br>mode 2, GCI mode, SIM mode, IEBus <sup>(1)</sup><br>(optional <sup>(2)</sup> )) × 5 channels |

|                                | Count Source                      | f1, f8, f32                                                                                                                                                                                                                          | f1, f8, f2n $(n = 0 \text{ to } 15, \text{ no division only where } n = 0)$                                                                                                         |

| A/D Converter                  | Operating Clock<br>$\phi$ AD      | •fAD, fAD/2, fAD/4, fAD = f(XIN) (VCC = 5 V)<br>•fAD/2, fAD/4, fAD = f(XIN) (VCC = 3 V)                                                                                                                                              | •fAD, fAD/2, fAD/3, fAD/4, fAD/6, fAD/8                                                                                                                                             |

|                                | Operating<br>Modes                | 5 modes                                                                                                                                                                                                                              | 7 modes                                                                                                                                                                             |

| Analog Input<br>Pins           |                                   | 10 pins:<br>•8 pins of AN_0 to AN_7<br>•2 extended input pins (ANEX0 and<br>ANEX1)                                                                                                                                                   | 34 pins:<br>•8 pins of AN_0 to AN_7<br>•8 pins of AN0_0 to AN0_7<br>•8 pins of AN2_0 to AN2_7<br>•8 pins of AN15_0 to AN15_7<br>•2 extended input pins (ANEX0 and<br>ANEX1)         |

| DRAM Controller                | -                                 | Available                                                                                                                                                                                                                            | Not available                                                                                                                                                                       |

| Flash<br>Memory <sup>(3)</sup> | Rewrite Mode                      | •CPU rewrite mode (EW0 mode)                                                                                                                                                                                                         | •EW0 mode<br>•EW1 mode                                                                                                                                                              |

|                                | Program<br>Method                 | In units of pages (in units of 256-byte)                                                                                                                                                                                             | In units of 4-byte                                                                                                                                                                  |

|                                | Erase Method                      | •Collective erase<br>•Block erase                                                                                                                                                                                                    | •Block erase                                                                                                                                                                        |

|                                | Number of<br>Software<br>Commands | 8 commands                                                                                                                                                                                                                           | 9 commands                                                                                                                                                                          |

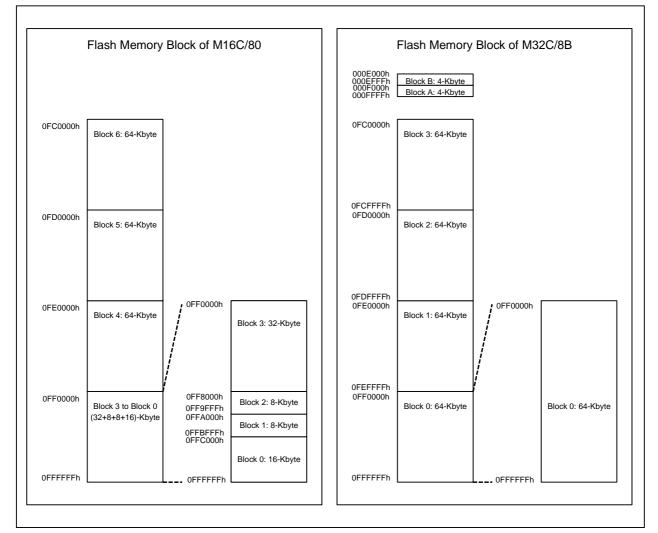

|                                | Data Flash                        | Not available                                                                                                                                                                                                                        | 4-Kbyte × 2 (block A, block B)                                                                                                                                                      |

| User ROM                       |                                   | •64-Kbyte × 3<br>•32-Kbyte × 1<br>•16-Kbyte × 1<br>•8-Kbyte × 2                                                                                                                                                                      | ●64-Kbyte × 4                                                                                                                                                                       |

#### Table 3.2Differences in Functions (2/2)

Notes:

- 1. IEBus is a registered trademark of NEC Electronics Corporation.

- 2. Please contact a Renesas sales office for optional features.

- 3. Only flash memory version

# 3.2 **Pin Characteristics**

Table 3.1 lists differences in pin characteristics.

#### Table 3.3Differences in Pin Characteristics

| M16C/80                    | M32C/8B                          | Changes from M16C/80              |

|----------------------------|----------------------------------|-----------------------------------|

| VCC                        | VCC1, VCC2                       | Deleted: VCC<br>Added: VCC1/VCC2  |

| P7_3/CTS2/RTS2/TA1IN/V     | P7_3/TA1IN/ V/CTS2/RTS2/SS2      | Added: SS2                        |

| P7_1/RXD2/SCL2/TA0IN/TB5IN | P7_1/TA0IN/TB5IN/RXD2/SCL2/STXD2 | Added: STXD2                      |

| P7_0/TXD2/SDA2/TA0OUT      | P7_0/TA0OUT/TXD2/SDA2/SRXD2      | Added: SRXD2                      |

| P6_7/TXD1                  | P6_7/TXD1/SDA1/SRXD1             | Added: SDA1/SRXD1                 |

| P6_6/RXD1                  | P6_6/RXD1/SCL1/STXD1             | Added: SCL1/STXD1                 |

| P6_4/CTS1/RTS1/CTS0/CLKS1  | P6_4/CTS1/RTS1/SS1               | Deleted: CTS0/CLKS1<br>Added: SS1 |

| P6_3/TXD0                  | P6_3/TXD0/SDA0/SRXD0             | Added: SDA0/SRXD0                 |

| P6_2/RXD0                  | P6_2/RXD0/SCL0/STXD0             | Added: SCL0/STXD0                 |

| P6_0/CTS0/RTS0             | P6_0/CTS0/RTS0/SS0               | Added: SS0                        |

| P5_6/ALE/RAS               | P5_6/ALE                         | Deleted: RAS                      |

| P5_2/RD/DW                 | P5_2/RD                          | Deleted: DW                       |

| P5_1/WRH/BHE/CASH          | P5_1/WRH/BHE                     | Deleted: CASH                     |

| P5_0/WRL/WR/CASL           | P5_0/WRL/WR                      | Deleted: CASL                     |

| P4_4/CS3/A20 (MA12)        | P4_4/CS3/A20                     | Deleted: MA12                     |

| P4_3/A19 (MA11)            | P4_3/A19                         | Deleted: MA11                     |

| P4_2/A18 (MA10)            | P4_2/A18                         | Deleted: MA10                     |

| P4_1/A17 (MA9)             | P4_1/A17                         | Deleted: MA9                      |

| P4_0/A16 (MA8)             | P4_0/A16                         | Deleted: MA8                      |

| P3_7/A15 (MA7) (/ D15)     | P3_7/A15, [A15/D15]              | Deleted: MA7                      |

| P3_6/A14 (MA6) (/ D14)     | P3_6/A14, [A14/D14]              | Deleted: MA6                      |

| P3_5/A13 (MA5) (/ D13)     | P3_5/A13, [A13/D13]              | Deleted: MA5                      |

| P3_4/A12 (MA4) (/ D12)     | P3_4/A12, [A12/D12]              | Deleted: MA4                      |

| P3_3/A11 (MA3) (/ D11)     | P3_3/A11, [A11/D11]              | Deleted: MA3                      |

| P3_2/A10 (MA2) (/ D10)     | P3_2/A10, [A10/D10]              | Deleted: MA2                      |

| P3_1/A9 (MA1) (/ D9)       | P3_1/A9, [A9/D9]                 | Deleted: MA1                      |

| P3_0/A8 (MA0) (/ D8)       | P3_0/A8, [A8/D8]                 | Deleted: MA0                      |

| P0_7/D7                    | P0_7/AN0_7/D7                    | Added: AN0_7                      |

| P0_6/D6                    | P0_6/AN0_6/D6                    | Added: AN0_6                      |

| P0_5/D5                    | P0_5/AN0_5/D5                    | Added: AN0_5                      |

| P0_4/D4                    | P0_4/AN0_4/D4                    | Added: AN0_4                      |

| P0_3/D3                    | P0_3/AN0_3/D3                    | Added: AN0_3                      |

| P0_2/D2                    | P0_2/AN0_2/D2                    | Added: AN0_2                      |

| P0_1/D1                    | P0_1/AN0_1/D1                    | Added: AN0_1                      |

| P0_0/D0                    | P0_0/AN0_0/D0                    | Added: AN0_0                      |

| P15_7                      | P15_7/AN15_7                     | Added: AN15_7                     |

| <br>P15_6                  | <br>P15_6/AN15_6                 | Added: AN15_6                     |

| P15_5                      | P15_5/AN15_5                     | Added: AN15_5                     |

| <br>P15_4                  | <br>P15_4/AN15_4                 | Added: AN15_4                     |

| <br>P15_3                  | <br>P15_3/AN15_3                 | Added: AN15_3                     |

| P15_2                      | P15_2/AN15_2                     | Added: AN15_2                     |

| P15_1                      | P15_1/AN15_1                     | Added: AN15_1                     |

| P15_0                      | P15_0/AN15_0                     | Added: AN15_0                     |

# 4. Detailed Comparison

#### 4.1 Differences in Processor Mode

Table 4.1 lists the differences in processor mode associated SFR.

#### Table 4.1Differences in Processor Mode Associated SFR

| Symbol | Add     | ress    | Bit    | Differences                                      |                                                          |

|--------|---------|---------|--------|--------------------------------------------------|----------------------------------------------------------|

| Symbol | M16C/80 | M32C/8B | ы      | M16C/80                                          | M32C/8B                                                  |

| PM1    | 0005h   |         | 3      | Reserved bit                                     | SFR area wait bit<br>0: 1 wait state<br>1: 2 wait states |

|        |         |         | 7 to 6 | Reserved bits<br>Set to 1 (flash memory version) | Reserved bits<br>Set to 0                                |

#### 4.2 Differences in Bus

Table 4.2 lists the differences in bus and Table 4.3 lists the differences in bus associated SFR.

#### Table 4.2Differences in Bus

| Item                       | M16C/80                        | M32C/8B                       |

|----------------------------|--------------------------------|-------------------------------|

| Bus Wait Status            | No wait state to 3 wait states | 1 wait state to 7 wait states |

| Recovery Cycle             | Not available                  | Insertable                    |

| Page Mode Control Function | Not available                  | Available (ROMless version)   |

#### Table 4.3Differences in Bus Associated SFR

| Symbol                           | Address |                                  |     | Differ       | ences                          |

|----------------------------------|---------|----------------------------------|-----|--------------|--------------------------------|

| Symbol                           | M16C/80 | M32C/8B                          | Bit | M16C/80      | M32C/8B                        |

| WCR                              | 0008h   | -                                | -   | Only M16C/80 | -                              |

| EWCR0<br>EWCR1<br>EWCR2<br>EWCR3 | _       | 0048h<br>0049h<br>004Ah<br>004Bh | _   | _            | Only M32C/8B                   |

| PWCR0                            | -       | 004Ch                            | _   | _            | Only M32C/8B (ROMless version) |

| PWCR1                            | -       | 004Dh                            | _   | -            | Only M32C/8B (ROMless version) |

# 4.3 Differences in Clock

Table 4.4 lists the differences in clock and Table 4.5 lists the differences in clock associated SFR.

#### Table 4.4Differences in Clock

| Item                                      | M16C/80                                  | M32C/8B                                                                                       |

|-------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|

| Clock Generation Circuits                 | 2 circuits:<br>•Main clock<br>•Sub clock | 4 circuits:<br>•Main clock<br>•Sub clock<br>•On-chip oscillator<br>•PLL frequency synthesizer |

| Maximum Frequency of the Main<br>Clock    | 20 MHz                                   | 16 MHz                                                                                        |

| Oscillation Stop Detection                | Not available                            | Available                                                                                     |

| XCIN-XCOUT Drive Capability<br>Select Bit | Selectable                               | Not available                                                                                 |

| System Clock Protect Function             | Not available                            | Available                                                                                     |

| Flash Memory Low-speed Access             | Not available                            | Available (flash memory version)                                                              |

| Main Voltage Regulator Stop<br>Function   | Not available                            | Available                                                                                     |

### Table 4.5 Differences in Clock Associated SFR

| Symbol | Add     | ress    | Bit | Differ                                                       | rences                                                                                                     |

|--------|---------|---------|-----|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Symbol | M16C/80 | M32C/8B | DIL | M16C/80                                                      | M32C/8B                                                                                                    |

| CM0    | 0006h   |         | 7   | System clock select bit<br>0: XIN, XOUT<br>1: XCIN, XOUT     | CPU clock select bit 0<br>0: Clock selected by the CM21 bit<br>divided by the MCD register<br>1: Sub clock |

| CM1    | 0007h   |         | 5   | XCIN-XCOUT drive capacity select<br>bit<br>0: LOW<br>1: HIGH | Reserved bit<br>Set to 1                                                                                   |

|        |         |         | 7   | Reserved bit                                                 | CPU clock select bit 1<br>0: Main clock<br>1: PLL clock                                                    |

| CM2    | -       | 000Dh   | _   | -                                                            | Only M32C/8B                                                                                               |

| PLC0   | -       | 0026h   | _   | -                                                            | Only M32C/8B                                                                                               |

| PM2    | -       | 0013h   | _   | -                                                            | Only M32C/8B                                                                                               |

| TCSPR  | -       | 035Fh   | _   | -                                                            | Only M32C/8B                                                                                               |

| FMR4   | -       | 0059h   | -   | -                                                            | Only M32C/8B<br>(flash memory version)                                                                     |

| VRCR   | -       | 001Fh   | -   | -                                                            | Only M32C/8B                                                                                               |

# 4.4 Differences in Protection

Table 4.6 lists the differences in protection associated SFR.

| Symbol | Add     | Address |     | Differ                                            | ences                                                            |

|--------|---------|---------|-----|---------------------------------------------------|------------------------------------------------------------------|

| Symbol | M16C/80 | M32C/8B | Bit | M16C/80                                           | M32C/8B                                                          |

| PRCR   | 000Ah   |         | 0   | Writing to registers CM0, CM1 and MCD is enabled. | Writing to registers CM0, CM1, CM2, MCD, and PLC0 is enabled.    |

|        |         |         | 1   | Writing to registers PM0 and PM1 is enabled.      | Writing to registers PM0, PM1, PM2, INVC0, and INVC1 is enabled. |

|        |         |         | 3   | No register bit                                   | Writing to registers DVCR, LVDC, and VRCR is enabled.            |

#### Table 4.6 Differences in Protection Associated SFR

# 4.5 Differences in Interrupt

Table 4.7 lists the differences in interrupt, Table 4.8 lists the differences in interrupt vector and Table 4.9 lists the differences in interrupt associated SFR.

| Table 4.7 | Differences in Interrupt |

|-----------|--------------------------|

|-----------|--------------------------|

| Item                    | M16C/80                                                                       | M32C/8B                                                                                                                                                                               |

|-------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special Interrupt       | Reset<br>NMI<br>Watchdog timer<br>Single step <sup>(1)</sup><br>Address match | Reset         NMI         Watchdog timer         Single step <sup>(1)</sup> Address match         Oscillation stop detection         Voltage monitor         DMACII transfer complete |

| Address Match Interrupt | 4 addresses                                                                   | 8 addresses                                                                                                                                                                           |

Note:

1. Do not use these interrupts. They are for use with development tool only.

| Table 4.8 | Differences in Interrupt Vector |

|-----------|---------------------------------|

|-----------|---------------------------------|

| Software Interrupt<br>Number | Vector Table Address        | M16C/80            | M32C/8B                                 |

|------------------------------|-----------------------------|--------------------|-----------------------------------------|

| 17                           | +68 to +71 (0044h to 0047h) | UART0 transmission | UART0 transmission, NACK <sup>(1)</sup> |

| 18                           | +72 to +75 (0048h to 004Bh) | UART0 reception    | UART0 reception, ACK <sup>(1)</sup>     |

| 19                           | +76 to +79 (004Ch to 004Fh) | UART1 transmission | UART1 transmission, NACK <sup>(1)</sup> |

| 20                           | +80 to +83 (0050h to 0053h) | UART1 reception    | UART1 reception, ACK <sup>(1)</sup>     |

Note:

1. In I<sup>2</sup>C mode, NACK, ACK or start/stop condition detection can be the interrupt sources.

| Queshal         | Add     | lress             | Dit | Differences                                               |                                                                                                                                                                                                                                              |

|-----------------|---------|-------------------|-----|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | M16C/80 | M32C/8B           | Bit | M16C/80                                                   | M32C/8B                                                                                                                                                                                                                                      |

| BCN0IC          | -       | 0071h             | _   | -                                                         | Only M32C/8B                                                                                                                                                                                                                                 |

| BCN1IC          | -       | 0091h             | _   | -                                                         | Only M32C/8B                                                                                                                                                                                                                                 |

| ADIC<br>(AD0IC) | 0073h   |                   | -   | Symbol is changed from ADIC (M16C/80) to AD0IC (M32C/8B). |                                                                                                                                                                                                                                              |

| RLVL            | 009Fh   |                   | 5   | No register bit                                           | <ul> <li>DMACII select bit</li> <li>0: Interrupt priority level 7 is used for<br/>interrupt</li> <li>1: Interrupt priority level 7 is used for<br/>DMACII transfer</li> </ul>                                                                |

| IFSR            | 031Fh   |                   | 6   | No register bits                                          | UART0, UART3 interrupt source select bit<br>0: UART3 bus conflict, start condition<br>detection, stop condition detection<br>1: UART0 bus conflict, start condition<br>detection, stop condition detection                                   |

|                 |         |                   | 7   |                                                           | <ul> <li>UART1, UART4 interrupt source select bit</li> <li>0: UART4 bus conflict, start condition<br/>detection, stop condition detection</li> <li>1: UART1 bus conflict, start condition<br/>detection, stop condition detection</li> </ul> |

| RMAD4           | -       | 0028h to<br>002Ah | -   | -                                                         | Only M32C/8B                                                                                                                                                                                                                                 |

| RMAD5           | -       | 002Ch to<br>002Eh | -   | -                                                         | Only M32C/8B                                                                                                                                                                                                                                 |

| RMAD6           | -       | 0038h to<br>003Ah | -   | -                                                         | Only M32C/8B                                                                                                                                                                                                                                 |

| RMAD7           | -       | 003Ch to<br>003Eh | -   | -                                                         | Only M32C/8B                                                                                                                                                                                                                                 |

| AIER            | 0009h   |                   | 4   | No register bits                                          | Address match interrupt 4 enable bit<br>0: Interrupt disabled<br>1: Interrupt enabled                                                                                                                                                        |

|                 |         |                   | 5   |                                                           | Address match interrupt 5 enable bit<br>0: Interrupt disabled<br>1: Interrupt enabled                                                                                                                                                        |

|                 |         |                   | 6   |                                                           | Address match interrupt 6 enable bit<br>0: Interrupt disabled<br>1: Interrupt enabled                                                                                                                                                        |

|                 |         |                   | 7   |                                                           | Address match interrupt 7 enable bit<br>0: Interrupt disabled<br>1: Interrupt enabled                                                                                                                                                        |

# Table 4.9 Differences in Interrupt Associated SFR

#### 4.6 Differences in Watchdog Timer

Table 4.10 lists the differences in watchdog timer and Table 4.11 lists the differences in watchdog timer associated SFR.

#### Table 4.10 Differences in Watchdog Timer

| Item         | M16C/80                       | M32C/8B                                                                                                            |

|--------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Count Source | •BCLK (main clock, sub clock) | <ul> <li>CPU clock (main clock, sub clock, PLL frequency synthesizer)</li> <li>On-chip oscillator clock</li> </ul> |

#### Table 4.11 Differences in Watchdog Timer Associated SFR

| Symbol | Add     | ress    | Bit | Differences |                                                                                                                                                                                           | Differences |  |

|--------|---------|---------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| Symbol | M16C/80 | M32C/8B | DIL | M16C/80     | M32C/8B                                                                                                                                                                                   |             |  |

| PM2    | _       | 0013h   | 2   | _           | <ul> <li>WDT count source protect bit</li> <li>0: CPU clock as count source for the watchdog timer</li> <li>1: On-chip oscillator clock as count source for the watchdog timer</li> </ul> |             |  |

#### 4.7 Differences in DMAC

Table 4.12 lists the differences in DMAC associated SFR.

| Symbol            | Address    |         | Bit    | Differ                                                                                        | ences                                                                                                                                                      |

|-------------------|------------|---------|--------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | M16C/80    | M32C/8B | ы      | M16C/80                                                                                       | M32C/8B                                                                                                                                                    |

| DM0SL to<br>DM3SL | 0378h to 0 | 37Bh    | 4 to 0 | DMA request source select bits <sup>(1)</sup><br>01111: UART0 receive<br>10001: UART1 receive | DMA request source select bits<br>01111: UART0 receive interrupt or<br>ACK interrupt request<br>10001: UART1 receive interrupt or<br>ACK interrupt request |

Note:

1. "DMA request cause select bit" is used in M16C/80, and this word is changed to "DMA request source select bit" in M32C/8B.

#### 4.8 Differences in Timer A

Table 4.13 lists the differences in timer A and Table 4.14 lists the differences in timer A associated SFR.

#### Table 4.13Differences in Timer A

| Item         | M16C/80           | M32C/8B                           |

|--------------|-------------------|-----------------------------------|

| Count Source | f1, f8, f32, fC32 | f1, f8, f2n <sup>(1)</sup> , fC32 |

Note:

1. Bits CNT3 to CNT0 in the TCSPR register select no division (n = 0) or divide-by-2n (n = 1 to 15).

#### Table 4.14 Differences in Timer A Associated SFR

| Symbol                | Address    |         | Bit    | Differences                                                             |                                                                                        |  |

|-----------------------|------------|---------|--------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| Symbol                | M16C/80    | M32C/8B | DIL    | M16C/80                                                                 | M32C/8B                                                                                |  |

| TAiMR<br>(i = 0 to 4) | 0356h to 0 | 35Ah    | 7 to 6 | Count source select bits<br>0 0: f1<br>0 1: f8<br>1 0: f32<br>1 1: fC32 | Count source select bits<br>0 0: f1<br>0 1: f8<br>1 0: f2n <sup>(1)</sup><br>1 1: fC32 |  |

| TCSPR                 | -          | 035Fh   | -      | _                                                                       | Only M32C/8B                                                                           |  |

Note:

Bits CNT3 to CNT0 in the TCSPR register select no division (n = 0) or divide-by-2n (n = 1 to 15). To select f2n, set the CST bit in the TCSPR register to 1 before setting bits TCK1 and TCK0 to 10b.

#### 4.9 Differences in Timer B

Table 4.15 lists the differences in timer B and Table 4.16 lists the differences in timer B associated SFR.

#### Table 4.15Differences in Timer B

| Item         | M16C/80           | M32C/8B                           |

|--------------|-------------------|-----------------------------------|

| Count Source | f1, f8, f32, fC32 | f1, f8, f2n <sup>(1)</sup> , fC32 |

Note:

1. Bits CNT3 to CNT0 in the TCSPR register select no division (n = 0) or divide-by-2n (n = 1 to 15).

Table 4.16 Differences in Timer B Associated SFR

| Symbol                | Address                  |         | Bit    | Differ                                                                  | ences                                                                                  |

|-----------------------|--------------------------|---------|--------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Symbol                | M16C/80                  | M32C/8B | DIL    | M16C/80                                                                 | M32C/8B                                                                                |

| TBiMR<br>(i = 0 to 5) | 035Bh to 0<br>031Bh to 0 | ,       | 7 to 6 | Count source select bits<br>0 0: f1<br>0 1: f8<br>1 0: f32<br>1 1: fC32 | Count source select bits<br>0 0: f1<br>0 1: f8<br>1 0: f2n <sup>(1)</sup><br>1 1: fC32 |

| TCSPR                 | -                        | 035Fh   | -      | _                                                                       | Only M32C/8B                                                                           |

Notes:

Bits CNT3 to CNT0 in the TCSPR register select no division (n = 0) or divide-by-2n (n = 1 to 15). To select f2n, set the CST bit in the TCSPR register to 1 before setting bits TCK1 and TCK0 to 10b.

# 4.10 Differences in Three-Phase Motor Control Timer Function

Table 4.17 lists the differences in three-phase motor control timer function and Table 4.18 lists the differences in three-phase motor control timer function associated SFR.

| Table 4.17 Differences in Three-Phase Motor Control Timer Function |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

| Item              | M16C/80              | M32C/8B    |

|-------------------|----------------------|------------|

| Count Source      | f1, f8, f32, fC32 f1 |            |

| Dead Time         | Available            | Selectable |

| Dead Time Trigger | Fixed                | Selectable |

| Table 4.18 | Differences in Three-Phase Motor Control Timer Function Associated SFR |

|------------|------------------------------------------------------------------------|

|            |                                                                        |

| Sumbol                  | Add                     | Address |        | Differences                                                             |                                                                                                                                                                                                               |

|-------------------------|-------------------------|---------|--------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                  | M16C/80                 | M32C/8B | Bit    | M16C/80                                                                 | M32C/8B                                                                                                                                                                                                       |

| INVC1                   | 0309h                   |         | 5      | No register bits                                                        | Dead time disable bit<br>0: Dead time enabled<br>1: Dead time disabled                                                                                                                                        |

|                         |                         |         | 6      |                                                                         | <ul> <li>Dead time timer trigger select bit</li> <li>0: Falling edge of one-shot pulse of timer (A4, A1 and A2)</li> <li>1: Rising edge of the three-phase output shift register (U-, V-, W-phase)</li> </ul> |

|                         |                         |         | 7      |                                                                         | Reserved bit                                                                                                                                                                                                  |

| TA1MR<br>TA2MR<br>TA4MR | 0357h<br>0358h<br>035Ah |         | 7 to 6 | Count source select bits<br>0 0: f1<br>0 1: f8<br>1 0: f32<br>1 1: fC32 | Count source select bits<br>Set to 00b (f1) to use the three-<br>phase motor control timer function                                                                                                           |

| TB2MR                   | 035Dh                   |         | 7 to 6 | Count source select bits<br>0 0: f1<br>0 1: f8<br>1 0: f32<br>1 1: fC32 | Count source select bits<br>Set to 00b (f1) to use the three-<br>phase motor control timer function                                                                                                           |

#### 4.11 Differences in Serial Interface

Table 4.19 lists the differences in serial interface and Table 4.20 to Table 4.24 list the differences in serial interface associated SFR.

| Item                                                                                     | M16C/80                                                                                                                                                                                                                                       | M32C/8B                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Modes                                                                          | UART0, UART1<br>•Clock synchronous mode<br>•Clock asynchronous mode (UART<br>mode)<br>UART2 to UART4<br>•Clock synchronous mode<br>•Clock asynchronous mode<br>•I2C-bus<br>•IEBus <sup>(1)</sup> (optional <sup>(2)</sup> )<br>•SIM interface | UART0 to UART4<br>•Clock synchronous mode<br>•Clock asynchronous mode (UART<br>mode)<br>•I <sup>2</sup> C-bus<br>•Special mode 2<br>•GCI mode<br>•SIM mode<br>•IEBus <sup>(1)</sup> (optional <sup>(2)</sup> )                                                                                                                                                                          |

| Count Source                                                                             | f1, f8, f32                                                                                                                                                                                                                                   | f1, f8, f2n<br>(n = 0 to 15, no division only where $n = 0$ )                                                                                                                                                                                                                                                                                                                           |

| LSB First or MSB First                                                                   | <ul> <li>•UART0, UART1</li> <li>Selectable in clock synchronous mode</li> <li>•UART2 to UART4</li> <li>Selectable in clock synchronous mode or UART mode</li> </ul>                                                                           | •UART0 to UART4<br>Selectable in clock synchronous mode<br>or UART mode                                                                                                                                                                                                                                                                                                                 |

| Transfer Clock Output from<br>Multiple Pins Selection                                    | 1 channel (UART1)                                                                                                                                                                                                                             | Not available                                                                                                                                                                                                                                                                                                                                                                           |

| Separate CTS/RTS Pins                                                                    | 1 channel (UART0)                                                                                                                                                                                                                             | Not available                                                                                                                                                                                                                                                                                                                                                                           |

| Serial Data Logic Inverse                                                                | 3 channels (UART2 to UART4)                                                                                                                                                                                                                   | 5 channels (UART0 to UART4)                                                                                                                                                                                                                                                                                                                                                             |

| Sleep Mode Selection                                                                     | 2 channels (UART0, UART1)                                                                                                                                                                                                                     | Not available                                                                                                                                                                                                                                                                                                                                                                           |

| TXD and RXD I/O Polarity Inverse                                                         | 3 channels (UART2 to UART4)                                                                                                                                                                                                                   | 5 channels (UART0 to UART4)                                                                                                                                                                                                                                                                                                                                                             |

| Bus Conflict Detection                                                                   | 3 channels (UART2 to UART4)                                                                                                                                                                                                                   | 5 channels (UART0 to UART4)                                                                                                                                                                                                                                                                                                                                                             |

| Occurrence Timing of Overrun<br>Error                                                    | •Clock synchronous/UART mode<br>The overrun error occurs when the next<br>data is ready before reading the UiRB<br>register (i = 0 to 4).                                                                                                     | <ul> <li>Clock synchronous mode<br/>The overrun error occurs when the 7th<br/>bit of the next data is received before<br/>reading the UiRB register.</li> <li>UART mode<br/>Overrun error occurs when the<br/>preceding bit of the final stop bit of the<br/>next data (the first stop bit when<br/>selecting 2 stop bits) is received before<br/>reading the UiRB register.</li> </ul> |

| Timing of "L" Signal Output from<br>RTSi Pin in UART Mode                                | At the completion of reception operation                                                                                                                                                                                                      | At the completion of reading receive<br>buffer                                                                                                                                                                                                                                                                                                                                          |

| Automatic Generation of Start<br>Condition or Stop Condition in I <sup>2</sup> C<br>Mode | Not available                                                                                                                                                                                                                                 | Available                                                                                                                                                                                                                                                                                                                                                                               |

| Count Source of SDAi Delay                                                               | 1/f(XIN)                                                                                                                                                                                                                                      | UiBRG register count source                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                          |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 4.19 | Differences in Serial Interface |

|------------|---------------------------------|

|------------|---------------------------------|

Notes:

- 1. IEBus is a registered trademark of NEC Electronics Corporation.

- 2. Please contact a Renesas sales office for optional features.

| Symbol                     | Address                 |                   | Bit    | Differences                                                                                                                                         |                                                                                                                     |  |

|----------------------------|-------------------------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Symbol                     | M16C/80                 | M32C/8B           | DIL    | M16C/80                                                                                                                                             | M32C/8B                                                                                                             |  |

| UCON                       | 0370h                   | -                 | _      | Only M16C/80                                                                                                                                        | _                                                                                                                   |  |

| U0TB                       | 0362h to<br>0363h       | 036Ah to<br>036Bh | _      | Different address                                                                                                                                   |                                                                                                                     |  |

| U1TB                       | 036Ah to<br>036Bh       | 02EAh to<br>02EBh | _      | Different address                                                                                                                                   |                                                                                                                     |  |

| U0RB                       | 0366h to                | 036Eh to          | -      | Different address                                                                                                                                   |                                                                                                                     |  |

|                            | 0367h                   | 036Fh             | 11     | No register bit                                                                                                                                     | Arbitration lost detect flag<br>0: Not detected (won)<br>1: Detected (lost)                                         |  |

| U1RB                       | 036Eh to                | 02EEh to          | -      | Different address                                                                                                                                   |                                                                                                                     |  |

|                            | 036Fh                   | 02EFh             | 11     | No register bit                                                                                                                                     | Arbitration lost detect flag<br>0: Not detected (won)<br>1: Detected (lost)                                         |  |

| U0MR                       | 0360h                   | 0368h             | -      | Different address                                                                                                                                   |                                                                                                                     |  |

| U1MR                       | MR 0368h 02             | 02E8h             | 2 to 0 | Serial I/O mode select bits<br>0 1 0: Do not set this value.                                                                                        | Serial interface mode select bits<br>0 1 0: I <sup>2</sup> C mode                                                   |  |

|                            |                         |                   | 7      | Sleep select bit<br>•(In clock synchronous serial I/O<br>mode)<br>Set to 0<br>•(In UART mode)<br>0: Sleep mode deselected<br>1: Sleep mode selected | TXD, RXD input/output polarity<br>switch bit<br>0: Not inverted<br>1: Inverted                                      |  |