# **APPLICATION NOTE**

TW2880P-BC2-GR Chip Application Note

AN1659 Rev. 2.00 January 26, 2012

# **Table of Contents**

| Section 1: Clockgen and PLL                                      | 11 |

|------------------------------------------------------------------|----|

| Introduction                                                     | 11 |

| SCLK                                                             | 11 |

| Clock Listing                                                    | 12 |

| Register Setting for SPLL                                        |    |

| MCLK                                                             | 13 |

| Introduction                                                     |    |

| Master Clock Calculation                                         |    |

| Clock Relationship                                               |    |

| VCLK                                                             | 16 |

| Popular Main Display Clocks                                      | 17 |

| Dual Monitor Setting                                             |    |

| Using SCLK Clock Group For Dual Monitor Clock                    |    |

| Example                                                          | 19 |

| MCLK registers                                                   |    |

| VCLK registers                                                   |    |

| VCLK registers                                                   |    |

| Techwell Terminal Tool Setting                                   |    |

| Layout of the CFG File                                           |    |

| Explanation                                                      |    |

| Section 2: PCB Layout Guide                                      | 23 |

| Introduction                                                     | 23 |

| Placement Suggestions                                            | 23 |

| Signal Integrity                                                 | 23 |

| Power Regulator and Noise Filtering                              |    |

| Power Distribution                                               |    |

| TW2880 Power Rails                                               |    |

| SDRAM                                                            |    |

| Introduction                                                     |    |

| Termination Resistors                                            |    |

| Equi-Length Line Rule                                            |    |

| DAC                                                              | 28 |

| Introduction                                                     |    |

| Power Supply                                                     |    |

| Proper Termination                                               |    |

| Connection Example                                               |    |

| PCB Layout Considerations                                        |    |

| Recommended Routing/Layout RulesRecommended Routing/Layout Rules | 29 |

| HDMI                                                                                 | 30 |

|--------------------------------------------------------------------------------------|----|

| General Description                                                                  | 30 |

| Signal Integrity                                                                     |    |

| Impedance Control                                                                    |    |

| 45°Bends                                                                             | 32 |

| Skew Control                                                                         | 33 |

| Symmetrical Design                                                                   | 34 |

| Power and Ground                                                                     | 35 |

| Power and GND Planes                                                                 |    |

| Plane Isolation                                                                      |    |

| Recommendation of Layer Structure                                                    |    |

| Recommendation of power supply pin connections                                       |    |

| Clocking Design                                                                      |    |

| Requirement of Jitter                                                                |    |

| Additional Parts (for ESD and EMI)                                                   |    |

| ESD Protector                                                                        |    |

| EMI filter                                                                           |    |

| Check List                                                                           |    |

| Capacitance Reduced PADs                                                             |    |

| Section 3: PB Window and Channel ID Decoding                                         | 43 |

| Introduction                                                                         | 43 |

| Features                                                                             | 43 |

| Limitations                                                                          |    |

| Normal Mode Registers Setting                                                        |    |

| Auto Mode Registers Setting                                                          |    |

|                                                                                      |    |

| Register DescriptionRegister Setting Sequence                                        |    |

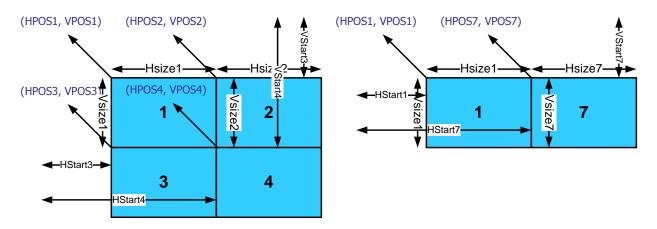

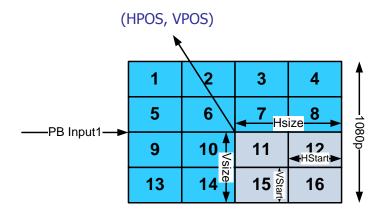

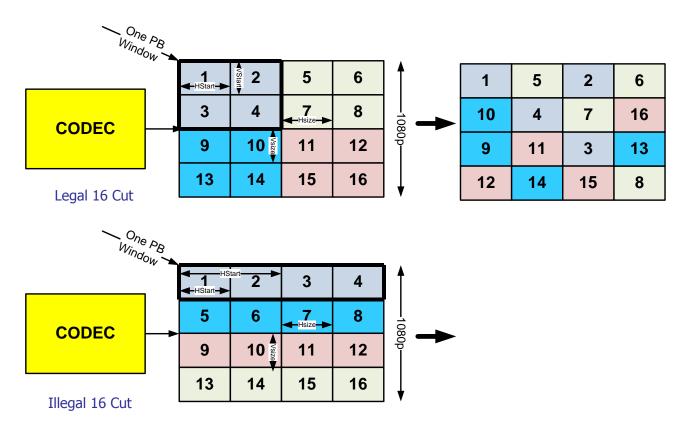

| Channel Cutting Using Hstart and Vstart                                              |    |

| Automatic CHID Insertion                                                             |    |

| Channel Ignore Function                                                              |    |

|                                                                                      |    |

| Some Setting Examples                                                                |    |

| Channel Setting Example in Auto Mode                                                 |    |

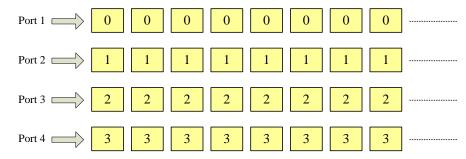

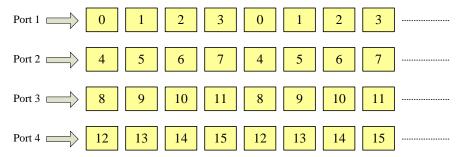

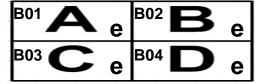

| One port has one channel                                                             |    |

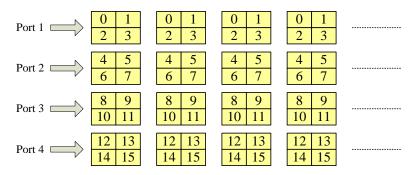

| One port has four channels, frame / field interleaved                                |    |

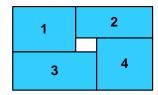

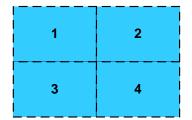

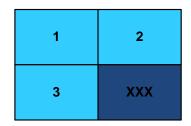

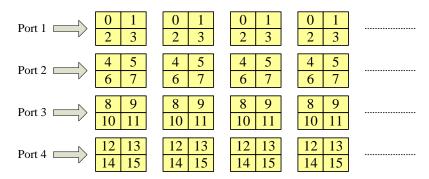

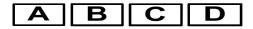

| One port has four channels, Quad mode                                                |    |

| One port has 16 channels, CIF mode                                                   |    |

| One port has 16 channels, Mixed mode                                                 |    |

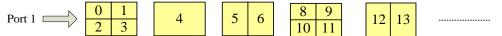

| One port has 13 channels, Mixed mode                                                 |    |

| Hstart and Vstart setting example One HD stream gets divided into 16 channel example |    |

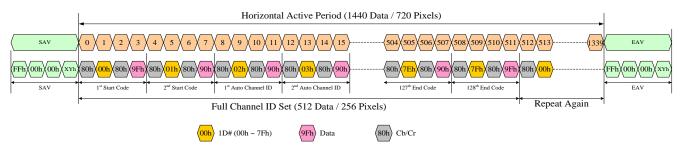

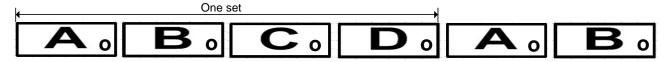

| Digital Channel ID in First Active Line                                              |    |

| ID Structure                                                                         |    |

| Register Setting                                                                     |    |

| Read Channel ID from Registers                                                       |    |

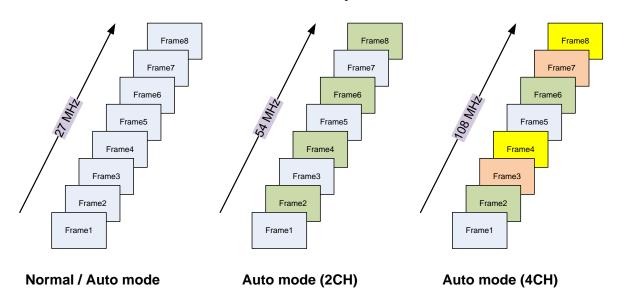

| Frame Interleaved Mode Setting                                                       |    |

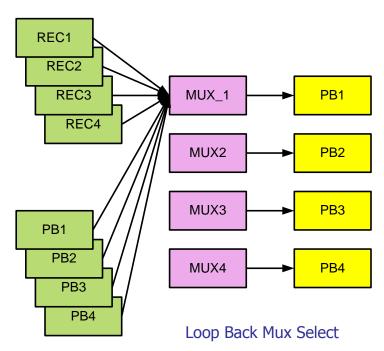

| PB Loop Back Control                                                                 |    |

| Automatic Channel ID Insertion                                                       |    |

| Repeat Cutting                                                                       |    |

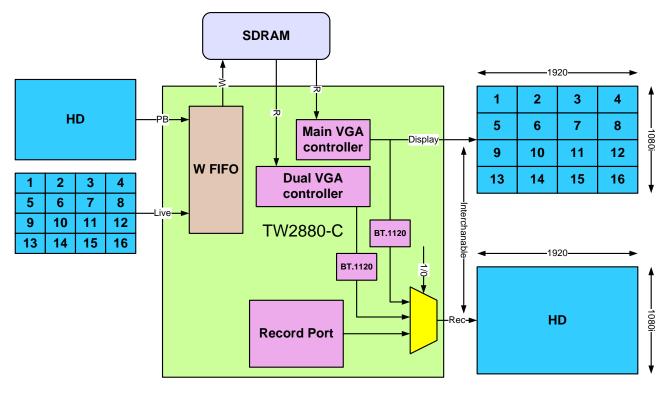

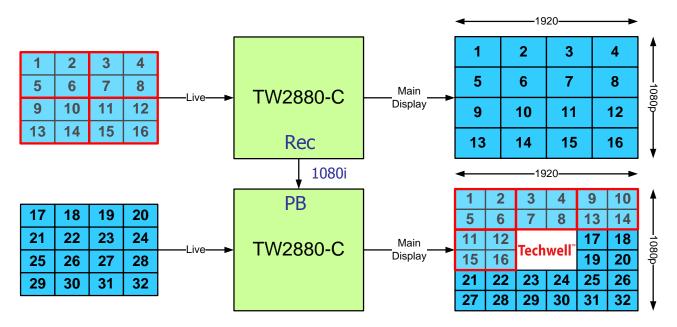

| Cascading Two TW2880Cs                                                               |    |

| _                                                                                    |    |

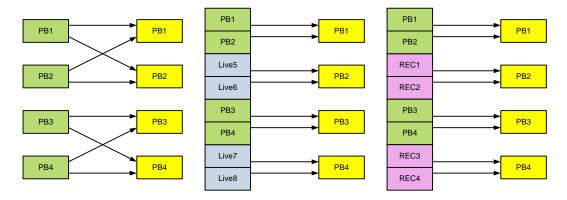

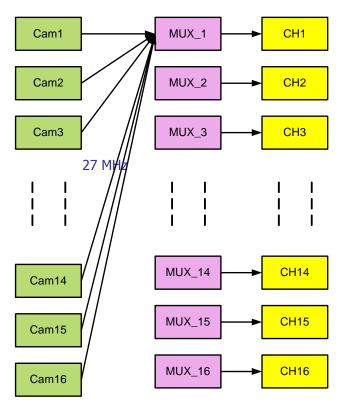

| Display Output Multiplexing                                                          |    |

| 32 Live Channel Example                                                              |    |

| Advanced Topics                                                                      |    |

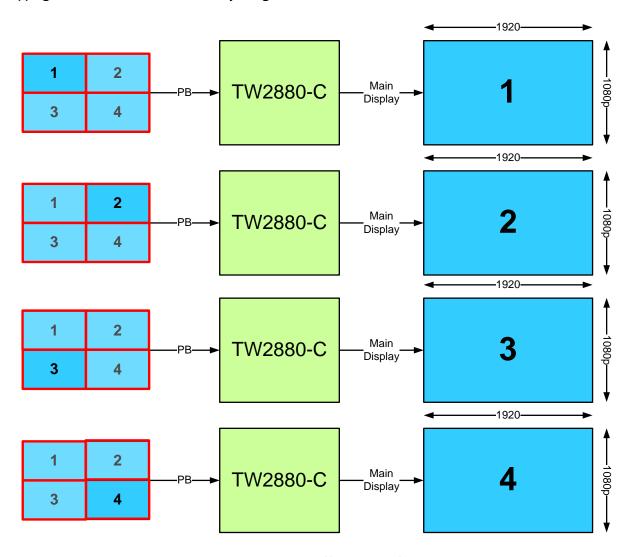

| TV Wall Example                                                                      |    |

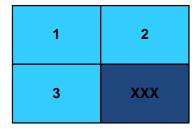

| Ignore Bit                                                                           | 62 |

| One Field Mode                                                                       | 63  |

|--------------------------------------------------------------------------------------|-----|

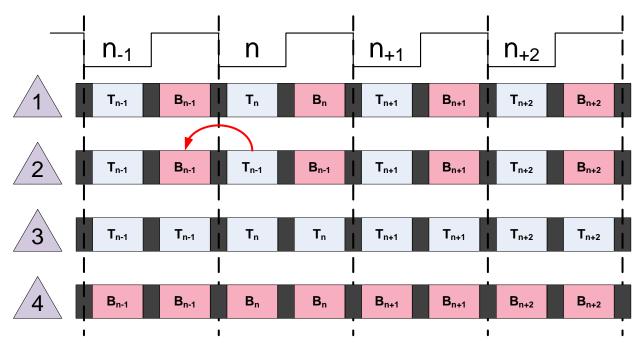

| Section 4: Recording and SPOT Unit                                                   | 64  |

| Overview                                                                             | 64  |

| Programming Model                                                                    | 64  |

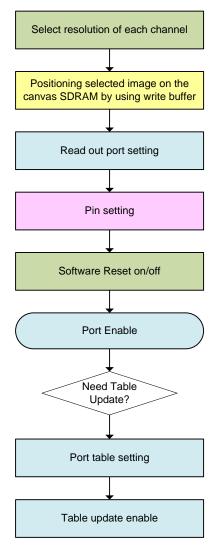

| Programming Flow                                                                     |     |

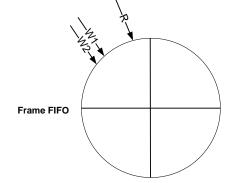

| Write Buffer Setting                                                                 | 69  |

| 256Mbit                                                                              | 69  |

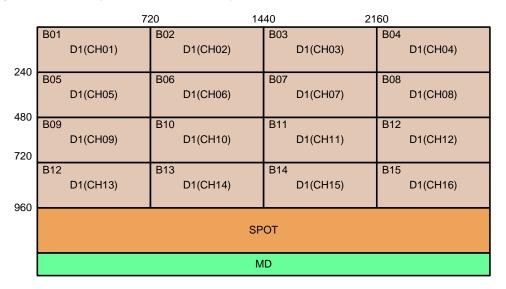

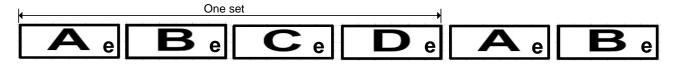

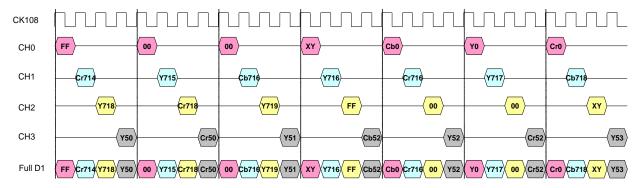

| Case 1: 16-D1, FLI and NTSC (Refer to Figure 20)                                     |     |

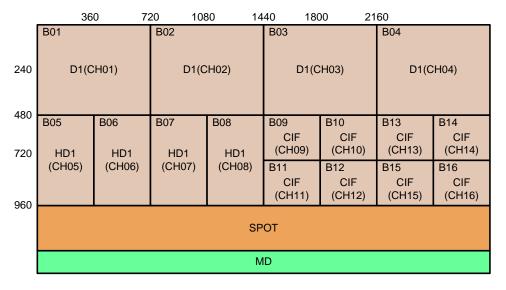

| Case 2: 16-D1, FMI and NTSC (Refer to Figure 21)                                     |     |

| 512Mbit                                                                              |     |

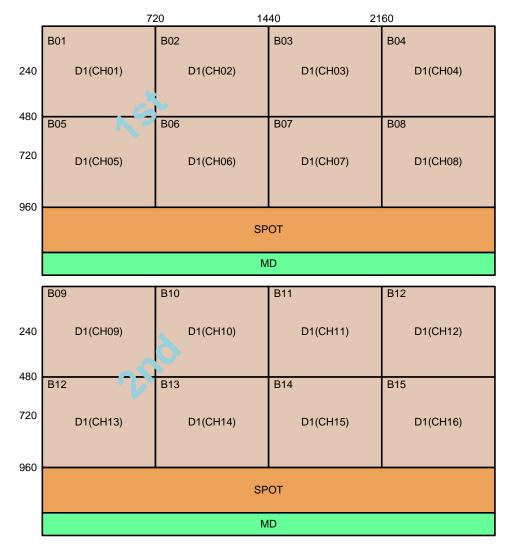

| Case 1: 16-D1, FMI and NTSC(Refer to Figure 22)                                      |     |

| SPOT Buffer                                                                          |     |

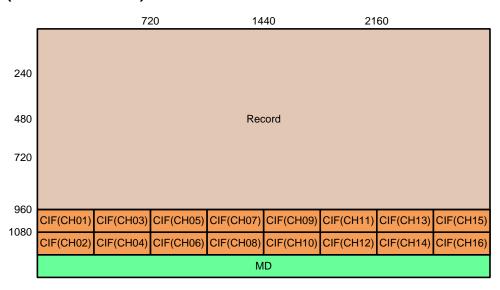

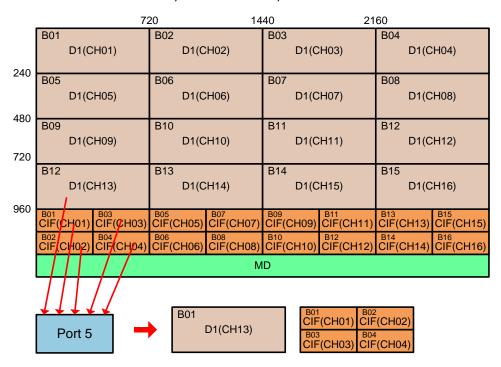

| Case 1: 16-CIF (Refer to Figure 23)                                                  |     |

| Case 2: Port 5 uses Record buffer 12, SPOT buffer 1, SPOT buffer 2 and SPOT buffer 3 |     |

| Read Port Setting                                                                    |     |

| Normal Port(Port 1 ~ Port 4)                                                         |     |

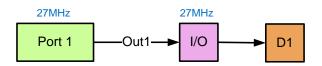

| Case 1: Port 1, D1, FMI and 27MHz (Refer to Figure 25)                               |     |

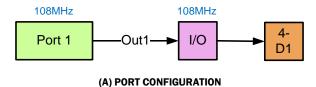

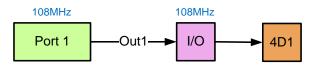

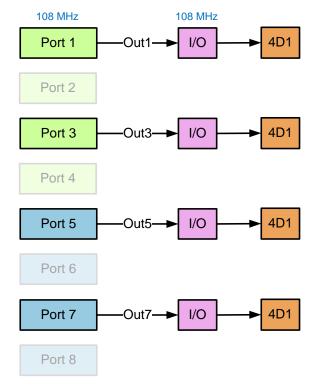

| Case 2: Port 1, 4-D1, FMI and 108MHz (Refer to Figure 26)                            |     |

| Case 3: Port 1, 4-D1, FLI and 108MHz (Refer to Figure 27)                            |     |

| Case 4: Port 1, 4D1 mode (Special), FLI and 108MHz (Refer to Figure 28)              |     |

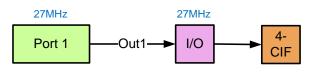

| Case 5: Port 1, 4-CIF and 27MHz (Refer to Figure 29)                                 |     |

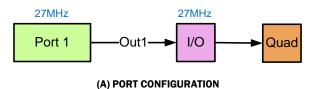

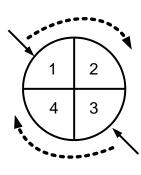

| Case 6: Port 1, Quad, FLI and 27MHz (Refer to Figure 30)                             |     |

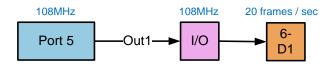

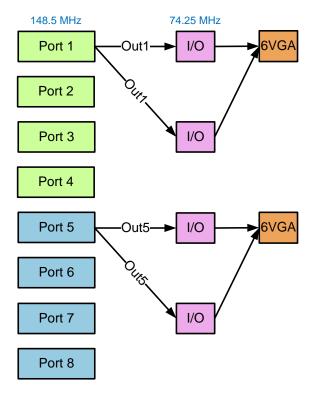

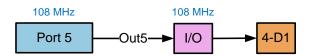

| Case 1: Port 5, 6-D1, FMI, 108MHz (Refer to Figure 31)                               |     |

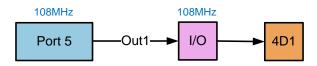

| Case 2: Port 5, 4D1 mode(Special), FLI and 108MHz (Refer to Figure 32)               |     |

| Case 3: Table live update                                                            |     |

| Output Pin Setting                                                                   |     |

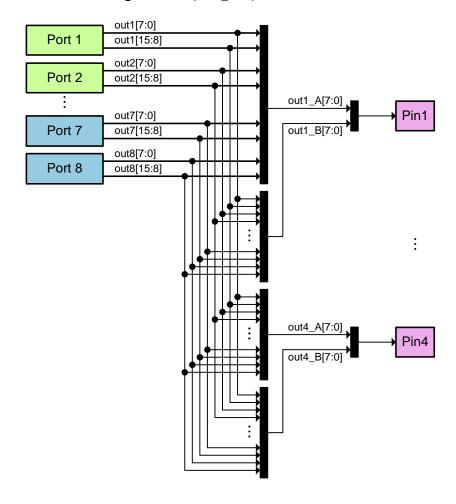

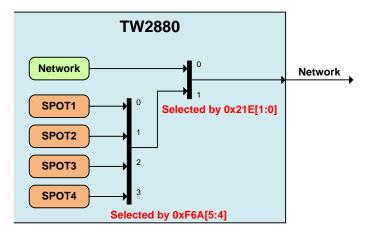

| Port Muxing                                                                          |     |

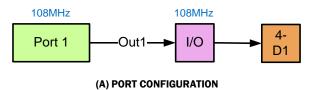

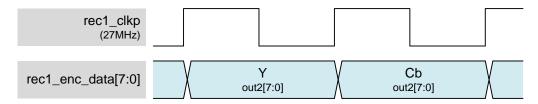

| Case 1: Output Pin 1, 8-bit, 1 codec (Refer to Figure 34)                            |     |

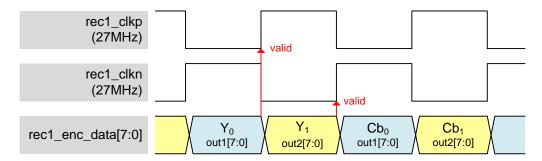

| Case 2: Output Pin 1, 8-bit, 2 codec (Refer to Figure 35)                            |     |

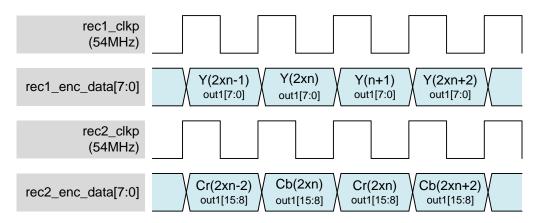

| Case 3: 16-bit, 1 codec, 54MHz (Refer to Figure 36)                                  |     |

| Output Clock Selection                                                               |     |

| Output Clock Phase Control                                                           |     |

| ETC                                                                                  | 87  |

| OSD                                                                                  |     |

| Privacy Window                                                                       |     |

| Freeze                                                                               |     |

| BT.1120                                                                              |     |

| SPOT Connection                                                                      | 89  |

| Frame Rate Control                                                                   | 89  |

| Programming Example                                                                  | 90  |

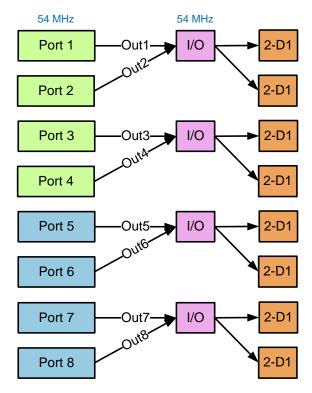

| Eight 2-D1, FLI                                                                      | 90  |

| Four 4D1, FMI                                                                        | 92  |

| 6VGA                                                                                 | 94  |

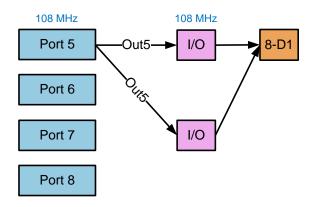

| 8-D1 and Two 4D1                                                                     |     |

| Field Switching Mode                                                                 |     |

| Case 1: 4-D1 and Field Switching Mode, Only Even Field out (Refer to Figure 45)      |     |

| Priority & Frame Rate Control                                                        |     |

| Using SPOT Buffer for Recording                                                      |     |

| Network Port                                                                         |     |

| PB Loopback Test                                                                     |     |

| Q & A                                                                                |     |

| Q001: What is difference between FLI mode and FMI mode in buffer control?            |     |

| Q002: Does TW2880 support progressive frame interleaved record output                | 102 |

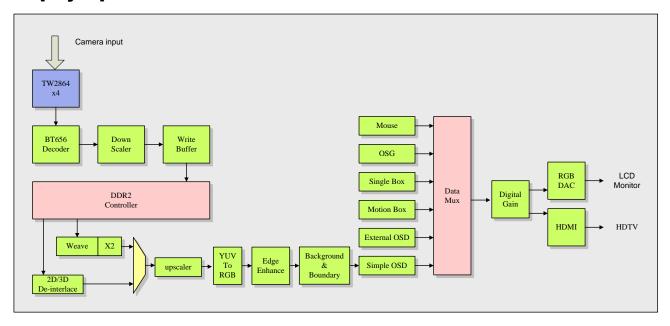

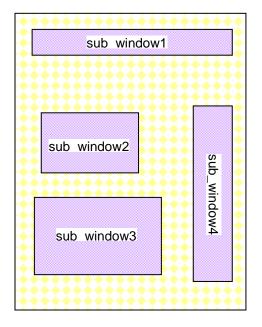

| Section 5: How to Setup a TW2880C-Based Display              | 103 |

|--------------------------------------------------------------|-----|

| Introduction                                                 | 103 |

| Input Arrangement                                            | 103 |

| Live input                                                   |     |

| Playback input                                               |     |

| Input and channel mapping                                    |     |

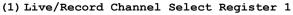

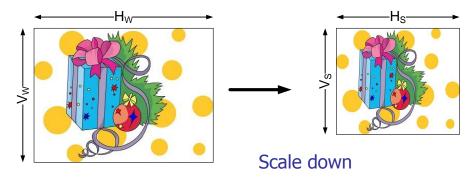

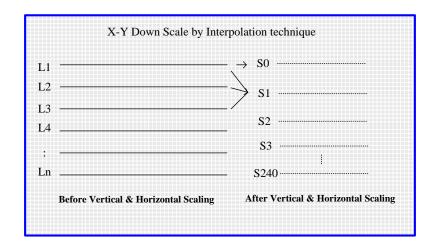

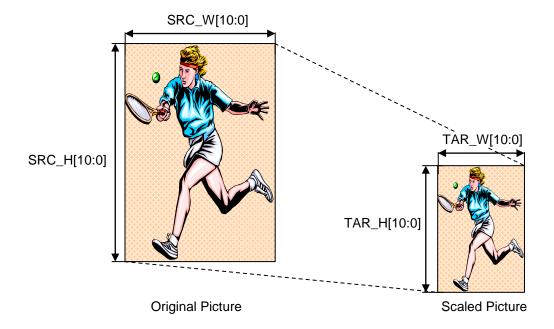

| Down scaler                                                  |     |

| Test pattern                                                 |     |

| Main Display                                                 |     |

| Introduction                                                 |     |

| Live and PB Window Register Arrangement                      |     |

| Window Write Process Protection                              |     |

| 33rd Window                                                  |     |

| Test Pattern                                                 |     |

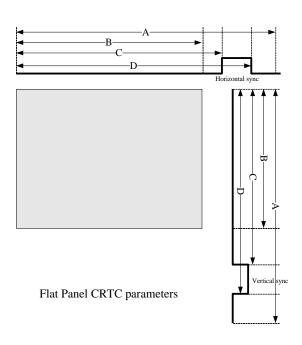

| CRTC Parameters                                              |     |

| Introduction                                                 |     |

| Horizotal synchronization and Refresh rate adjustment        |     |

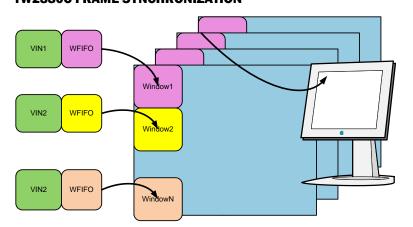

| TW2880C frame synchronization                                |     |

| Write buffer update and correction circuit (NEW for TW2880C) |     |

| 60Hz Display and correction table                            |     |

| PAL mode interpolation and correction                        |     |

| Correction in details                                        |     |

| Beat frequency                                               |     |

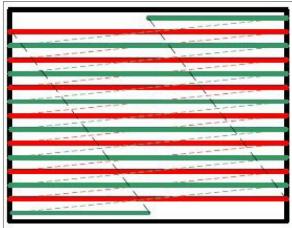

| Interlaced mode setting                                      |     |

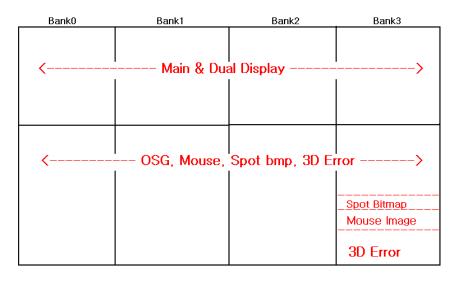

| Display Memory and Buffer Management                         |     |

| Display Pipe                                                 |     |

| De-interlacing Effect Select and Up scaler                   |     |

| 3D Mode Adress calculation                                   |     |

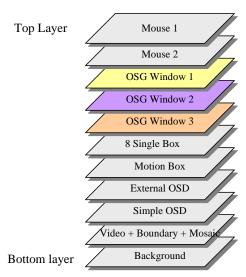

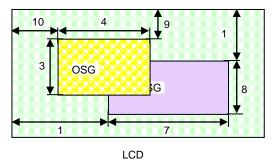

| Display Layers                                               |     |

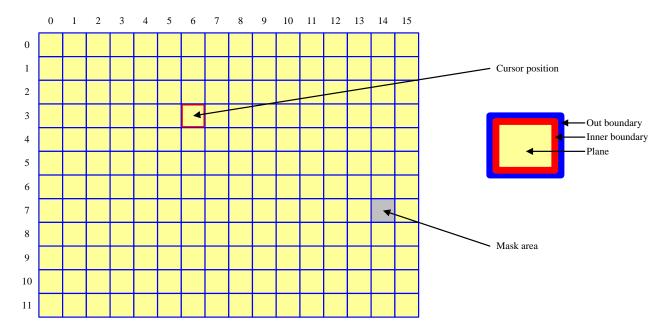

| Mouse Pointer                                                |     |

| Single Box                                                   |     |

| Motion Box                                                   |     |

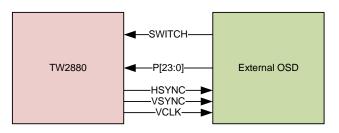

| External OSD                                                 |     |

| Privacy Windows                                              |     |

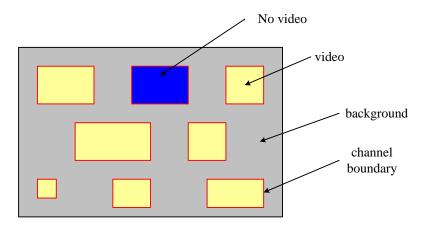

| Background and Channel Boundary                              |     |

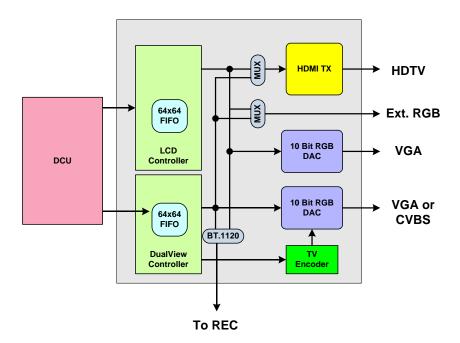

| Flexible Output                                              |     |

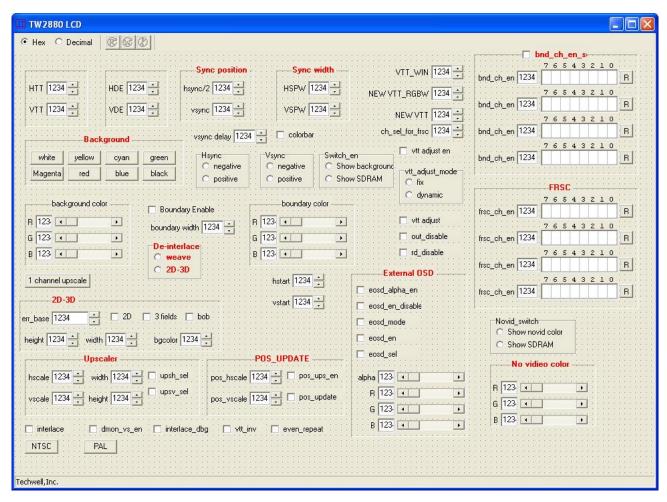

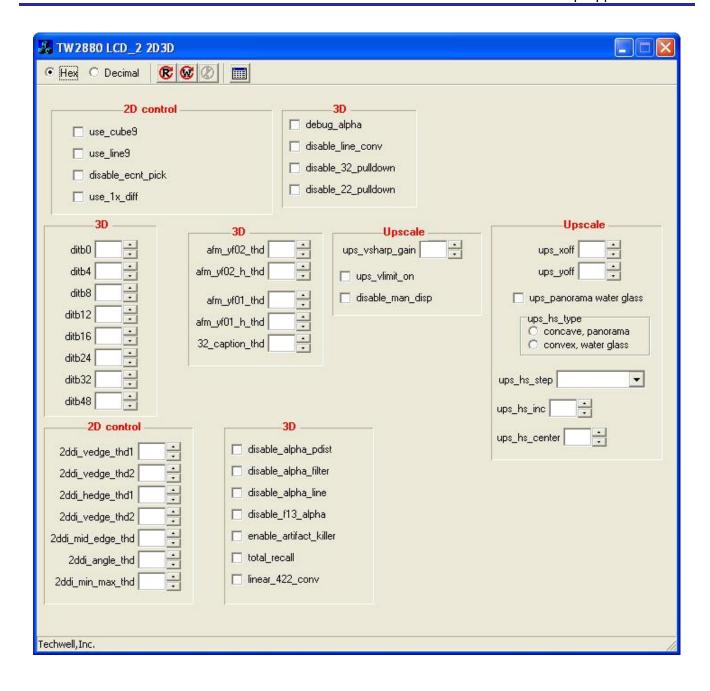

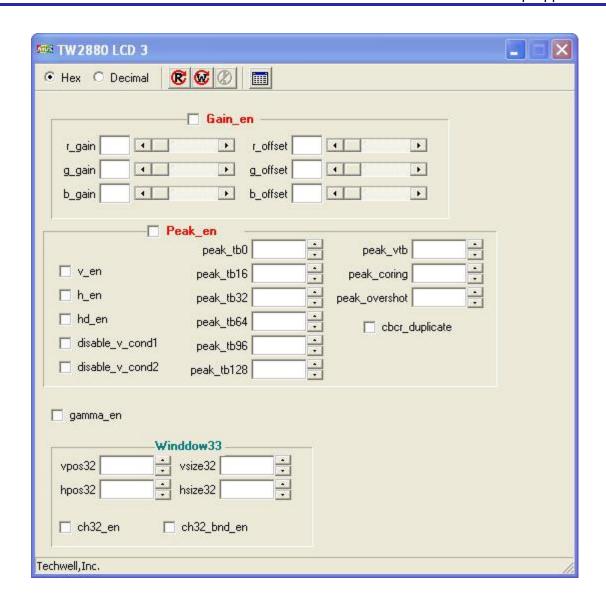

| Terminal Tool                                                | 123 |

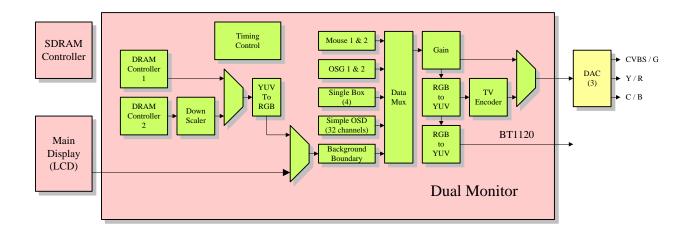

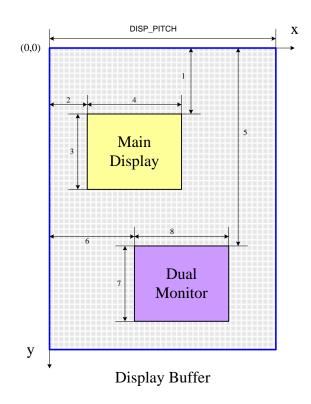

| Dual Monitor                                                 | 126 |

| Introduction                                                 |     |

| Features                                                     |     |

| Dual Monitor Controller Block Diagram                        |     |

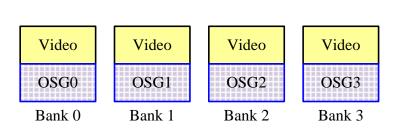

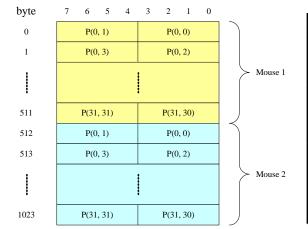

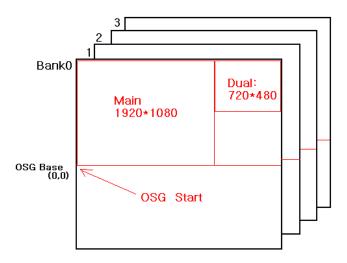

| Memory Diagram                                               |     |

| CRTC setting                                                 |     |

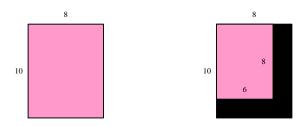

| Down Scalar                                                  |     |

| OSD Control                                                  |     |

| Font & Picture                                               |     |

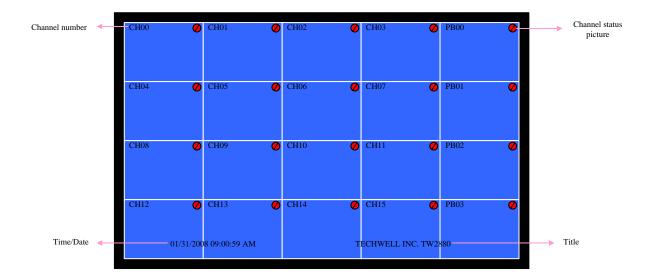

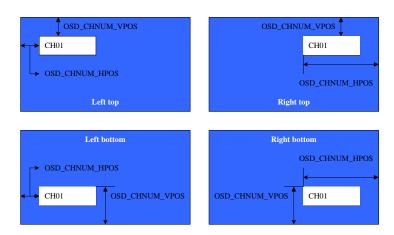

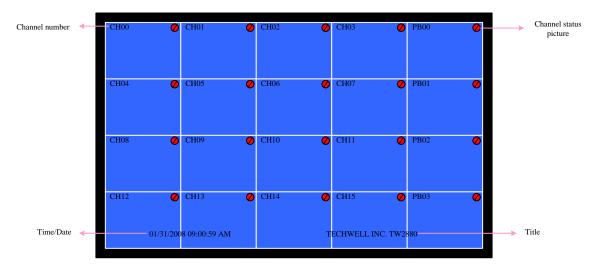

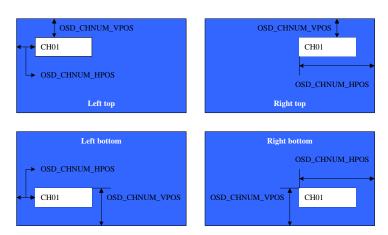

| Channel Number                                               |     |

| Date and Time                                                |     |

| Title                                                        |     |

| Display DRAM                                                 |     |

| TV Encoder                                                   |     |

| Mouse                                                        |     |

| OSG                                                          |     |

| Introduction                                                 |     |

| Features                                                     |     |

| Bitmap Buffer Display                                        |     |

| ·                                                            |     |

| Alpha Blending                                                                    |     |

|-----------------------------------------------------------------------------------|-----|

| Blinking                                                                          |     |

| Transparent                                                                       |     |

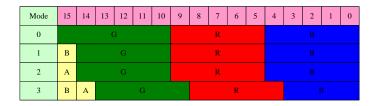

| RGB Format                                                                        |     |

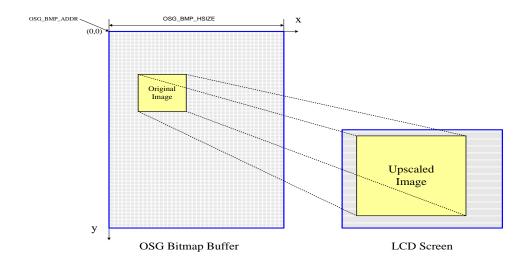

| Upscale                                                                           |     |

| Single Box                                                                        |     |

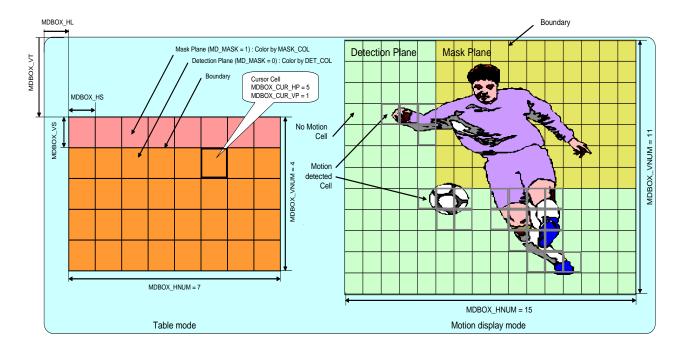

| Motion Box                                                                        | 146 |

| Section 6: OSG and Simple OSD                                                     | 148 |

| Introduction                                                                      | 148 |

| Programming Model                                                                 | 148 |

| Compression Format                                                                |     |

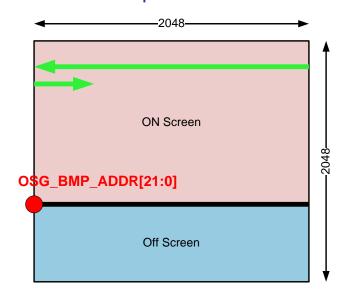

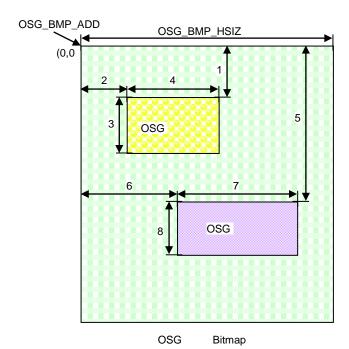

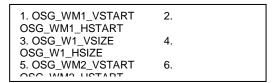

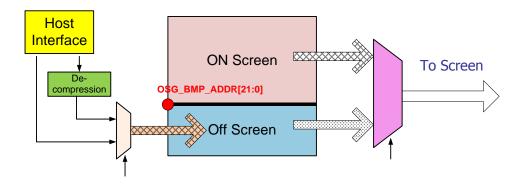

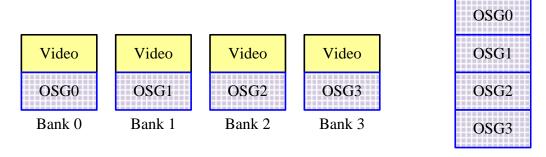

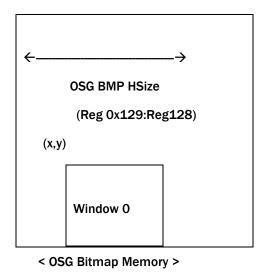

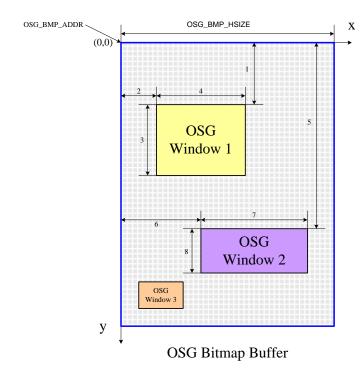

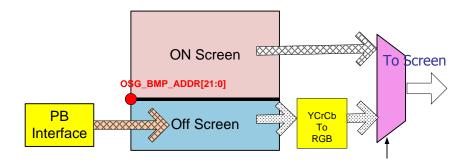

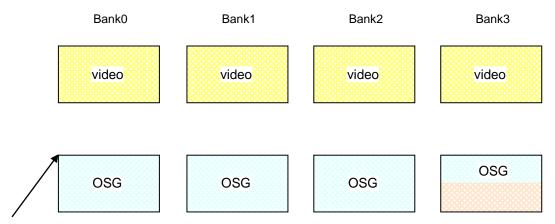

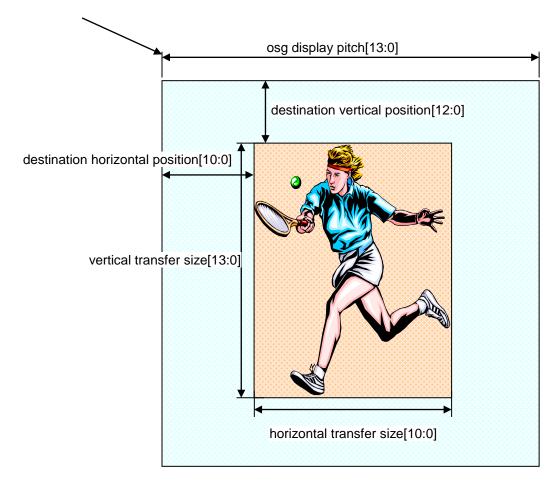

| OSG Bitmap Buffer Start Address Calculation                                       | 149 |

| Writing Bitmap Data                                                               |     |

| Visual Effect Walk Through                                                        |     |

| Block Fill                                                                        | 153 |

| Block Transfer                                                                    |     |

| Color Conversion                                                                  |     |

| Bitblit and Selective Overwrite                                                   |     |

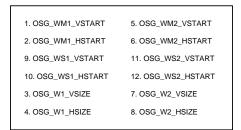

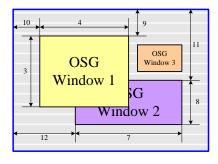

| OSG Window Display                                                                |     |

| External OSG Mater mode                                                           |     |

| External OSG Slave mode                                                           | 157 |

| Programming Model                                                                 |     |

| YCrCb to RGB                                                                      | 157 |

| On Screen memory display                                                          | 157 |

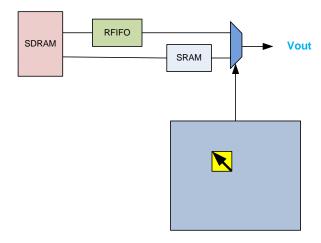

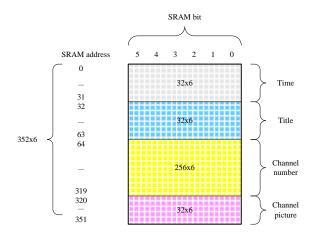

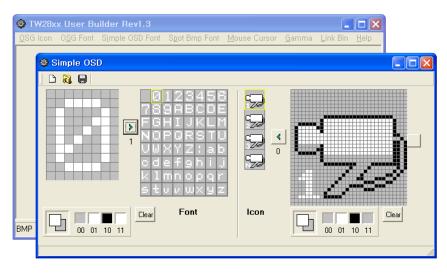

| Simple OSD                                                                        | 158 |

| Introduction                                                                      |     |

| Architecture                                                                      |     |

|                                                                                   |     |

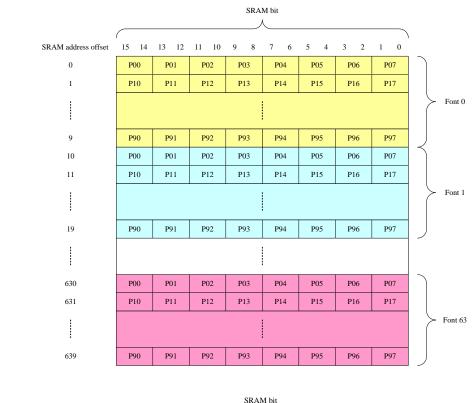

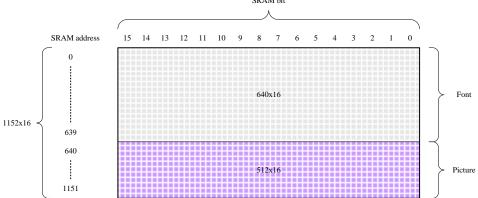

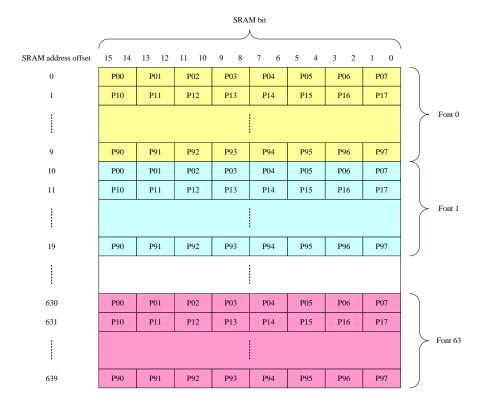

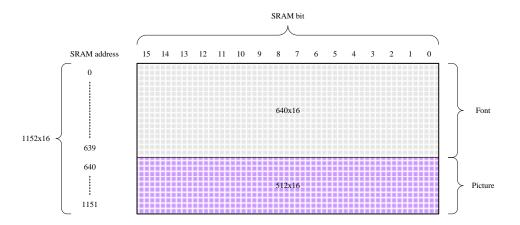

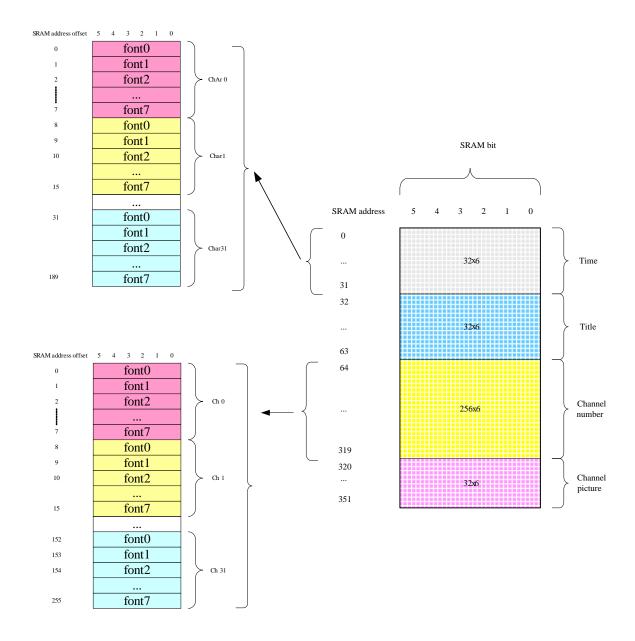

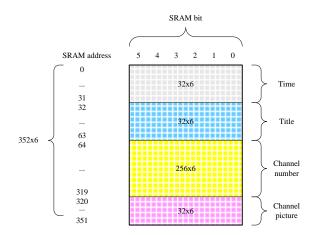

| Fonts and SRAM Memory Size Requirement                                            |     |

| Pictues and SRAM Memory Requirements  Fonts and Pictues in SRAM memory allocation |     |

| Display Information                                                               |     |

| Display Information  Display Date and Time                                        |     |

| Display Date and Time                                                             |     |

| Display Title                                                                     |     |

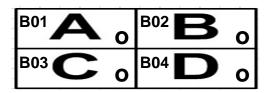

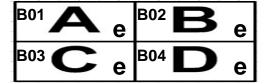

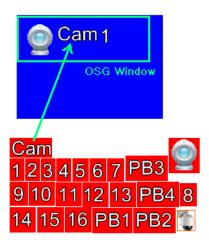

| Display Channel Pictures                                                          |     |

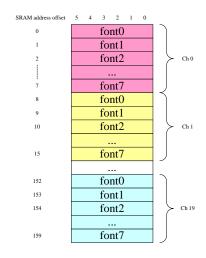

| Display memory                                                                    |     |

| Example                                                                           |     |

| Writing Simple OSD                                                                |     |

| Display Simple OSD                                                                |     |

| • • •                                                                             |     |

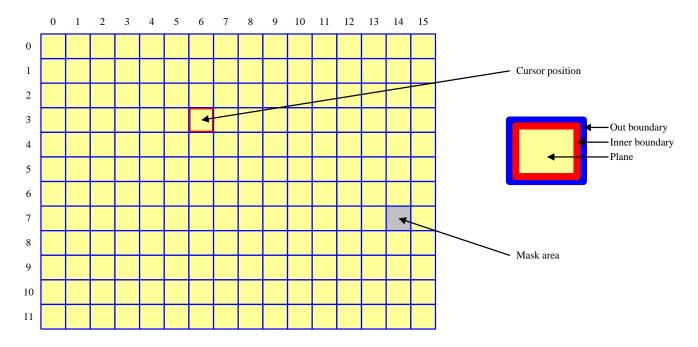

| Section 7: Motion Detection and Interrupt                                         |     |

| Introduction                                                                      |     |

| Mask and Detection Region Selection                                               |     |

| Register settings                                                                 |     |

| Sensitivity Control                                                               | 171 |

| Register settings                                                                 |     |

| Velocity Control                                                                  | 171 |

| Register settings                                                                 |     |

| Blind Detection                                                                   |     |

| Register settings                                                                 |     |

| Night Detection                                                                   |     |

| Register settings                                                                 | 174 |

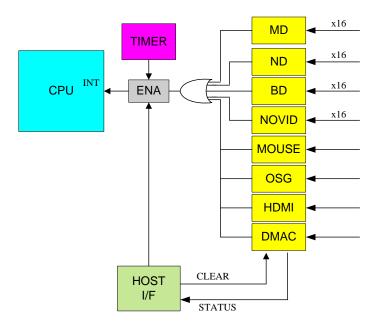

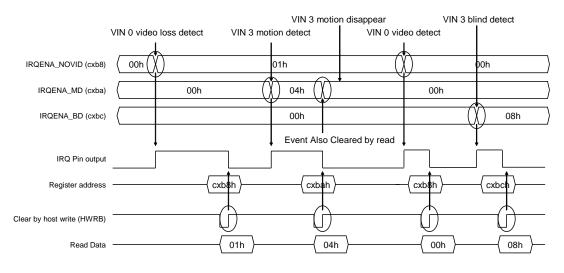

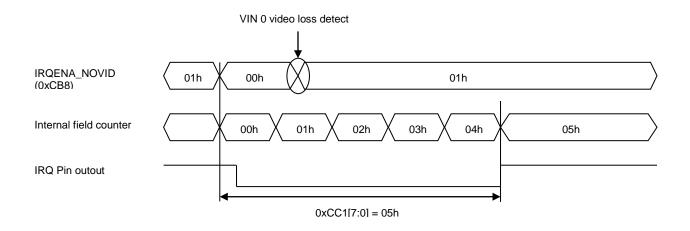

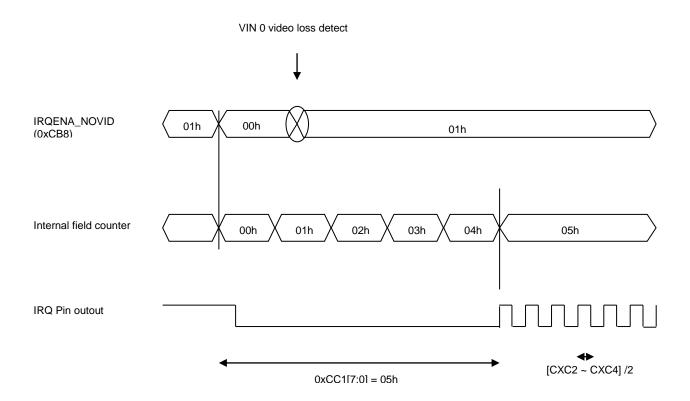

| Interrupt Interface                                                               | 176 |

| Interrupt Interface                                                               |     |

| Register Settings                                                                 |     |

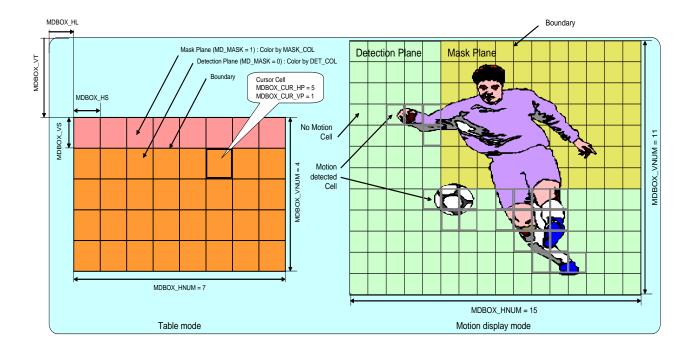

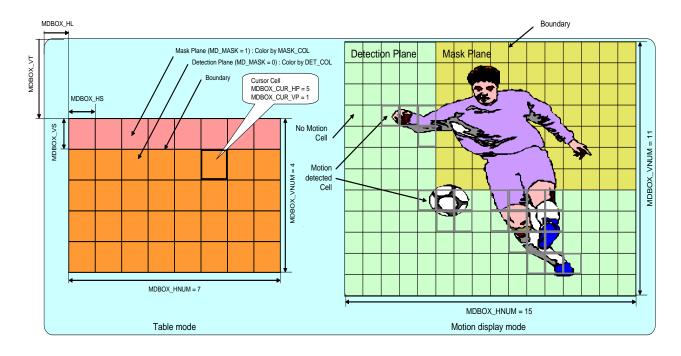

| Motion Box Setting                                                                |     |

| v.v.v. =v. vvttiis                                                                |     |

| Register Settings                                                | 182 |

|------------------------------------------------------------------|-----|

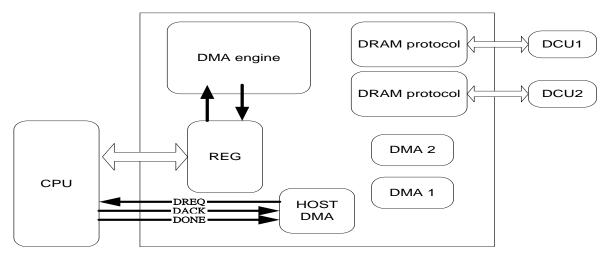

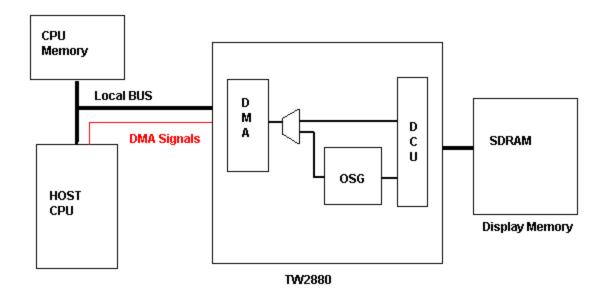

| Section 8: DMA Function                                          | 185 |

| Introduction                                                     | 185 |

| Features                                                         | 185 |

| DMA Engine                                                       | 185 |

| DRAM interface                                                   |     |

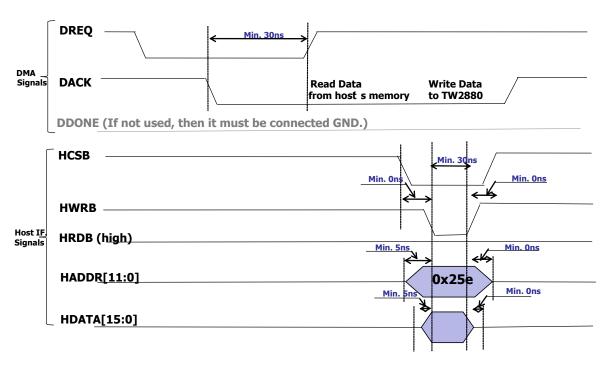

| EXTERNAL DMA DREQ/DACK PROTOCOL                                  |     |

| Basic DMA Timing                                                 |     |

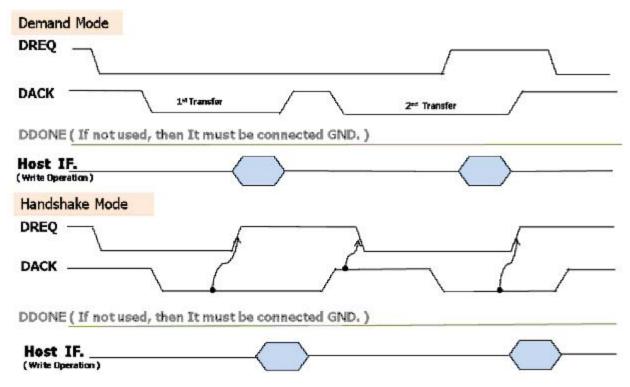

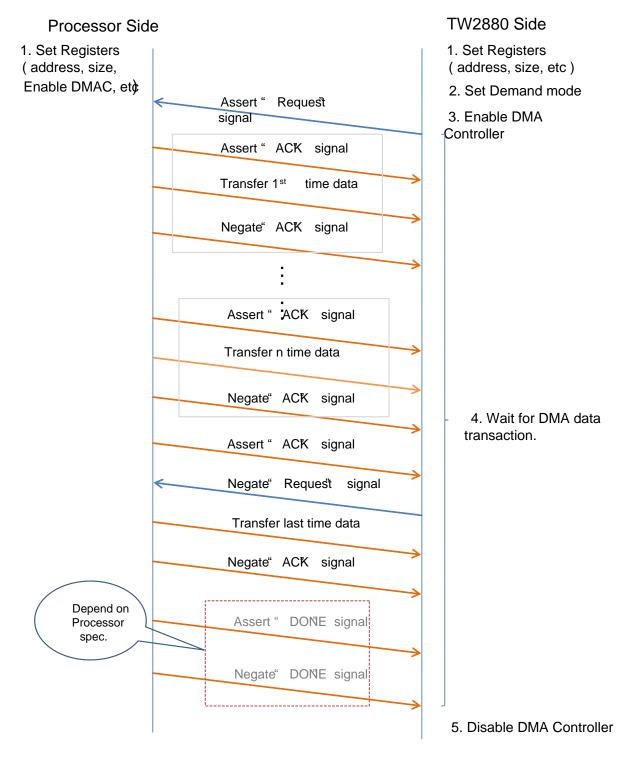

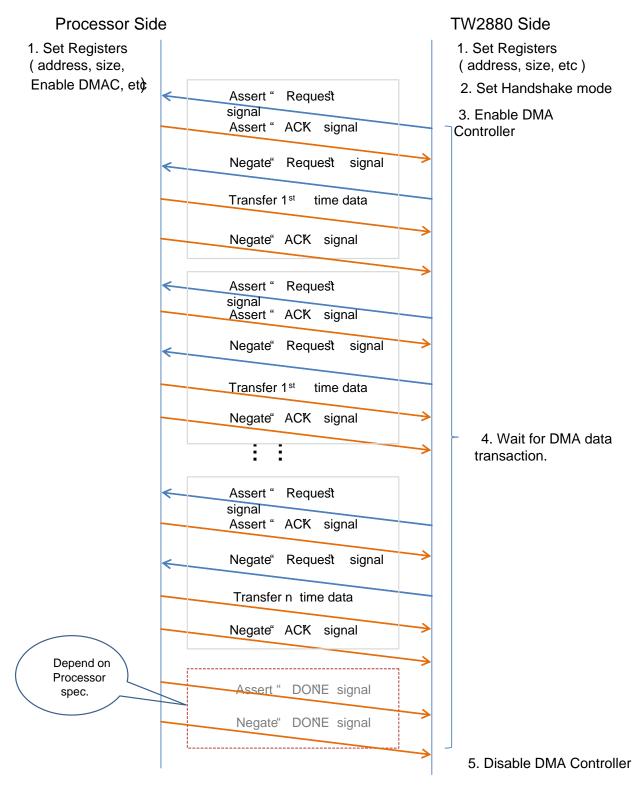

| Demand / Handshake Mode Comparison                               |     |

| Examples                                                         |     |

| DMA Function Software Example                                    |     |

| Data Flow for DMA demand mode                                    |     |

| Data Flow for DMA handshake mode                                 |     |

| Register Setting Example                                         |     |

| Host to SDRAM Moves (OSG Data Transfer)                          |     |

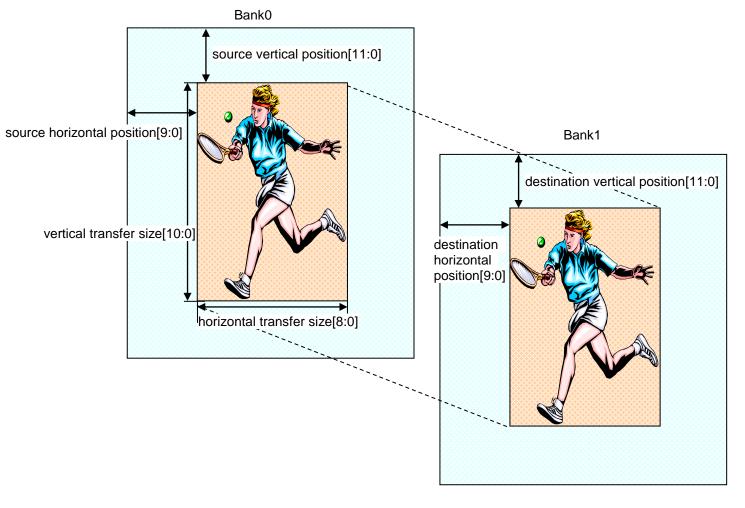

| DRAM Data Copy ( Display DRAM )                                  |     |

| DRAM Data Copy (Record DRAM)                                     |     |

| DMA Function Firmware Example                                    | 198 |

| Introduction                                                     | 198 |

| DMA Write Mode Sequence                                          |     |

| DMA Through OSG Write Mode Sequence                              | 201 |

| Section 9: Audio Interface                                       | 202 |

| Introduction                                                     |     |

| Features                                                         |     |

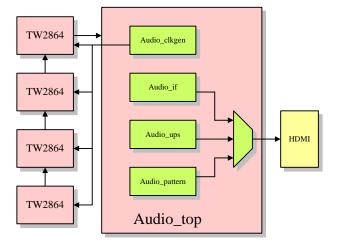

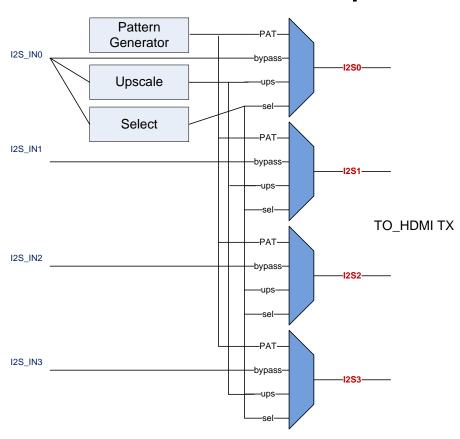

| Block Diagram                                                    |     |

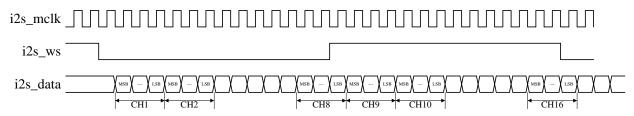

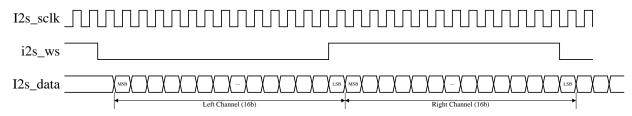

| Timing Diagram                                                   |     |

| Input Timing                                                     |     |

| Output Timing                                                    |     |

| Clock slave mode                                                 |     |

| Clock master mode                                                |     |

| Register Setting Guide                                           |     |

| HDMI Audio Registers                                             |     |

| Audio Interface Registers                                        |     |

| TW2864 Registers                                                 | 206 |

| Register Table                                                   |     |

| Register Description                                             |     |

| Audio Control 1 Register - 0x228                                 |     |

| Audio Control 2 Register – 0x229                                 |     |

| Section 10: Differences Between C2 and B1                        |     |

| The Register Revision List for Recording Unit                    | 209 |

| Separated 'wr_page' Reference                                    |     |

| New Write Buffer Mapping for Read Port                           |     |

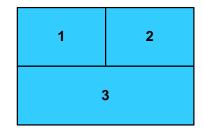

| New Field Signal Generation Scheme in the Field Interleaved Mode |     |

| New Non-Real Time Field Interleaved Mode                         |     |

| Bitmapped OSD                                                    |     |

| Audio Interface Block                                            |     |

| Play Back Unit                                                   | 212 |

| Live Unit                                                        | 212 |

| OSG                                                              | 213 |

| DMON Unit                                                        | 213 |

| Host DMA                                                         |     |

| OSD                                                              |     |

|                                                                  |     |

| LCD Display Unit                         | 214 |

|------------------------------------------|-----|

| Simple OSD Unit                          | 214 |

| DRAM Arbitration Control Unit            | 214 |

| LCD Priority Arbitration 1 — 0x280 (New) | 214 |

| LCD Priority Arbitration 2 — 0x281 (New) | 215 |

| LCD Priority Arbitration 3 — 0x282 (New) | 215 |

| REC Priority Arbitration 1 — 0x284 (New) | 215 |

| REC Priority Arbitration 2 — 0x285 (New) |     |

| Privacy Windows Unit                     | 216 |

| SPOT                                     | 216 |

| CLKGEN                                   | 217 |

| Section 11: Firmware Change Summary      | 218 |

| Rev.1.57                                 | 218 |

| Rev.1.58                                 | 219 |

| Rev.1.59                                 |     |

| Rev.1.60                                 | 221 |

| Rev.1.66                                 | 222 |

# **List of Figures**

| Figure 1. Differential line structures                                                                           | 21 |

|------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Corner patterns                                                                                        |    |

| Figure 3. Space between differential lines at corner areas                                                       |    |

| Figure 4. Meander lines                                                                                          |    |

| Figure 5. Adjustment of skew between differential lines                                                          |    |

| Figure 6. Symmetrical architecture of shield patterns                                                            |    |

| Figure 7. Supply of power and GND by planes, and decoupling capacitor produced by interlayer dielectric material |    |

| Figure 8. Isolation of digital and analog planes                                                                 |    |

| Figure 9. Example of layer structure for 8-layer printed circuit board                                           |    |

| Figure 10. Recommended power supply pin connections                                                              |    |

| Figure 11. Separation of REFCLK and other signals                                                                |    |

| Figure 12. Example of placement of ESD protectors and EMI filters                                                |    |

| Figure 13. Reduction of ball pad capacitance                                                                     |    |

| Figure 14. Reduction of lead pad capacitance                                                                     |    |

| Figure 15. Programming Model of Recording Path                                                                   |    |

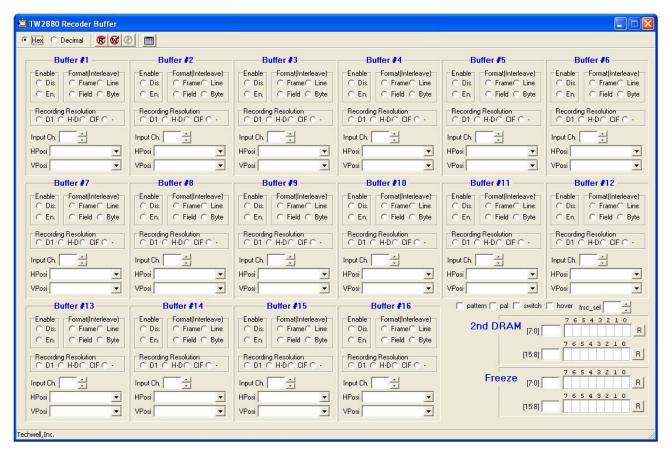

| Figure 16. Record Buffer Control Window                                                                          |    |

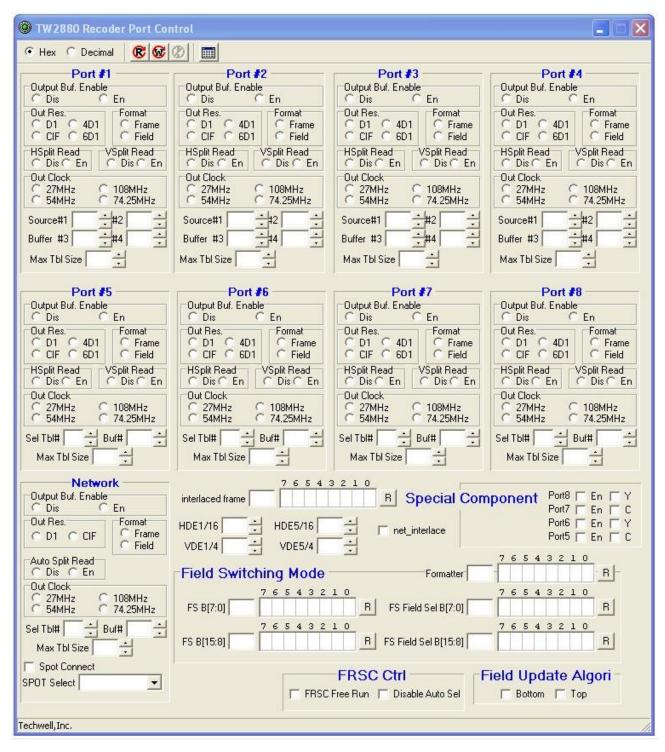

| Figure 17. Record Port Control Window                                                                            |    |

| Figure 18. Record Port Control Window                                                                            |    |

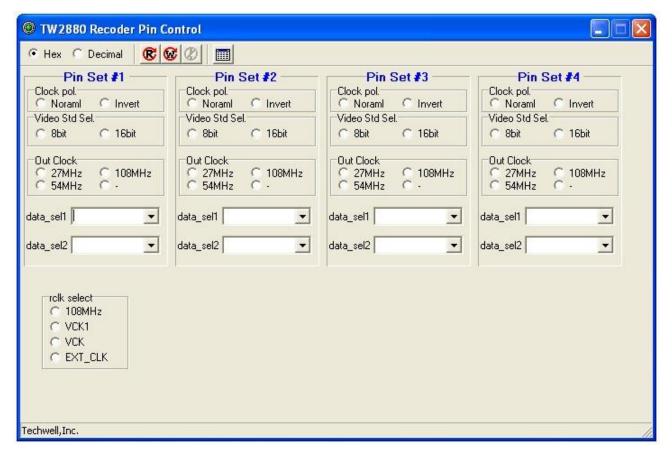

| Figure 19. Flow Chart for Record Programming                                                                     |    |

| Figure 20. Write Buffer Setting Example for 16-D1, FLI mode and NTSC                                             |    |

| Figure 21. Write Buffer Setting Example for mixed resolution, FMI mode and NTSC                                  |    |

|                                                                                                                  |    |

| Figure 22. Write Buffer Setting Example for 16-D1, FMI mode and NTSC                                             |    |

| Figure 23. SPOT Write Buffer Setting Example for 16-CIF, FLI mode and NTSC                                       |    |

| Figure 24. Example for Record using SPOT Buffer                                                                  |    |

| Figure 25. Port Setting Example 1 : D1                                                                           |    |

| Figure 26. Port Setting Example 2 : 4-D1, FMI                                                                    |    |

| Figure 27. Port Setting Example 3 : 4-D1, FLI                                                                    |    |

| Figure 28. Port Setting Example 4 : 4-D1, FLI                                                                    |    |

| Figure 29. Port Setting Example 5 : 4-CIF                                                                        |    |

| Figure 30. Port Setting Example 6 : Quad                                                                         |    |

| Figure 31. Port Setting Example 1 : 6-D1                                                                         |    |

| Figure 32. Port Setting Example 2 : 4D1, FLI                                                                     |    |

| Figure 33. Output Pin Muxing                                                                                     |    |

| Figure 34. Output Pin Setting Example 1 : 8-bit, 1-codec                                                         |    |

| Figure 35. Output Pin Setting Example 2 : 8-bit, 2-codec                                                         |    |

| Figure 36. Output Pin Setting Example 3 : 16-bit, 1-codec\                                                       |    |

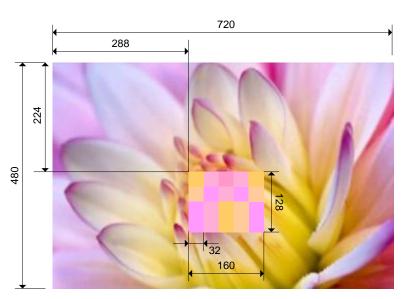

| Figure 37. Privacy Window Setting Example 1 : 16-bit, 1-codec                                                    |    |

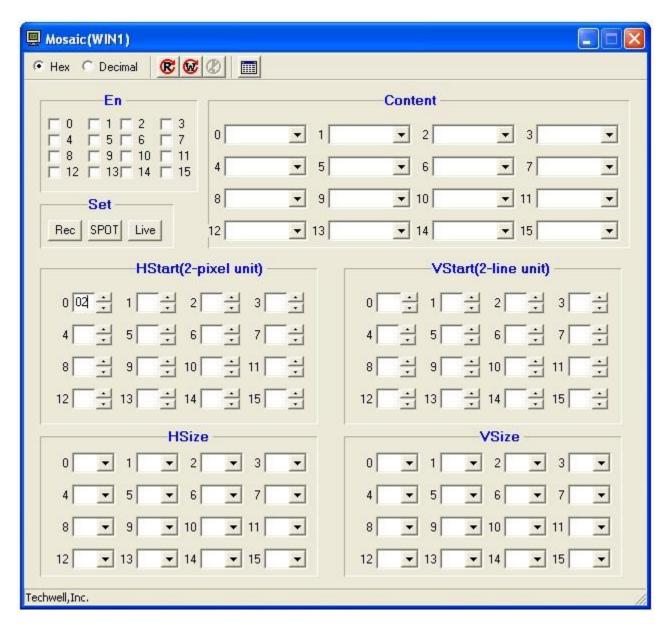

| Figure 38. Privacy Window' Control Widow                                                                         |    |

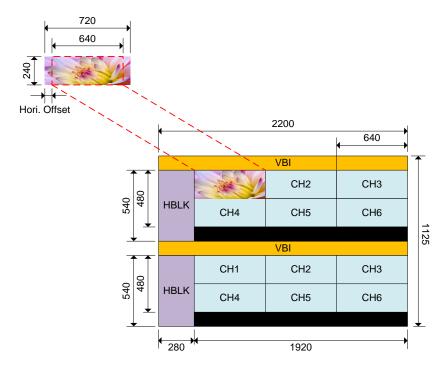

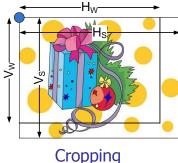

| Figure 39. 6VGA(BT.1120) Image Mapping by horizontal cropping                                                    |    |

| Figure 40. Programming Example 1 : Eight 2-D1, FLI                                                               |    |

| Figure 41. Programming Example 2 : Four 4D1, FMI                                                                 |    |

| Figure 42. Programming Example 3 : 6VGA, FMI                                                                     |    |

| Figure 43. Programming Example 4 : 8-D1, FMI                                                                     |    |

| Figure 44. Image Flow of Field Switching Mode                                                                    |    |

| Figure 45. Programming Example 6 : 8-D1, FMI                                                                     |    |

| Figure 46. Priority and Frame Rate Control Example                                                               | 99 |

| Figure 47. SPOT connection to the network port                                       | 100 |

|--------------------------------------------------------------------------------------|-----|

| Figure 48. PB loopback connection for test                                           | 101 |

| Figure 49. Display memory map                                                        | 150 |

| Figure 50. OSG bitmap buffer starting address                                        | 151 |

| Figure 51. OSG bitmap buffer                                                         | 155 |

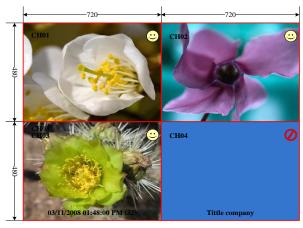

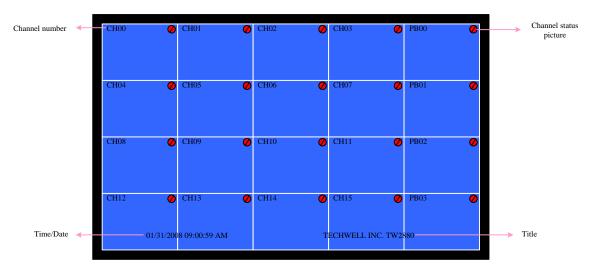

| Figure 52. OSD Functions as showN on the display                                     | 158 |

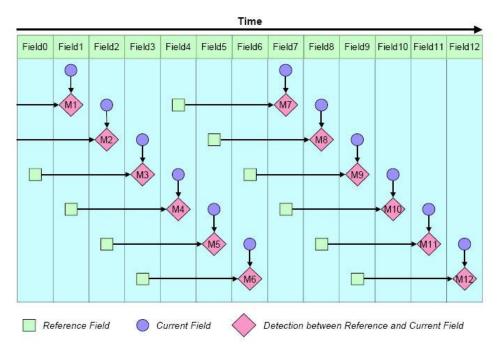

| Figure 53. The Relationship between current and reference field when ND_REFFLD = "0" | 172 |

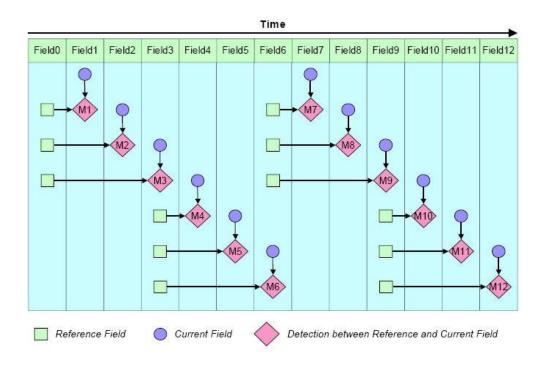

| Figure 54. The Relationship between current and reference field when ND_REFFLD = "1  | 173 |

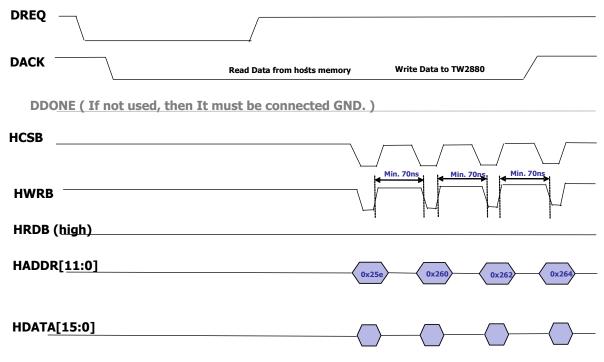

| Figure 55. Basic DMA Timing Diagram                                                  | 187 |

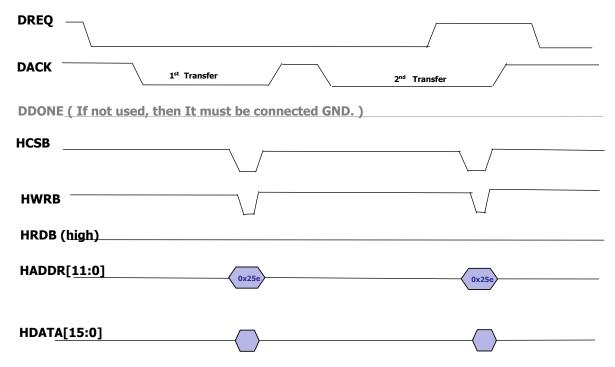

| Figure 56. Demand/Handshake Mode Comparison (example: 2 times transaction)           | 188 |

| Figure 57. Burst 4 Transfer Size                                                     | 189 |

| Figure 58. Single service in Demand Mode with Single Transfer Size                   | 189 |

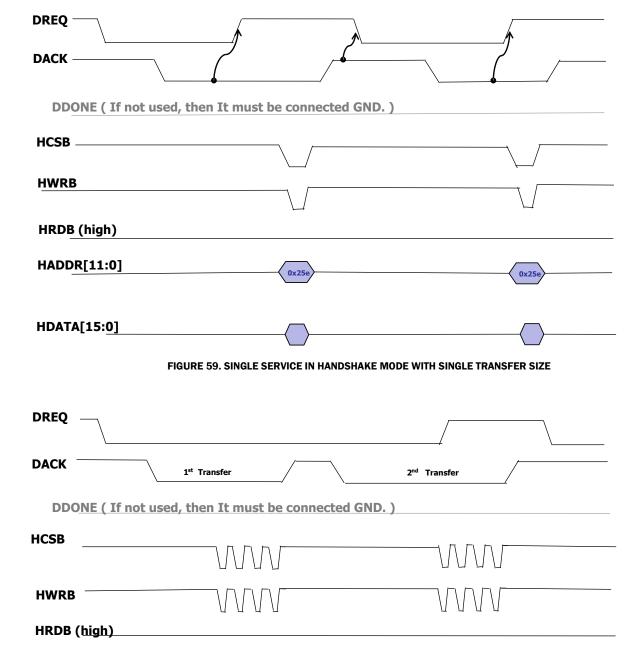

| Figure 59. Single service in Handshake Mode with Single Transfer Size                | 190 |

| Figure 60. Burst 4 service in Demand Mode with Single Transfer Size                  | 190 |

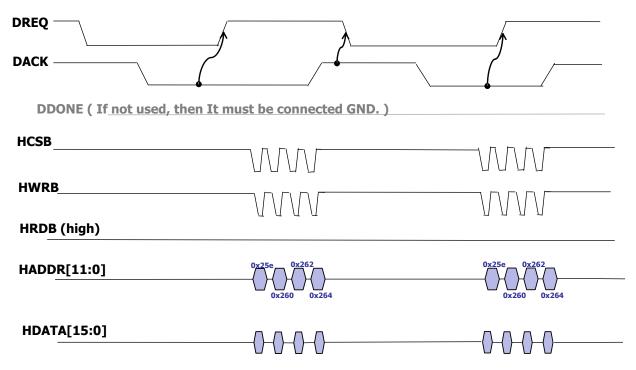

| Figure 61. Burst 4 service in Handshake Mode with Single Transfer Size               | 191 |

| Figure 62. DMA Operation Diagram                                                     | 199 |

# **List of Tables**

| Table 1. Write Buffer Setting Example Code for 16-D1, FLI mode and NTSC                     | 69  |

|---------------------------------------------------------------------------------------------|-----|

| Table 2. Write Buffer Setting Example Code for mixed resolution, FMI mode and NTSC          | 70  |

| Table 3. Write Buffer Setting Example Code for 16-D1, FMI mode and NTSC                     | 72  |

| Table 4. SPOT Write Buffer Setting Example Code for 16-CIF, FLI mode and NTSC               | 74  |

| Table 5. Example Code for Record using SPOT Buffer                                          | 76  |

| Table 6. Port Setting Example Code 1 : D1                                                   | 77  |

| Table 7. Port Setting Example Code 2: 4-D1, FMI                                             | 78  |

| Table 8. Port Setting Example Code 3 : 4-D1, FLI                                            | 79  |

| Table 9. Port Setting Example Code 4 : 4-D1, FLI                                            | 80  |

| Table 10. Port Setting Example Code 5 : 4-CIF                                               | 80  |

| Table 11. Port Setting Example Code 6 : Quad                                                | 81  |

| Table 12 Port Setting Example Code 1 : 6-D1                                                 | 82  |

| Table 13 Port Setting Example Code 2 : 4D1, FLI                                             | 83  |

| Table 14 Table Live Update Example Code                                                     | 83  |

| Table 15. Output Pin Setting Example Code 1:8-bit, 1-codec                                  | 85  |

| Table 16 Output Pin Setting Example Code 2 : 8-bit, 2-codec                                 | 85  |

| Table 17 Output Pin Setting Example Code 3: 16-bit, 1-codec                                 | 86  |

| Table 18 Privacy Window Setting Example Code 1: 16-bit, 1-codec                             | 87  |

| Table 19 Programming Example Code 1 : Eight 2-D1, FLI                                       | 90  |

| Table 20 Programming Example Code 2 : Four 4D1, FMI                                         | 92  |

| Table 21 Programming Example Code 3 : 6VGA, FMI                                             | 94  |

| Table 22 Programming Example Code 4 : 8-D1, FMI                                             | 96  |

| Table 23 Programming Example Code 6: 8-D1, FMI                                              | 98  |

| Table 24 Priority and Frame Rate Control Example Code                                       | 99  |

| Table 25 Programming Example Code 1: Using SPOT Buffer for Recording                        | 100 |

| Table 26 The register for separated 'wr_page' reference                                     | 209 |

| Table 27. The register for new write buffer mapping of read port                            | 210 |

| Table 28. The register for new Field Signal Generation Scheme in The field Interleaved Mode | 211 |

| Table 29. The register for new non-real time field interleaved mode                         | 211 |

| Table 30. The register revision list of Play Back Unit                                      | 212 |

| Table 31. The register revision list of Live Unit                                           | 212 |

| Table 32. OSG BUG correction list                                                           | 213 |

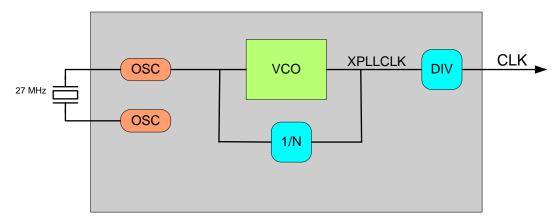

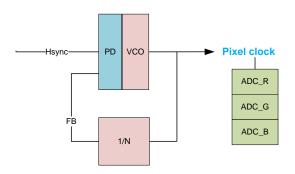

# **Section 1: Clockgen and PLL** Introduction

TW2880C has three clock domains, they are, system clock domain, memory clock domain and video clock domain. Each clock domain support different kind of functional units. The clocks are generated from three different free running PLLs. The high-speed clock after the VCO stage will go through a series divider and phase select before reach the final circuit. Now we will walk through each clock domain in detail.

## **SCLK**

System clock is used throughout the TW2880. The idea is we will also use clocks with multiple of 27 in this clock group. The reason is obvious; 27 MHz clock is the data clock for the BT.656 standard. Because of these characteristics, some video decoders or CVBS output sections will use this clock group.

#### **Clock Listing**

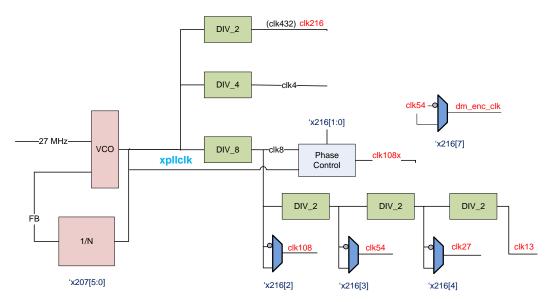

12 clocks are generated from this clock group.

- 108 MHz system clock

- 54, 27, 13.5 MHz system using in input / output blocks

- 108 MHz system clock with phase control, used in recording output unit.

- High speed 216 MHz scaler clock (can be 432 MHz)

- Dual monitor TV encoder clock

- Dual monitor video clock

- · Dual monitor fast clock for scaler

- Dual monitor DAC clock

- Dual monitor external video clock for VGA

- · Network port output clock

## **Register Setting for SPLL**

In normal cases, [0x207] bit[5:0] is designed to have default value of 5'd31 as this will make xpllclk 864 MHz and after divided by 8 circuits will create 108 MHz system clock.

[0x216] bit 2, 3, 4 are used to select the phases of 108 MHz, 54 MHz, and 27 MHz clock.

[0x216] bit 1, 0 are used to select the phases of 108 MHz clock, this to adjust the record port clock / data relationship.

[0x21F] bit 2:1 are used to select the source of dual monitor clock, if CVBS is wanted, we should use the clock generated from the SCLK group. If display mode other than 27 MHz related then we should set these two bits to one and use clock generated from VCLK group.

## **MCLK**

#### Introduction

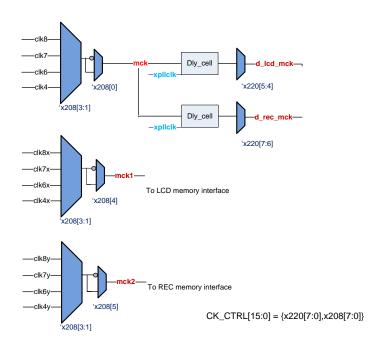

The memory clock range supported in TW2880C is between 133 - 200 MHz. User needs to program the multiplier register x203[5:0] and choose the desired divider to generate frequency. One thing needs to remember is the larger the divider, the more steps in the delay control. Five clocks are needed to adjust in a TW2880C system. They are:

- . Master clock for internal memory related blocks

- Clock for external SDRAM to use (Display side)

- Clock for external SDRAM to use (Recording side)

- Delayed version of display memory clock for latching incoming data

- . Delayed version of recording memory clock for latching incoming data

#### **Master Clock Calculation**

Follow are the examples of popular master clock frequencies based on SDRAM speed grade.

| For 133 MI | Iz (-7.5 ns) |   |        |        |

|------------|--------------|---|--------|--------|

| 27         | 19           | 4 | 128.25 |        |

| 27         | 29           | 6 | 130.50 |        |

| 27         | 34           | 7 | 131.14 |        |

| 27         | 39           | 8 | 131.63 | Select |

| For 166 MI | Iz (-6 ns)   |   |        |        |

| 27         | 24           | 4 | 162.00 |        |

| 27         | 37           | 6 | 166.50 | Select |

| 27         | 43           | 7 | 165.86 |        |

| 27         | 48           | 8 | 162.00 |        |

| For 175 MI | Iz (-5 ns)   |   |        |        |

| 27         | 26           | 4 | 175.50 |        |

| 27         | 39           | 6 | 175.50 | Select |

| 27         | 45           | 7 | 173.57 |        |

| 27         | 52           | 8 | 175.50 |        |

| For 200 MI | Iz (-5 ns)   |   |        |        |

| 27         | 29           | 4 | 195.75 |        |

| 27         | 44           | 6 | 198.00 |        |

| 27         | 52           | 7 | 200.57 |        |

| 27         | 59           | 8 | 199.13 | Select |

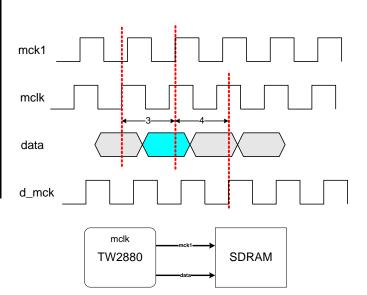

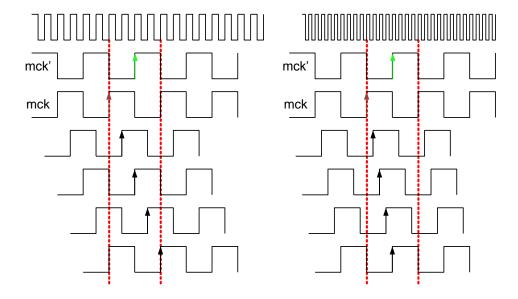

## **Clock Relationship**

Two derivative clocks need to be adjusted to make the memory system work:

- 1. TW2880 to SDRAM: command, write data, controlled by 0x220[1:0] on the display, 0x220[3:2] for the record.

- 2. SDRAM to TW2880: read data, controlled by 0x220[5:4] on the display, 0x220[7:6] for the record.

The steps are determined by divider, for example, divided by 4 you have only four steps, divided by 8, 8 steps.

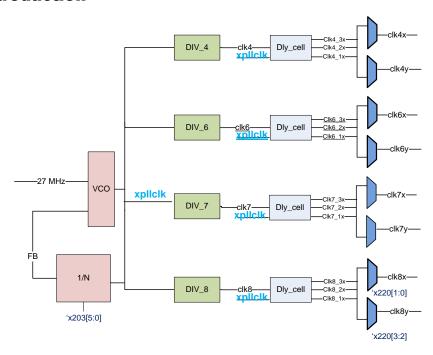

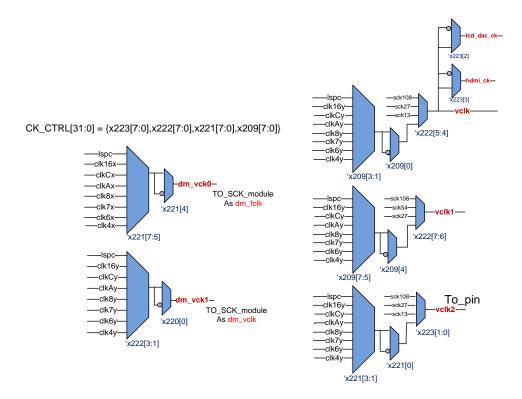

## **VCLK**

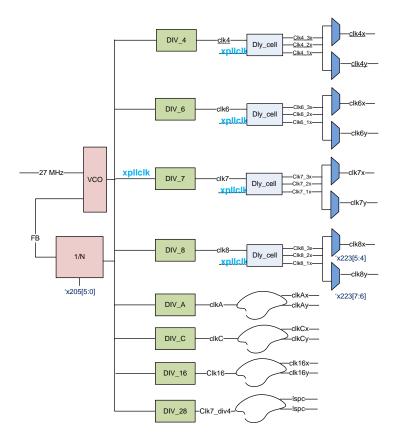

The VCLK in TW2880C has the most complicated clock tree in the three as many exact frequencies are needed. To use it user needs to program the multiplier register x205[5:0] and choose the desired divider to generate frequency. 8 dividers are provided to generate correct clock for display. All together, seven clocks are generated:

- Clock for internal video related clock (vclk)

- Clock for VGA DAC

- Clock for HDMI block

- VCLK1 (not used)

- Clock for digital interface

- Two other dual monitor clock mux with SCLK

## **Popular Main Display Clocks**

From the table shown in the following, TW2880C clock generation module can support most VESA standard resolution for the main display and HDMI TV Standard by selecting the proper VCK\_N and VCK\_Q values.

|        | Res                    | FRS   | PCLK   | VCK_N | VCK_Q | PCLK2  | D iff |

|--------|------------------------|-------|--------|-------|-------|--------|-------|

|        | 640x480                | 50H z | 19.75  | 23    | 28    | 22.18  | -2.43 |

|        | 640x480                | 60H z | 23.88  | 25    | 28    | 24.11  | -0.23 |

|        | 800x600                | 50H z | 31.13  | 32    | 28    | 30.86  | 0.27  |

|        | 800x600                | 60H z | 38.13  | 40    | 28    | 38.57  | -0.45 |

|        | 1024x768               | 50H z | 51.75  | 23    | 12    | 51.75  | 0.00  |

|        | 1024x768               | 60H z | 64.13  | 38    | 16    | 64.13  | 0.00  |

| 4:3    | 1280x960               | 50H z | 83.00  | 37    | 12    | 83.25  | -0.25 |

|        | 1280x960               | 60H z | 102.00 | 38    | 10    | 102.60 | -0.60 |

|        | 1400x1050              | 50H z | 99.75  | 37    | 10    | 99.90  | -0.15 |

|        | 1400x1050              | 60H z | 122.50 | 32    | 7     | 123.43 | -0.93 |

|        | 1600x1200              | 50H z | 132.38 | 39    | 8     | 131.63 | 0.75  |

|        | 1600x1200              | 60H z | 160.88 | 24    | 4     | 162.00 | -1.13 |

|        | 1600x1200r             | 60H z | 130.38 | 29    | 6     | 130.50 | -0.13 |

|        | 848x480                | 60H z | 31.50  | 33    | 28    | 31.82  | -0.32 |

|        | 1064x600               | 60H z | 51.00  | 30    | 16    | 50.63  | 0.38  |

|        | 1280x720               | 50H z | 60.38  | 27    | 12    | 60.75  | -0.38 |

|        | 1280x720               | 60H z | 74.38  | 33    | 12    | 74.25  | 0.13  |

|        | 1360x768               | 50H z | 69.50  | 31    | 12    | 69.75  | -0.25 |

|        | 1360x768               | 60H z | 84.63  | 25    | 8     | 84.38  | 0.25  |

|        | 1704x960               | 50H z | 110.25 | 41    | 10    | 110.70 | -0.45 |

|        | 1704x960               | 60H z | 134.88 | 30    | 6     | 135.00 | -0.13 |

|        | 1864x1050              | 50H z | 133.50 | 30    | 6     | 135.00 | -1.50 |

|        | 1864x1050              | 60H z | 163.25 | 24    | 4     | 162.00 | 1.25  |

|        | 1864x1050r             | 60H z | 131.13 | 34    | 7     | 131.14 | -0.02 |

|        | 1920x1080              | 50H z | 141.38 | 42    | 8     | 141.75 | -0.38 |

|        | 1920x1080              | 60H z | 172.73 | 38    | 6     | 171.00 | 1.72  |

|        | 1920x1080r             | 60H z | 138.63 | 36    | 7     | 138.86 | -0.23 |

|        | 768x480                | 50H z | 23.63  | 24    | 28    | 23.14  | 0.48  |

|        | 768x480                | 60H z | 28.63  | 30    | 28    | 28.93  | -0.30 |

|        | 960x600                | 50H z | 37.00  | 38    | 28    | 36.64  | 0.36  |

|        | 960x600                | 60H z | 45.88  | 27    | 16    | 45.56  | 0.3   |

|        | 1152x720               | 60H z | 67.25  | 25    | 10    | 67.50  | -0.2  |

|        | 1680x1050              | 50H z | 120.13 | 31    | 7     | 119.57 | 0.5   |

| 16:10  | 1680x1050              | 60H z | 147.00 | 38    | 7     | 146.57 | 0.43  |

| 10.110 | 1680x1050r             | 60H z | 119.13 | 44    | 10    | 118.80 | 0.33  |

|        | 1728x1080              | 60H z | 155.50 | 23    | 4     | 155.25 | 0.2   |

|        | 1728x1080r             | 60H z | 125.75 | 28    | 6     | 126.00 | -0.2  |

|        | 1920x1200              | 50H z | 158.00 | 41    | 7     | 158.14 | -0.1  |

|        | 1920x1200              | 60H z | 193.13 | 43    | 6     | 193.50 | -0.3  |

|        | 1920x1200r             | 60H z | 154.13 | 40    | 7     | 154.29 | -0.1  |

|        | 1280x1024              | 50H z | 89.38  | 33    | 10    | 89.10  | 0.23  |

| 5:4    | 1280x1024<br>1280x1024 | 60H z | 108.88 | 24    | 6     | 108.00 | 0.28  |

|        | 1280x768               |       | 65.13  | 29    | 12    | 65.25  | -0.1  |

| 15:9   |                        | 50H z |        |       |       |        |       |

| דעתט   | 1280x768               | 60H z | 80.13  | 24    | 8     | 81.00  | -0.88 |

| HDMI   | 1920x1080p             | 60H z | 148.50 | 44    | 8     | 148.50 | 0.00  |

|        | 1920x1080i             | 30H z | 74.25  | 44    | 16    | 74.25  | 0.0   |

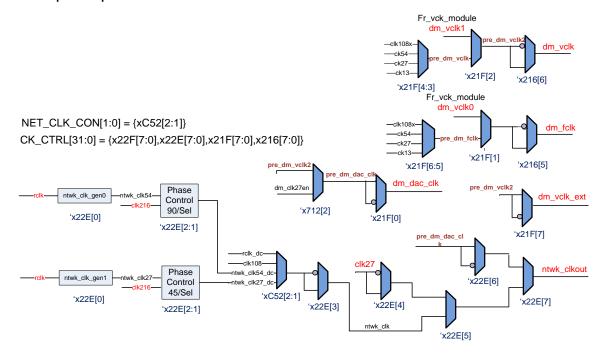

## **Dual Monitor Setting**

Dual monitor's clock setting is a little bit different from the main display's settings. As mentioned before in the SCLK group, dual monitor block can take SCLK as clock source if CVBS output is needed. This is done by setting [0x21F] bit 2:1 to zero. When dual monitor block is running at frequencies other than multiples of 27 MHz, for example, driving a progressive VGA monitor, you need to set [0x21F] bit 2:1 to one and select the output from VCLK VCO. The VCO frequency will be the same for both displays and only the dividers are different. For example, the

main display is set at 1080P and the Dual monitor is set at 1280x1024 resolution. Then, select the SCLK (108 MHz) as the dual monitor video clock and set the main display frequency as listed in the following Table.

| MAIN DISPLAY RESOLUTION | FRAME RATE | MAIN<br>PCLK | VCK_N | VCK_Q | DUAL MON.<br>RESOLUTION | DUAL MON.<br>PCLK | REG SETTING           |

|-------------------------|------------|--------------|-------|-------|-------------------------|-------------------|-----------------------|

| 1920x1080P              | 60Hz       | 148.50       | 44    | 8     | 800x600x60Hz            | 42.4 MHz          | x205= 2B (VCK_N)      |

|                         |            |              |       |       |                         |                   | x209= 66 (div by 8)   |

|                         |            |              |       |       |                         |                   | x221= C6 (div by 28)  |

|                         |            |              |       |       |                         |                   | x222= 0C              |

|                         |            |              |       |       |                         |                   | x216= 02              |

|                         |            |              |       |       |                         |                   | x21f= 06 (dm sel VCK) |

| 1920x1080P              | 60Hz       | 148.50       | 44    | 8     | 1280x1024x60Hz          | 108               | x205= 2B (VCK_N)      |

|                         |            |              |       |       |                         |                   | x209= 66 (div by 8)   |

|                         |            |              |       |       |                         |                   | x221= C6              |

|                         |            |              |       |       |                         |                   | x222= 0C              |

|                         |            |              |       |       |                         |                   | x216= 02              |

|                         |            |              |       |       |                         |                   | x21f= 78 (dm sel SCK) |

| 1280x1024               | 60Hz       | 108          | 32    | 8     | 1024x768x70Hz           | 72                | x205= 1F (VCK_N)      |

|                         |            |              |       |       |                         |                   | x209= 66 (div by 8)   |

|                         |            |              |       |       |                         |                   | x221= A6 (div by 12)  |

|                         |            |              |       |       |                         |                   | x222= 0A              |

|                         |            |              |       |       |                         |                   | x216= 02              |

|                         |            |              |       |       |                         |                   | x21f= 06 (dm sel VCK) |

When the Dual monitor is used to drive an analog TV, the frequency setting is simply by choosing the 54 Mhz as the  $dm_vck$  output. The registers x21F[4:2]='x4

## **Using SCLK Clock Group For Dual Monitor Clock**

Usually, the SCLK frequency should not be changed either for system, record ports, or SPOT displays stability.

The performance of the above ports as well as the host bandwidth will also be affected if SCLK frequency is changed. For Dual monitor, if SCLK clock is used, the registers x21F need to be set properly.

## **Example**

As an illustration, if the main display is in 1080p mode so the output frequency is 148.5 MHz, the dual monitor is VGA with 640x480@72Hz. The dual monitor clock is 31.5 MHz. Therefore, in addition to correcting the RGB register settings, the clock gen registers setting are:

#### **MCLK REGISTERS**

| REG ADDRESS | DEFAULT SETTING | NEW SETTING | COMMENTS        |

|-------------|-----------------|-------------|-----------------|

| x202        | 'x <b>12</b>    |             | MCLK M          |

| x203        | 'x23            |             | MCLK N          |

| x208        | 'x02            |             | MCLK CTRL[7:0]  |

| x220        | 'x00            |             | MCLK CTRL[15:8] |

Default setting is 162 MHz.

#### **VCLK REGISTERS**

| REG ADDRESS | DEFAULT SETTING | NEW SETTING | COMMENTS         |

|-------------|-----------------|-------------|------------------|

| x204        | 'xOd            |             | VCLK M           |

| x205        | 'x27            | 'x20        | VCLK N           |

| x209        | 'x88            | 'x02        | VCLK CTRL[7:0]   |

| x221        | 'x88            | ʻxc0        | VCLK CTRL[15:8]  |

| x222        | 'x00            | 'xcc        | VCLK CTRL[23:16] |

| x223        | 'x00            | 'x00        | VCLK CTRL[31:24] |

The main display frequency is calculate as 27 \* 33 / 6 = 148.5 MHz

The Dual monitor frequency is selected as 27 \* 33 / 28 = 31.8 MHz

#### **VCLK REGISTERS**

| REG ADDRESS | DEFAULT SETTING | NEW SETTING | COMMENTS         |

|-------------|-----------------|-------------|------------------|

| x206        | 'x0f            |             | SCLK M           |

| x207        | ʻx <b>1</b> f   |             | SCLK N           |

| x216        | 'x00            |             | SCLK CTRL[7:0]   |

| x21F        | 'x78            | 'x07        | SCLK CTRL[15:8]  |

| x22E        | 'x00            |             | SCLK CTRL[23:16] |

| x22F        | 'x00            |             | SCLK CTRL[31:24] |

| X712        | 'x00            | 'x04        | DM_LCD           |

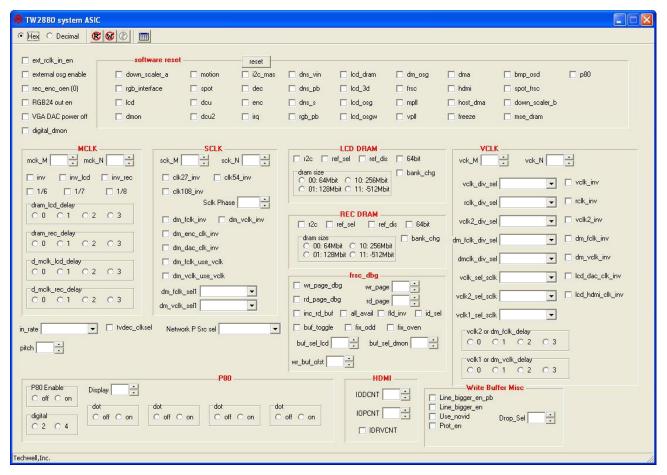

# **Techwell Terminal Tool Setting**

### **Layout of the CFG File**

## **Explanation**

In the Terminal, there are bold red characters, which describe the functions along with registers values that can be selected or white boxes that may be filled in to control the behavior of the functions.

- In the software reset section, a checked box would reset the specified module until the box is un-checked.

- In the MCK section, the mck\_M is for the mck duty cycle control. The mck\_N is the multiplier to the MPLL with the 27 MHz oscillator input, the PLL frequency output equals (mck\_N + 1) x 27 MHz. The MPLL output frequency must less 1200 MHz and higher than 600 MHz for the MPLL to operate stable. After the mck\_N is set, then final mck frequency is derived from check one of the division 1/6, 1/7, or 1/8. By properly choose the mck\_N value and the division, the optimal MCK frequency can be acquired.

- In the MCK section, there are four other delay control selections, which are used for timing control to the DRAM interface. Two MCK outputs delay control such as dram\_lcd\_delay and dram\_rec\_delay, are used to clock phase delay respect to data and control signals. When delay 0 is check, the MCK output and the 64b data and control signals are aligned as the chip layout timing. If the PCB timing is not ideal and needs to be adjusted, then the MCK phase control can be set to 90, 180, or 270 degrees with respect to the data and control signals.

- There are two d\_mclk\_lcd\_delay and d\_mclk\_rec\_delay, which are used to adjust the input data to be latched by the TW2880. If 0 is checked, the data are latched by the MCK, otherwise, the data are latched by the delayed MCK.

- In the SCLK section, the M, N values are set as the MCK. The SCLK is set to 108 MHz as the default and should not be changed. Others boxes can be checked or un-checked to tune the inputs or outputs timing as needed. There are some boxes called dm\_enc\_clk\_inv ..., which are used by the DUAL MONITOR module timing control.

- In the VCLK section, the M, N values are set as the MCK. All the boxes in the section are used to control the data timing respect to the VCLK or Dual\_Monitor VCLK.

- In the LCD\_DRAM or REC\_DRAM section, dram size indicates the DRAM size used on the board.

- The 64-bit box is checked indicates the TW2880 interface to DRAM in 64-bit bus. Otherwise, it is 32-bit bus. Other buttons are for internal use only. The SDRAM controller default value should be good enough for everyday use.

- In the frsc\_dbg section, the options for write pages and read pages can be controlled for debug purpose.

- In the P80 section. This is the LED control module used for debugging purposes.

- In the HDMI section, the setting is to control the HDMI output. The IODCNT control the output currents, the IOPCNT control the De-Emphasis and IDRVCNT Disable the De-emphasis if the box is checked.

- In the Write Buffer Misc section, these registers are used to protect SDRAM off-screen memory from being overwritten by run away RGB write FIFO process.

# **Section 2: PCB Layout Guide**

## Introduction

TW2880 is a complicated VLSI device whose inputs and outputs include several high frequency signal groups. To achieve the best result, the traces and associated discrete components need to carefully designed, placed and connected. To further complicate the board design, there are several power rails used either by digital or by analog functions. This guide served as a general reference for the board designer of TW2880.

#### **Placement Suggestions**

The first suggestion in designing TW2880 related PCB is clearly identifying the major functions that you want to include in this board. The second step involves planning the input / output connectors in a way such that do not let the signal trace crossed by traces in other groups if you can, whether it is signal traces or power traces. These are very important steps for getting a clean video output because crosstalk noise between the groups can easily destroy a board.

For the people not familiar with the term, crosstalk is the unwanted coupling of signals between parallel traces. To reduce crosstalk in TW2880 related boards, use dual-stripline layouts, which have two signal layers next to each other, route all traces perpendicular, increase the distance between the two signal layers, and minimize the distance between the signal layer and adjacent plane. Use the following steps to reduce crosstalk in either microstrip or stripline layouts:

- Widen spacing between signal lines as much as routing restrictions will allow. Try not to bring traces closer than three times the dielectric height.

- Design the transmission line so that the conductor is as close to the ground plane as possible. This technique will couple the transmission line tightly to the ground plane and help decouple it from adjacent signals.

- Use differential routing techniques where possible, especially for critical nets (i.e., match the lengths as well as the gyrations that each trace goes through).

- If there is significant coupling, route single-ended signals on different layers orthogonal to each other.

Minimize parallel run lengths between single-ended signals. Route with short parallel sections and minimize long, coupled sections between nets.

Crosstalk also increases when two or more single-ended traces run parallel and are not spaced far enough apart. The distance between the centers of two adjacent traces should be at least four times the trace width. To improve design performance, lower the distance between the trace and the ground plane to under 10 mils without changing the separation between two traces.

## Signal Integrity

For a single-ended trace, like clock transmission line, it could be improved using the following guidelines:

- · Keep clock traces as straight as possible. Use arc-shaped traces instead of right-angle bends.

- Do not use multiple signal layers for clock signals.

- Do not use via in clock transmission lines. Via can cause impedance change and reflection.

- Place a ground plane next to the outer layer to minimize noise. A "grow to fill" function in the layout tool provides exactly this. If you use an inner layer to route the clock trace, sandwich the layer between reference planes.

- Terminate clock signals to minimize reflection.

- Use point-to-point clock traces as much as possible.

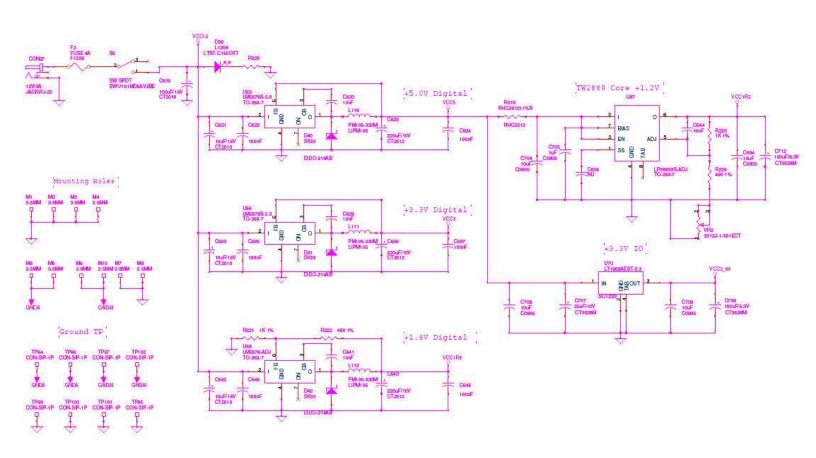

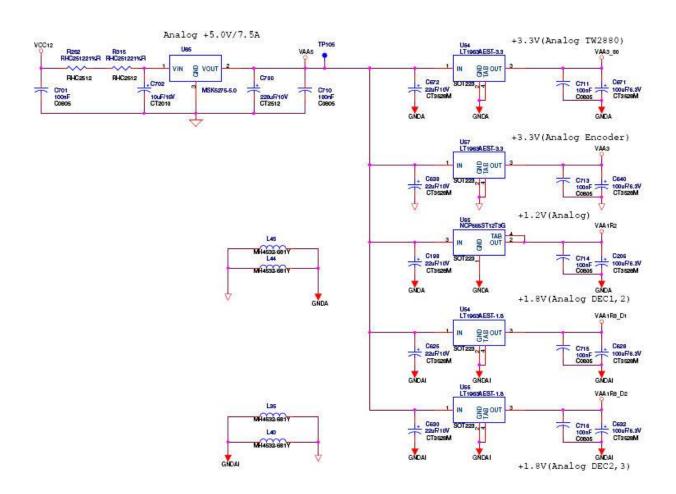

## **Power Regulator and Noise Filtering**

TW2880 has 5 voltage tails for analog and digital functions. To get the best possible result but still keep the power consumption down, we suggestion using the switching regulator in the beginning of the power network and switching to LDO in the end to reduce the switching noise. This is especially true if the power is used for analog function. To

decrease the low frequency (below 1 kHz) noise caused by the power supply, filter the noise on power lines at the point where the power connects to the PCB and to each device. Place a 100 µF electrolytic capacitor where the power supply lines enter the PCB and after the first stage voltage regulator VCC signal. (Capacitors not only filter low-frequency noise from the power supply, but also supply extra current when many outputs switch simultaneously in a circuit.)

To filter power supply noise, use a non-resonant, surface-mount ferrite bead large enough to handle the current in series with the power supply. Place a 10 to 100 µF bypass capacitor next to the ferrite bead. (If proper termination, layout, and filtering eliminate enough noise, you do not need to use a ferrite bead.) The ferrite bead acts as a short for high frequency noise coming from the VCC source. Any low frequency noise is filtered by a large 10 µF capacitor after the ferrite bead. Usually, elements on the PCB add high-frequency noise to the power plane. To filter the high-frequency noise at the device, place decoupling capacitors as close as possible to each VCC and GND

#### **Power Distribution**

You can distribute power throughout the TW2880 PCB with either power planes or a power bus network. When designing TW2880 related PCB, a multi-layer PCBs that consist of two or more metal layers that carry VCC and GND to TW2880 is highly recommended. Because the power plane covers the full area of the PCB, its DC resistance is very low. The power plane maintains VCC and distributes it equally to all devices while providing very high current-sink capability, noise protection, and shielding for the logic signals on the PCB. It is recommended to use lower planes to distribute power. The power bus network, which consists of two or more wide metal traces that carry VCC and GND to devices, is often used on two-layer PCBs and is less expensive than power planes. When designing with power bus networks, be sure to keep the trace widths as wide as possible. The main drawback to using power bus networks is significant DC resistance. It is recommended to separate analog and digital power planes. For fully digital systems that do not already have a separate analog power plane, it can be expensive to add new power planes. However, you can create partitioned islands (split planes).

If your system shares the same plane between analog and digital power supplies, there may be unwanted interaction between the two circuit types. The following suggestions will help to reduce noise:

- For equal power distribution, use separate power planes for the analog (PLL) power supply. Avoid using trace or multiple signal layers to route the PLL power supply.

- Use a ground plane next to the PLL power supply plane to reduce power-generated noise.

- Place analog and digital components only over their respective ground planes.

- Use ferrite beads to isolate the PLL power supply from digital power supply.

#### TW2880 Power Rails

There are eleven voltage sources in a TW2880 HQ EV board. There are 5V digital, 3.3V digital, 3.3V TW2880 analog, 3.3V I/O, 1.8V digital, 1.8V analog, 1.2V TW2880 core, 1.2V TW2880 analog, 3.3V analog encoder, 1.8V analog decoder x2. We used a buck-switching regulator to create power source from external 12V DC adapter. In the final stage, we use many LDO to get the desired analog voltage. Please reference to the next two schematics. Please pay special attention to all analog power supplies to TW2880 and the I/O video chip, as this will determine the final visual effect.

### **SDRAM**

#### Introduction

TW2880 has two 64-bit memory sub-systems, each can support up to 64M Byte SDRAM. To form a system, you can select x16 or x32 width SDRAM. In addition, to support all features in the chip, at least -6 speed grade device is needed. Use -5 device if you can find them.

#### **Termination Resistors**

Because the operating frequency is pretty high for SDR operation, certain rules need to be observed for trouble free results. The clock trace on the board needs to wider and short with respect to other trace. Secondly, all address / control lines to the SDRAM should be terminated. We suggest values of 22 ohms to soften the rising / falling edge of the signals.

### **Equi-Length Line Rule**

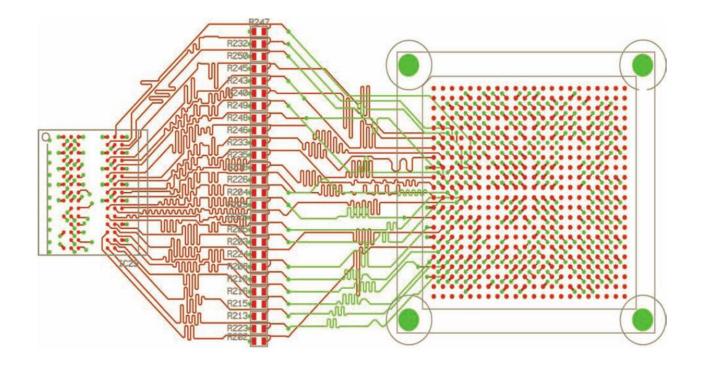

TW2880 has various read / write timing adjustments built in to let user to program to fit different SDRAM into TW2880's environment. However, one rule the layout engineer needs to follow is the equi-length rule. Each address line and data line need to hand matched to similar total trace length in the board as the following diagram suggestive.

### DAC

#### Introduction

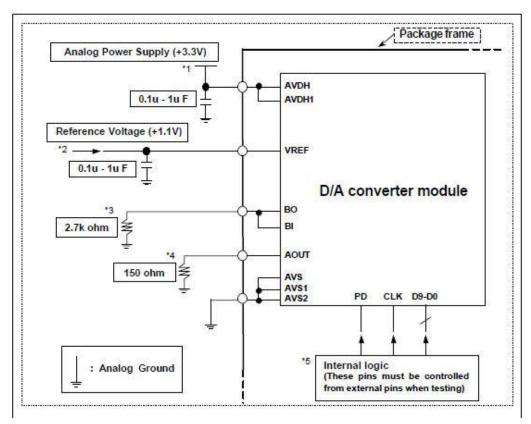

TW2880 has 10 DACs built into the chip. Three DACs are used for main VGA output; three DACs are used for secondary VGA / CVBS and S-video. The remaining four DACs are used for SPOT monitors. The following is a suggestion of how to get good video quality and is applicable to every DAC on the chip.

#### **Power Supply**

For accurate operation of D/A converter, we must pay special attention to the noise of analog power supply. The wiring impedance is the most important factor for its accuracy. It is recommended to use the high frequency type ceramic capacitor for decoupling to the analog ground. The decoupling capacitor must be as close as possible to the TW2880 to keep lead lengths to an absolute minimum.

The voltage of 1.1V must be drawn from a clean voltage source or the video result will be bad. This is especially true is high frequency mode is desired. This voltage source also needs to be de-coupled by using the high frequency type ceramic capacitor and the location should be close to the chip.

#### **Proper Termination**

Mismatched impedance between DAC and the monitor causes video signals to reflect back and forth along the lines, which will cause the annoying ringing effect at the TV or monitor. The ringing reduces the dynamic range of the receiver and can cause false triggering. To eliminate reflections, the impedance of the source (ZS) must equal the impedance of the trace (Zo), as well as the impedance of the load (ZL). The loading in TW2880 application is 37.5R as we are using the standard 75R double terminated scheme to cut down reflection.

### **Connection Example**

#### **PCB Layout Considerations**

The TW2880 is dedicated video VLSI with many integrated functions. To complement the excellent performance of the TW2880, it is imperative that great care be given to the PCB layout. The diagram on the previous page shows a recommended connection diagram for the TW2880. The layout should be optimized for lowest noise on the TW2880 power and ground lines. This can be achieved by shielding the digital inputs and providing good decoupling. Shorten the lead length between groups of VAA and GND pins to minimize inductive ringing.

It is recommended to use at least 6-layer printed circuit board with a single ground plane. The ground and power planes should separate the signal trace layer and the solder side layer. Noise on the analog power plane can be further reduced by using multiple decoupling capacitors (see diagram on the previous page). Optimum performance is achieved by using 0.1 µF and 0.01 µF ceramic capacitors. Individually decouple each VAA pin to ground by placing the capacitors as close as possible to the device with the capacitor leads as short as possible, thus minimizing lead inductance. If a high frequency switching power supply is used, pay close attention to reducing power supply noise. A dc power supply filter (Murata BNX002) provides EMI suppression between the switching power supply and the main PCB.

#### **RECOMMENDED ROUTING/LAYOUT RULES**

- Do not run analog and digital signals in parallel.

- Use separate analog and digital power planes to supply power.

- Traces should run on top of the ground plane at all times.

- No trace should run over ground/power splits.

- · Avoid routing at 90-degree angles.

- Minimize clock and video data trace length differences

#### **HDMI**

#### **General Description**

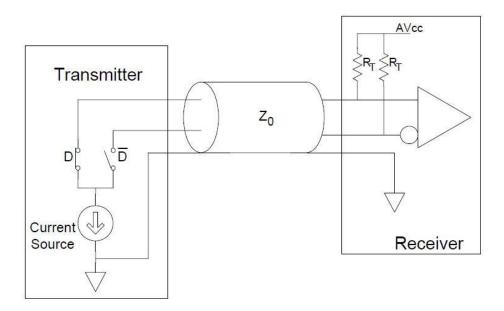

The guidelines in this chapter apply to the following listed signals of TW2880' HDMI transmitter. These signals are TMDS (Transition Minimized Differential Signaling) and are open-drain outputs. Therefore, these signals need to be pulled up to 3.3 V power supply via resistors of 50 $\Omega$  at the receiver side.

- EXCP

- EXCN

- EXP0

- EXNO

- EXP1

- EXN1

- EXP2

- EXN2

The conceptual schematic of a TW2880 enabled transmitter / receiver pair is shown below. TMDS technology uses current drive to develop the low voltage differential signal at the Sink side of the DC-coupled transmission line. The link reference voltage AV∞ sets the high voltage level of the differential signal, while the low voltage level is determined by the current source of the HDMI Source and the termination resistance at the Sink. The termination resistance (R<sub>T</sub>) and the characteristic impedance of the cable (Z<sub>0</sub>) must be matched.

## **Signal Integrity**

The basic rules related to the layout of transmission lines on a printed circuit board are explained below.

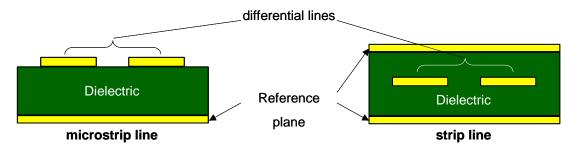

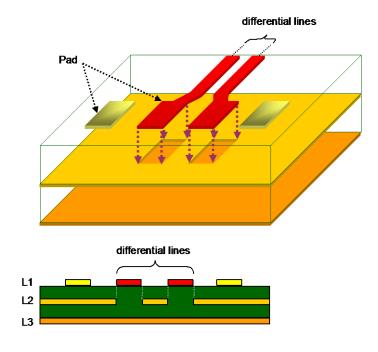

#### **IMPEDANCE CONTROL**

The characteristics impedance of the transmission lines must be differential impedance of  $100\Omega\pm10\%$  as a rule. For proper characteristics impedance, use the strip line or microstrip line structure. Study which of them should be used on a case-by-case basis, considering the package and the numbers of the pins and macros.

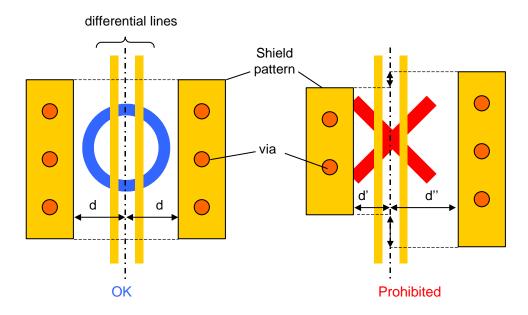

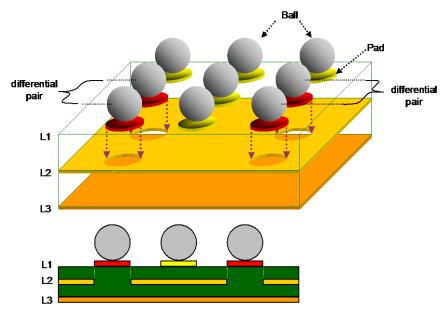

FIGURE 1. DIFFERENTIAL LINE STRUCTURES

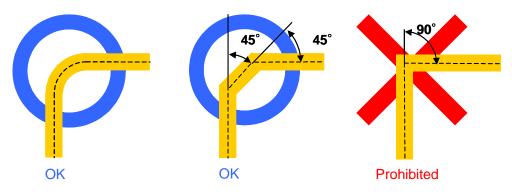

#### 45°BENDS

At corner areas, keep the bending degrees of the transmission lines up to 45  $^{\circ}$  .

**FIGURE 2. CORNER PATTERNS**

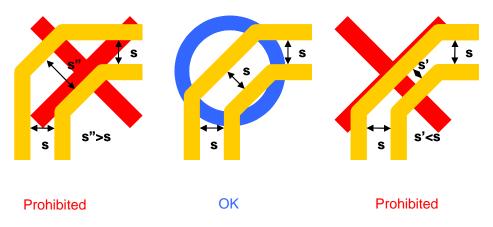

Also at corner areas, keep the same space between the differential lines.

FIGURE 3. SPACE BETWEEN DIFFERENTIAL LINES AT CORNER AREAS

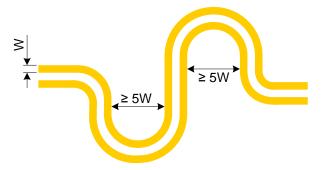

#### **SKEW CONTROL**

Eliminate the skew between the clock channel and the data channels. If an inter-channel skew exists between the clock and data within the LSI package, correct the wiring of the lines on the printed circuit board. When meander lines are used, keep at least 5W of spaces between the meander line patterns.

**FIGURE 4. MEANDER LINES**

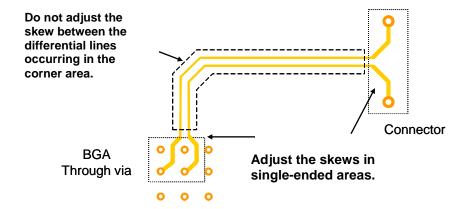

For the inter-channel skew between the clock and data, refer to the specification documents for each product.

Concerning the skews occurring in single-ended areas of the differential lines around the BGA, adjust them within each single-ended area. Do not adjust the skew between the differential lines occurring in the corner areas.

FIGURE 5. ADJUSTMENT OF SKEW BETWEEN DIFFERENTIAL LINES

#### SYMMETRICAL DESIGN

When providing the patterns in the peripheral areas of the differential lines and connecting parts to the differential lines, provide and connect them in such a way that they are symmetrically provided and connected with respect to the centerline between the differential lines. When shielding the differential lines, shield both the clock channel and the data channels using the same architecture.

FIGURE 6. SYMMETRICAL ARCHITECTURE OF SHIELD PATTERNS

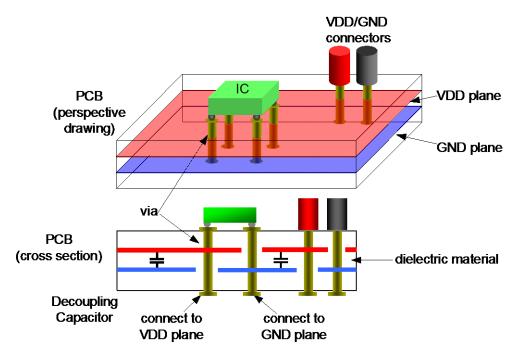

## **Power and Ground POWER AND GND PLANES**

Use planes, not wires, for power supply and GND. Laying the power supply and GND planes in layers produces capacitive coupling, which functions also as a decoupling capacitor reducing power supply noises.

FIGURE 7. SUPPLY OF POWER AND GND BY PLANES, AND DECOUPLING CAPACITOR PRODUCED BY INTERLAYER DIELECTRIC MATERIAL

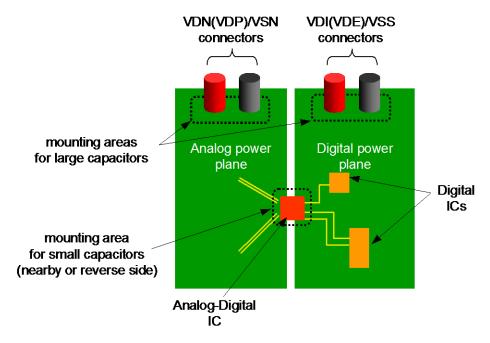

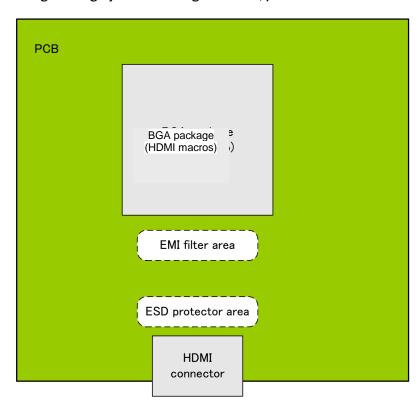

#### **PLANE ISOLATION**

Divide the power supply and GND planes into an analog (VDN, VDU, VDP, VSN) area and a digital (VDI, VDE, VSS) area respectively according to function. In each area, mount large capacitance capacitors close to the power supply and GND connectors, and mount small capacitance capacitors close to the ICs.

FIGURE 8. ISOLATION OF DIGITAL AND ANALOG PLANES

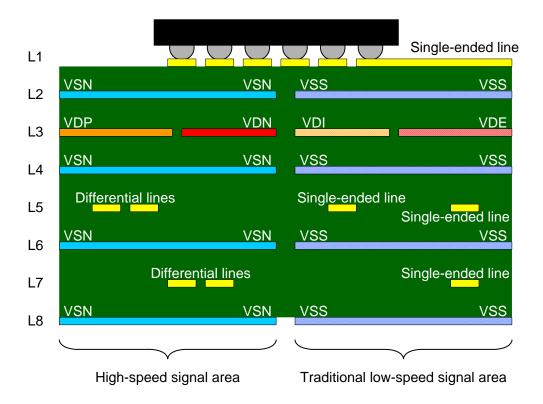

#### **RECOMMENDATION OF LAYER STRUCTURE**

Figure 9 shows an example of the layer structure for an 8-layer printed circuit board, where a chip with high-speed I/O macros implemented is mounted on the layer L1. In this structure, the following points are considered.

- Power and GND plane coupling (See "Power and GND Planes" on page 35 in "Section 2: PCB Layout Guide")

- Power isolation (See "Plane Isolation" on page 36 in "Section 2: PCB Layout Guide")

- Implementation of differential lines on lower layers

<sup>\*</sup> It is assumed that in the PCB above, the signal lines are provided not using through-vias. When using through-vias, not to cause stubs, connect the signals through the layers between the top layers (L1/L2) and the bottom layers (L7/L8).

FIGURE 9. EXAMPLE OF LAYER STRUCTURE FOR 8-LAYER PRINTED CIRCUIT BOARD

#### **RECOMMENDATION OF POWER SUPPLY PIN CONNECTIONS**

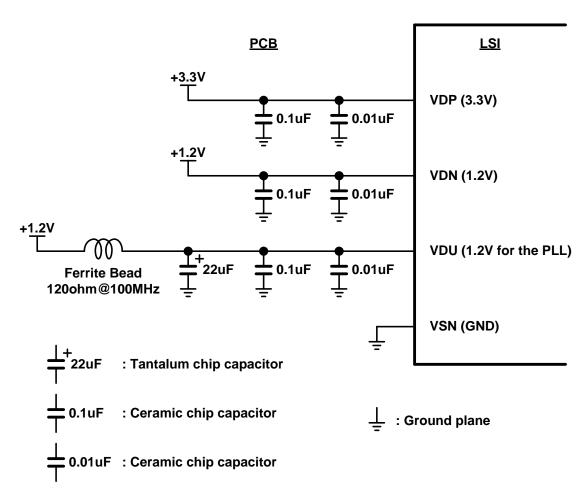

Recommended power supply pin connections are shown in Figure 10.

- Power and ground planes should be used in the PCB.

- Bypass capacitors should be placed near the LSI.

- 0.01uF capacitors should be placed close to the LSI than other capacitors.

FIGURE 10. RECOMMENDED POWER SUPPLY PIN CONNECTIONS

## **Clocking Design**

The reference clock supplied to high-speed I/O macros has a significant influence over the macro operations. To supply the clock having a waveform with less noise, pay attention to the rule in "General Description" on page 30.

#### **REQUIREMENT OF JITTER**

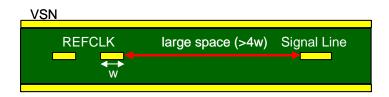

The influence of the noise from power supply and signal lines over the clock line to the chip causes an increase in the jitter of the macros. To avoid crosstalk from the lines in the peripheral area, provide a space of at least four times the clock line width (≥ 4w, w: clock line width) between the clock line and other lines, or take other measures such as providing shield patterning.

Specific requirements may be specified in specification documents. Please make sure to check them.

FIGURE 11. SEPARATION OF REFCLK AND OTHER SIGNALS

## Additional Parts (for ESD and EMI) ESD PROTECTOR

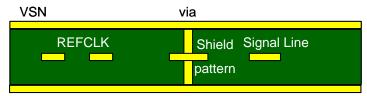

For higher ESD performance, ESD protection elements can be used. They must be limited to those parts specified for HDMI use. (Indispensable) Variations in the characteristics impedance of transmission lines caused by connection patterning, vias, parts mounting pads, and protection elements themselves cause degradation of signal integrity. In the design of printed circuit board, take measures such as making a sample board to check signal integrity. When using ESD protectors, place them near the HDMI connectors.

#### **EMI FILTER**

As an EMI countermeasure, EMI filters can be used.