# SH7216グループ

RJJ06B1173-0100 Rev.1.00 2010.07.30

A/D 変換器、データトランスファコントローラ、

およびシリアルコミュニケーションインタフェースの組み合わせ使用例

### 要旨

本アプリケーションノートは、A/D変換器、データトランスファコントローラ、およびシリアルコミュニケーションインタフェースの組み合わせ使用例について説明しています。

# 動作確認デバイス

SH7216

# 目次

| 1. | はじめに       | 2  |

|----|------------|----|

| 2. | 応用例の説明     | 3  |

|    | 参考プログラムリスト |    |

|    | ★孝ドキュメント   | 46 |

### 1. はじめに

#### 1.1 仕様

データトランスファコントローラを使用して、A/D変換結果を以下の手順でシリアル送信します。

- コンペアマッチ割り込みによりデータトランスファコントローラを起動して、あらかじめ内蔵 RAM に格納した A/D 変換開始設定データを A/D コントロールレジスタへ転送し、A/D 変換器を起動します。

- A/D 変換終了割り込みによりデータトランスファコントローラを起動して、ブロック転送モードで A/D 変換結果を内蔵 RAM に転送します。このとき、チェイン転送を使用して、あらかじめ内蔵 RAM に格納 した送信データエンプティ割り込み許可設定データをシリアルコントロールレジスタへ転送し、送信 データエンプティ割り込みを発生します。

- 送信データエンプティ割り込みによりデータトランスファコントローラを起動して、内蔵 RAM に転送した A/D 変換結果をシリアルコミュニケーションインタフェースへ転送し、調歩同期式モードでシリアル 送信します。

### 1.2 使用機能

- コンペアマッチタイマ (CMT)

- A/D 変換器(ADC)

- データトランスファコントローラ (DTC)

- シリアルコミュニケーションインタフェース (SCI)

#### 1.3 適用条件

マイコン SH7216

動作周波数 内部クロック: 200 MHz

バスクロック: 50 MHz 周辺クロック: 50 MHz AD クロック: 50 MHz

統合開発環境 ルネサス エレクトロニクス製

High-performance Embedded Workshop Ver.4.07.00

C コンパイラ ルネサス エレクトロニクス製 SuperH RISC engine ファミリ

C/C++コンパイラパッケージ Ver.9.03 Release 00

コンパイルオプション High-performance Embedded Workshop でのデフォルト設定

(-cpu=sh2afpu -fpu=single -debug -gbr=auto -global\_volatile=0

-opt\_range=all -infinite\_loop=0 -del\_vacant\_loop=0 -struct\_alloc=1)

#### 1.4 関連アプリケーションノート

本アプリケーションノートに関連するアプリケーションノートを以下に示します。合わせて参照してください。

• SH7216 グループ 初期設定例

# 2. 応用例の説明

#### 2.1 使用機能の動作概要

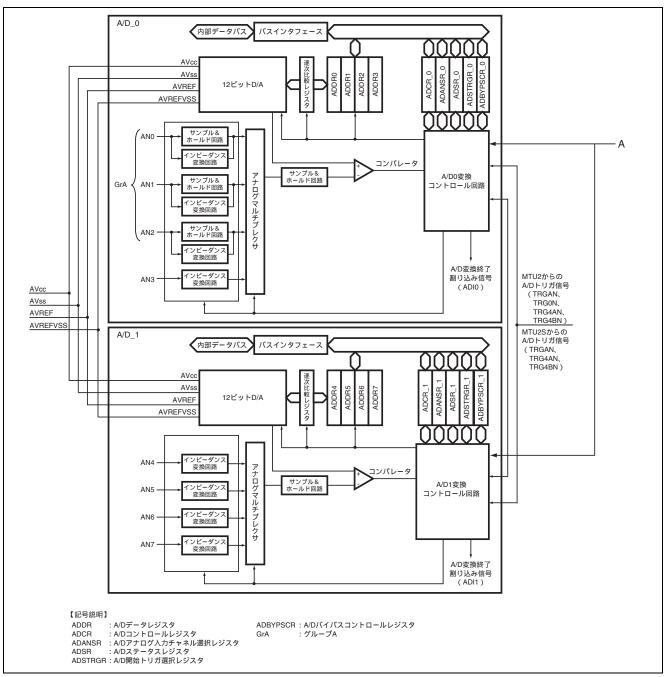

#### 2.1.1 A/D変換器

A/D 変換器は、12 ビットの分解能をもつ 4 チャネル入力の A/D モジュールを 2 つ(A/D\_0、A/D\_1)搭載しています。A/D 変換されたデータは A/D データレジスタ(ADDR)に格納されます。

A/D 変換器の動作モードには1サイクルスキャンモードと連続スキャンモードがあります。1サイクルスキャンモードは、指定した1チャネル以上のA/D変換を1回行った後、A/D変換待機状態になるモードです。連続スキャンモードは、指定した1チャネル以上のA/D変換を繰り返し行うモードです。また、A/D変換終了時にはCPUに対しA/D変換終了割り込みを発生することが可能です。また、A/D変換終了割り込み発生時にはダイレクトメモリアクセスコントローラ/データトランスファコントローラを起動することが可能です。\*

表 1にA/D変換器の仕様を、また 図 1にブロック図を示します。A/D変換器についての詳細は、「SH7214 グループ、SH7216 グループ ユーザーズマニュアル ハードウェア編 A/D変換器(ADC)」の章を参照してください。

【注】\*ダイレクトメモリアクセスコントローラ起動時は CPU に対する割り込みは発生しません。また、ダイレクトメモリアクセスコントローラを起動できるのは A/D モジュール 0 (A/D 0) のみです。

| 項目          | 内容                                                    |

|-------------|-------------------------------------------------------|

| 分解能         | 12 ビット                                                |

| 変換スピード      | 最小変換時間 1 チャネル当たり 1.0 μs(A φ = 50 MHz 動作時)             |

| モジュール数      | 2モジュール (A/D_0、A/D_1)                                  |

| 入力チャネル数     | 8 チャネル(ANO~AN7)                                       |

| 動作モード       | • 1サイクルスキャンモード                                        |

|             | ● 連続スキャンモード                                           |

| サンプル&ホールド機能 | ● チャネル 0~3 共通: 1 回路、チャネル 4~7 共通: 1 回路                 |

|             | <ul><li>チャネル 0~2: それぞれ専用に 1 回路(計 3 回路)</li></ul>      |

| A/D 変換起動要因  | ● ソフトウェア:ADST ビットの設定                                  |

|             | <ul><li>● タイマ:</li></ul>                              |

|             | — マルチファンクションタイマパルスユニット2のTRGAN、TRG0N、<br>TRG4AN、TRG4BN |

|             | — マルチファンクションタイマパルスユニット 2S の TRGAN、                    |

|             | TRG4AN、TRG4BN                                         |

|             | 外部トリガ:ADTRG                                           |

表 1 A/D 変換器の仕様

図 1 A/D 変換器のブロック図

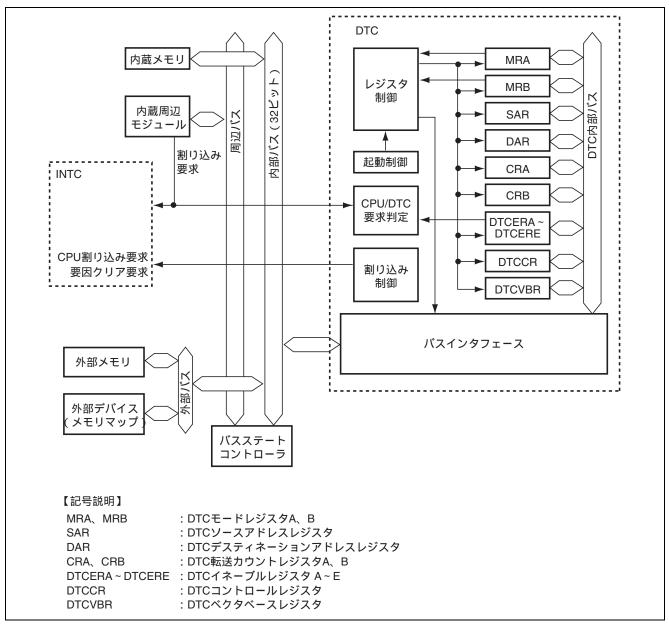

#### 2.1.2 データトランスファコントローラ

データトランスファコントローラは、割り込み要求により起動するデータ転送モジュールです。動作モー ドはノーマル転送モード、リピート転送モード、ブロック転送モードの3種類あり、転送情報をデータ領域 に格納することで、任意のチャネル数のデータ転送を行うことができます。データトランスファコントロー ラが起動すると、データ領域から転送情報をリードしてデータ転送を行い、データ転送後の転送情報をライ トバックします。

データトランスファコントローラについての詳細は、「SH7214 グループ、SH7216 グループ ユーザーズマ ニュアル ハードウェア編 データトランスファコントローラ(DTC)」の章を参照してください。

表 2にデータトランスファコントローラの仕様を、また 図 2にブロック図を示します。

内容 項目 チャネル数 任意のチャネル数を設定可能 • ノーマル転送モード 転送モード リピート転送モード ブロック転送モード 転送回数 ● ノーマル転送モード: 1~65536回 リピート転送モード: 1~256回 ブロック転送モード: 1~65536 回 転送データサイズ バイト、ワード(2バイト)、ロングワード(4バイト) CPU 割り込み要求 ● 1回のデータ転送終了後、CPUに対して割り込み要求可能 ● 指定したデータ転送終了後、CPU に対して割り込み要求可能 外部端子(8要因) 起動要因 内蔵周辺モジュール(55 要因) その他 ● 1つの起動要因に対して複数のデータ転送が可能(チェイン転送) 転送情報のリードスキップモードを設定可能 ● モジュールストップモード設定可能 ● ショートアドレスモード設定可能 バス権解放タイミングを3種類から選択可能

表 2 データトランスファコントローラの仕様

【注】 転送元もしくは転送先の少なくともどちらか一方は必ず内蔵周辺モジュールに設定してください。 外部メモリ、メモリマップト外部デバイス、内蔵メモリ間の転送はできません。

● データトランスファコントローラ起動時の優先順位を2種類から選択可能

図 2 データトランスファコントローラのブロック図

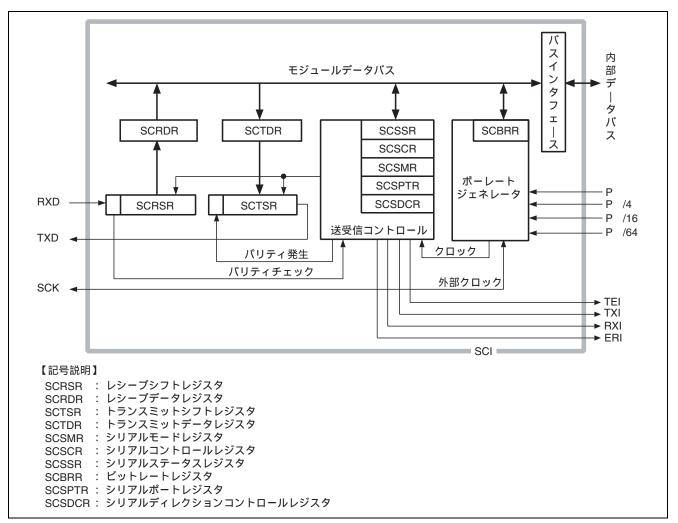

#### 2.1.3 シリアルコミュニケーションインタフェース (調歩同期式モード)

シリアルコミュニケーションインタフェースの調歩同期式モードでは、通信開始を意味するスタートビットと通信終了を意味するストップビットとをデータ付加したキャラクタを送信/受信し、1キャラクタ単位で同期を取りながらシリアル通信を行います。また、各チャネルともに独立した送信部と受信部を備えているで、送信と受信を同時に行うことができます。さらに、送信部と受信部はともにダブルバッファ構造となっているため、シリアルデータの高速連続送信/受信が可能です。

調歩同期式シリアル通信では、通信回線は通常、マーク状態(ハイレベル)に保たれています。シリアルコミュニケーションインタフェースは通信回線を監視し、スペース(ローレベル)になったところをスタートビットとみなしてシリアル通信を開始します。

シリアル通信の1キャラクタは、スタートビット(ローレベル)から始まり、データ(LSBファースト:最下位ビットから)、パリティビット(ハイ/ローレベル)、最後にストップビット(ハイレベル)の順で構成されています。

シリアルコミュニケーションインタフェースについての詳細は、「SH7214 グループ、SH7216 グループユーザーズマニュアル:ハードウェア編 シリアルコミュニケーションインタフェース(SCI)」の章を参照してください。

表 3に、調歩同期式シリアル通信の仕様を、また 図 3にシリアルコミュニケーションインタフェースのブロック図を示します。

| 項目        | 内容                                                         |

|-----------|------------------------------------------------------------|

| チャネル数     | 4 チャネル(SCIO、SCI1、SCI2、SCI4)                                |

| クロックソース   | 内部クロック/外部クロックから選択可能:                                       |

|           | <ul><li>内部クロック: Pø、Pø/4、Pø/16、Pø/64</li></ul>              |

|           | — SCI はボーレートジェネレータのクロックで動作し、 ビットレートの 16 倍                  |

|           | の周波数クロックを出力することが可能。                                        |

|           | ● 外部クロック:SCK 端子入力クロック                                      |

|           | — ビットレートの 16 倍の周波数クロックを入力することが必要。                          |

|           | (内部ボーレートジェネレータを使用しない)                                      |

| データフォーマット | ● 転送データ長:7ビット/8ビットから選択                                     |

|           | ● 転送順序:LSB ファースト/MSB ファースト選択可能                             |

|           | (7 ビットデータ長の場合は LSB ファーストのみ)                                |

| ボーレート     | ● 内部クロック選択時:110 bps ~ 1.5625 Mbps(P <i>φ</i> = 50 MHz 動作時) |

|           | ● 外部クロック選択時:最大 781250 bps                                  |

|           | (P φ = 50 MHz 外部クロック入力 15 MHz 動作時)                         |

| エラーの検出    | フレーミングエラー、パリティエラー、オーバランエラー、                                |

|           | およびブレーク検出可能                                                |

| 割り込み要求    | ● 送信データエンプティ割り込み(TXI)                                      |

|           | ● 受信データフル割り込み (RXI)                                        |

|           | ● 受信エラー割り込み (ERI)                                          |

|           | ● 送信終了割り込み (TEI)                                           |

表 3 調歩同期式シリアル通信の仕様

図 3 シリアルコミュニケーションインタフェースのブロック図

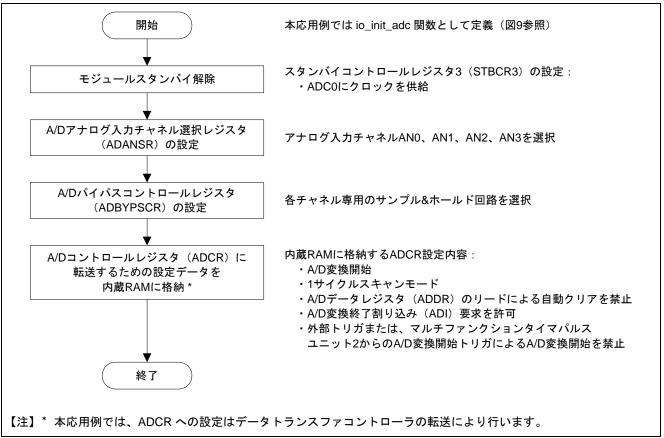

#### 2.2 使用機能の設定手順

#### 2.2.1 A/D変換器の設定手順

図 4に、本応用例で使用するA/D変換器の初期設定フローを示します。なお、各レジスタ設定の詳細は、「SH7214 グループ、SH7216 グループユーザーズマニュアル:ハードウェア編」を参照してください。

図 4 A/D 変換器の初期設定フロー

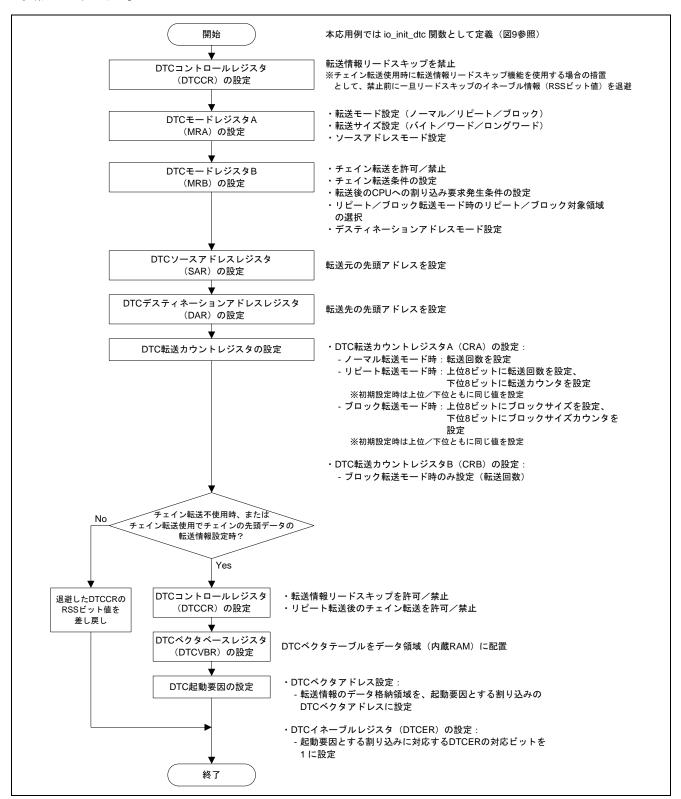

# 2.2.2 データトランスファコントローラの設定手順

図 5に、本応用例で使用するデータトランスファコントローラの初期設定フローを示します。なお、各レジスタ設定の詳細は、「SH7214 グループ、SH7216 グループ ユーザーズマニュアル:ハードウェア編」を参照してください。

図 5 データトランスファコントローラの初期設定フロー

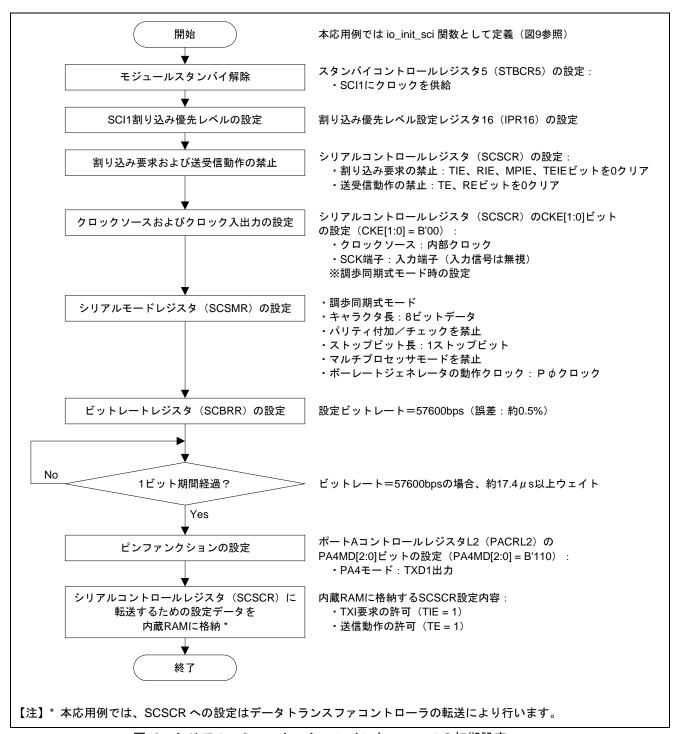

#### 2.2.3 シリアルコミュニケーションインタフェースの設定手順

図 6に本応用例で使用する、シリアルコミュニケーションインタフェースの初期設定フローを示します。 なお、各レジスタ設定の詳細は、「SH7214 グループ、SH7216 グループユーザーズマニュアル:ハードウェ ア編」を参照してください。

図 6 シリアルコミュニケーションインタフェースの初期設定フロー

# 2.3 参考プログラムの処理手順

#### 2.3.1 参考プログラムの動作概要

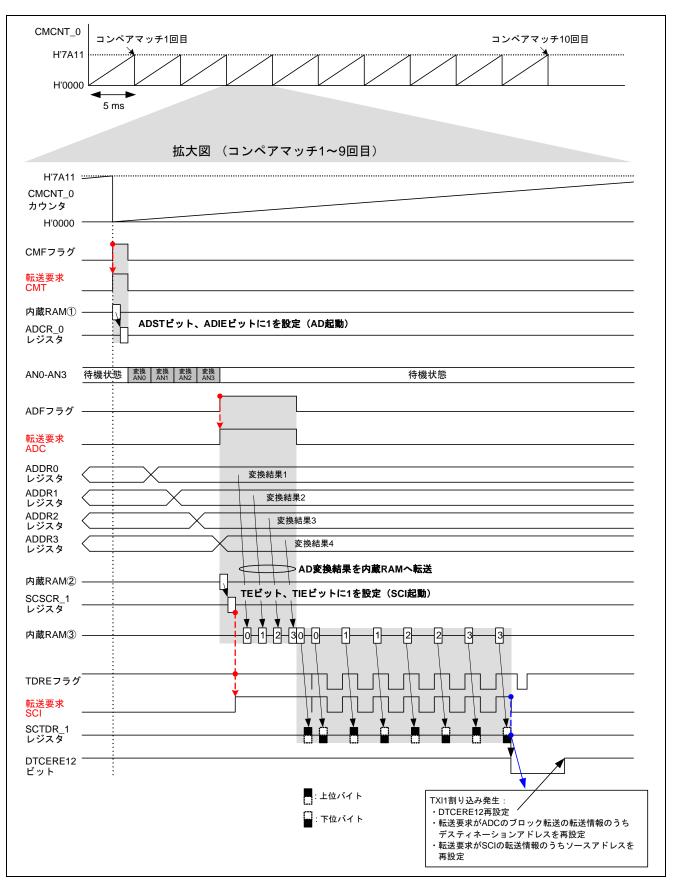

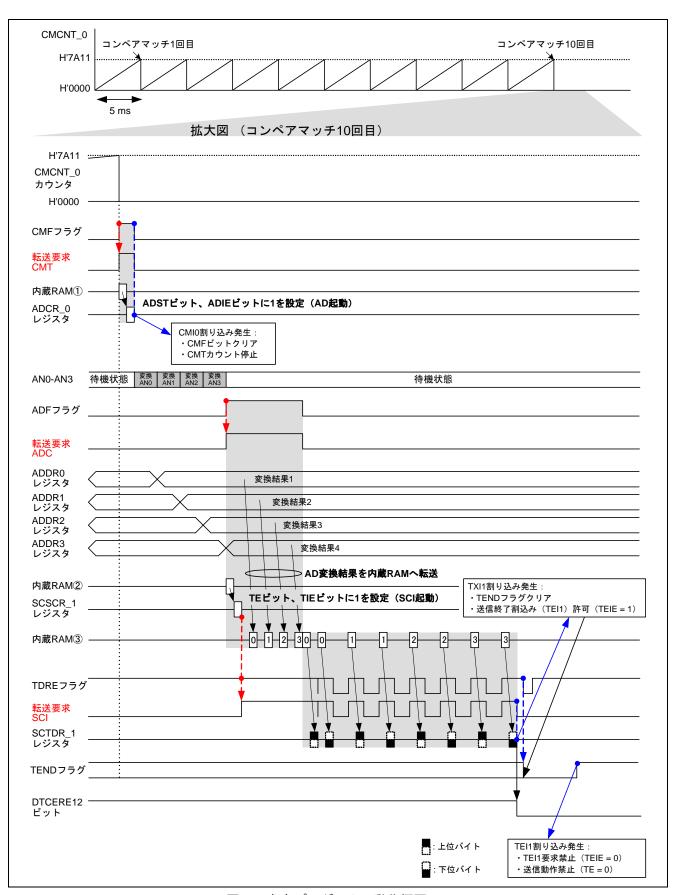

参考プログラムでは、3種類の割り込み起動要因を使用してデータトランスファコントローラを連動的に起動し、4 チャネル分の A/D 変換結果を内蔵 RAM へ格納後、シリアルコミュニケーションインタフェースに転送して連続送信を行います。この一連の動作は 5 ms 周期ごとに計 10 回行います。

以下に、参考プログラムで使用するデータトランスファコントローラの3種類の割り込み起動要因とそれぞれの転送内容について説明します。また、表4に、参考プログラムにおけるデータトランスファコントローラの主な動作仕様を示します。

#### 1. コンペアマッチ割り込み (CMIO)

CMIO を起動要因とするデータトランスファコントローラでは、あらかじめ内蔵 RAM に格納した A/D 変換開始設定データを、A/D コントロールレジスタに転送します。この転送が終了すると、A/D 変換器が起動して 4 チャネル分(ANO~AN3)の A/D 変換を行います。A/D 変換終了後は、A/D 変換終了割り込み(ADIO)が発生します。

#### 2. A/D 変換終了割り込み (ADIO)

ADIO を起動要因とするデータトランスファコントローラでは、チェイン転送を使用して、以下の2種類のデータ転送を行います。

- (1) あらかじめ内蔵 RAM に格納した送信データエンプティ割り込み(TXII)許可設定データをシリアルコントロールレジスタへ転送。

- (2) ブロック転送モードを使用して、4 チャネル分の A/D 変換結果 (A/D データレジスタ 0~3) を内蔵 RAM へ転送。

(1)の転送が終了すると、TXI1 が発生しますが、TXI1 を起動要因とするデータトランスファコントローラ転送は、(1)および(2)の転送終了後に行われます。

#### 3. 送信データエンプティ割り込み (TXI1)

TXII を起動要因とするデータトランスファコントローラでは、内蔵 RAM に転送した 4 チャネル分の A/D 変換結果(計 8 バイト)をトランスミットデータレジスタに転送し、シリアル送信を行います。

| 表 4 参考プログラムにおけるデータトランスファコントローラの主な動作仕村 |

|---------------------------------------|

|---------------------------------------|

| 起動要因         | 転送元       | 転送先           | 転送回数 | 備考                 |

|--------------|-----------|---------------|------|--------------------|

| コンペアマッチ      | 内蔵 RAM    | A/D コントロール    | 10   | 転送元のデータは、          |

| 割り込み (CMIO)  |           | レジスタ(ADCR_0)  |      | コンペアマッチタイマの        |

|              |           |               |      | 初期設定時に内蔵 RAM に格納   |

| A/D 変換終了割り込み | 内蔵 RAM    | シリアルコントロール    | 10   | ● 転送元のデータは、        |

| (ADI0)       |           | レジスタ(SCSCR_1) |      | A/D 変換器の初期設定時に     |

|              |           |               |      | 内蔵 RAM に格納         |

|              |           |               |      | ● チェイン転送使用         |

|              | A/D データ   | 内蔵 RAM        | 10   | ブロック転送モード使用        |

|              | レジスタ      |               |      | ※ブロックサイズ:4ワード      |

|              | (ADDR0∼3) |               |      |                    |

| 送信データエンプティ   | 内蔵 RAM    | トランスミットデータ    | 8    | 転送回数は、4 チャネル分の     |

| 割り込み (TXI1)  |           | レジスタ(SCTDR_1) |      | A/D 変換結果(計 8 バイト)の |

|              |           |               |      | 連続シリアル送信回数に相当      |

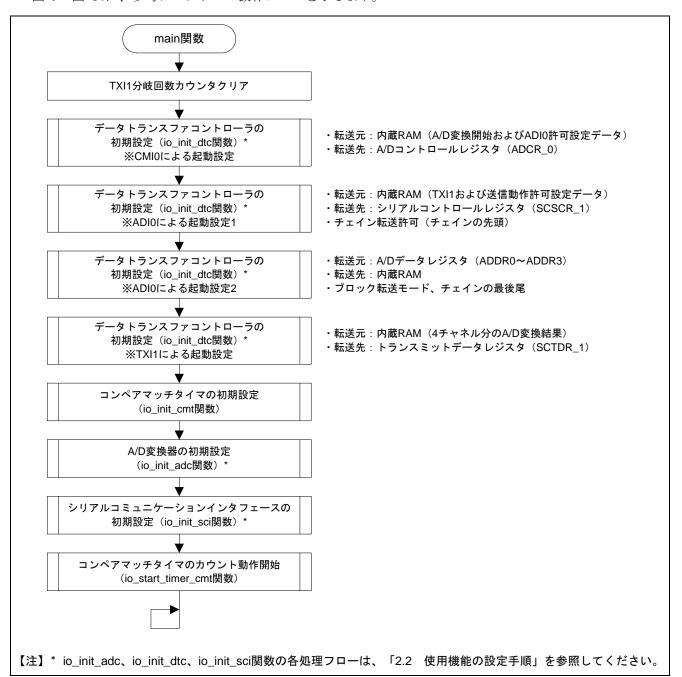

参考プログラムは、CPU リセット後、メイン処理にてコンペアマッチタイマ、A/D 変換器、データトランスファコントローラ、およびシリアルコミュニケーションインタフェースの初期設定を行います。

A/D 変換器の初期設定では、A/D 変換開始および A/D 変換終了割り込み(ADIO)を許可するための A/D コントロールレジスタ(ADCR\_O)への設定データを内蔵 RAM に格納します。データトランスファコントローラの初期設定では、使用する 3 種類の起動要因それぞれに対し転送情報の設定を行います。シリアルコミュニケーションインタフェースの初期設定では、送信データエンプティ割り込み(TXII)および送信動作を許可するためのシリアルコントロールレジスタ(SCSCR 1)への設定データを内蔵 RAM に格納します。

上記の初期設定終了後、参考プログラムはコンペアマッチタイマのカウント動作を開始します。カウント動作開始後、5 ms 周期ごとにコンペアマッチ割り込み(CMIO)要求が発生します。この割り込み要求を最初のデータトランスファコントローラの起動要因として、内蔵 RAM に格納した A/D 変換開始および ADIOを許可するための設定データを ADCR\_0 へ転送します。

上記の転送終了後、A/D 変換器が起動して 4 チャネル分(ANO~AN3)の A/D 変換を行います。A/D 変換終了後は ADI0 要求が発生します。この割り込み要求を 2 番目のデータトランスファコントローラの起動要因として、内蔵 RAM に格納した TXII および送信動作を許可するための設定データを SCSCR\_1 へ転送します。このとき、さらにブロック転送モードに設定したチェイン転送を使用して、4 チャネル分の A/D 変換結果を内蔵 RAM へ転送します。

上記の転送終了後、TXI1 要求(計 8 回)を 3 番目のデータトランスファコントローラの起動要因として、内蔵 RAM に転送した 4 チャネル分の A/D 変換結果(計 8 バイト)をトランスミットデータレジスタ (SCTDR 1) へ転送し、シリアル送信出力を行います。

4 チャネル分の A/D 変換結果のシリアル送信出力が終了すると、CPU に対し TXI1 要求が発生します。参考プログラムでは、TXI1 の割り込み処理内で、データトランスファコントローラの転送情報を再設定します。これにより、5 ms 周期で CMI0 要求が発生するたびに、参考プログラムは上記の一連の転送処理を繰り返します。

参考プログラムは、上記の一連の転送処理を、CMIOおよびADIOの起動要因で使用するデータトランスファコントローラの転送回数(10回)分行います。10回分の転送処理を終了すると、参考プログラムはTXI1の割り込み処理内でトランスミットエンド(TEND)フラグを0クリアし、送信終了割り込み(TEII)要求を許可に設定した後、TEIIの割り込み処理内で送信動作を禁止に設定します。\*

上記の処理をすべて終了すると、CPU に対し CMIO 要求が発生します。参考プログラムでは、CMIO の割り込み処理内でカウント動作を停止します。

図 7および 図 8に、参考プログラムの動作概要を示します。

【注】\* TXI を割り込み要因としてデータトランスファコントローラを起動し、SCTDR へデータを書き込ん だ場合、TEND フラグは不定となるため、TEND フラグを送信終了フラグとして使用できません。こ のため、参考プログラムでは TEI を使用して送信終了を判断しています。

図 7 参考プログラムの動作概要 (1)

図 8 参考プログラムの動作概要 (2)

#### 2.3.2 A/D変換器のレジスタ設定

表 5に、A/D変換器のレジスタ設定例を示します。

なお、本設定では、A/D変換終了割り込み発生を許可していますが、データトランスファコントローラの起動時にチェイン転送を行うため、CPUに対する割り込みは発生しません。

表 5 A/D 変換器のレジスタ設定例

| レジスタ名                                | アドレス        | 設定値   | 機能                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイコントロール<br>レジスタ 3(STBCR3)        | H'FFFE 0408 | H'7A  | <ul><li>MSTP32 = "0":</li><li>A/D_0 にクロック供給</li></ul>                                                                                                                                                                                                                                                                                                                                    |

| A/D コントロールレジスタ_0<br>(ADCR_0)*        | H'FFFF E800 | H'90* | <ul> <li>ADST = "1":         A/D 変換開始</li> <li>ADCS = "0":         1 サイクルスキャンモードを選択</li> <li>ACE = "0":         ADDR レジスタのリードによる ADDR レジスタの自動クリアを禁止</li> <li>ADIE = "1":         A/D 変換終了割り込み発生の許可</li> <li>TRGE = "0":         外部トリガまたは、マルチファンクションタイマパルスユニット2からの A/D 変換開始トリガによるA/D 変換の開始を禁止</li> <li>EXTRG = "0":         マルチファンクションタイマパルスユニット2からの A/D 変換開始トリガにより A/D 変換器を起動</li> </ul> |

| A/D アナログ入力チャネル<br>選択レジスタ_0(ADANSR_0) | H'FFFF E820 | H'0F  | <ul> <li>ANS3 = "1":</li> <li>ANS2 = "1":</li> <li>ANS1 = "1":</li> <li>ANS0 = "1":</li> <li>アナログ入力端子 AN0~AN3 を選択</li> </ul>                                                                                                                                                                                                                                                             |

| A/D バイパスコントロール<br>レジスタ_0(ADBYPSCR_0) | H'FFFF E830 | H'01  | ● SH = "1":<br>各チャネル専用のサンプル&ホールド<br>回路を選択                                                                                                                                                                                                                                                                                                                                                |

【注】\* 本応用例では初期化時に設定値を内蔵 RAM に格納し、レジスタへの設定は CMIO を起動要因とするデータトランスファコントローラの転送により行います。

# 2.3.3 データトランスファコントローラのレジスタ設定

表 6~表 10に、データトランスファコントローラのレジスタ設定例を示します。

表 6 データトランスファコントローラのレジスタ設定例(共通)

| レジスタ名                       | アドレス        | 設定値         | 機能                                                                                                        |

|-----------------------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------|

| DTC イネーブルレジスタ A<br>(DTCERA) | H'FFFE 6000 | H'0088      | <ul> <li>DTCE7 = "1":<br/>割り込み起動要因を ADIO に設定</li> <li>DTCE3 = "1":<br/>割り込み起動要因を CMIO に設定</li> </ul>      |

| DTC イネーブルレジスタ E<br>(DTCERE) | H'FFFE 6008 | H'1000      | ● DTCE12 = "1":<br>割り込み起動要因を TXI1 に設定                                                                     |

| DTC コントロールレジスタ<br>(DTCCR)   | H'FFFE 6010 | H'00        | <ul> <li>RRS = "0":</li> <li>転送情報リードスキップを行わない</li> <li>RCHNE = "0":</li> <li>リピート転送後のチェイン転送を禁止</li> </ul> |

| DTC ベクタベースレジスタ<br>(DTCVBR)  | H'FFFE 6014 | H'FFF8 5000 | DTC ベクタテーブルアドレス算出時の<br>ベースアドレス                                                                            |

#### 表 7 データトランスファコントローラのレジスタ設定例(起動要因: CMIO)

| レジスタ名                              | アドレス*       | 設定値         | 機能                                                                                                                                                                                                                                         |

|------------------------------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTC モードレジスタ A<br>(MRA)             | H'FFF8 4000 | H'00        | <ul> <li>MD[1:0] = "B'00": ノーマル転送モード</li> <li>Sz[1:0] = "B'00": バイトサイズ転送</li> <li>SM[1:0] = "B'00": 転送後 SAR は固定</li> </ul>                                                                                                                 |

| DTC モードレジスタ B<br>(MRB)             | H'FFF8 4001 | H'00        | <ul> <li>CHNE = "0":     チェイン転送禁止</li> <li>CHNS = "0":     連続してチェイン転送を行う</li> <li>DISEL = "0":     指定した回数分のデータ転送後、CPUに対し割り込み要求を発生</li> <li>DTS = "0":     デスティネーション側がリピート領域またはブロック領域</li> <li>DM[1:0] = "B'00":     転送後 DAR は固定</li> </ul> |

| DTC ソースアドレスレジスタ<br>(SAR)           | H'FFF8 4004 | H'FFF8 4108 | 転送元のアドレス:<br>A/D_0 の変換開始設定データ(H'90)<br>を格納した内蔵 RAM 上のアドレス                                                                                                                                                                                  |

| DTC デスティネーション<br>アドレスレジスタ<br>(DAR) | H'FFF8 4008 | H'FFFF E800 | 転送先のアドレス:<br>A/D コントロールレジスタ_0<br>(ADCR_0)                                                                                                                                                                                                  |

| DTC 転送カウントレジスタ A<br>(CRA)          | H'FFF8 400C | H'000A      | 転送回数:10 回                                                                                                                                                                                                                                  |

<sup>【</sup>注】\* 本応用例における転送情報のメモリ配置先であり、ユーザ側の設定に依存します。

# 表 8 データトランスファコントローラのレジスタ設定例 (起動要因: ADIO) (1)

| レジスタ名                              | アドレス*       | 設定値         | 機能                                                                                                                                                                                                                                               |

|------------------------------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTC モードレジスタ A<br>(MRA)             | H'FFF8 4010 | H'00        | <ul> <li>MD[1:0] = "B'00":         ノーマル転送モード</li> <li>Sz[1:0] = "B'00":         バイトサイズ転送</li> <li>SM[1:0] = "B'00":         転送後 SAR は固定</li> </ul>                                                                                               |

| DTC モードレジスタ B<br>(MRB)             | H'FFF8 4011 | H'80        | <ul> <li>CHNE = "1":     チェイン転送許可</li> <li>CHNS = "0":     連続してチェイン転送を行う</li> <li>DISEL = "0":     指定した回数分のデータ転送後、     CPU に対し割り込み要求を発生</li> <li>DTS = "0":     デスティネーション側がリピート領域またはブロック領域</li> <li>DM[1:0] = "B'00":     転送後 DAR は固定</li> </ul> |

| DTC ソースアドレスレジスタ<br>(SAR)           | H'FFF8 4014 | H'FFF8 410C | 転送元のアドレス:<br>TXI1 の許可設定データ(H'A0)<br>を格納した内蔵 RAM 上のアドレス                                                                                                                                                                                           |

| DTC デスティネーション<br>アドレスレジスタ<br>(DAR) | H'FFF8 4018 | H'FFFF 8804 | 転送先のアドレス:<br>シリアルコントロールレジスタ_1<br>(SCSCR_1)                                                                                                                                                                                                       |

| DTC 転送カウントレジスタ A<br>(CRA)          | H'FFF8 401C | H'000A      | 転送回数:10 回                                                                                                                                                                                                                                        |

【注】\* 本応用例における転送情報のメモリ配置先であり、ユーザ側の設定に依存します。

# 表 9 データトランスファコントローラのレジスタ設定例 (起動要因: ADIO) (2)

| レジスタ名                              | アドレス*       | 設定値         | 機能                                                                                                                                                                                                                               |

|------------------------------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTC モードレジスタ A<br>(MRA)             | H'FFF8 4020 | H'98        | <ul> <li>MD[1:0] = "B'10":         ブロック転送モード</li> <li>Sz[1:0] = "B'01":         ワードサイズ転送</li> <li>SM[1:0] = "B'10":         転送後 SAR をインクリメント</li> </ul>                                                                          |

| DTC モードレジスタ B<br>(MRB)             | H'FFF8 4021 | H'18        | <ul> <li>CHNE = "0":     チェイン転送禁止</li> <li>CHNS = "0":     連続してチェイン転送を行う</li> <li>DISEL = "0":     指定した回数分のデータ転送後、CPUに対し割り込み要求を発生</li> <li>DTS = "1":     ソース側がブロック領域</li> <li>DM[1:0] = "B'10":     転送後 DAR をインクリメント</li> </ul> |

| DTC ソースアドレスレジスタ<br>(SAR)           | H'FFF8 4024 | H'FFFF E840 | 転送元のアドレス:<br>A/D データレジスタ 0(ADDR0)                                                                                                                                                                                                |

| DTC デスティネーション<br>アドレスレジスタ<br>(DAR) | H'FFF8 4028 | H'FFF8 4102 | 転送先のアドレス:<br>A/D 変換結果(ANO~AN3)の格納先<br>(内蔵 RAM)の先頭アドレス                                                                                                                                                                            |

| DTC 転送カウントレジスタ A<br>(CRA)          | H'FFF8 402C | H'0404      | <ul> <li>CRAH(上位8ビット):         ブロックサイズ=4ワード</li> <li>CRAL(下位8ビット):         ブロックサイズカウンタ=4         ※初期設定時はブロックサイズと同じ値</li> </ul>                                                                                                   |

| DTC 転送カウントレジスタ B<br>(CRB)          | H'FFF8 402E | H'000A      | 転送回数:10 回                                                                                                                                                                                                                        |

【注】\* 本応用例における転送情報のメモリ配置先であり、ユーザ側の設定に依存します。

表 10 データトランスファコントローラのレジスタ設定例(起動要因: TXI1)

| レジスタ名                              | アドレス*       | 設定値         | 機能                                                                                                                                                                                                                                                |

|------------------------------------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTC モードレジスタ A<br>(MRA)             | H'FFF8 4030 | H'08        | <ul> <li>MD[1:0] = "B'00":         ノーマル転送モード</li> <li>Sz[1:0] = "B'00":         バイトサイズ転送</li> <li>SM[1:0] = "B'10":         転送後 SAR をインクリメント</li> </ul>                                                                                           |

| DTC モードレジスタ B<br>(MRB)             | H'FFF8 4031 | H'00        | <ul> <li>CHNE = "0":     チェイン転送禁止</li> <li>CHNS = "0":     連続してチェイン転送を行う</li> <li>DISEL = "0":     指定した回数分のデータ転送後、     CPU に対し割り込み要求を発生</li> <li>DTS = "0":     デスティネーション側がリピート領域 またはブロック領域</li> <li>DM[1:0] = "B'00":     転送後 DAR は固定</li> </ul> |

| DTC ソースアドレスレジスタ<br>(SAR)           | H'FFF8 4034 | H'FFF8 4102 | 転送元のアドレス:<br>アナログ入力チャネル ANO〜AN3 の<br>A/D 変換結果を格納した内蔵 RAM 上の<br>先頭アドレス                                                                                                                                                                             |

| DTC デスティネーション<br>アドレスレジスタ<br>(DAR) | H'FFF8 4038 | H'FFFF 8806 | 転送先のアドレス:<br>トランスミットデータレジスタ_1<br>(SCTDR_1)                                                                                                                                                                                                        |

| DTC 転送カウントレジスタ A<br>(CRA)          | H'FFF8 403C | H'0008      | 転送回数:8回                                                                                                                                                                                                                                           |

<sup>【</sup>注】\* 本応用例における転送情報のメモリ配置先であり、ユーザ側の設定に依存します。

# 2.3.4 シリアルコミュニケーションインタフェースのレジスタ設定

表 11に、シリアルコミュニケーションインタフェースのレジスタ設定例を示します。

表 11 シリアルコミュニケーションインタフェースのレジスタ設定例

| レジスタ名                          | アドレス        | 設定値    | 機能                                                                                                                                                                                                                                        |

|--------------------------------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| スタンバイコントロール<br>レジスタ 5(STBCR5)  | H'FFFE 0418 | H'BF   | MSTP56 = "0":     SCI1 ヘクロック供給                                                                                                                                                                                                            |

| 割り込み優先レベル設定<br>レジスタ(IPR16)     | H'FFFE 0C14 | H'0F00 | SCI1 割り込み優先レベル: 15                                                                                                                                                                                                                        |

| ポートAコントロール<br>レジスタ L2(PACRL2)  | H'FFFE 3814 | H'0006 | ● PA4MD[2:0] = " B'110" :<br>PA4 端子を TXD1 出力に設定                                                                                                                                                                                           |

| シリアルモードレジスタ_1<br>(SCSMR_1)     | H'FFFF 8800 | H'00   | <ul> <li>C/A = "0":<br/>調歩同期式モード</li> <li>CHR = "0":<br/>8 ビットデータ</li> <li>PE = "0":<br/>パリティビットの付加、およびチェックを禁止</li> <li>STOP = "0":<br/>1 ストップビット</li> <li>MP = "0":<br/>マルチプロセッサモードを禁止</li> <li>CKS[1:0] = "B'00":<br/>P クロック</li> </ul> |

| ビットレートレジスタ_1<br>(SCBRR_1)      | H'FFFF 8802 | H'1A   | 設定ビットレート:57870.37 bps<br>(想定ビットレートは 57600 bps)                                                                                                                                                                                            |

| シリアルコントロール<br>レジスタ_1(SCSCR_1)* | H'FFFF 8804 | H'A0*  | <ul> <li>TIE = "1":     送信データエンプティ割り込み(TXI)     要求を許可</li> <li>TE = "1":     送信動作を許可</li> <li>CKE[1:0] = "B'00":     内部クロック/SCK 端子は入力端子     (入力信号は無視)</li> </ul>                                                                          |

【注】\* 本応用例では初期化時に設定値を内蔵 RAM に格納し、レジスタへの設定は ADIO を起動要因とする データトランスファコントローラの転送により行います。

#### 2.3.5 参考プログラムの動作フロー

図 9~図 14に、参考プログラムの動作フローを示します。

図 9 メイン処理フロー

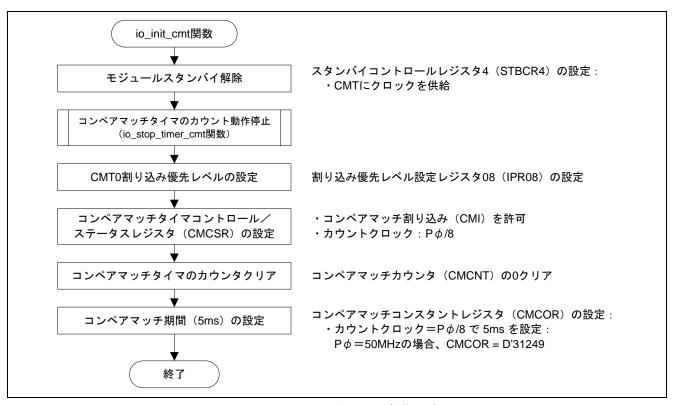

図 10 コンペアマッチタイマの初期設定フロー

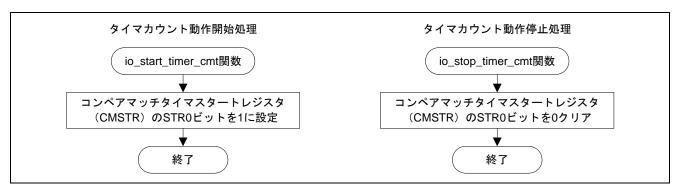

図 11 コンペアマッチタイマのカウント動作制御処理フロー

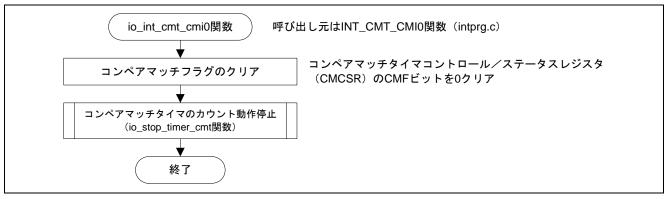

図 12 コンペアマッチ割り込み (CMIO) 処理フロー

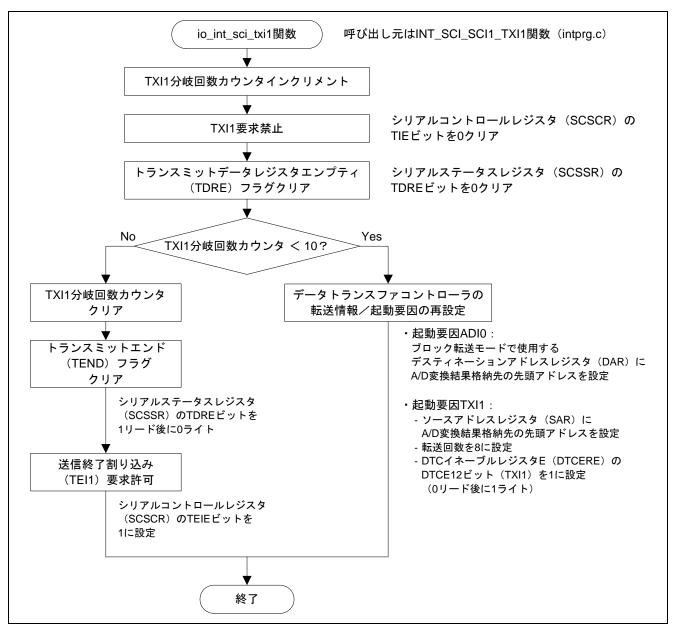

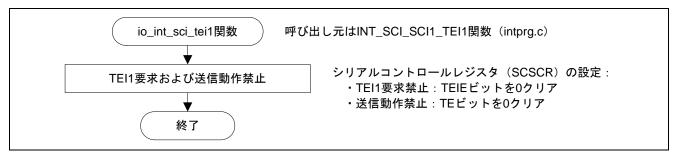

図 13 送信データエンプティ割り込み(TXI1)処理フロー

図 14 送信終了割り込み (TEI1) 処理フロー

### 3. 参考プログラムリスト

# 3.1 サンプルプログラムリスト "main.c" (1)

```

1

DISCLAIMER

2

This software is supplied by Renesas Electronics Corp. and is only

4

5

intended for use with Renesas products. No other uses are authorized.

6

7

* This software is owned by Renesas Electronics Corp. and is protected under

8

all applicable laws, including copyright laws.

* THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

10

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

12

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

13

PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

* DISCLAIMED.

14

15

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

16

17

ELECTRONICS CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

18

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

19

AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

20

21

2.2

* Renesas reserves the right, without notice, to make changes to this

software and to discontinue the availability of this software.

23

24

By using this software, you agree to the additional terms and

25

conditions found by accessing the following link:

http://www.renesas.com/disclaimer

26

********************

2.7

28

* Copyright (C) 2010 Renesas Electronics Corporation. All rights reserved.

*************************

/*""FILE COMMENT""******** Technical reference data *****************************

30

31

System Name : SH7216 Sample Program

32

File Name : main.c

Abstract : ADC+DTC+SCI Module Application

33

Version : 1.00.00

34

* Device

35

: SH7216

* Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

: C/C++ compiler package for the SuperH RISC engine family

37

38

(Ver.9.03 Release00).

* OS

39

: None

40

H/W Platform: ROK572167 (CPU board)

41

Description :

************************

42

43

* History

: Jul.30,2010 Ver.1.00.00

44

#include <machine.h>

45

46

#include "iodefine.h"

#include "dtc.h"

47

48

```

# 3.2 サンプルプログラムリスト "main.c" (2)

```

49

/* ==== Prototype declaration ==== */

50

void main(void);

51

void io_init_adc(void);

52

void io_init_dtc(DTC_TRANS_INFO *dtc_info, unsigned long src,

53

unsigned long dst, unsigned long count, unsigned long mode);

void io_init_sci(void);

54

55

void io_init_cmt(void);

void io_start_timer_cmt(void);

56

57

void io_stop_timer_cmt(void);

58

void io_int_cmt_cmi0(void);

59

void io_int_sci_txil(void);

void io_int_sci_teil(void);

60

61

62

/* ==== Global variable ==== */

int gCnt_TXI; /* TXI1 分岐回数カウンタ */

63

unsigned long *gData_DTCvect = (unsigned long *)DTC_VECT_BASE; /* DTC ベクタテーブル */

64

/* ---- DTC 転送用データ格納先(URAM) ---- */

66

#pragma section DTCDATA

unsigned char gData_ADstart; /* A/D変換開始データ */

67

68

unsigned char gData_TXIenable; /* TXI 許可データ */

unsigned short gData_ADconv[4]; /* A/D変換データ(偶数番地に配置) */

69

70

#pragma section

71

72

73

: サンプルプログラムメイン

* Outline

74

*_____

75

76

: "dtc.h"

77

78

* Declaration : void main(void);

*-----

79

80

81

*_____

82

* Argument

: void

83

84

* Return Value : void

85

86

: None

87

88

void main(void)

89

/* ==== TXI1 分岐回数カウンタクリア ==== */

90

91

gCnt_TXI = 0;

92

```

# 3.3 サンプルプログラムリスト "main.c" (3)

```

/* ==== DTC 設定 ==== */

93

/* ---- CMIOによる起動設定 ---- */

94

io_init_dtc(&DTC_CMIO, /* 転送情報格納領域の参照先アドレス */

(unsigned long)&gData_ADstart, /* 転送元:URAM */

96

/* 転送先:ADCR */

97

(unsigned long)&ADC0.ADCR,

98

DTC_COUNT_LINK, /* DTC 連動回数 */

99

(DTC_TRG_CMI0 | DTC_MODE_NORMAL | DTC_SIZE_BYTE)

/* 起動要因 CMIO、ノーマル転送モード、バイトサイズ転送 */

100

101

);

102

/* ---- ADIOによる起動設定(チェイン転送) ---- */

103

io_init_dtc(&DTC_ADIO_CHN1, /* 転送情報格納領域の参照先アドレス */

(unsigned long)&gData_TXIenable, /* 転送元:URAM */

104

105

(unsigned long)&SCI1.SCSCR, /* 転送先:SCSCR */

DTC_COUNT_LINK, /* DTC 連動回数 */

106

(DTC_TRG_ADIO | DTC_MODE_NORMAL | DTC_SIZE_BYTE | DTC_CHN_INITIAL)

107

/* 起動要因 ADIO、ノーマル転送モード、バイトサイズ転送、 */

108

/* チェイン転送使用(チェインの先頭)

109

110

);

/* 転送情報格納領域の参照先アドレス */

111

io_init_dtc(&DTC_ADI0_CHN2,

112

(unsigned long)&ADC0.ADDR0, /* 転送元:ADDR0-ADDR3 */

(unsigned long)&gData_ADconv[0], /* 転送先:URAM */

113

(DTC COUNT LINK | DTC COUNT BLKSIZE), /* DTC 連動回数、ブロックサイズ指定 */

114

(DTC_TRG_ADIO | DTC_MODE_BLOCK | DTC_SIZE_WORD | DTC_SRC_UP | DTC_DST_UP |

115

116

DTC_TARGET_SRC | DTC_CHN_FINAL)

117

/* 起動要因 ADIO、ブロック転送モード、ワードサイズ転送、

/* 転送後 SAR, DAR ともにインクリメント、ソース側がブロック領域、 */

118

/* チェイン転送使用(チェインの最後尾)

119

120

);

121

/* ---- TXI1による起動設定 ---- */

io_init_dtc(&DTC_TXI1, /* 転送情報格納領域の参照先アドレス */

122

(unsigned long)&gData_ADconv[0], /* 転送元:URAM */

123

(unsigned long)&SCI1.SCTDR, /* 転送先:SCTDR */

124

DTC COUNT SCI, /* シリアルデータ転送回数 */

125

126

(DTC_TRG_TXI1 | DTC_MODE_NORMAL | DTC_SIZE_BYTE | DTC_SRC_UP)

127

/* 起動要因 TXI1、ノーマル転送モード、バイトサイズ転送、 */

/* 転送後 SAR をインクリメント

128

129

);

130

/* ==== CMT 設定 ==== */

131

132

io_init_cmt();

133

/* ==== ADC 設定 ==== */

134

135

io_init_adc();

136

/* ==== SCI 設定 ==== */

137

138

io_init_sci();

139

```

# 3.4 サンプルプログラムリスト "main.c" (4)

```

/* ==== CMT タイマカウント動作開始 ==== */

140

141

io_start_timer_cmt();

142

143

while(1)

144

/* Dead loop */

145

}

146

}

147

148

: ADC 設定

* Outline

150

*-----

151

152

* Include

: "iodefine.h"

153

* Declaration : void io_init_adc(void);

154

155

* Description : ADCO の初期化処理を行います。

157

:・動作モード:1サイクルスキャン

: ・アナログ入力チャネル: ANO, AN1, AN2, AN3

158

159

:・変換回路:サンプル&ホールド回路

160

: サンプルプログラムでは、ADCRへの設定(A/D変換開始および

161

: ADI 要求許可)は DTC 転送により行います。

162

163

: このため本関数にて転送元の設定データを URAM に格納しています。

164

* Argument

165

: void

166

*_____

167

* Return Value : void

168

169

170

171

void io_init_adc(void)

172

{

/* ==== モジュールスタンバイ解除 ==== */

173

174

STB.CR3.BIT._ADC0 = 0; /* ADC0 にクロックを供給 */

175

/* ==== A/Dアナログ入力チャネル選択レジスタ(ADANSR)設定 ==== */

176

177

ADCO.ADANSR.BYTE = 0x0f; /* アナログ入力チャネル ANO~AN3 を選択 */

178

/* ==== A/D バイパスコントロールレジスタ(ADBYPSCR)設定 ==== */

179

/* サンプル&ホールド回路を選択 */

ADCO.ADBYPSCR.BIT.SH = 1;

180

181

```

# 3.5 サンプルプログラムリスト "main.c" (5)

```

/* ==== A/D コントロールレジスタ(ADCR)に転送するための設定データを URAM に格納 ==== */

182

183

gData_ADstart = 0x90;

184

185

bit7 : ADST = 1 ---- A/D 変換開始

bit6 : ADCS = 0 ---- 1 サイクルスキャン

186

bit5 : ACE = 0 ---- ADDR のリードによる ADDR の自動クリアを禁止

187

bit4 : ADIE = 1 ---- A/D変換終了割り込み(ADI)要求の許可

188

bit3-2: Reserved(0)

189

bit1 : TRGE = 0 ---- 外部トリガまたは、MTU2/MTU2SからのA/D変換

190

開始トリガによる A/D 変換の開始を禁止

bit0 : EXTRG = 0 --- MTU2/MTU2SからのA/D変換開始トリガにより

192

A/D 変換器を起動

193

194

* /

195

}

196

197

199

* Outline

: DTC 設定

200

*-----

201

: "iodefine.h" and "dtc.h"

* Include

*-----

* Declaration : void io_init_dtc(DTC_TRANS_INFO *dtc_info,

203

204

unsigned long src,

205

unsigned long dst,

206

unsigned long count,

207

unsigned long mode);

208

*_____

* Description : DTC の初期化処理を行います。

209

: 引数 src,dst,count,mode に指定した転送情報を、引数 *dtc_info

210

: に指定した DTC 転送情報レジスタ (MRA, MRB, SAR, DAR, CRA, CRB) 配置先へ

211

: 設定します。

212

: チェイン転送不使用時、またはチェイン転送使用でチェインの先頭

213

: データの転送情報設定時は、引数 *dtc info に指定した転送情報

214

: 配置先の参照アドレスを、使用する割り込み起動要因の DTC ベクタ

215

216

: テーブルに登録します。

217

* Argument

: ・DTC_TRANS_INFO *dtc_info ; I/O : DTC 転送情報レジスタ配置先へ

218

219

: の参照アドレス

: •unsigned long src

; I : SAR に設定するアドレス

220

221

: •unsigned long dst

; I : DAR に設定するアドレス

: ·unsigned long count ; I : 転送回数

222

223

: ·unsigned long mode

; I :

: 転送モード/転送サイズ/起動要因トリガ等の DTC 設定情報を

224

: サンプルプログラムのヘッダファイル "dtc.h" にてマクロ定義

225

しているパラメータで指定します。

226

227

パラメータを複数指定する場合は、OR 演算子 "|" で区切って

228

指定してください。

229

230

* Return Value : void

```

# 3.6 サンプルプログラムリスト "main.c" (6)

```

* Note

: ・本関数を実行する際、使用する起動要因モジュールの割り込みは

232

禁止にしてください。

233

:・引数 *dtc_info に指定する転送情報レジスタ配置先の

234

参照アドレスは、4バイトアライメントにしてください。

235

: ・ブロック転送モードを使用する場合は、引数 count の

236

: bit23~bit16 にブロックサイズを指定し、さらに

237

238

: 下位 16 ビット(bit15~bit0)に転送回数を指定してください。

239

240

void io_init_dtc(DTC_TRANS_INFO *dtc_info, unsigned long src,

241

unsigned long dst, unsigned long count, unsigned long mode)

242

{

243

unsigned long chain_info;

244

unsigned char set_mra, set_mrb, set_dtccr, f_rrs;

245

/* ---- DTC 設定情報を第5引数より抽出 ---- */

246

set_mra = (unsigned char)((mode >> 8) & 0x000000fc); /* MRA 設定情報 */

247

248

set_mrb = (unsigned char)(mode & 0x000000fc); /* MRB 設定情報 */

249

set_dtccr = (unsigned char)((mode >> 24) & 0x00000018);

/* DTCCR 設定情報 */

chain_info = mode & 0x00ffc0c3; /* チェイン転送情報 */

250

251

/* **** 転送情報設定 **** */

252

/* ==== DTC コントロールレジスタ(DTCCR)設定 ==== */

253

/* ---- 転送情報リードスキップイネーブル情報退避(チェイン転送使用時の措置) ---- */

254

255

f_rrs = DTC.DTCCR.BIT.RRS;

256

/* ---- 転送情報リードスキップ禁止 ---- */

DTC.DTCCR.BIT.RRS = 0;

257

/* ==== DTC モードレジスタ A (MRA)設定 ==== */

258

259

dtc_info->MRA = set_mra;

/* ==== DTCモードレジスタB (MRB)設定 ==== */

260

dtc info->MRB = set mrb;

261

/* ==== DTC ソースアドレスレジスタ(SAR)設定 ==== */

262

dtc info->SAR = src;

/* ==== DTC デスティネーションアドレスレジスタ(DAR)設定 ==== */

264

265

dtc_info->DAR = dst;

/* ==== DTC 転送カウントレジスタ A,B (CRA,CRB)設定 ==== */

266

267

if((chain_info & DTC_MODE_REPEAT) != 0){

/* ---- リピート転送モード時 ---- */

268

dtc_info->CRA.BYTE.H = (unsigned char)(count & 0x000000ff); /* 転送回数 */

269

270

dtc_info->CRA.BYTE.L = dtc_info->CRA.BYTE.H; /* 転送カウンタ */

271

}

272

else if((chain_info & DTC_MODE_BLOCK) != 0){

273

/* ---- ブロック転送モード時 ---- */

dtc_info->CRA.BYTE.H = (unsigned char)((count & 0x00ff0000) >> 16); /* ブロックサイズ */

274

dtc info->CRA.BYTE.L = dtc info->CRA.BYTE.H; /* ブロックサイズカウンタ */

275

dtc_info->CRB = (unsigned short)(count & 0x0000ffff); /* 転送回数 */

276

277

278

else{

/* ---- ノーマル転送モード時 ---- */

279

280

dtc_info->CRA.WORD = (unsigned short)(count & 0x0000ffff); /* 転送回数 */

281

282

```

# 3.7 サンプルプログラムリスト "main.c" (7)

```

if(((chain_info & 0x00000083) == DTC_CHN_DISABLE) ||

283

284

((chain_info & 0x00000083) == DTC_CHN_INITIAL)){

/* ---- チェイン転送不使用時、または

チェイン転送使用でチェインの先頭データの転送情報設定時 ---- */

286

287

288

/* **** DTC コントロールレジスタ(DTCCR)設定 **** */

289

DTC.DTCCR.BYTE = set_dtccr;

290

291

bit7-5: Reserved(0)

292

bit4 : RRS = x ----- 転送情報リードスキップを許可/禁止

293

(デフォルト禁止)

bit3 : RCHNE = x --- リピート転送後のチェイン転送を許可/禁止

294

(デフォルト禁止)

295

:

296

bit2-1: Reserved(0)

bit0 : ERR = 0 ---- 転送停止フラグ

297

298

299

/* **** DTC ベクタベースレジスタ(DTCVBR)設定 **** */

300

301

DTC.DTCVBR = DTC VECT BASE;

302

/* **** DTC ベクタアドレス/起動要因設定 **** */

303

switch(chain_info & 0x00ff0000){

304

case 0x00010000: /* DTCベクタアドレス設定:CMIO */

305

306

gData_DTCvect[DTC_VECT_CMI0/sizeof(unsigned long)] = (unsigned long)dtc_info;

307

DTC.DTCERA.BIT.CMIO = 1; /* DTC 起動イネーブル: CMIO */

308

break;

case 0x00020000: /* DTCベクタアドレス設定:ADIO */

309

310

gData_DTCvect[DTC_VECT_ADIO/sizeof(unsigned long)] = (unsigned long)dtc_info;

DTC.DTCERA.BIT.ADIO = 1; /* DTC 起動イネーブル:ADIO */

311

312

case 0x00030000: /* DTCベクタアドレス設定:TXI1 */

313

gData_DTCvect[DTC_VECT_TXI1/sizeof(unsigned long)] = (unsigned long)dtc_info;

314

DTC.DTCERE.BIT.TXI1 = 1; /* DTC 起動イネーブル:TXI1 */

315

316

break;

317

default:

318

break;

}

319

320

321

else{

/* ---- チェイン転送使用でチェインの中間または最後尾データの

322

転送情報設定時 ---- */

323

DTC.DTCCR.BIT.RRS = f_rrs; /* 転送情報リードスキップイネーブル情報差し戻し */

324

325

}

}

326

327

```

# 3.8 サンプルプログラムリスト "main.c" (8)

```

328

329

* ID

330

* Outline

: SCI 設定

331

332

* Include

: "iodefine.h"

*-----

333

* Declaration : void io_init_sci(void);

334

335

* Description : SCI1の初期化処理を行います。

336

337

: ・調歩同期式モード

:・キャラクタ長:8ビットデータ

338

: ・パリティ無し

339

: ・ストップビット長:1ストップビット

340

: ・ビットレート:57600bps

341

342

: ピンファンクションは PA4 を TXD1(出力)に設定しています。

343

344

: サンプルプログラムでは、SCSCRへの設定(TXI要求許可および

345

: 送信動作許可)は DTC 転送により行います。

346

347

: このため本関数にて転送元の設定データを URAM に格納しています。

*-----

348

* Argument

349

: void

350

351

* Return Value : void

352

: None

* Note

353

354

355

void io_init_sci(void)

356

{

volatile int CntWait_lbit = 600; /* 1ビット期間ウェイト用カウンタ@200MHz */

357

358

/* ==== モジュールスタンバイ解除 ==== */

359

STB.CR5.BIT._SCI1 = 0; /* SCI1にクロックを供給 */

360

361

362

/* ==== SCI1割り込み優先レベル設定 ==== */

363

INTC.IPR16.BIT._SCI1 = 0xf;

/* Level=15 */

364

/* ==== シリアルコントロールレジスタ(SCSCR)設定 ==== */

365

/* ---- 割り込み要求禁止/送受信動作禁止 ---- */

367

SCI1.SCSCR.BYTE = 0x00;

/* ---- クロックソース/クロック入出力設定 ---- */

368

SCI1.SCSCR.BIT.CKE = 0; /* 内部クロック/SCK 端子は入力端子(入力信号は無視) */

369

```

# 3.9 サンプルプログラムリスト "main.c" (9)

```

371

/* ==== シリアルモードレジスタ(SCSMR)設定 ==== */

372

SCI1.SCSMR.BYTE = 0x00;

373

bit7 : C/A# = 0 ----- 調歩同期式モード

374

bit6 : CHR = 0 ------ キャラクタ長:8ビットデータ

375

376

bit5 : PE = 0 ------ パリティビットの付加/チェックを禁止

bit4 : O/E# = 0 ----- 不使用

377

bit3 : STOP = 0 ------ ストップビット長:1ストップビット

378

bit2 : MP = 0 -----マルチプロセッサモードを禁止

379

380

bit1-0: CKS[1:0] = B'00 --- ボーレートジェネレータの動作クロック: Pφ

381

382

/* ==== ビットレートレジスタ(SCBRR)設定 ==== */

383

/* 設定ビットレート=57870.37bps@Pφ=50MHz */

384

SCI1.SCBRR = 0x1a;

385

/* (想定ビットレート=57600bps) */

386

387

/* ==== 1 ビット期間ウェイト ==== */

388

while(CntWait_1bit-- > 0){

389

}

390

391

/* ==== ピンファンクション設定 ==== */

392

PFC.PACRL2.BIT.PA4MD = 6; /* PA4 端子機能を TXD1(出力)に設定 */

393

/* ==== SCSCR に設定(転送)するためのデータ値を URAM に格納 ==== */

394

395

gData_TXIenable = 0xa0;

396

bit7 : TIE = 1 ----- TXI 要求を許可

397

398

bit6 : RIE = 0 ------ RXI, ERI 要求を禁止

399

bit5 : TE = 1 ------ 送信動作を許可

bit4 : RE = 0 ----- 受信動作を禁止

400

bit3 : MPIE = 0 ------ マルチプロセッサ機能ディスエーブル

401

bit2 : TEIE = 0 ----- TEI 要求を禁止

402

bit1-0: CKE[1:0] = B'00 --- 内部クロック/SCK 端子は入力端子

403

(入力信号は無視)

404

405

* /

406

}

407

```

# 3.10 サンプルプログラムリスト "main.c" (10)

```

408

* ID

409

410

* Outline

: CMT 設定

411

412

* Include

: "iodefine.h"

413

*-----

* Declaration : void io_init_cmt(void);

414

415

416

* Description : CMTO を 5msec の定周期タイマとして設定します。

417

418

* Argument

: void

*-----

419

420

* Return Value : void

421

422

* Note : None

423

void io_init_cmt(void)

424

425

{

/* ==== モジュールスタンバイ解除 ==== */

426

STB.CR4.BIT._CMT = 0; /* CMT にクロックを供給 */

427

/* ==== CMT カウント動作停止 ==== */

428

429

io_stop_timer_cmt();

/* ==== CMT0割り込み優先レベル設定 ==== */

430

431

432

/* ==== CMT コントロール/ステータスレジスタ(CMCSR)設定 ==== */

CMTO.CMCSR.WORD = 0x0040; /* CMI 要求許可、カウントクロック:Pø/8 */

433

/* ==== CMT カウンタクリア ==== */

434

CMT0.CMCNT = 0 \times 0000;

/* ==== コンペアマッチ期間の設定 ==== */

436

CMT0.CMCOR = 31250 - 1; /* 5msec@P\phi/8 (P\phi=50MHz) */

437

438

}

439

```

# 3.11 サンプルプログラムリスト "main.c" (11)

```

440

* ID

441

* Outline : CMT タイマカウント動作開始

442

443

444

* Include

: "iodefine.h"

*-----

445

* Declaration : void io_start_timer_cmt(void);

446

447

* Description : CMT のタイマカウント動作を開始します。

448

: void

450

* Argument

451

452

* Return Value : void

453

* Note : None

454

455

void io_start_timer_cmt(void)

457

{

CMT.CMSTR.BIT.STR0 = 1; /* CMCNT_0 カウント動作開始 */

458

459

}

460

461

462

* Outline

: CMT タイマカウント動作停止

463

464

* Include

: "iodefine.h"

465

*-----

466

467

* Declaration : void io_stop_timer_cmt(void);

468

* Description : CMT のタイマカウント動作を停止します。

469

470

471

472

473

* Return Value : void

474

475

* Note

: None

476

477

void io_stop_timer_cmt(void)

478

479

CMT.CMSTR.BIT.STR0 = 0; /* CMCNT_0 カウント動作停止 */

480

}

481

```

# 3.12 サンプルプログラムリスト "main.c" (12)

```

482

* ID

483

* Outline : CMT コンペアマッチ割り込み(CMIO)処理

484

485

486

* Include

: "iodefine.h"

487

*_____

488

* Declaration : void io_int_cmt_cmi0(void);

489

* Description : コンペアマッチフラグをクリア後、CMT カウント動作を停止します。

490

492

* Argument

: void

493

494

* Return Value : void

495

496

* Note : None

497

498

void io_int_cmt_cmi0(void)

499

{

500

unsigned short dummy;

501

502

/* ==== コンペアマッチフラグクリア ==== */

503

CMT0.CMCSR.BIT.CMF &= 0;

504

/* ==== CMT カウント動作停止 ==== */

505

io_stop_timer_cmt();

506

507

dummy = CMT0.CMCSR.WORD; /* dummy read */

508

}

509

```

# 3.13 サンプルプログラムリスト "main.c" (13)

```

510

* ID

511

* Outline : SCI 送信データエンプティ割り込み(TXI1)処理

512

513

514

* Include

: "iodefine.h"

*-----

515

* Declaration : void io_int_sci_txi1(void);

516

517

* Description : TXI1要求を禁止に設定し、TDREフラグをクリアした後、

518

519

: TXI1 への分岐回数別に以下の処理を行います。

520

:・TXI1への分岐回数が、DTC初期設定時に指定した連動回数より

521

522

: 少ない場合、以下の転送情報を初期化した後、起動要因 TXI1 を

: イネーブルに設定します。

523

: - 起動要因 ADIO におけるブロック転送用の転送先アドレス (DAR)

524

: - 起動要因 TXI1 における転送元アドレス (SAR) および

525

シリアルデータ転送回数(CRA)

526

527

:・TXI1 への分岐回数が、DTC 初期設定時に指定した連動回数に

528

529

: 達した場合、TEND フラグをクリア(TDRE ビットを1リード後に

: 0 ライト) した後に、SCI 送信終了割り込み(TEI1)要求を許可に設定

: します。

531

532

533

* Argument

534

535

* Return Value : void

536

*-----

537

538

void io_int_sci_txi1(void)

539

540

/* ==== TXI1 分岐回数カウンタインクリメント ==== */

541

gCnt_TXI++;

542

543

544

/* ==== TXI1 要求禁止 ==== */

545

SCI1.SCSCR.BIT.TIE = 0;

546

/* ==== TDRE フラグクリア ==== */

547

SCI1.SCSSR.BIT.TDRE = 0;

548

549

```

## 3.14 サンプルプログラムリスト "main.c" (14)

```

550

if(gCnt_TXI < DTC_COUNT_LINK){</pre>

551

/* ==== DTC 転送情報/起動要因再設定 ==== */

/* ---- 起動要因 ADIO ---- */

552

DTC_ADIO_CHN2.DAR = (unsigned long)&gData_ADconv[0]; /* ブロック転送用 DAR */

553

/* ---- 起動要因 TXI1 ---- */

554

555

DTC_TXI1.SAR = (unsigned long)&gData_ADconv[0];

/* SAR */

DTC_TXI1.CRA.WORD = DTC_COUNT_SCI; /* シリアルデータ転送回数 */

556

DTC.DTCERE.BIT.TXI1 = 1; /* DTC 起動イネーブル:TXI1 */

557

558

else{

/* ==== TXI1 分岐回数カウンタクリア ==== */

560

gCnt_TXI = 0;

561

/* ==== TEND フラグクリア ==== */

562

SCI1.SCSSR.BIT.TDRE = 0; /* TDRE ビットを1リード後に0ライト */

563

/* ==== TEI1 要求許可 ==== */

564

SCI1.SCSCR.BIT.TEIE = 1;

565

566

567

}

568

569

* ID

570

571

* Outline

: SCI 送信終了割り込み(TEI1)処理

*_____

572

573

* Include

: "iodefine.h"

* Declaration : void io_int_sci_teil(void);

575

576

*_____

* Description : TEI1要求および送信動作を禁止します。

577

578

579

* Argument

580

* Return Value : void

582

583

* Note

: None

584

585

void io int sci teil(void)

586

587

unsigned char dummy;

588

589

/* ==== TEI1 要求禁止 ==== */

SCI1.SCSCR.BIT.TEIE = 0;

590

591

/* ==== 送信動作禁止 ==== */

592

SCI1.SCSCR.BIT.TE = 0;

593

594

dummy = SCI1.SCSCR.BYTE; /* dummy read */

595

596

597

/* End of File */

```

# 3.15 サンプルプログラムリスト "intprg.c" (1)

```

/************************

1

DISCLAIMER

2

4

This software is supplied by Renesas Electronics Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

This software is owned by Renesas Electronics Corp. and is protected under

all applicable laws, including copyright laws.

8

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

16

ELECTRONICS CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

17

18

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

* Renesas reserves the right, without notice, to make changes to this

22

23

software and to discontinue the availability of this software.

24

By using this software, you agree to the additional terms and

conditions found by accessing the following link:

26

http://www.renesas.com/disclaimer

***********************

2.7

28

* Copyright (C) 2010 Renesas Electronics Corporation. All rights reserved.

*************************

29

30

* System Name : SH7216 Sample Program

31

File Name : intprg.c

33

Abstract : Interrupt Functions

* Version : 1.00.00

34

35

: SH7216

* Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

36

37

: C/C++ compiler package for the SuperH RISC engine family

38

(Ver.9.03 Release00).

39

: None

40

H/W Platform: R0K572167 (CPU board)

* Description:

41

*******************

42

43

* History : Jul.30,2010 Ver.1.00.00

44

```

# 3.16 サンプルプログラムリスト "intprg.c" (2)

```

#include <machine.h>

45

46

#include "vect.h"

47

48

extern void io_int_cmt_cmi0(void);

49

extern void io_int_txil(void);

50

extern void io_int_teil(void);

51

52

#pragma section IntPRG

53

// 4 Illegal code

55

void INT_Illegal_code(void){/* sleep(); */}

// 5 Reserved

56

57

// 6 Illegal slot

58

void INT_Illegal_slot(void){/* sleep(); */}

59

. . .

// 140 CMT CMI0

326

327

void INT_CMT_CMI0(void)

/* ==== CMT コンペアマッチ割り込み(CMIO)処理 ==== */

329

330

io_int_cmt_cmi0();

331

}

...

542

// 246 SCI SCI1 TXI1

543

void INT_SCI_SCI1_TXI1(void)

544

/* ==== SCI 送信データエンプティ割り込み(TXI1)処理 ==== */

545

546

io_int_sci_txi1();

547

}

548

// 247 SCI SCI1 TEI1

549

void INT_SCI_SCI1_TEI1(void)

550

/* ==== SCI 送信終了割り込み(TEI1)処理 ==== */

551

552

io_int_sci_tei1();

553

...

// 254 SCIF SCIF3 RXI3

566

void INT_SCIF_SCIF3_RXI3(void){/* sleep(); */}

567

// 255 SCIF SCIF3 TXI3

568

void INT_SCIF_SCIF3_TXI3(void){/* sleep(); */}

// Dummy

570

void Dummy(void){/* sleep(); */}

571

572

573

/* End of File */

```

## 3.17 サンプルプログラムリスト "dtc.h" (1)

```

/*************************

1

DISCLAIMER

2

4

This software is supplied by Renesas Electronics Corp. and is only

5

intended for use with Renesas products. No other uses are authorized.

This software is owned by Renesas Electronics Corp. and is protected under

all applicable laws, including copyright laws.

8

9

10

THIS SOFTWARE IS PROVIDED "AS IS" AND RENESAS MAKES NO WARRANTIES

REGARDING THIS SOFTWARE, WHETHER EXPRESS, IMPLIED OR STATUTORY,

11

INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

12

13

* PARTICULAR PURPOSE AND NON-INFRINGEMENT. ALL SUCH WARRANTIES ARE EXPRESSLY

14

* DISCLAIMED.

15

* TO THE MAXIMUM EXTENT PERMITTED NOT PROHIBITED BY LAW, NEITHER RENESAS

16

ELECTRONICS CORP. NOR ANY OF ITS AFFILIATED COMPANIES SHALL BE LIABLE

17

18

FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

19

FOR ANY REASON RELATED TO THIS SOFTWARE, EVEN IF RENESAS OR ITS

20

* AFFILIATES HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

* Renesas reserves the right, without notice, to make changes to this

22

23

software and to discontinue the availability of this software.

24

By using this software, you agree to the additional terms and

conditions found by accessing the following link:

26

http://www.renesas.com/disclaimer

***********************

2.7

28

* Copyright (C) 2010 Renesas Electronics Corporation. All rights reserved.

*************************

29

30

* System Name : SH7216 Sample Program

31

File Name : dtc.h

Abstract : Macro definition for DTC setting

33

* Version : 1.00.00

34

35

: SH7216

* Tool-Chain : High-performance Embedded Workshop (Ver.4.07.00).

36

37

: C/C++ compiler package for the SuperH RISC engine family

38

(Ver.9.03 Release00).

39

: None

40

H/W Platform: R0K572167 (CPU board)

* Description:

41

*******************

42

43

* History : Jul.30,2010 Ver.1.00.00

44

#ifndef _DTC_H_

45

#define _DTC_H_

46

47

```

## 3.18 サンプルプログラムリスト "dtc.h" (2)

```

/* **** Structure definition **** */

48

/* ==== DTC 転送情報用レジスタ定義 ==== */

49

50

typedef struct {

/* DTC モードレジスタ A

* /

51

unsigned char MRA;

/* DTC モードレジスタ B

unsigned char MRB;

* /

52

unsigned char dummy1;

/* Reserved

* /

53

54

unsigned char dummy2;

/* Reserved

* /

/* DTC ソースアドレスレジスタ

55

unsigned long SAR;

/* DTC デスティネーションアドレスレジスタ */

56

unsigned long DAR;

57

union{

58

unsigned short WORD;

59

struct {

60

unsigned char H;

61

unsigned char L;

} BYTE;

62

/* DTC 転送カウントレジスタ A

63

} CRA;

/* DTC 転送カウントレジスタ B

unsigned short CRB;

64

65

} DTC_TRANS_INFO;

66

67

/* **** Macro definition **** */

/* ==== 転送情報格納領域 ==== */

69

#define DTC_CMIO (*(volatile DTC_TRANS_INFO *)0xfff84000) /* CMIO 起動用 */

70

71

#define DTC_ADIO_CHN1 (*(volatile DTC_TRANS_INFO *)0xfff84010) /* ADIO起動用1 */

72

#define DTC_ADIO_CHN2 (*(volatile DTC_TRANS_INFO *)0xfff84020) /* ADIO 起動用 2 */

#define DTC_TXI1 (*(volatile DTC_TRANS_INFO *)0xfff84030) /* TXI1起動用 */

73

74

75

/* ==== DTC ベクタ設定用パラメータ ==== */

76

/* ---- DTCベクタテーブル用ベースアドレス ---- */

#define DTC_VECT_BASE 0xfff85000

77

/* ---- DTC 起動要因ベクタアドレスオフセット ---- */

78

#define DTC_VECT_ADIO 0x0570 /* ADIO */

79

#define DTC VECT CMIO 0x0630 /* CMIO */

80

81

#define DTC_VECT_TXI1 0x07d8 /* TXI1 */

82

/* ==== io_init_dtc 関数の第 4 引数(転送回数)設定用パラメータ ==== */

83

#define DTC_COUNT_LINK 10 /* DTC 連動回数 */

84

#define DTC_COUNT_BLKSIZE 0x00040000 /* ブロック転送時のブロックサイズ(bit23-16) */

85

86

#define DTC_COUNT_SCI 8 /* シリアルデータ転送回数 */

87

```

## 3.19 サンプルプログラムリスト "dtc.h" (3)

```

/* ==== io_init_dtc 関数の第5引数(mode)設定用パラメータ ==== */

88

/* ---- 起動要因トリガ ---- */

89

90

91

92

/* ---- 転送モード ---- */

93

#define DTC_MODE_NORMAL 0x00000000 /* ノーマル転送モード */

94

#define DTC_MODE_REPEAT 0x00004000 /* リピート転送モード */

95

#define DTC_MODE_BLOCK 0x00008000 /* ブロック転送モード */

96

97

/* ---- 転送サイズ ---- */

#define DTC_SIZE_BYTE 0x00000000 /* バイトサイズ転送 */

98

#define DTC_SIZE_WORD 0x00001000 /* ワードサイズ転送 */

99

#define DTC_SIZE_LONG 0x00002000 /* ロングワードサイズ転送 */

100

/* ---- 転送元/転送先アドレスモード ---- */

101

#define DTC_SRC_FIX 0x00000000 /* 転送後 SAR は固定 */

102

#define DTC_SRC_UP 0x00000800 /* 転送後 SAR をインクリメント */

103

#define DTC_SRC_DOWN 0x00000c00 /* 転送後 SAR をデクリメント */

104

105

#define DTC_DST_FIX 0x00000000 /* 転送後 DAR は固定 */

#define DTC_DST_UP 0x00000008 /* 転送後 DAR をインクリメント */

106

107

#define DTC_DST_DOWN 0x0000000c /* 転送後 DAR をデクリメント */

/* ---- チェイン転送関連 ---- */

108

#define DTC CHN DISABLE 0x00000000 /* チェイン転送不使用 */

109

#define DTC_CHN_INITIAL 0x00000080 /* チェイン転送使用(チェインの先頭) */

110

#define DTC_CHN_MIDDLE

111

0x00000081 /* チェイン転送使用(チェインの中間) */

112

#define DTC_CHN_FINAL

0x00000002 /* チェイン転送使用(チェインの最後尾) */

#define DTC_CHN_CONTINUE 0x00000000 /* 連続してチェイン転送実施 */

113

#define DTC_CHN_COUNTER0 0x00000040 /* 転送回数ゼロ時のみチェイン転送実施 */

114

115

/* ---- CPU への割り込み要求発生タイミング ---- */

#define DTC_INT_TRANSTIME 0x00000000 /* 転送回数ごとに発生 */

116

#define DTC_INT_EVERYTIME 0x00000020 /* 1回の転送ごとに発生 */

117

/* ---- リピート/ブロック転送モード時の対象領域指定 ---- */

118

#define DTC_TARGET_DST 0x00000000 /* デスティネーション側がリピート/ブロック領域 */

119

0x00000010 /* ソース側がリピート/ブロック領域 */

120

#define DTC TARGET SRC

/* ---- DTCCR 設定用 ---- */

121

#define DTC_CR_RRS_DISABLE 0x00000000 /* 転送情報リードスキップ禁止 */

122

#define DTC_CR_RRS_ENABLE 0x10000000 /* 転送情報リードスキップ許可 */

123

#define DTC_CR_RCHNE_DISABLE 0x00000000 /* リピート転送後のチェイン転送禁止 */

124

#define DTC_CR_RCHNE_ENABLE 0x08000000 /* リピート転送後のチェイン転送許可 */

125

126

127

#endif /* _DTC_H_ */

128

129

130

/* End of File */

```

## 4. 参考ドキュメント

- ソフトウェアマニュアル

SH-2A、SH2A-FPU ソフトウェアマニュアル Rev.3.00

(最新版をルネサス エレクトロニクスのホームページから入手してください。)

- ハードウェアマニュアル SH7214 グループ、SH7216 グループ ユーザーズマニュアル:ハードウェア編 Rev.2.00 (最新版をルネサス エレクトロニクスのホームページから入手してください。)

# ホームページとサポート窓口

ルネサス エレクトロニクス ホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/inquiry

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 改訂記録

|      |            | 改訂内容 |      |  |  |

|------|------------|------|------|--|--|

| Rev. | 発行日        | ページ  | ポイント |  |  |

| 1.00 | 2010.07.30 | _    | 初版発行 |  |  |

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意 事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の 記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は、製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 4. クロックについて

【注意】リセット時は、クロックが安定した後、リセットを解除してください。

プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営 業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、 ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害 に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されて いる当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の 法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命維持を目的として設計されていない医療機器

(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療

行為 (患部切り出し等) を行うもの、その他直接人命に影響を与えるもの) (厚生労働省定義の高度管理医療機器に相当) またはシステム等

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制するRoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

■営業お問合せ窓口

http://www.renesas.com

※営業お問合せ窓口の住所・電話番号は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス販売株式会社 〒100-0004 千代田区大手町2-6-2(日本ビル)

(03)5201-5307

| ■技術的なお問合せおよび資料のご請求は下記へ               | くど  | う   | ぞ。 |

|--------------------------------------|-----|-----|----|

| 総合お問合せ窓口: http://japan.renesas.com/i | ngu | iry | ,  |