## カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# アプリケーション・ノート

# 78K0S/Kx1+

8ビット・シングルチップ・マイクロコンピュータ フラッシュ・メモリ・プログラミング(プログラマ編)

μPD78F9200

μPD78F9201

μPD78F9202

μPD78F9210

μPD78F9211

μPD78F9212

μPD78F9221

μPD78F9222

μPD78F9232

μPD78F9234

資料番号 U17470JJ4V0AN00 (第4版) 発行年月 September 2006 NS CP(K) (メ モ)

## 目次要約

第1章 概 要 ... 9

第2章 通信プロトコル ... 12

第3章 フラッシュ・メモリ・プログラミング・モード設定 ... 14

第4章 コマンド仕様 ... 19

第5章 フラッシュ・メモリ・プログラミング・パラメータ特性 ... 59

**付録 改版履歴** ... 61

### CMOSデバイスの一般的注意事項

#### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

CMOSデバイスの入力がノイズなどに起因して, $V_L$ (MAX.)から $V_H$ (MIN.)までの領域にとどまるような場合は,誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん, $V_L$ (MAX.)から $V_H$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

#### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVpoまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については、その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また,MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

#### 電源投入時,MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象となります。

リセット機能を持つデバイスの電源投入後は,まずリセット動作を実行してください。

#### 電源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については、その内容を守ってください。

#### 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に,入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

- ◆本資料に記載されている内容は2006年9月現在のもので、今後、予告なく変更することがあります。量 産設計の際には最新の個別データ・シート等をご参照ください。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は,本資料の誤りに関し,一切 その責を負いません。

- 当社は、本資料に記載された当社製品の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、一切その責を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 本資料に記載された回路, ソフトウエアおよびこれらに関する情報は, 半導体製品の動作例, 応用例を 説明するものです。お客様の機器の設計において, 回路, ソフトウエアおよびこれらに関する情報を使 用する場合には, お客様の責任において行ってください。これらの使用に起因しお客様または第三者に 生じた損害に関し, 当社は, 一切その責を負いません。

- 当社は,当社製品の品質,信頼性の向上に努めておりますが,当社製品の不具合が完全に発生しないことを保証するものではありません。当社製品の不具合により生じた生命,身体および財産に対する損害の危険を最小限度にするために,冗長設計,延焼対策設計,誤動作防止設計等安全設計を行ってください。

- 当社は,当社製品の品質水準を「標準水準」,「特別水準」およびお客様に品質保証プログラムを指定していただく「特定水準」に分類しております。また,各品質水準は,以下に示す用途に製品が使われることを意図しておりますので,当社製品の品質水準をご確認ください。

標準水準:コンピュータ,OA機器,通信機器,計測機器,AV機器,家電,工作機械,パーソナル機器,産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート,データ・ブック等の資料で特に品質水準の表示がない場合は,標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には,事前に当社販売窓口までお問い合わせください。

#### (注)

- (1)本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2)本事項において使用されている「当社製品」とは,(1)において定義された当社の開発,製造製品をいう。

M8E 02.11

## はじめに

**対象者** このアプリケーション・ノートは,78K0S/Kx1+の機能を理解し,それを用いたアプリケーション・システムを設計するユーザを対象としています。

**目 的** このアプリケーション・ノートは , 78KOS/Kx1+内蔵のフラッシュ・メモリの書き換えを行うのに , 専用のフラッシュ・メモリ・プログラマを開発するための方法をユーザに理解していただくことを目的としています。

構 成 このマニュアルは,大きく分けて次の内容で構成しています。

・概要

・通信プロトコル

・フラッシュ・メモリ・プログラミング・モード設定

・コマンド仕様

・フラッシュ・メモリ・プログラミング・パラメータ特性

読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコンピュータの一般知識を必要とします。本文欄外の 印は、本版で改訂された主な箇所を示しています。この""をPDF上でコピーして「検索する文字列」に指定することによって、改版箇所を容易に検索できます。

78K0S/Kx1+のハードウエア機能を知りたいとき

78KOS/Kx1+ 各製品のユーザーズ・マニュアルを参照してください。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記 :  $\overline{\times \times \times}$  (端子,信号名称に上線)

注:本文中につけた注の説明

注意:気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数…××××または××××B

10進数...×××× 16進数...××××H

#### 関連資料

関連資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

#### デバイスの関連資料

| 資 料 名                      |         | 資料番号 |         |   |

|----------------------------|---------|------|---------|---|

|                            | 和       | 文    | 英       | 文 |

| 78K0S/KU1+ ユーザーズ・マニュアル     | U18172J |      | U18172E |   |

| 78K0S/KY1+ ユーザーズ・マニュアル     | U16994J |      | U16994E |   |

| 78K0S/KA1+ ユーザーズ・マニュアル     | U16898J |      | U16898E |   |

| 78K0S/KB1+ ユーザーズ・マニュアル     | U17446J |      | U17446E |   |

| 78K/0Sシリーズ ユーザーズ・マニュアル 命令編 | U11047J |      | U11047E | Ξ |

# 目 次

| 第1         | 章    | 概 要 … 9                                          |

|------------|------|--------------------------------------------------|

|            | 1. 1 | <b>システム構成</b> 9                                  |

|            |      | 78K0S/Kx1+ <b>製品固有情報</b> 10                      |

|            |      |                                                  |

| <b>第</b> 2 | 章    | <b>通信プロトコル</b> 12                                |

|            | 2. 1 | <b>通信設定</b> 12                                   |

|            | 2. 2 | フレーム・フォーマット 13                                   |

|            |      | 2. 2. 1 通信データ・フォーマット 13                          |

|            |      | 2. 2. 2 コマンド・フレーム・フォーマット(プログラマから78K0S/Kx1+へ) 13  |

|            |      | 2. 2. 3 コマンド・フィールドの説明 13                         |

|            |      | 2. 2. 4 ステータス・データ・フォーマット(78K0S/Kx1+からプログラマへ) 13  |

|            |      | 2. 2. 5 チェックサム・データ・フォーマット(78K0S/Kx1+からプログラマへ) 13 |

| <b>第</b> 3 | 章    | フラッシュ・メモリ・プログラミング・モード設定 14                       |

|            |      |                                                  |

|            |      | フラッシュ・メモリ・プログラミング・モードへの設定手順 15                   |

|            | 3. 2 | フラッシュ・メモリ・プログラミング・モードの終了 18                      |

| <b>第</b> 4 | 章    | コマンド仕様 19                                        |

|            |      |                                                  |

|            |      | コマンドの概要 20                                       |

|            |      | ステータス一覧 21                                       |

|            | 4. 3 | チップ・プランク・チェック処理 22                               |

|            |      | 4. 3. 1 説明 22<br>4. 3. 2 基本的なコマンド・フレーム 22        |

|            |      | 4.3.2 基本的なコマンド・フレーム 22<br>4.3.3 正常終了 22          |

|            |      | 4.3.4 異常終了 23                                    |

|            |      | 4.3.5 コマンド・フロー 24                                |

|            |      | 4.3.6 タイミング図 25                                  |

|            | 4 4  | プロック・プランク・チェック処理 26                              |

|            |      | 4. 4. 1 説明 26                                    |

|            |      | 4. 4. 2 基本的なコマンド・フレーム 26                         |

|            |      | 4.4.3 正常終了 26                                    |

|            |      | 4. 4. 4 異常終了 26                                  |

|            |      | 4.4.5 コマンド・フロー 27                                |

|            |      | 4.4.6 タイミング図 28                                  |

|            | 4. 5 | <b>チップ消去処理</b> 29                                |

|            |      | 4. 5. 1 説明 29                                    |

|            |      | 4. 5. 2 基本的なコマンド・フレーム 29                         |

|            |      | 4. 5. 3 正常終了 30                                  |

4.5.4 異常終了 ... 30

|             | 4. 5. 5  | コマンド・フロー 31                   |

|-------------|----------|-------------------------------|

|             | 4. 5. 6  | タイミング図 34                     |

| 4. 6        | ブロック     | <b>7消去処理</b> 35               |

|             | 4. 6. 1  | 説明 35                         |

|             | 4. 6. 2  | 基本的なコマンド・フレーム 35              |

|             | 4. 6. 3  | 正常終了 35                       |

|             | 4. 6. 4  | 異常終了 36                       |

|             | 4. 6. 5  | コマンド・フロー 37                   |

|             | 4. 6. 6  | タイミング図 39                     |

| 4. 7        | 書き込み     | <b>÷処理</b> 40                 |

|             | 4. 7. 1  | 説明 40                         |

|             | 4. 7. 2  | 基本的なコマンド・フレーム 40              |

|             | 4. 7. 3  | 正常終了 41                       |

|             | 4. 7. 4  | 異常終了 41                       |

|             | 4. 7. 5  | コマンド・フロー 42                   |

|             | 4. 7. 6  | タイミング図 47                     |

| 4. 8        | セキュリ     | リティ <b>設定処理</b> 48            |

|             | 4. 8. 1  | 説明 48                         |

|             | 4. 8. 2  | 基本的なコマンド・フレーム 48              |

|             | 4. 8. 3  | 正常終了 49                       |

|             | 4. 8. 4  | 異常終了 50                       |

|             | 4. 8. 5  | コマンド・フロー 51                   |

|             |          | タイミング図 54                     |

| 4. 9        | チェック     | <b>7サム処理</b> 55               |

|             | 4. 9. 1  |                               |

|             | 4. 9. 2  | 基本的なコマンド・フレーム 55              |

|             |          | 正常終了 55                       |

|             |          | 異常終了 55                       |

|             |          | コマンド・フロー 56                   |

|             |          | タイミング図 57                     |

|             | 4. 9. 7  | チェックサム・アルゴリズム 58              |

|             | <b>=</b> | JTU <b></b>                   |

| 弗5草         | ノフツ:     | <b>シュ・メモリ・プログラミング・パラメータ特性</b> |

| <i>(</i> -} | 5年20年    |                               |

| 付録          | 以似很烂     | 61                            |

付.1 本版で改訂された主な箇所 ... 61

付. 2 前版までの改版履歴 ... 61

59

## 第1章 概 要

78K0S/Kx1+内蔵のフラッシュ・メモリの書き換えを行うには,通常は,専用のフラッシュ・メモリ・プログラマ (以降プログラマ)を使用する必要があります。

このアプリケーション・ノートでは、ユーザが専用のプログラマを開発するための方法を説明します。

### 1.1 システム構成

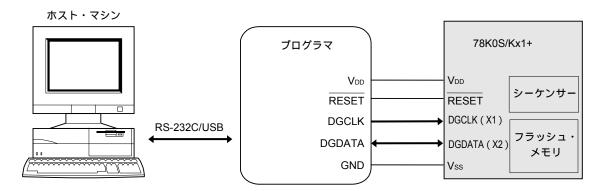

フラッシュ・メモリ・プログラミング時のシステム構成例を次に示します。 図1 - 1は , ホスト・マシンからの制御によりプログラマを使用するプログラミング方法を示しています。

図1-1 プログラミング環境

- 注意 フラッシュ・メモリ・プログラミング・モード設定前のデバイス・ハードウエアの初期化を正しく行うために, Vppは0 Vから起動してください。

- **備考** プログラマと78K0S/Kx1+間のコマンド / データ通信インタフェースは ,DGDATA端子を使用したシングル・ワイヤUARTです。

プログラマの実装方法によっては,あらかじめユーザ・プログラムがプログラマにダウンロードされている場合には,ホスト・マシンを使用せずにスタンド・アローンでプログラマを動作させることもできます。

たとえば、NECエレクトロニクス製フラッシュ・メモリ・プログラマ PG-FP4は、ホスト・マシンを接続してGUIソフトウエアにより実行する方法と、スタンド・アローン・モードで実行する方法のどちらでも動作可能です。

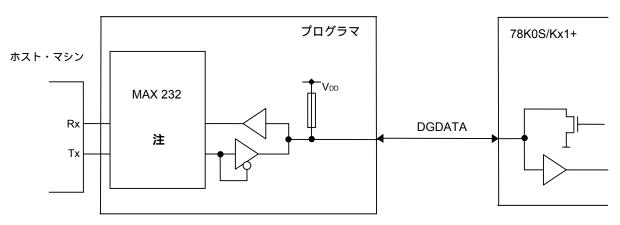

前述のとおり,プログラマと78K0S/Kx1+間の通信は,シングル・ワイヤUARTによって行われます。 図1-2にホスト・マシンとプログラマをRS-232Cで接続する場合のドライバ構成例を示します。

図1-2 ドライバ構成例

注 すべての接続が記述されているわけではありません。

## 1.2 78K0S/Kx1+製品固有情報

78KOS/Kx1+は製品を識別するための"シグネチャ"を持っていません。

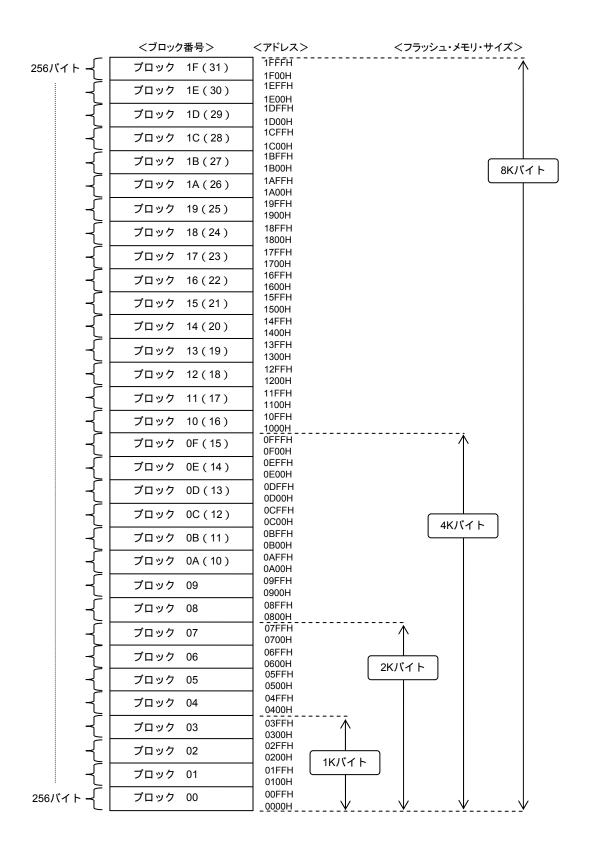

したがって,プログラマ側で製品固有情報(デバイス名,メモリ情報)を管理しておく必要があります。 表1 - 1に78K0S/Kx1+のフラッシュ・メモリ・サイズ,図1 - 3にフラッシュ・メモリ構成を示します。

| デバイス名                 |             | フラッシュ・メモリ・サイズ |

|-----------------------|-------------|---------------|

| 78K0S/KU1+ μPD78F9200 |             | 1KB           |

|                       | μ PD78F9201 | 2KB           |

|                       | μ PD78F9202 | 4KB           |

| 78K0S/KY1+ μPD78F9210 |             | 1KB           |

| μPD78F9211            |             | 2KB           |

|                       | μ PD78F9212 | 4KB           |

| 78K0S/KA1+ μPD78F9221 |             | 2KB           |

| μPD78F9222            |             | 4KB           |

| 78K0S/KB1+ μPD78F9232 |             | 4KB           |

|                       | μ PD78F9234 | 8KB           |

表1 - 1 78K0S/Kx1+のフラッシュ・メモリ・サイズ

図1-3 フラッシュ・メモリ構成

## 第2章 通信プロトコル

## 2.1 通信設定

プログラマと78K0S/Kx1+間の通信は,シングル・ワイヤUARTによって行われます。 シングル・ワイヤUARTの基本プロトコルを表2 - 1に示します。

表2-1 基本プロトコル

| 項目                            | 内 容         |

|-------------------------------|-------------|

| 方向                            | LSB優先       |

| パリティ・ビット                      | 偶数パリティ      |

| ストップ・ビット                      | 1ビット        |

| データ長                          | 8ビット        |

| 標準クロック <sup>注</sup> ( DGCLK ) | 8 MHz ± 1 % |

| 標準ボー・レート                      | 115200 bps  |

注 標準クロックは,フラッシュ・メモリ・プログラミング・モード遷移後に出力してください。

注意 プログラマから供給する発振周波数は,ターゲット・システム上で使用する発振子の直列 / 並列共振周 波数と反共振周波数を調査し,この共振周波数よりも10 %以上ずらして,設定してください。

DGCLKへのクロックは,標準ボー・レートと標準クロックの組み合わせのご使用をお勧めします。

ただし,ターゲット・システム上に発振子が実装されている状態でDGCLKへのクロック供給を行う場合は,次の表2-2の組み合わせでの使用も可能です。

表2-2 クロックとボー・レートの組み合わせ(ターゲット・システムに発振子が実装されている場合)

| クロック         | ボー・レート     |

|--------------|------------|

| 10 MHz ± 1 % | 144000 bps |

| 9 MHz ± 1 %  | 129600 bps |

| 6 MHz ± 1 %  | 86400 bps  |

### 2.2 フレーム・フォーマット

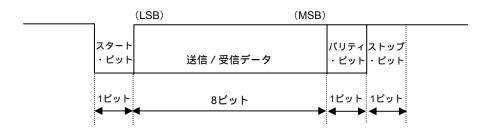

### 2.2.1 通信データ・フォーマット

図2-1に通信データ・フォーマットを示します。

図2-1 通信データ・フォーマット

### 2. 2. 2 コマンド・フレーム・フォーマット (プログラマから78K0S/Kx1+へ)

コマンド・フレームは,4つのフィールドを次のフォーマットに従い通信します。

| コマンド・  | プロック・  | オフセット・        | 最終アドレス・ |

|--------|--------|---------------|---------|

| フィールド  | フィールド  | フィールド         | フィールド   |

| (1パイト) | (1パイト) | (1パイト)        | (1パイト)  |

|        |        | 00H <b>固定</b> |         |

#### 2.2.3 コマンド・フィールドの説明

各コマンド・フィールドの説明を次に示します。コマンド・フィールドで無効な値が送信された場合は,ステータス・コード "Unknown error (01H)" が返されます。

表2-3 コマンド・フィールドの説明

| フィールド  | 説明                     | 値                                      |

|--------|------------------------|----------------------------------------|

| コマンド   | コマンド番号                 | 19H, 20H, 22H, 30H, 32H, 40H, B0H, A0H |

| ブロック   | ブロック番号                 | 00H-1FH <sup>注</sup>                   |

| オフセット  | 固定値                    | 00H                                    |

| 最終アドレス | 書き込みを行う最終アドレスの下位1バイトの値 | FFH, 00H                               |

注 使用可能なブロック番号は,フラッシュ・メモリ・サイズによって変わります。

| <フラッシュ・メモリ・サイズ> | <プロック番号> |

|-----------------|----------|

| 1KB             | 00H-03H  |

| 2KB             | 00H-07H  |

| 4KB             | 00H-0FH  |

| 8KB             | 00H-1FH  |

#### 2. 2. 4 ステータス・データ・フォーマット (78K0S/Kx1+からプログラマへ)

78KOS/Kx1+の応答として、1バイトのステータス・データがプログラマへ送信されます。

#### 2.2.5 チェックサム・データ・フォーマット (78K0S/Kx1+からプログラマへ)

プログラマから送信されたChecksumコマンドの応答として,78K0S/Kx1+からプログラマへ2バイトのチェックサム・データが送信されます。送信データは,チェックサム・データの下位バイト,上位バイトの順です。

## 第3章 フラッシュ・メモリ・プログラミング・モード設定

プログラマにてフラッシュ・メモリの書き換えを行うには,まず,78K0S/Kx1+の動作モードをフラッシュ・メモリ・プログラミング・モードに遷移させる必要があります。

モード設定は、パワーオン・クリア (POC)回路による内部リセット信号解除後にDGCLK, DGDATA, RESETの3端子の特定シーケンスを検出することによって行われます。

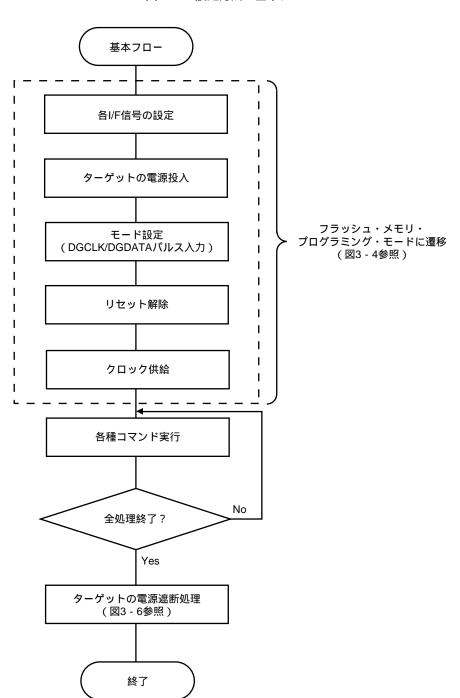

パワーオン・クリア ( POC ) 回路を正常起動させるため , VdDは0 Vから起動させてください。 プログラマの設定方法の基本フローを図3 - 1に示します。

図3-1 設定方法の基本フロー

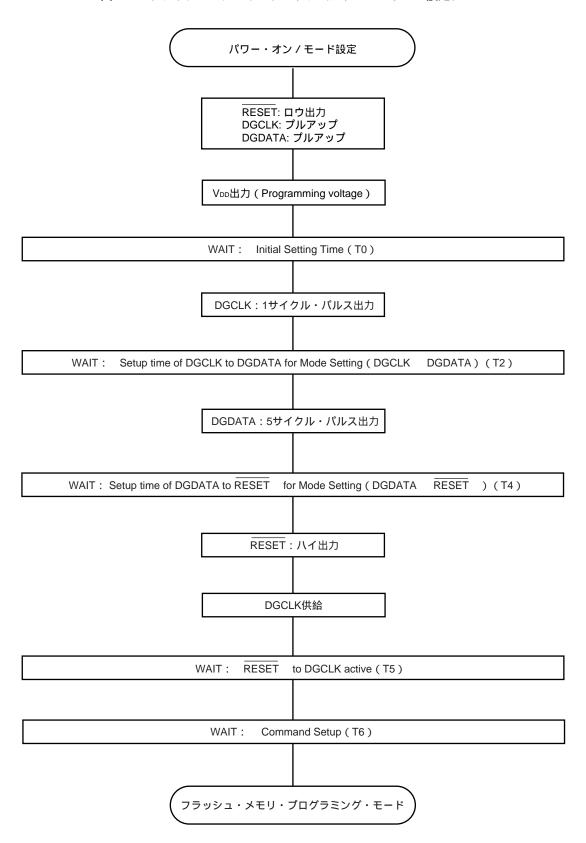

### 3.1 フラッシュ・メモリ・プログラミング・モードへの設定手順

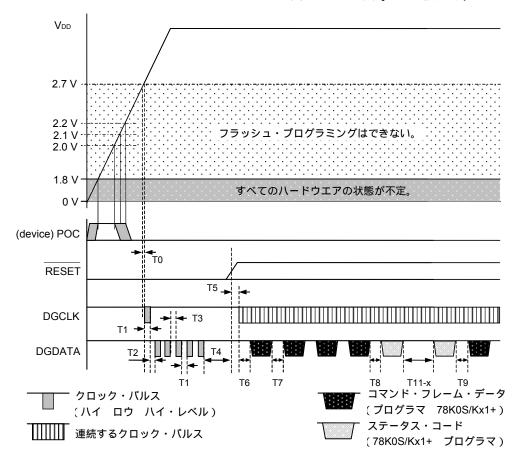

フラッシュ・メモリ・プログラミング・モードへの設定手順を次に示します。

#### <ステップ1 ハードウエアの初期化>

最初にRESET端子をロウ・ドライブ制御,DGCLK端子とDGDATA端子をハイ・ドライブ制御にします。 DGCLK端子およびDGDATA端子は,それぞれ数kΩの抵抗でプルアップしてください(DGCLK端子と DGDATA端子は,RESET入力時に78K0S/Kx1+内部にて高抵抗(30 kΩ(TYP.))にてプルダウンされています)。

電源投入後,POC回路により内部リセット信号が発生し,各ハードウエアが初期化されます。

#### <ステップ2 モードの指定>

次の方法で、78K0S/Kx1+の動作モードをフラッシュ・メモリ・プログラミング・モードに指定します。 フラッシュ・メモリ・プログラミング・モードの指定には、POC回路による内部リセット信号解除後、RESET 端子がロウ・レベル期間中に、プログラマからDGCLK端子とDGDATA端子に次のフォーマットのパルスを送信 する必要があります。

- ・プログラマからDGCLK端子へ ハイ ロウ ハイ・レベルのシングルショット・パルスを入力

- ・プログラマからDGDATA端子へ DGCLK端子へのシングルショット・パルスのあと, ハイ ロウ ハイ・レベルの5つのパルスを入力

DGCLK端子へ余分なパルス入力を行ったり,DGDATA端子へのクロック数に過不足があった場合,フラッシュ・メモリ・プログラミング・モードではなく通常モードに指定されます。

#### <ステップ3 モードの固定とフラッシュ・プログラミング操作>

ステップ1およびステップ2のあと、RESET端子をハイ・レベルに変更することにより、フラッシュ・メモリ・プログラミング・モードが確定します。モード確定後、プログラマからDGCLK端子にクロック供給を行い、内部安定時間が経過したあと、78K0S/Kx1+はコマンド待ち状態になります。

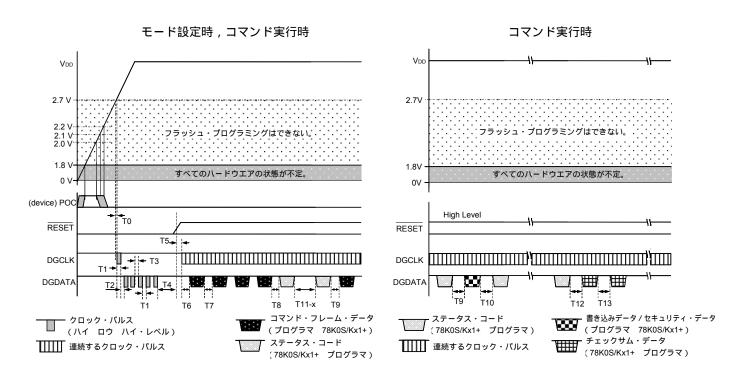

フラッシュ・メモリ・プログラミング・モードへの設定手順のタイミング図と設定フローを次に示します。

図中のTxの値については,第5章 フラッシュ・メモリ・プログラミング・パラメータ特性を参照してください。

#### 図3-2 フラッシュ・メモリ・プログラミング・モードへの変更タイミング図(モード設定時,コマンド実行時)

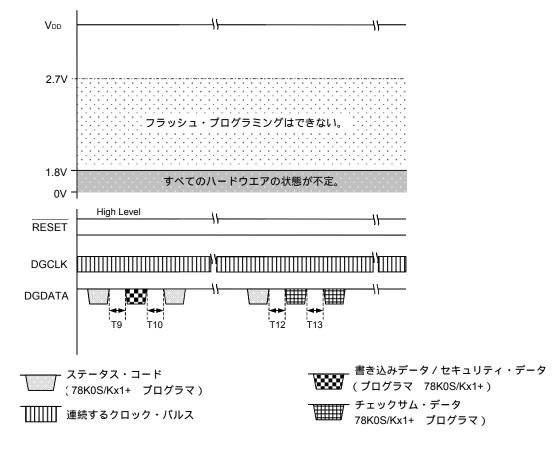

図3-3 フラッシュ・メモリ・プログラミング・モードへの変更タイミング図(コマンド実行時)

#### 図3-4 フラッシュ・メモリ・プログラミング・モードへの設定フロー

## 3.2 フラッシュ・メモリ・プログラミング・モードの終了

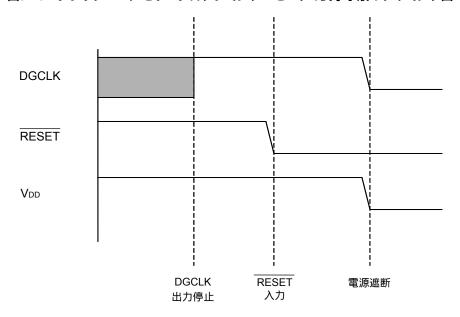

フラッシュ・メモリ・プログラミング・モードの終了時は,DGCLK出力停止後,RESET端子をロウ・レベルに 設定し,78K0S/Kx1+の電源を遮断してください。

フラッシュ・メモリ・プログラミング・モードの終了手順のタイミング図と設定フローを次に示します。

注意 DGCLKに関しては,ACKなどのステータス・コードの受信後,適切なタイミングで出力停止を行ってください。また,コマンド処理中のリセット入力および電源遮断は行わないでください。

図3-5 フラッシュ・メモリ・プログラミング・モードの終了手順のタイミング図

図3-6 フラッシュ・メモリ・プログラミング・モードの終了手順の設定フロー

## 第4章 コマンド仕様

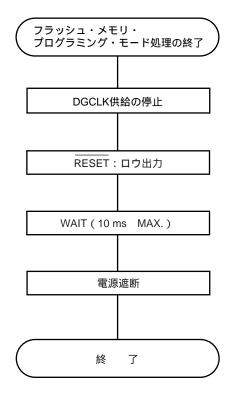

プログラマによるフラッシュ・メモリの書き換え時の一般的なコマンド・フローを図4-1に示します。

図4-1 書き換え時の一般的なコマンド・フロー

**備考** その他に,ブロック・ブランク・チェック処理およびブロック消去処理のサポートが可能です。

## 4.1 コマンドの概要

プログラマで使用されるコマンドの一覧と機能を次に示します。

表4-1 コマンド一覧

| コマンド番号 | コマンド名              | 機能                                                         |  |

|--------|--------------------|------------------------------------------------------------|--|

| 20H    | Chip Erace         | 全フラッシュ・メモリを消去します。                                          |  |

|        |                    | Security setコマンドで設定した情報も初期化します。                            |  |

|        |                    | このコマンド実行後 ,必ずChip Erase VerifyコマンドとBlock Erase Verifyコマンドを |  |

|        |                    | 実行してください。                                                  |  |

| 30H    | Chip Erase Verify  | 全フラッシュ・メモリの消去レベルを確認します。                                    |  |

| 22H    | Block Erase        | 指定ブロックのフラッシュ・メモリを消去します。                                    |  |

|        |                    | このコマンド実行後,必ずBlock Erase Verifyコマンドを実行してください。               |  |

| 32H    | Block Erase Verify | 指定ブロックの消去レベルを確認します。                                        |  |

| 40H    | Programming        | 指定プロックにデータを書き込みます。                                         |  |

|        |                    | このコマンド実行前にErase操作(Chip / Block), コマンド実行後にInternal Verifyニ  |  |

|        |                    | マンドを必ず実行してください。                                            |  |

| 19H    | Internal Verify    | 指定ブロックの書き込みレベルを確認します。                                      |  |

| вон    | Checksum           | 指定ブロックのデータのチェックサム値を受信します。                                  |  |

| 40H    | Security set       | セキュリティ情報を設定します。このコマンド実行後,必ずInternal Verifyコマンド             |  |

|        |                    | を実行してください。                                                 |  |

## 4.2 ステータス一覧

プログラマが78K0S/Kx1+から受信するステータス・コードの一覧を次に示します。

表4-2 ステータス・コード一覧

| ステータス・ | ステータス                                     | 内 容                               |

|--------|-------------------------------------------|-----------------------------------|

| コード    |                                           |                                   |

| 01H    | Unknown error                             | サポートされていないコマンド ,または ,異常フレームを受信し   |

|        |                                           | た場合のエラー                           |

| 06H    | 正常応答(ACK)                                 | 正常応答                              |

|        |                                           | 次の場合に返されます。                       |

|        |                                           | ・コマンドを正しく受信した                     |

|        |                                           | ・書き込みデータを受信した                     |

|        |                                           | ・次の書き込みデータを受信し,1バイトの書き込み完了        |

|        |                                           | ・1バイトの書き込み完了                      |

|        |                                           | ・Chip Erase Verify正常完了            |

|        |                                           | ・Block Erase Verify正常完了           |

|        |                                           | ・Internal Verify正常完了              |

| 15H    | 否定応答(NACK)                                | 否定応答                              |

|        |                                           | コマンド , または , データにパリティ・エラーがあった場合に返 |

|        |                                           | されます。                             |

| 1AH    | MRG10 error                               | 消去ベリファイ・エラー                       |

| 1BH    | MRG11 error                               | 内部ベリファイ・エラー                       |

| 1CH    | Write error                               | 書き込みエラー                           |

| 1DH    | Write data received but write error       | 書き込みデータを受信したが ,書き込みを失敗した場合のエラー    |

| 1EH    | Write data received error and write error | 書き込みデータ受信と書き込みの両方を失敗した場合のエラー      |

| 1FH    | Write data received error but write OK    | 書き込みデータ受信を失敗し,書き込みは正常な場合のエラー      |

| FFH    | 処理中(BUSY)                                 | -                                 |

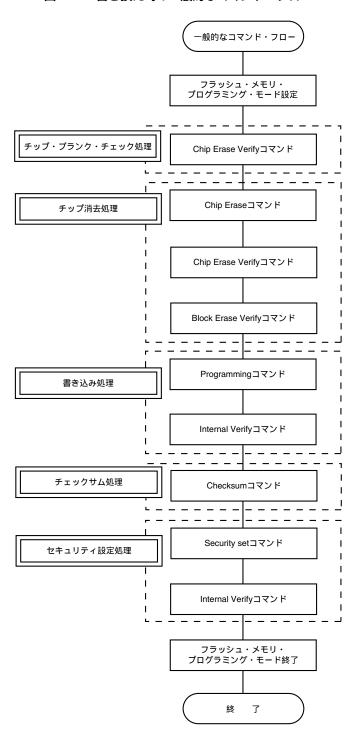

## 4.3 チップ・ブランク・チェック処理

#### 4.3.1 説明

全フラッシュ・メモリのデータが消去状態であるかどうかを確認します。 チップ・ブランク・チェック処理は、Chip Erase Verifyコマンドを実行します。

#### 4.3.2 基本的なコマンド・フレーム

チップ・ブランク・チェック処理で実行するコマンド・フレームは,図4-2のようになります。

図4 - 2 Chip Erase Verifyコマンド・フレーム

| フィールド | コマンド | ブロック                  | オフセット | 最終アドレス |

|-------|------|-----------------------|-------|--------|

| 値     | 30H  | 最大ブロック番号 <sup>注</sup> | 00H   | FFH    |

注 最大ブロック番号として有効な値は、フラッシュ・メモリ・サイズによって変わります。

<フラッシュ・メモリ・サイズ> <プロック番号>

1KB 03H

2KB 07H

4KB 0FH

8KB 1FH

#### 4.3.3 正常終了

チップ・ブランク・チェック処理は, Chip Erase Verifyコマンドを実行します。 正常終了時の78KOS/Kx1+とプログラマ間の処理フローの概要は,次のようになります。

プログラマから78K0S/Kx1+に, Chip Erase Verifyコマンドを送信します。

78K0S/Kx1+は, Chip Erase Verifyコマンド受信後, ACKを送信し, 消去ベリファイを開始します。

プログラマがこの消去ベリファイ終了のACKを受信し,チップ・ブランク・チェック処理は完了です。

## 4.3.4 異常終了

異常終了には,次の3つの場合があります。

- ・78K0S/Kx1+がプログラマからのコマンド受信時に,パリティ・エラーが発生した場合,78K0S/Kx1+からNACKが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・プログラマからの送信コマンドが,サポートされていないコマンドの場合や,異常フォーマットの場合は,78K0S/Kx1+からUnknown errorが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・Chip Erase Verifyコマンドによってエラーが検出された場合,78K0S/Kx1+は,消去ベリファイ・プロセスを終了し,エラー・ステータス(MRG 10 error)を返します。この場合,プログラマは,チップ・ブランク・チェック処理エラーとしてチップ・ブランク・チェック処理を終了します。

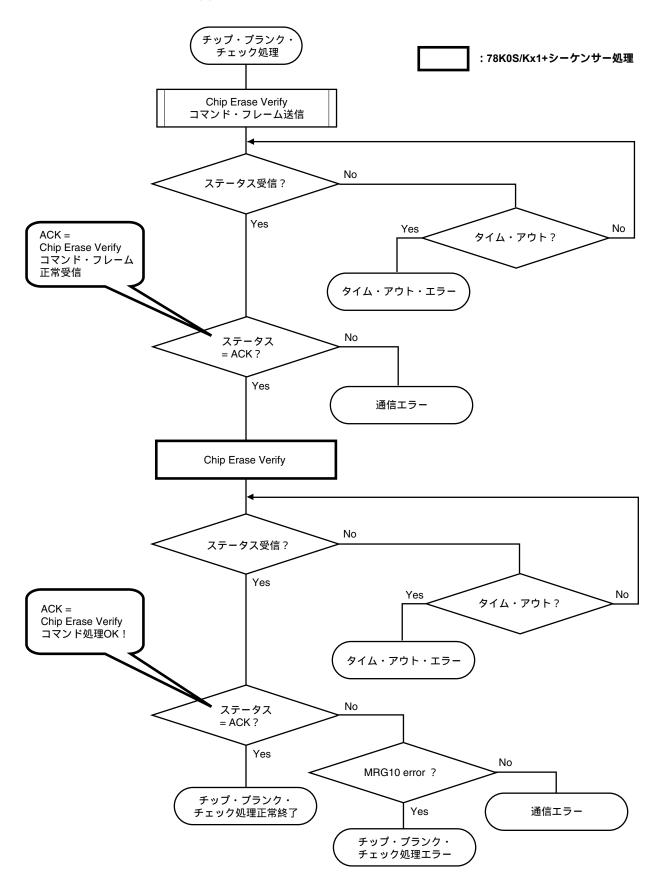

## 4.3.5 **コマンド・フロー**

チップ・ブランク・チェック処理フローを図4-3に示します。

図4-3 チップ・ブランク・チェック処理フロー

## 4.3.6 タイミング図

図4-4にチップ・ブランク・チェック処理のタイミング図を示します。

図中のTxの値については,**第5章 フラッシュ・メモリ・プログラミング・パラメータ特性**を参照してください。

図4-4 チップ・プランク・チェック処理のタイミング図

| ח | G | ח | Δ. | ГΑ |

|---|---|---|----|----|

|   |   |   |    |    |

| "30H"                       |   | "0FH" <sup>注</sup> |             | "00H" |             | "FFH"      |             |

|-----------------------------|---|--------------------|-------------|-------|-------------|------------|-------------|

| Chip Eras<br>Verify<br>コマンド | e | プロック<br>番号         | <b>→</b> T7 | オフセット | <b>→</b> T7 | 最終<br>アドレス | <b>←</b> T8 |

| "06H"       | Chip Erase Verify | "06H"          |

|-------------|-------------------|----------------|

| ACK = "06H" |                   | ACK =<br>"06H" |

| i           | T11-2             | i              |

: プログラマから 78K0S/Kx1+へ

: 78K0S/Kx1+からプログラマへ

注 フラッシュ・メモリ・サイズが4KBの場合のブロック番号です。フラッシュ・メモリ・サイズにより値が異なります。

## 4.4 プロック・プランク・チェック処理

#### 4.4.1 説明

Block Erase Verifyコマンドの実行により,指定したブロック番号のフラッシュ・メモリのデータが消去状態であるかどうかを確認します。

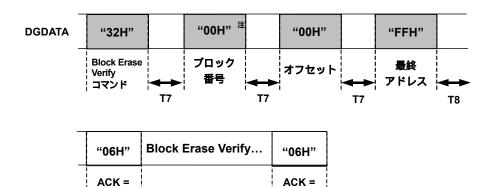

#### 4.4.2 基本的なコマンド・フレーム

ブロック・ブランク・チェック処理で実行するコマンドの基本的なコマンド・フレームは,図4-5のようになります。

図4 - 5 Block Erase Verifyコマンド・フレーム

| フィールド | コマンド | ブロック                | オフセット | 最終アドレス |

|-------|------|---------------------|-------|--------|

| 値     | 32H  | ブロック番号 <sup>注</sup> | 00H   | FFH    |

注 ブロック番号として有効な値は、フラッシュ・メモリ・サイズによって変わります。

| <フラッシュ・メモリ・サイズ> | <ブロック番号> |

|-----------------|----------|

| 1KB             | 00H-03H  |

| 2KB             | 00H-07H  |

| 4KB             | 00H-0FH  |

| 8KB             | 00H-1FH  |

#### 4.4.3 正常終了

ブロック・ブランク・チェック処理は, Block Erase Verifyコマンドを実行します。 正常終了時の78K0S/Kx1+とプログラマ間の処理フローの概要は,次のようになります。

プログラマから78K0S/Kx1+に,Block Erase Verifyコマンドを送信します。

78K0S/Kx1+は, Block Erase Verifyコマンド受信後, ACKを送信し, 消去ベリファイを開始します。 プログラマが, この消去ベリファイ終了のACKを受信し, ブロック・ブランク・チェック処理は完了です。

#### 4.4.4 異常終了

異常終了には,次の3つの場合があります。

- ・78K0S/Kx1+がプログラマからのコマンド受信時に,パリティ・エラーが発生した場合,78K0S/Kx1+からNACKが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・プログラマからの送信コマンドがサポートされていないコマンドの場合や,異常フォーマットの場合は, Unknown errorが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・Block Erase Verifyコマンドによってエラーが検出された場合,78K0S/Kx1+は,消去ベリファイ・プロセスを終了し,エラー・ステータス(MRG 10 error)を返します。この場合,プログラマは,ブロック・ブランク・チェック処理エラーとしてブロック・ブランク・チェック処理を終了します。

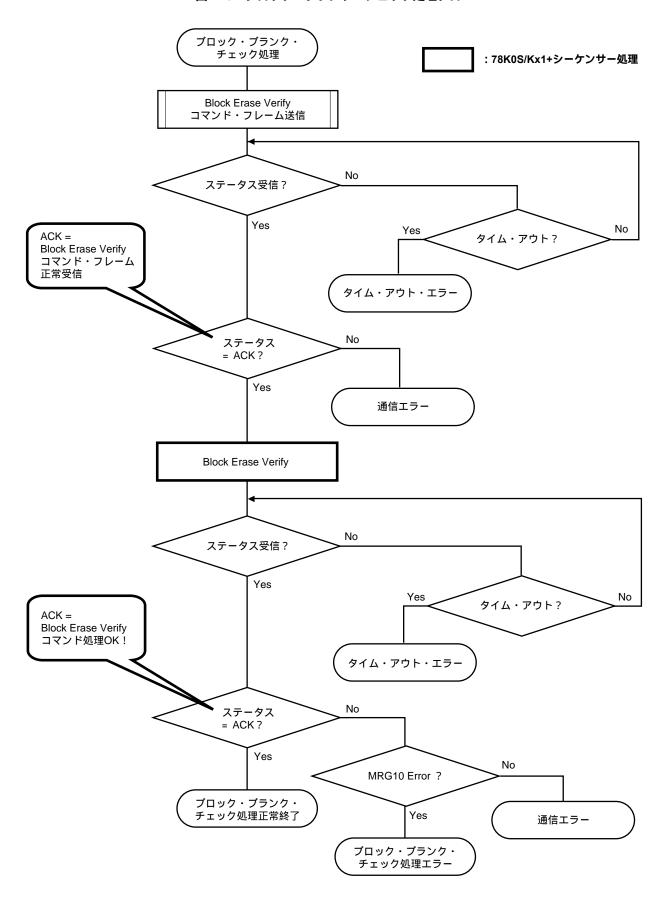

## 4. 4. 5 **コマンド・フロー**

ブロック・ブランク・チェック処理フローを図4-6に示します。

図4-6 ブロック・プランク・チェック処理フロー

## 4.4.6 タイミング図

"06H"

図4 - 7にブロック・ブランク・チェック処理のタイミング図を示します。

図中のTxの値については,**第5章 フラッシュ・メモリ・プログラミング・パラメータ特性**を参照してください。

図4-7 ブロック・ブランク・チェック処理のタイミング図

: プログラマから 78K0S/Kx1+へ

T11-3

: 78K0S/Kx1+からプログラマへ

注 ブロック00のブロック・ブランク・チェックを行う場合のブロック番号です。

"06H"

## 4.5 チップ消去処理

### 4.5.1 説明

全フラッシュ・メモリの消去 (チップ消去)を行います。

チップ消去により, Security setコマンドで設定された, すべての情報も初期化することができます。

ただし,チップ消去禁止設定時は,チップ消去は実行できません。

チップ消去処理は , Chip Eraseコマンド , Chip Erase Verifyコマンド , およびBlock Erase Verifyコマンドを連続して実行します。

#### 4.5.2 基本的なコマンド・フレーム

チップ消去処理で実行する3つのコマンドの基本的なコマンド・フレームは,図4-8~図4-10のようになります。

図4 - 8 Chip Eraseコマンド・フレーム

| フィールド | コマンド | ブロック                  | オフセット | 最終アドレス |

|-------|------|-----------------------|-------|--------|

| 値     | 20H  | 最大ブロック番号 <sup>注</sup> | 00H   | FFH    |

図4 - 9 Chip Erase Verifyコマンド・フレーム

| フィールド | コマンド | ブロック                  | オフセット | 最終アドレス |

|-------|------|-----------------------|-------|--------|

| 値     | 30H  | 最大ブロック番号 <sup>注</sup> | 00H   | FFH    |

注 最大ブロック番号として有効な値は、フラッシュ・メモリ・サイズによって変わります。

<フラッシュ・メモリ・サイズ> <プロック番号>

1KB 03H

2KB 07H

4KB 0FH

8KB 1FH

図4 - 10 Block Erase Verifyコマンド・フレーム

| フィールド | コマンド | ブロック     | オフセット | 最終アドレス |

|-------|------|----------|-------|--------|

| 値     | 32H  | 80H (固定) | 00H   | FFH    |

#### 4.5.3 正常終了

チップ消去処理を実行する場合は,必ず, Chip Erase, Chip Erase Verify, およびBlock Erase Verifyコマンドを連続して実行します。

正常終了時の78K0S/Kx1+とプログラマ間の処理フローの概要は,次のようになります。

プログラマから78K0S/Kx1+に, Chip Eraseコマンドを送信します。

78K0S/Kx1+は, Chip Eraseコマンド受信後, ACKを送信し, 消去を開始します。

プログラマは,消去プロセス終了のACK受信後,Chip Erase Verifyコマンドを送信します。

78K0S/Kx1+は, Chip Erase Verifyコマンド受信後, ACKを送信し, 消去ベリファイを開始します。

プログラマは消去ベリファイ終了のACK受信後,続いて,ブロック80Hに対してBlock Erase Verifyコマンドを送信します。

78K0S/Kx1+は, Block Erase Verifyコマンド受信後, ACKを送信し, ブロック80Hの消去ベリファイを開始します。

プログラマが,この消去ベリファイ終了のACKを受信し,チップ消去処理は完了です。

#### 4.5.4 異常終了

異常終了には,次の3つの場合があります。

- ・78KOS/Kx1+がプログラマからのコマンド受信時に,パリティ・エラーが発生した場合,78KOS/Kx1+からNACKが返されます。その後,78KOS/Kx1+はコマンド待ち状態になります。

- ・プログラマからの送信コマンドがサポートされていないコマンドの場合や,異常フォーマットの場合, Unknown errorが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・Chip / Block Erase Verifyコマンドによってエラーが検出された場合,78K0S/Kx1+は,消去ベリファイ・プロセスを終了し,エラー・ステータス(MRG 10 error)を返します。この場合,プログラマは,Chip Erase コマンド,およびChip / Block Erase Verifyコマンドを再実行します。Chip Eraseコマンドの総実行回数は256回です。256回実行後も,エラー・ステータスが解除されない場合,チップ消去処理エラーとしてチップ消去処理を終了します。

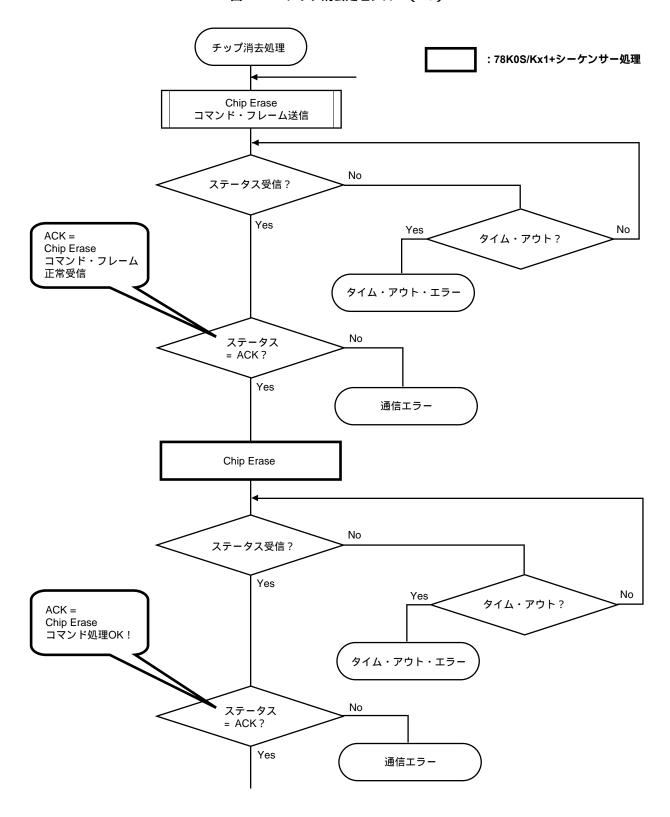

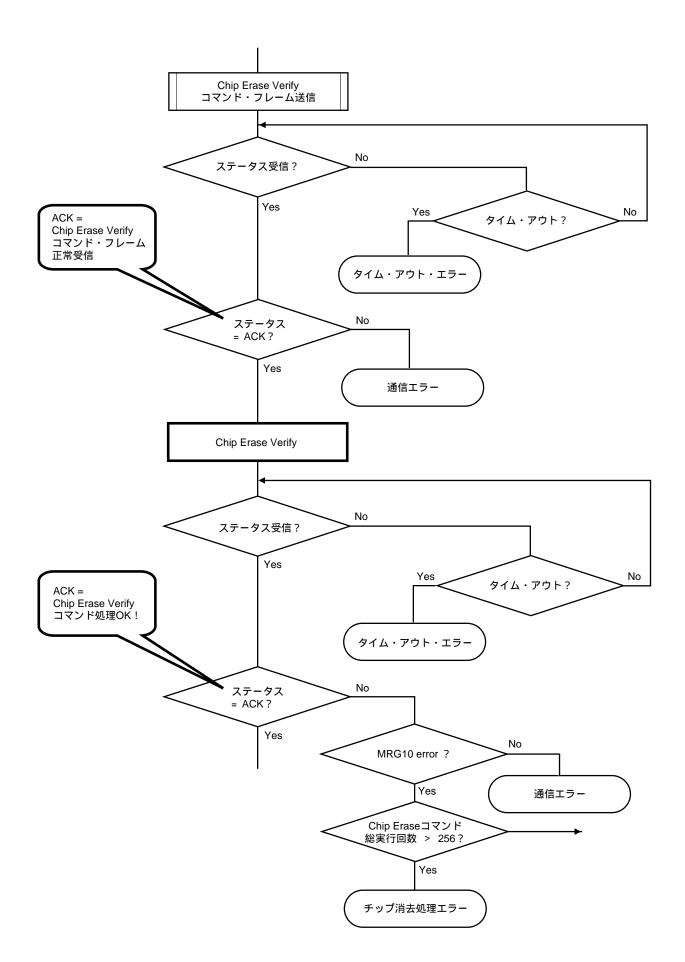

## 4. 5. 5 **コマンド・フロー**

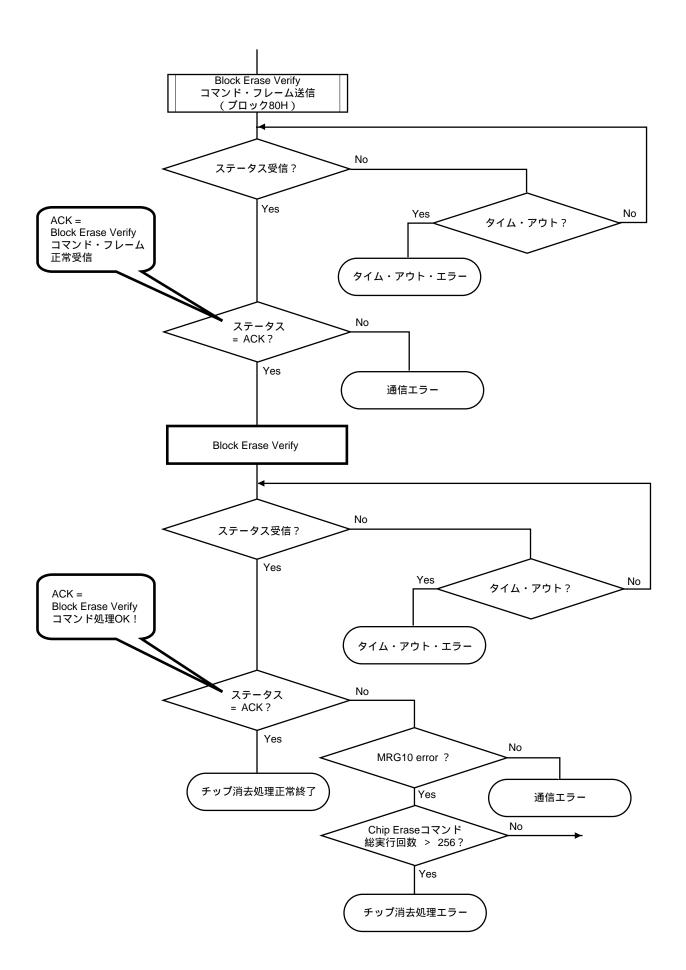

チップ消去処理フローを図4 - 11に示します。

図4 - 11 チップ消去処理フロー (1/3)

図4 - 11 チップ消去処理フロー (2/3)

図4 - 11 チップ消去処理フロー(3/3)

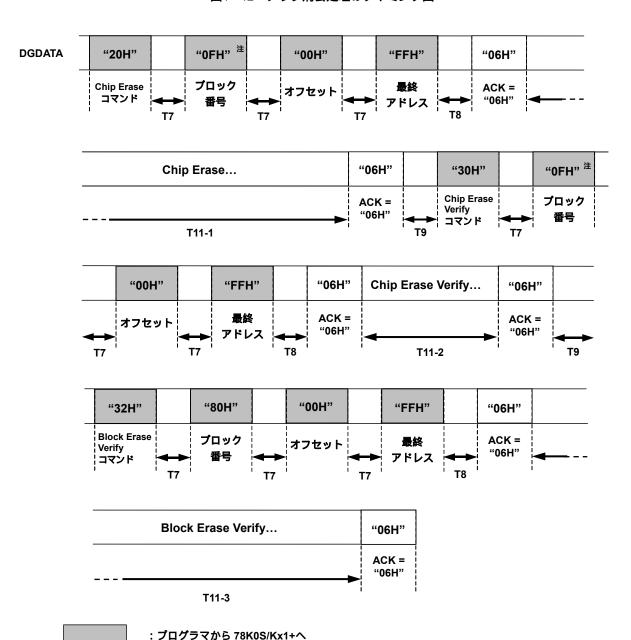

## 4.5.6 **タイミング図**

図4-12にチップ消去処理のタイミング図を示します。

図中のTxの値については,**第5章 フラッシュ・メモリ・プログラミング・パラメータ特性**を参照してください。

図4-12 チップ消去処理のタイミング図

**注** フラッシュ・メモリ・サイズが4KBの場合のブロック番号です。 フラッシュ・メモリ・サイズにより値が異なります。

: 78K0S/Kx1+からプログラマへ

# 4.6 ブロック消去処理

#### 4.6.1 説明

指定したブロック番号のフラッシュ・メモリの消去(ブロック消去)を行います。 ブロック消去処理は, Block EraseコマンドとBlock Erase Verifyコマンドを連続して実行します。

#### 4.6.2 基本的なコマンド・フレーム

ブロック消去処理で実行する2つのコマンドの基本的なコマンド・フレームは,図4 - 13と図4 - 14のようになります。

図4 - 13 Block Eraseコマンド・フレーム

| フィールド | コマンド | ブロック                | オフセット | 最終アドレス |

|-------|------|---------------------|-------|--------|

| 値     | 22H  | ブロック番号 <sup>注</sup> | 00H   | FFH    |

注 ブロック番号として有効な値は、フラッシュ・メモリ・サイズによって変わります。

| < フラッシュ・メモリ・サイズ > | <ブロック番号> |

|-------------------|----------|

| 1KB               | 00H-03H  |

| 2KB               | 00H-07H  |

| 4KB               | 00H-0FH  |

| 8KB               | 00H-1FH  |

図4 - 14 Block Erase Verifyコマンド・フレーム

| フィールド | コマンド | ブロック                | オフセット | 最終アドレス |

|-------|------|---------------------|-------|--------|

| 値     | 32H  | ブロック番号 <sup>注</sup> | 00H   | FFH    |

注 Block Erase Verify コマンドのブロック番号の値は, Block Erase コマンドのブロック番号と同一にしてください。

#### 4.6.3 正常終了

ブロック消去処理を実行する場合は,必ず,Block EraseコマンドとBlock Erase Verifyコマンドを連続して実行します。

正常終了時の78K0S/Kx1+とプログラマ間の処理フローの概要は,次のようになります。

プログラマから78K0S/Kx1+に, Block Eraseコマンドを送信します。

78KOS/Kx1+は, Block Eraseコマンド受信後, ACKを送信し, 消去を開始します。

プログラマは,消去プロセス終了のACK受信後,Block Erase Verifyコマンドを送信します。

78KOS/Kx1+は, Block Erase Verifyコマンド受信後, ACKを送信し, 消去ベリファイを開始します。

プログラマが,この消去ベリファイ終了のACKを受信し,ブロック消去処理は完了です。

# 4.6.4 異常終了

異常終了には,次の3つの場合があります。

- ・78K0S/Kx1+がプログラマからのコマンド受信時に,パリティ・エラーが発生した場合,78K0S/Kx1+からNACKが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・プログラマからの送信コマンドがサポートされていないコマンドの場合や,異常フォーマットの場合, Unknown errorが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・Block Erase Verifyコマンドによってエラーが検出された場合,78K0S/Kx1+は,消去ベリファイ・プロセスを終了し,エラー・ステータス(MRG 10 error)を返します。この場合,プログラマは,Block Eraseコマンド,およびBlock Erase Verifyコマンドを再実行します。Block Eraseコマンドの総実行回数は256回です。256回実行後も,エラー・ステータスが解除されない場合,ブロック消去処理エラーとしてブロック消去処理を終了します。

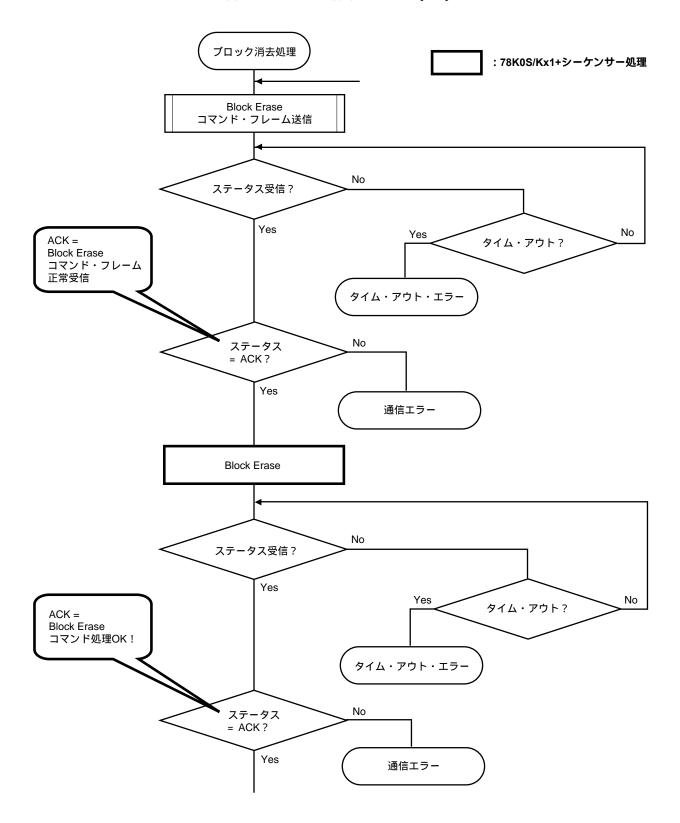

# 4. 6. 5 **コマンド・フロー**

ブロック消去処理フローを図4 - 15に示します。

図4 - 15 ブロック消去処理フロー (1/2)

## 図4-15 プロック消去処理フロー (2/2)

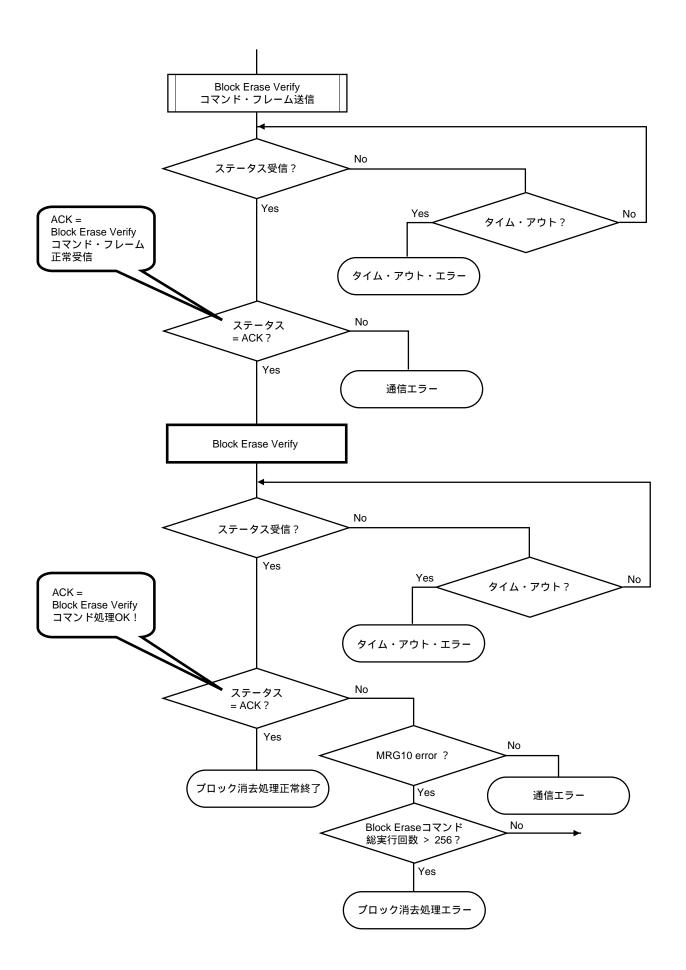

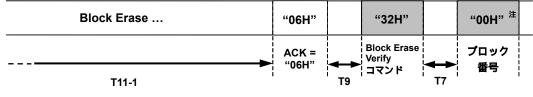

# 4.6.6 タイミング図

図4-16にブロック消去処理のタイミング図を示します。

図中のTxの値については,**第5章 フラッシュ・メモリ・プログラミング・パラメータ特性**を参照してください。

DGDATA "22H" "00H" "FFH" "06H" Block Erase コマンド 番号 オフセット 最終 アドレス T7 T7 T7 T8

図4-16 プロック消去処理のタイミング図

: プログラマから 78K0S/Kx1+へ

: 78K0S/Kx1+からプログラマへ

注 ブロック00のブロック消去を行う場合のブロック番号です。

# 4.7 書き込み処理

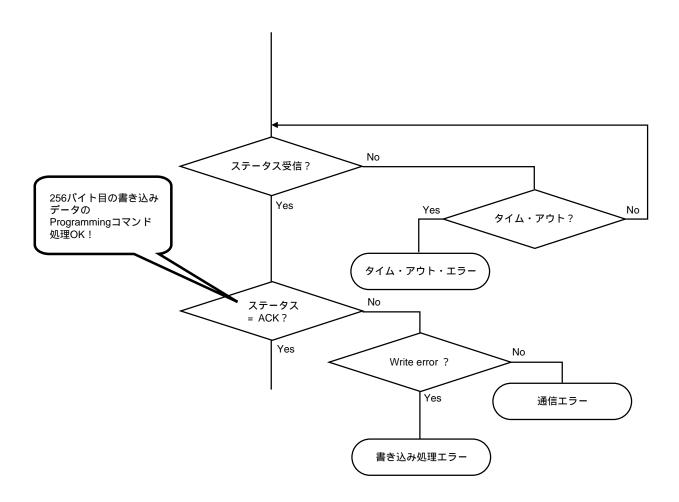

## 4.7.1 説明

Programmingコマンドを実行し,1プロック(256バイト)単位でユーザ・プログラムをフラッシュ・メモリに書き込みます。続いて,Internal Verifyコマンドを実行し,書き込みレベルを確認します。

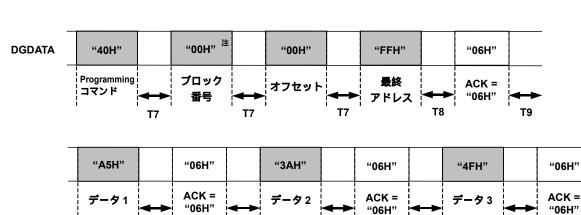

## 4.7.2 基本的なコマンド・フレーム

書き込み処理で実行する2つのコマンドの基本的なコマンド・フレームは,図4 - 17と図4 - 18のようになります。

図4 - 17 Programmingコマンド・フレーム

| フィールド | コマンド | ブロック                | オフセット | 最終アドレス |

|-------|------|---------------------|-------|--------|

| 値     | 40H  | ブロック番号 <sup>注</sup> | 00H   | FFH    |

図4 - 18 Internal Verifyコマンド・フレーム

| フィールド | コマンド | ブロック                | オフセット | 最終アドレス |

|-------|------|---------------------|-------|--------|

| 値     | 19H  | ブロック番号 <sup>注</sup> | 00H   | FFH    |

注 ブロック番号として有効な値は、フラッシュ・メモリ・サイズによって変わります。

<フラッシュ・メモリ・サイズ> <プロック番号>

1KB 00H-03H

2KB 00H-07H

4KB 00H-0FH

8KB 00H-1FH

Internal Verify コマンドのブロック番号の値は ,Programming コマンドのブロック番号と同一にしてください。

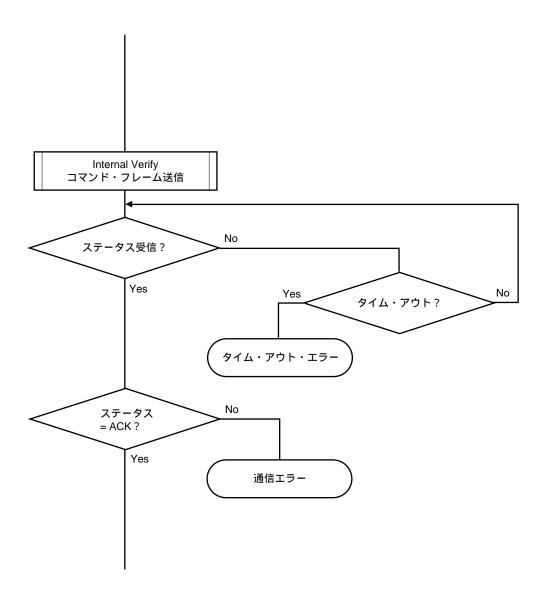

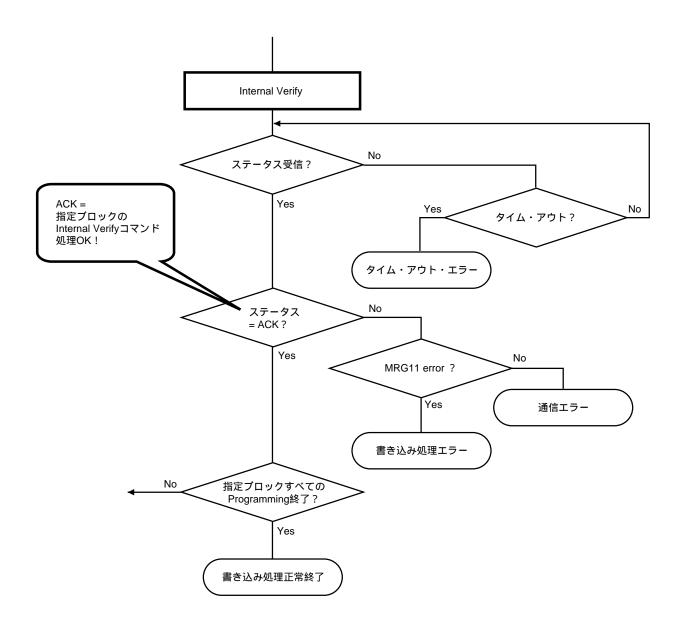

## 4.7.3 正常終了

フラッシュ・メモリへの書き込みを実行する場合は、必ず、ProgrammingコマンドとInternal Verifyコマンドを連続して実行します。

正常終了時の78K0S/Kx1+とプログラマ間の処理フローの概要は,次のようになります。

プログラマは,Programmingコマンドを送信し,ACK受信後,書き込みデータ(1バイト目)を送信します。

78K0S/Kx1+は,書き込みデータ(1バイト目)を受信後,ACKを送信し,書き込みを開始します。 プログラマは,次の書き込みデータ(2バイト目)を送信します(78K0S/Kx1+が書き込み中も送信可能)

78K0S/Kx1+は,1バイト目の書き込みと2バイト目の受信が完了するとACKを返し,2バイト目の書き込みを開始します。

このようにして,書き込みを最終アドレスまで続けます。

78K0/Kx1+は,256バイト目(最終データ)を受信後,次のようにACKを連続して2回送信します。

- ・1回目のACK: 255バイト目の書き込みが完了し, 256バイト目のデータを受信した。

- ・2回目のACK: 256バイト目のデータの書き込みが完了した。

プログラマは,この2回目のACK受信後,Internal Verifyコマンドを送信します。

78K0S/Kx1+は, Internal Verifyコマンド受信後, ACKを送信し, 内部ベリファイを開始します。 プログラマが, この内部ベリファイ終了のACKを受信し,書き込み処理は完了です。

#### 4.7.4 異常終了

異常終了には,次の4つの場合があります。

- ・78K0S/Kx1+がプログラマからのコマンド受信時に,パリティ・エラーが発生した場合,78K0S/Kx1+からNACKが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・プログラマからの送信コマンドがサポートされていないコマンドの場合や,異常フォーマットの場合, Unknown errorが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・Programmingコマンド実行中に書き込みエラー (ステータス・コード: 1CH, 1DH, 1EH, 1FH) が発生した場合,78K0S/Kx1+はコマンド待ち状態となります。プログラマは,書き込み処理エラーとして処理を終了します。

- ・Internal Verifyコマンドによってエラーが検出された場合,78K0S/Kx1+は,内部ベリファイ・プロセスを終了し,エラー・ステータス(MRG 11 error)を返したのち,コマンド待ち状態となります。プログラマは,書き込み処理エラーとして処理を終了します。

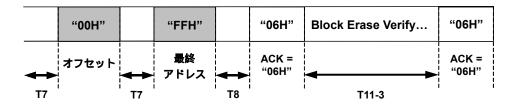

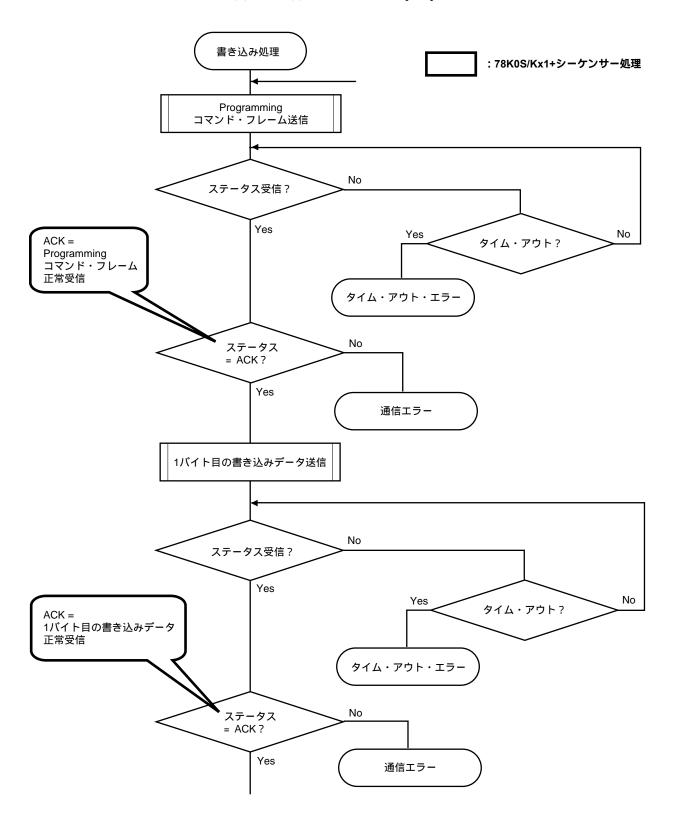

# 4.7.5 **コマンド・フロー**

書き込み処理フローを図4 - 19に示します。

図4 - 19 書き込み処理フロー (1/5)

図4 - 19 書き込み処理フロー (2/5)

図4 - 19 書き込み処理フロー (3/5)

図4 - 19 書き込み処理フロー (4/5)

図4 - 19 書き込み処理フロー (5/5)

# 4.7.6 タイミング図

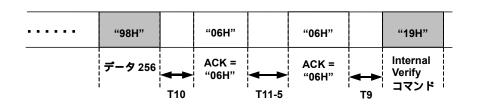

図4-20に書き込み処理のタイミング図を示します。

図中のTxの値については,**第5章 フラッシュ・メモリ・プログラミング・パラメータ特性**を参照してください。

図4-20 書き込み処理のタイミング図

T10

T10

: プログラマから 78K0S/Kx1+へ

T10

: 78K0S/Kx1+からプログラマへ

注 ブロック00の書き込みを行う場合のブロック番号です。

**備考** データ1~データ256は,フラッシュ・メモリに書き込みを行うデータです。

## 4.8 セキュリティ設定処理

#### 4.8.1 説明

フラッシュ・メモリのデータを第三者からの不正アクセスなどから守るためのセキュリティ・フラグを設定 します。

セキュリティ・フラグには,書き込み禁止,ブロック消去禁止,チップ消去禁止の3種類があります。

セキュリティ・フラグの設定は, Security setコマンドとInternal Verifyコマンドを連続して実行します。

設定したセキュリティ・フラグは,一度フラッシュ・メモリ・プログラミング・モードから抜け,再度フラッシュ・メモリ・プログラミング・モードに設定したときから有効になります。

#### 4.8.2 基本的なコマンド・フレーム

セキュリティ設定処理で実行する2つのコマンドの基本的なコマンド・フレームは,図4 - 21と図4 - 22のようになります。

図4 - 21 Security setコマンド・フレーム

| フィールド | コマンド | ブロック | オフセット | 最終アドレス |

|-------|------|------|-------|--------|

| 値     | 40H  | 80H  | 00H   | 00H    |

図4 - 22 Internal Verifyコマンド・フレーム

| フィールド | コマンド | ブロック | オフセット | 最終アドレス |

|-------|------|------|-------|--------|

| 値     | 19H  | 80H  | 00H   | 00H    |

図4-23 セキュリティ・データ(1パイトのみ)

|        | 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|---|---|-----|-----|-----|-----|-----|-----|

| セキュリティ | 1 | 1 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

Security setコマンド実行後は,セキュリティ・データに従いセキュリティ・フラグが設定され,設定値に応じ,Programming,Chip Erase,およびBlock Eraseコマンド実行が禁止されます。セキュリティ・フラグの初期化は,チップ消去の実行により行います。セキュリティ・フラグの初期化により,すべてのコマンドの実行が再び許可されます。ただし,チップ消去禁止設定を行った場合,セキュリティ・フラグの初期化,およびフラッシュ・メモリの初期化が不可となりますので,設定をする際に再確認できるようにしておくことをお勧めいたします。

セキュリティ・データ・フレームの下位6ビットの2ビットずつが,このセキュリティ機能を制御します。 2ビットのうちの1ビットまたは両方が0に設定された場合,対応するコマンド操作が実行不可になります。 次にセキュリティ・データの詳細を示します。

[ビット 5-4] 書き込み保護

| PR5 | PR4 | 制 御    |

|-----|-----|--------|

| 1   | 1   | 書き込み許可 |

| 1   | 0   |        |

| 0   | 1   | 書き込み禁止 |

| 0   | 0   |        |

[ビット 3-2] チップ消去保護

| PR3 | PR2 | 制 御     |  |  |  |  |

|-----|-----|---------|--|--|--|--|

| 1   | 1   | チップ消去許可 |  |  |  |  |

| 1   | 0   |         |  |  |  |  |

| 0   | 1   | チップ消去禁止 |  |  |  |  |

| 0   | 0   |         |  |  |  |  |

[ビット 1-0] ブロック消去保護

| PR1 | PR0 | 制御       |

|-----|-----|----------|

| 1   | 1   | ブロック消去許可 |

| 1   | 0   |          |

| 0   | 1   | ブロック消去禁止 |

| 0   | 0   |          |

それぞれのセキュリティ設定と設定後の各コマンド動作を次に示します。

| 動作モード      | フラッシュ・メモリ・プログラミング・モード |                         |             | セルフ・プログラミング・モード                |

|------------|-----------------------|-------------------------|-------------|--------------------------------|

| אעדב       |                       | ィ設定後のコマン<br>3行可能 × : 実行 |             | ・セキュリティ設定値に関わら<br>ず,全コマンド実行可能。 |

| セキュリティ設定項目 | Programming           | Chip Erase              | Block Erase | ・セキュリティ設定値の保持のみ                |

| 書き込み禁止     | ×                     |                         | ×           | 可能。                            |

| チップ消去禁止    |                       | ×                       | ×           |                                |

| ブロック消去禁止   |                       |                         | ×           |                                |

## 4.8.3 正常終了

フローは,書き込み処理と同じです。

セキュリティ・フラグ設定を実行する場合は,必ず,Security setコマンドとInternal Verifyコマンドを連続して実行します。

正常終了時の78K0S/Kx1+とプログラマ間の処理フローの概要は,次のようになります。

プログラマは , Security setコマンドを送信しACK受信後 , セキュリティ・データ ( 1バイト ) を送信します。

78KOS/Kx1+は,セキュリティ・データ(1バイト)を受信後,次のようにACKを連続して2回送信します。

- ・1回目のACK: セキュリティ・データを受信した。

- ・2回目のACK:セキュリティ・データの書き込みが完了した。

プログラマは,2回目のACK受信後,Internal Verifyコマンドを送信します。

78K0S/Kx1+はコマンド受信後,ACKを送信し,内部ベリファイを開始します。

プログラマが,この内部ベリファイ終了のACKを受信し,セキュリティ設定処理は完了です。

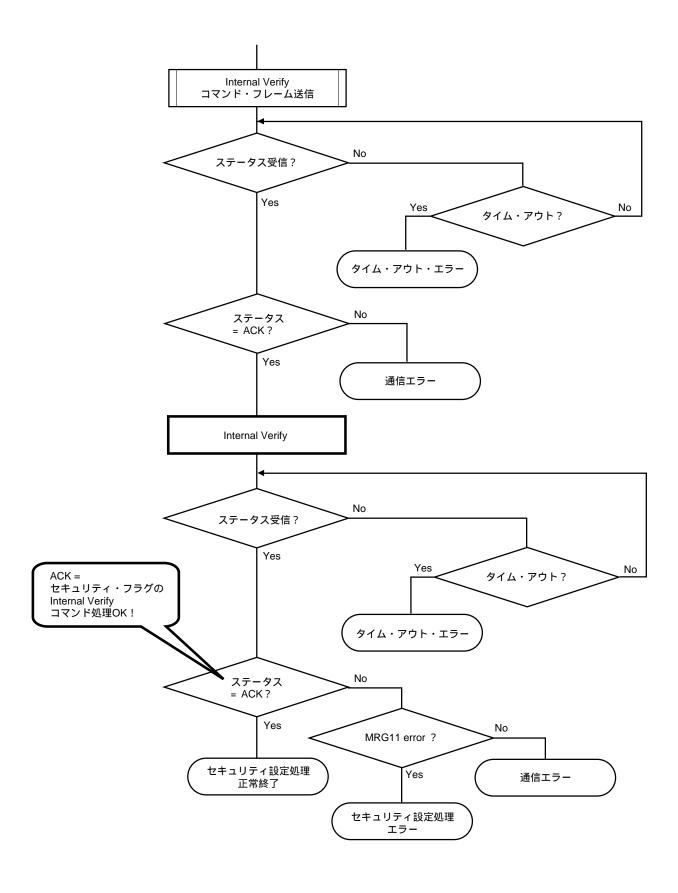

#### 4.8.4 異常終了

書き込み処理が正常に終了しなかった場合は, Chip Eraseコマンドを適用してください。

セキュリティ・フラグの設定後の再設定(追加変更,設定変更)は行えません。実行した場合, Write error (1CH)になります。

異常終了には,次の4つの場合があります(Programmingコマンドと同様です)。

- ・78K0S/Kx1+がプログラマからのコマンド受信時に,パリティ・エラーが発生した場合,78K0S/Kx1+からNACKが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・プログラマからの送信コマンドがサポートされていないコマンドの場合や,異常フォーマットの場合, Unknown errorが返されます。その後,78K0S/Kx1+はコマンド待ち状態になります。

- ・Security setコマンド実行中に書き込みエラー (ステータス・コード:1CH,1DH,1EH,1FH)が発生した場合,78K0S/Kx1+はコマンド待ち状態となります。プログラマは,書き込み処理エラーとして処理を終了します。

- ・Internal Verifyコマンドによってエラーが検出された場合,78KOS/Kx1+は,内部ベリファイ・プロセスを終了し,エラー・ステータス(MRG 11 error)を返したのち,コマンド待ち状態となります。プログラマは,セキュリティ設定処理エラーとして処理を終了します。

- 注意 セキュリティ設定処理を正常終了できなかった場合は,リセットやデバイスの電源遮断前に Chip Erase コマンドを実行してください。

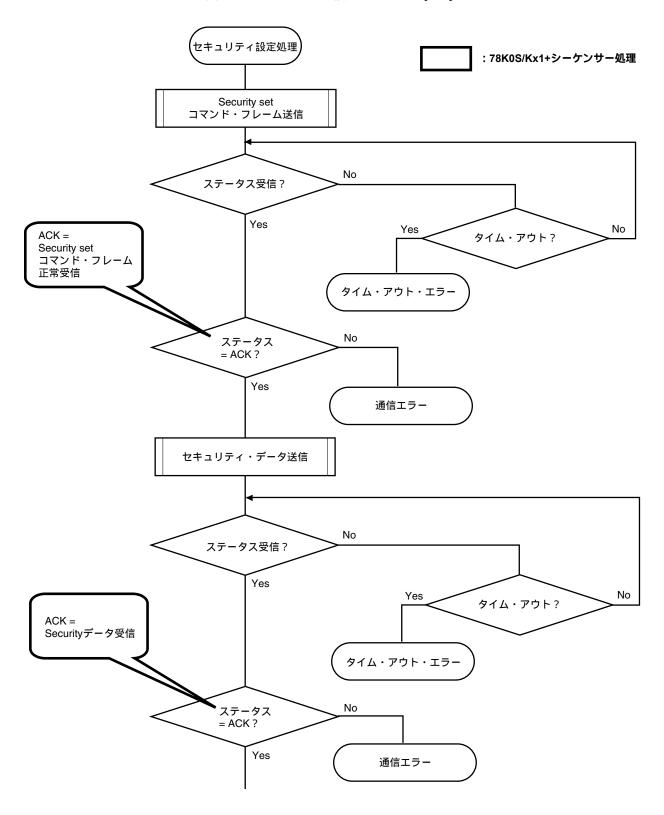

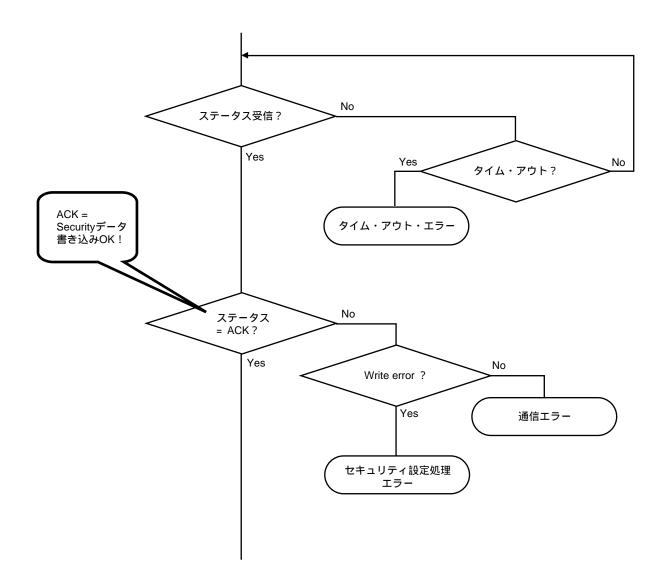

# 4.8.5 **コマンド・フロー**

セキュリティ設定処理フローを図4 - 24に示します。

図4 - 24 セキュリティ設定処理フロー (1/3)

図4-24 セキュリティ設定処理フロー (2/3)

#### 図4 - 24 セキュリティ設定処理フロー (3/3)

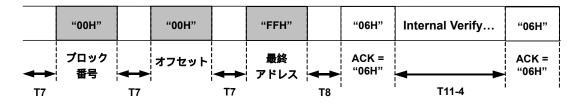

# 4.8.6 タイミング図

図4-25にセキュリティ設定処理のタイミング図を示します。

図中のTxの値については,**第5章 フラッシュ・メモリ・プログラミング・パラメータ特性**を参照してください。

図4-25 セキュリティ設定処理のタイミング図

| DGDATA | ""        | 40H"            |                   | "80        | DH"                 |          | "(        | 00H"        |          | "00H'                      | ,        | "06H"       |          |

|--------|-----------|-----------------|-------------------|------------|---------------------|----------|-----------|-------------|----------|----------------------------|----------|-------------|----------|

|        | Seci      | urity set<br>ンド | <b>←→</b>         |            | ック<br><del>:号</del> | <b></b>  | オフ        | セット         | -        | 最終アドレ                      | <b>√</b> | ACK = "06H" | <b>←</b> |

|        | •         |                 | T7                | •          |                     | T7       | •         |             | ` T7     |                            | Т8       | •           | Т9       |

| _      | "         | CFH"            |                   | "06        | Н"                  |          | "06       | BH"         |          | "19H"                      |          | "80H"       |          |

|        |           | ュリティ<br>データ     | <b>←</b>          | ACI<br>"06 |                     | <b>←</b> | AC<br>"06 |             | <b>↔</b> | Internal<br>Verify<br>コマンド | <b></b>  | プロック<br>番号  |          |

|        |           |                 | T10               |            | Ĭ                   | Г11-6    |           |             | Т9       | . 4()1                     | T7       |             |          |

| _      |           | "00Н            | "                 |            | "00H                | l"       |           | "06H        | -{"   I  | Internal V                 | erify    | "06H"       |          |

| -      | <b>←→</b> | オフセ             | y <b>⊦</b> _      | <b></b>    | 最約<br>アドレ           |          | ←→        | ACK<br>"06H |          | •                          | <b>-</b> | ACK = "06H" |          |

|        | Т7        |                 |                   | T7         |                     | ·        | Т8        |             | i        | T11                        | -4       | i           | i        |

|        |           |                 | : プロ <sup>.</sup> | グラマ        | アからで                | 78K0S    | S/Kx1-    | ٠^          |          |                            |          |             |          |

: 78K0S/Kx1+からプログラマへ

**備考** セキュリティ・データに関しては,4.8.2 **基本的なコマンド・フレーム**を参照してください。

# 4.9 チェックサム処理

#### 4.9.1 説明

ブロック0から指定ブロックまでの領域のチェックサム・データを受信します。

チェックサム値は,演算結果の下位2バイトを下位バイト,上位バイトの順で,78K0S/Kx1+から送信されます。

# 4.9.2 基本的なコマンド・フレーム

チェックサム処理で実行するコマンドの基本的なコマンド・フレームは,図4-26のようになります。

図4 - 26 Checksumコマンド・フレーム

| フィールド | コマンド | ブロック                | オフセット | 最終アドレス |

|-------|------|---------------------|-------|--------|

| 値     | вон  | ブロック番号 <sup>注</sup> | 00H   | FFH    |

#### 注 ブロック番号として有効な値は,フラッシュ・メモリ・サイズによって変わります。

| <フラッシュ・メモリ・サイズ> | <ブロック番号> |

|-----------------|----------|

| 1KB             | 00H-03H  |

| 2KB             | 00H-07H  |

| 4KB             | 00H-0FH  |

| 8KB             | 00H-1FH  |

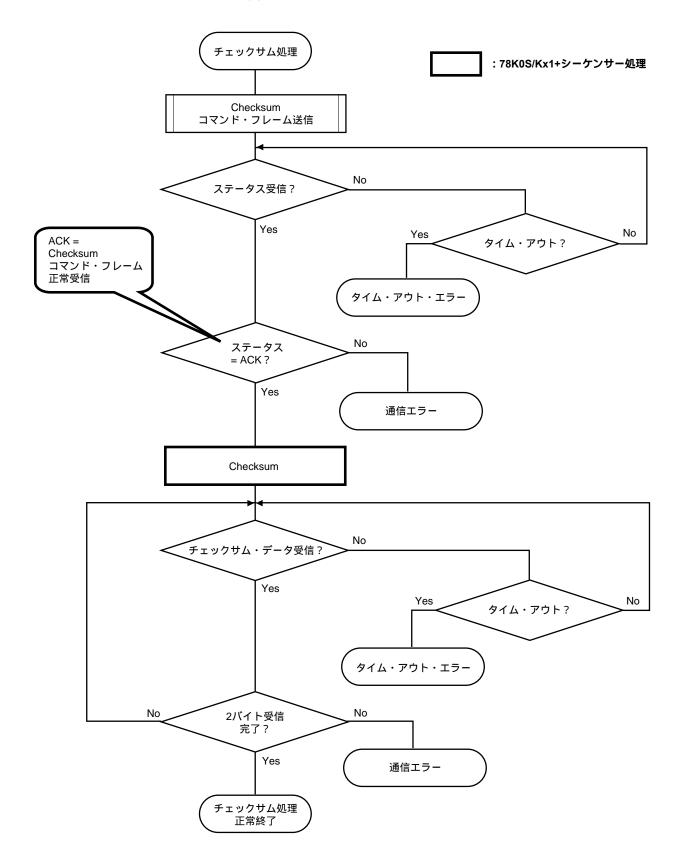

#### 4.9.3 正常終了

演算結果の下位2バイトのチェックサム・データが受信されます。受信は,チェックサム・データの下位バイト,上位バイトの順で行われます。

#### 4.9.4 異常終了

パリティ・エラーが発生すると, NACKが返されて, チェックサム処理は終了します。

# 4.9.5 **コマンド・フロー**

チェックサム処理フローを図4-27に示します。

図4-27 チェックサム処理フロー

# 4.9.6 タイミング図

図4 - 28にチェックサム処理のタイミング図を示します。

図中のTxの値については,**第5章 フラッシュ・メモリ・プログラミング・パラメータ特性**を参照してください。

図4-28 チェックサム処理のタイミング図

| DGDATA | "B0H"            |              | "00H"      |              | "00H" |              | "FFH"      |               | "06H"          |              |

|--------|------------------|--------------|------------|--------------|-------|--------------|------------|---------------|----------------|--------------|

|        | Checksum<br>コマンド | <b>←→</b> T7 | プロック<br>番号 | <b>←→</b> T7 | オフセット | <b>←→</b> T7 | 最終<br>アドレス | <b>←</b> ► T8 | ACK =<br>"06H" | <b>←</b> T12 |

| "3AH" <sup>注</sup> |           | "48H" <sup>注</sup> |

|--------------------|-----------|--------------------|

| SUM1               | <b>←→</b> | SUM2               |

| i i                | T13       | i i                |

: プログラマから 78K0S/Kx1+へ

: 78K0S/Kx1+からプログラマへ

注 チェックサム値は,483AHの場合のSUM1,SUM2データです。

**備考** SUM1は,チェックサム値の下位バイトです。 SUM2は,チェックサム値の上位バイトです。

# 4.9.7 チェックサム・アルゴリズム

チェックサム処理のアルゴリズムを図4 - 29に示します。

#### 図4-29 チェックサム処理のアルゴリズム

```

#define BLOCKSIZ 256

/* 1プロックの ROM データを格納する必要がある。 */

unsigned char rom_data [BLOCKSIZ];

unsigned char bist_calc()

{

int i;

unsigned short bist, bist_temp;

bist = 0;

for(i = 0; i < BLOCKSIZ; i++){

bist_temp = bist & 0x1;

bist_temp = (bist_temp << 8) | (bist_temp << 9) | (bist_temp << 11) | (bist_temp << 12);

bist = (bist >> 1) ^ rom_data[i] ^ bist_temp;

}

return((unsigned char)bist);

}

```

# 第5章 フラッシュ・メモリ・プログラミング・パラメータ特性

この章では,フラッシュ・メモリ・プログラミング・モード時のプログラマと78K0S/Kx1+の間のパラメータ特性を記載しています。その他の電気的特性は,78K0S/Kx1+各製品のユーザーズ・マニュアルを参照のうえ,設計してください。

パラメータ特性1 (Ta = -40~+85 , 2.7 V VDD 5.5 V, Vss = 0 V)

| パラメータ               | シンボル | 条件                        | MIN. | TYP.  | MAX. | 単位   |

|---------------------|------|---------------------------|------|-------|------|------|

| Frequency Tolerance | ΔF   | DGCLK Frequency Tolerance | - 1  |       | 1    | %    |

| Baud Rate           | -    | DGCLK = 8 MHz             |      | 115.2 |      | kbps |

| Optional Baud Rate  | -    | DGCLK = 10 MHz            |      | 144.0 |      | kbps |

| (ターゲット・システムに発振子が    | -    | DGCLK = 9 MHz             |      | 129.6 |      | kbps |

| 実装されている場合)          | -    | DGCLK = 6 MHz             |      | 86.4  |      | kbps |

パラメータ特性2 (Ta = -40~+85 , 2.7 V VDD 5.5 V, Vss = 0 V)

|                             | 項 目                                                                     |          | 略号    | MIN. | TYP. | MAX. | 単位 |

|-----------------------------|-------------------------------------------------------------------------|----------|-------|------|------|------|----|

| Initial Setting Time        |                                                                         |          | T0    | 10   |      |      | ms |

| Minimum Low Width for M     | lode Setting                                                            |          | T1    | 1    |      |      | μs |

| Setup time of DGCLK to D    | OGDATA for Mode Setting                                                 | T2       | 1     |      |      | μs   |    |

| Minimum High Width for N    | Т3                                                                      | 1        |       |      | μs   |      |    |

| Setup time of DGDATA to     | RESET for Mode Setting                                                  |          | T4    | 1    |      |      | μs |

| RESET to DGCLK activ        | ve                                                                      |          | T5    | 2    |      |      | ms |

| Command Setup               |                                                                         |          | Т6    | 2    |      |      | μs |

| Command Data Interval       |                                                                         |          | T7    | 20   |      |      | μs |

| Command to Status Interv    | Т8                                                                      |          |       | 6    | μs   |      |    |

| Status to Command / Data    | Т9                                                                      | 1        |       |      | μs   |      |    |

| Data to Status Interval 121 |                                                                         |          | T10   |      |      | 150  | μs |

| ACK to Status Interval      | Chip / Block Erase Comm                                                 | T11-1    |       |      | 10   | ms   |    |

|                             | Chip Erase Verify Comma                                                 | T11-2    |       |      | 16   | ms   |    |

|                             | Block Erase Verify Comm                                                 | T11-3    |       |      | 500  | μs   |    |

|                             | Internal Verify Command                                                 | T11-4    |       |      | 6    | ms   |    |

|                             | Programming Command <sup>3</sup>                                        | T11-5    |       |      | 150  | μs   |    |

|                             | (最終(256バイト目)書                                                           |          |       |      |      |      |    |

|                             | Security Command <sup>3±2</sup>                                         |          | T11-6 |      |      | 150  | μs |

|                             | ( セキュリティ・データ送                                                           | 信後)      |       |      |      |      |    |

| ACK to Checksum 1st byt     | Checksum領域                                                              | T12-1    |       |      | 4    | ms   |    |

|                             |                                                                         | 4 Kバイトまで |       |      |      |      |    |

|                             | Checksum領域                                                              | T12-2    |       |      | 8    | ms   |    |

|                             |                                                                         | 8 Kバイトまで |       |      |      |      |    |

| Checksum 1st byte to Che    | Checksum 1st byte to Checksum 2nd byte (Checksum Command) <sup>注4</sup> |          |       |      |      | 2    | μs |

(注1~4と備考は次頁にあります。)

- **注**1. 78KOS/Kx1+が,プログラマからのコマンド・フレーム,または,データを受信後,ステータス・データを送信するまでに要する最大時間です。プログラマは,この最大時間までステータス受信処理を続ける必要があります。

- 2. 78K0S/Kx1+が,プログラマからのコマンド・フレーム受信,または,データ受信のACKを送信してから,コマンド処理終了のACKを送信するまでに要する最大時間です。プログラマは,この最大時間までステータス受信処理を続ける必要があります。

- 3. 78KOS/Kx1+が,プログラマからのコマンド・フレームを受信してから,1バイト目のチェックサム・データ を送信するまでに要する最大時間です。プログラマは,この最大時間までステータス受信処理を続ける必要が あります。

- 4. 78KOS/Kx1+が,1バイト目のチェックサム・データを送信してから,2バイト目のチェックサム・データを送信してから,2バイト目のチェックサム・データを送信するまでに要する最大時間です。プログラマは、この最大時間までデータ受信処理を続ける必要があります。

**備考** "ACK to Status Interval"の各項目名は,プログラマから78K0S/Kx1+に発行する,それぞれのコマンド名と 関連しています。

# 付録 改版履歴

# 付.1 本版で改訂された主な箇所

| 箇 所     | 内 容                                                    |

|---------|--------------------------------------------------------|

| p.10    | 表1 - 1 78K0S/Kx1+ <b>のフラッシュ・メモリ・サイズ</b> に78K0S/KU1+を追加 |

| p.19    | <b>図</b> 4 - 1 <b>書き換え時の一般的なコマンド・フロー</b> を修正           |

| p.22    | 4. 3. 1 説明の記述を修正                                       |

| p.22    | 図4 - 3 Block Erase Verifyコマンド・フレームを削除                  |

| p.22    | 4.3.3 正常終了の記述を修正および削除                                  |

| p.23    | 4.3.4 異常終了の記述を修正,注意を削除                                 |

| p.24    | <b>図</b> 4-3 チップ・ブランク・チェック <b>処理フロー</b> を修正,(2/2)の図を削除 |

| p.25    | 図4 - 4 チップ・ブランク・チェック <b>処理のタイミング図</b> を修正              |

| 旧版 p.62 | 第6章 <b>電気的特性 (参考値)</b> を削除                             |

# 付.2 前版までの改版履歴

前版までの改版履歴を次に示します。なお、適用箇所は各版での章を示します。

| 版数  | 前版からの主な改版内容                                            | 適用箇所        |

|-----|--------------------------------------------------------|-------------|

| 第2版 | 図3-2 フラッシュ・メモリ・プログラミング・モードへの変更タイミング図(モード設定時,           | 第3章 フラッシュ・メ |

|     | コマンド実行時), 図3-3 フラッシュ・メモリ・プログラミング・モードへの変更タイミン           | モリ・プログラミング・ |

|     | <b>グ図(コマンド実行時)</b> を変更                                 | モード設定       |

|     | 図4 - 21 <b>書き込み処理のタイミング図</b> の"T11" "T11-5"に変更         | 第4章 コマンド仕様  |

|     | 図4-26 セキュリティ設定処理のタイミング図の略語名を変更                         |             |

|     | <b>図</b> 4 - 29 チェックサム処理のタイミング図の略語名を変更                 |             |

|     | ・パラメータ特性1の表を追加,パラメータ特性2の表を変更                           | 第5章 フラッシュ・メ |

|     | ・DGDATAのタイミング・チャートを変更                                  | モリ・プログラミング・ |

|     |                                                        | パラメータ特性     |

| 第3版 | 2.1 <b>通信設定</b> の説明文, <b>表</b> 2-2のタイトルを変更             | 第2章 通信プロトコル |

|     | <b>図</b> 4-1 <b>書き換え時の一般的なコマンド・フローのチェックサム処理</b> の位置を変更 | 第4章 コマンド仕様  |

|     | 表4 - 1 <b>コマンド一覧</b> のSecurity setのコマンド番号を修正           |             |

|     | <b>図</b> 4 - 26 <b>セキュリティ設定処理のタイミング図</b> の最終アドレスの値を修正  |             |

|     | 第5章 フラッシュ・メモリ・プログラミング・パラメータ特性                          | 第5章 フラッシュ・メ |

|     | ・パラメータ特性1の表の " Optional Baud Rate " のパラメータ欄を変更         | モリ・プログラミング・ |

|     | ・パラメータ特性2の表のT8のMAX.値を変更                                | パラメータ特性     |

|     | ・パラメータ特性2の表のT12をChecksum領域で2つに場合分け                     |             |

(メ モ)

(メ モ)

## 【発 行】

## NECエレクトロニクス株式会社

〒211-8668 神奈川県川崎市中原区下沼部1753

電話(代表):044(435)5111

一 お問い合わせ先-

#### 【ホームページ】

NECエレクトロニクスの情報がインターネットでご覧になれます。

URL(アドレス) http://www.necel.co.jp/

#### 【営業関係,技術関係お問い合わせ先】

半導体ホットライン電話: 044-435-9494(電話:午前9:00~12:00,午後1:00~5:00)E-mail: info@necel.com

#### 【資料請求先】

NECエレクトロニクスのホームページよりダウンロードいただくか, NECエレクトロニクスの販売特約店へお申し付けください。