## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 455A Group

## Staircase Key Matrix (Using Time-of-Day Clock Operation Mode)

## 1. Abstract

This document presents the method for using the staircase key matrix of the 455A-group microcomputers and shows an application example.

## 2. Instruction

The application example explained in this document applies for use with the microcomputers and under the conditions described below.

- Microcomputer : 455A group

- Oscillation frequency : 4 MHz as f(XIN) or 32.767 kHz as subclock f(XCIN)

- System clock : Used in through mode (not frequency divided)

## 3. Related Registers

## 3.1 Interrupt Control Register V1

Table 3.1 shows the bit configuration of the Interrupt Control Register V1. For write to the register V1, first set a value in the register A and then use the TV1A instruction. Furthermore, the TAV1 instruction may be used to transfer the content of register V1 to the register A.

| Table 3.1 | Bit Configuration of Inte | errupt Control Register V1 |

|-----------|---------------------------|----------------------------|

|           |                           |                            |

|      | Interrupt control register V1       |   | at reset : 00002                                     | at power down : 00002            | R/W<br>TAV1/TV1A |  |  |  |

|------|-------------------------------------|---|------------------------------------------------------|----------------------------------|------------------|--|--|--|

| V13  | Timer 2 interrupt enable bit        | 0 | Interrupt disabled (                                 | SNZT2 instruction is valid))     |                  |  |  |  |

| V 13 |                                     |   | Interrupt enabled (S                                 | SNZT2 instruction is invalid)    |                  |  |  |  |

| V12  | V12 Timer 1 interrupt enable bit    |   | Interrupt disabled (SNZT1 instruction is valid)      |                                  |                  |  |  |  |

| VIZ  |                                     |   | Interrupt enabled (SNZT1 instruction is invalid)     |                                  |                  |  |  |  |

| V/11 | V11 Not used                        |   | This bit has no function, but read/write is enabled. |                                  |                  |  |  |  |

| VII  |                                     |   |                                                      | alon, but read/write is enabled. |                  |  |  |  |

| V10  | V10 External 0 interrupt enable bit |   | Interrupt disabled (                                 | SNZ0 instruction is valid)       |                  |  |  |  |

| VIO  |                                     |   | Interrupt enabled (SNZ0 instruction is invalid)      |                                  |                  |  |  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

Note2: Unused bits when the staircase key matrix is set

## 3.2 Interrupt Control Register V2

Table 3.2 shows the bit configuration of the Interrupt Control Register V2. For write to the register V2, first set a value in the register A and then use the TV2A instruction. Furthermore, the TAV2 instruction may be used to transfer the content of register V2 to the register A.

| Table 3.2 | Bit Configuration of | Interrupt Control Register V2 |

|-----------|----------------------|-------------------------------|

|-----------|----------------------|-------------------------------|

|              | Interrupt control register V2      |   | at reset : 00002                                     | at power down : 00002                                | R/W<br>TAV2/TV2A |  |  |  |  |

|--------------|------------------------------------|---|------------------------------------------------------|------------------------------------------------------|------------------|--|--|--|--|

| V23          | Not used                           | 0 | This hit has no fund                                 | This hit has no function, but road/write is onabled  |                  |  |  |  |  |

| V 2.5        |                                    |   |                                                      | This bit has no function, but read/write is enabled. |                  |  |  |  |  |

| V/22         | V22 Not used                       |   | This bit has no function, but read/write is enabled. |                                                      |                  |  |  |  |  |

| V <b>Z</b> Z |                                    |   |                                                      |                                                      |                  |  |  |  |  |

| \/21         | V21 Not used                       |   | This bit has no function, but read/write is enabled. |                                                      |                  |  |  |  |  |

| VZI          |                                    |   |                                                      | tion, but read/while is chabled.                     |                  |  |  |  |  |

| V/20         | V20 Timer 3 interrupt enable bit - |   | Interrupt disabled (SNZT3 instruction is valid)      |                                                      |                  |  |  |  |  |

| V 20         |                                    |   | Interrupt enabled (SNZT3 instruction is invalid)     |                                                      |                  |  |  |  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

## 3.3 Timer Control Register PA

Table 3.3 shows the bit configuration of the Timer Control Register PA. For write to the register PA, first set a value in the register A and then use the TPAA instruction.

|     | Timer control register PA | at reset : 02 |                  | at power down : 02 | W<br>TPAA |

|-----|---------------------------|---------------|------------------|--------------------|-----------|

| ΡΔο | PA0 Prescaler control bit | 0             | Stop (state reta | ained)             |           |

| 170 |                           |               | Operating        |                    |           |

Note1: The letter W denotes "writable."

## 3.4 Timer Control Register W1

Table 3.4 shows the bit configuration of the Timer Control Register W1. For write to the register W1, first set a value in the register A and then use the TW1A instruction. Furthermore, the TAW1 instruction may be used to transfer the content of register W1 to the register A.

| Table 3.4 | Bit Configuration of | Timer Control Register W1 |

|-----------|----------------------|---------------------------|

|-----------|----------------------|---------------------------|

| Timer control register W1 |                                                            | at reset : 00002 |           | 00002                                    | at power down : state retained | R/W<br>TAW1/TW1A |  |  |

|---------------------------|------------------------------------------------------------|------------------|-----------|------------------------------------------|--------------------------------|------------------|--|--|

| \W/12                     | W13 Timer 1 count auto-stop circuit selection bit (Note 2) |                  | Timer     | 1 count aut                              | o-stop circuit not selected    |                  |  |  |

| VV15                      |                                                            |                  | Timer     | Timer 1 count auto-stop circuit selected |                                |                  |  |  |

| W/12                      | W12 Timer 1 control bit                                    |                  | Stop (s   | Stop (state retained)                    |                                |                  |  |  |

| VV 12                     |                                                            |                  | Operating |                                          |                                |                  |  |  |

|                           |                                                            | W11              | W10       | Count source                             |                                |                  |  |  |

| W11                       | <b>-</b>                                                   | 0                | 0         | PWM signal (PWMOUT)                      |                                |                  |  |  |

|                           | Timer 1 count source selection bits (Note 3)               |                  | 1         | Prescaler output (ORCLK)                 |                                |                  |  |  |

| W10                       |                                                            | 1                | 0         | Timer 3 underflow signal (T3UDF)         |                                |                  |  |  |

| VV 10                     |                                                            | 1                | 1         | CNTR inp                                 | ut                             |                  |  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

Note2: This function is usable only when the timer 1 count start synchronization circuit is selected (110 = 1).

Note3: When CNTR input is selected for the timer 1 count source, the output of port C has no effect.

## 3.5 Timer Control Register W3

Table 3.5 shows the bit configuration of the Timer Control Register W3. For write to the register W3, first set a value in the register A and then use the TW3A instruction. Furthermore, the TAW3 instruction may be used to transfer the content of register W3 to the register A.

| Table 3.5 | Bit Configuration of 7 | Timer Control Register W3 |

|-----------|------------------------|---------------------------|

|-----------|------------------------|---------------------------|

| Timer control register W3 |                                    | at reset : 00002 |                        | 0002 | at power down : state retained | R/W<br>TAW3/TW3A |  |  |

|---------------------------|------------------------------------|------------------|------------------------|------|--------------------------------|------------------|--|--|

| W33                       | Timer 3 control bit                | 0                | 0 Stop (initial state) |      |                                |                  |  |  |

| VV 33                     |                                    | 1                | Operat                 | ing  |                                |                  |  |  |

|                           |                                    |                  | W31                    | W30  | Count value                    |                  |  |  |

| W32                       | W32                                | 0                | 0                      | 0    | Underflow every 512 count      |                  |  |  |

|                           |                                    | 0                | 0                      | 1    | Underflow every 1024 count     |                  |  |  |

|                           |                                    | 0                | 1                      | 0    | Underflow every 2048 count     |                  |  |  |

| W31                       | Timer 3 count value selection bits | 0                | 1                      | 1    | Underflow every 4096 count     |                  |  |  |

|                           |                                    | 1                | 0                      | 0    | Underflow every 8192 count     |                  |  |  |

|                           | W30                                | 1                | 0                      | 1    | Underflow every 16384 count    |                  |  |  |

| W30                       |                                    | 1                | 1                      | 0    | Underflow every 32768 count    |                  |  |  |

|                           |                                    | 1                | 1                      | 1    | Underflow every 65536 count    |                  |  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

## 3.6 Timer Control Register W5

Table 3.6 shows the bit configuration of the Timer Control Register W5. For write to the register W5, first set a value in the register A and then use the TW5A instruction. Furthermore, the TAW5 instruction may be used to transfer the content of register W5 to the register A.

| Table 3.6 | Bit Configuration of | f Timer Control Register W5 |

|-----------|----------------------|-----------------------------|

|-----------|----------------------|-----------------------------|

|      | Timer control register W5           | 5 at rese |         | 00002                                                | at power down : state retained     | R/W<br>TAW5/TW5A |  |  |

|------|-------------------------------------|-----------|---------|------------------------------------------------------|------------------------------------|------------------|--|--|

| W/52 | W53 Not used                        |           | This bi | it has no fu                                         | nction, but read/write is enabled. |                  |  |  |

| VV05 |                                     |           | This bi | it has no fu                                         | nction, but read/write is enabled. |                  |  |  |

| W/52 | W52 Not used                        |           | This bi | This bit has no function, but read/write is enabled. |                                    |                  |  |  |

| 1102 |                                     |           | This bi | This bit has no function, but read/write is enabled. |                                    |                  |  |  |

|      |                                     | W51       | W50     | Count source                                         |                                    |                  |  |  |

| W51  |                                     | 0         | 0       | Xcin input                                           |                                    |                  |  |  |

|      | Timer 3 count source selection bits | 0         | 1       | ORCLK in                                             | put                                |                  |  |  |

| W50  |                                     | 1         | 0       | Low-speed                                            | d on-chip oscillator               |                  |  |  |

| VV30 |                                     | 1         | 1       | High-speed on-chip oscillator                        |                                    |                  |  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

## 3.7 Port Output Mode Control Register FR1

Table 3.7 shows the bit configuration of the Port Output Mode Control Register FR1. For write to the register FR1, first set a value in the register A and then use the TFR1A instruction.

| Table 3.7 | Bit Configuration of F | Port Output Mode | Control Register FR1 |

|-----------|------------------------|------------------|----------------------|

|           |                        |                  |                      |

| P     | ort output structure control register FR1 | a | at reset : 00002            | at power down : state retained | W<br>TFR1A |  |  |

|-------|-------------------------------------------|---|-----------------------------|--------------------------------|------------|--|--|

| ED1a  | Ports D3 output structure selection bit   | 0 | N-channel open-drain output |                                |            |  |  |

| FN 13 |                                           | 1 | CMOS output                 |                                |            |  |  |

| ED1a  | Ports D2 output structure selection bit   | 0 | N-channel open-drain output |                                |            |  |  |

| FR12  |                                           | 1 | CMOS output                 |                                |            |  |  |

| ED14  | Ports D1 output structure selection bit   | 0 | N-channel open-c            | Irain output                   |            |  |  |

| FNI   |                                           | 1 | CMOS output                 |                                |            |  |  |

| ED10  | Ports Do output structure selection bit   | 0 | N-channel open-c            | Irain output                   |            |  |  |

|       |                                           | 1 | CMOS output                 |                                |            |  |  |

Note1: The letter W denotes "writable."

## 3.8 Port Output Mode Control Register FR2

Table 3.8 shows the bit configuration of the Port Output Mode Control Register FR2. For write to the register FR2, first set a value in the register A and then use the TFR2A instruction.

Table 3.8 Bit Configuration of Port Output Mode Control Register FR2

| P      | ort output structure control register FR2 | a | at reset : 00002 | at power down : state retained | W<br>TFR2A |  |  |  |

|--------|-------------------------------------------|---|------------------|--------------------------------|------------|--|--|--|

| FR23   | Ports P32 and P33 output structure        | 0 | N-channel open-c | N-channel open-drain output    |            |  |  |  |

| 11123  | selection bit                             | 1 | CMOS output      |                                |            |  |  |  |

| FR22   | Ports P30 and P31 output structure        | 0 | N-channel open-c | Irain output                   |            |  |  |  |

| FR22   | selection bit                             | 1 | CMOS output      | CMOS output                    |            |  |  |  |

| ED 24  | Ports D5 output structure selection bit   | 0 | N-channel open-c | Irain output                   |            |  |  |  |

| FRZI   |                                           | 1 | CMOS output      |                                |            |  |  |  |

| EP 20  | Ports D4 output structure selection bit   | 0 | N-channel open-c | Irain output                   |            |  |  |  |

| 1 1/20 |                                           | 1 | CMOS output      |                                |            |  |  |  |

Note1: The letter W denotes "writable."

## 3.9 Key-on Wakeup Control Register K3

Table 3.9 shows the bit configuration of the Key-on Wakeup Control Register K3. To write to the register K3, set any value in the register A and then use the TK3A instruction. Furthermore, the content of register K3 can be transferred to the register A using the TAK3 instruction.

#### Table 3.9 Bit Configuration of the Key-on Wakeup Control Register K3

|      | Key-on wakeup control register K3                                 | a              | at reset : 00002       | at power down : state retained | R/W<br>TAK3/TK3A |  |  |

|------|-------------------------------------------------------------------|----------------|------------------------|--------------------------------|------------------|--|--|

| K33  | Ports D6 and D7 key-on wakeup control bit                         | 0              | Key-on wakeup not used |                                |                  |  |  |

| 1005 | Tons be and brikey on wakeup control bit                          | 1              | Key-on wakeup u        | sed                            |                  |  |  |

| K32  | Ports D4 and D5 key-on wakeup control bit                         | 0 Key-on wakeu |                        | ot used                        |                  |  |  |

| 1102 | Tons by and bs key on wakeup control bit                          | 1              | Key-on wakeup used     |                                |                  |  |  |

| K31  | Ports D <sub>2</sub> and D <sub>3</sub> key-on wakeup control bit | 0              | Key-on wakeup n        | ot used                        |                  |  |  |

| N31  | Tons bz and bs key-on wakeup control bit                          | 1              | Key-on wakeup u        | sed                            |                  |  |  |

| K30  | Ports D <sub>0</sub> and D <sub>1</sub> key-on wakeup control bit | 0              | Key-on wakeup not used |                                |                  |  |  |

| 100  | Kou Ports Du and Di key-on wakeup controi bit                     | 1              | Key-on wakeup u        | sed                            |                  |  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

Note2: Unused bits when the staircase key matrix is set

## 3.10 Pullup Control Register PU3

Table 3.10 shows the bit configuration of the Pullup Control Register PU3. To write to the register PU3, set any value in the register A and then use the TPU3A instruction. Furthermore, the content of register PU3 can be transferred to the register A using the TAPU3 instruction.

#### Table 3.10 Bit Configuration of the Pullup Control Register PU3

|        | Pull-up control register PU3                       | â                    | at reset : 00002      | at power down : state retained R/W<br>TAPU3/TPU3A |  |  |  |

|--------|----------------------------------------------------|----------------------|-----------------------|---------------------------------------------------|--|--|--|

| PI 132 | Port De and D7 pull-up transistor control bit      |                      | Pull-up transistor    | OFF                                               |  |  |  |

| 1 005  |                                                    | 1                    | Pull-up transistor    | ON                                                |  |  |  |

|        | Port D4 and D5 pull-up transistor control bit      | 0 Pull-up transistor |                       | OFF                                               |  |  |  |

| 1 0 32 |                                                    |                      | Pull-up transistor ON |                                                   |  |  |  |

|        | Port D2 and D3 pull-up transistor control bit      |                      | Pull-up transistor    | OFF                                               |  |  |  |

| 1 031  |                                                    | 1                    | Pull-up transistor    | ON                                                |  |  |  |

|        | Port Do and D1 pull-up transietor control bit      |                      | Pull-up transistor    | OFF                                               |  |  |  |

| 1 0 30 | PU30 Port D0 and D1 pull-up transistor control bit | 1                    | Pull-up transistor    | ON                                                |  |  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

## 3.11 Clock Control Register RG

Table 3.11 shows the bit configuration of the Clock Control Register RG. To write to the register RG, set any value in the register A and then use the TRGA instruction.

#### Table 3.11 Bit Configuration of the Clock Control Register RG

|                 | Clock control register RG                | a                                                                      | at reset : 10002                                                        | at power down : state retained            | W<br>TRGA |  |  |

|-----------------|------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------|-----------|--|--|

| RG3             | Low-speed on-chip oscillator (f(LSOCO))  | SOCO)) 0 Low-speed on-chip oscillator (f(LSOCO)) oscillation available |                                                                         |                                           |           |  |  |

| 1.03            | control bit (Note 3)                     | 1                                                                      | Low-speed on-ch                                                         | ip oscillator (f(LSOCO)) oscillation stop |           |  |  |

| RG <sub>2</sub> |                                          | 0                                                                      | Sub-clock (f(Xcin)) oscillation available, ports D6 and D7 not selected |                                           |           |  |  |

| 102             |                                          | 1                                                                      | Sub-clock (f(Xcin)) oscillation stop, ports D6 and D7 selected          |                                           |           |  |  |

| RG1             | Main-clock (f(XIN)) control bit (Note 3) | 0                                                                      | Main clock (f(XIN)                                                      | ) oscillation available                   |           |  |  |

| KGI             |                                          | 1                                                                      | Main clock (f(XIN)                                                      | ) oscillation stop                        |           |  |  |

| RG <sub>0</sub> | High-speed on-chip oscillator (f(HSOCO)) | 0                                                                      | High-speed on-ch                                                        | ip oscillator (f(HSOCO)) oscillation avai | lable     |  |  |

|                 | control bit (Note 3)                     | 1                                                                      | High-speed on-chip oscillator (f(HSOCO)) oscillation stop               |                                           |           |  |  |

Note1: The letter W denotes "writable."

Note2: Unused bits when the staircase key matrix is set

Note3: The oscillator circuit selected for the system clock cannot be stopped.

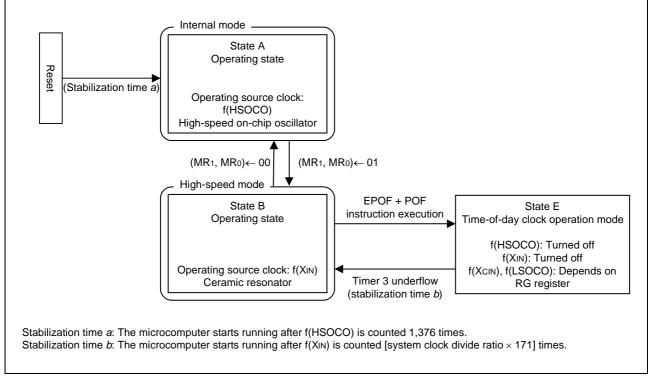

## 3.12 Clock Control Register MR

Table 3.12 shows the bit configuration of the Clock Control Register MR. To write to the register MR, set any value in the register A and then use the TMRA instruction. Furthermore, the content of register MR can be transferred to the register A using the TAMR instruction.

|                 | Clock control register MR            | at  | reset :         | 11002                       | at power down : state retained | R/W<br>TAMR/TMRA |  |

|-----------------|--------------------------------------|-----|-----------------|-----------------------------|--------------------------------|------------------|--|

|                 |                                      | MRз | MR2             |                             | Operation mode                 |                  |  |

| MRз             |                                      | 0   | 0               | Through m                   | node                           |                  |  |

|                 | Operation mode selection bits        | 0   | 1               | Frequency                   | / divided by 2 mode            |                  |  |

| MR2             |                                      | 1   | 0               | Frequency                   | / divided by 4 mode            |                  |  |

| IVITX2          |                                      | 1   | 1               | Frequency divided by 8 mode |                                |                  |  |

|                 |                                      | MR1 | MR <sub>0</sub> |                             | System clock                   |                  |  |

| MR1             |                                      | 0   | 0               | f(HSOCO)                    |                                |                  |  |

|                 | System clock selection bits (Note 2) | 0   | 1               | f(XIN)                      |                                |                  |  |

| MR <sub>0</sub> |                                      | 1   | 0               | f(Xcin)                     |                                |                  |  |

| IVIIXU          |                                      | 1   | 1               | f(LSOCO)                    |                                |                  |  |

Note1: The letter R denotes "readable," and the letter W denotes "writable."

Note2: No clocks that are turned off can be selected for the system clock.

## 4. Application Example of the Staircase Key Matrix

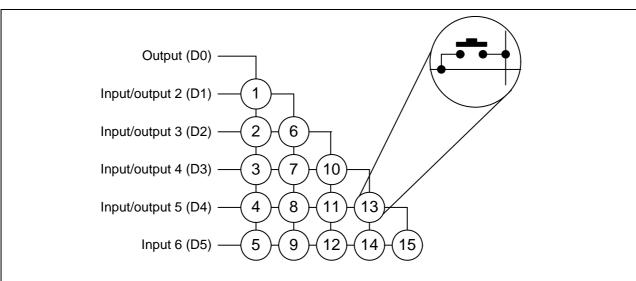

The staircase key matrix refers to the one where a key is located at all combinatorial positions of two shorted port pins in a key matrix configuration.

| Point         | : Up to 15 switches can be located at 6 input/output ports.                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|               | For the conventional key matrix using the same number of pins (consisting of 3 output ports $\times$ 3 input ports), a total number of keys is 9. |

|               | Therefore, the staircase key matrix permits a greater number of keys to be arranged than in the conventional key matrix.                          |

|               | However, if two or more keys are pressed at the same time, the matrix cannot determine which key                                                  |

|               | has been depressed.                                                                                                                               |

| Specification | : The matrix is reawaken by an underflow of a timer, and key numbers $(1-15)$ are stored in RAM according to the depressed key.                   |

|               | Furthermore, when multiple keys are pressed at the same time, key number 255 is assumed; when                                                     |

|               | no keys are entered, key number 0 is assumed.                                                                                                     |

|               | When the matrix confirms that no keys have been entered, it goes to time-of-day clock operation mode.                                             |

|               | Keys are scanned in a cycle of 9.984 ms.                                                                                                          |

|               | If the scan result matches twice in succession, a key is confirmed to have been pressed and a key                                                 |

|               | input confirmed flag is set.                                                                                                                      |

|               | If the result of successive key scans does not match, no keys are confirmed to have been pressed<br>and a key input confirmed flag is cleared.    |

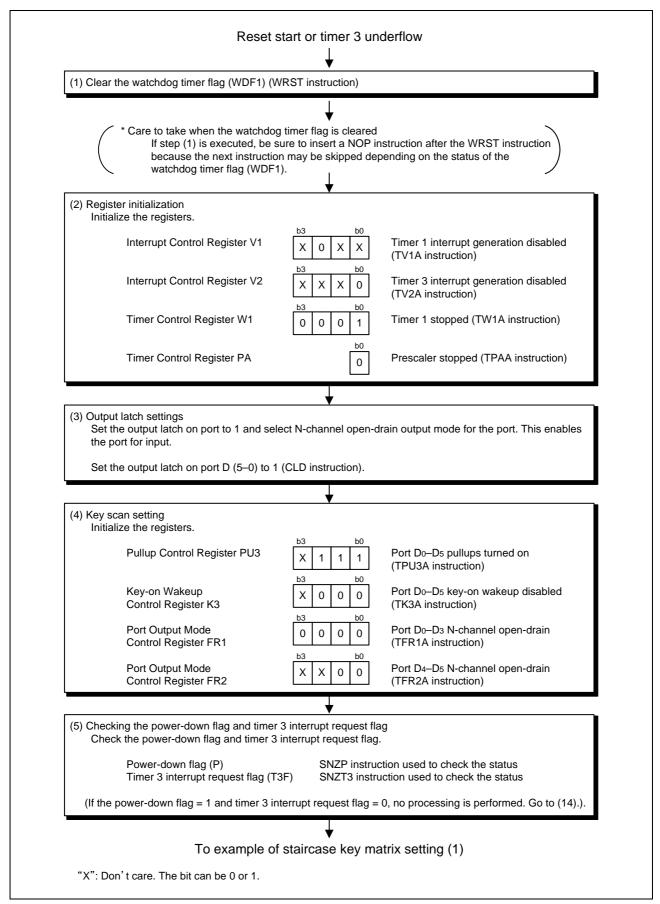

Figure 4.4 shows an example of staircase key matrix settings (1). Figure 4.5 shows an example of staircase key matrix settings (2). Figure 4.6 shows an example of staircase key matrix settings (3).

Figure 4.1 State Transition Diagram

#### <Key number assignments>

| Number of low level input ports | Key number | Supplement            |

|---------------------------------|------------|-----------------------|

| 0                               | 0          | No key input          |

| 1                               | 1–15       | Single key input      |

| 2 or more                       | 255        | Multiple keys pressed |

<Multiple key depressions>

If two or more keys are pressed at the same time, the matrix cannot determine which key is pressed.

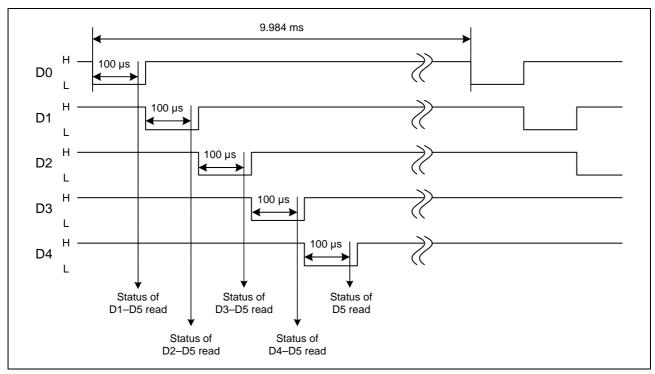

<How to count the number of low level input ports>

(1) Enable all ports (D0–D5) for input.

(Select N-channel open-drain output mode for the ports and set the output latches to 1.)

- (2) Output a low signal from the D0 port (setting its output latch to 0) and after waiting for a 100 µs or more, read the status of the D1–D5 ports. (Key scans for key numbers 1–5)

- (3) Enable the D0 port for input and terminate key scans on D0 port output.

- (4) In the same way, output a low signal from the D1–D4 ports in that order and perform key scans on each port output. At this time, do not check the status of a port that has had a signal already output from it.

<Return from power-save mode (time-of-day clock operation mode>

When using the staircase key matrix, be aware that if after RAM backup mode is entered into for power-save operation an attempt is made to return from power-save mode by a key-on wakeup, the microcomputer may not always be restored. (See \*1 below.) For this reason, in the sample program presented herein, the microcomputer enters time-ofday clock operation mode as it goes to power-save mode.

An underflow signal from timer 3 is used to return from time-of-day clock operation mode, so that the microcomputer is restored from power-save mode periodically (every 15.625 ms). Each time the microcomputer is restored from power-save mode, the key matrix is checked for key input.

\*1: For the key-on wakeup function to work effectively, the following conditions must be met.

- Scan output ports: Pullup is turned off, the wakeup function is disabled, and the port is set for low level output.

Scan input ports: Pullup is turned on, the wakeup function is enabled, and the port is placed in the high-impedance

- state.

In the sample program presented herein, however, since the scan output and scan input ports are not fixed, there is always a key depression that does not cause the microcomputer to reawake by key-on as in the following cases. For this reason, the microcomputer may not always be restored from RAM backup mode by a key-on wakeup.

• A key that shorts the ports together that are set for scan output is depressed.

• A key that shorts the ports together that are set for scan input is depressed.

<About pullup control>

In the sample program presented herein, the key matrix using only the D ports is designed by considering that all SEG pins are used for LCD display. Since the D ports are pulled high 2 bits at a time, there is a low level output from even a port that has no keys depressed during a key scan. Therefore, be aware that the current drain in the ports increases. The ports P2 and P3 can have their pull-ups turned on or off 1 bit at a time, so that use of these ports in key scans help to reduce the current drain in the ports.

Figure 4.2 Key Matrix Arrangement

Figure 4.3 Key Scan Timing Chart

Figure 4.4 Example of Staircase Key Matrix Setting (1)

|          | From example of staircase key matrix setting (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| Set      | er value settings<br>the prescaler and timer 1 count time. (Calculation formula is shown in *A below.)<br>Prescaler Reload Register RPS "FF16" Prescaler count value is set to 255 (TPSAB<br>instruction)<br>Timer 1 "3316" Timer count value is set to 51 (T1AB instruction)<br>(The same value is set in the Reload Register R1 at the same time by the T1AB instruction.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|          | $\downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 |

| Cle      | ring the timer 1 underflow flag<br>ar the timer 1 underflow flag.<br>Timer 1 Underflow Flag T1F "0" Timer 1 underflow flag cleared (SNZT1 instruction)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

|          | <ul> <li>* Care to take when the timer 1 underflow flag is cleared</li> <li>If step (7) is executed, be sure to insert a NOP instruction after the SNZT1 instruction because the next instruction may be skipped depending on the status of the timer 1 underflow flag T1F.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| Res      | mencement of timer and prescaler operation         start the timer 1 and prescaler that have been stopped.         ect the prescaler for the timer 1 count source.         Timer 1 Control Register W1       b3         b3       b0         Timer 1 Control Register W1       X         b0       1         b1       1         b2       0         b3       1         b4       1         b5       1         b6       1         b7       1         b7       1         b6       1         b7       1         b6       1         b7       1      < |   |

|          | ↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I |

|          | ring the RMA used<br>ar the RMA used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| (10) Cle | aring the watchdog timer flag (WDF1) (WRST instruction)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| (        | * Care to take when the watchdog timer flag is cleared<br>If step (10) is executed, be sure to insert a NOP instruction after the WRST<br>instruction because the next instruction may be skipped depending on the status of<br>the watchdog timer flag WDF1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| Ead      | ecking a key depression<br>ch time timer 1 underflows (every 9.984 ms), perform a key scan.<br>cput a signal from the ports in order beginning with port Do to check the input status of each port. (For<br>ails, see the key scan timing in Figure 4.3.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|          | To example of staircase key matrix setting (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|                                                                                                                                                                                                                                                                                                               | <b>\</b>                                                                                         |                                                                              |                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------|

| <ul> <li>(12) Setting key numbers</li> <li>If no low level inputs are detected, se</li> <li>If a low level input on one port is dete</li> <li>port. (Single key input)</li> <li>If a low level input on two or more poi</li> <li>* The above setting shows the result</li> <li>is made separately.</li> </ul> | ected, set any value (1<br>irts is detected, set 25                                              | –15) for the key<br>5 for the key nur                                        | number corresponding to each<br>nber. (Multiple key depressions) |

|                                                                                                                                                                                                                                                                                                               | •                                                                                                |                                                                              |                                                                  |

| flag.<br>(When not confirmed) Hold the curre                                                                                                                                                                                                                                                                  | n succession, determi<br>mine that no keys have<br>to have been pressed<br>number in the key inp | e been pressed.<br>d, perform the re<br>out confirmed RA<br>memory for the c | espective processing described                                   |

|                                                                                                                                                                                                                                                                                                               |                                                                                                  |                                                                              |                                                                  |

| <ul> <li>(14) Entering time-of-day clock operation<br/>If no key inputs are detected twice in<br/>mode ).</li> <li>* Timer 3 was turned off when w</li> <li>Timer Control Register W3</li> </ul>                                                                                                              | succession, go to pov                                                                            | Timer 3 count                                                                | value is set to generate an                                      |

| Timer Control Register W5                                                                                                                                                                                                                                                                                     | b3 b0<br>0 0 0 0                                                                                 |                                                                              | for the timer 3 count source ction)                              |

| Clear the timer 3 underflow flag.<br>Timer 3 Underflow Flag T3F                                                                                                                                                                                                                                               | "0" Time                                                                                         | er 3 underflow fla                                                           | ag cleared (SNZT3 instruction)                                   |

| *To run timer 3 during time-of-da<br>duration of time before the POF                                                                                                                                                                                                                                          | F instruction is execute                                                                         |                                                                              |                                                                  |

| Timer Control Register W3                                                                                                                                                                                                                                                                                     | b3 b0<br>1 0 0 0                                                                                 | Timer 3 starts                                                               | operating (TW3A instruction)                                     |

| Clearing the watchdog timer flag                                                                                                                                                                                                                                                                              | 3 (WDF1)                                                                                         | WRST instruc                                                                 | tion                                                             |

| *Be sure to insert a NOP instruc<br>skipped depending on the statu                                                                                                                                                                                                                                            |                                                                                                  |                                                                              | se the next instruction may be                                   |

| Interrupt Enable Flag INTE<br>Entering power-save mode<br>(time-of-day clock operation mod                                                                                                                                                                                                                    | "0"<br>de)                                                                                       |                                                                              | disabled (DI instruction)<br>tion + POF instruction              |

| In other cases, continue a 9.984 ms o                                                                                                                                                                                                                                                                         | cycle key scan. (Retur                                                                           | n to (10).)                                                                  |                                                                  |

| _                                                                                                                                                                                                                                                                                                             | $\checkmark$                                                                                     |                                                                              |                                                                  |

| To power-save                                                                                                                                                                                                                                                                                                 | mode (time-of-day                                                                                | / clock opera                                                                | tion mode)                                                       |

| *A To generate an interrupt every 9.984                                                                                                                                                                                                                                                                       | ms, set the prescaler                                                                            | count value and                                                              | timer 1 count value as shown belo                                |

| 9.984ms≒(4.0MHz) - 1 × 3<br>System clock Instruction                                                                                                                                                                                                                                                          | × (255+<br>Prescaler                                                                             | .~.~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                      | 51+1)<br>er 1 count                                              |

# 455A Group Staircase Key Matrix (Using Time-of-Day Clock Operation Mode)

### 5. Reference Documents

Data sheet 455A Group Data Sheet (The latest version is available from the Renesas Technology Web site.)

Technical news / Technical Update

(The latest information is available from the Renesas Technology Web site.)

## 6. Sample Programs

Sample programs are available from the Renesas Technology Web site. To download one, click the screen menu "Application Note" on the left side of 455A group Web site.

### Renesas Web Site and Where to Contact

Renesas Technology Web site: http://japan.renesas.com/

Where to contact: http://japan.renesas.com/inquiry csc@renesas.com

| Revision histor | 455A Group Staircase Key Matrix (Using Time-of-Day Clock<br>Operation Mode) |

|-----------------|-----------------------------------------------------------------------------|

|                 | · · · · · · · · · · · · · · · · · · ·                                       |

| Rev. | Date       | Description |                      |  |

|------|------------|-------------|----------------------|--|

|      |            | Page        | Points               |  |

| 1.00 | 2008.02.29 | -           | First edition issued |  |

|      |            |             |                      |  |

All trademarks and registered trademarks are the property of their respective owners.

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

#### © 2008. Renesas Technology Corp., All rights reserved.