# Using the RC32434/5 Verilog Model

## Notes

By Fred Santilo

## Introduction

The RC32434/5 is a member of the IDT<sup>™</sup> Interprise<sup>™</sup> family of PCI integrated communications processors. It incorporates a high performance CPU core and a number of on-chip peripherals. Using a highly sophisticated direct memory access (DMA) engine, the RC32434/5 integrated processor is designed to transfer information from I/O modules to main memory with minimal CPU intervention.

The RC32434/5 Verilog Model is a bus functional model designed to be used in a simulation environment with other verilog device models to simulate a system, thus enabling the designer to verify connectivity and functionality of the devices being used in the system prior to physically building the system. This document describes the contents of the RC32434/5 Verilog Model package and how to compile and run the model.

# Contents of the Verilog Model Package

The RC32434/5 Verilog Model package, rc434\_bfm.tar, is comprised of the following files:

- jade\_vmc\_model.vcs.v Protected form of the MIPS 4Kc ("Jade") RTL using the SWIFT language.

- all\_rtl-jade.vp Encrypted RC32438 RTL (except the Jade core).

- boot\_mem.v 8-bit wide boot ROM model attached to chip select 0 csn[0].

- mt46v16m16.v Micron Technology DDR memory model attached to DDR chip select 0 ddrcsn[0].

- Makefile Used to compile the executable VCS simulator.

- memory.jade\_config Used to customize MIPS-4Kc VMC model, however, this file should not require modification. See MIPS 4Kc Integrator's guide documentation for more details.

- system.v Top-level Verilog file that instantiates everything and creates the clocks and resets.

- program.srec Sample program S-Record file.

- program.dis Sample program disassembly file.

- memmod0\_0.mem 8-bit wide hex memory image loaded by the boot memory model.

- memmake Perl script that calls srec2mem and memsplit scripts with parameters.

- srec2mem Executable for Solaris that converts S-Records into an intermediate memory image.

- memsplit Executable for Solaris that converts the output of srec2mem into an 8-bit wide memory image required by the boot\_mem.v model.

The sample boot code provided is automatically loaded into the boot memory model at startup. However, customized boot code can be substituted by replacing one or both of the hex image files. The helper scripts (memmake, srec2mem, and memsplit) are provided to convert the S-Records into the required hex format.

Notes

# Additional Requirements

To compile and run the RC32434/5 Verilog Model the user must have the following licenses and tools:

- FlexLM License File Required for the Jade VMC model (www.mips.com).

- VCS 6.1 (Synopsys) Used to compile the model. Note that only version 6.1 has been tested.

- SignalScan or other waveform viewer tool.

## Test Bench

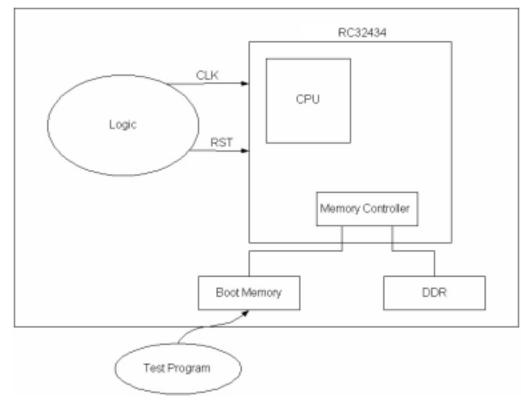

Figure 1 shows the sample test bench used in this model. Designers can vary this test bench as required.

#### Figure 1 RC32434/5 Sample Test Bench

# Using the Verilog Model

This section describes the various steps involved in compiling and running the RC32434/5 model.

## **Getting Started**

Extract the compressed files from the rc32434\_bfm.tar file. The files will be extracted to a folder called "rc32434\_bfm". Also, verify the Flex license from MIPS, any other necessary license(s), and the tools are correctly installed.

Notes

#### Compiling the Verilog Simulator

a) Customize the Makefile as follows:

- Choose the appropriate VCS command/path.

- Link the desired PLI for signal dumping (e.g. Signal Scan, Debussy, etc.).

- Add RTL files for other models if desired.

b) Customize the system.v file as follows:

- If desired, instantiate additional device models.

- If desired, modify clocks, resets, pull up/down resistors, etc.

- If desired, modify the boot vector (configuration data latched by the processor during cold reset).

- If desired, modify Signal Scan recording options.

c) Type 'gmake' to build the rc32434\_bfm executable.

## Compiling a Test

If you are using the included sample test, skip this part and go to the next section, Running a Simulation.

If you are <u>not</u> using the included sample test, perform the following steps:

- Generate an S-Record file of the test you would like to perform with your compiler/tool.

- Convert the .srec format into a hex format required by the boot memory model. The following three helper scripts are provided for this:

memmake — Perl script that calls the srec2mem and memsplit scripts with parameters.

srec2mem — Executable for Solaris that converts the S-Records into an intermediate memory image.

memsplit — Executable for Solaris that converts that output of srec2mem into the 8-bit wide memory image file required by the boot memory model.

## **Running a Simulation**

Type 'rc32434\_bfm' at the command line prompt. The simulation will automatically terminate when it has reached the end. However, the designer can terminate the simulation while it is running by writing to the special offset address of 0x300000 in Device0 space.

# Conclusion

The RC32434/5 Verilog Model is easy to implement as a stand-alone or system test bench using the files contained in the RC32434/5 Verilog Model Package. Following the steps outlined in this document will ensure ease of model integration into a system level simulation test environment.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.