# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

## ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# 7547グループ レジスター覧

## 1. 要約

この資料は7547グループのレジスタについて説明しています。

### 2. はじめに

この資料で説明するレジスタは次の条件での利用に適用されます。

・マイコン:7547グループ

## 3. レジスタ構成図

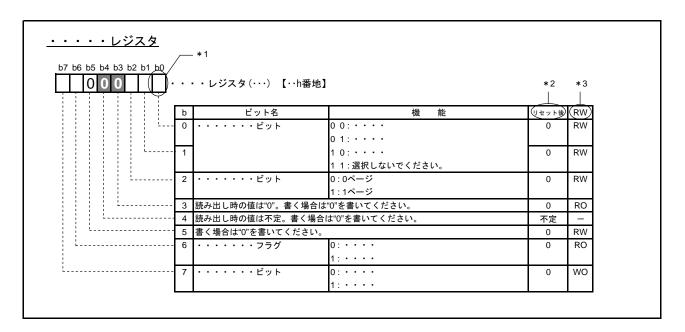

このアプリケーションノートに掲載している制御レジスタ構成図の例と、その中で使用されている略号などの意味を以下に示します。

\* 1

空白:用途に応じて"0"又は"1"を設定してください。

0 :書く場合は"0"を書いてください。

:書く場合は"1"を書いてください。 、 :特定のモード又は状態で使用しないビット。"0"又は"1"いずれでもよい。

:何も配置されていない。

\* 2 0

:リセット後"0"になる。

1 :リセット後"1"になる。

不定:リセット後、不定になる。

\* 3

RW:読み出し可能。書き込み可能。

RO :読み出し可能。書く場合の値は、それぞれのビットに依存します。

WO :書き込み可能。読み出し時の値は不定。

一:読み出し時の値は不定。書く場合の値は、それぞれのビットに依存します。

# 4. レジスタの説明

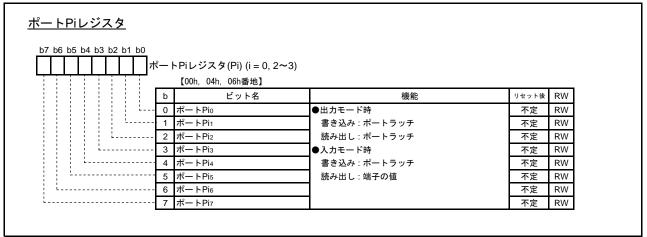

図4.1 ポートPiレジスタの構成 (i = 0, 2~3)

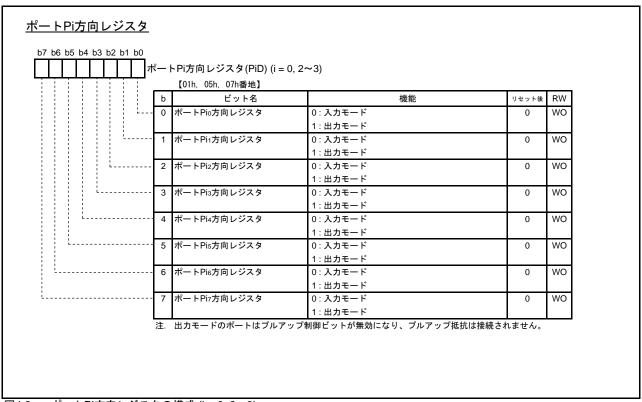

図4.2 ポートPi方向レジスタの構成 (i = 0, 2~3)

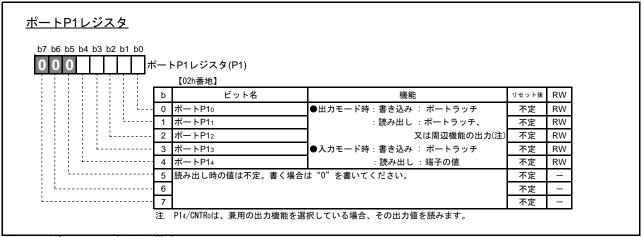

図4.3 ポートP1レジスタの構成

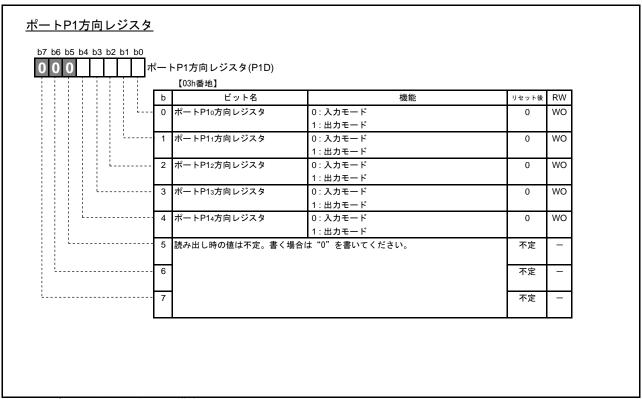

図4.4 ポートP1方向レジスタの構成

#### 割り込み要因設定レジスタ b7 b6 b5 b4 b3 b2 b1 b0 割り込み要因設定レジスタ(INTSET) 【OAh番地】 ビット名 機能 リセット後 RW キーオンウェイクアップ 0:割り込み無効 RW 割り込み有効ビット 1:割り込み有効 UART1バス衝突検出 0:割り込み無効 0 RW 割り込み有効ビット 1:割り込み有効 2 A/D変換 0:割り込み無効 0 RW 割り込み有効ビット 1:割り込み有効 RW 3 タイマ1 0:割り込み無効 0 割り込み有効ビット 1:割り込み有効 読み出し時の値は"0"。書く場合は"0"を書いてください。 4 RO 0 5 0 RO 6 0 RO 0 RO

割り込み要因設定レジスタの構成 図4.5

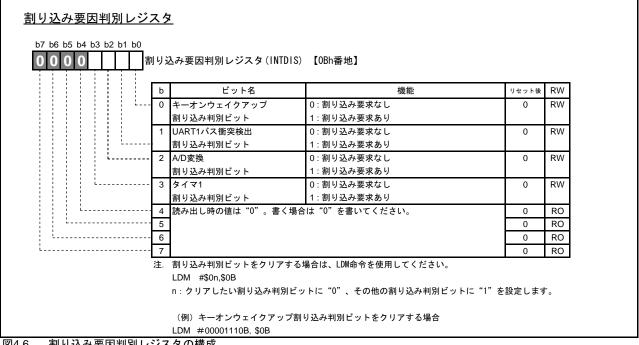

図4.6 割り込み要因判別レジスタの構成

#### <u>キャプチャレジスタi(下位)</u> b7 b6 b5 b4 b3 b2 b1 b0 キャプチャレジスタi(CAPiL) (i = 0, 1) 【0Ch, 0Eh番地】 ビット名 機能 リセット後 RW 0 ・キャプチャ入力にてタイマのカウント値(下位)の読み出しを行うレジスタです。 RO 不定 ・キャプチャレジスタの読み出しは、キャプチャレジスタリードポインタで制御します。 RO キャプチャレジスタからの読み出し手順は、次の様になります。 不定 RO RO 3 ①キャプチャレジスタリードポインタに読み出したいキャプチャラッチを設定する。 不定 4 ②キャプチャレジスタ(下位)とキャプチャレジスタ(上位)を読 み出す。 不定 RO 5 ・キャプチャレジスタの下位と上位を読み出している間にキャプチャトリガが入力された場合、 不定 RO 6 下位と上位の値は別々のタイミングでキャプチャされた値となりますので 不定 RO ソフトウェアで複数回の読み出し結果を比較する等の対策を行ってください。 不定 RO

図4.7 キャプチャレジスタi(下位)の構成

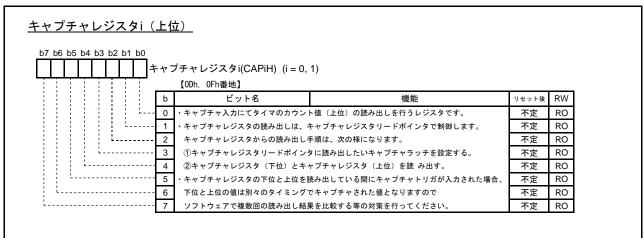

図4.8 キャプチャレジスタi(上位)の構成

#### <u>コンペアレジスタ(下位)</u> b7 b6 b5 b4 b3 b2 b1 b0 コンペアレジスタ(CMPL)【10h番地】 ビット名 機能 RW リセット後 0 ・コンペア出力にてタイマのカウント値(下位)を設定するレジスタです。 WO ・書き込み手順は、コンペアレジスタR/W ポインタに書き込み先のコンペア 1 0 WO チャネルを設定し、コンペアレジスタ(下位)とコンペアレジスタ(上位) 0 WO 3 に値を設定します。 0 WO 4 0 WO 5 0 WO 6 0 WO 7 0 WO 注1. それぞれのコンペアチャネルのソースとして選択しているタイマが停止している場合、 コンペアレジスタに値を書き込んだ時点でコンペアラッチにも値が転送されます。 $\hat{x}$ コンペアラッチx0 とコンペアラッチx1 には、同一の値を設定しないでください (x = 0, 1, 2, 3)。 注3. コンペアレジスタの設定値がタイマの設定値より大きい場合はコンペア一致の信号を発生しません。 従って出力波形は "H" 又は "L" レベルに固定されます。ただし、もう一方のコンペアレジスタの 設定値がタイマの設定値より小さい場合には、小さい側のコンペアー致の信号は発生しますので、 コンペアー致割り込みは発生します。

図4.9 コンペアレジスタ(下位)の構成

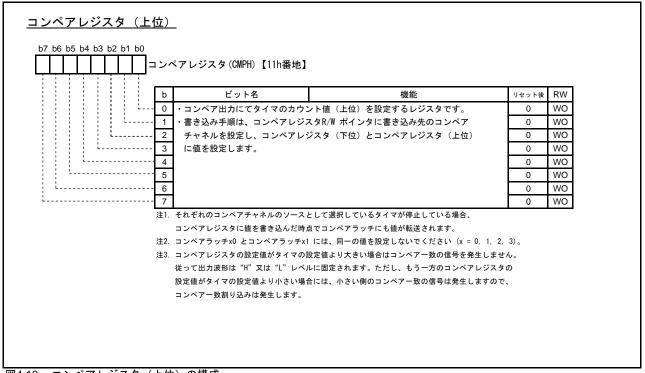

図4.10 コンペアレジスタ (上位) の構成

#### <u>キャプチャ/コンペアレジスタR/Wポインタ</u> b7 b6 b5 b4 b3 b2 b1 b0 キャプチャ/コンペアレジスタR/Wポインタ(CCRP) 【12h番地】 0 ビット名 機能 リセット後 RW b 0 コンペアレジスタR/Wポインタ b2 b1 b0 RW 000:コンペアラッチ00 001:コンペアラッチ01 1 010: コンペアラッチ10 0 RW 011:コンペアラッチ11 100:コンペアラッチ20 101:コンペアラッチ21 2 0 RW 110: コンペアラッチ30 111:コンペアラッチ31 3 読み出し時の値は "0"。書く場合は "0"を書いてください。 0 RO 4 キャプチャレジスタ0 0: キャプチャラッチ00 0 RW R/Wポインタ 1 : キャプ<u>チャラッチ01</u> 5 キャプチャレジスタ1 0: キャプチャラッチ10 RW 1:キャプチャラッチ11 R/Wポインタ 6 読み出し時の値は"0"。書く場合は"0"を書いてください。 RO 0 0 RO

図4.11 キャプチャ/コンペアレジスタR/Wポインタの構成

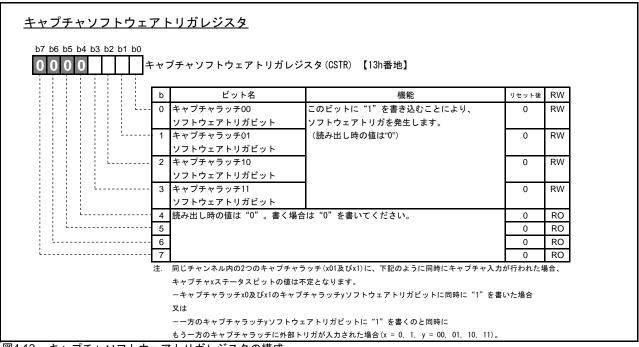

図4.12 キャプチャソフトウェアトリガレジスタの構成

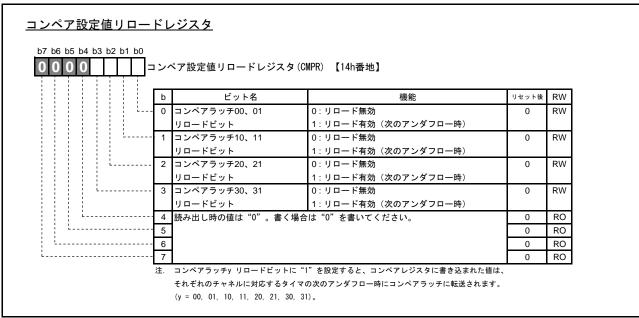

図4.13 コンペア設定値リロードレジスタの構成

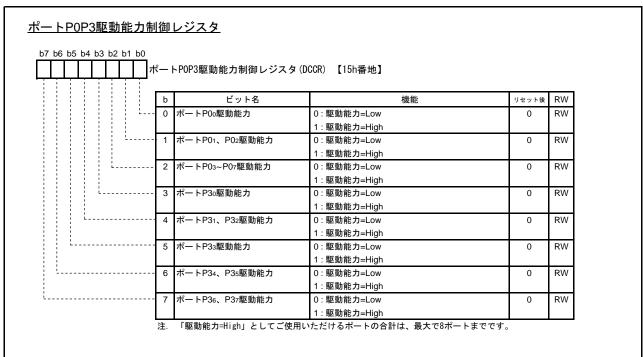

図4.14 ポートP0P3駆動能力制御レジスタの構成

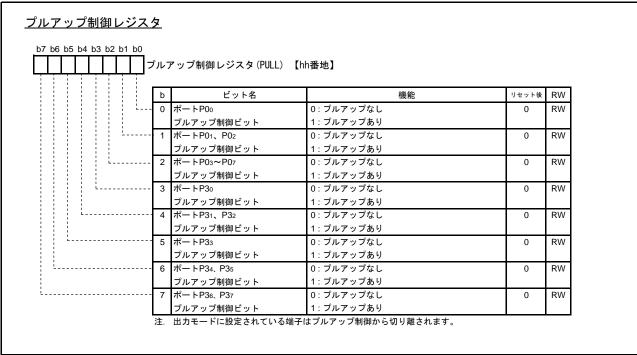

図4.15 プルアップ制御レジスタの構成

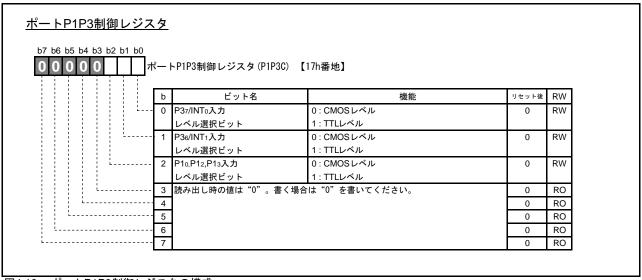

図4.16 ポートP1P3制御レジスタの構成

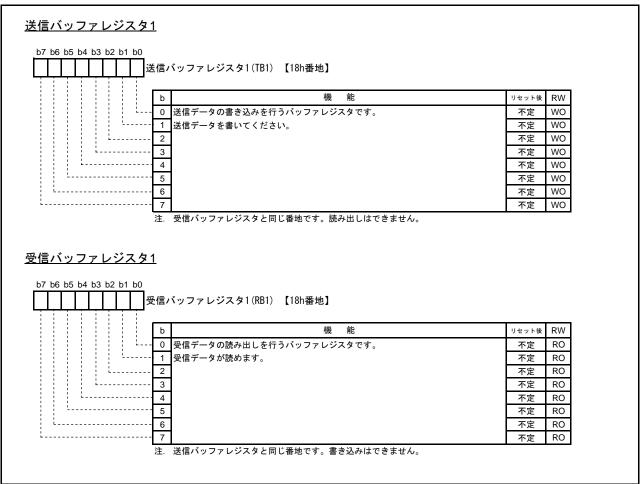

図4.17 送信バッファレジスタ1及び受信バッファレジスタ1の構成

#### <u>シリアルI/O1ステータスレジスタ</u> b7 b6 b5 b4 b3 b2 b1 b0 シリアルI/01ステータスレジスタ(SI01STS) 【19h番地】 ビット名 機能 リセット後 RW b 0 送信バッファエンプティ 0: バッファレジスタフル状態 RO フラグ(TBE) 1: バッファレジスタエンプティ状態 受信バッファフルフラグ 0: バッファレジスタエンプティ状態 0 RO (RBF) (注1、2) 1: バッファレジスタフル状態 2 送信シフトレジスタシフト 0: 送信シフト中 0 RO 1:送信シフト終了 終了フラグ(TSC) (注1) 0: オーバランエラーなし オーバランエラーフラグ 0 RO (OE) (注3) 1: オーバランエラー発生 パリティエラ**ー**フラグ RO 0:パリティエラーなし 0 (PE) 1: パリティエラー発生 (注3) フレーミングエラーフラグ 0: フレーミングエラーなし RΩ 0 5 (FE) 1: フレーミングエラー発生 (注3) サミングエラーフラグ 0: (OE)U(PE)U(FE) = 06 0 RO (SE) (注3) 1 : (OE)U(PE)U(FE) = 1 7 読み出し時の値は"1"。書く場合は"1"を書いてください。 RO 注1. 書く場合は"0"を書いてください。 注2. 受信バッファレジスタを読み出すと"0"にクリアされます。 注3. このレジスタへの書き込みで、このビットは"0"になります。書く場合は"0"を書いてください。

図4.18 シリアルI/O1ステータスレジスタの構成

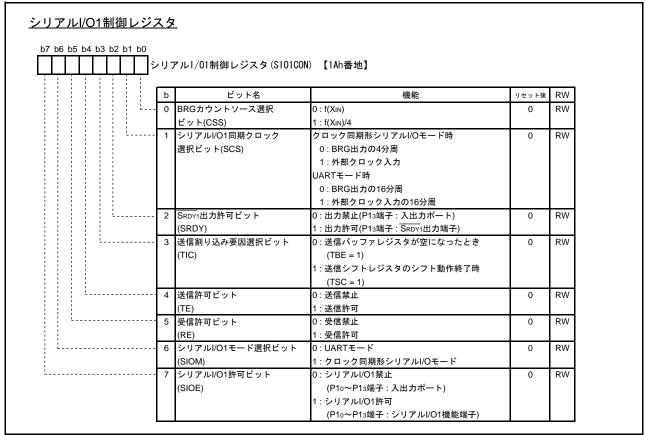

図4.19 シリアルI/O1制御レジスタの構成

#### UART1制御レジスタ b7 b6 b5 b4 b3 b2 b1 b0 UART1制御レジスタ(UART1CON) 【1Bh番地】 ビット名 機能 リセット後 RW 0 キャラクタ長選択ビット 0:8ビット RW 1:7ビット (CHAS) パリティ許可ビット 0:パリティ禁止 0 RW (PARE) 1: パリティ許可 2 パリティ選択ビット 0:偶数パリティ 0 RW (PARS) 1: 奇数パリティ ストップビット長選択ビット 0:1ストップビット RW 0 (STPS) 1:2ストップビット P11/TxD1Pチャネル出力禁止 0 RW 出力モード時 ビット(POFF) 0:CMOS出力 1 : Nチャネルオープンドレイン出力 入力モード時、このビットは無効 5 読み出し時の値は"1"。書く場合は"1"を書いてください。 RO RO RO

図4.20 UART1制御レジスタの構成

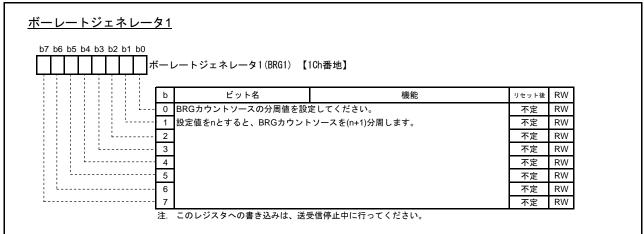

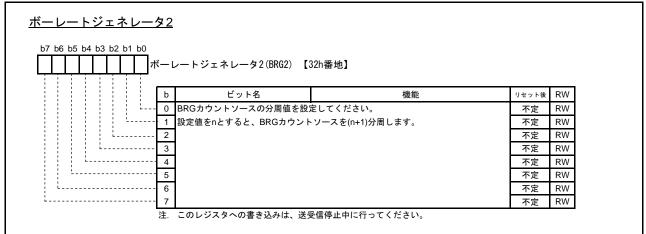

図4.21 ボーレートジェネレータ1の構成

#### <u>タイマA,Bモードレジスタ</u> b7 b6 b5 b4 b3 b2 b1 b0 タイマA, Bモードレジスタ(TABM) 【1Dh番地】 ビット名 機能 リセット後 RW 0 タイマA書き込み制御ビット 0:ラッチ及びタイマ同時書き込み RW 1: ラッチのみ書き込み タイマAカウント停止ビット 0:カウント開始 0 RW 1: カウント停止 2 タイマB書き込み制御ビット 0:ラッチ及びタイマ同時書き込み 0 RW 1:ラッチのみ書き込み 3 タイマBカウント停止ビット 0:カウント開始 0 RW 1: カウント停止 4 読み出し時の値は"0"。書く場合は"0"を書いてください。 RO 0 0 RO 6 コンペア0、1変調モードビット 0 · 埜止 0 RW 1:許可 コンペア2、3変調モードビット 0·埜止 RW 0 1:許可 注、タイマA.B書き込み制御ビットを「ラッチのみ書き込み」に設定している場合は、 タイマの停止中であっても、書き込みデータはラッチのみに書き込まれます。 したがって、タイマの初期設定において、タイマの停止中に値を設定する場合は、 「ラッチ及びタイマ同時書き込み」を選択した状態で行ってください。

図4.22 タイマA,Bモードレジスタ

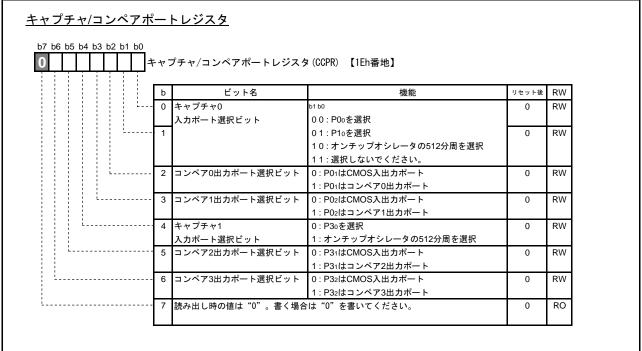

図4.23 キャプチャ/コンペアポートレジスタの構成

RW

RW

### <u>キャプチャ/コンペアタイマソース選択レジスタ</u>

b7 b6 b5 b4 b3 b2 b1 b0

|                | b | ビット名           | 機能              | リセット後 | RW |

|----------------|---|----------------|-----------------|-------|----|

|                | 0 | コンペア0タイマソース    | 0:タイマA          | 0     | RW |

|                |   | 選択ビット          | 1:タイマB          |       |    |

| <del> </del> - | 1 | コンペア1タイマソース    | 0:タイマA          | 0     | RW |

|                |   | 選択ビット          | 1:タイマB          |       |    |

|                | 2 | コンペア2タイマソース    | 0:タイマA          | 0     | RW |

|                |   | 選択ビット          | 1:タイマB          |       |    |

|                |   | コンペア3タイマソース    | 0:タイマA          | 0     | RW |

|                |   | 選択ビット          | 1:タイマB          |       |    |

| 4              |   | キャプチャ0タイマソース   | 0:タイマA          | 0     | RW |

|                |   | 選択ビット          | 1:タイマB          |       |    |

|                | 5 | キャプチャ1タイマソース   | 0:タイマA          | 0     | RW |

|                |   | 選択ビット          | 1:タイマB          |       |    |

| 6              |   | 読み出し時の値は"0"。書く | 場合は"0"を書いてください。 | 0     | RO |

| i              | 7 |                |                 | 0     | RΩ |

- 注1. CPUの動作クロック源がXIN発振の場合で、タイマAのカウントソースにオンチップオシレータ出力を選択している 場合は、タイマAはキャプチャ入力のソースタイマとして使用できません。

- 注2. CPUの動作クロック源がXIN発振の場合で、タイマBのカウントソースにタイマAアンダフローを選択し、かつタイマAのカウントソースにオンチップオシレータ出力を選択している場合は、タイマBはキャプチャ入力のソースタイマとして使用できません。

図4.24 キャプチャ/コンペアタイマソース選択レジスタの構成

<u>キャプチャモードレジスタ</u>

#### b7 b6 b5 b4 b3 b2 b1 b0 キャプチャモードレジスタ(CAPM) 【20h番地】 機 能 リセット後 RW Ω キャプチャ0割り込みエッジ b1 b0 0 RW 選択ビット 00:立ち上がり及び立ち下がりエッジ 1 01:立ち上がりエッジ 0 RW 10:立ち下がりエッジ 11:選択禁止 2 キャプチャ1割り込みエッジ o3 b2 RW 0 選択ビット 00:立ち上がり及び立ち下がりエッジ 01:立ち上がりエッジ RW 3 0 10:立ち下がりエッジ 11:選択禁止 4 キャプチャ0ノイズフィルタ o5 b4 0 RW 00:フィルタなし 選択ビット 5 0 1 : f(XIN) 0 RW

注1. 外部割り込みCAPO, CAP1 の割り込みエッジ選択ビット及びノイズフィルタ選択ビットを設定する際、割り込み要求 ビットが"1"になる場合があります。割り込みエッジ選択ビット又はノイズフィルタ選択ビットの設定に同期

1 0 : f(XIN)/8 1 1 : f(XIN)/32

0 1 : f(XIN)

1 0 : f(XIN)/8 1 1 : f(XIN)/32

00:フィルタなし

b7 b6

した割り込みが不要な場合には以下の手順で設定してください。 ①該当する割り込み許可ピットを"0" (禁止) にする。

6 キャプチャ1ノイズフィルタ

選択ビット

- ②割り込みエッジ選択ビット又はノイズフィルタ選択ビットを設定する。

- ③一命令以上おいてから、該当する割り込み要求ビットを"0"にする。

- ④該当する割り込み許可ビットを"1" (許可) にする。

- 注2. キャプチャ割り込みをストップモードからの復帰用割り込みとして使用する場合は、キャプチャx ノイズフィルタ 選択ビットを "00:フィルタなし" に設定してください  $(x=0,\ 1)$ 。

図4.25 キャプチャモードレジスタの構成

#### コンペア出力モードレジスタ b7 b6 b5 b4 b3 b2 b1 b0 コンペア出力モードレジスタ(CMOM) 【21h番地】 ビット名 機能 リセット後 RW 0 コンペア0出力レベルラッチ 0:正極性出力 RW 1: 反極性出力 コンペア1出力レベルラッチ 0:正極性出力 0 RW 1: 反極性出力 2 コンペア2出力レベルラッチ 0:正極性出力 0 RW 1:反極性出力 3 コンペア3出力レベルラッチ 0:正極性出力 0 RW 1: 反極性出力 4 コンペア0トリガ有効ビット RW 0:トリガ無効 0 1:トリガ有効 5 コンペア1トリガ有効ビット RW 0:トリガ無効 0 1:トリガ有効 6 コンペア2トリガ有効ビット 0:トリガ無効 0 RW 1:トリガ有効 7 コンペア3トリガ有効ビット 0:トリガ無効 RW 1:トリガ有効 注. コンペア x トリガ有効ビットに "0" (無効)を設定すると、波形出力回路への一致トリガは禁止されるので、 出力波形を "H" 又は "L" に固定できます。ただし、この場合でもコンペア一致の信号は発生するので コンペアー致割り込みの発生は可能です (x = 0, 1, 2, 3)。

図4.26 コンペア出力モードレジスタの構成

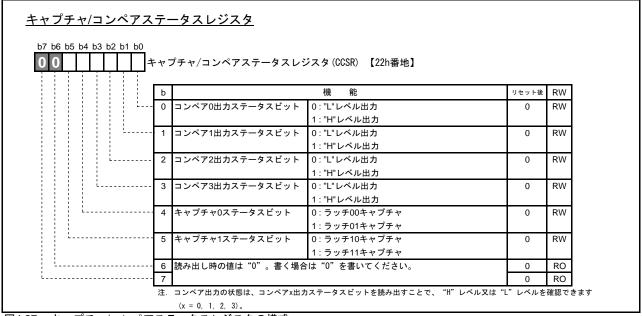

図4.27 キャプチャ/コンペアステータスレジスタの構成

#### <u>コンペア割り込みソース設定レジスタ</u> b7 b6 b5 b4 b3 b2 b1 b0 コンペア割り込みソース設定レジスタ(CISR) 【23h番地】 ビット名 機能 RW リセット後 0 コンペアラッチ00 0:無効 RW 1:有効 割り込みソースビット コンペアラッチ01 0:無効 0 RW 割り込みソースビット 1:有効 2 コンペアラッチ10 0:無効 0 RW 割り込みソースビット 1:有効 コンペアラッチ11 0:無効 0 RW 割り込みソースビット 1:有効 コンペアラッチ20 0:無効 0 RW 割り込みソースビット 1:有効 5 コンペアラッチ21 0:無効 0 RW 割り込みソースビット 1:有効 コンペアラッチ30 6 0:無効 RW 0 割り込みソースビット 1:有効 コンペアラッチ31 RW 0:無効 0 割り込みソースビット 1:有効 注. コンペア出力割り込みは、コンペアラッチの値とタイマカウント値が一致するタイミングで発生することができます。 それぞれのコンペアラッチからの割り込み信号は、コンペアラッチy 割り込みソース設定ビットで、有効又は無効に 設定できます (y = 00, 01, 10, 11, 20, 21, 30, 31)。

図4.28 コンペア割り込みソース設定レジスタの構成

#### <u>タイマA上位レジスタ、タイマA下位レジスタ</u> b7 b6 b5 b4 b3 b2 b1 b0 タイマA上位レジスタ(TAH)、タイマA下位レジスタ(TAL) 【25h番地、24h番地】 ビット名 機能 リセット後 RW 0 タイマAのカウント値を設定します。 RW ・書き込みを行う場合、タイマA書き込み制御ビットの設定値により、 1 RW ラッチ及びタイマAの両方に書き込むか、ラッチのみに書き込むかを選択できます。 RW 3 RW 下位、上位の順で必ず両レジスタ共に書き込んでください。 1 4 RW 5 ・このレジスタを読み出すと、タイマAのカウント値が読み出されます。 RW 6 上位、下位の順で必ず両レジスタ共に読み出してください。 1 RW 7 RW 注. CPU の動作クロック源がXIN 発振の場合で、タイマA のカウントソースにオンチップオシレータ出力を選択している場合は、 タイマA への書き込み及び読み出しはタイマA を停止した状態で行ってください。

図4.29 タイマA上位レジスタ、タイマA下位レジスタの構成

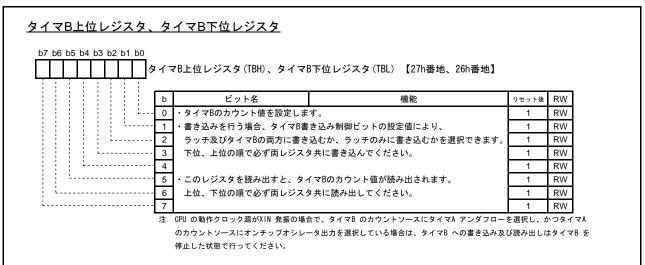

図4.30 タイマB上位レジスタ、タイマB下位レジスタの構成

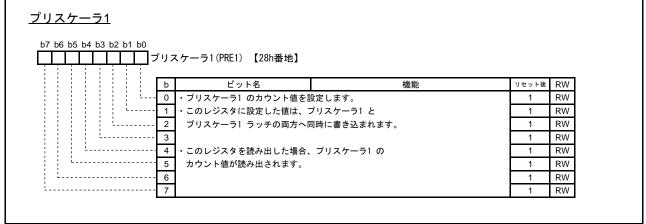

図4.31 プリスケーラ1の構成

#### <u>タイマ1レジスタ</u> b7 b6 b5 b4 b3 b2 b1 b0 タイマ1(T1) 【29h番地】 機能 RW リセット後 0 ・タイマ1のカウント値を設定します。 RW ・このレジスタに設定した値は、タイマ1 とタイマ1 0 RW 1 ラッチの両方へ同時に書き込まれます。 0 RW 3 RW ・このレジスタを読み出した場合、タイマ1の 0 4 カウント値が読み出されます。 0 RW 5 0 RW 6 0 RW 0 RW

図4.32 タイマ1レジスタの構成

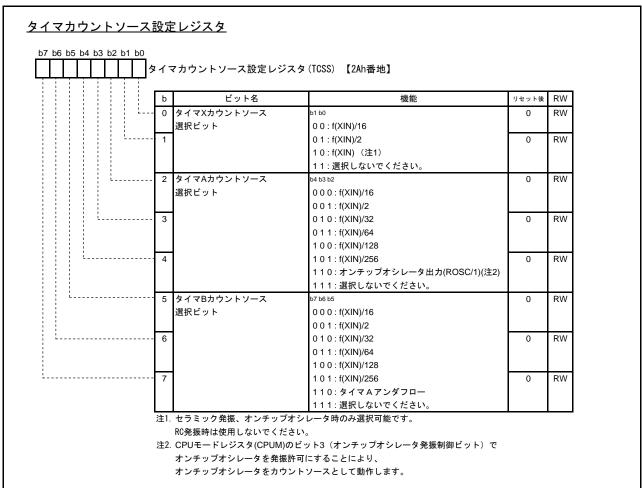

図4.33 タイマカウントソース設定レジスタの構成

### <u>タイマXモードレジスタ</u>

b7 b6 b5 b4 b3 b2 b1 b0

**000** タイマXモードレジスタ(TXM) 【2Bh番地】

|   |       | b | ビット名             | 機能                | リセット後 | RW |

|---|-------|---|------------------|-------------------|-------|----|

|   |       | 0 | タイマX動作モードビット     | b1 b0             | 0     | RW |

|   |       |   |                  | 0 0:タイマモード        |       |    |

|   | 1 1 1 | 1 |                  | 0 1:パルス出力モード      | 0     | RW |

|   |       |   |                  | 10:イベントカウンタモード    |       |    |

|   |       |   |                  | 1 1:パルス幅測定モード     |       |    |

|   | 1     | 2 | CNTRo極性切り替えビット   | タイマXの動作モードにより異なる。 | 0     | RW |

|   |       |   |                  | (表4.1を参照)         |       |    |

|   | ļ L   | 3 | タイマXカウント停止ビット    | 0: カウント動作         | 0     | RW |

|   |       |   |                  | 1: カウント停止         |       |    |

|   | i     | 4 | P0₃/TXouт出力有効ビット | 0:出力無効(入出力ポート)    | 0     | RW |

|   |       |   |                  | 1:出力有効(CNTRO反転出力) |       |    |

|   |       | 5 | 読み出し時の値は"0"。書く場  | 合は"0"を書いてください。    | 0     | RO |

| 1 | 6     |   | ]                |                   | 0     | RO |

| i |       | 7 | 1                |                   | 0     | RO |

注. 外部割り込みCNTROの極性切り替えビットを切り替える際、割り込み要求ビットが"1"になる場合があります。

極性切り替えビットの設定に同期した割り込みが不要な場合には以下の手順で設定してください。

①該当する割り込み許可ビットを"0"(禁止)にする。

②極性切り替えビットを設定する。

③一命令以上おいてから、該当する割り込み要求ビットを"0"にする。

④該当する割り込み許可ビットを"1"(許可)にする。

図4.34 タイマXモードレジスタの構成

表4.1 CNTRo極性切り替えビットの機能

| タイマX動作モード   | 設定値 | タイマ機能の選択           | CNTRo割り込み要求発生要因     |

|-------------|-----|--------------------|---------------------|

| タイマモード      | "0" |                    | CNTRoの入力信号の立ち下がりエッジ |

|             |     |                    | (タイマのカウントに影響なし)     |

|             | "1" |                    | CNTRoの入力信号の立ち上がりエッジ |

|             |     |                    | (タイマのカウントに影響なし)     |

| パルス出力モード    | "0" | パルス出力開始 : "H" から出力 | 出力信号の立ち下がりエッジ       |

|             | "1" | パルス出力開始 : "L" から出力 | 出力信号の立ち上がりエッジ       |

| イベントカウンタモード | "0" | 立ち上がりエッジをカウント      | 入力信号の立ち下がりエッジ       |

|             | "1" | 立ち下がりエッジをカウント      | 入力信号の立ち上がりエッジ       |

| パルス幅測定モード   | "0" | "H" 幅を測定           | 入力信号の立ち下がりエッジ       |

|             | "1" | "L" 幅を測定           | 入力信号の立ち上がりエッジ       |

#### <u>プリスケーラX</u> b7 b6 b5 b4 b3 b2 b1 b0 プリスケーラX(PREX) 【2Ch番地】 ビット名 RW 機能 リセット後 0 ・プリスケーラXのカウント値を設定します。 RW 1 ・このレジスタに設定した値は、プリスケーラXと RW RW プリスケーラXラッチの両方へ同時に書き込まれます。 3 1 RW 4 RW ・このレジスタを読み出した場合、プリスケーラXの 5 カウント値が読み出されます。 RW 6 RW RW

図4.35 プリスケーラXの構成

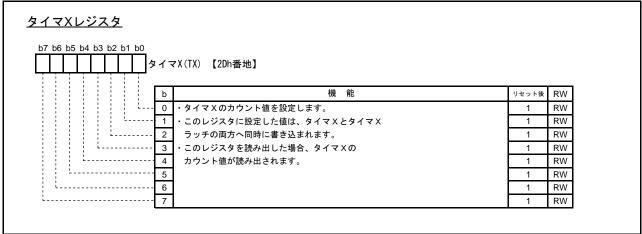

図4.36 タイマXレジスタの構成

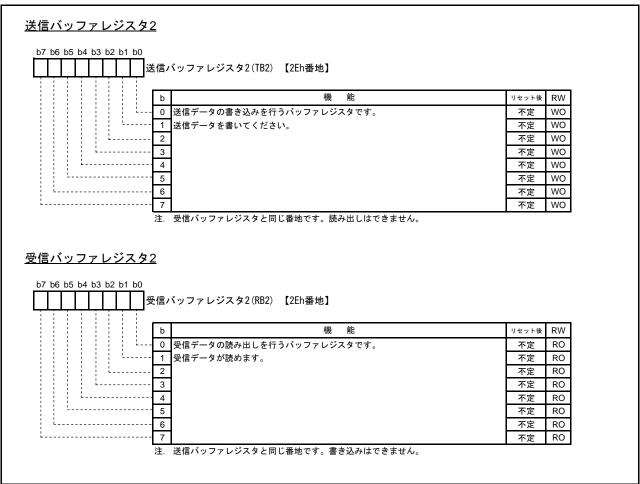

図4.37 送信バッファレジスタ2及び受信バッファレジスタ2の構成

#### <u>シリアルI/O2ステータスレジスタ</u> b7 b6 b5 b4 b3 b2 b1 b0 シリアルI/02ステータスレジスタ(SI02STS) 【2Fh番地】 ビット名 機能 リセット後 RW b 0 送信バッファエンプティ 0: バッファレジスタフル状態 RO フラグ(TBE) 1: バッファレジスタエンプティ状態 受信バッファフルフラグ 0: バッファレジスタエンプティ状態 0 RO (RBF) (注1、2) 1: バッファレジスタフル状態 2 送信シフトレジスタシフト 0: 送信シフト中 0 RO 1:送信シフト終了 終了フラグ(TSC) (注1) 0: オーバランエラーなし オーバランエラーフラグ 0 RO (OE) (注3) 1: オーバランエラー発生 パリティエラ**ー**フラグ RO 0:パリティエラーなし 0 (PE) 1: パリティエラー発生 (注3) フレーミングエラーフラグ 0: フレーミングエラーなし RΩ 0 5 (FE) 1: フレーミングエラー発生 (注3) サミングエラーフラグ 0: (OE)U(PE)U(FE) = 06 0 RO (SE) (注3) 1 : (OE)U(PE)U(FE) = 1 7 読み出し時の値は"1"。書く場合は"1"を書いてください。 RO 注1. 書く場合は"0"を書いてください。 注2. 受信バッファレジスタを読み出すと"0"にクリアされます。 注3. このレジスタへの書き込みで、このビットは"0"になります。書く場合は"0"を書いてください。

図4.38 シリアルI/O2ステータスレジスタの構成

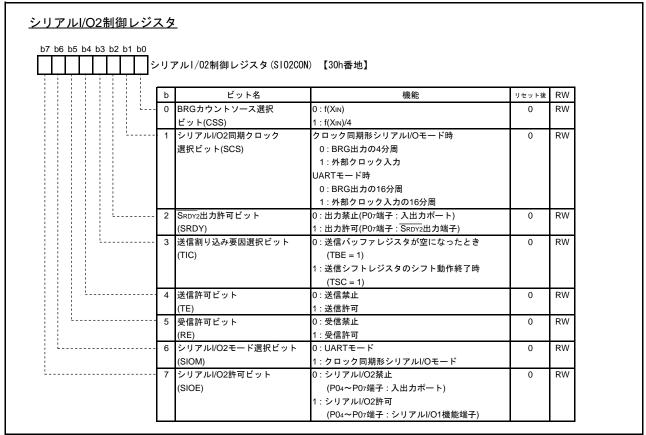

図4.39 シリアルI/O2制御レジスタの構成

#### UART2制御レジスタ b7 b6 b5 b4 b3 b2 b1 b0 1 1 1 0 UART2制御レジスタ(UART2CON) 【31h番地】 ビット名 機能 リセット後 RW 0 キャラクタ長選択ビット 0:8ビット RW (CHAS) 1:7ビット パリティ許可ビット 0:パリティ禁止 0 RW (PARE) 1:パリティ許可 2 パリティ選択ビット 0:偶数パリティ 0 RW (PARS) 1: 奇数パリティ 0:1ストップビット RW 3 ストップビット長選択ビット 0 (STPS) 1:2ストップビット 読み出し時の値は"0"。書く場合は"0"を書いてください。 0 RW このビットには"1"を書き込まないでください。 5 読み出し時の値は"1"。書く場合は"1"を書いてください。 RO 1 RO RO 1

図4.40 UART2制御レジスタの構成

図4.41 ボーレートジェネレータ2の構成

#### A/D制御レジスタ b7 b6 b5 b4 b3 b2 b1 b0 A/D制御レジスタ(ADCON) 【34h番地】 機能 ビット名 リセット後 RW アナログ入力端子選択ビット b2 b1 b0 RW 0.0.0 · ANo 0 0 1 : AN<sub>1</sub> 0 1 0 : AN<sub>2</sub> 1 0 RW 0 1 1 : AN<sub>3</sub> 1 0 0 : AN4 2 1 0 1 : AN5 0 RW 1 1 0 : AN6 1 1 1 : AN7 3 A/D変換クロック選択ビット 0: f(XIN)/2 RW (注) 1 : f(XIN) 4 A/D変換終了ビット 0:変換中 RW 1:変換終了 5 読み出し時の値は"0"。書く場合は"0"を書いてください。 0 RO 6 0 RO RO 注. A/D変換クロック=f(XIN)は、セラミック発振、オンチップオシレータ時のみ使用可能です。 RC発振時はf(XIN)/2を選択してください。

図4.42 A/D制御レジスタの構成

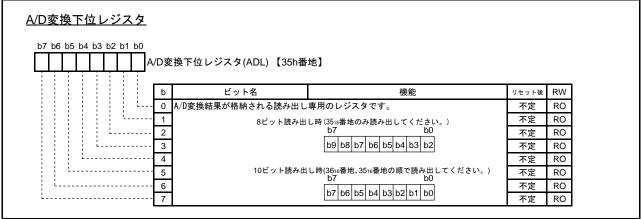

図4.43 A/D変換レジスタ下位の構成

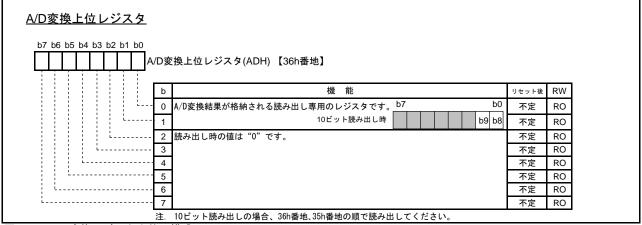

図4.44 A/D変換レジスタ上位の構成

#### <u>オンチップオシレータ分周比選択レジスタ</u> b7 b6 b5 b4 b3 b2 b1 b0 000000 オンチップオシレータ分周比選択レジスタ(RODR) 【37h番地】 機能 リセット後 RW 0 オンチップオシレータ分周比 b1 b0 RW 00: オンチップオシレータ倍速モード(Rosc/1) 選択ビット 01: オンチップオシレータ高速モード(Rosc/2) RW 10: オンチップオシレータ中速モード(Rosc/8) 11: オンチップオシレータ低速モード(Rosc/128) 2 読み出し時の値は"0"。書く場合は"0"を書いてください。 0 RO 3 0 RO 4 0 RO 5 RO 0 6 0 RO RO 0

図4.45 オンチップオシレータ分周比選択レジスタの構成

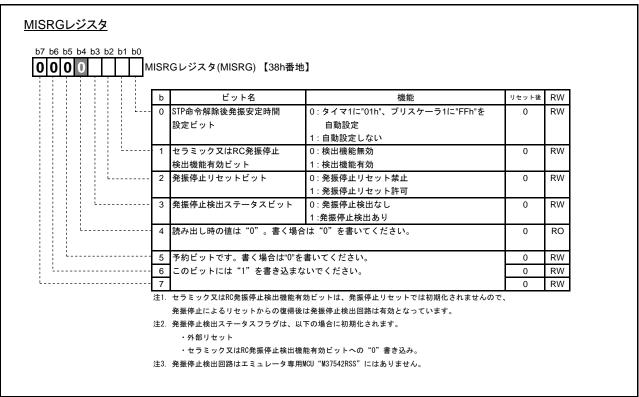

図4.46 MISRGレジスタの構成

#### ウォッチドッグタイマ制御レジスタ b7 b6 b5 b4 b3 b2 b1 b0 ウォッチドッグタイマ制御レジスタ(WDTCON) 【39h番地】 ビット名 機能 リセット後 RW 0 ウォッチドッグタイマH RO 1 (上位6ビット読み出し専用) 1 RO RO 3 RO 1 4 RO 5 1 RO 0:STP命令実行時、ストップモードへ移行 6 STP命令機能選択ビット (注1) 0 RW 1:STP命令実行時、内部リセットを発生 ウォッチドッグタイマH 0: ウォッチドッグタイマLのアンダフロー 0 RW カウントソース選択ビット(注2) 1:オンチップオシレータの16分周又はf(XIN)/16 (注3) 注1. このビットはリセット解除後1回だけ書き込みが可能です。書き込み後はロックされるため、書き換えはできません。 このビットの機能は機能設定ROMデータ2(FSROM2)のビット3でも設定できます。 その場合、このビットの値は、FSROM2のビット3と同じ値に固定され、プログラムで変更できなくなります。 また、FSROM2のビット3による設定を行うと、その設定値により、このビットのリセット後の初期値は変化します。 注2. このビットの機能はFSROM2のビット2でも設定できます。 その場合、このビットの値は、FSROM2のビット2と同じ値に固定され、プログラムで変更できなくなります。 また、FSROM2のビット2による設定を行うと、その設定値により、このビットのリセット後の初期値は変化します。 注3. クロック分周比選択ビット(CPUモードレジスタのビット7,6)で倍速モード、高速モード、中速モードを 選択している時はf(XIN)/16となります。 オンチップオシレータから供給を選択している時はオンチップオシレータの16分周となります。 注4. リセット後このレジスタへの任意の値の書き込みで、ウォッチドッグタイマはFFFFhになり、 カウントを開始します。FSROM2のビット1で、リセット後自動的にカウント開始させることができます。

図4.47 ウォッチドッグタイマ制御レジスタの構成

#### 割り込みエッジ選択レジスタ b7 b6 b5 b4 b3 b2 b1 b0 割り込みエッジ選択レジスタ(INTEDGE) 【3Ah番地】 00 ビット名 機能 リセット後 RW 0 INTo割り込みエッジ選択ビット 0:立ち下がりエッジアクティブ RW 1・立ち上がりエッジアクティブ INT1割り込みエッジ選択ビット 0: 立ち下がりエッジアクティブ RW 0 1: 立ち上がりエッジアクティブ 2 INT1入力ポート選択ビット 0 RW 1 : P33 3 読み出し時の値は "0"。書く場合は "0"を書いてください。 0 RO 4 0 RO RW 5 P00キーオンウェイクアップ 0: キーオンウェイクアップ許可 選択ビット 1: キーオンウェイクアップ禁止 0: キーオンウェイクアップ許可 6 P04キーオンウェイクアップ RW 0 選択ビット 1: キーオンウェイクアップ禁止 0: キーオンウェイクアップ許可 P06キーオンウェイクアップ n RW 選択ビット 1: キーオンウェイクアップ禁止

図4.48 割り込みエッジ選択レジスタの構成

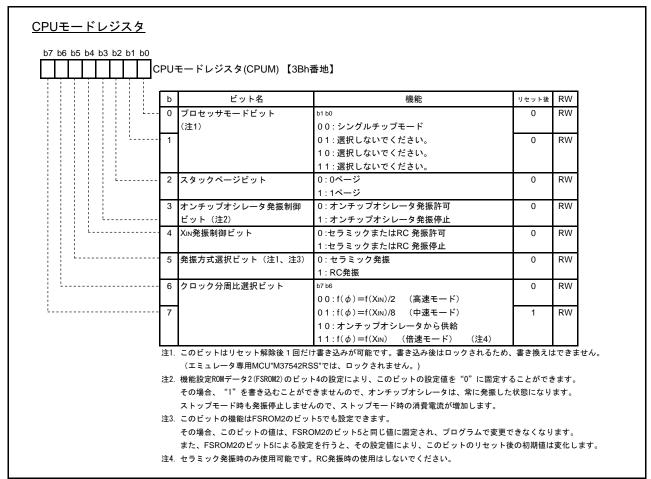

図4.49 CPUモードレジスタの構成

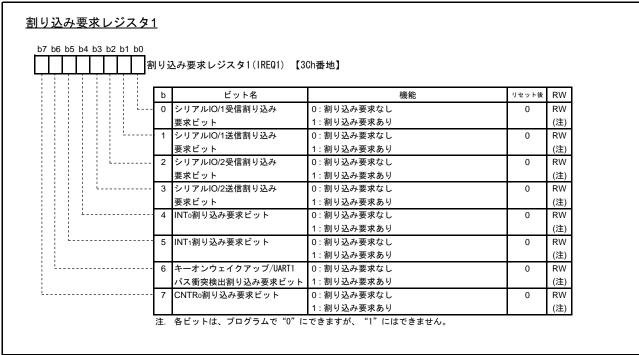

図4.50 割り込み要求レジスタ1の構成

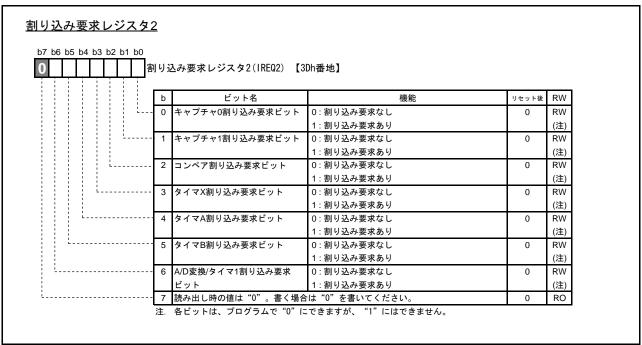

図4.51 割り込み要求レジスタ2の構成

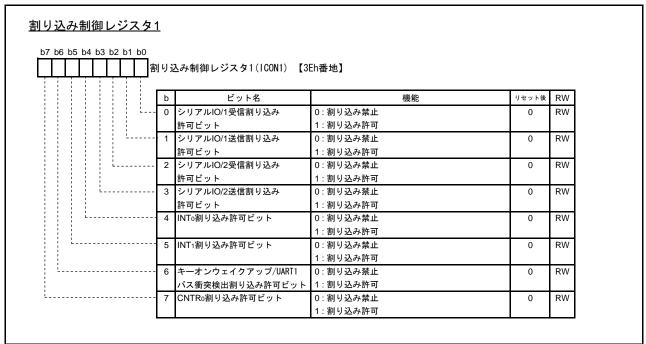

図4.52 割り込み制御レジスタ1の構成

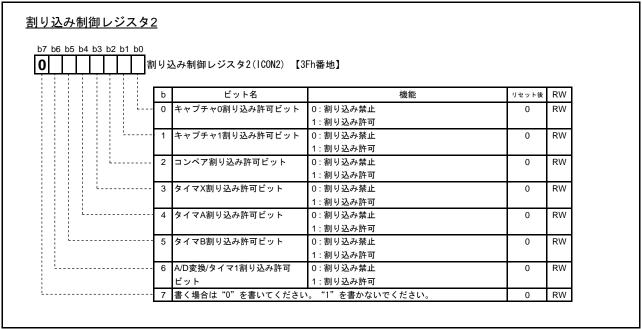

図4.53 割り込み制御レジスタ2の構成

機能設定ROMデータ0,1,2は周辺機能の設定をQzROMの書き込みデータで行うための領域で、プログラムで設定できません。この領域に設定されたデータは、マイコンのリセット解除時より有効となります。 周辺機能の使用/未使用に関わらず、システムに合わせた値を必ず設定してください。

### 機能設定ROMデータ0 b7 b6 b5 b4 b3 b2 b1 b0 100000 機能設定ROMデータO(FSROMO) 【FFD8h番地】 ビット名 機能 0 機能設定ROM無効ビット 0:機能設定ROMデータ1のビット5~ビット0設定有効 (注1) 1:機能設定ROMデータ1のビット5~ビット0設定無効 0:電圧低下検出回路無効 電圧低下検出回路有効ビット 1:電圧低下検出回路有効 "0"を設定してください。 ストップモード時の電圧低下検出 0:ストップモード時は電圧低下検出回路無効 回路有効ビット(注2) 1:ストップモード時は電圧低下検出回路有効 "0"を設定してください。 4 5 6 "1"を設定してください。 注1. このビットに"1"を設定すると、機能設定ROMデータ2のビット5~ビット0の設定値は無効になります。 これらの機能に関してはプログラムでの設定が可能となります。 (このビットは機能設定ROMデータ2のビット5~ビット0以外には影響しません。) 注2. ストップモード時に電圧低下検出回路を有効にすると、ストップモード時の消費電流が増加します。

図4.54 機能設定ROMデータ0の構成

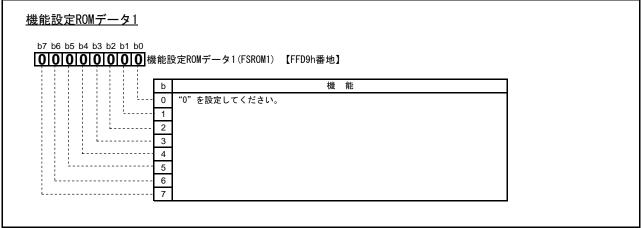

図4.55 機能設定ROMデータ1の構成

### 機能設定ROMデータ2

b7 b6 b5 b4 b3 b2 b1 b0

**00** 機能設定ROMデータ2(FSROM2) 【FFDAh番地】

|   | b | ビット名             | 機能                           |

|---|---|------------------|------------------------------|

|   | 0 | ウォッチドッグタイマソース    | 0:オンチップオシレータの16分周            |

| 1 |   | クロック選択ビット(注1)    | 1:オンチップオシレータの16分周又はf(XIN)/16 |

|   |   |                  | (注2)                         |

|   | 1 | ウォッチドッグタイマ起動選択   | 0:リセット後に自動的に起動               |

|   |   | ビット (注3)         | 1:リセット後は停止状態                 |

|   | 2 | ウォッチドッグタイマHカウント  | 0:ウォッチドッグタイマLのアンダフロー         |

|   |   | ソース選択ビット(注4)     | 1 : ウォッチドッグタイマLのカウントソース      |

|   |   |                  | (ウォッチドッグタイマソースクロック選択ビット      |

|   |   |                  | (ビット0)で選択されたクロック)            |

|   | 3 | STP命令機能選択ビット(注5) | 0:STP命令実行時、ストップモードへ移行        |

|   |   |                  | 1:STP命令実行時、内部リセット発生          |

|   | 4 | オンチップオシレータ制御ビット  | 0:オンチップオシレータ停止の禁止            |

|   |   | (注6)             | 1:オンチップオシレータ停止の許可            |

|   | 5 | 発振方式選択ビット(注7)    | 0:セラミック発振                    |

|   |   |                  | 1:RC発振                       |

|   | 6 | "0"を設定してください。    |                              |

| L | 7 |                  |                              |

- 注1. このビットは、機能設定ROM無効ビット(機能設定ROMデータ0のビット0)が "0" の時に有効になります。 機能設定ROM無効ビットが "1" (無効)の時は、ウォッチドッグタイマのソースクロックは、f(XIN)/16になります。

- 注2. クロック分周比選択ビット(CPUモードレジスタのビット7,6)で倍速モード、高速モード、中速モードを選択している時はf(XIN)/16となります。

- オンチップオシレータから供給を選択している時はオンチップオシレータの16分周となります。

- 注3. このビットは、機能設定ROM無効ビットが"0"の時に有効になります。 機能設定ROM無効ビットが"1"(無効)の時、ウォッチドッグタイマは、リセット後、停止状態です。 ウォッチドッグタイマ制御レジスタへの書き込みでカウントを開始します。

- 注4. このビットは、機能設定ROM無効ビットが"0"の時に有効になります。 機能設定ROM無効ビットが"1"(無効)の時は、ウォッチドッグタイマHのカウントソースは、ウォッチドッグ タイマ制御レジスタ(0039h番地)のビット7で決まります。

- 注5. このビットは、機能設定ROM無効ビットが"0"の時に有効になります。 機能設定ROM無効ビットが"1"(無効)の時は、STP命令の機能は、ウォッチドッグタイマ制御レジスタ (0039h番地)のビット6で決まります。

- 注6. このビットは、機能設定ROM無効ビットが"0"の時に有効になります。 このビットに"0"を設定した場合、CPUモードレジスタのビット3の値を"0"(オンチップオシレータ発振許可)に 固定し、オンチップオシレータを停止することができなくなります。ストップモード時も発振停止しませんので、 ストップモード時の消費電流が増加します。

- 機能設定ROM無効ビットが"1" (無効)の時は、オンチップオシレータの動作は、CPUモードレジスタのビット3で決まります。

- 注7. このビットは、機能設定ROM無効ビットが"0"の時に有効になります。 機能設定ROM無効ビットが"1"(無効)の時は、発振方式は、CPUモードレジスタのビット5で決まります。

図4.56 機能設定ROMデータ2の構成

# 5. 参考ドキュメント

データシート **7547**グループデータシート 最新版をルネサス テクノロジ ホームページから入手してください。

テクニカルニュース/テクニカルアップデート 最新版をルネサス テクノロジ ホームページから入手してください。

# ホームページとサポート窓口

ルネサス テクノロジ ホームページ http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/inquiry

csc@renesas.com

# 改訂記録

|      |            | 改訂内容 |      |  |

|------|------------|------|------|--|

| Rev. | 発行日        | ページ  | ポイント |  |

| 1.00 | 2007.02.20 | _    | 初版発行 |  |

### ■ 本資料ご利用に際しての留意事項

- 本資料は、お客様に用途に応じた適切な弊社製品をご購入いただくための参考資料であり、本資料中に記載の技 術情報について弊社または第三者の知的財産権その他の権利の実施、使用を許諾または保証するものではありま せん

- 不見行に記載の表面・ ス、圏、衣、フロンノム、アルコットムでの他心用凹断がなどの主での情報は不見料光行時点のものであり、弊社は本資料に記載した製品または仕様等を予告なしに変更することがあります。弊社の 半導体製品のご購入およびご使用に当たりましては、事前に弊社営業窓口で最新の情報をご確認頂きますととも に、弊社ホームページ (http://www.renesas.com) などを通じて公開される情報に常にご注意下さい。

- 本資料に記載した情報は、正確を期すため慎重に制作したものですが、万一本資料の記述の誤りに起因する損害

- 本資料に記載した情報は、正確を物すために実施した制作としてすが、カース資料の記述の戻すためにする場合がお客様に生じた場合においても、弊社はその責任を負いません。 本資料に記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を流用する場合は、流用する情報を単独で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断して下さい。弊社は、適用可否に対する責任は負いません。

- 本資料に記載された製品は、各種安全装置や運輸・交通用、医療用、燃焼制御用、航空宇宙用、原子力、海底中継用の機器・システムなど、その故障や誤動作が直接人命を脅かしあるいは人体に危害を及ぼすおそれのあるような機器・システムや特に高度な品質・信頼性が要求される機器・システムでの使用を意図して設計、製造されたものではありません(弊社が自動車用と指定する製品を自動車に使用する場合を除きます)。これらの用途に 利用されることをご検討の際には、必ず事前に弊社営業窓口へご照会下さい。なお、上記用途に使用されたことにより発生した損害等について弊社はその責任を負いかねますのでご了承願います。

- 第7項にかかわらず、本資料に記載された製品は、下記の用途には使用しないで下さい。これらの用途に使用されたことにより発生した損害等につきましては、弊社は一切の責任を負いません。

- 1) 生命維持装置。

- 2) 人体に埋め込み使用するもの。

- 3)治療行為(患部切り出し、薬剤投与等)を行なうもの。 4)その他、直接人命に影響を与えるもの。

- 本資料に記載された製品のご使用につき、特に最大定格、動作電源電圧範囲、放熱特性、実装条件およびその他 諸条件につきましては、弊社保証範囲内でご使用ください。弊社保証値を越えて製品をご使用された場合の故障 および事故につきましては、弊社はその責任を負いません。

- 10. 弊社は製品の品質及および信頼性の向上に努めておりますが、特に半導体製品はある確率で故障が発生したり、 使用条件によっては誤動作したりする場合があります。弊社製品の故障または誤動作が生じた場合も人身事故、 火災事故、社会的損害などを生じさせないよう、お客様の責任において冗長設計、延焼対策設計、誤動作防止設計などの安全設計(含むハードウエアおよびソフトウエア)およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特にマイコンソフトウエアは、単独での検証は困難なため、お客様が製造さ

- ている山利米証とお願いいたします。行にマイコンファインエアは、単独での検証は凶難なため、お各様が衰退された最終の機器・システムとしての安全検証をお願い致します。

11. 本資料に記載の製品は、これを搭載した製品から剥がれた場合、幼児が口に入れて誤飲する等の事故の危険性があります。お客様の製品への実装後に容易に本製品が剥がれることがなきよう、お客様の責任において十分な安全設計をお願いします。お客様の製品から剥がれた場合の事故につきましては、弊社はその責任を負いません。

12. 本資料の全部または一部を弊社の文書による事前の承諾なしに転載または複製することを固くお断り致します。

13. 本資料に関する詳細についてのお問い合わせ、その他お気付きの点等がございましたら弊社営業窓口までご照会

- 下さい。

© 2007. Renesas Technology Corp., All rights reserved.