# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010 年 4 月 1 日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

# ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# 3850グループ(A仕様)

周辺機能の応用

# 1. はじめに

この資料は3850グループ(A仕様)の周辺機能の設定方法例を説明し、応用例を掲載しています。

この資料で説明する応用例は次のマイコンに適用されます。

・マイコン: 3850グループ(A仕様)

# 2. 応用

- 2.1 入出力ポート

- 2.2 割り込み

- 2.3 タイマ

- 2.4 シリアルI/O

- 2.5 PWM

- 2.6 A-D变换器

- 2.7 ウオッチドッグタイマ

- 2.8 リセット

- 2.9 クロック発生回路

- 2.10 スタンバイ機能

- 2.11 フラッシュメモリモード

# 2.1 入出力ポート

本節では入出力ポートに関するレジスタの設定方法、注意事項などを説明します。

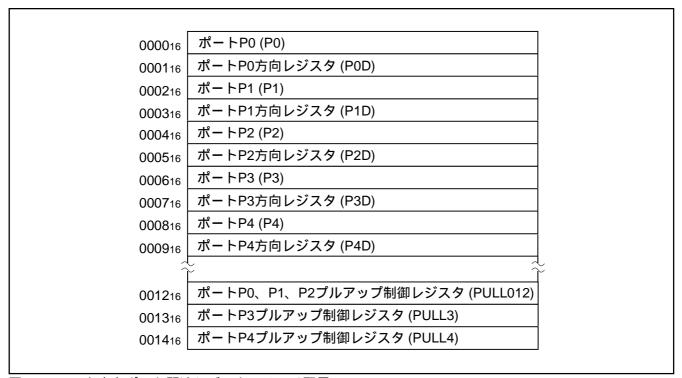

#### 2.1.1 メモリ配置図

図2.1.1 入出力ポート関連レジスタのメモリ配置

## 2.1.2 関連レジスタ

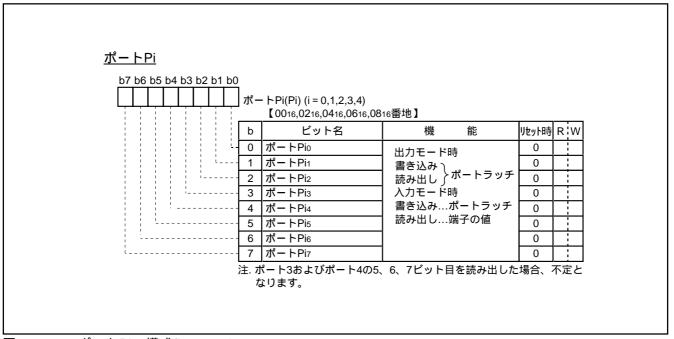

図2.1.2 ポートPiの構成(i = 0~4)

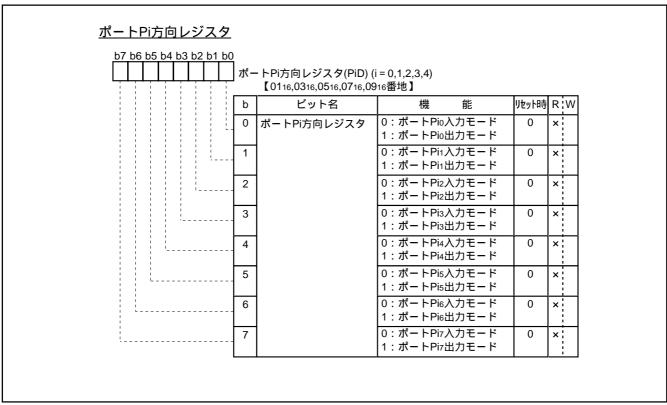

図2.1.3 ポートPi方向レジスタの構成(i = 0~4)

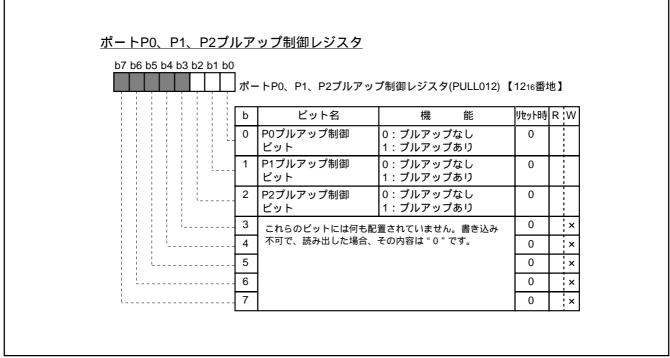

図2.1.4 ポートP0、P1、P2プルアップ制御レジスタの構成

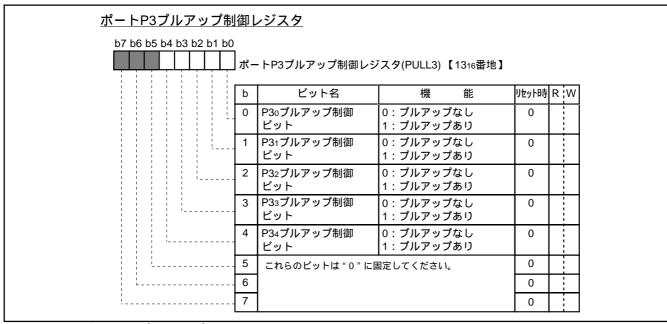

図2.1.5 ポートP3プルアップ制御レジスタの構成

図2.1.6 ポートP4プルアップ制御レジスタの構成

#### 2.1.3 未使用端子の処理

表2.1.1 未使用端子の処理

| 端子/ポート名        | 処理方法                                        |

|----------------|---------------------------------------------|

| P0、P1、P2、P3、P4 | ・入力モードに設定し、各端子ごとに1 k ~10 k の抵抗を介してVcc又はVssに |

|                | 接続。内蔵プルアップ抵抗が選択可能なポートでは内蔵プルアップ抵抗を使用可        |

|                | 能。                                          |

|                | ・出力モードに設定し、" L "又は" H "出力状態で開放              |

| VREF端子         | Vss( GND )に接続                               |

| AVss端子         | Vss( GND )に接続                               |

| XouT端子         | 開放(外部クロック使用時のみ)                             |

## 2.1.4 入出力ポートに関する注意事項

#### (1) スタンバイ状態での使用

スタンバイ状態\*1で使用する場合は、入出力ポートの入力レベルを不定の状態にしないでください。 特にNチャネルオープンドレインの入出力ポートでは注意が必要です。また、Nチャネルオープン ドレインの入出力ポートでは、出力に設定している場合でも、同様の注意が必要です。

この場合、抵抗を介してポートをプルアップ( Vccに接続 )又はプルダウン( Vssに接続 )してください。

抵抗値を決定する際は、以下の2点に留意してください。

- ・外付け回路

- ・通常動作時の出力レベルの変動

#### 理由

方向レジスタで入力ポートに設定している場合はトランジスタがOFF状態になるため、ポートはハイインピーダンス状態になります。このとき、入力レベルを不定の状態にすると、マイコン内部の入力バッファに入力される電位が不安定となるため、電源電流が流れることがあります。

また、Nチャネルオープンドレインの入出力ポートではポートラッチの内容が"1"の場合、方向レジスタで出力ポートに設定していても、入力ポートと同様の現象がおこります。

\*1スタンバイ状態:STP命令実行によるストップモード WIT命令実行によるウエイトモード

(2) ビット処理命令による出力データの書き替え

入出力ポートのポートラッチをビット処理命令\*を用いて書き替える場合、指定していないビットの 値が変化することがあります。

#### 理由

ビット処理命令はリード・モディファイ・ライト形式の命令で、バイト単位で読み出し及び書き 込みを行います。したがって入出力ポートのポートラッチの、あるビットに対してこの命令を実行 した場合、そのポートラッチの全ビットに対して以下の処理が行われます。

・入力に設定されているビット:

端子の値がCPUに読み込まれ、ビット処理後、このビットに書き込まれる。

- ・出力に設定されているビット:

- ポートラッチのビットの値がCPUに読み込まれ、ビット処理後、このビットに書き込まれる。 ただし、以下の点に注意してください。

- ・出力に設定されているポートを入力ポートに変更しても、ポートラッチには出力データが保持 される構成になっています。

- ・入力に設定されているポートラッチのビットについては、ビット処理命令で指定していない場合にも、端子とポートラッチの内容が異なる場合、ビットの値が変化します。

\*ビット処理命令:SEB命令、CLB命令

#### 2.1.5 未使用端子の処理に関する注意事項

#### (1) 未使用端子の適切な処理

#### 入出力ポート

入力モードに設定し、1~10k の抵抗を介してVcc又はVssに接続してください。内蔵プルアップ抵抗が選択可能なポートでは内蔵プルアップ抵抗を使用することもできます。出力モードに設定する場合は、"L"又は"H"出力状態で開放してください。

- ・出力モードに設定して開放する場合、リセット後プログラムによってポートを出力モードに 切り替えるまでは、初期状態の入力モードのままです。そのため端子の電圧レベルが不定とな り、ポートが入力モードになっている間、電源電流が増加する場合があります。システムへの 影響については、ユーザサイドで十分なシステム評価を行ってください。

- ・ノイズやノイズによって引き起こされる暴走などにより方向レジスタが変化する場合を考慮し、定期的に方向レジスタをプログラムで再設定することによって更にプログラムの信頼度が 高まります。

# A-D変換器を使用しない場合のA-D変換用電源端子AVss

A-D変換器を使用しない場合、A-D変換用電源端子AVssは以下のように処理してください。

・AVss: Vssに接続

#### (2) 処理上の留意事項

入力ポート及び入出力ポート

入力モードで開放しないでください。

#### 理由:

- ・初段回路によっては電源電流が増加する場合があります。

- ・上記適切な処理(1)の に比べ、ノイズの影響を受け易くなります。

## 入出力ポート

入力モードに設定した場合、Vcc又はVssに直結しないでください。

#### 理由

暴走、ノイズなどによって、方向レジスタが出力モードに変化した場合、短絡する可能性があります。

#### 入出力ポート

入力モードに設定した場合、複数ポートをまとめて抵抗を介し、Vcc又はVssに接続しないでください。

#### 理由:

暴走、ノイズなどによって、方向レジスタが出力モードに変化した場合、ポート間で短絡する可能性があります。

・未使用端子処理はマイコンの端子からできるだけ 短い配線(20mm以内)で処理してください。

# 2.2 割り込み

本節では割り込みに関するレジスタの設定方法、注意事項などを説明します。

# 2.2.1 メモリ配置図

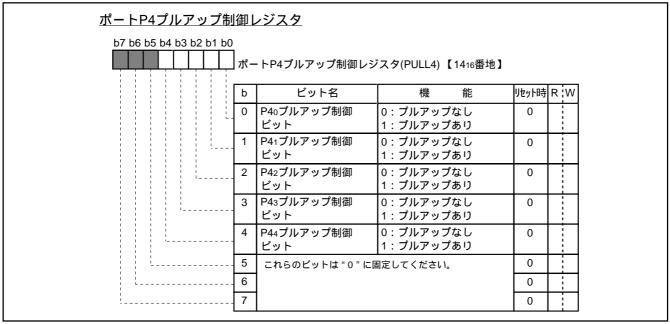

図2.2.1 割り込み関連レジスタのメモリ配置

#### 2.2.2 関連レジスタ

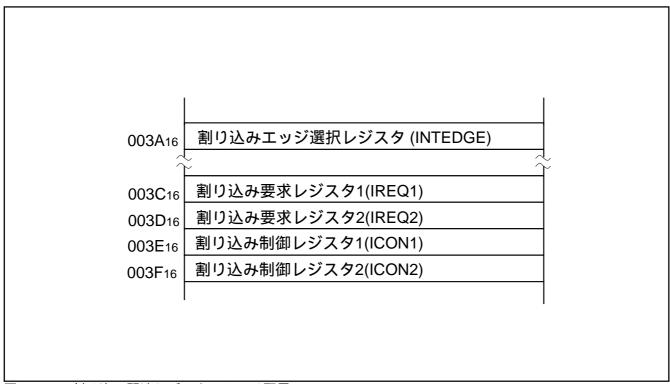

図2.2.2 割り込みエッジ選択レジスタの構成

#### 割り込み要求レジスタ1 b7 b6 b5 b4 b3 b2 b1 b0 割り込み要求レジスタ1(IREQ1) 【3C16番地】 ルット時 R ¦W ビット名 能 0 INTo割り込み要求 0:割り込み要求なし 0 \* ビット 1:割り込み要求あり ١\* 書き込む際は"0"を書き込んでください。 0 INT1割り込み要求 0:割り込み要求なし ビット 1:割り込み要求あり INT2割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり : \* INT3/シリアルI/O2割り 0:割り込み要求なし 0 込み要求ビット 1:割り込み要求あり 書き込む際は"0"を書き込んでください。 0 0:割り込み要求なし 0 タイマX割り込み要求 ビット 1:割り込み要求あり タイマY割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり \*ソフトウエアによって"0"にできますが、"1"にはできません。

図2.2.3 割り込み要求レジスタ1の構成

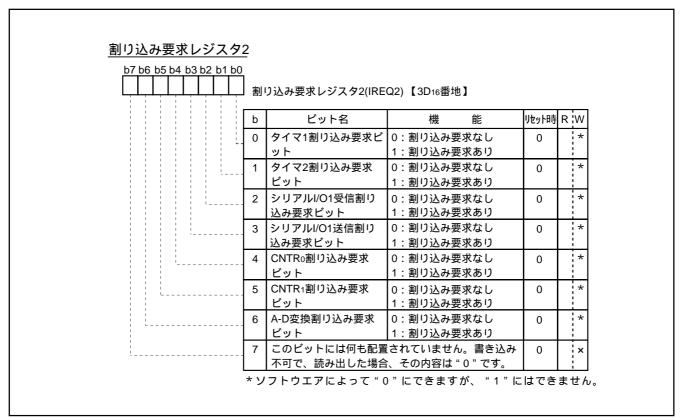

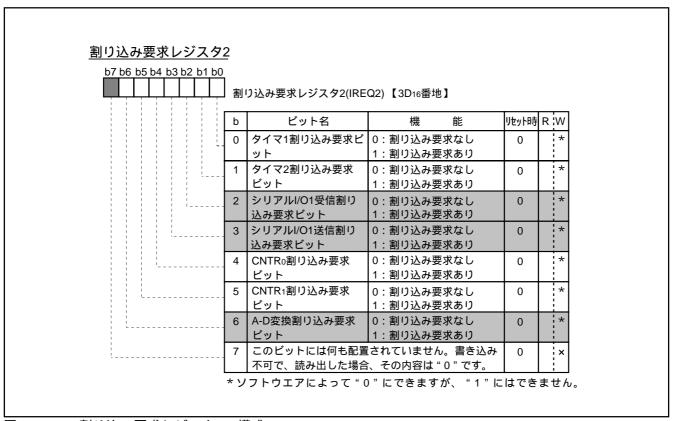

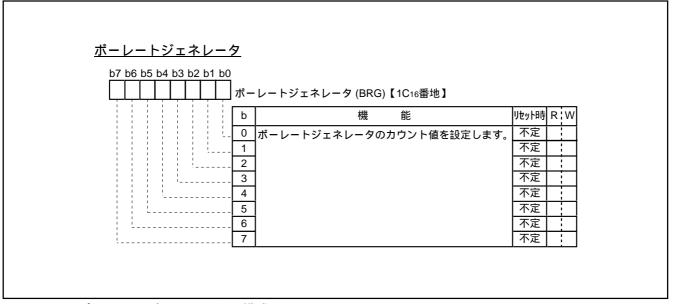

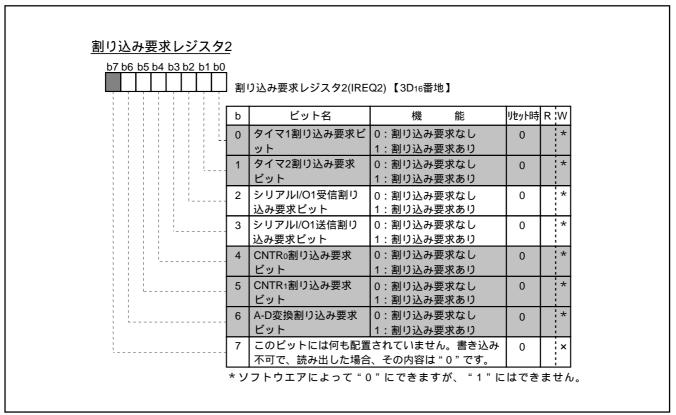

図2.2.4 割り込み要求レジスタ2の構成

RJJ05B0876-0100/Rev1.00 2005.11 Page 9 of 116

#### 割り込み制御レジスタ1 b7 b6 b5 b4 b3 b2 b1 b0 0 0 割り込み制御レジスタ1(ICON1) 【3E16番地】 ビット名 リセット時 R IW h INTo割り込み許可 0:割り込み禁止 0 ビット 1:割り込み許可 このビットは"0"に固定してください。 0 INT1割り込み許可ビッ 0:割り込み禁止 0 1:割り込み許可 INT2割り込み許可ビ 0:割り込み禁止 0 1:割り込み許可 ット INT3/シリアルI/O2割 0:割り込み禁止 0 り込み許可ビット 1:割り込み許可 このビットは"0"に固定してください。 0 0:割り込み禁止 6 n タイマX割り込み許可 ビット 1:割り込み許可 タイマY割り込み許可 0:割り込み禁止 0 ビット 1:割り込み許可

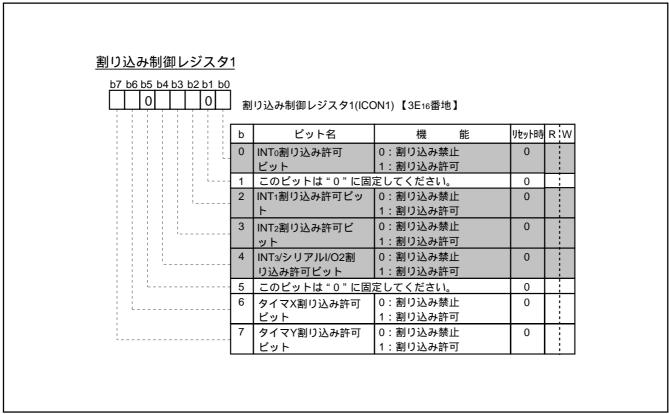

図2.2.5 割り込み制御レジスタ1の構成

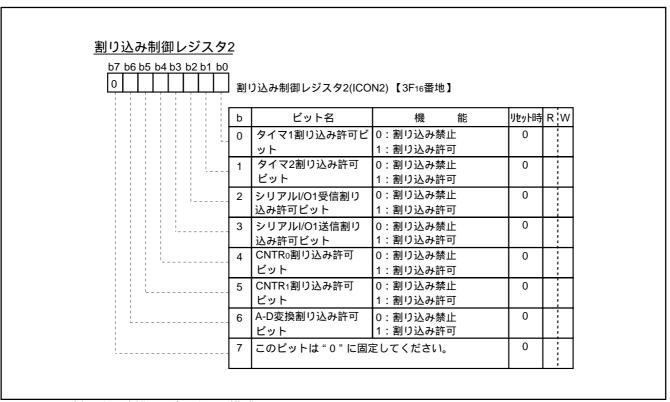

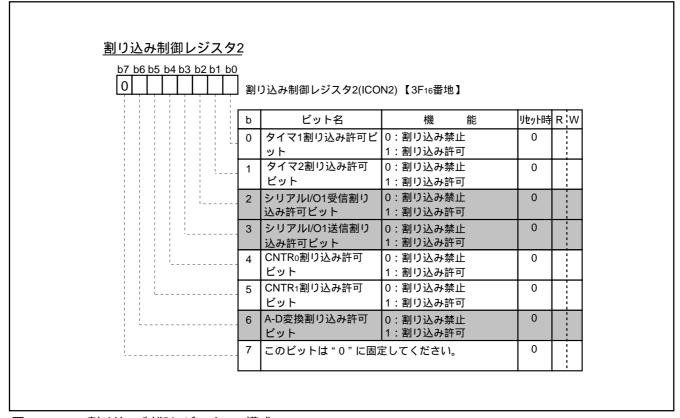

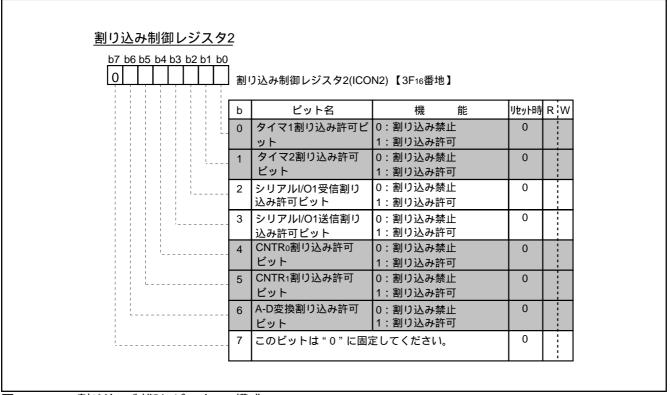

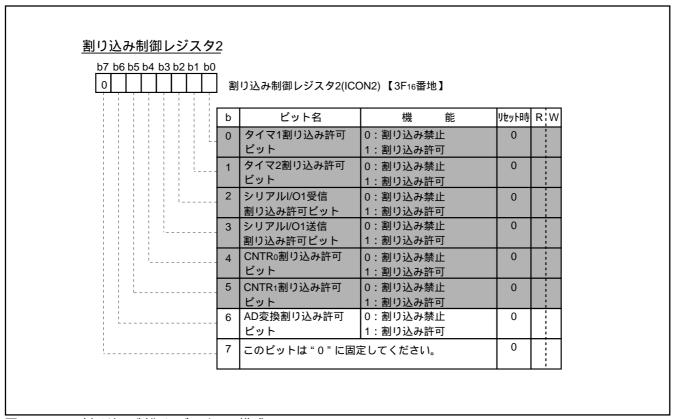

図2.2.6 割り込み制御レジスタ2の構成

#### 2.2.3 割り込み要因

3850グループでは、15要因で割り込みをかけることができます。固定優先度方式のベクトル割り込みですので、同一サンプリング時に2つ以上の割り込み要求がある場合は、優先順位の高い割り込みから受け付けます。この優先順位は、ハードウエアで決められていますが、割り込み許可ビット、割り込み禁止フラグを用いることによって、多様な優先処理をソフトウエアで行うことが可能です。割り込み要因とベクトル番地(注1)、割り込み優先順位は表2.2.1を参照してください。

表2.2.1 割り込みベクトル番地と優先順位

| 割けたれて、亜田          | 優先 | ベクトル番地(注1) |                    |                                                   | /# ±z                                                      |  |

|-------------------|----|------------|--------------------|---------------------------------------------------|------------------------------------------------------------|--|

| 割り込み要因            | 順位 | 上位         | 下位                 | 割り込み要求発生条件                                        | 備考                                                         |  |

| リセット(注2)          | 1  | FFFD16     | FFFC16             | リセット時                                             | ノンマスカブル                                                    |  |

| INTo              | 2  | FFFB16     | FFFA <sub>16</sub> | INTo入力の立ち上がり又は<br>立ち下がりエッジ検出時                     | 外部割り込み<br>(極性プログラマブル)                                      |  |

| 予約                | 3  | FFF916     | FFF816             | 予約                                                |                                                            |  |

| INT1              | 4  | FFF716     | FFF616             | INT1入力の立ち上がり又は<br>立ち下がりエッジ検出時                     | 外部割り込み<br>(極性プログラマブル)                                      |  |

| INT2              | 5  | FFF516     | FFF416             | INT2入力の立ち上がり又は<br>立ち下がりエッジ検出時                     | 外部割り込み<br>(極性プログラマブル)                                      |  |

| INT3<br>シリアJИ/O2  | 6  | FFF316     | FFF216             | INT3入力の立ち上がり又は立ち下がり<br>エッジ検出時<br>シリアルI/O2送受信完了時   | 外部割り込み<br>(極性プログラマブル)<br>シリアルI/O2/INT3割り込み<br>要因ビットにより切り替え |  |

| 予約                | 7  | FFF116     | FFF016             | 予約                                                |                                                            |  |

| タイマX              | 8  | FFEF16     | FFEE16             | タイマXアンダフロー時                                       |                                                            |  |

| タイマY              | 9  | FFED16     | FFEC16             | タイマYアンダフロー時                                       |                                                            |  |

| タイマ 1             | 10 | FFEB16     | FFEA <sub>16</sub> | タイマ 1 アンダフロー時                                     | STP解除タイマアンダフロー                                             |  |

| タイマ 2             | 11 | FFE916     | FFE816             | タイマ 2 アンダフロー時                                     |                                                            |  |

| シリアルI/O1受信        | 12 | FFE716     | FFE616             | シリアルI/O1データ受信完了時                                  | シリアル/O1選択時のみ有効                                             |  |

| シリアルI/O1送信        | 13 | FFE516     | FFE416             | シリアルI/O1送信シフト終了時<br>又は送信バッファ空き時                   | シリアルI/O1選択時のみ有効                                            |  |

| CNTR <sub>0</sub> | 14 | FFE316     | FFE216             | CNTRo入力の立ち上がり又は<br>立ち下がりエッジ検出時                    | 外部割り込み<br>(極性プログラマブル)                                      |  |

| CNTR1             | 15 | FFE116     | FFE016             | CNTR1入力の立ち上がり又は 外部割り込み<br>立ち下がりエッジ検出時 (極性プログラマブル) |                                                            |  |

| A-D変換             | 16 | FFDF16     | FFDE16             | A-D变換終了時                                          |                                                            |  |

| BRK命令             | 17 | FFDD16     | FFDC16             | BRK命令実行時                                          | ノンマスカブルソフトウエア割り込み                                          |  |

注1.ベクトル番地とは、割り込み飛び先番地の格納番地を示します。

<sup>2.</sup> リセットは最上位の優先順位を持つ割り込みとして処理されます。

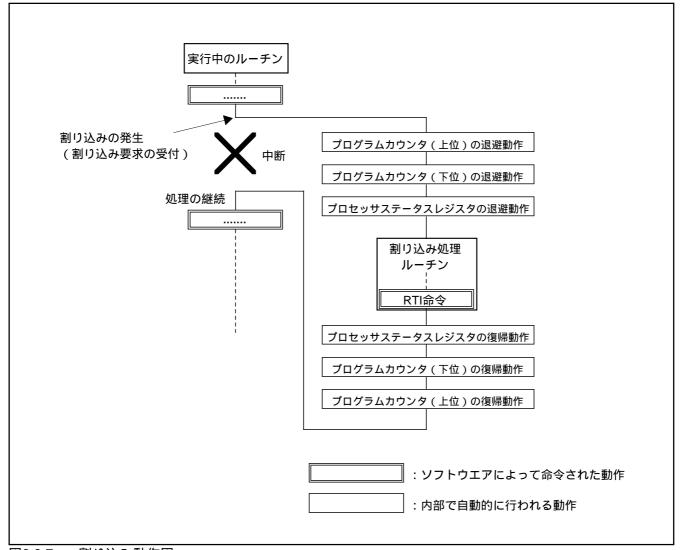

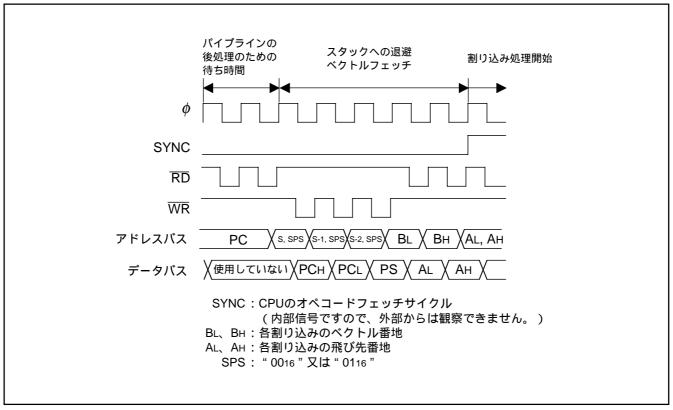

### 2.2.4 割り込み動作

割り込み要求が受け付けられると、次に示すレジスタの割り込み要求受付直前の状態が① ② ③と順次、自動的にスタック領域に退避されます。

- ①プログラムカウンタ上位(PCH)

- ②プログラムカウンタ下位(PCL)

- ③プロセッサステータスレジスタ(PS)

上記のレジスタが退避された後、受け付けられた割り込みの飛び先番地へ分岐します。割り込み処理ルーチンの最後でRTI命令を実行すると、スタック領域に退避されていた上記レジスタの内容が③ ② ① と順次それぞれのレジスタに復帰し、割り込み要求受付前の処理が継続されます。

図2.2.7に割り込み動作図を示します。

図2.2.7 割り込み動作図

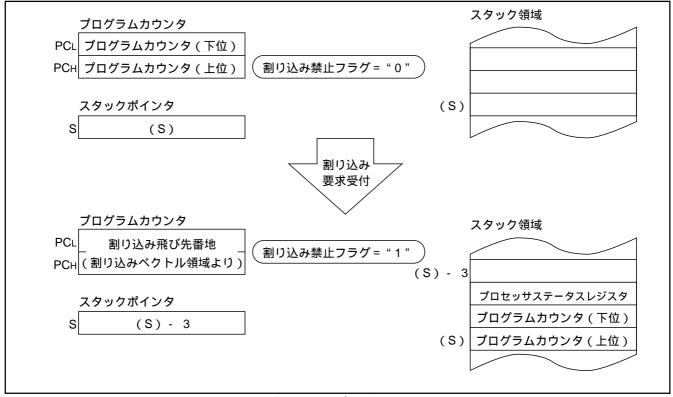

#### (1) 割り込み要求受付時の処理

割り込み要求を受け付けると以下の動作が自動的に行われます。

- ①現在実行中の処理が中断されます。

- ②プログラムカウンタ、及びプロセッサステータスレジスタの内容がスタック領域へ退避されます。 図2.2.8に割り込み要求受付時のスタックポインタとプログラムカウンタの変化を示します。

- ③退避と同時に、割り込みベクトル領域に格納されている、発生した割り込みの飛び先番地(割り込み処理ルーチンの先頭番地)がプログラムカウンタに設定され、割り込み処理ルーチンが実行されます。

- ④割り込み処理ルーチンに入ると、対応する割り込み要求ビットが自動的に"0"になります。また、割り込み禁止フラグが"1"になり、多重割り込みが禁止されます。

したがって、割り込み処理ルーチンを実行するためには、飛び先番地を各割り込みに対応したベクトル領域内に設定しておく必要があります。

図2.2.8 割り込み要求受付時のスタックポインタとプログラムカウンタの変化

#### (2) 割り込み要求受付後のタイミング

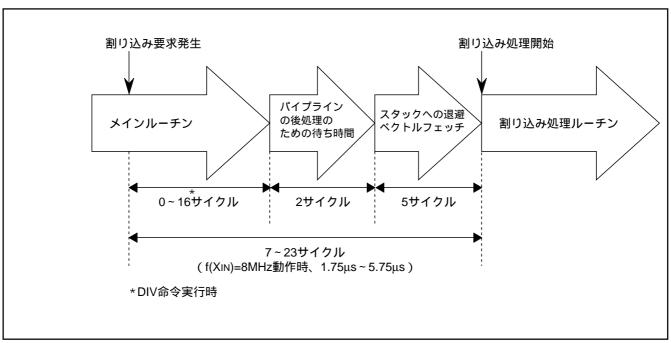

割り込み処理ルーチンは、現在実行中の命令終了後のマシンサイクルから始まります。図2.2.9に割り込み処理ルーチンを実行するまでの時間、図2.2.10に割り込み要求受付後のタイミングを示します。

図2.2.9 割り込み処理ルーチンを実行するまでの時間

図2.2.10 割り込み要求受付後のタイミング

RJJ05B0876-0100/Rev1.00 2005.11 Page 14 of 116

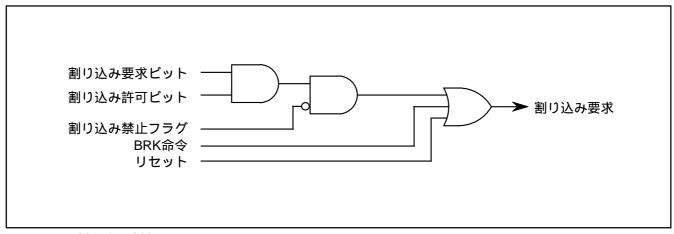

### 2.2.5 割り込み制御

BRK命令を除く割り込みは、割り込み要求ビット、割り込み許可ビット、及び割り込み禁止フラグによって割り込み要求の受付を制御できます。この節ではBRK命令を除く割り込みの制御について説明します。図2.2.11に割り込み制御図を示します。

図2.2.11 割り込み制御図

割り込み要求ビット、割り込み許可ビット、及び割り込み禁止フラグは独立して機能し、お互いに影響を与えることはありません。割り込み要求は以下の条件をすべて満たされると受け付けられます。

- ●割り込み要求ビット・・・・・"1"

- ●割り込み許可ビット・・・・・・ 1 "

- ●割り込み禁止フラグ・・・・・"0"

割り込みの優先順位は、ハードウエアで決められていますが、上記のビット及びフラグを用いることによって、多様な優先処理をソフトウエアで行うことができます。表2.2.2に各割り込み要因に対する割り込み制御ビット一覧を示します。

## (1) 割り込み要求ビット

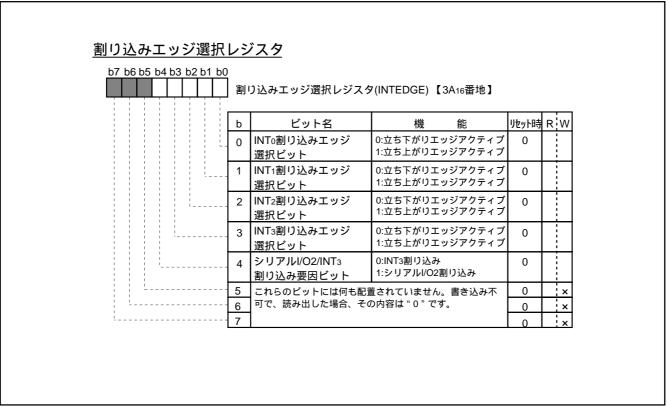

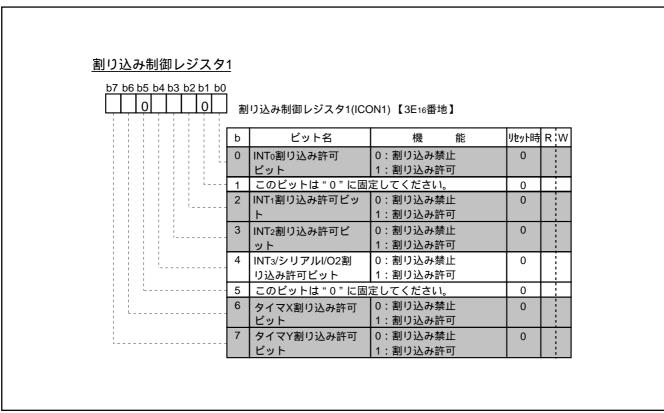

割り込み要求ビットは、割り込み要求レジスタ1(3C16番地)、割り込み要求レジスタ2(3D16番地) に割り当てられています。

割り込み要求が発生すると、対応する割り込み要求ビットが"1"になります。"1"にセットされた割り込み要求ビットは、割り込み要求が受け付けられるまで"1"の状態で保持されます。割り込み要求が受け付けられると、自動的に"0"になります。

割り込み要求ビットは、ソフトウエアで' 0 'にできますが、ソフトウエアで' 1 'にすることはできません。

#### (2) 割り込み許可ビット

割り込み許可ビットは、割り込み制御レジスタ1(3E16番地)及び割り込み制御レジスタ2(3F16番地) に割り当てられています。

割り込み許可ビットは、対応する割り込み要求の受付を制御するビットです。

このビットが 0 'のとき、対応する割り込み要求が禁止されます。このビットが 0 'の状態で割り込み要求が発生すると、対応する割り込み要求ビットが 1 "になるだけで、その割り込み要求は受け付けられません。この場合、ソフトウエアで割り込み要求ビットを 0 "にするまで、割り込み要求ビットは 1 "のままです。

このビットが 1 "のとき、対応する割り込み要求が許可されます。このビットが 1 "の状態で割り込み要求が発生すると、その割り込み要求が受け付けられます(割り込み禁止フラグ = "0"の場合)。 割り込み許可ビットはソフトウエアで 0"、又は 1"にすることができます。

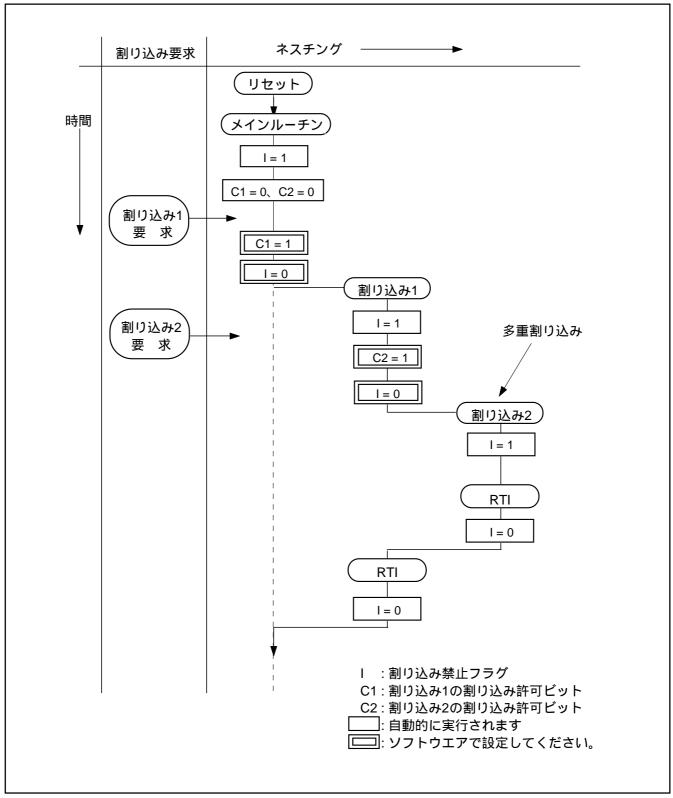

#### (3) 割り込み禁止フラグ

割り込み禁止フラグは、プロセッサステータスレジスタのb2に割り当てられています。割り込み禁止フラグは、BRK命令を除く割り込み要求の受付を制御するフラグです。

このフラグが 1 "のとき、割り込み要求の受付が禁止されます。" 0 "のとき、割り込み要求の受付が 許可されます。" 1 "にする命令はSEI命令、" 0 "にする命令はCLI命令です。

割り込み処理ルーチンへの分岐時、このフラグは自動的に"1"になり、多重割り込みを禁止します。 多重割り込みを使用する場合は、割り込み処理ルーチン内でCLI命令を用いて、このフラグを"0"にしてください。図2.2.12に多重割り込みの例を示します。

表2.2.2 各割り込み要因に対する割り込み制御ビット一覧

| 割り込み要因            | 割り込み詞              | 午可ビット | 割り込み要求ビット          |     |

|-------------------|--------------------|-------|--------------------|-----|

| 別り匹の安囚            | 番地                 | ビット   | 番地                 | ビット |

| INT <sub>0</sub>  | 003E <sub>16</sub> | b0    | 003C <sub>16</sub> | b0  |

| INT <sub>1</sub>  | 003E <sub>16</sub> | b2    | 003C <sub>16</sub> | b2  |

| INT <sub>2</sub>  | 003E <sub>16</sub> | b3    | 003C <sub>16</sub> | b3  |

| INT3/シリアルI/O2     | 003E <sub>16</sub> | b4    | 003C <sub>16</sub> | b4  |

| タイマX              | 003E <sub>16</sub> | b6    | 003C <sub>16</sub> | b6  |

| タイマY              | 003E <sub>16</sub> | b7    | 003C <sub>16</sub> | b7  |

| タイマ1              | 003F <sub>16</sub> | b0    | 003D <sub>16</sub> | b0  |

| タイマ2              | 003F <sub>16</sub> | b1    | 003D <sub>16</sub> | b1  |

| シリアルI/O1受信        | 003F <sub>16</sub> | b2    | 003D <sub>16</sub> | b2  |

| シリアルI/O1送信        | 003F <sub>16</sub> | b3    | 003D <sub>16</sub> | b3  |

| CNTR <sub>0</sub> | 003F <sub>16</sub> | b4    | 003D <sub>16</sub> | b4  |

| CNTR <sub>1</sub> | 003F <sub>16</sub> | b5    | 003D <sub>16</sub> | b5  |

| AD変換              | 003F <sub>16</sub> | b6    | 003D <sub>16</sub> | b6  |

図2.2.12 多重割り込みの例

# 2.2.6 INT割り込み

INT割り込みは、各INT端子(INTo~INT3)のレベル変化を検出して、割り込み要求が発生します。

## (1) 有効エッジの選択

INTo~INT3は有効エッジとして、立ち下がりエッジ、又は立ち上がりエッジのどちらを検出するかを、割り込みエッジ選択レジスタによってそれぞれ選択できます。"0"にすると対応する端子の立ち下がりエッジ、"1"にすると対応する端子の立ち上がりエッジが検出されます。

#### (2) INT3割り込み要因の選択

シリアルI/O2/INT3割り込み要因を使用する場合、シリアルI/O2/INT3割り込み要因ビット(  $3A_16$ 番地のビット4 )で、どちらの割り込み要因を使用するかを選択してください ( INT3を使用する場合は" 0 "に設定)。

# 2.2.7 割り込みに関する注意事項

#### (1) 関連レジスタの設定変更

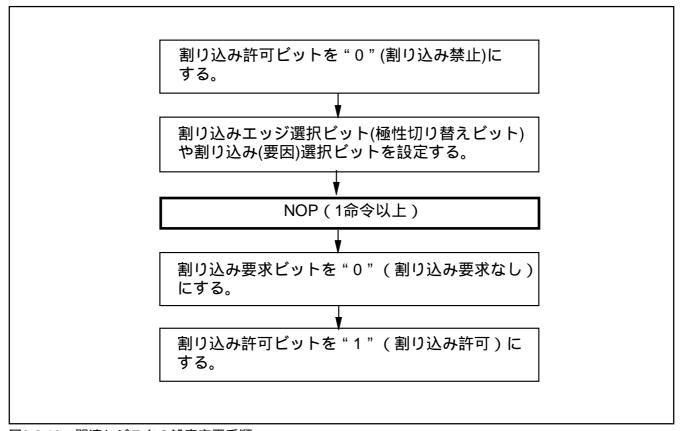

割り込みエッジ選択レジスタ(3A16番地)及びタイマXYモードレジスタ(2316番地)の設定を変更する場合、これらの設定に同期した割り込み発生が不要なら、以下の手順で設定してください。

図2.2.13 関連レジスタの設定変更手順

#### 理由

次の場合、割り込み要求ビットが "1"になる場合があります。

- ・外部割り込みのアクティブエッジを設定する際 対象レジスタ:割り込みエッジ選択レジスタ(3A16番地) タイマXYモードレジスタ(2316番地)

- ・同一割り込みベクトルに複数の割り込み要因が割り当てられたベクトルの割り込み要因を切り 替える際

対象レジスタ:割り込みエッジ選択レジスタ(3A16番地)

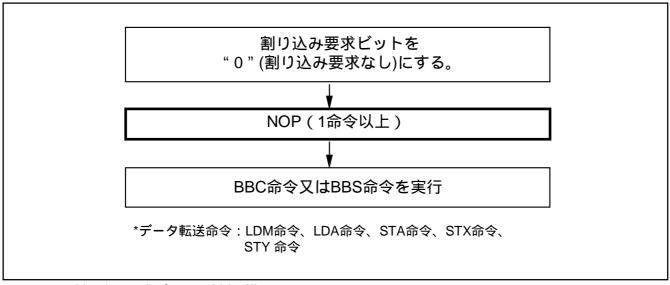

#### (2) 割り込み要求ビットの判定

データ転送命令を使用して割り込み要求レジスタの割り込み要求ビットを"0"にした直後、BBC命令又はBBS命令をこの割り込み要求ビットに対して実行する場合は、BBC命令又はBBS命令を実行する前に、1命令実行してください。

図2.2.14 割り込み要求ビットの判定手順

#### 理由

割り込み要求レジスタの割り込み要求ビットを"0"にした直後にBBC命令又はBBS命令を実行すると、"0"になる前の割り込み要求ビットの値を判定します。

# 2.3 タイマ

本節ではタイマに関するレジスタの設定方法、注意事項などを説明します。

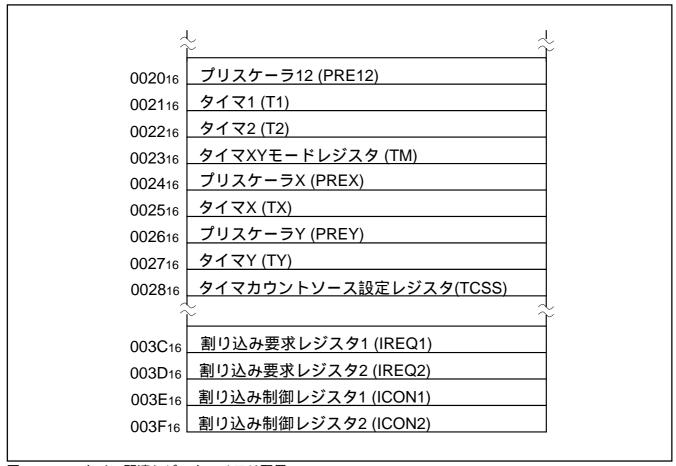

#### 2.3.1 メモリ配置図

図2.3.1 タイマ関連レジスタのメモリ配置

#### 2.3.2 関連レジスタ

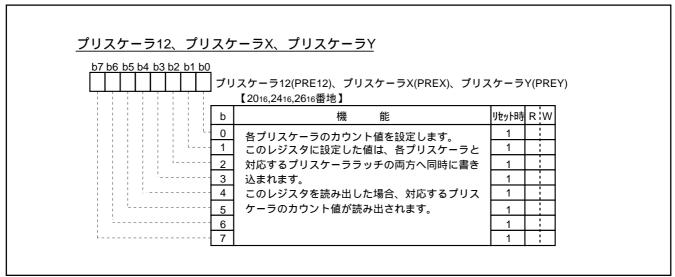

図2.3.2 プリスケーラ12、プリスケーラX、プリスケーラYの構成

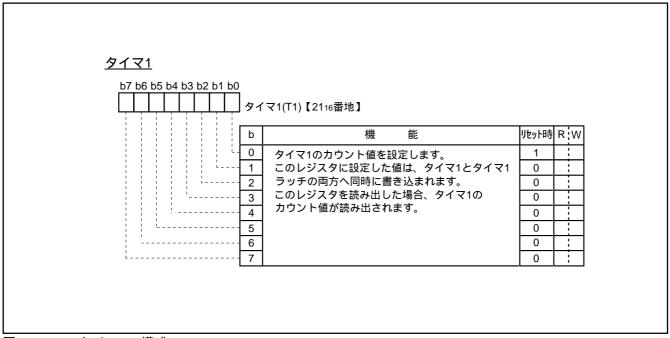

図2.3.3 タイマ1の構成

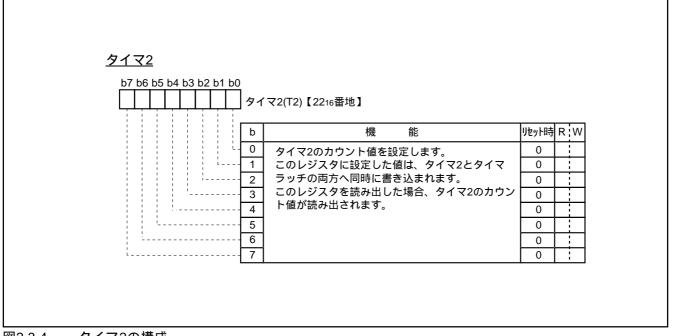

図2.3.4 タイマ2の構成

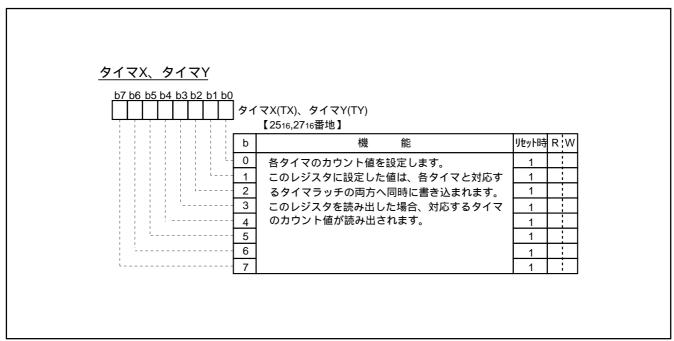

図2.3.5 タイマX、タイマYの構成

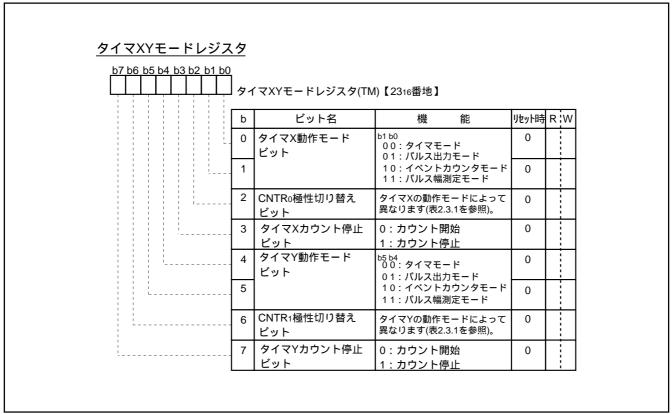

図2.3.6 タイマXYモードレジスタの構成

#### 表2.3.1 CNTR<sub>0</sub>/CNTR<sub>1</sub>極性切り替えビットの機能

| タイマX / Y<br>動作モード | 設定値   | タイマの機能の選択     | CNTR <sub>0</sub> /CNTR <sub>1</sub> 割り込み要求発生要因 |

|-------------------|-------|---------------|-------------------------------------------------|

| タイマモード            | " 0 " | -             | CNTRo/CNTR1入力信号の立ち下がりエッジ                        |

|                   | "1"   | -             | CNTRo/CNTR1入力信号の立ち上がりエッジ                        |

| パルス出力             | " 0 " | " H "レベルからパルス | 出力信号の立ち下がりエッジ                                   |

| モード               |       | 出力            |                                                 |

|                   | " 1 " | " L "レベルからパルス | 出力信号の立ち上がりエッジ                                   |

|                   |       | 出力            |                                                 |

| イベント              | " 0 " | 立ち上がりエッジ      | 入力信号の立ち下がりエッジ                                   |

| カウンタ              |       | をカウント         |                                                 |

| モード               | " 1 " | 立ち下がりエッジ      | 入力信号の立ち上がりエッジ                                   |

|                   |       | をカウント         |                                                 |

| パルス幅              | " 0 " | " H "レベル幅を測定  | 入力信号の立ち下がりエッジ                                   |

| 測定モード             |       |               |                                                 |

|                   | "1"   | " L "レベル幅を測定  | 入力信号の立ち上がりエッジ                                   |

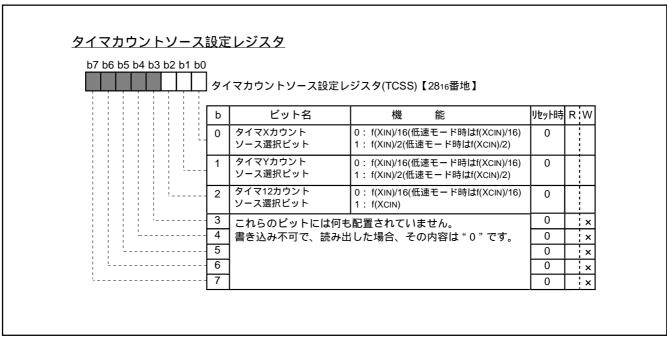

図2.3.7 タイマカウントソース設定レジスタの構成

#### 割り込み要求レジスタ1 b7 b6 b5 b4 b3 b2 b1 b0 割り込み要求レジスタ1(IREQ1)【3C16番地】 ビット名 Jセット時 R W INTo割り込み要求 0:割り込み要求なし 0 0 ビット 1:割り込み要求あり . | \* 書き込む際は"0"を書き込んでください。 0 INT1割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり INT2割り込み要求 0:割り込み要求なし 3 0 ビット 1:割り込み要求あり INT3/シリアルI/O2割り 0:割り込み要求なし 0 込み要求ビット 1:割り込み要求あり 書き込む際は"0"を書き込んでください 0 6 タイマX割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり 0:割り込み要求なし タイマY割り込み要求 0 ビット 1:割り込み要求あり \*ソフトウエアによって"0"にできますが、"1"にはできません。

図2.3.8 割り込み要求レジスタ1の構成

図2.3.9 割り込み要求レジスタ2の構成

図2.3.10 割り込み制御レジスタ1の構成

図2.3.11 割り込み制御レジスタ2の構成

### 2.3.3 タイマの応用例

#### (1) 基本的な機能と用途

[機能1]イベント間隔の管理(タイマX、タイマY、タイマ1、タイマ2) タイマにカウント値を設定すると、一定時間後にタイマの割り込み要求が発生します。 用途

- ・出力信号のタイミング生成

- ・ウエイト時間の生成

#### 「機能2] 周期的な動作の管理(タイマX、タイマY、タイマ1、タイマ2)

タイマがアンダフローするごとに、自動的にタイマラッチの値を対応するタイマに書き込み、 周期的にタイマの割り込み要求が発生します。

#### 用途

- ・周期的な割り込みの発生

- ・時計機能(250msの測定) 応用例1

- ・メインルーチンの周期管理

#### 「機能3] 方形波の出力(タイマX、タイマY)

タイマがアンダフローするごとに、CNTR端子の出力レベルを反転します(パルス出力モード)。 用途

- ・圧電ブザー出力 応用例2

- ・リモコン搬送波の発生

#### [機能4]外部パルスのカウント(タイマX、タイマY)

タイマのカウントソースとして、CNTR端子に入力される外部パルスをカウントします(イベントカウンタモード)。

#### 用途

- ・周波数の測定 応用例3

- ・外部パルスの分周

- ・外部パルスをカウントソースとする周期の割り込み発生(リールパルスのカウント)

#### [機能5]外部パルス幅の測定(タイマX、タイマY)

CNTR端子に入力される外部パルスの H "レベル幅又は L "レベル幅を測定します(パルス幅測定モード)。

#### 用途

- ・外部パルスの周波数の測定(モータのFGパルス(注)のパルス幅測定) 応用例4

- ・外部パルスのデューティの測定(周波数が固定されている場合)

- 注. FGパルス:モータの速度制御を行うためモータの速度を検出するパルス

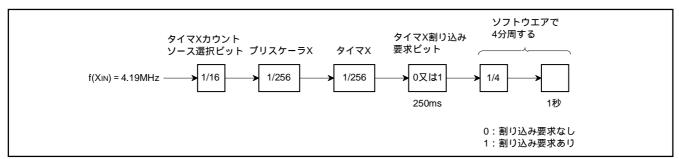

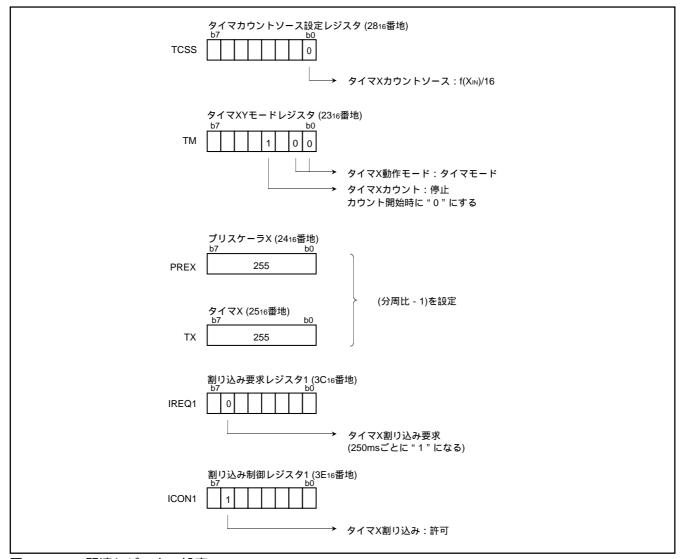

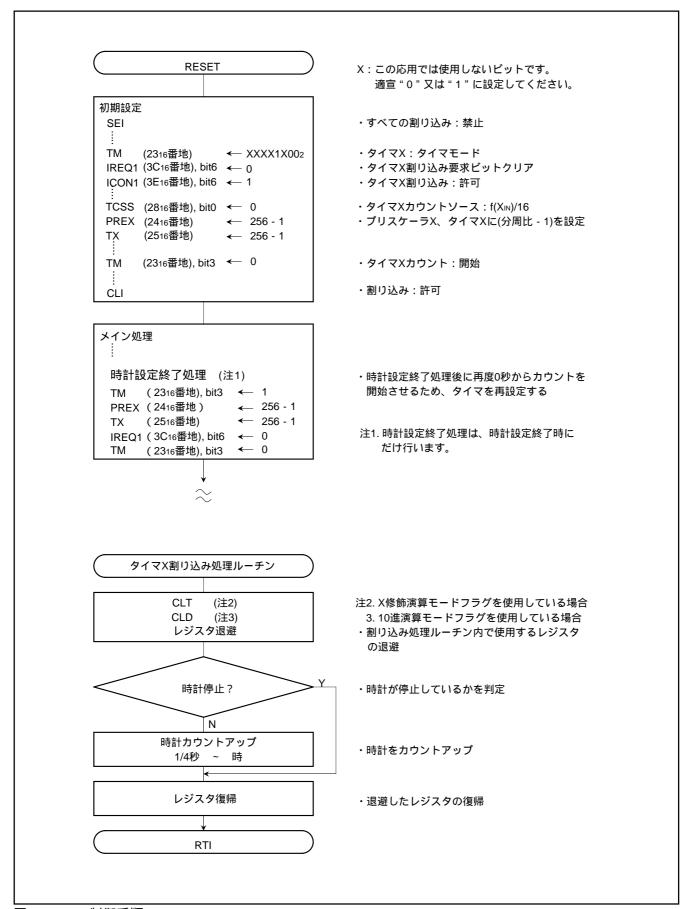

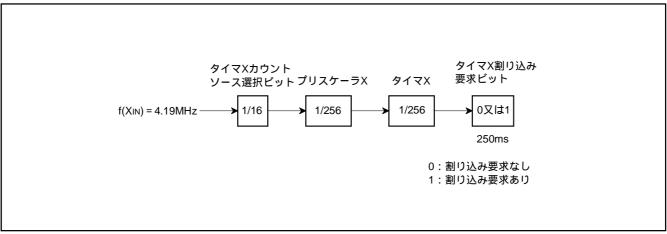

(2) タイマの応用例1:時計機能(250 msの測定)

ポイント: クロックをタイマで分周し、250 msごとに時計をカウントアップします。

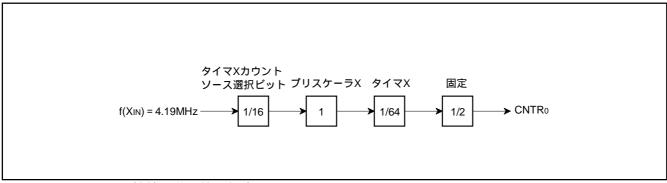

仕 様:・クロックf(XIN) = 4.19 MHz (2<sup>22</sup> Hz)をタイマXで分周。

・タイマX割り込み(250 msごとに発生)処理ルーチンで、時計をカウントアップ。

タイマの接続と分周比の設定を図2.3.12、関連レジスタの設定を図2.3.13、制御手順を図2.3.14に示します。

図2.3.12 タイマの接続と分周比の設定

図2.3.13 関連レジスタの設定

図2.3.14 制御手順

RJJ05B0876-0100/Rev1.00 2005.11 Page 30 of 116

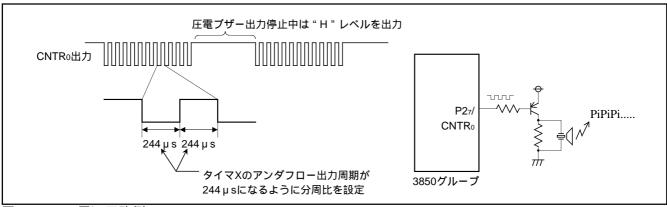

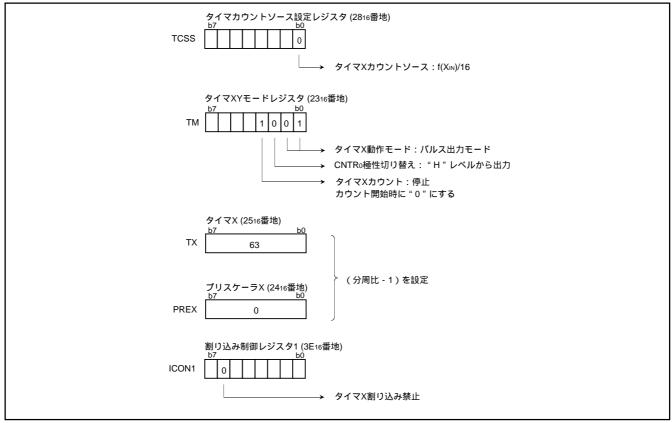

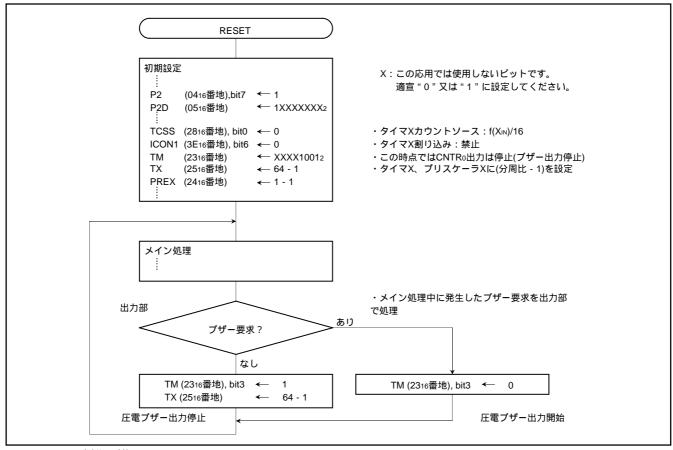

(3) タイマの応用例2:圧電ブザー出力

ポイント:タイマの方形波出力機能を圧電ブザー出力に応用します。

仕 様:・クロックf(XIN) = 4.19MHz (2<sup>22</sup> Hz)を約2kHz(2048Hz)まで分周した方形波を、P27/CNTRo端子から出力。

・圧電ブザー出力停止中はP27/CNTR0端子のレベルを"H"に固定。

周辺回路例を図2.3.15、タイマの接続と分周比の設定を図2.3.16に示します。また、関連レジスタの設定を図2.3.17、制御手順を図2.3.18に示します。

図2.3.15 周辺回路例

図2.3.16 タイマの接続と分周比の設定

図2.3.17 関連レジスタの設定

図2.3.18 制御手順

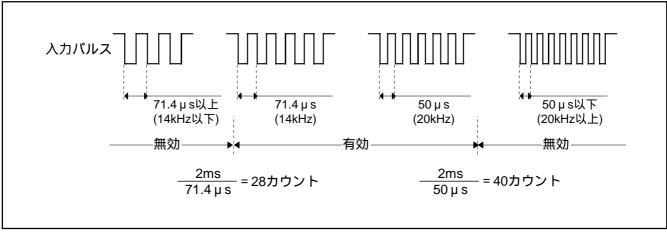

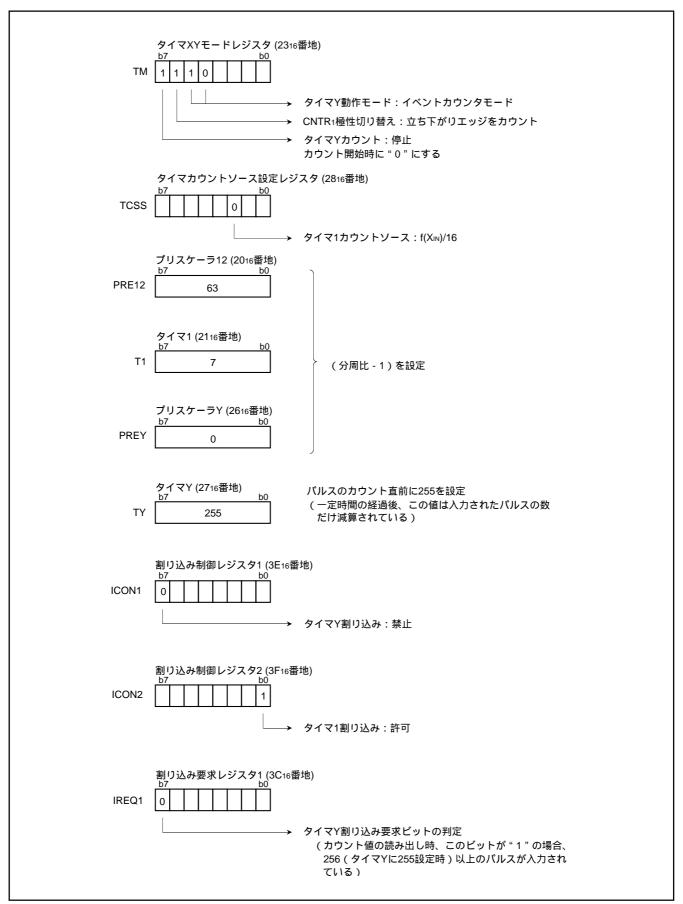

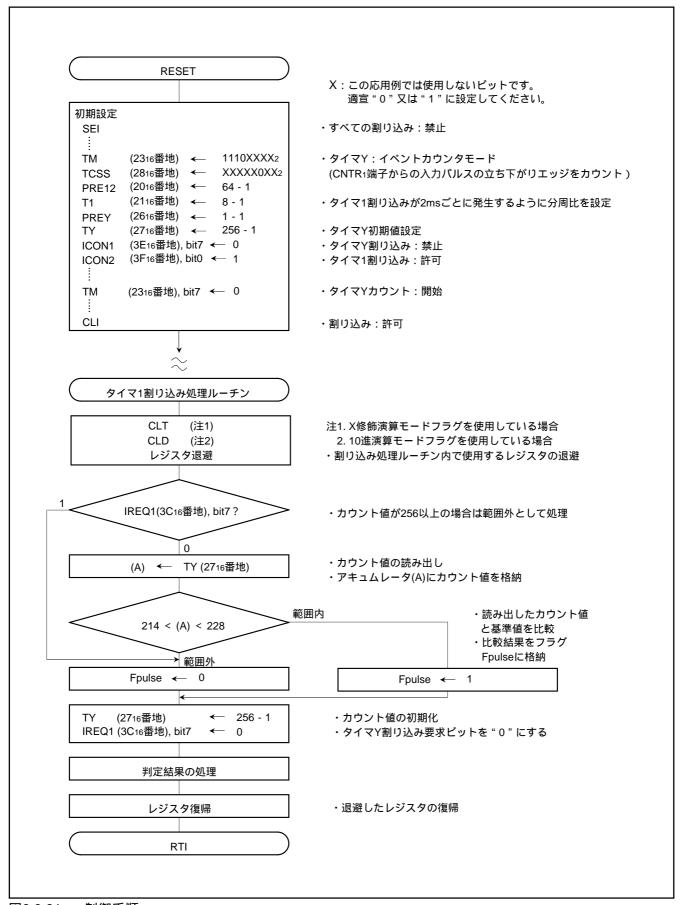

(4) タイマの応用例3:周波数の測定

ポイント:周波数が有効範囲内にあるかを判定するために、以下に示す2つの値を比較します。

- ・P40/CNTR1端子に入力されるパルスをタイマでカウントした値

- ・基準値

- 仕 様:・クロックf(XIN) = 4.19MHz(2<sup>22</sup>Hz)

- ・P40/CNTR1端子にパルスを入力し、タイマYでカウント。

- ・約2 ms(タイマ1割り込み間隔)ごとにカウント値を読み出し、28~40カウントの場合を有効と判断。

- ・タイマがダウンカウンタであるため、227~215(注)とカウント値を比較。 注. 227~215 = 255(カウンタの初期値) - 28~40(有効カウント数)

入力パルスの有効又は無効の判定方法を図2.3.19、関連レジスタの設定を図2.3.20、制御手順を図2.3.21に示します。

図2.3.19 入力パルス有効又は無効の判定方法

図2.3.20 関連レジスタの設定

図2.3.21 制御手順

RJJ05B0876-0100/Rev1.00 2005.11 Page 35 of 116

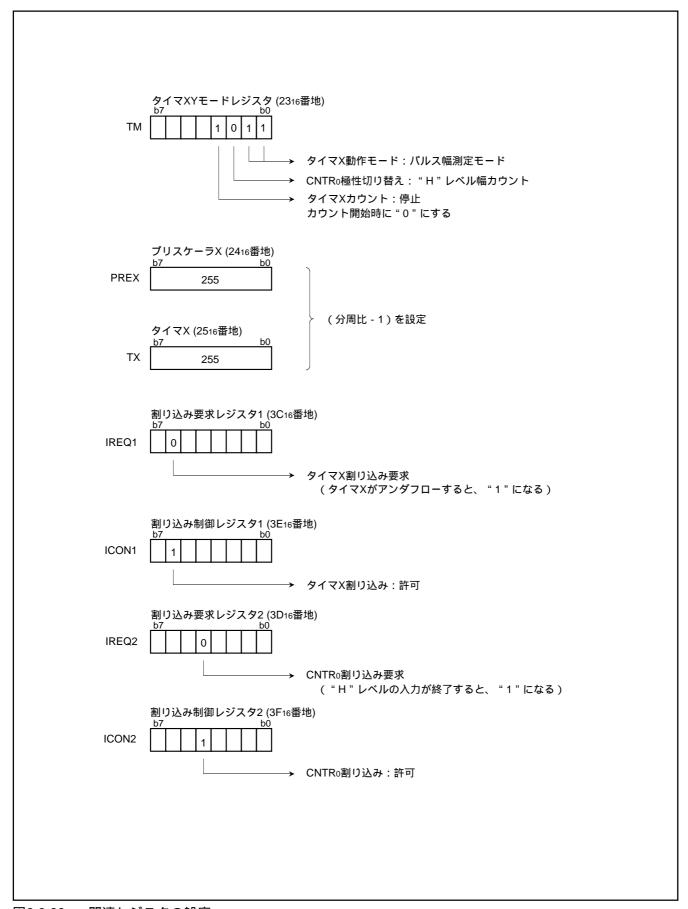

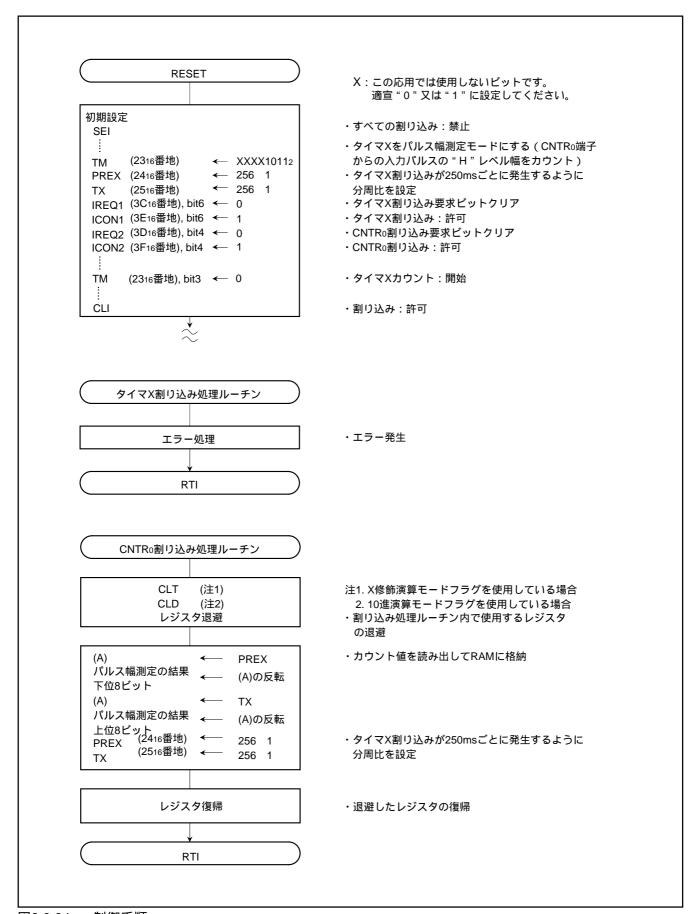

(5) タイマの応用例4:モータのFGパルスのパルス幅測定

ポイント: CNTRo端子に入力されるパルスの"H"レベル幅をタイマXでカウントします。アンダフローはタイマX割り込みで検出され、入力パルスの"H"レベルの終了はCNTRo割り込みで検出されます。

仕 様:CNTRo端子から入力されるFGパルスの"H"レベル幅をタイマXでカウント

例:4.19 MHzの場合、16分周された3.8 µ sがカウントソースとなる。FFFF16 ~ 000016の範囲で250 msまで測定可能。

タイマの接続と分周比の設定を図2.3.22、関連レジスタの設定を図2.3.23、制御手順を図2.3.24に示します。

図2.3.22 タイマの接続と分周比の設定

図2.3.23 関連レジスタの設定

RJJ05B0876-0100/Rev1.00 2005.11 Page 37 of 116

図2.3.24 制御手順

RJJ05B0876-0100/Rev1.00 2005.11 Page 38 of 116

#### 2.3.4 タイマに関する注意事項

タイマラッチに値n(\*0 "~\* 255 ")を書き込んだ場合の分周比は、1/(n+1)です。 タイマ12カウントソース選択ビット及びタイマXカウントソース選択ビット、タイマYカウントソース選択ビットによりタイマのカウントソースを切り替えるとき、タイマのカウント入力に細かいパルスが生じてタイマのカウント値が大きく変わることがあります。したがって、タイマのカウントソースを設定した後、プリスケーラ及びタイマに値を設定してください。

# 2.4 シリアル/(0

本節ではシリアルI/Oに関するレジスタの設定方法、注意事項などを説明します。

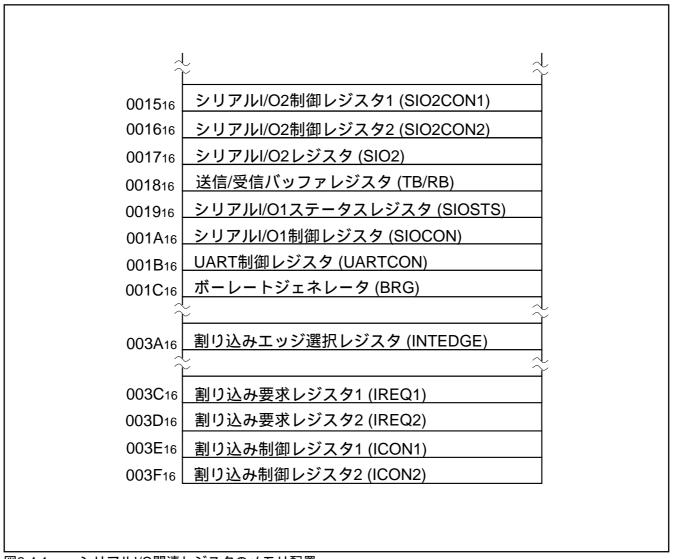

#### 2.4.1 メモリ配置図

図2.4.1 シリアルI/O関連レジスタのメモリ配置

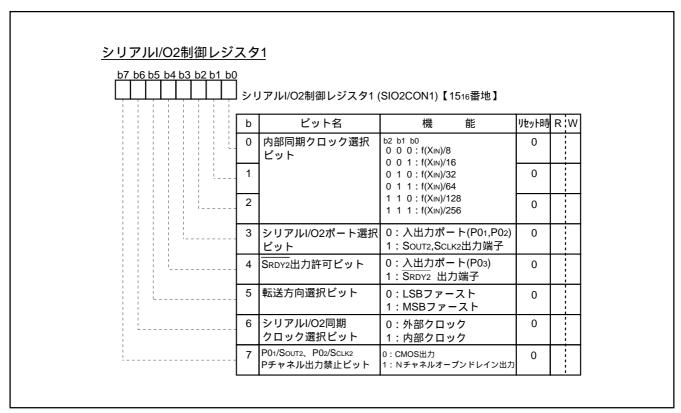

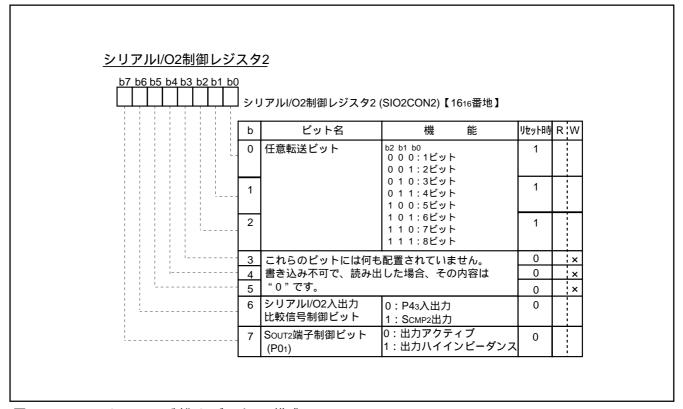

#### 2.4.2 関連レジスタ

図2.4.2 シリアルI/O2制御レジスタ1の構成

図2.4.3 シリアルI/O2制御レジスタ2の構成

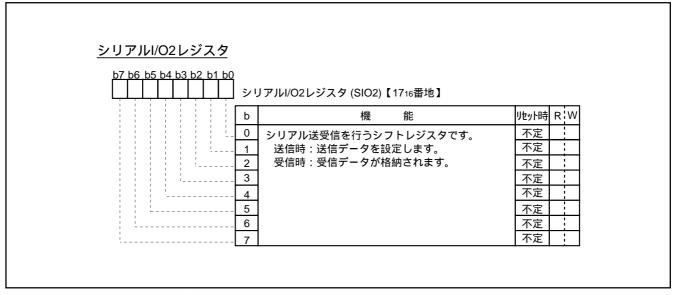

図2.4.4 シリアルI/O2レジスタの構成

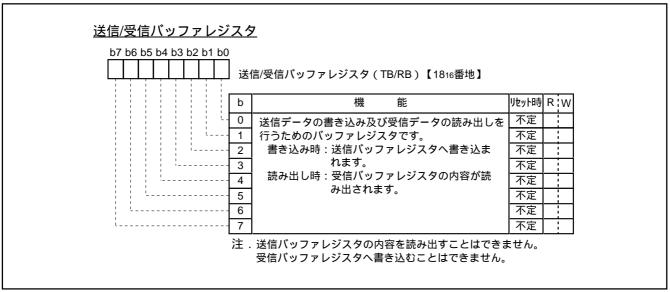

図2.4.5 送信/受信バッファレジスタの構成

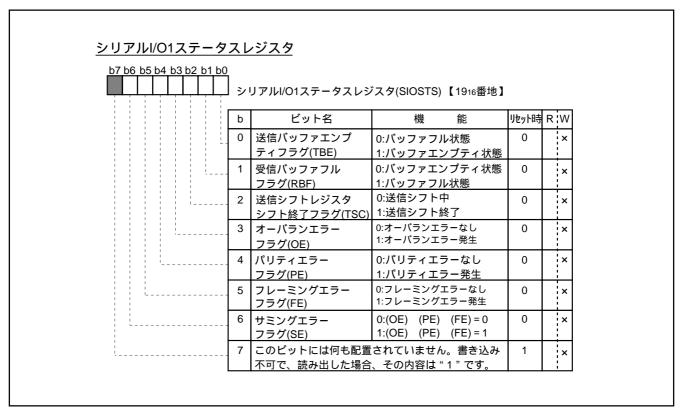

図2.4.6 シリアルI/O1ステータスレジスタの構成

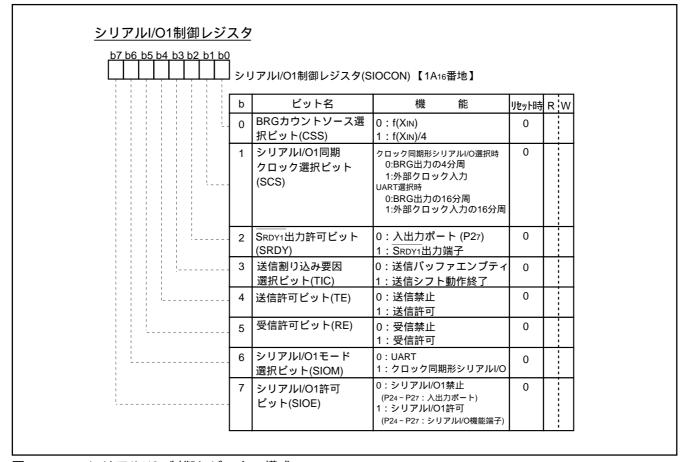

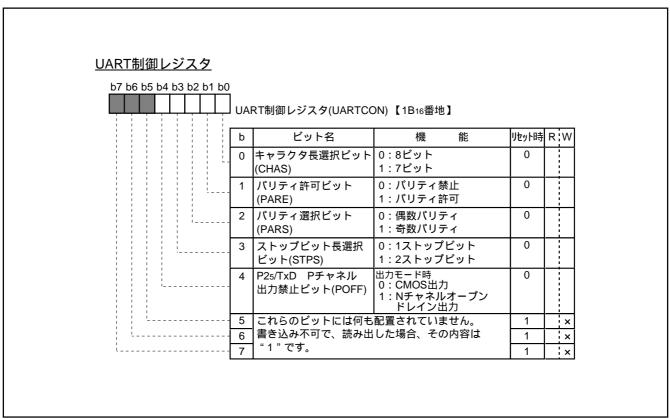

図2.4.7 シリアルI/O1制御レジスタの構成

図2.4.9 ボーレートジェネレータの構成

#### 割り込みエッジ選択レジスタ b7 b6 b5 b4 b3 b2 b1 b0 割り込みエッジ選択レジスタ(INTEDGE)【3A16番地】 リセット時 R W b ビット名 機 0:立ち下がりエッジアクティブ 1:立ち上がりエッジアクティブ INTo割り込みエッジ 0 0 選択ビット INT1割り込みエッジ 0:立ち下がりエッジアクティブ 0 1:立ち上がりエッジアクティブ 選択ビット 0:立ち下がりエッジアクティブ 1:立ち上がりエッジアクティブ INT2割り込みエッジ 0 選択ビット 3 INT3割り込みエッジ 0:立ち下がりエッジアクティブ 0 1:立ち上がりエッジアクティブ 選択ビット シリアルI/O2/INT3 0:INT3割り込み 0 割り込み要因ビット 1:シリアルI/O2割り込み 5 これらのビットには何も配置されていません。書き込み不 0 可で、読み出した場合、その内容は"0"です。 6 × 0 7

図2.4.10 割り込みエッジ選択レジスタの構成

#### 割り込み要求レジスタ1 b7 b6 b5 b4 b3 b2 b1 b0 割り込み要求レジスタ1(IREQ1) 【3C16番地】 リセット時 R W ビット名 b INTo割り込み要求 0:割り込み要求なし 0 0 ビット 1:割り込み要求あり 1 書き込む際は"0"を書き込んでください。 0 INT1割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり INT2割り込み要求 0:割り込み要求なし 3 0 ビット 1:割り込み要求あり INT3/シリアルI/O2割り 0:割り込み要求なし n 込み要求ビット 1:割り込み要求あり 書き込む際は"0"を書き込んでください。 \* 0 タイマX割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり タイマY割り込要求 0:割り込み要求なし ビット 1:割り込み要求あり \*ソフトウエアによって"0"にできますが、"1"にはできません。

図2.4.11 割り込み要求レジスタ1の構成

図2.4.12 割り込み要求レジスタ2の構成

図2.4.13 割り込み制御レジスタ1の構成

図2.4.14 割り込み制御レジスタ2の構成

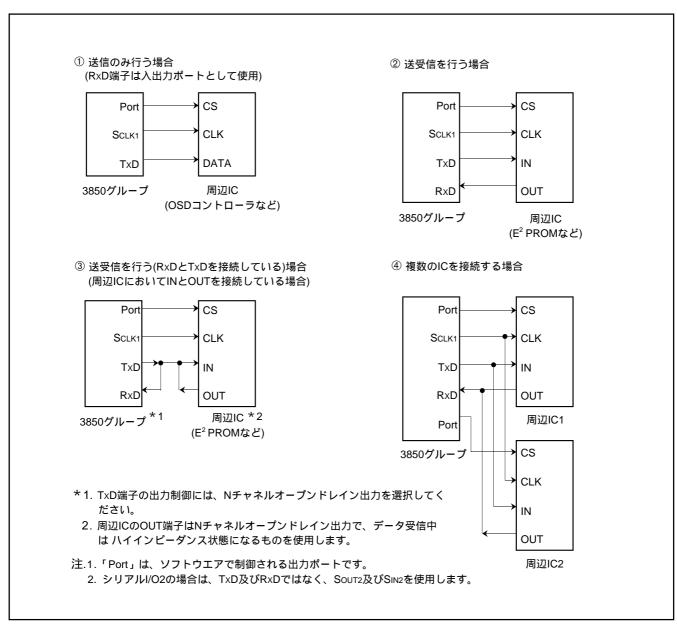

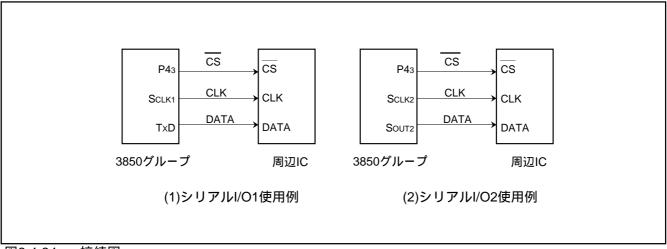

#### 2.4.3 シリアルI/Oの接続例

(1) CS端子を備えている周辺ICの制御

CS端子を備えている周辺ICとの接続例を図2.4.15に示します。 いずれもクロック同期形シリアルI/Oモードを使用した接続例です。

図2.4.15 シリアルI/Oの接続例1

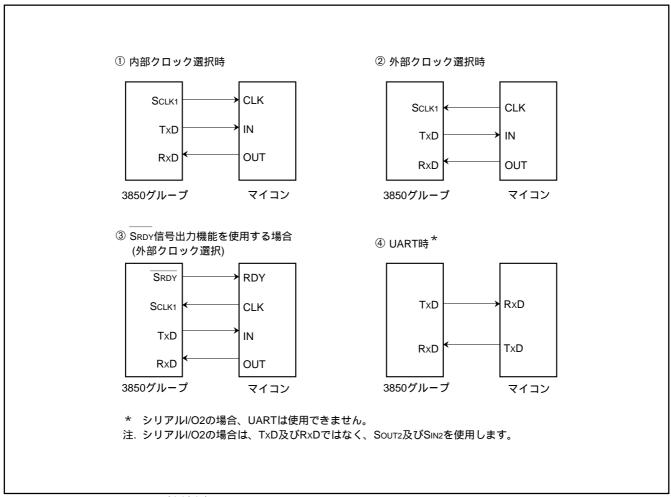

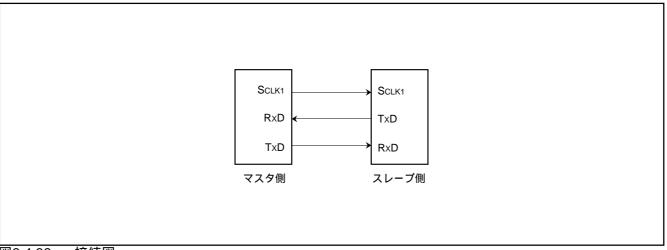

#### (2) マイコンとの接続

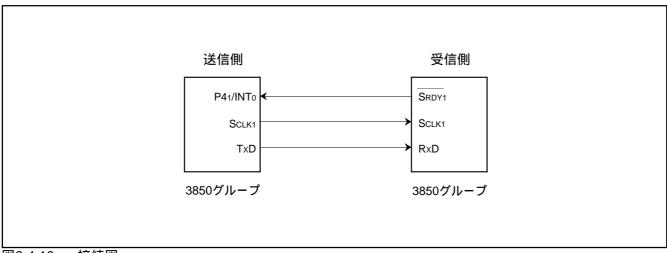

他のマイコンとの接続例を図2.4.16に示します。

図2.4.16 シリアルI/Oの接続例2

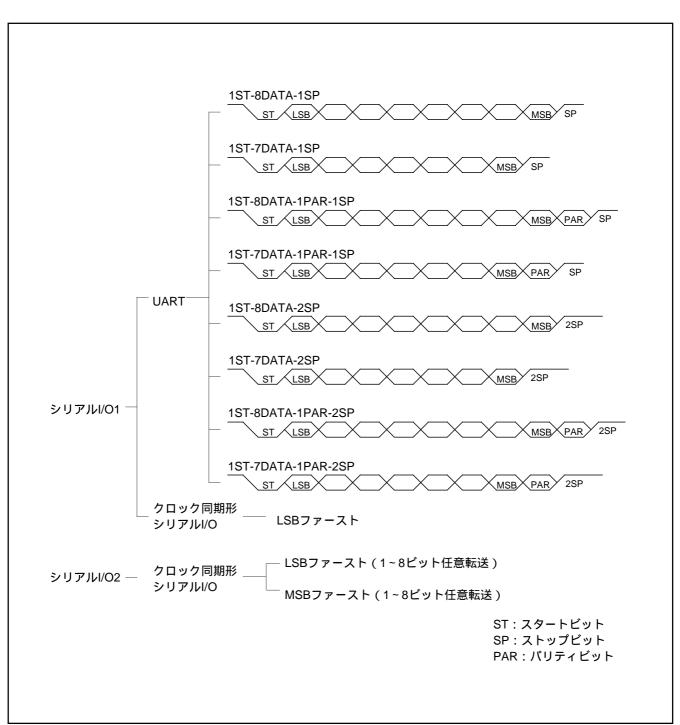

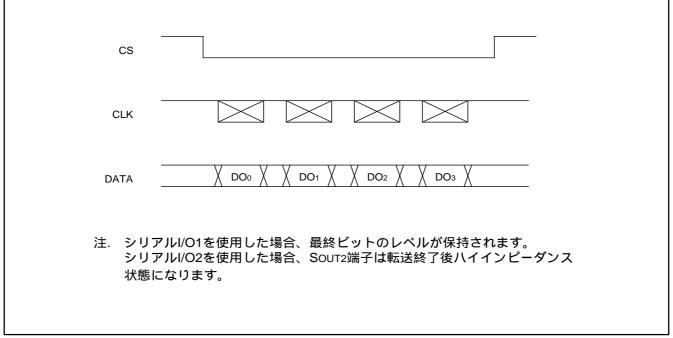

#### 2.4.4 シリアルI/O転送データフォーマット

シリアルI/O1はクロック同期形、非同期形(UART)が選択できます。 シリアルI/O2はクロック同期形で動作します。 シリアルI/O転送データフォーマットを図2.4.17に示します。

図2.4.17 シリアルI/O転送データフォーマット

# 2.4.5 シリアルI/Oの応用例

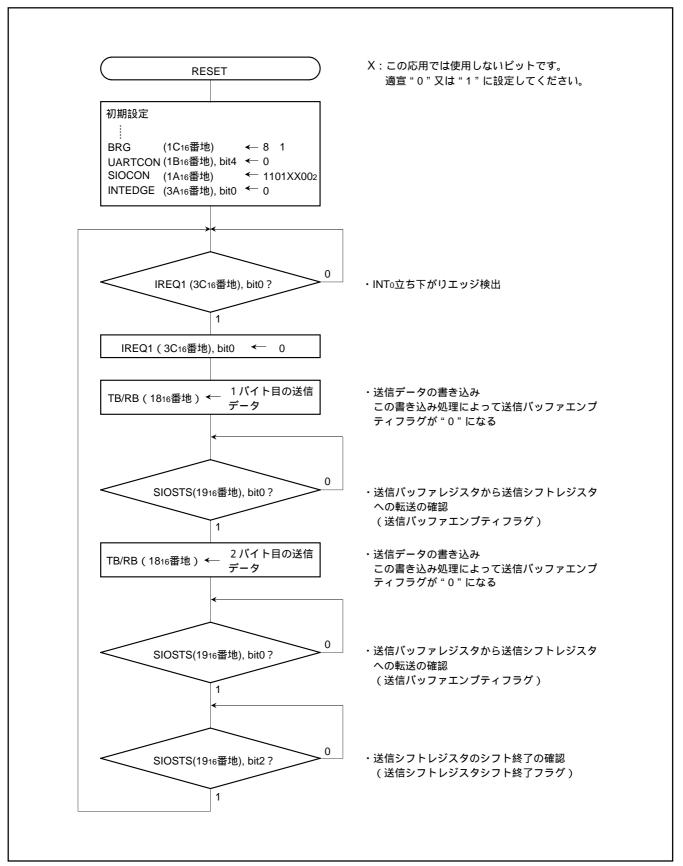

(1) クロック同期形シリアルI/Oを使用した通信(送信/受信)

ポイント:クロック同期形シリアルI/Oを使用して2バイトデータの送受信を行います。 通信制御には、SRDY1信号を使用します。

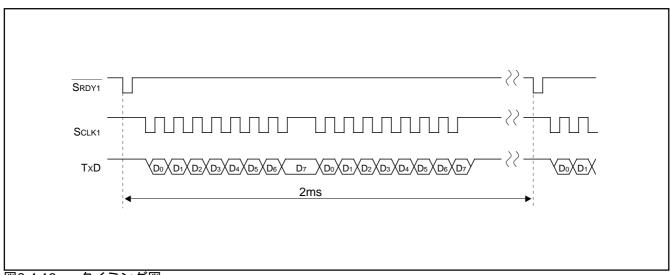

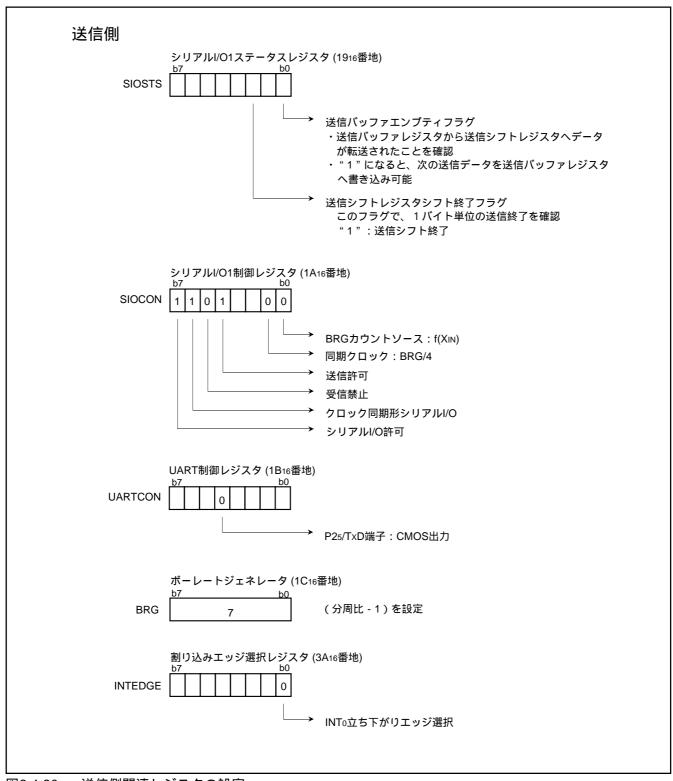

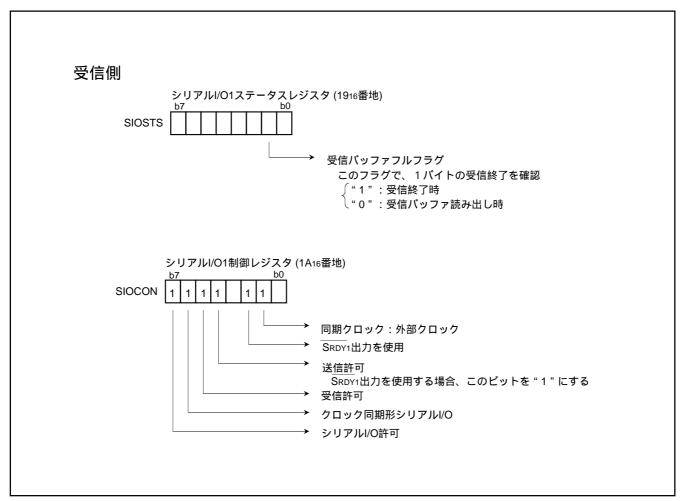

接続図を図2.4.18、タイミング図を図2.4.19、送信側関連レジスタの設定を図2.4.20、受信側関連レジスタの設定を図2.4.21に示します。

図2.4.18 接続図

仕 様:・シリアルI/O(クロック同期形シリアルI/Oを選択)を使用。

- ・同期クロック周波数: 125 kHz (f(XIN) = 4 MHzの32分周)

- ・SRDY1 (受信可能信号)を使用。

- ・2 ms間隔 (タイマにより生成)で受信側からSRDY1信号を出力し、2バイトのデータを 送信側から受信側へ転送。

図2.4.19 タイミング図

図2.4.20 送信側関連レジスタの設定

図2.4.21 受信側関連レジスタの設定

図2.4.22に送信側の制御手順、図2.4.23に受信側の制御手順を示します。

図2.4.22 送信側の制御手順

図2.4.23 受信側の制御手順

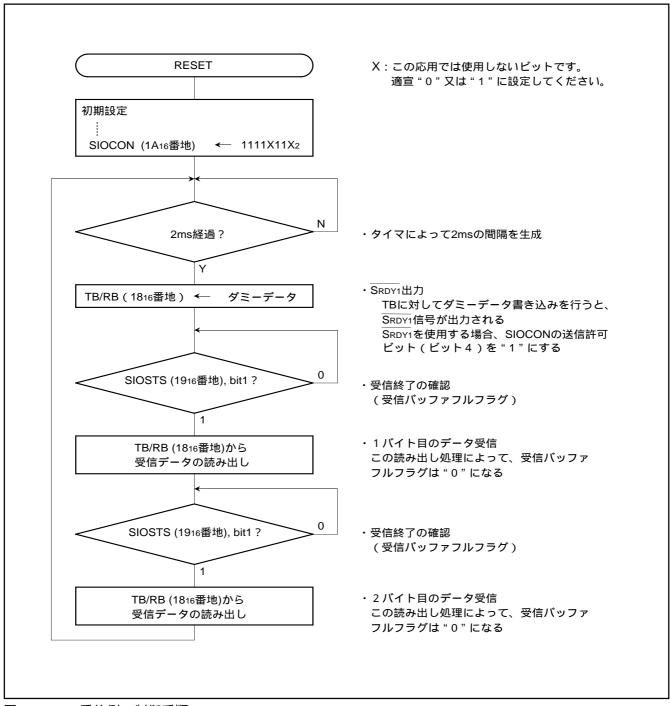

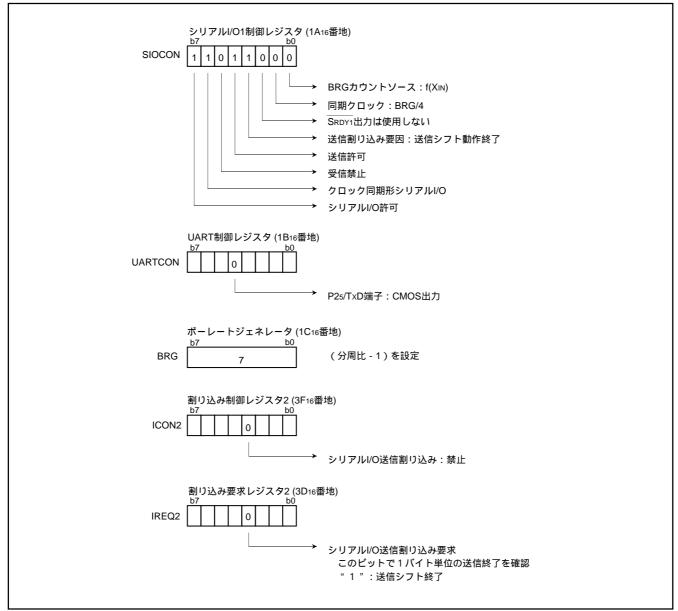

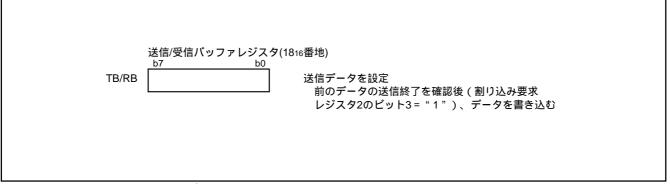

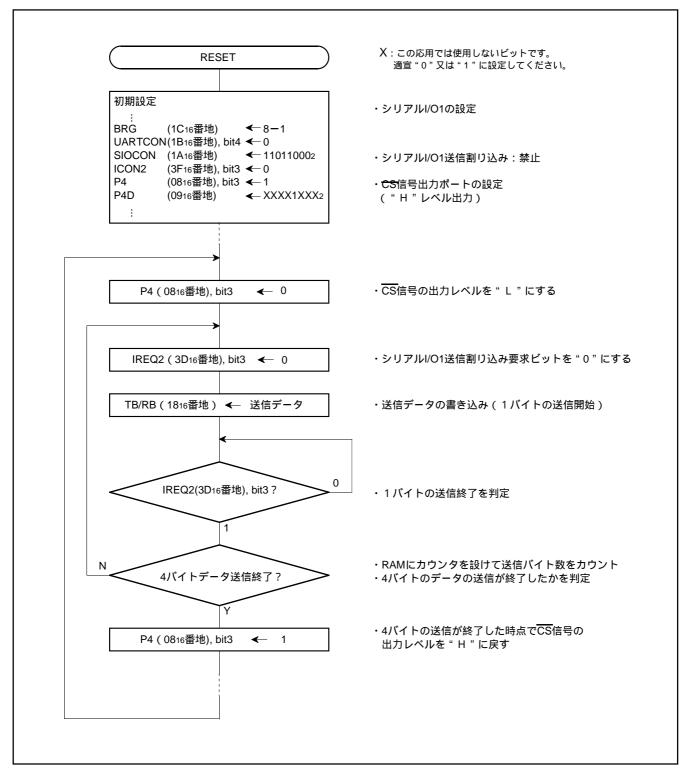

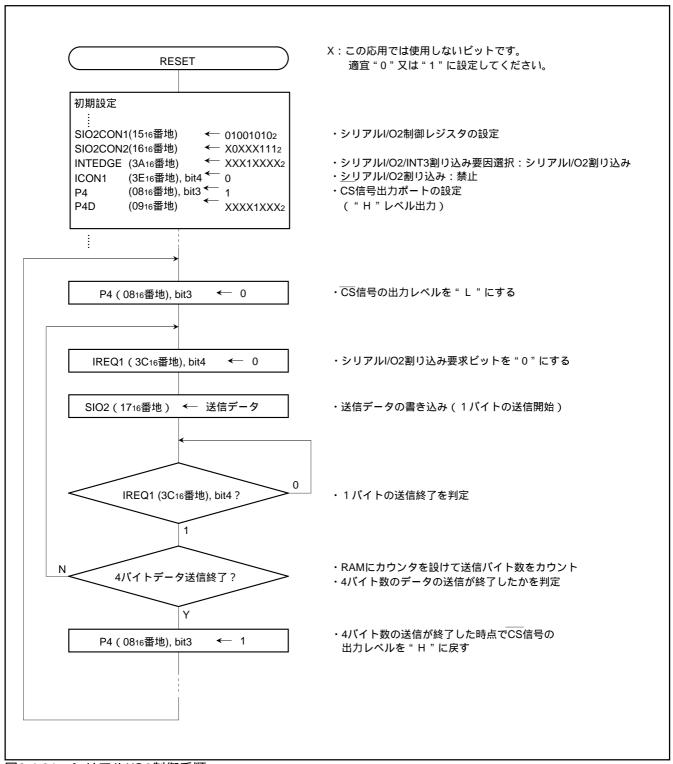

### (2) シリアルデータ出力(周辺I/Cの制御)

ポイント:クロック同期形シリアルI/Oを使用して4バイトデータの送受信を行います。 ポートP43を使用して、周辺ICに対するCS信号を出力します。

接続図を図2.4.24、タイミング図を図2.4.25に示します。

図2.4.24 接続図

仕 様:・クロック同期形シリアルI/Oを使用。

・同期クロック周波数: 125 kHz (f(XIN) = 4 MHzの32分周)

・転送方向:LSBファースト

- ・シリアルI/O割り込みは使用しない。

- ・ポートP43 を周辺ICのCS端子 ("L"アクティブ)に接続して、送信を制御(ポートP43 の出力レベルはソフトウエアで制御)。

図2.4.25 タイミング図(シリアルI/O1)

図2.4.26にシリアルI/O1関連レジスタの設定、図2.4.27にシリアルI/O1送信データの設定を示します。

図2.4.26 シリアルI/O1関連レジスタの設定

図2.4.27 シリアルI/O1送信データの設定

### シリアルI/O1使用例

図2.4.26に示すレジスタ設定において、送信バッファレジスタにデータを書き込むことによって、 シリアルI/O1は1バイトの送信を行える状態になります。

したがって、CS信号を"L"にした後、送信データを1バイトごとに送信バッファレジスタへ書き込み、4バイトのデータ送信が終了した時点でCS信号を"H"に戻します。図2.4.28にシリアルI/O制御手順を示します。

図2.4.28 シリアルI/O制御手順

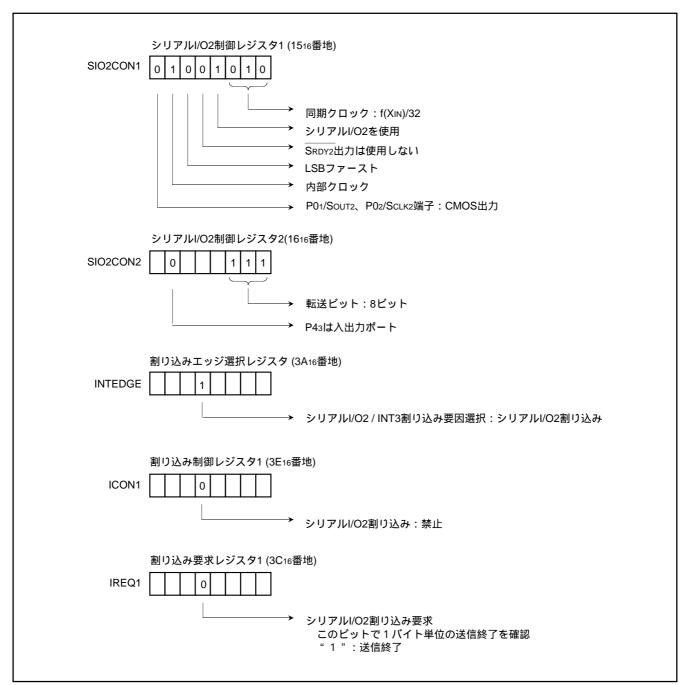

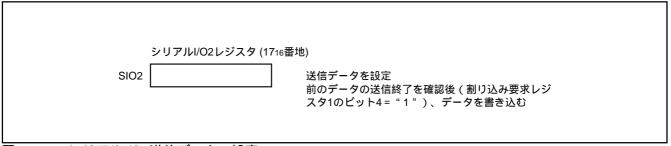

図2.4.29にシリアルI/O2関連レジスタの設定、図2.4.30にシリアルI/O2送信データの設定を示します。

図2.4.29 シリアルI/O2関連レジスタの設定

図2.4.30 シリアルI/O2送信データの設定

#### シリアルI/O2使用例

図2.4.29に示すようにレジスタを設定し、シリアルI/O2レジスタにデータを書き込むことによって、シリアルI/O2は1バイトの送信を行える状態になります。

CS信号を"L"にした後、送信データを1バイトずつシリアルI/O2に書き込み、4バイトのデータ送信が終了した時点でCS信号を"H"に戻してください。図2.4.31にシリアルI/O2制御手順を示します。

図2.4.31 シリアルI/O2制御手順

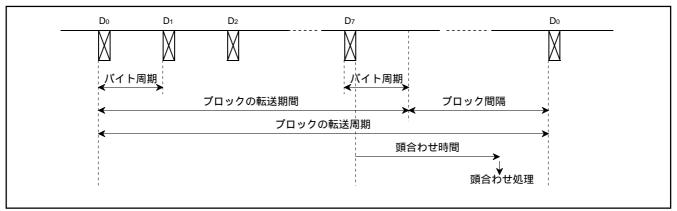

(3) 2つのマイコン間におけるブロックデータ(決められたバイト数のデータ)の周期的な送受信

ポイント:クロック同期形シリアルI/Oを用いて通信を行う場合、同期クロックに含まれたノイズによって送信側と受信側でクロックとデータ間の同期がずれることがあります。そのずれを補正する「頭合わせ」を利用し、常に正常な動作をさせます。この例ではブロック間隔を利用して頭合わせを行っています。

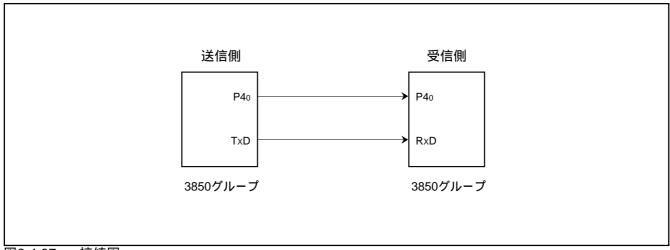

図2.4.32に接続図を示します。

図2.4.32 接続図

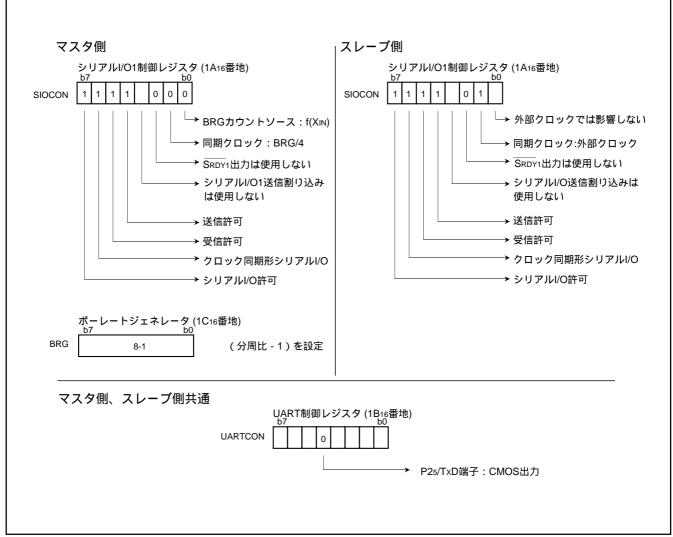

仕様:・シリアルI/O1(クロック同期形シリアルI/Oモード)を使用。

・同期クロック周波数: 125 kHz (f(XIN) = 4 MHzの32分周)

・バイト周期:500 µs

・送受信バイト数:8バイト/各ブロック

・ブロックの転送周期:16 ms・ブロックの転送期間:4 ms

・ブロック間隔:12 ms ・頭合わせ時間:8 ms

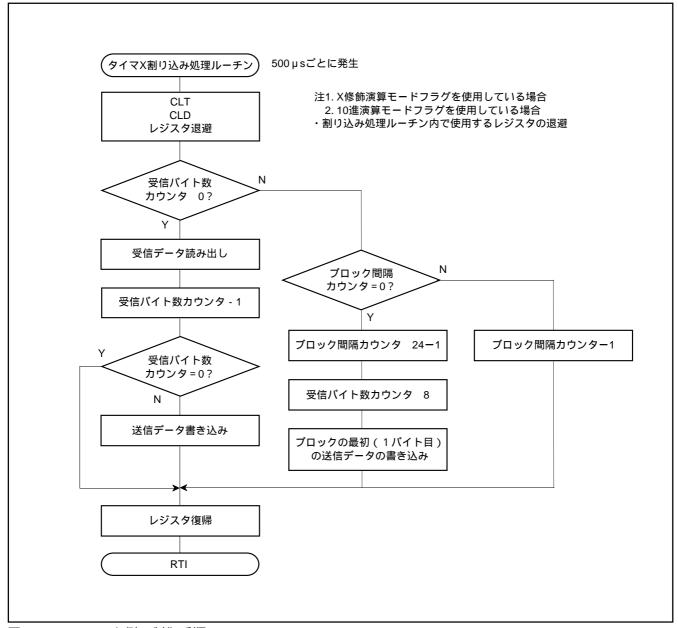

### マスタ側制御

・バイト周期(500 µs)ごとに発生する割り込みルーチンでデータを送受信。

#### スレーブ側制御

- ・シリアルI/O1受信割り込みルーチンでデータを送受信。

- ・1 msごとに発生する割り込みルーチンで頭合わせ。

# 仕様の制限事項:

・「バイト周期 - 1バイトの転送時間」の時間内で受信データの読み込みと次の送信データの 書き込みが行えること。

注.この例ではシリアルI/O1受信割り込み要求発生から次の同期クロックの入力までの時間は436 µ s。

・「頭合わせ時間 < ブロック間隔」であること。

通信は図2.4.33に示すタイミングで行います。スレーブ側では一定時間(頭合わせ時間)以上同期クロックが入力されていない場合、次に入力されたクロックをブロックの初め(頭)として処理します。 1ブロック(8バイト)受信後に入力されたクロックは無視されます。図2.4.34に関連レジスタの設定を示します。

図2.4.33 タイミング図

図2.4.34 関連レジスタの設定

#### ソフトウエアによる制御:

#### マスタ側の制御

500 µ sごとに発生する割り込みルーチンで送信バッファレジスタへの送信データ書き込みにより、送受信を開始します。この割り込みルーチンでは、受信データを読んだ後、次に送信するデータを送信バッファレジスタに書きます。また、1ブロック8バイトの送受信を制御し、ブロック間隔を生成します。

図2.4.35にマスタ側の制御手順を示します。

図2.4.35 マスタ側の制御手順

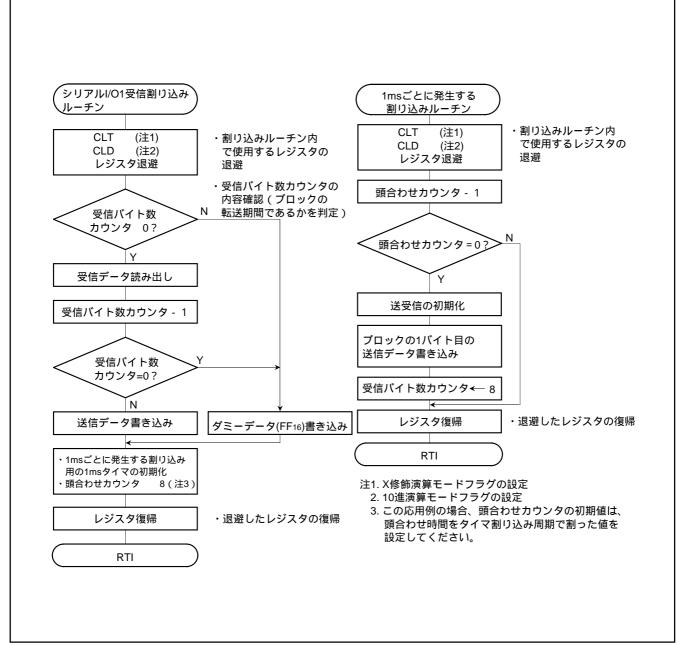

### スレーブ側の制御

図2.4.34に示す関連レジスタの設定終了後、スレーブ側は常に同期クロックを受け付けられる状態になり、8ビットの同期クロックを受信するごとにシリアルI/O受信割り込みが発生します。

シリアルI/O受信割り込み処理ルーチンでは、受信データを読み出した後、次に送信するデータを送信バッファレジスタに書き込みます。

ただし、一定時間(頭合わせ時間)以上、シリアルI/O1受信割り込み要求が発生しない場合は、 1msごとに発生する割り込みルーチンで次の処理を行います。

- 1.シリアルI/O1を初期化する

- 2. ブロックの1バイト目の送信データを送信バッファレジスタに書く

- 3. 次に受信するデータをブロックの1バイト目の受信データとして処理するために、受信バイト 数カウンタを初期化する

図2.4.36にスレーブ側の制御手順を示します。

図2.4.36 スレーブ側の制御手順

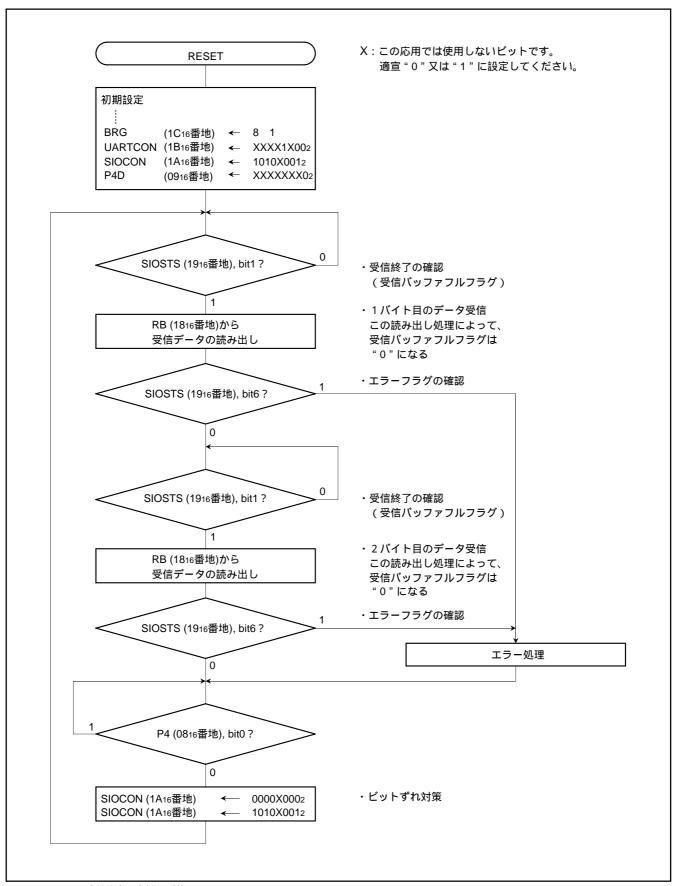

(4) 非同期形シリアルI/O(UART)を使用した通信(送信/受信)

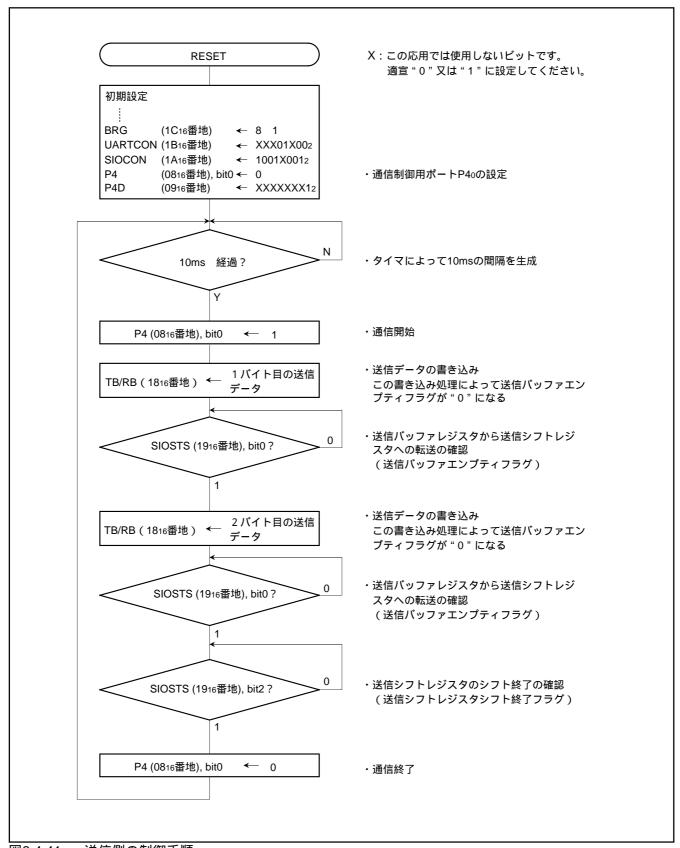

ポイント: 非同期形シリアルI/Oを使用して2バイトデータの送受信を行います。 通信制御には、ポートP40を使用します。

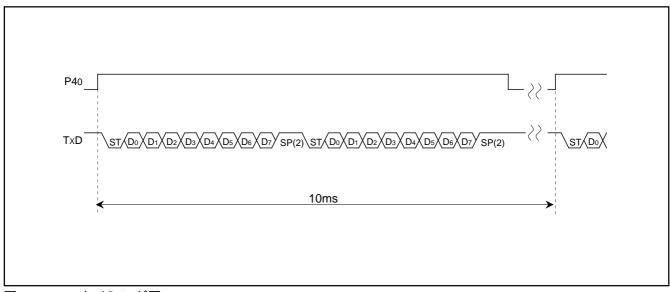

接続図を図2.4.37、タイミング図を図2.4.38に示します。

図2.4.37 接続図

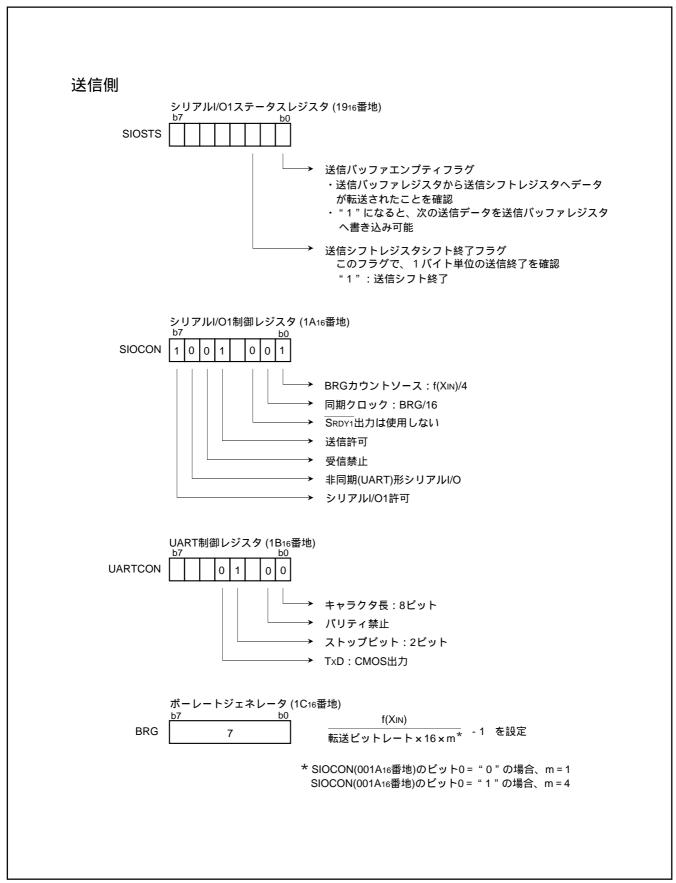

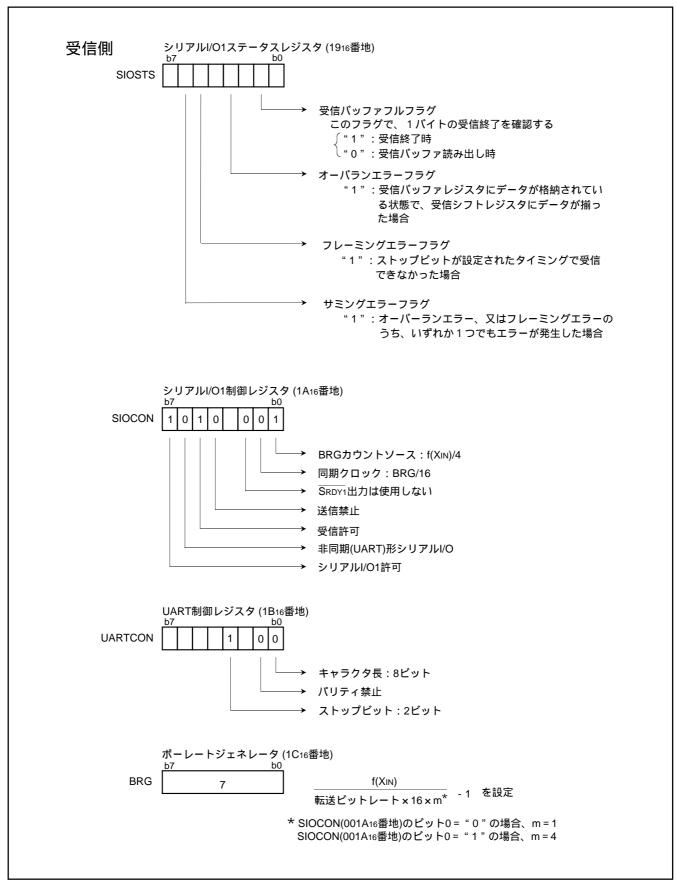

仕 様:・シリアルI/O1(UART選択)を使用。

- ・転送ビットレート: 9600 bps (f(XIN) = 4.9152 MHzの512分周)

- ・ポートP40 を使用する通信制御(ポートP40 の出力レベルはソフトウエアで制御する)。

- ・10 ms間隔(タイマにより生成)で、2バイトのデータを送信側から受信側へ転送。

図2.4.38 タイミング図

表2.4.1、表2.4.2にボーレートジェネレータの設定値と転送ビットレート選択例、図2.4.39に送信側関連レジスタの設定、図2.4.40に受信側関連レジスタの設定を示します。

#### 表2.4.1 ボーレートジェネレータ(BRG)の設定値と転送ビットレート選択例1

| BRGカウント  |           | 転送ビットレート(bps)(注2)    |                 |

|----------|-----------|----------------------|-----------------|

| _ソース(注1) | BRG設定値    | f(XIN) = 4.9152 MHz時 | f(XIN) = 8 MHz時 |

| f(XIN)/4 | 255(FF16) | 300                  | 488.28125       |

| f(XIN)/4 | 127(7F16) | 600                  | 976.5625        |

| f(XIN)/4 | 63(3F16)  | 1200                 | 1953.125        |

| f(XIN)/4 | 31(1F16)  | 2400                 | 3906.25         |

| f(XIN)/4 | 15(0F16)  | 4800                 | 7812.5          |

| f(XIN)/4 | 7(0716)   | 9600                 | 15625           |

| f(XIN)/4 | 3(0316)   | 19200                | 31250           |

| f(XIN)/4 | 1(0116)   | 38400                | 62500           |

| f(XIN)   | 3(0316)   | 76800                | 125000          |

| f(XIN)   | 1(0116)   | 153600               | 250000          |

| f(XIN)   | 0(0016)   | 307200               | 500000          |

## 表2.4.2 ボーレートジェネレータ(BRG)の設定値と転送ビットレート選択例2

| BRGカウント  |                       | 転送ビットレート(bps)(注2)    |

|----------|-----------------------|----------------------|

| _ソース(注1) | BRG設定値                | f(XIN) = 7.9872 MHz時 |

| f(XIN)/4 | 207(CF16)             | 600                  |

| f(XIN)/4 | 103(6716)             | 1200                 |

| f(XIN)/4 | 51(3316)              | 2400                 |

| f(XIN)/4 | 25(1916)              | 4800                 |

| f(XIN)/4 | 12(0C16)              | 9600                 |

| f(XIN)   | 25(1916)              | 19200                |

| f(XIN)   | 12(0C <sub>16</sub> ) | 38400                |

注1. BRGカウントソースはシリアルI/O1制御レジスタ(1A16番地)のビット0で選択します。

2. 転送ビットレートの算出式

m: シリアルI/O制御レジスタのビット0 = "0"の場合、m = 1 シリアルI/O制御レジスタのビット0 = "1"の場合、m = 4

図2.4.39 送信側関連レジスタの設定

図2.4.40 受信側関連レジスタの設定

図2.4.41に送信側の制御手順、図2.4.42に受信側の制御手順を示します。

図2.4.41 送信側の制御手順

図2.4.42 受信側の制御手順

#### 2.4.6 シリアルI/Oに関する注意事項

(1) クロック同期形の選択時(シリアルI/O1)

### 送信動作の停止

シリアルI/O1許可ビット及び送信許可ビットを" 0 "シリアルI/O及び送信禁止)にしてください。

## 理由

シリアルI/O1許可ビットだけを"0"(シリアルI/O1禁止)にしても、送信動作の停止及び送信回路の初期化は行われず、内部の送信動作は継続して行われます(TxD、RxD、SCLK1、SRDY1各端子の機能は入出力ポート機能となるため、送信データが外部へ出力されることはありません)。この状態で、送信バッファレジスタにデータを書き込むと、データは送信シフトレジスタに転送されマイコン内部のシフト動作が開始されます。この時点でシリアルI/O許可ビットを"1"にすると、内部でシフト中のデータが途中からTxD端子に出力され、不具合の原因となります。

### 受信動作の停止

受信許可ビットを"0"(受信禁止)、又はシリアルI/O1許可ビットを"0"(シリアルI/O禁止)にしてください。

### 送受信動作の停止

送信許可ビット、及び受信許可ビットの両方を同時に"0"送受信禁止)にしてください。 (クロック同期形シリアルI/Oモードのデータ送受信時、送信動作又は受信動作のいずれか一方だけを停止することはできません。)

## 理由

クロック同期形シリアルI/Oモードでは、送信及び受信に同一のクロックを使用しているため、いずれか一方だけを禁止した場合、送信と受信の同期がとれなくなり、ビットずれが生じます。 クロック同期形シリアルI/Oモードでは、受信のためにも送信回路のクロック回路が動作しています。そのため、送信許可ビットだけを"0 (送信禁止)にしても送信回路は止まらない構成になっています。また (1)の 送信動作の停止 と同様に、シリアルI/O1許可ビットを"0 (シリアルI/O禁止)にしても送信回路を初期化できません。

### (2) 非同期形の選択時(シリアルI/O1)

## 送信動作の停止

送信許可ビットを"0"(送信禁止)にしてください。

#### 理由

シリアルI/O1許可ビットだけを"0"(シリアルI/O1禁止)にしても、送信動作の停止及び送信回路の初期化は行われず、内部の送信動作は継続して行われます(TxD、RxD、SCLK1、SRDY1各端子の機能は入出力ポート機能となるため、送信データが外部へ出力されることはありません)。この状態で、送信バッファレジスタにデータを書き込むと、データは送信シフトレジスタに転送されマイコン内部のシフト動作が開始されます。この時点でシリアルI/O許可ビットを"1"にすると、内部でシフト中のデータが途中からTxD端子に出力され、不具合の原因となります。

### 受信動作の停止

受信許可ビットを"0"(受信禁止)にしてください。

#### 送受信動作の停止

#### 送信のみの停止

送信許可ビットを"0"(送信禁止)にしてください。

#### 理由

シリアルI/O1許可ビットだけを"0"(シリアルI/O1禁止)にしても、送信動作の停止及び送信回路の初期化は行われず、内部の送信動作は継続して行われます(TxD、RxD、SCLK1、SRDY1各端子の機能は入出力ポート機能となるため、送信データが外部へ出力されることはありません)。この状態で、送信バッファレジスタにデータを書き込むと、データは送信シフトレジスタに転送されマイコン内部のシフト動作が開始されます。この時点でシリアルI/O許可ビットを"1"にすると、内部でシフト中のデータが途中からTxD端子に出力され、不具合の原因となります。

## 受信のみの停止

受信許可ビットを"0"(受信禁止)にしてください。

## (3) 受信側のSRDY1出力

クロック同期形シリアルI/Oモードにおいて、外部クロックを用いて受信側がSRDY1出力を行う場合、受信許可ビット及びSRDY1出力許可ビットとともに、送信許可ビットも"1(送信許可)にしてください。

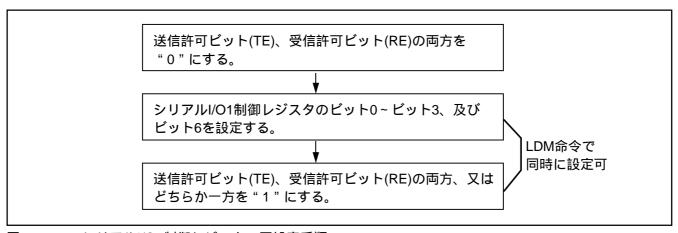

## (4) シリアルI/O1制御レジスタの再設定(シリアルI/O1)

シリアルI/O1制御レジスタを再設定する場合は、送信許可ビット及び受信許可ビットの両方を"0"にして、送信及び受信回路をリセットした後、設定し直してください。

図2.4.43 シリアルI/O1制御レジスタの再設定手順

(5) 送信シフトレジスタシフト終了フラグを使用したデータ送信制御(シリアルI/O1)

送信シフトレジスタシフト終了フラグは、シフトクロックの0.5~1.5クロック分遅れで"1"から"0"へ変化します。したがって送信バッファに送信データを書き込んだ後、送信シフトレジスタ終了フラグを参照してデータ送信を制御する場合、この遅れに注意してください。

(6) 外部クロック選択時の送信制御(シリアルI/O1)

データ送信時、同期クロックとして外部クロックを選択している場合、SCLK1が H 'の状態で送信許可ビットを'1'にしてください。また、送信バッファレジスタへの書き込みも、SCLK1が H 'の状態で行ってください。

(7) 送信許可ビットセット時の送信割り込み要求(シリアルI/O1)

送信割り込みを使用する場合は、以下の手順で送信許可ビットを許可状態にしてください。 CLB命令により、割り込み許可ビットを"0 (禁止状態)にする。

シリアルI/Oの送受信準備を行う。

一命令以上おいてからCLB命令により割り込み要求ビットを"0"にする。

割り込み許可ビットを"1(許可状態)にする。

## 理由

送信許可ビットを"1"に設定すると、送信バッファエンプティフラグ、及び送信シフトレジスタシフト終了フラグは"1"に設定されます。送信割り込みの発生するタイミングに以下どちらかのフラグが"1"に設定されたタイミングを選択しても、割り込み要求が発生し、送信割り込み要求ビットがセットされます。

- ・送信バッファエンプティフラグを"1"に設定

- ・送信シフトレジスタシフト終了フラグを"1"に設定

- (8) 送信データの書き込み(シリアルI/O2)

クロック同期シリアルI/Oでは、同期クロックとして外部クロックを選択した場合、転送クロックの入力レベルが H "の時に、シリアルI/O2レジスタ(シリアルI/Oシフトレジスタ)へ送信データを書き込んでください。

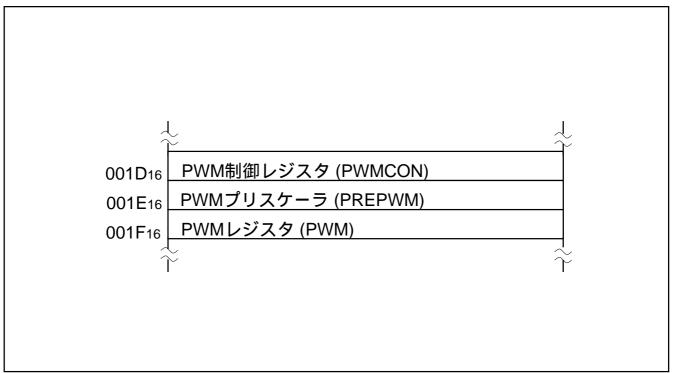

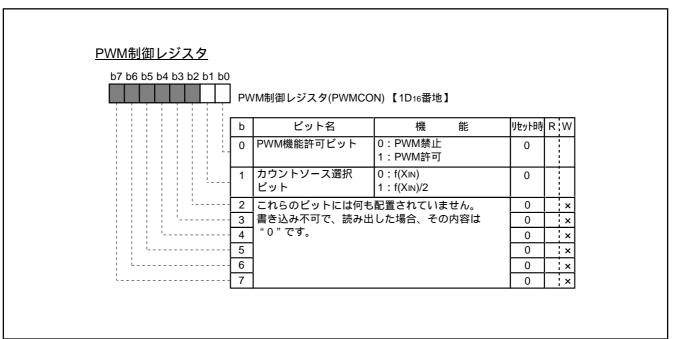

## 2.5 PWM

本節ではPWMに関するレジスタの設定方法、注意事項などを説明します。

### 2.5.1 メモリ配置図

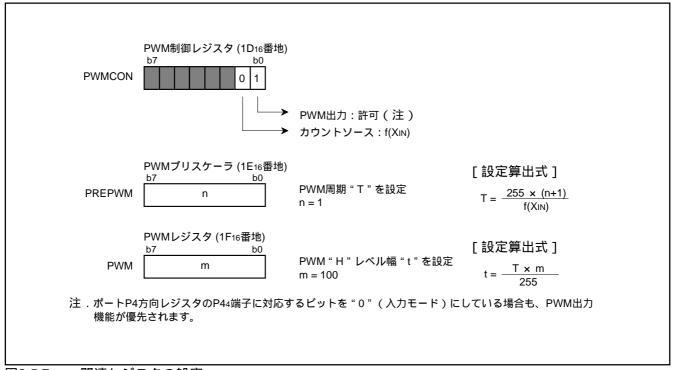

図2.5.1 PWM関連レジスタのメモリ配置

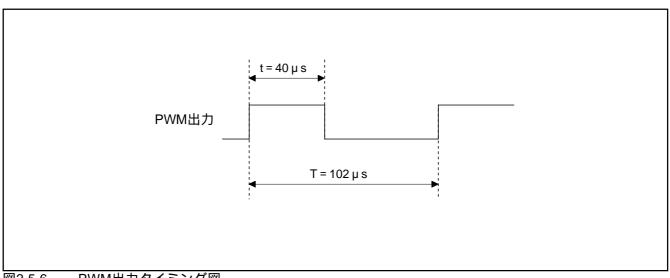

## 2.5.2 関連レジスタ

図2.5.2 PWM制御レジスタの構成

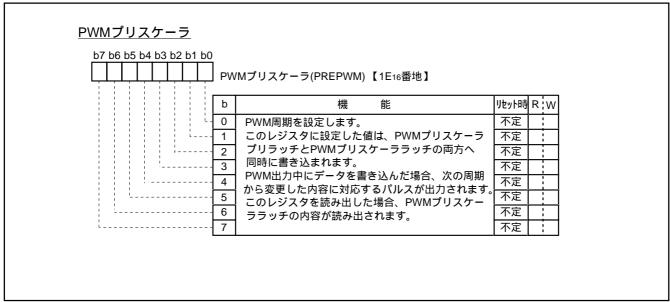

図2.5.3 PWMプリスケーラの構成

図2.5.4 PWMレジスタの構成

## 2.5.3 PWM出力回路の応用例

## モータの制御

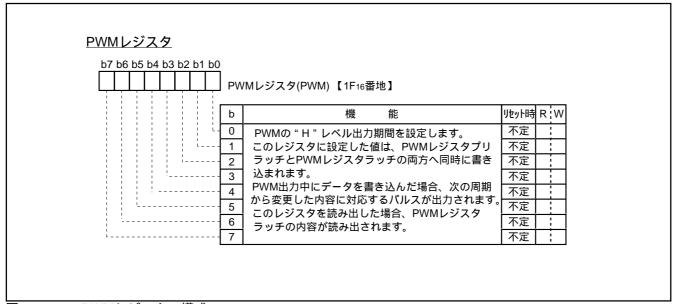

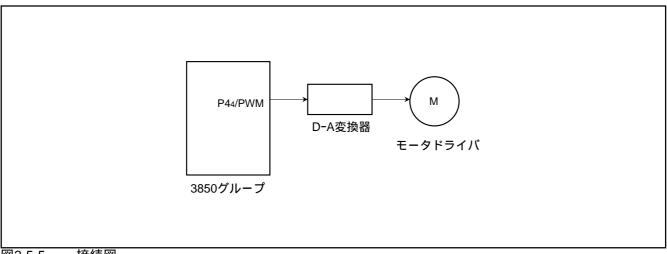

ポイント:PWM(パルス幅変調)出力を使用して、モータの回転速度を制御します。

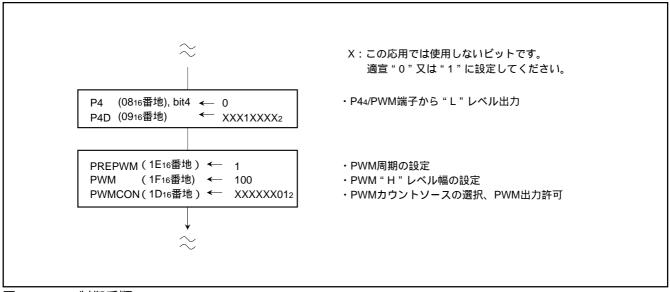

接続図を図2.5.5、PWM出力タイミングを図2.5.6、関連レジスタの設定を図2.5.7に示します。

図2.5.5 接続図

仕 様:・8ビット分解能のPWM出力機能を使用したモータ制御。

・クロックf(XIN) = 5MHz

・PWM周期" T ": 102 μs

・出力パルスの" H "レベル幅" t ": 40 µs(速度固定\*)

\*出力パルス"H"レベル幅を変化させることにより、モータの速度を変更できる。

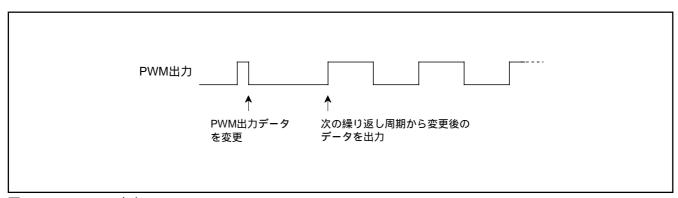

図2.5.6 PWM出力タイミング図

図2.5.7 関連レジスタの設定

## PWM出力について

- PWM機能許可ビットに" 1 "を設定

P44/PWM端子をPWM端子として使用します。" H "から始まるパルスを出力します。

- 2. PWM機能許可ビットに" 0 "を設定 P44/PWM端子をポートP44として使用します。したがって、出力レベルを固定する場合は以下の 処理を順に行ってください。

- ・ポートP4レジスタのビット6に出力値を書き込む

- ・ポートP4方向レジスタに"000100002"を書き込む

- 3. PWMプリスケーラ、及びPWMレジスタにデータを設定後、次の繰り返し周期から新しいデータ に対応するPWM波形が出力されます。

図2.5.8 PWM出力

RJJ05B0876-0100/Rev1.00 2005.11 Page 77 of 116

図2.5.7に示す関連レジスタの設定を行うとPWM波形が外部に出力されます。このPWM出力をローパスフィルタで積分して直流信号に変換し、モータの制御に使用します。図2.5.9に制御手順を示します。

図2.5.9 制御手順

### 2.5.4 PWMに関する注意事項

PWM機能許可ビットが許可に設定され、PWM端子から"L"レベルが出力された後、PWMは開始します。この"L"レベルの出力時間は次のとおりです。

・カウントソース選択ビット = "0"、n = プリスケーラ設定値

$$\frac{n+1}{2 \times f(XIN)}$$

(秒)

・カウントソース選択ビット = "1"、n = プリスケーラ設定値

$$\frac{n+1}{f(XIN)}$$

(秒)

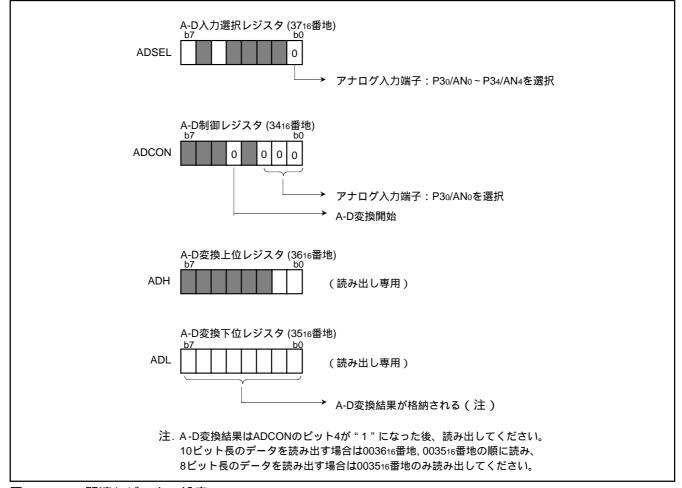

## 2.6 A-D变換器

本節ではA-D変換器に関するレジスタの設定方法、注意事項などを説明します。

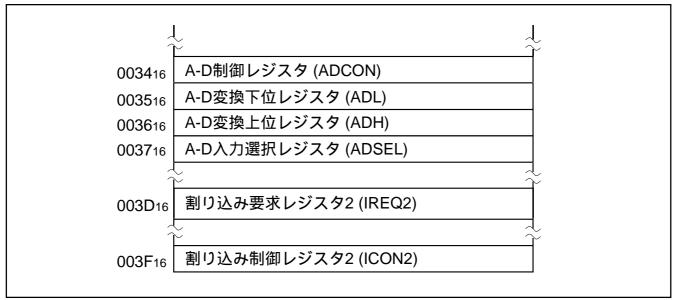

### 2.6.1 メモリ配置図

図2.6.1 A-D変換器関連レジスタのメモリ配置

## 2.6.2 関連レジスタ

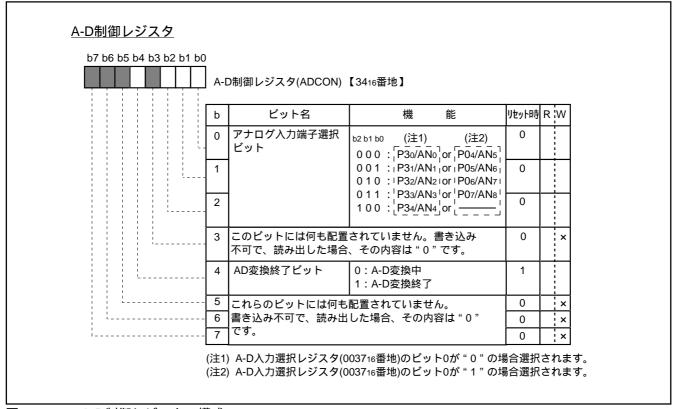

図2.6.2 A-D制御レジスタの構成

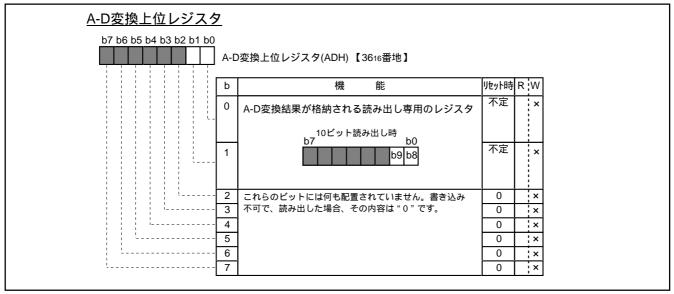

図2.6.3 A-D変換上位レジスタの構成

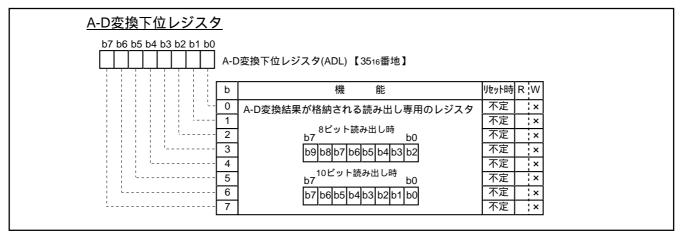

図2.6.4 A-D変換下位レジスタの構成

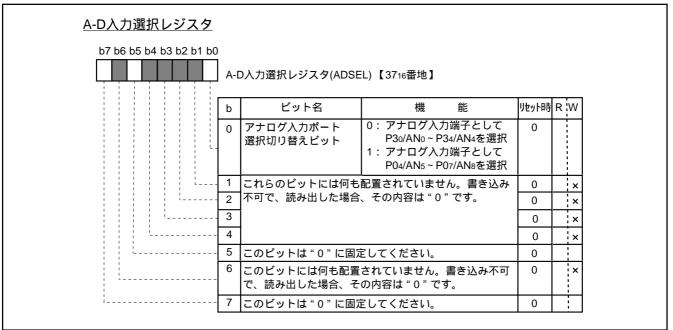

図2.6.5 A-D入力選択レジスタの構成

#### 割り込み要求レジスタ2 b7 b6 b5 b4 b3 b2 b1 b0 割り込み要求レジスタ2(IREQ2) 【3D16番地】 ビット名 リセット時 R¦W 桦 能 h 0 タイマ1割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり タイマ2割り込み要求 0:割り込み要求なし 0 ビット 1:割り込み要求あり シリアルI/O1受信 0:割り込み要求なし 0 1:割り込み要求あり 割り込み要求ビット シリアルI/O1送信 0:割り込み要求なし 0 : \* 3 1:割り込み要求あり 割り込み要求ビット 0:割り込み要求なし CNTRo割り込み要求 0 1:割り込み要求あり ビット 0:割り込み要求なし 5 CNTR1割り込み要求 0 1:割り込み要求あり ビット AD変換割り込み要求 0:割り込み要求なし ビット 1:割り込み要求あり このビットには何も配置されていません。書き込み 0 不可で、読み出した場合、その内容は"0"です。 \*ソフトウエアによって"0"にできますが、"1"にはできません。

図2.6.6 割り込み要求レジスタ2の構成

図2.6.7 割り込み制御レジスタ2の構成

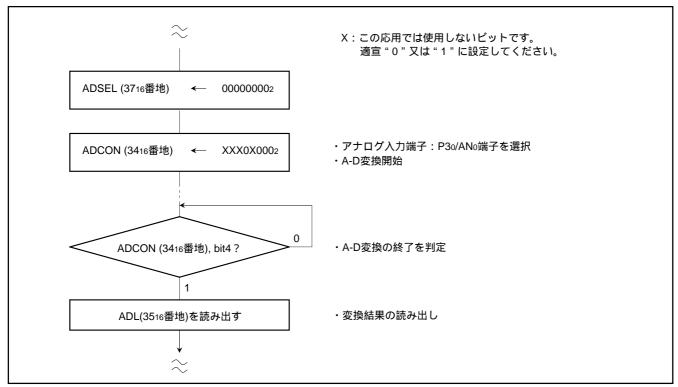

## 2.6.3 A-D变換応用例

## アナログ信号の読み込み

ポイント:センサからのアナログ入力電圧をデジタル値に変換します。

接続図を図2.6.8、関連レジスタの設定を図2.6.9に示します。

図2.6.8 接続図

仕 様:・センサからアナログ入力電圧をデジタル値に変換。

・アナログ入力端子にはP30/AN0端子を使用。

図2.6.9 関連レジスタの設定

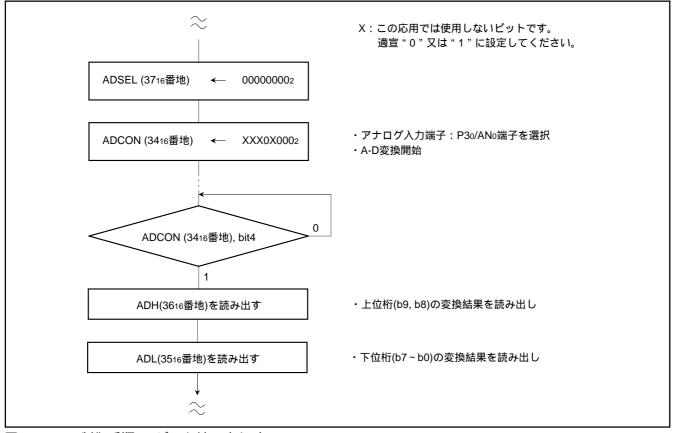

図2.6.9に示す関連レジスタの設定を行うとセンサからのアナログ入力信号をデジタル値に変換します。図2.6.10に8ビット読み出し時の制御手順を、図2.6.11に10ビット読み出し時の制御手順を示します。

図2.6.10 制御手順(8ビット読み出し時)

図2.6.11 制御手順(10ビット読み出し時)

RJJ05B0876-0100/Rev1.00 2005.11 Page 83 of 116

## 2.6.4 A-D変換器に関する注意事項

## (1) アナログ入力端子

アナログ入力の信号源インピーダンスは小さくしてください。又は、アナログ入力端子に、0.01  $\mu$  F ~ 1  $\mu$  F の外付けのコンデンサを付加してください。更に、ユーザサイドで応用製品の十分な動作確認を行ってください。

## 理由

アナログ入力端子には、アナログ電圧比較用のコンデンサが内蔵されています。そのため、インピーダンスの高い信号源からの信号をアナログ入力端子に入力した場合、充放電ノイズが発生し、十分なA-D変換精度が得られない場合があります。

## (2) A-D变換器用電源端子

A-D変換機能の使用又は不使用にかかわらず、A-D変換器用電源端子AVssは以下のように処理してください。

・AVss: Vssに接続

### 理由

AVss端子を開放すると、ノイズなどの影響を受けるためマイコンが誤動作をすることがあります。

### (3) A-D変換中のクロック周波数

比較器は容量結合で構成されており、クロック周波数が低いと電荷が失われます。そのため、A-D 変換中は以下の2点に留意してください。

- ・中速/高速モード時のf(XIN)は500kHz以上にしてください。

- ・STP命令を実行しないでください。

- ・低速モードでA-D変換を実行する場合は、内蔵の自己発振回路を使用してA-D変換を行いますので、f(XIN)の下限周波数の制限はありません。

## 2.7 ウオッチドッグタイマ

本節ではウオッチドッグタイマに関するレジスタの設定方法、制御手順などを説明します。

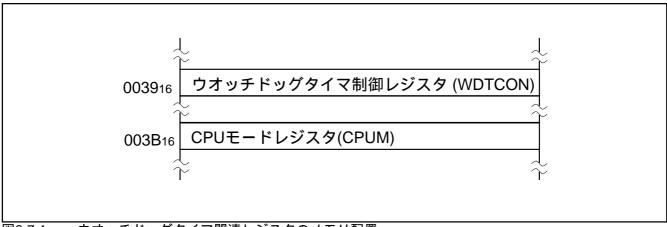

## 2.7.1 メモリ配置図

図2.7.1 ウオッチドッグタイマ関連レジスタのメモリ配置

## 2.7.2 関連レジスタ

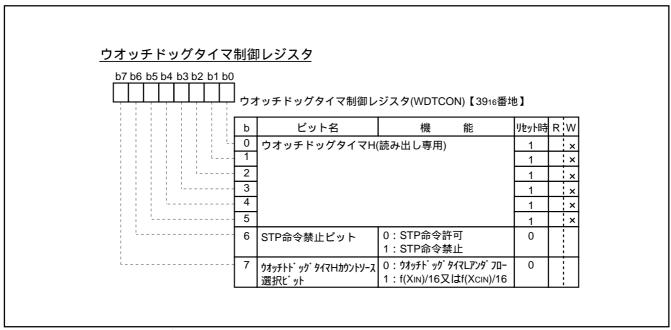

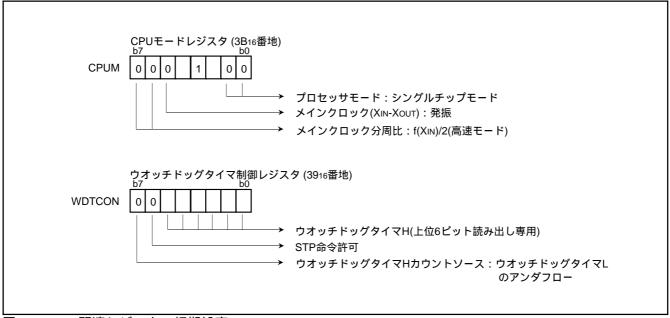

図2.7.2 ウオッチドッグタイマ制御レジスタの構成

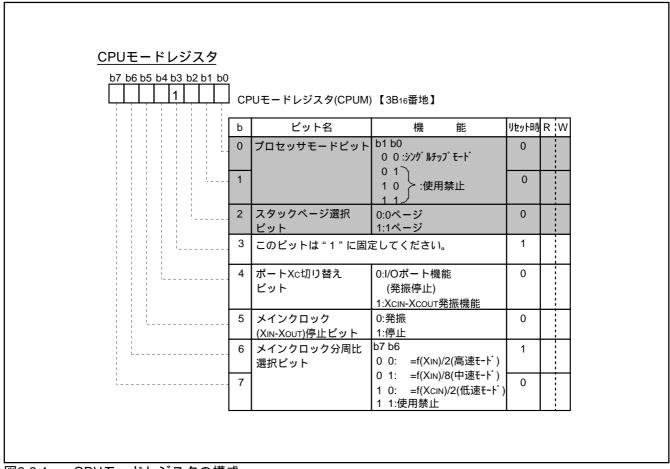

| <u>CPUモードレジスタ</u>       |   |                            |                                                                                     |       |     |

|-------------------------|---|----------------------------|-------------------------------------------------------------------------------------|-------|-----|

| b7 b6 b5 b4 b3 b2 b1 b0 | 1 | PUモードレジスタ(CPUM)            | 【3B16番地】                                                                            |       |     |

|                         | b | ビット名                       | 機能                                                                                  | リセット時 | R W |

|                         | 0 | プロセッサモードビット                | b1 b0<br>0 0 :シングルチップモード<br>0 1 ``                                                  | 0     |     |

|                         | 1 |                            | 10 :使用禁止                                                                            | 0     |     |

|                         | 2 | スタックページ選択<br>ビット           | 0:0ページ<br>1:1ページ                                                                    | 0     |     |

|                         | 3 | このビットは"1"に固え               | 定してください。<br>                                                                        | 1     |     |

|                         | 4 | ポートXc切り替え<br>ビット           | 0:I/Oポート機能<br>(発振停止)<br>1:Xcɪn-Xcouт発振機能                                            | 0     |     |

|                         | 5 | メインクロック<br>(XIN-XOUT)停止ビット | 0:発振<br>1:停止                                                                        | 0     |     |

| 1                       | 6 | メインクロック分周比<br>選択ビット        | b7 b6<br>0 0: =f(X <sub>I</sub> N)/2(高速モート*)<br>0 1: =f(X <sub>I</sub> N)/8(中速モート*) | 1     |     |

| i                       | 7 |                            | 1 0: =f(XCIN)/2(低速t-h<br>1 1:使用禁止                                                   | 0     |     |

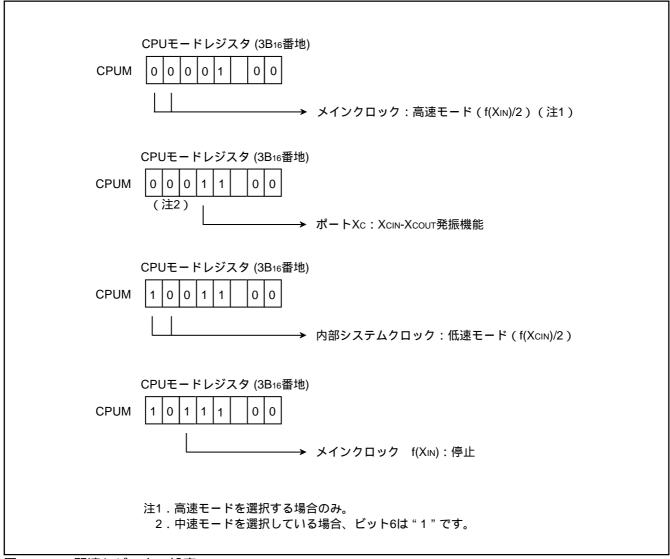

図2.7.3 CPUモードレジスタの構成

## 2.7.3 ウオッチドッグタイマの応用

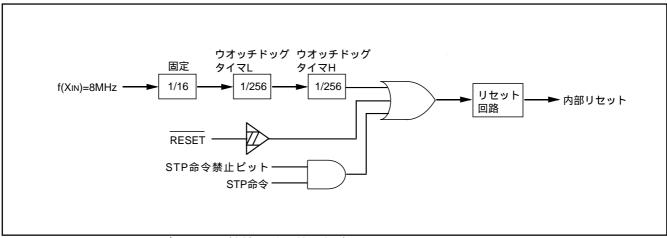

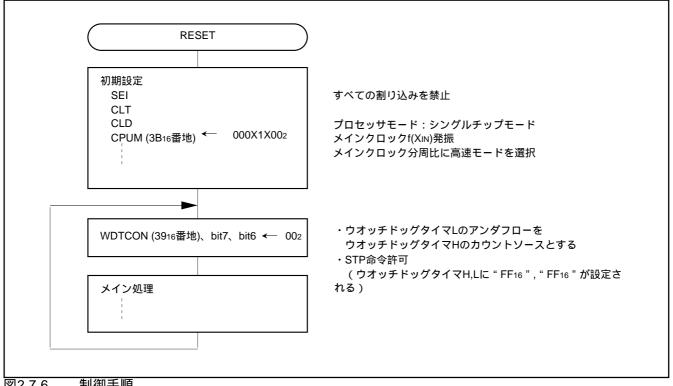

(1) ウオッチドッグタイマの応用例:暴走検出

ポイント:プログラムが暴走した場合に、内部暴走検知タイマでマイコンをリセット状態に復帰させる手段を与えます。

#### 仕様:

- ・ウオッチドッグタイマHのアンダフローによって、プログラムの異常と判断し、マイコンをリセット状態に復帰

- ・ウオッチドッグタイマがアンダフローする前に、メインルーチン1周ごとにウオッチドッグ タイマ制御レジスタのビット6,7へ"0"を設定

- ・メインクロック分周比は高速モードを使用

- ・ウオッチドッグタイマHのカウントソースにはウオッチドッグタイマLのアンダフローを接続

ウオッチドッグタイマの接続と分周比の設定を図2.7.4、関連レジスタの設定を図2.7.5、及び制御手順を図2.7.6に示します。

図2.7.4 ウオッチドッグタイマの接続と分周比の設定

図2.7.5 関連レジスタの初期設定

図2.7.6 制御手順

### 2.7.4 ウオッチドッグタイマに関する注意事項

ストップ解除の待ち時間の間もウオッチドッグタイマはカウントするため、この間にウオッチドッ グタイマがアンダフローしないようにしてください。

ウオッチドッグタイマ制御レジスタのSTP命令禁止ビットを"1"にすると、プログラムにより"0"に 書き替えることはできません。

## 2.8 リセット

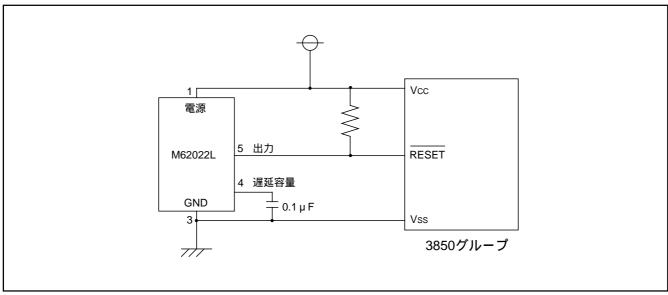

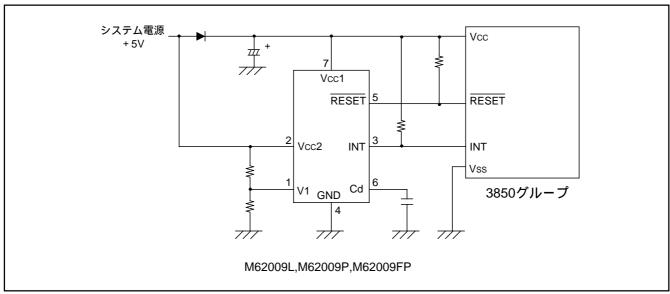

## 2.8.1 リセットICを用いた接続例

図2.8.1 パワーオンリセット回路例

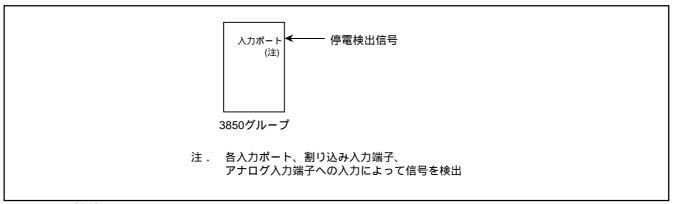

INT割り込みでシステム電源の低下を検出することによって、RAMバックアップモードに切り替えるシステム例を図2.8.2に示します。

図2.8.2 RAMバックアップシステム

RJJ05B0876-0100/Rev1.00 2005.11 Page 89 of 116

## 2.8.2 リセット端子に関する注意事項

## (1) コンデンサの接続

リセット信号が緩やかに立ち上がる場合は、RESET端子とVss端子の間に、セラミックコンデンサなどの高周波特性の良い1000pF以上のコンデンサを接続してください。コンデンサを使用する際は、以下の2点に留意してください。

- ・コンデンサの配線長は最短にしてください。

- ・ユーザサイドで応用製品の動作確認を十分行ってください。

## 理由

RESET入力端子に数nsから数十nsのインパルス性のノイズが乗った場合、マイコンが誤動作をすることがあります。

## (2) 電源投入後のリセット解除

パワーオンリセット等、電源投入後リセットを解除する場合は、電源電圧が2.7V以上に達し、XINが安定発振している状態でXINが20サイクル以上経過した後に解除してください。

## 理由

リセット解除には電源電圧が $2.7 \sim 5.5 V$ にあり、XINが安定発振しているときにXINの20サイクル以上の期間 L"レベルにする必要があります。

## 2.9 クロック発生回路

本節ではクロック発生回路に関するレジスタの設定方法、応用例などを説明します。

## 2.9.1 関連レジスタ

図2.9.1 CPUモードレジスタの構成

#### 2.9.2 クロック発生回路の応用例

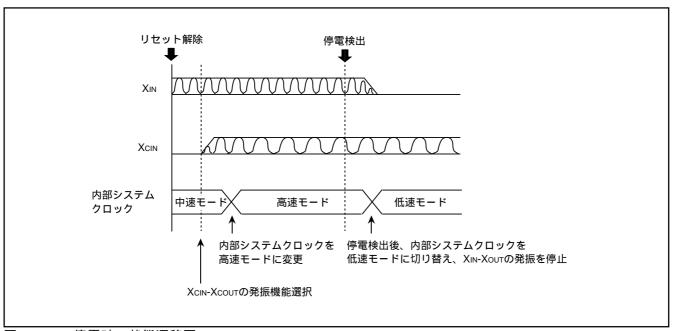

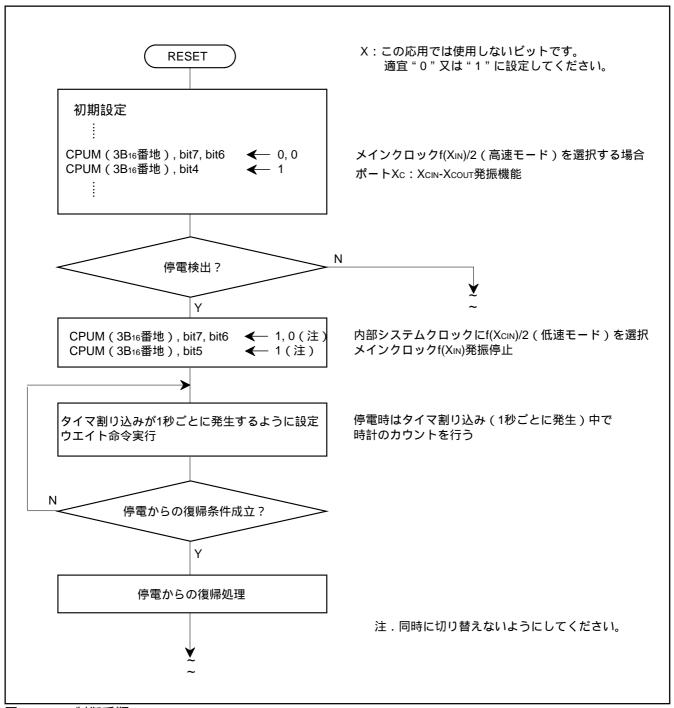

## (1) 停電時の状態遷移

ポイント:停電時にタイマ割り込みを使用して、1秒ごとに時計をカウントアップします。

図2.9.2 接続図

仕 様: 時計機能を維持しながら可能な限り消費電力を抑制。

クロック: f(XIN)=8MHz、f(XCIN)=32.768kHzを使用

ポート処理

入力ポート:外部で H "又は" L "レベルに固定

出力ポート:外部に電流が流れ出さない出力レベルに固定

(例:出カレベル"L"時に電流が流れてLEDが点灯するような回路の場合、出カレベル"H"に固定)

入出力ポート:入力ポート 外部で"H"又は"L"レベルに固定

出力ポート 電流を消費しないデータを出力

VREF端子:A-D変換動作を終了させることにより、VREF電流消費を止める。

図2.9.3に停電時の状態遷移図、図2.9.4に関連レジスタの設定を示します。

図2.9.3 停電時の状態遷移図

図2.9.4 関連レジスタの設定

#### 制御手順:

下記の順に関連レジスタを設定することによって停電に対応します。

図2.9.5 制御手順

## 2.10 スタンバイ機能

3850グループはソフトウエアでCPUの動作を停止させ、低消費電力でCPUを待機させるスタンバイ機能を持ちます。

スタンバイ機能には次の2種類があります。

STP命令によるストップモード WIT命令によるウエイトモード

## 2.10.1 関連レジスタ

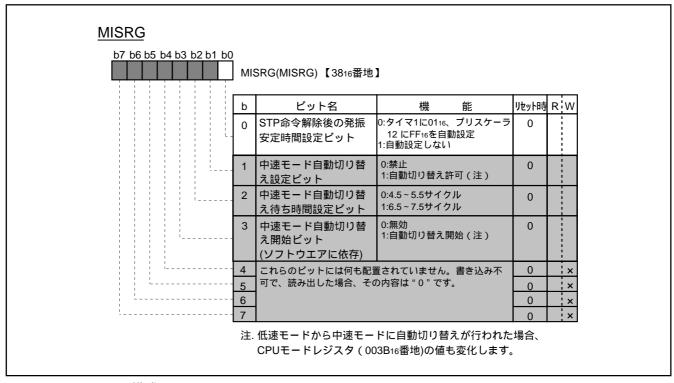

図2.10.1 MISRGの構成

## 2.10.2 ストップモード

STP命令の実行によって、ストップモードの状態になります。ストップモードではメインクロック( XIN-XOUT )、サブクロック( XCIN-XCOUT )とも発振が停止し、内部クロック $\phi$ は" H "レベルで停止します。 CPUは停止し、周辺機能の動作も停止します。その結果、消費電力の低減を実現できます。

## (1) ストップモード時の状態

ストップモード時の状態を表2.10.1に示します。

表2.10.1 ストップモード時の状態

| 項目                | ストップモード時の状態                        |

|-------------------|------------------------------------|

| 発振                | 停止                                 |

| CPU               | 停止                                 |

| 内部クロック $\phi$     | " H "レベルで停止                        |

| 入出力ポートP0~P4       | STP命令実行時の状態を保持                     |

| タイマ               | 停止( タイマ1、2、X、Y )                   |

|                   | ただし、タイマX、タイマYではイベントカウンタモードが使用できます。 |

| PWM               | 停止                                 |

| ウオッチドッグタイマ        | 停止                                 |

| シリアルI/O1、シリアルI/O2 | 停止                                 |

|                   | ただし、外部クロックモードで動作できます。              |

| A-D变换器            | 停止                                 |

### (2) ストップモードの解除

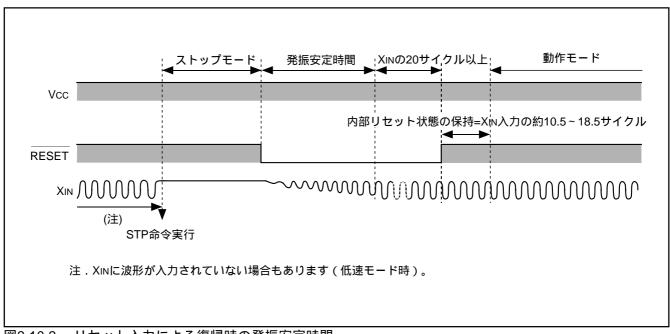

ストップモードはリセット入力、又は割り込み要求の発生によって解除されます。リセット入力を使用する場合と、割り込みを使用する場合では、ストップモードからの復帰処理が異なります。

#### リセット入力による復帰

ストップモード中にRESET端子の入力レベルを"L"にすると、ストップモードは解除されます。 すべてのポートが入力状態となり、メインクロック(XIN-XOUT)のストップモードが解除されると、 発振が開始します。

発振開始時の発振<u>は不安定</u>であり、発振が安定するまでの時間(発振安定時間)(注)が必要です。 発振が安定するまでRESET端子の入力レベルを"L"にしておく必要があります。

安定発振しているときに、RESE $\underline{T}$ 端子を $\underline{X}$ INの20サイクル以上" L"レベルに保つと内部がリセット状態になります。リセット状態はRESET端子の入力を" H"レベルに戻した後、 $\underline{X}$ IN入力の約10.5~18.5サイクル後に解除されます。

図2.10.2にリセット入力による復帰時の発振安定時間を示します。

リセット入力によるストップモードの解除では、STP命令実行前の内部RAMの内容が保持されます。ただし、CPUレジスタ、SFRの内容は保持されません。

リセットについては「2.8 リセット」を参照してください。

注. 発振安定時間の設定については、MISRG(003816番地)を参照してください。

図2.10.2 リセット入力による復帰時の発振安定時間

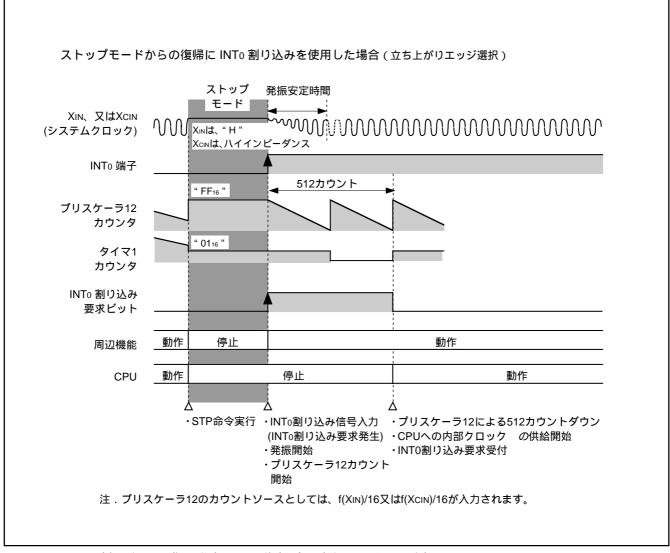

## 割り込みによる復帰

ストップモード中に割り込み要求が発生すると、ストップモードは解除され、発振が再開します。復帰に使用できる割り込み要因は、下記のとおりです。

- INTo ~ INT3

- · CNTR<sub>0</sub>, CNTR<sub>1</sub>

- ・外部クロック使用のシリアルI/O(1,2)

- ・外部クロック使用のタイマ(X,Y)

ただし、上記の割り込み要因をストップモードからの復帰に使用する場合は、<u>使用する割り込み</u>を許可するため、次の設定を行った後、STP命令を実行してください。

## 【必要なレジスタ設定】

- ①割り込み禁止フラグI="0(許可)

- ②タイマ1の割り込み許可ビット="0(禁止)

- ③復帰に用いる割り込み要因の割り込み要求ビット="0~要求なし)

- ④復帰に用いる割り込み要因の割り込み許可ビット="1(許可)

割り込みについては、「2.2割り込み」を参照してください。

発振開始時の発振は不安定であり、発振が安定するまでの時間、発振安定時間)が必要です。割り込みによる復帰時には、プリスケーラ12、タイマ1 $^*$ 1がCPUへの内部クロック $\phi$ 0供給を待機する時間を生成します $^*$ 2。この待機する時間で、システムクロック側の発振安定時間を確保します。CPUへの内部クロック $\phi$ 0供給は、タイマ1のアンダフロー時から開始されます。

図2.10.3にINTo割り込み要求の発生による復帰時の実行シーケンス例を示します。

- \*1:STP命令解除後の発振安定時間設定ビット(3816番地のビット0)が 0 のときにSTP命令を実行すると、プリスケーラ12のカウンタ/ラッチに FF16 が、タイマ1のカウンタ/ラッチに 0116 が自動的に設定されます。STP命令解除後の発振安定時間設定ビットが 1 でときは自動設定が行われませんので、STP命令実行前に発振安定時間に適した値を任意にプリスケーラ12、タイマ1に設定できます。

- \*2:発振開始直後からカウントソースはプリスケーラ12カウンタへ供給され、カウント動作が開始します。

図2.10.3 INTo割り込み要求の発生による復帰時の実行シーケンス例

#### (3) ストップモード使用上の注意事項

### レジスタ設定

ストップモードからの復帰時、プリスケーラ12、タイマ1の値は自動的に書き換えられていますので、それぞれ再設定してください。(STP命令解除後の発振安定時間設定ビットが 0 "のとき)

### 復帰後のクロック

割り込みによってストップモードから復帰すると、STP命令実行前のCPUモードレジスタの内容が保持されています。そのためSTP命令実行前にメインクロック、サブクロックとも発振させていた場合は、割り込みによってストップモードから復帰するとメインクロック、サブクロックとも発振を再開します。

上記においてメインクロック側がシステムクロックに設定されていた場合、ストップモードからの復帰時にXIN入力の約8000サイクル分の発振安定時間が確保されます。このとき、メインクロック側の発振安定時間経過後でもサブクロック側の発振は安定していないことがありますので、注意してください。

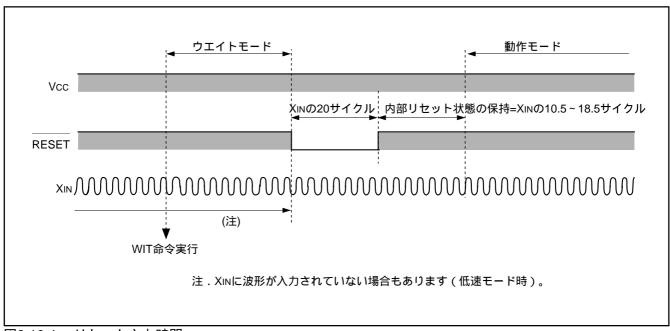

## 2.10.3 ウエイトモード

WIT命令の実行によって、ウエイトモードの状態になります。ウエイトモードでは発振は継続しますが、内部クロック $\phi$ は" H "レベルで停止します。

CPUは停止しますが、大部分の周辺機能は動作します。

## (1) ウエイトモード時の状態

周辺機能へのクロックは供給され続けています。ウエイトモード時の状態を表2.10.2に示します。

表2.10.2 ウエイトモード時の状態

| 項目                | ウエイトモード時の状態    |

|-------------------|----------------|

| 発振                | 動作             |

| CPU               | 停止             |

| 内部クロック $\phi$     | " H "レベルで停止    |

| 入出力ポートP0~P4       | WIT命令実行時の状態を保持 |

| タイマ               | 動作             |

| PWM               | 動作             |

| ウオッチドッグタイマ        | 動作             |

| シリアルI/O1、シリアルI/O2 | 動作             |

| A-D变換器            | 動作             |

### (2) ウエイトモードの解除

ウエイトモードはリセット入力、又は割り込み要求の発生によって解除されます。リセット入力を 使用する場合と、割り込みを使用する場合では、ウエイトモードからの復帰処理が異なります。

ウエイトモードでは発振は継続されていますので、ウエイトモードが解除されるとただちに命令を 実行できます。

## リセット入力による復帰

ウエイトモード中にRESET端子の入力レベルを" L "にすると、ウエイトモードは解除されます。 ウエイトモードが解除されると、すべてのポートが入力状態になり、CPUへの内部クロック $\phi$ の 供給が開始します。RESET端子をXINの20サイクル以上" L "レベルに保つと内部がリセット状態になります。リセット状態はRESET端子の入力を" H "レベルに戻した後、XIN入力の約10.5~18.5サイクル後に解除されます。

ウエイトモードの解除では、リセット前の内部RAMの内容が保持されます。ただし、CPUレジスタ、SFRの内容は保持されません。

図2.10.4にリセット入力時間を示します。

リセットについては「2.8 リセット」を参照してください。

図2.10.4 リセット入力時間

## 割り込みによる復帰

ウエイトモード中に割り込み要求が発生すると、ウエイトモードは解除され、CPUへの内部クロック $\phi$ の供給が開始します。同時に復帰に使用した割り込み要因の要求が受け付けられて、その割り込み処理ルーチンが実行されます。

ただし、割り込み要因をウエイトモードからの復帰に使用する場合は、<u>使用する割り込みを許可</u>するため、次の設定を行った後、WIT命令を実行してください。

### 【必要なレジスタ設定】

- ①割り込み禁止フラグI="0(許可)

- ②復帰に用いる割り込み要因の割り込み要求ビット="0(要求なし)

- ③復帰に用いる割り込み要因の割り込み許可ビット="1(許可)

割り込みについては、「2.2割り込み」を参照してください。

## (3) ウエイトモード使用上の注意事項

## 復帰後のクロック

WIT命令実行時にXCINをシステムクロックとして設定し、XINの発振を停止させていた場合に、リセットによってウエイトモードから復帰すると、XCINの発振が停止し、XINが発振を開始し、XINがシステムクロックになります。

上記においてXINの発振が安定するまで、RESET端子に"L"レベルを入力しておく必要があります。

## 2.11 フラッシュメモリモード

本節ではフラッシュメモリに関するレジスタの設定方法、注意事項などを説明します。

### 2.11.1 概要

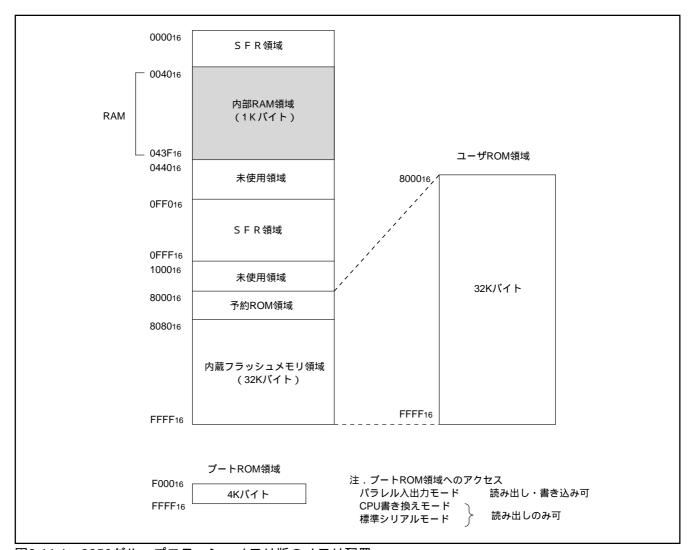

フラッシュメモリ版は、フラッシュメモリを内蔵していることを除いて、マスクROM版と同じ機能を持ちます。ただし、SFR領域の一部がマスクROM版と異なります(「2.11.2メモリ配置」参照)。

フラッシュメモリ版では、パラレル入出力モード、標準シリアル入出力モード、及びCPU書き換えモードの3つの書き換えモードで内蔵フラッシュメモリを操作できます。

#### 2.11.2 メモリ配置

M38507F8FP/SPは32Kバイトのフラッシュメモリを内蔵しています。 図2.11.1にフラッシュメモリ版のメモリ配置を示します。

図2.11.1 3850グループフラッシュメモリ版のメモリ配置

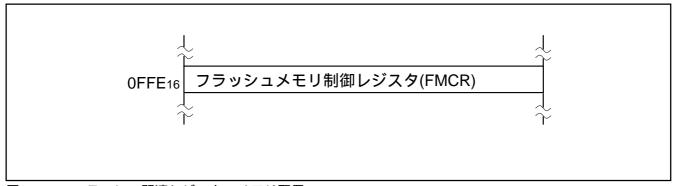

## 2.11.3 関連レジスタ

図2.11.2 フラッシュ関連レジスタのメモリ配置

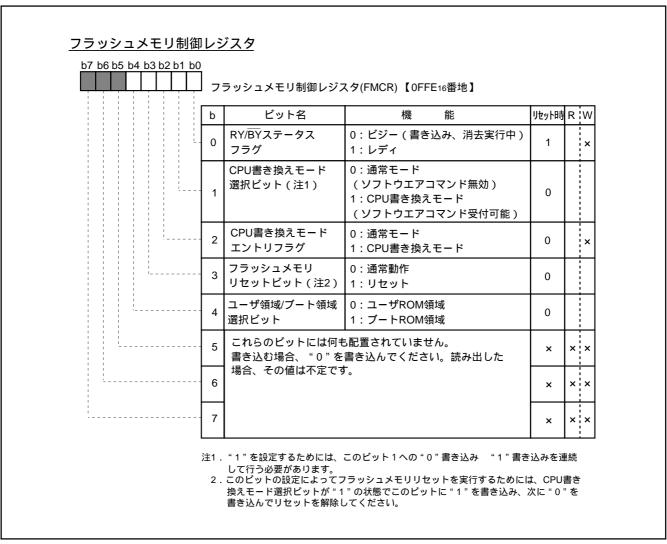

図2.11.3 フラッシュメモリ制御レジスタの構成

#### 2.11.4 パラレル入出力モード

パラレル入出力モードは、プログラマ(EFP-)を使用することによって、内蔵フラッシュメモリ領域へのプログラム/イレーズを行うことができます。プログラム/イレーズのメモリ領域は、ブートROM領域:  $0F00016 \sim 0FFFF16$ 番地、ユーザROM領域:  $0800016 \sim 0FFFF16$ 番地となります。特にイレーズを行うときにメモリ領域の設定を間違えると、製品の永久的なダメージにつながりますので注意が必要です。

表2.11.1にパラレル入出力モードでプログラムを行う場合のプログラマの設定を示します。

・EFP-I:(株)彗星電子システム社製

表2.11.1 パラレル書き込み時のプログラマ設定

| 品種名        | パラレルユニット    | ブートROM領域          | ユーザROM領域          |  |

|------------|-------------|-------------------|-------------------|--|

| M38507F8FP | EF3850F-42E | 0E00016 ~ 0EEE16  | 0800016 ~ 0FFFF16 |  |

| M38507F8SP | EF3850F-42S | 01 00010 01 11 10 | 0000010 0111110   |  |

## 2.11.5 標準シリアル入出力モード

シリアル入出力モードで書き込みを行う場合の、プログラマ(EFP- ; 別途シリアルユニット EF1SRP-01Uが必要)とマイコンの端子接続例(4線式)について表2.11.2に示します。

・EFP- : (株)彗星電子システム社製

表2.11.2 シリアル書き込み時のプログラマとの接続例(4線式)

| 1416 AJ-            | EFP- (E    | F1SRP-01U)                 | 3850グループフラッシュマイコン |       |  |

|---------------------|------------|----------------------------|-------------------|-------|--|

| 機能                  | 信号名        | EF1RP-01U側<br>コネクタ PIN No. | 端子名               | ピン番号  |  |

| 転送クロック入力            | T_SCLK1    | 9                          | P26/SCLK1         | 10    |  |

| シリアルデータ入力           | T_RXD      | 11                         | P25/TxD           | 11    |  |

| シリアルデータ出力           | T_TXD      | 10                         | P24/RxD           | 12    |  |

| 送受信許可出力             | T_BUSY     | 12                         | P27/CNTR0/SRDY1   | 9     |  |

| 5V入力                | T_VPP      | 3                          | CNVss             | 15    |  |

| リセット入力              | T_RESET    | 14                         | RESET (注1)        | 18    |  |

| ターゲットボード<br>電源モニタ入力 | T_VDD (注2) | 4                          | Vcc (注2)          | 1     |  |

| GND                 | GND (注3)   | 1,2,15,16                  | Vss, AVss (注3)    | 21, 3 |  |

- 注1. 書き込みベリファイ後のリセット解除は行われないため、書き込み後、MCUを動作させるときは、ターゲット接続ケーブルを切り離してください。

- 2. EFP-I側で使用する出力バッファの電源電圧を、ユーザ側電源電圧(Vcc)と合わせるために、Vccをユーザ側から供給してください。

- 3. GND信号にはEF1SRP-01U側コネクタの1、2、15、16番の4端子を用意しています。ターゲット基板に接続する場合、1端子のみの接続でも問題はありませんが、2端子以上で接続することを推奨します。

### 2.11.6 CPU書き換えモード

CPU書き換えモードでは、中央演算処理装置(CPU)がソフトウエアコマンドを実行することにより、内蔵フラッシュメモリ領域を書き換えることができます。したがってROMライタなどを使用せずに、マイクロコンピュータを基板に実装した状態で、内蔵フラッシュメモリ領域の内容を書き換えることができます。

書き換えプログラムは、あらかじめ内蔵フラッシュメモリ領域に書き込んでください。ただし、CPU書き換えモードでは、内蔵フラッシュメモリからの読み出しができません。したがって、書き換え制御プログラムは、内蔵フラッシュメモリ以外の領域(内部RAM領域など)に転送した後、その領域上で実行してください。

CPU書き換えモードでは、リードアレイコマンド、リードステータスレジスタコマンド、クリアステータスレジスタコマンド、プログラムコマンド、イレーズ全ブロックコマンド、ブロックイレーズコマンドが使用できます。各コマンドの詳細については「1章 フラッシュメモリモード(CPU書き換えモード)」を参照してください。

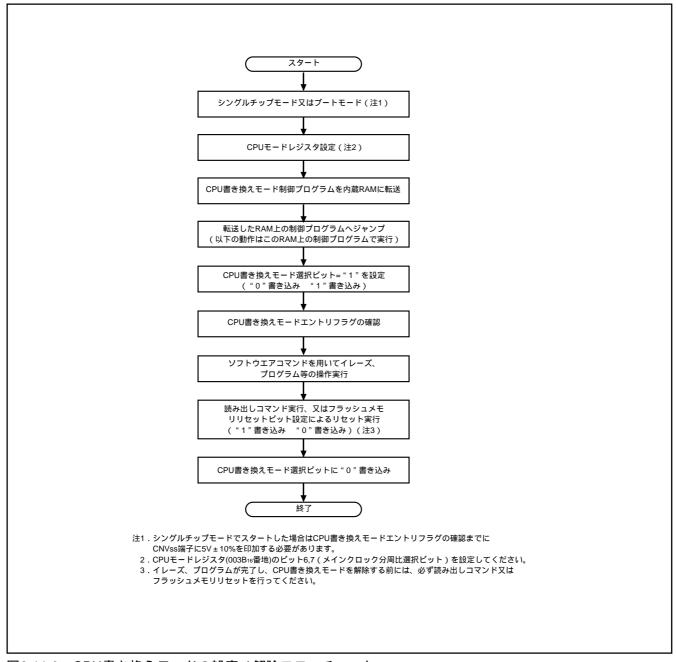

## (1) CPU書き換えモード設定/解除方法

内蔵フラッシュメモリの書き換えモードでの操作手順を示します。 制御例については「2.11.7 (2)CPU書き換えモード時の制御例」を参照してください。

#### <開始手順>

CNVss/Vpp端子に5V±10%を印加する。(ブートROM領域へエントリの場合)

リセットを解除する。

CPUモードレジスタのビット6,7(メインクロック分周比選択ビット)を設定する。

CPU書き換えモード制御プログラムを内蔵RAMに転送した後、RAM上のこの制御プログラムへジャンプする(この制御プログラムで、以下の動作を制御してください)。

CNVss/Vpp端子に5V±10%を印加する。(シングルチップモードの場合)

CPU書き換えモード選択ビット(0FFE16番地のビット1)に"1"を設定する。

このビットに"1"を設定するには"0"書き込み、"1"書き込みを連続して行う必要があります。

CPU書き換えモードエントリフラグ( 0FFE16番地のビット2 )を読み出し、CPU書き換えモードが " 1 "になっていることを確認する。

ソフトウエアコマンドを用いて、フラッシュメモリの操作を実施する。

注. これ以外に、フラッシュメモリに書き込むデータを外部(例えばシリアルI/O)から入力する ための制御、ポート等の初期設定、ウオッチドッグタイマへの書き込み等が必要です。

## <解除手順>

読み出しコマンドを実行又は、フラッシュメモリリセットビット( 0FFE16番地のビット3 )設定によるセットを実行する。

CPU書き換えモード選択ビット(OFFE16番地のビット1)を"O"に設定する。

また、CPU書き換えモード中に割り込みが発生しないように、CPU書き換えモードを選択する前に、以下の処理を実施してください。

・割り込み禁止フラグ(I) = " 1 "にする。

既にウオッチドッグタイマが起動している場合は、CPU書き換えモード中、ウオッチドッグタイマ制御レジスタ(39個番地)には定期的に書き込みを行い、ウオッチドッグタイマHのアンダフローによるリセットが発生しないようにしてください。

なお、プログラム又はイレーズ中は、ウオッチドッグタイマは自動的にクリアされるため、アンダフローによる内部リセットは発生しません。

CPU書き換えモード時に、割り込み及びリセットが発生した場合は、以下のようになります。

- ・割り込み:プログラムが暴走します。割り込みベクトル領域のあるフラッシュメモリの読み出しができないためです。

- ・ウオッチドッグタイマHアンダフロー、リセット

: 内蔵フラッシュメモリ制御回路、及びフラッシュメモリ制御レジスタがリセットされ、マイクロコンピュータがリセットされます。リセット解除時、CNVss="H"の場合はブートモードで起動されます。

また、プログラム/イレーズ中に上記割り込み及びリセットが発生した場合、フラッシュメモリの書き換えが完了していないため、リセット解除後も正常に動作しないデータになっている可能性が高く、注意が必要です。この場合には、パラレルモード又はシリアルモードでフラッシュメモリを再度正しくプログラムしてください。

## 2.11.7 フラッシュメモリモードの応用例

シリアル入出力モード使用時のシステム基板上での制御端子処理例、及びCPU書き換えモード時の制御例について示します。

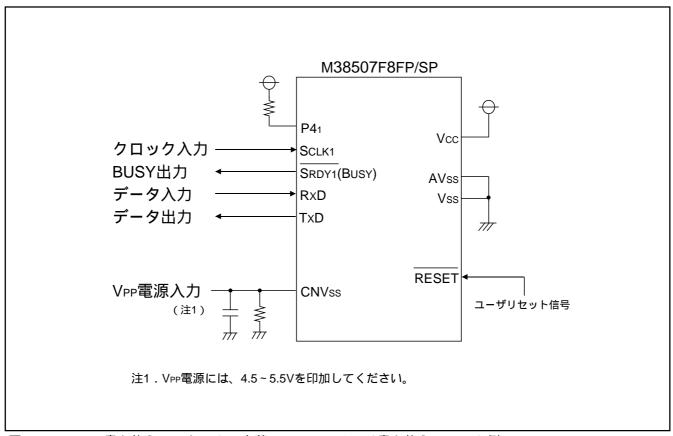

## (1) シリアル入出力モード使用時のシステム基板上での制御端子処理例

図2.11.4に示すように、シリアル入出力モードでは、マイクロコンピュータを基板に実装した状態で、内蔵フラッシュメモリの内容を書き換えることができます。シリアル入出力モード時、制御端子となるP24/RxD、P25/TxD、P26/SCLK1、P27/SRDY1、P41、CNVss、及びRESET端子の処理例を以下に示します。

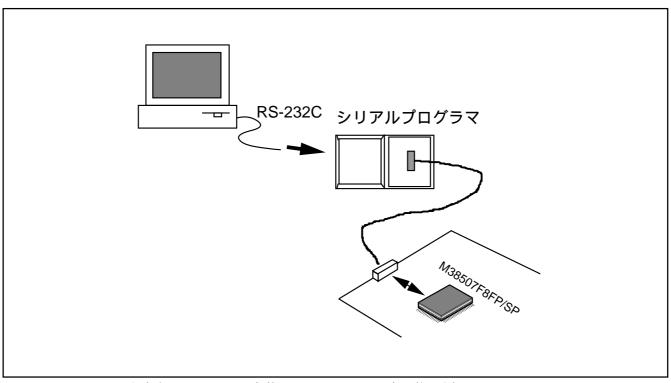

図2.11.4 シリアル入出力モードによる内蔵フラッシュメモリ書き換え例

## 制御信号がユーザシステム回路に影響しない場合

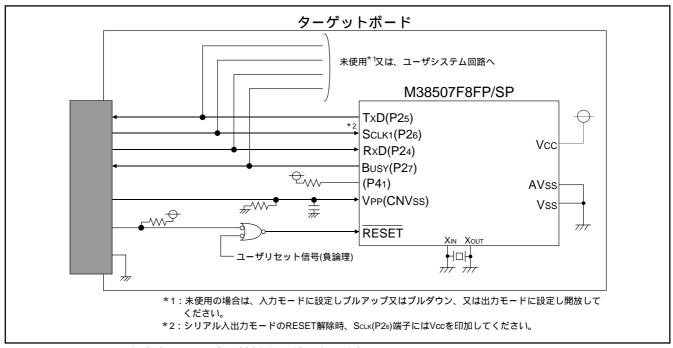

シリアル入出力モード時の制御信号が、ユーザシステム回路で使用されていない、あるいはユーザシステム回路に影響しない場合は、図2.11.5に示すように結線できます。

図2.11.5 シリアル入出力モード時の基板上の端子処理例(1)

## 制御信号がユーザシステム回路に影響する場合

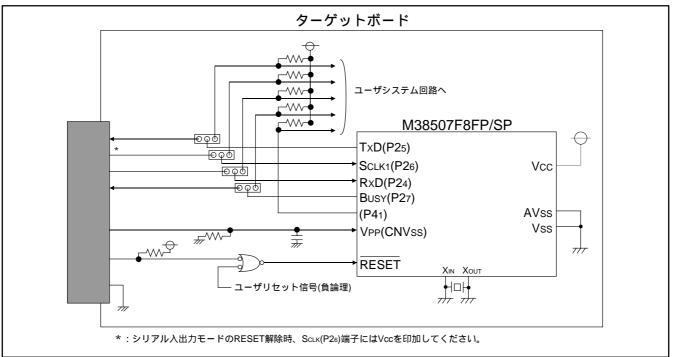

図2.11.6はシリアル入出力モード時、ジャンパスイッチによりユーザシステム回路へ供給される制御信号を遮断する例です。

図2.11.6 シリアル入出力モード時の基板上の端子処理例(2)

## 制御信号がユーザシステム回路に影響する場合

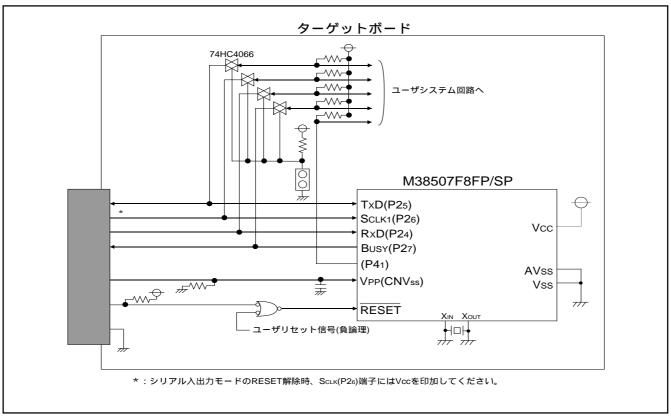

図2.11.7はシリアル入出力モード時、アナログスイッチ(74HC4066)によりユーザシステム回路へ供給される制御信号を遮断する例です。

図2.11.7 シリアル入出力モード時の基板上の端子処理例(3)

## (2) CPU書き換えモード時の制御例

この例では、シリアルI/Oを用いてデータを受信し、そのデータをCPU書き換えモードで内蔵フラッシュメモリへ書き込みます。

図2.11.8にCPU書き換えモードによる内蔵フラッシュメモリ書き換えシステム例、図2.11.9にCPU 書き換えモードの設定 / 解除のフローチャートを示します。

図2.11.8 CPU書き換えモードによる内蔵フラッシュメモリ書き換えシステム例

図2.11.9 CPU書き換えモードの設定/解除フローチャート

## 2.11.8 CPU書き換えモードに関する注意事項

## (1) 動作速度

CPU書き換えモード中は、メインクロック分周比選択ビット(003B16番地のビット6,7)によって、内部クロックが4.0MHz以下になるように設定してください。

## (2) 使用禁止命令

CPU書き換えモード中、フラッシュメモリ内部のデータを参照する命令は使用できません。

## (3) 割り込み

CPU書き換えモード中、割り込みはフラッシュメモリ内部のデータを参照するため使用できません。

## (4) ウオッチドッグタイマ

すでにウオッチドッグタイマが起動されている場合は、プログラム又はイレーズ中、ウオッチドッグタイマは常にクリアされるので、アンダフローによる内部リセットは発生しません。

## (5) リセット

常に受け付けます。リセット解除時、CNVss=Hの場合、ブートモードで起動されるので、ブートROM領域のFFFC16、FFFD16番地に格納されたアドレスからプログラムがスタートします。

# 3. 参考プログラム例

参考プログラムは、ルネサステクノロジホームページから入手してください。 3850グループのページの画面左メニュー「アプリケーションノート」をクリックしてください。

## 4. 参考ドキュメント

データシート 3850グループ(A仕様)データシート 最新版をルネサス テクノロジホームページから入手してください。

テクニカルニュース / テクニカルアップデート 最新の情報をルネサス テクノロジホームページから入手してください。

## 5. ホームページとサポート窓口

ルネサス テクノロジホームページ http://japan.renesas.com/

ルネサス製品全般に関するお問合せ先 カスタマ・サポート・センター:csc@renesas.com

# 改訂記録

|      |            | 改訂内容 |                                   |

|------|------------|------|-----------------------------------|

| Rev. | 発行日        | ページ  | ポイント                              |

| 1.00 | 2005.11.14 | -    | 3850グループ(A仕様) ユーザーズマニュアル Rev.1.00 |

|      |            |      | 「第2章 応用」をアプリケーションノートに様式変更して発行     |

|      |            | 30   | 図2.3.14 制御手順を一部変更                 |

|      |            | 52   | 図2.4.20 送信側関連レジスタの設定を一部変更         |

|      |            | 54   | 図2.4.22 送信側の制御手順を一部変更             |

|      |            | 58   | 図2.4.28 シリアルI/O 制御手順を一部変更         |

|      |            | 60   | 図2.4.31 シリアルI/O2制御手順を一部変更         |

|      |            | 61   | 仕様、仕様の制限事項を変更                     |

|      |            | 62   | 図2.4.33 タイミング図を変更                 |

|      |            |      | 図2.4.34 関連レジスタの設定を一部変更            |

|      |            | 63   | マスタ側の制御を変更                        |

|      |            |      | 図2.4.35 マスタ側の制御手順を一部変更            |

|      |            | 64   | スレーブ側の制御を一部変更                     |

|      |            |      | 図2.4.36 スレーブ側の制御手順を変更             |

|      |            | 69   | 図2.4.41 送信側の制御手順を一部変更             |

|      |            | 70   | 図2.4.42 受信側の制御手順を一部変更             |

|      |            | 88   | 図2.7.6 制御手順を一部変更                  |

## 安全設計に関するお願い •

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

## 本資料ご利用に際しての留意事項

- 1. 本資料は、お客様が用途に応じた適切なルネサス テクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサス テクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ(http://www.renesas.com)などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起 因する損害がお客様に生じた場合には、ルネサステクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサステクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに 用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、 移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途 へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサステクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。