# IDT BUS SWITCH CHARACTERISTICS AND APPLICATIONS

#### By Anupama Hegde

# INTRODUCTION

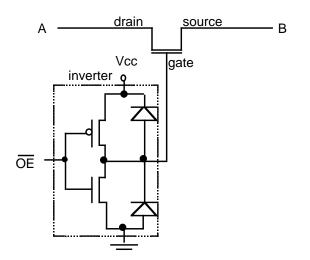

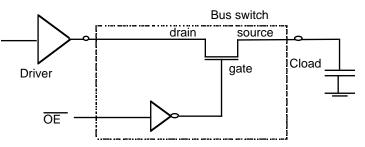

IDT Bus switch devices provide a "zero-delay" isolation mechanism in digital systems. The Bus switch consists of an NMOS transistor with a low on-resistance and low off-state capacitance. Bus switch products are built on IDT's halfmicron CMOS n-well process technology. Much of the delay in a discrete logic buffer comes from the input translator and output buffer circuitry. The Bus switch eliminates these stages altogether, reducing the delay through the device to under a nanosecond. Figure 1 shows a Bus switch device used to connect or isolate two ports.

# TABLE OF CONTENTS

| INTRODUCTION                |    |

|-----------------------------|----|

| TABLE OF CONTENTS           |    |

| BUS SWITCH OPERATION        |    |

| IDT "FST" BUS SWITCH FAMILY |    |

| Precharge                   |    |

| BUS SWITCH APPLICATIONS     |    |

| Bus Isolation               |    |

| Live Insertion              |    |

| Mixed Voltage Operation     |    |

| Zero-Delay Multiplexing     | 40 |

| Memory Applications         |    |

| Analog Switching            |    |

| SUMMARY                     | 41 |

|                             |    |

# **BUS SWITCH OPERATION**

The Bus switch device consists of an enhancement-mode NFET which is turned on when its gate is adequately forward biased. Figure 1 shows a negative-asserted output enable where a logic LOW on  $\overline{OE}$  connects the gate to Vcc.

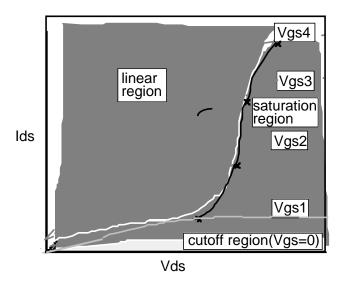

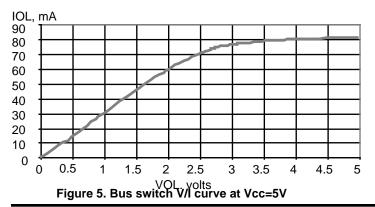

When Vgs is less than the transistor threshold voltage,  $V_{Th}$ , the transistor is off and in the "cutoff" region. When Vgs exceeds  $V_{Th}$  the transistor operates in one of the other two regions. The NFET has three regions of operation as shown in Figure 2 - linear, saturation and cutoff. While on, the transistor operates in the linear region and is resistive

if Vds < Vgs -  $V_{Th}$

to

With the gate voltage at 5V and  $V_{Th}\cong 1V,$  this translates

Vin - Vout < 5V - Vout - 1V or Vin < 4V

Figure 1. Bus switch

Conversely, the transistor is in the saturation region when  $Vin \ge 4V$

In the saturation region, the transistor behaves like a current source and the output voltage is no longer dependent on the input voltage but only on the gate voltage and the load.

Figure 2. Bus switch NMOSFET characteristics

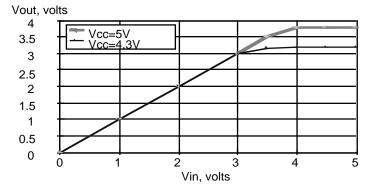

#### Figure 3. Vout vs Vin

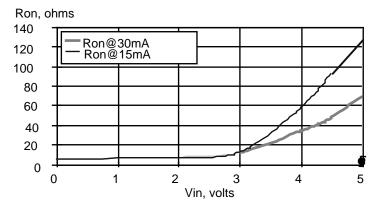

Thus for Vin values upto approximately 4V, Vout follows Vin. Beyond this voltage, Vout is held at approximately one threshold voltage( $V_{Th}$ ) below the gate voltage by the load capacitance. The "on-resistance" ( $R_{on}$ ) of the NFET is dependent on the gate-source bias voltage and so  $R_{on}$  is a function of Vcc, Vin and Vout voltages as can be seen in Figures 3 and 4. For a gate-source bias under 1V, the NFET resistance begins to increase and the switch begins to turn off as seen in the figures.

At an input voltage of 0V, the typical on-resistance of the FST3xxx switch is 50hms.

## 4. Ron vs Vin at Vcc=5V

When  $\overline{OE}$  is HIGH, the gate voltage is zero and the switch is off. Figure 6 shows a model of a Bus switch device separating a driver and a load. While operating in the linear region, Bus switch devices provide no drive but are capable of passing specified CMOS/TTL levels.

In the datasheets, R<sub>on</sub> is specified at specific static current levels unlikely to be exceeded in typical systems.

When the switch is off, input and output ports are isolated and the only leakage paths are to ground rather than between ports. The switch presents a load capacitance of 6 to 8pF in the OFF state. When the switch is on, the delay through the device is very small and is a function of the RC ( $R_{on}$  x Cload) time constant.

Figure 6. Bus switch load model

Like other IDT CMOS families, IDT Bus switch products have extremely low power dissipation. Static power dissipation is close to zero. Dynamic power dissipation is primarily dependent on the number of switches toggling and is under  $30\mu$ A/MHz per switch. For example, the FST3384 has 10 switches, thus its total dynamic power dissipation is  $300\mu$ A/MHz.

# IDT "FST" BUS SWITCH FAMILY

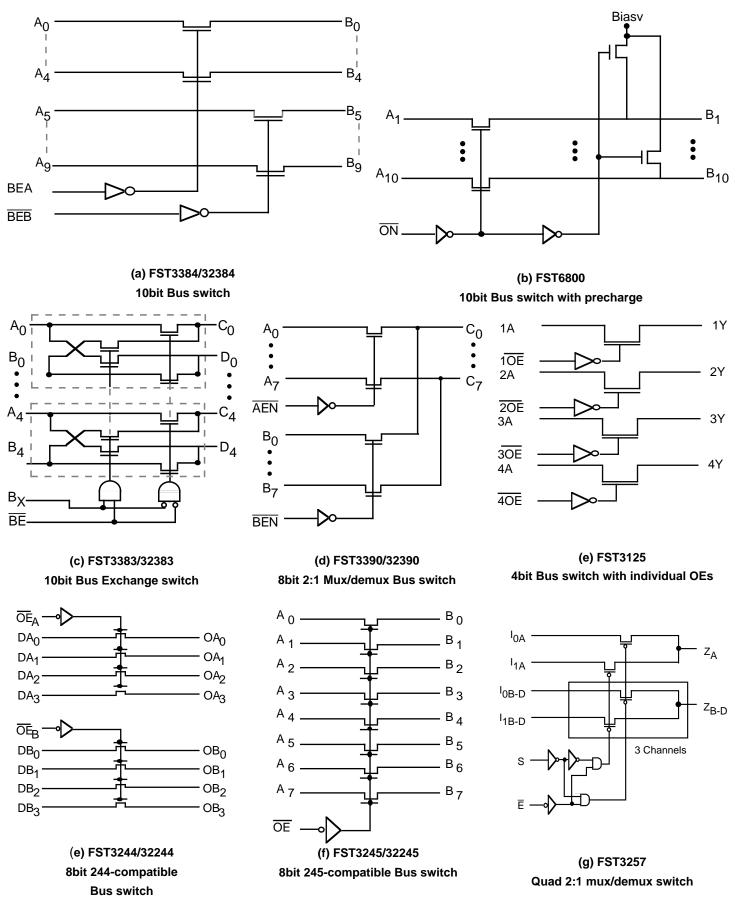

IDT has a family of Bus switch products. In addition to the various function types available, two versions of the IDT octal Bus switch family exist. The FST3xxx Bus switches have a typical on-resistance of 5ohms at an input voltage of 0 volts. IDT offers a second version of the Bus switch family with an integrated series resistor. This integrated resistance is equally distributed on the source and drain sides of NFET switch. The typical on-resistance of the FST32xxx Bus switch is 28ohms at the same input voltage of 0V. Due to its higher Ron value, the propagation delay through the FST32xxx family is higher than FST3xxx devices. Figure 7 shows block diagrams of the various IDT Bus switch functions.

#### Precharge

The FST6800 supports "precharge" on the outputs. Figure 7(b) shows the precharge circuit configuration which consists of an NMOS transistor connected between the output port and Vbias. When the Bus switch is off, the precharge transistor drives the tristated B port to the bias voltage, Vbias, through the equivalent of 10Kohm. Certain system software requirements include specific default logic states at powerup or when the bus is in high impedance. Precharge is useful in this type of application.

Figure 7. IDT FST Octal Bus switch Family

# **BUS SWITCH APPLICATIONS**

## **Bus Isolation**

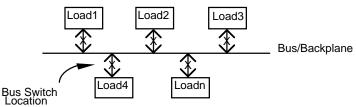

The small delay through the Bus switch makes it suitable for a number of different applications. In particular, providing "zero delay" bus isolation paths as shown in Figure 9 can be useful.

#### Figure 9. "Zero-delay" Bus isolation

The Bus switch FST3245 is pin-compatible with the 245 buffer; in applications that do not require any drive, the FST3245 replaces the 245 buffer. The Bus switch isolates heavy bus loads that slow down the performance of the bus.

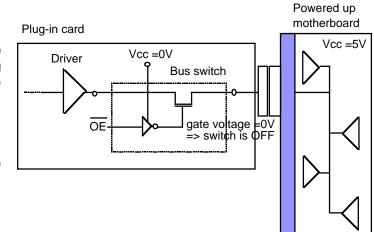

# **Live Insertion**

The Bus switch is useful in live insertion and hot-plug applications. Due to its construction, the Bus switch device meets the key requirement for live insertion. There are no diodes to Vcc at the input, output or I/O ports on a Bus switch device (devices with precharge are an exception here). Thus the device can be attached to a live bus when powered down and will neither clamp an active bus nor incur any damage itself. The added advantage of using a Bus switch in this application is that the switch is normally off. So until OE is driven low the switch is off and the two ports that the Bus switch connects will be isolated. Applications that require hot insertion must ensure that the card or module being plugged in is supplied with ground first. Most applications ensure this by maintaining a longer ground connector than Vcc and other connectors. This prevents the damage done due to short circuit paths to ground forming on other pins. Figure 10 illustrates this application. Live insertion capability is useful in docking station applications for portable computers and also in portable computers and Cardbus applications. Many telecom and Server applications also need hot-plug capability and a layer of Bus switch devices on the hot pluggable module or card interface allows live insertion with no delay premium.

# Figure 10. Live Insertion application

In many instances  $\overline{OE}$  is tied to Vcc through a pull-up resistor. Thus the Vcc (supply to the Bus switch) ramp-up may be significantly faster than the  $\overline{OE}$  ramp-up and the Bus switch may be enabled during the ramp-up. In order to prevent this, the  $\overline{OE}$  ramp should track the Vcc ramp within approximately 1V.

# **Mixed Voltage Operation**

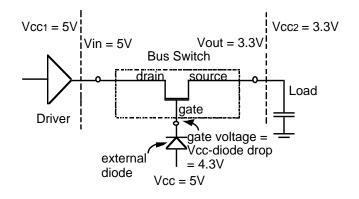

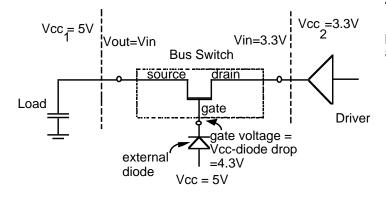

The Bus switch is sometimes used to provide a solution for mixed voltage systems. To interface 5V and 3.3V buses, an external diode is placed in series with the 5V power supply as shown in Figure 11. Figure 11(a) shows the case where the 5V device drives the 3.3V load and figure 11(b) shows the case where the 3.3V device drives the 5V load. The external diode drops the NFET gate voltage to 4.3V.

Driving from 5V to 3.3V Figure 11(a). 5V/3.3V mixed voltage operation

#### Driving from 3.3V to 5V

#### Figure 11(b). 5V/3.3V mixed voltage operation

In figure 11(a), the Bus switch limits voltage on the output to,

(Vcc - diode drop) - V<sub>Th</sub>

Assuming an external diode drop of 0.7V and a Vgs (V<sub>th</sub>) drop of 1V, the output voltage on a logic HIGH can thus be limited to 3.3V.

Figure 11(b) illustrates the reverse situation where the 3.3V bus drives a 5V load. In this case, the NFET operates in its linear region and the output voltage follows the input voltage.

Thus this arrangement can be used in mixed voltage environments for voltage translation.

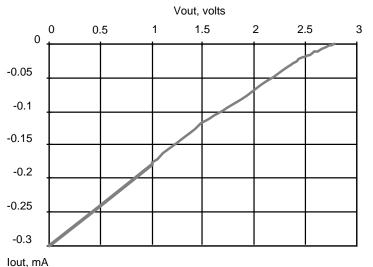

# Figure 12. Bus switch Logic HIGH V/I curve at Vcc=4.3V and Vin=3.3V

Bus switch devices are intended for 5V operation. At lower voltages, the devices would not be capable of meeting TTL input threshold levels. For example with a supply voltage of 3V, the switch would be in the cutoff region for most valid logic HIGH levels. Consequently, the output voltage would be Vcc- $V_{Th} \cong 2V$ , which provides no margin for a TTL logic HIGH threshold.

# Zero-delay multiplexing

The Bus switch works well in multiplexing applications. It provides the address and data multiplexing function without adding any delay to critical paths.

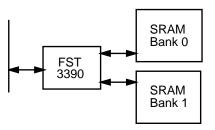

## Figure 13. Bus switch in memory applications

The Bus switch can be used in memory interleaving applications as shown in Figure 13.

# Memory applications

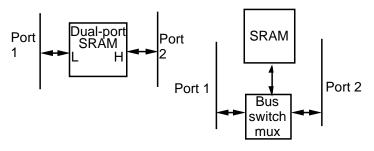

# Figure 14. Dual port versus shared memory using Bus switch

Bus switch parts can be used as an inexpensive way of building multiport memories. Used in conjunction with regular SRAMs Bus switches provide shared multiple access to the same SRAM port. Figure 14 compares the use of a dual port RAM with an implementation using ordinary SRAM and Bus switch devices.

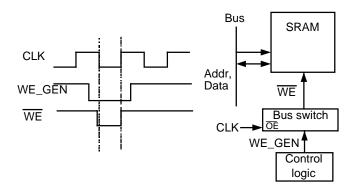

## Figure 15. Bus switch for memory WE generation

Although it may not offer true simultaneous access, the Bus switch offers an inexpensive alternative to the dual port or multiport RAM by trading off some performance for cost. Deeper, wider SRAMs are more easily available than corresponding multiport memory thus this approach offers some advantage.

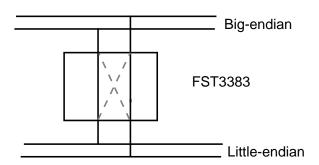

#### Figure 16. Bus switch for Byte Swapping applications

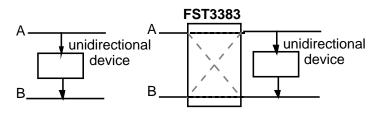

Bus switches can also be used to generate the WE (write enable) pulse in SRAM applications as shown in Figure 15. The "zero" delay of the Bus switch is useful in synchronizing the WE pulse to the system clock. The FST3383 Bus switch is also useful in swapping bytes between big-endian and littleendian buses as Figure 16 indicates. Another application where the 3383 function is used is shown in Figure 17; Where the bus exchange feature adapts a unidirectional device to bidirectional applications.

Figure 17. Bus switch used to convert unidirectional designs

# Analog switching

Low impedance silicon switches have long been used in analog switching applications such as video graphics. Key requirements in this type of application include low on-resistance, flat  $R_{on}$  characteristics over frequency and Vin, low crosstalk and off-isolation characteristics. Bus switch parts have lower on-resistance than traditional analog switches, so they have some advantage in this area. The ability to use Bus switch parts for switching differential signals is limited. The absolute maximum ratings for the device preempt usage in this type of application and the datasheets can be referenced to determine if the voltage required by the application is compatible with the device specifications.

# SUMMARY

As is evident from the above sections, Bus switch products have a range of different applications in designs today. This application note provides information on the characteristics of IDT Bus switch products. For current information on products mentioned here, designers are referred to the latest IDT logic databook.

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.