Author: Volodymyr Batig Date: February 19, 2014

## Introduction

A D Flip-Flop (DFF) with nRESET or nSET captures the value of the D-input, usually at the rising edge of the clock (CK) input. That captured value becomes the Q output. At other times, the output Q does not change. The nRESET or nSET input is used for resetting the device to its initial state. Both nRESET / nSET input types are active LOW, but nRESET initializes Q output to LOW, while nSET initializes Q HIGH. If a DFF cell had no nRESET / nSET inputs available, this design example shows how to add them.

# D Flip-Flop with nRESET circuit design

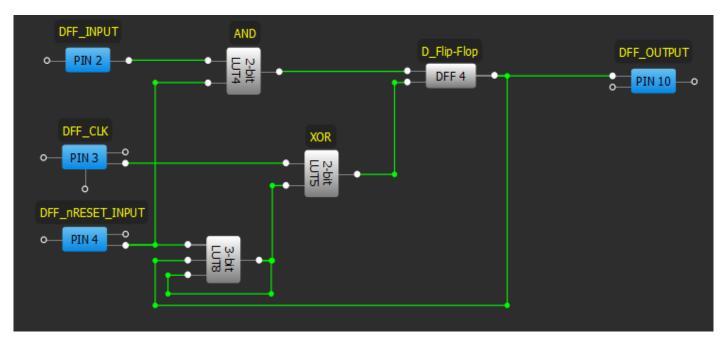

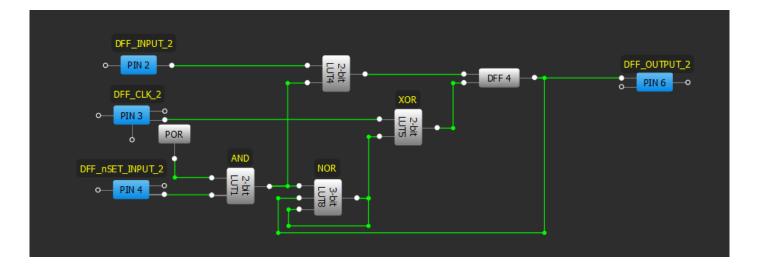

As shown in Figure 1, DFF nRESET function is implemented using 2-bit LUT4 (AND gate), 3-bit LUT8 and 2-bit LUT5. DFF\_INPUT (PIN2) is connected to IN1 of 2-bit LUT4, DFF\_CLK (PIN3) to IN1 of 2-bit LUT5 and DFF\_nRESET\_INPUT (PIN4) to IN2 of 3-bit LUT8. Also DFF4 has a feedback from its output to IN2 of 3-bit LUT8.

# D Flip-Flop with nRESET circuit analysis

Only when DFF\_INPUT (PIN2) and DFF\_nRESET\_INPUT (PIN4) are HIGH, 2-bit LUT4 (AND gate) produces a HIGH signal on its output connected to data input of DFF4 cell. After DFF\_CLK (PIN3) goes HIGH, 2-bit LUT5 (XOR gate) will produce a HIGH level signal and switch DFF4 output to a HIGH state.

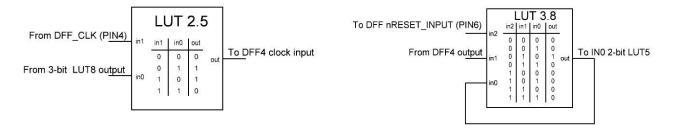

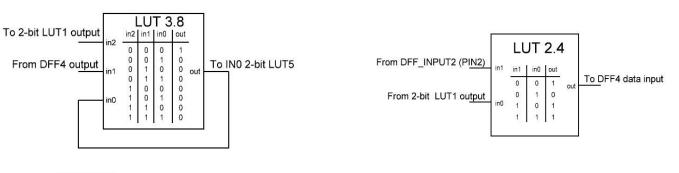

When DFF\_nRESET \_INPUT (PIN4) goes LOW, output of 2-bit LUT4 (AND gate) also will go LOW. Meanwhile, 3-bit LUT8, due to feedback from its output to IN0 will form an oscillator. It will send pulses to IN0 of 2-bit LUT5 which in turn will clock the CK input of DFF4 until its output goes LOW. See truth table of 3-bit LUT8 in Figure 3.

Figure 1. DFF with nRESET circuit design

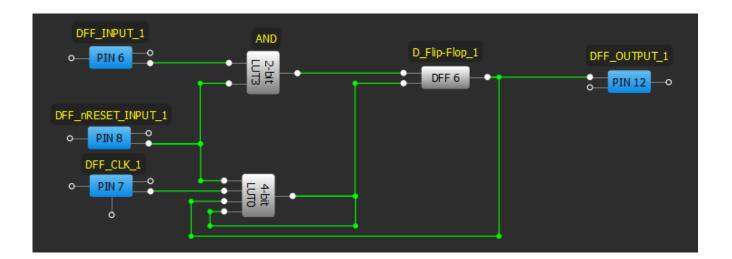

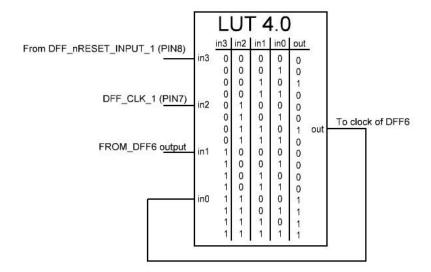

The nRESET DFF circuit can be simplified if 2-bit LUT5 and 3-bit LUT8 are replaced with their logic equivalent using 4-bit LUT0. See Figure 4. The only difference is that the truth table of 4-bit LUT0 will combine both 2-bit LUT5 and 3-bit LUT8 truth tables. See 4-bit LUT0 truth table in Figure 5.

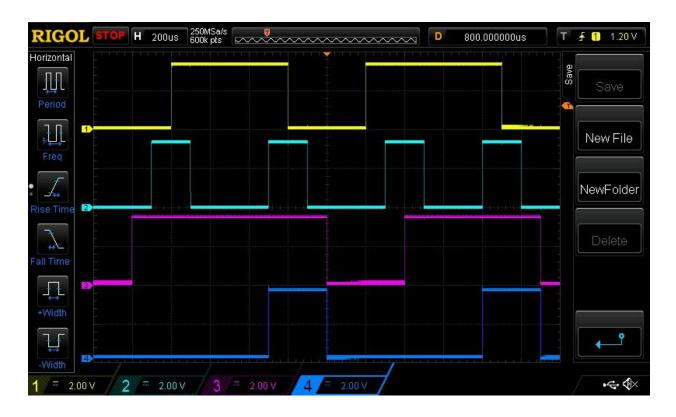

Functionality waveforms of this nRESET DFF circuit created in GreenPAK3 Designer software are shown in Figure 6.

Channel 1 (yellow/top line) – PIN2 (DFF\_INPUT), Channel 2 (light blue/2<sup>nd</sup> line) – PIN3 (DFF\_CLK), Channel 3 (magenta/3<sup>rd</sup> line) – PIN4 (DFF\_nRESET\_INPUT)

Channel 4 (blue/4<sup>th</sup> line) – PIN10 (DFF\_OUTPUT).

To create an nSET operation a simple change is needed, see Figure 7.

Figure 2. 2-bit LUT5 truth table

Figure 3. 3-bit LUT8 truth table

## GreenPAK Macro Circuit Design: Adding nSET/ nRESET to DFF's

Figure 7. D Flip-Flop with nSET Function Circuit Design

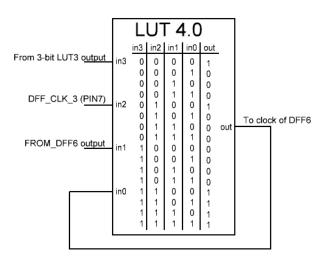

As shown in Figure 7, a 2-bit LUT1 (AND gate) is added. On chip power up, before POR output goes HIGH, 2-bit LUT1 output will be LOW. This initiates an oscillator from 3-bit LUT8 (truth table in Figure 8) which will run until the DFF4 output goes HIGH.

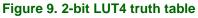

Also, a LOW state from 2-bit LUT1 will propagate to IN0 of 2-bit LUT4 and set its output HIGH (truth table in Figure 9). Thus, the DFF with nSET will initialize HIGH.

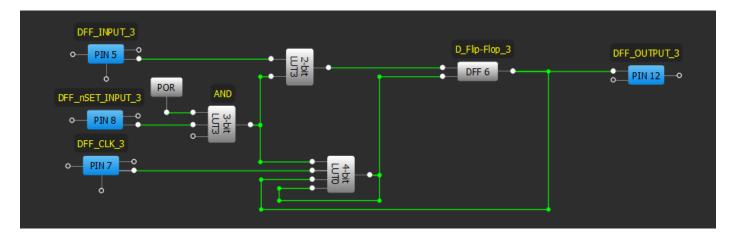

Figure 10. Digital nSET D Flip-Flop Trigger circuit design simplified

As in the nRESET circuit, this design also could be simplified by replacing 2-bit and 3-bit LUTs with 4-bit LUT0. See Figure 10.

In the simplified version of the design, NOR and XOR functions are combined in 4-bit LUT0. See Figure 7 and truth table in Figure 11.

Channel 1 (yellow/top line) – PIN2 (DFF\_INPUT\_2), Channel 2 (light blue/2nd line) – PIN3 (DFF\_CLK\_2), Channel 3 (magenta/3rd line) – PIN4 (DFF\_nSET\_INPUT\_2) and

Channel4 (blue/4th line) – PIN10 (DFF\_OUTPUT\_2).

Functionality waveforms of DFF with nSET is shown in Figure 12. Where:

Figure 11. 4-bit LUT0 truth table

Figure 12. D Flip-Flop with nSET Functionality Waveform

## Conclusion

nRESET / nSET DFF function can be very useful in the design of data processing and latching systems. The absence of the nSET/nRESET function of a DFF can be resolved by adding some combinatorial logic cells to the circuit as was shown.

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

## Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

## **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.