# HC5503PRC SLIC and the IDT821034 Quad PCM CODEC with Programmable Gain

Author: Don LaFontaine and Chris Ludeman(Intersil)

# Reference Design Using the HC5503PRC SLIC and the IDT821034 Quad PCM CODEC with Programmable Gain

The network requirements of many countries require the analog subscriber line circuit (SLIC) to terminate the subscriber line with an impedance for voiceband frequencies which is complex, rather than resistive (e.g.,  $600\Omega$ ). This requires that the physical resistance that is situated between the SLIC and the subscriber line, comprised of protection and/or sensing resistors, and the output resistance of the SLIC itself, be adapted to present an impedance to the subscriber line that varies with frequency. This is accomplished using feedback around the SLIC.

The purpose of this application note is to show a means of accomplishing this task for the HC5503PRC and the IDT Quad PCM CODEC [1].

Discussed in this application note are the following:

- 2-wire 600 *Q* impedance matching

- 2-wire complex impedance matching

- Receive gain (4-wire to 2-wire) and transmit gain (2-wire to 4-wire) calculations

- Transhybrid balance calculations

- Reference design for  $600\Omega$  2-wire load

- Reference design for China complex 2-wire load

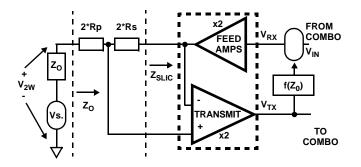

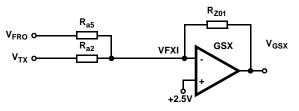

Figure 1 Impedance Matching Block Diagram

#### **Impedance Matching**

Impedance matching of the HC5503PRC to the subscriber load is important for optimization of 2-wire return loss, which in turn cuts down on echoes in the end-to-end voice communication path. It is also important for maintaining voice signal levels on long loops. Consider the equivalent circuit shown in Figure 1.

The circuitry inside the dotted box is representative of the SLIC feed and transmit amplifiers. The feed and transmit amplifiers pass the voice signals in the receive and transmit directions respectively. Without the feedback block  $f(Z_0)$ , the termination resistance at  $V_{2W}$  would equal the two protection resistors ( $R_P$ ) and the two sense resistors ( $R_S$ ), as the feed amplifiers present a very low output impedance to the subscriber line. The desired termination impedance at  $V_{2W}$  is  $Z_0$ . The feedback block  $f(Z_0)$  matches the SLICs output impedance ( $Z_{SLIC}$ ) plus the two protection resistors ( $R_P$ ) and the two sense resistors ( $R_S$ ) to the load ( $Z_0$ ).

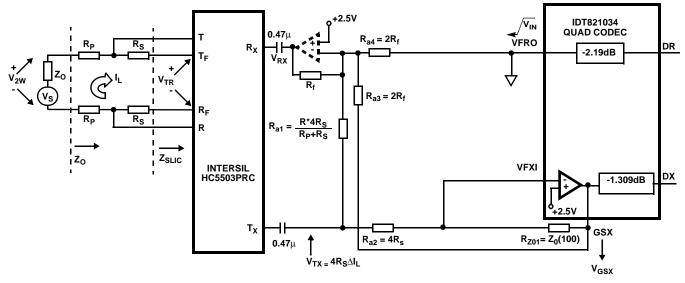

Figure 2 Impedance Matching

Impedance matching of the HC5503PRC is accomplished by making the SLIC's impedance ( $Z_{SLIC}$ , Figure 2) equal to the desired terminating impedance  $Z_0$ , minus the value of the protection and sense resistors. The desired impedance at the input to the SLIC is given in Equation 1.

$$Z_{SLIC} = Z_0 - 2 \times R_P - 2 \times R_S$$

(EQ. 1)

The AC loop current required to satisfy this condition is given in Equation 2.

$$\Delta I_{L} = \frac{V_{TR}}{(Z_0 - 2 \times R_P - 2 \times R_S)} \text{ at matching}$$

(EQ. 2)

The current calculated in Equation 2 is used as feedback to match the impedance of the SLIC and both protection and sense resistors to the load  $Z_0$ .

The output voltage of the SLIC (VTX) is defined by design and given in Equation 3.

$$V_{TX} = 4R_{S}\Delta I_{L}$$

(EQ. 3)

Substituting for  $\Delta I_1$  from Equation 2 into Equation 3 results in the voltage at the VTX output that will be used to generate the required feedback.

$$V_{TX} = \frac{4R_S \times V_{TR}}{(Z_0 - 2 \times R_P - 2 \times R_S)}$$

(EQ. 4)

By design,  $V_{TR}$  is equal to 2 times the voltage at the receive input (RX) Figure 2.

$$V_{TR} = 2 \times V_{RX}$$

(EQ. 5)

Substituting Equation 5 into Equation 4.

$$V_{TX} = \frac{4R_S \times 2 \times V_{RX}}{(Z_0 - 2 \times R_P - 2 \times R_S)}$$

(EQ. 6)

#### HC5503PRC SLIC and the IDT821034 Quad PCM CODEC with Programmable Gain

**Application Note AN-352**

Solving Equation 6 for the voltage at  $V_{RX}$  as a function of  $V_{TX}$  (when matching the  $Z_{SLIC}$ , the two protection resistors ( $R_P$ ) and the two sense resistors ( $R_S$ ) to the load  $Z_O$ ) is given in Equation 7.

$$\frac{V_{RX}}{V_{TX}} = \frac{(Z_0 - 2 \times R_p - 2 \times R_S)}{8 \times R_S}$$

(EQ. 7)

Equation 7 is the gain of the feedback circuit (output/input =  $V_{RX}/V_{TX}$ ) used to match the impedance of the SLIC and both protection and sense resistors. Note: In Equation 7 it seemed logical to simplify the numerator by trying to combine Z<sub>0</sub> and the two subsequent terms together. In practice however, the impedance of the network you want to match (Z<sub>0</sub>) cannot easily have  $2^*R_p$  and  $2^*R_s$  subtracted from it since the sum of these resistors is often larger than the value of the series resistance of the complex network.

Equation 7 is therefore rewritten in Equation 8.

$$\frac{V_{RX}}{V_{TX}} = \frac{Z_0}{8 \times R_S} - \frac{2 \times (R_P + R_S)}{8 \times R_S}$$

(EQ. 8)

Analysis of Equation 8 yields a 2 OpAmp feedback network. The first term has  $Z_0$  and no phase inversion. This requires the path to flow through 2 OpAmps and makes the matching of different complex loads easy. (i.e., can set  $Z_0$  in feedback network equal to the  $Z_0$  you want to match). The second term has a phase inversion and requires only one OpAmp in the feedback path.

Figure 2 shows the circuit required to achieve matching of the SLIC's impedance to the load  $Z_0$ . The voltage at  $V_{RX}$  is a function of  $V_{TX}$ ,  $V_{GSX}$  ( $V_{TX}R_{ZO1}/R_{a2}$ ) and  $V_{IN}$ .

The voltage at V<sub>RX</sub> is determined via superposition. The circuit equation for the feedback network is given in Equation 9.

$$V_{RX} = -V_{TX} \frac{R_f}{R_{a1}} + \frac{V_{TX} R_{ZO1} R_f}{R_{a2} R_{a3}} - \frac{V_{IN} R_f}{R_{a4}}$$

(EQ. 9)

For impedance matching of the two wire side, we set V<sub>IN</sub> equal to zero. This reduces Equation 9 to that shown in Equation 10.

$$V_{RX} = -V_{TX} \frac{R_f}{R_{a1}} + \frac{V_{TX} R_{ZO1} Rf}{R_{a2} R_{a3}}$$

(EQ. 10)

To achieve the desired matching of the circuit to the line impedance  $Z_0$ , we set our design Equation 8 equal to our circuit Equation 10. By inspection of the correct phase in Equations 8 and 10, we have Equations 11 and 12.

$$\frac{Z_0}{8 \times R_S} = \frac{R_{ZO1}Rf}{R_{a2}R_{a3}}$$

(EQ. 11)

$$\frac{2 \times (R_{\rm P} + R_{\rm S})}{8 \times R_{\rm S}} = \frac{R_{\rm f}}{R_{\rm a1}}$$

(EQ. 12)

Given: Rf = R,  $R_{a3} = 2R$ ,  $R_{ZO1} = Z_0$  Note: by making  $R_{a3} = 2R_f$ , the value of  $R_{a2}$  becomes  $4R_S$  (Equation 13). This results in the 2-wire to 4-wire gain being equal to 1 (Equation 24 and Equation 25)

From Equation 11.

$$\mathbf{R}_{a2} = 4\mathbf{R}_{S} \tag{EQ. 13}$$

From Equation 12.

$$R_{a1} = \frac{R \times 4R_S}{R_P + R_S} \tag{EQ. 14}$$

#### Receive Gain (V<sub>IN</sub> to V<sub>2W</sub>)

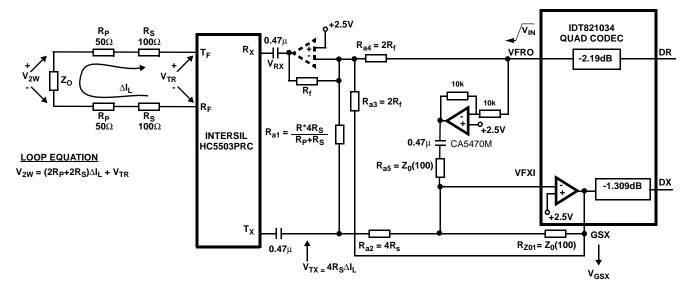

4-wire to 2-wire gain is equal to the V<sub>2W</sub> divided by the input voltage V<sub>IN</sub>, reference Figure 3. The gain through the IDT821034 is programmed for this example to one (V<sub>IN</sub> = V<sub>DR</sub> = V<sub>VFRO</sub>).

$$A_{4W-2W} = \frac{V_{2W}}{V_{IN}}$$

(EQ. 15)

The 2-wire voltage  $V_{2W}$  is determined by a loop equation and is given in Equation 16.

$$V_{2W} = (2R_P + 2R_S)\Delta I_L + V_{TR}$$

(EQ. 16)

----

Combining Equation 5 and Equation 9, gives an expression for V<sub>TR</sub> in terms of V<sub>RX</sub>, as shown in Equation 17.

$$V_{TR} = 2V_{RX} = 2\left(-V_{TX}\frac{R_f}{R_{a1}} + \frac{V_{TX}R_{ZO1}Rf}{R_{a2}R_{a3}} - \frac{V_{IN}R_f}{R_{a4}}\right)$$

(EQ. 17)

The voltage at  $V_{TR}$  is therefore a function of  $V_{TX}$  and  $V_{IN}$ . Note: contribution from  $V_{GSX}$  (middle term in Equation 17) is zero due to the transhybrid circuit, reference section titled "Transhybrid Balance G(4-4)".

This reduces Equation 17 to Equation 18.

$$V_{TR} = 2V_{RX} = -2\left(V_{TX}\frac{R_f}{R_{a1}} + \frac{V_{IN}R_f}{R_{a4}}\right)$$

(EQ. 18)

Substituting  $4R_S\Delta I_L$  (Equation 3) for  $V_{TX}$  in Equation 18 and combining this with Equation 16, results in an equation for  $V_{2W}$  in terms of:  $\Delta I_L$ , the external resistors and the input voltage  $V_{IN}$  (Equation 19).

$$V_{2W} = (2R_{P} + 2R_{S})\Delta I_{L} - 8R_{S}\Delta I_{L}\frac{R_{f}}{R_{a1}} - 2\frac{V_{IN}R_{f}}{R_{a4}}$$

(EQ. 19)

Ohms law defines  $\Delta I_L$  as being equal to  $-V_{2W}/Z_0$ . Substituting  $-V_{2W}/Z_0$  for  $\Delta I_L$  in Equation 19 gives Equation 20.

$$V_{2W} = -(2R_{P} + 2R_{S})\frac{V_{2W}}{Z_{O}} + 8R_{S}\frac{V_{2W}}{Z_{O}}\frac{R_{f}}{R_{a1}} - 2\frac{V_{IN}R_{f}}{R_{a4}}$$

(EQ. 20)

Equation 20 can be rearranged to solve for the 4-wire to 2-wire gain  $V_{2W}/V_{IN}$ , as shown in Equation 21.

$$A_{4W-2W} = \frac{V_{2W}}{V_{IN}} = -\left(\frac{2R_f}{R_{a4}}\right) \times \frac{R_{a1}Z_O}{R_{a1}(2R_P + 2R_S) + R_{a1}Z_O - 8R_SR_A}$$

(EQ. 21)

Given: Rf=100k $\Omega$ , Ra4=200k $\Omega$ , Ra1=267k $\Omega$ , ZO=600 $\Omega$ , RS=100 $\Omega$ , RP=50 $\Omega$ .

Note: by making  $R_{a4}$  equal to  $2R_f$  the 4-wire to 2-wire gain becomes -1.

### Transmit Gain across HC5503PRC (V<sub>2W</sub> to V<sub>TX</sub>)

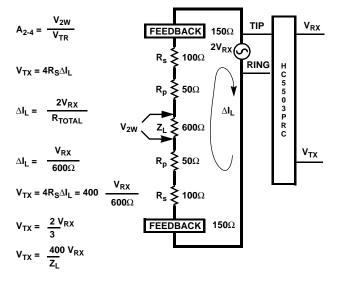

The output voltage of the SLIC ( $V_{TX}$ ) was defined in Equation 3 as being equal to  $4R_S\Delta I_L$ .  $\Delta I_L$  is equal to twice the input voltage ( $2V_{RX}$ ) divided by the total loop resistance as shown in Figure 4. If the load impedance is 600 $\Omega$  then the gain across the HC5503PRC is 2/3 (400/600) the input voltage  $V_{RX}$ .

#### Transmit Gain (V<sub>2W</sub> to V<sub>GSX</sub>)

2-wire to 4-wire gain is equal to the V<sub>GSX</sub> voltage divided by the 2-wire voltage V<sub>2W</sub>, reference Figure 3.

$$A_{2W-4W} = \frac{V_{GSX}}{V_{2W}}$$

(EQ. 22)

Figure 3 Receive Gain G(4-2), Transmit Gain (2-4) and Transhybrid Balance

Figure 4 Transmit Gain Across HC5503

$V_{GSX}$  is only a function of  $V_{TX}$  and the feedback resistors  $R_{a2}$  and  $R_{ZO1}$  Equation 23. This is because  $V_{IN}$  is considered ground for this analysis, thereby effectively grounding the VFRO input.

$$V_{GSX} = -V_{TX} \frac{R_{ZO1}}{R_{a2}}$$

(EQ. 23)

Substituting Equation 3 for  $V_{TX}$  and  $\Delta_{IL}$  for  $-V_{2W}/Z_0$  into Equation 23,  $V_{GSX}$  equals:

$$V_{GSX} = 4R_S \frac{V_{2W}}{Z_O} \left(\frac{R_{ZO1}}{R_{a2}}\right)$$

(EQ. 24)

$Z_0$  is equal to  $R_{ZO1}$  (actual values of  $R_{ZO1}$  and Ra2 were multiplied by 100 to reduce loading effects on the OpAmps). Simplifying Equation 24 and assuming  $R_{a2}$ =4RS from Equation 13 results in Equation 25.

$$A_{2W-4W} = \frac{V_{GSX}}{V_{2W}} = \left(\frac{4R_S}{4R_S}\right) = 1$$

(EQ. 25)

The transmit gain 2-wire to 4-wire is equal to one.

#### **Transhybrid Balance G(4-4)**

Transhybrid balance is a measure of how well the input signal is canceled (that being received by the SLIC) from the transmit signal (that being transmitted from the SLIC to the CODEC). Without this function, voice communication would be difficult because of the echo.

The signals at  $V_{FRO}$  and  $V_{TX}$  (Figure 3) are in phase. Transhybrid balance is achieved by summing two signals that are equal in magnitude and opposite in phase into the GSX amplifier. The CA5470M op-amp provides a signal that is equal in magnitude an opposite in phase from the  $V_{FRO}$  signal.

Transhybrid balance is achieved by summing the output of the CA5470M signal with the output signal from the HC5503PRC, when the proper gain adjustments are made to match  $V_{FRO}$  and  $V_{TX}$  magnitudes.

For discussion purpose, the GSX amplifier is redrawn with the external resistors in Figure 5.

Figure 5 Transhybrid Balance Circuit

The gain through the GSX amplifier from  $V_{TX}$  is set by resistors  $R_{a2}$  and  $R_{Z01}$ . Both resistors ( $R_{a2}$  and  $R_{Z01}$ ) are used in the feedback loop to match the two wire impedance, and thus set. The gain through the GSX amplifier from  $V_{FRO}$  is set by resistors  $R_{a5}$  and  $R_{Z01}$ . Matching of the magnitudes for transhybrid balance will be accomplished using resistor  $R_{a5}$ .

Using superposition for both inputs to the GSX amplifier and setting both gains equal to each other yields Equation 26.

$$V_{TX}\left(\frac{R_{Z01}}{R_{a2}}\right) = VFRO - \left(\frac{R_{Z01}}{R_{a5}}\right)$$

(EQ. 26)

Cancelling out  $R_{Z01}$ , setting  $V_{TX}$  equal to 400/Z<sub>L</sub> times ( $V_{FRO}$ ) and rearranging to solve for  $R_{a5}$  results in Equation 27.

$$R_{a5} = VFRO\left(\frac{R_{a2}}{V_{TX}}\right) = \frac{R_{a2}Z_L}{400}$$

(EQ. 27)

The values of R<sub>a2</sub>, R<sub>a5</sub>, and R<sub>ZO1</sub> should be scaled by 100 to minimize loading of the GSX amplifier (Figure 5).

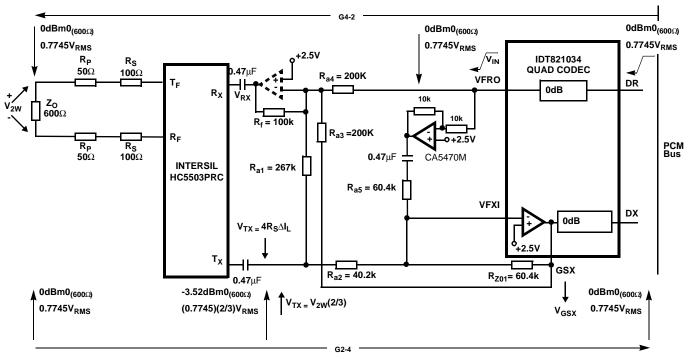

#### Reference Design of the HC5503PRC and the IDT821034 With a 600 $\Omega$ Load Impedance

The design criteria is as follows:

- 4-wire to 2-wire gain (PCMIN to V<sub>2W</sub>) equal 0dB

- 2-wire to 4-wire gain (V<sub>2W</sub> to PCMOUT) equal 0dB

- Two Wire Return Loss greater than -30dB (200Hz to 4kHz)

$$R_p = 50, R_s = 100.$$

Figure 6 gives the reference design using the Intersil HC5503PRC SLIC and the IDT821034 Quad Combo. Also shown in Figure 5 are the voltage levels at specific points in the circuit. These voltages will be used to adjust the gains of the network.

#### **Impedance Matching**

For impedance matching of the 2-wire side we set the input voltage at DR equal to zero. This effectively grounds the  $V_{FRO}$  input of the GSX amplifier. To determine the value of  $R_{a2}$  to achieve a 2-wire to 4-wire gain ( $V_{2W}$  to DX) of 0dB we use Equation 24, repeated here for convenience in Equation 28. The programmed transmit and receive gains of the IDT821034 are set to 0dB for this application.

$$V_{GSX} = 4R_{S} \frac{V_{2W}}{Z_{O}} \left(\frac{R_{ZO1}}{R_{a2}}\right)$$

(EQ. 28)

Substituting the required voltage levels (Figure 6) for  $V_{GSX}$  (0.7745) and  $V_{2W}$  (0.7745) and rearranging to solve for  $R_{a2}$  results in Equation 29. Where:  $V_{GSX} / V_{2W} = 1.0$ , and  $Z_0 = R_{Z01}$ :

$$R_{a2} = \frac{400}{1.0} = 400 \tag{EQ. 29}$$

The value of  $R_{a2}$  needs to be scaled by 100 to minimize the effects of loading on the GSX amplifier. The nearest standard value for  $R_{a2}$  is 40.2k $\Omega$ .

R<sub>a3</sub> needs to be adjusted by V<sub>GSX</sub> / V<sub>2W</sub> to maintain the same feedback for impedance matching Equation 30.

$$R_{a3} = (200k\Omega)(1.0) = 200k\Omega$$

(EQ. 30)

The closest standard value is for  $R_{a3}$  is 200k $\Omega$ .

#### **Transhybrid Balance (Z<sub>L</sub> = 600Ω)**

The internal GSX amplifier of the IDT821034 is used to perform the transhybrid balance function. Equation 27, repeated here in Equation 31, is used to determine the value of  $R_{a5}$  for proper transhybrid balance.

$$R_{a5} = V_{FRO} \left( \frac{R_{a2}}{V_{TX}} \right) = \frac{R_{a2}Z_L}{400}$$

(EQ. 31)

The values of R<sub>a2</sub>, R<sub>a5</sub>, and R<sub>Z01</sub> should be scaled by 100 to minimize loading of the GSX amplifier.

$V_{TX}$  is equal to (0.7745 $V_{RMS}$ )(2/3).  $V_{FRO}$  is equal to 0.7745 $V_{RMS}$ .

$$R_{a5} = \frac{R_{a2}Z_L}{400} = \frac{40.2K\Omega \times 600\Omega}{400\Omega} = 60.3k\Omega$$

(EQ. 32)

Closest standard value for Ra5 is 60.4k $\Omega$

Figure 6 Rreference Design of the HC5503PRC and the IDT821034 with a  $600\Omega$ Load Impedance

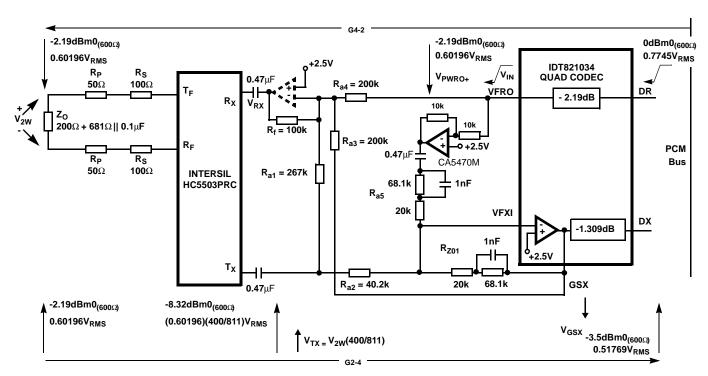

#### **Specific Implementation for China**

- The design criteria for a China specific solution are as follows:

- Desired line circuit impedance is 200 + 680//0.1µF

- Receive gain (V<sub>2W</sub>/V<sub>PCMIN</sub>) is -3.5dB

- Transmit gain (V<sub>PCMOUT</sub>/V<sub>2W</sub>) is 0dB

- 0dBm0 is defined as 1mW into the complex impedance at 1020Hz

$R_p = 50$ ,  $R_s = 100$ .

Figure 7 gives the reference design using the Intersil HC5503PRC SLIC and the IDT821034 Quad Combo. Also shown in Figure 7 are the voltage levels at specific points in the circuit. These voltages will be used to adjust the gains of the network.

#### Adjustment to Get -3.5dBm0 at The Load Referenced to 600 $\Omega$

The voltage equivalent to 0dBm0 into 811 $\Omega$  (0dBm0<sub>(811 $\Omega$ )</sub>) is calculated using Equation 33. China complex load @ 1kHz is equal to 811 $\Omega$

$$0 dBm_{(811\Omega)} = 10 log \frac{V^2}{811(0.001)} = 0.90055 V_{RMS}$$

(EQ. 33)

The gain referenced back to  $0dBmO_{(600\Omega)}$  is equal to:

$$GAIN = 20\log \frac{0.90055 V_{RMS}}{0.7745 V_{RMS}} = 1.309 dB$$

(EQ. 34)

The adjustment to get -3.5dBm0 at the load referenced to  $600\Omega$  is:

$$Adjustment = -3.5dBm0 + 1.309dBm0 = -2.19dB$$

(EQ. 35)

The voltage at the load (referenced to  $600\Omega$ ) is given in Equation 36:

$$-2.19 dBm_{(600\Omega)} = 10 \log \frac{V^2}{600(0.001)} = 0.60196 V_{RMS}$$

(EQ. 36)

#### HC5503PRC SLIC and the IDT821034 Quad PCM CODEC with Programmable Gain

#### **Impedance Matching**

For impedance matching of the 2-wire side we set the input voltage at DR equal to zero. To determine the value of  $R_{a2}$  to achieve a 2-wire to 4-wire gain ( $V_{2W}$  to DX) of 0dB we use Equation 24, repeated in Equation 37.

$$V_{GSX} = 4R_S \frac{V_{2W}}{Z_O} \left( \frac{R_{ZO1}}{R_{a2}} \right)$$

(EQ. 37)

Substituting the required voltage levels Figure 7) for  $V_{GSX}$  (0.60196) and  $V_{2W}$  (0.60196) and rearranging to solve for  $R_{a2}$  results in Equation 39. Where:  $V_{GSX} = V_{2W}$ , and  $Z_0 = R_{Z01}$ :

$$R_{a2} = \frac{400}{1} = 400 \times 100 = 40k$$

(EQ. 38)

Figure 7 Reference Design of the HC5503PRC and the IDT821034 with Cchina Complex Load Impedance

The value of R<sub>a2</sub> needs to be scaled by 100 to minimize the effects on the GSX amplifier.

The nearest standard value for  $R_{a2}$  is 40.2k $\Omega$ .

$R_{a3}$  needs to increase by the ratio  $V_{GSX}/V_{2W}$  (1 for this example) to maintain the same feedback for impedance matching as shown in Equation 39.

$$R_{a3} = (200k\Omega)(1) = 200k\Omega$$

(EQ. 39)

The closest standard value is for  $R_{a3}$  is 200k $\Omega$

# **Programming the Gain of the IDT821034**

To achieve a receive gain (V2W / VDX) of -3.5dB at the load referenced to  $600\Omega$  the IDT821034 receive gain must be programmed to -2.19dB. To achieve a transmit gain (V<sub>DX</sub> / V<sub>2W</sub>) of 0dB, the IDT821034 transmit gain must be programmed to -1.309dB.

# HC5503PRC SLIC and the IDT821034 Quad PCM CODEC with Programmable Gain

#### Transhybrid Balance ( $Z_L = 200 + 680//0.1 \mu F$ )

The internal GSX amplifier of theIDT821034 is used to perform the transhybrid balance function. Equation 27, repeated here in Equation 40, is used to determine the value of  $R_{a5}$  for proper transhybrid balance.

$$R_{a5} = VFRO\left(\frac{R_{a2}}{V_{TX}}\right) = \frac{R_{a2}Z_L}{400}$$

(EQ. 40)

V<sub>TX</sub> is equal to (0.60196V<sub>RMS</sub>)(400/811). V<sub>PWRO-</sub> is equal to 0.60196V<sub>RMS</sub>.

$$R_{a5} = \frac{R_{a2}Z_L}{400} = \frac{40K\Omega \times 200\Omega + 680\Omega\Pi 0.1\mu F}{400\Omega}$$

(EQ. 41)

Closest standard values, Ra5 =  $20k\Omega + 68.1k\Omega II 1nF$ .

The values of  $R_{a2}$ ,  $R_{a5}$ , and  $R_{ZO1}$  should be scaled by 100 to minimize loading of the GSX amplifier. Scaling of a complex load is shown in Equation 46.

$$R_{ZO1}$$

or  $R_{ZO2} = 100(Resistive) + \frac{Reactive}{100}$  (EQ. 42)

Note: When matching a complex impedance some impedance models (900+2.15μF, K=100) will cause the OpAmp feedback to be open at DC currents, bringing the OpAmp to an output rail. A resistor with a value of about 10 times the reactance of the capacitor (21.6nF) at the low frequency of interest (200Hz for example) can be placed in parallel with the capacitor in order to solve the problem (368kΩfor a 21.6nF capacitor).

#### Reference

[1] Website

www.idt.com/

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.