# **COMMON INFORMATION**

# Package Information

Thermal Characterization of Packaged Semiconductor Devices

TB379 Rev.4.00 August 10, 2015

# Abstract

With the continuing industry trends towards smaller, faster and higher power devices, thermal management is becoming increasingly important. After all, higher device performance can come at a price (higher temperatures and lower reliability) if thermal considerations aren't carefully weighed.

Not only are devices trending smaller but the boards they mount onto are also shrinking. Placing the units closer and closer together on smaller boards helps lower overall system size and cost and improves electrical performance. These benefits are important; but from a thermal standpoint, raising power while reducing size is a bad combination. It's this increase in "power density" that's been driving the heightened industry focus on thermal management.

To assist board and system level designers in this effort, Intersil provides standardized thermal resistance data, most commonly Theta-<sub>JA</sub>, on our product datasheets. This tech brief should assist in understanding and using these thermal resistances or "theta's". It also discusses several thermal characterization parameters called "psi's" that are coming into more widespread use.

# **Table of Contents**

| The Concept of Thermal Resistance                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Common Terminology                                                                                                                                                                                                           |

| Thermal Test Standardization                                                                                                                                                                                                 |

| The 3 Basic Thermal Test Board Types                                                                                                                                                                                         |

| Industry Standards for Thermal Test Boards                                                                                                                                                                                   |

| Typical Test Board Features                                                                                                                                                                                                  |

| Industry Standards for Thermal Test Procedures                                                                                                                                                                               |

| General Methodology .5   Natural Convection .5   Forced Convection .5   Junction-to-case .5   Junction-to-board .5                                                                                                           |

| General Test Procedures                                                                                                                                                                                                      |

| Lab Testing of Standard Packages on JEDEC Standard Boards 5   Lab Testing of Unique Packages Such as Modules on Product Evaluation Boards 5   Finite Element Analysis (FEA) or Computational Fluid Dynamics (CFD) Modeling 5 |

| The 5 Main Thermal Metrics                                                                                                                                                                                                   |

| Theta-JA. .6   Theta-JC. .7   Theta-JB. .8   Psi-JB. .8   Psi-JT. .9                                                                                                                                                         |

| Additional PCB Design Considerations                                                                                                                                                                                         |

| Spread the Heat Around and Down 10   Think "Thermal", not "Electrical" 10                                                                                                                                                    |

| Appendix A                                                                                                                                                                                                                   |

| JESD51-X. 11<br>JESD51-3 11<br>JESD51-7 11<br>JESD51-5 11<br>JESD51-9 11<br>JESD51-10 12<br>JESD51-11 12                                                                                                                     |

# **List of Figures**

| FIGURE 1. | Top View - Typical Test Board                                   | .4 |

|-----------|-----------------------------------------------------------------|----|

|           | Side View (~5X) - High Effective Conductivity (1S2P) Test Board |    |

|           | Theta-JA Measurement Points                                     |    |

| FIGURE 4. | Theta-IC Measurement Points for 3 Mounting Examples.            | .7 |

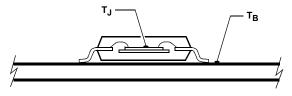

| FIGURE 5. | Theta-IB Measurement Points                                     | .8 |

| FIGURE 6. | PSI-JB Measurement Points                                       | .8 |

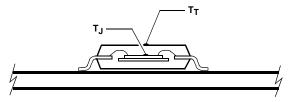

| FIGURE 7. | PSI-JT Measurement Points                                       | .9 |

# The Concept of Thermal Resistance

A common method of characterizing a packaged device's thermal performance is with "thermal resistance", denoted by the Greek letter "theta" or  $\theta$ . For a semiconductor device, thermal resistance indicates the steady state temperature rise of the die junction above a given reference for each watt of power (heat) dissipated at the die surface. Its units are °C/W.

The most common examples are Theta-<sub>JA</sub> (junction-to-ambient), Theta-<sub>JC</sub> (junction-to-case), and Theta-<sub>JB</sub> (junction-to-board). Knowing the reference, (i.e., ambient, case, or board) temperature, the power, and the relevant theta value, the junction temperature can be calculated. Theta-<sub>JA</sub> is commonly used with natural and forced convection air-cooled systems using components mounted on epoxy-glass PCBs. Theta-<sub>JC</sub> is useful when the package has a high conductivity case mounted directly to a PCB or heatsink. And theta-<sub>JB</sub> applies when the board temperature adjacent to the package is known.

In addition to these theta thermal resistances, the  $psi-_{JB}$  (junction-to-board) and  $psi-_{JT}$  (junction-to-top) thermal characterization parameters can be useful. For a device powered up on an application board, these psi's provide a correlation between junction temperature and the board temperature or "top of package" temperature.

The term "psi" is used to distinguish these from "theta" thermal resistances since not all heat is actually flowing between the points of temperature measurement with the psi's. They're not true thermal resistances for this reason.

# **Common Terminology**

- T<sub>J</sub> = Die junction temperature, °C

- T<sub>C</sub> = Package case temperature, °C

- T<sub>B</sub> = Board temperature adjacent to package, °C

- T<sub>T</sub> = Top of package temperature at center, °C

- T<sub>A</sub> = Ambient air temperature, °C

- $\theta_{JA}$  (Theta-<sub>JA</sub>) = Thermal resistance junction-to-ambient, °C/W

- $\theta_{JC}$  (Theta-<sub>JC</sub>) = Thermal resistance junction-to-case, °C/W

- $\theta_{JB}$  (Theta-<sub>JB</sub>) = Thermal resistance junction-to-board, °C/W

- +  $\Psi_{JB}$  (Psi-\_{JB}) = Junction-to-board characterization parameter,  $^{\circ}$  C/W

- Ψ<sub>JT</sub> (Psi-<sub>JT</sub>) = Junction-to-top (of package) characterization parameter, °C/W

- P = Power dissipated by device, Watts

# **Thermal Test Standardization**

The main purpose of standard datasheet thermal ratings is to compare the relative performance of packaged devices against each other. These comparisons are more accurate and meaningful when the tests are performed using standardized procedures. Intersil generally follows the following industry standards:

• JEDEC EIA/ JESD 51-X Series Standards

They're available at <u>www.jedec.org</u> under the "Standards and Documents" area. These define thermal test board designs as well as general thermal test procedures. This tech brief will summarize key details.

# The 3 Basic Thermal Test Board Types

Because of the influence of the Printed Circuit Board (PCB) on results, tight control of the test board design is needed. This helps ensure that differences in published thermal ratings from various suppliers are due to the component or package design, and not test board variability.

When directly comparing theta- $_{JA}$ 's for different products, be sure to compare data for the same board type. The 3 basic board types have different heat spreading capability and will result in different theta- $_{JA}$  values, even for the exact same device. On each product datasheet, Intersil generally provides thermal data based on the board type(s) that are likely to be used in the application.

The 3 basic test board types are:

#### 1. "Low Effective" Thermal Conductivity Board (1SOP)

- Top surface traces only.

- Called 1S or 1SOP for "1 Signal, 0 Plane" layers.

- Similar to previous "SEMI" 1S0P boards.

- Applicable JEDEC board specs:

- JESD51-3: Most surface mount packages.

- JESD51-9: Area array (e.g., BGA, WLCSP).

- JESD51-10: Through-hole perimeter leaded (e.g., DIP, SIP).

- JESD51-11: Through-hole area array (e.g., PGA).

#### 2. "High Effective" Thermal Conductivity Board (1S2P)

- Top surface traces + 2 buried planes.

- Called 1S2P for "1 Signal, 2 Plane" layers.

- Also called 2S2P because of a 2nd nonrelevant bottom edge signal trace layer for wiring.

- Adding 2 planes lowers theta-<sub>JA</sub> roughly 20-40+% vs 1S0P (reduction varies widely by package size and style).

- Applicable JEDEC board specs:

- JESD51-7: Most surface mount packages.

- JESD51-9: Area array (e.g., BGA, WLCSP).

- JESD51-10: Through-hole perimeter leaded (e.g., DIP, SIP).

- JESD51-11: Through-hole area array (e.g., PGA).

- 3. "High Effective" Thermal Conductivity Board with "Direct Attach" Features (1S2P+Vias)

- Top surface traces + 2 buried planes + thermal vias.

- Called 1S2P+Vias or 1S2P-DA board type.

- Applies to WLCSPs with GND/thermal balls and to plastic packages with exposed metal pads (e-pads), thermal balls, etc.

- Applies to ceramic/metal packages when the base (whether ceramic or metal finish) is adhered to the PCB (no air gap).

- Thermal vias are added into the PCB below the package to connect to the upper buried plane.

- Adding vias lowers theta-JA vs 1S2P type (percentage varies but generally significant).

- Applicable JEDEC board specs:

- JESD51-5 add-on to JESD51-7: Most surface mount packages.

- JESD51-9: Area array (e.g., BGA, WLCSP).

# Industry Standards for Thermal Test Boards

JEDEC uses a number of standards to define the test board designs that apply to the various package styles:

- JESD51-3: "Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages"

- JESD51-7: "High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages"

- JESD51-5: "Extension of Thermal Test Board Standards for Packages with Direct Thermal Attachment Mechanisms"

- JESD51-9: "Test Boards for Area Array Surface Mount Package Thermal Measurements"

- **JESD51-10:** "Test Boards for Through-hole Perimeter Leaded Package Thermal Measurements"

- JESD51-11: "Test Boards for Through-hole Area Array Leaded Package Thermal Measurements"

Studying these standards isn't necessary to simply compare datasheet theta- $_{JA}$ 's for different devices. But understanding more of the test board design details should help a system level designer estimate the device thermal performance on their actual application board.

This is accomplished by comparing such details as board size, metal coverage, buried planes, thermal vias, etc. This can help determine whether a device will be hotter or cooler on the application board vs the standard test board. Note that these test boards contain only 1 self-heated unit, so theta-JA's based on them don't include mutual heating from any other devices.

The typical features listed below apply to most test boards. A more extensive summary by each JEDEC test board standard is found in <u>"Appendix A" on page 11</u>.

# **Typical Test Board Features**

- Board Material: FR-4 epoxy-glass

- Finished copper metal layer thickness

- Surface traces: 2 ounce ±20%

- Buried planes: 1 ounce +0/-20%

- Board thickness: ~1.6mm (63mils)

• Board and buried plane size for most leaded and leadless surface mount packages

| PACKAGE LENGTH (L) | BOARD SIZE | PLANE SIZE<br>(IF PRESENT) |

|--------------------|------------|----------------------------|

| L ≤27mm            | 3 x 4.5"   | 2.92 x 2.92"               |

| 27 < L ≤48mm       | 4 x 4.5"   | 3.92 x 3.92"               |

• Board and buried planes size for BGA, WLCSP, DIP, SIP and PGA packages.

| PACKAGE LENGTH (L) | BOARD SIZE | PLANE SIZE<br>(IF PRESENT) |

|--------------------|------------|----------------------------|

| L ≤ 40mm           | 4 x 4.5"   | 3.92 x 3.92"               |

| 40 < L ≤ 65mm      | 5 x 5.5"   | 4.92 x 4.92"               |

| 65 < L ≤ 90mm      | 6 x 6.5"   | 5.92 x 5.92"               |

- See <u>"Appendix A" on page 11</u> for extensive summary.

- See JEDEC specs for all details.

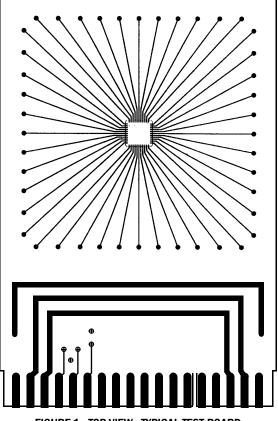

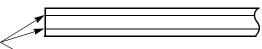

- Figures 1 and 2 show a typical test board from Top and Side Views.

FIGURE 1. TOP VIEW - TYPICAL TEST BOARD

INTERNAL PLANES, 1oz. SOLID CU

FIGURE 2. SIDE VIEW (~5X) - HIGH EFFECTIVE CONDUCTIVITY (1S2P) TEST BOARD

# Industry Standards for Thermal Test Procedures

Intersil calculates Theta and Psi values using temperature and power data from a lab test or equivalent computer simulation. Testing procedures generally follow the JEDEC EIA/JESD 51-X series. The applicable standards grouped by type are:

# **General Methodology**

- JESD51: "Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device)"

- JESD51-1: "Integrated Circuits Thermal Measurement Method-electrical Test Method (Single Semiconductor Device)"

- JESD51-13: "Glossary of Thermal Measurement Terms and Conditions"

- JEP140: "Beaded Thermocouple Temperature Measurement of Semiconductor Packages"

### **Natural Convection**

(Applies to Theta-JA, psi-JT, psi-JB)

• JESD51-2A: "Integrated Circuits Thermal Test Method Environmental Conditions - Natural Convection (Still Air)"

These "still air" tests are run in a 1 cubic foot box to prevent stray air currents. The JEDEC compliant board is mounted horizontally, with the device on the top side.

# **Forced Convection**

(Applies to Theta-JA, psi-JT, psi-JB)

• JESD51-6: Integrated Circuits Thermal Test Method Environmental Conditions - Forced Convection (Moving Air)

Airflow tests are run in a wind tunnel with a single device mounted on a JEDEC compliant board. The board is mounted vertically and parallel to the airflow, which cools both sides of the board. Common airflow speeds are 100 to 600 Linear Feet per Minute (LFM). For reference, a commonly used speed of 200 LFM equals about 1 meter/second or 2.3 miles/hour, equivalent to a light breeze.

### Junction-to-case

(Applies to Theta-JC)

- SEMI G30-88: "Junction-to-case Thermal Resistance Measurements of Ceramic Packages"

- Mil-Std 883 Method 1012.1: Thermal Characteristics

The objective of the theta- $_{JC}$  test is to force almost all of the heat flow through either the package top or bottom surface (i.e., the "case"). This is achieved by mounting that surface onto a temperature-controlled heatsink.

#### Junction-to-board

(Applies to Theta-JB)

• JESD51-8: "Integrated Circuits Thermal Test Method Environmental Conditions - Junction-to-board" Defines a ring style cold plate used with a standard 1S2P or 1S2P+Vias test board. The cold plate is clamped onto both sides of the board at least 5mm from the package. Almost all heat is forced to flow from the package into the plane of the board so that accurate "junction-to-board" thermal resistance can be measured.

# **General Test Procedures**

### Lab Testing of Standard Packages on JEDEC Standard Boards

This type of data is based on results from an industry-standard Thermal Analyzer designed for this purpose.

$T_{\rm J}$  is determined using the semiconductor junction characteristic of a declining forward voltage drop with increasing temperature. Before each test, a sample unit is calibrated over the necessary temperature range while immersed in a heated mineral oil bath. The resulting calibration curve is used along with voltage readings to continuously monitor  $T_{\rm J}$  during the test.

Other temperatures (i.e.,  $T_A$ ,  $T_B$ ,  $T_T$ ,  $T_C$ ) are monitored using small thermocouples. Once the device has reached steady-state equilibrium, temperatures applicable to the test are recorded. The analyzer controls device power dissipation (P), which is used along with the temperature data to calculate the theta and/or psi values. Generally 3 or more units are tested and the results averaged.

### Lab Testing of Unique Packages Such as Modules on Product Evaluation Boards

Lab equipment specific to the product type involved may be used to take relevant device temperature and/or power data. Device internal  $(T_j)$  temperature data may be monitored through built-in device sensing methods, or embedded small thermocouples. In addition to the above, other temperatures are generally monitored using small thermocouples. Once the device has reached steady-state equilibrium, the device power dissipation (P) and temperatures applicable to the test are recorded and thermal metrics are calculated from the data.

Product datasheet Theta- $_{JA}$  or related metrics based on such work make reference to the product evaluation board used for thermal testing, rather than to a JEDEC standard thermal test board.

## Finite Element Analysis (FEA) or Computational Fluid Dynamics (CFD) Modeling

For a computer simulation, a detailed 3D-Solid model is constructed of the packaged device mounted as appropriate for the test involved. Intersil uses industry standard advanced thermal modeling software for these simulations.

With power applied to the die surface, the model is solved. The results provide full temperature contours across the package and board or heatsink. Temperatures at specific locations are extracted and used in relevant theta or psi calculations, just as if they had been obtained from lab testing.

# **The 5 Main Thermal Metrics**

| TABLE 1. QUICK SUMMARY |                 |                                   |                                                     |                               |                                                                                              |

|------------------------|-----------------|-----------------------------------|-----------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------|

| THERMAL<br>METRIC      | SYMBOL          | DEFINITION FORMULA                | GENERAL USAGE FORMULA                               | ТҮРЕ                          | MAIN PURPOSE                                                                                 |

| Theta- <sub>JA</sub>   | $\theta_{JA}$   | $\theta_{JA} = (T_J - T_A) / P$   | $T_{J} = T_{A} + (\theta_{JA} * P)$                 | Thermal<br>Resistance         | Used to rank package performance.                                                            |

| Theta- <sub>JC</sub>   | οιθ             | $\theta_{JC} = (T_J - T_C) / P$   | $T_{J} = T_{C} + (\theta_{JC} * P)$                 | Thermal<br>Resistance         | Used to rank package performance.                                                            |

| Theta- <sub>JB</sub>   | θJB             | $\theta_{JB} = (T_J - T_B) / P$   | $T_{J} = T_{B} + (\theta_{JB} * P)$                 | Thermal<br>Resistance         | Used to rank package performance and estimate T <sub>J</sub> of devices on application PCBs. |

| Psi- <sub>JB</sub>     | Ψјв             | $\Psi_{JB} = (T_{J} - T_{B}) / P$ | $T_{J} = T_{B} + (\Psi_{JB} * P)$                   | Characterization<br>Parameter | Used to estimate T <sub>J</sub> of devices on application PCBs.                              |

| Psi- <sub>JT</sub>     | τι <sup>Ψ</sup> | $\Psi_{JT} = (T_J - T_T) / P$     | $\mathbf{T}_{J} = \mathbf{T}_{T} + (\Psi_{JT} * P)$ | Characterization<br>Parameter | Used to estimate T <sub>J</sub> of devices on application PCBs.                              |

#### TABLE 1. QUICK SUMMARY

### Theta-<sub>JA</sub>

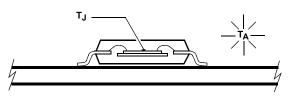

FIGURE 3. THETA-JA MEASUREMENT POINTS

#### DEFINITION: $\Theta_{JA} = (T_J - T_A) / P$

Where:

$\theta_{JA}$  = Thermal resistance junction-to-ambient, °C/W

$T_J$  = Die junction temperature, °C

T<sub>A</sub> = Ambient air temperature, °C

P = Power dissipated by device, watts

Example: To determine theta- $_{JA}$ , the lab test or model data needed is  $T_J$ ,  $T_A$ , and P. If  $T_J = 80$  °C,  $T_A = 25$  °C, and P = 1.0W, then:

$\theta_{IA} = (80^{\circ}C - 25^{\circ}C) / 1.0W = 55^{\circ}C/W.$

#### **USAGE FORMULA:**

With  $\theta_{JA},$  T\_A and P known, then:

$T_{J} = T_{A} + (\theta_{JA} * P)$

<u>Example</u>: If theta- $_{JA} = 55 \,^{\circ}$ C/W and the application board has similar construction as the thermal test board, then a 1st order approximation of T<sub>J</sub> in the system can be made. Assuming T<sub>A</sub> = +35  $^{\circ}$ C in the system, and steady state power of the device is P = 0.6W, then:

$T_J = 35^{\circ}C + (55^{\circ}C/W * 0.6W) = 68^{\circ}C$

#### KEY POINTS FOR $\Theta_{JA}$ :

- Indicates ease of heat flow through the total of all paths between die junction and ambient air.

- Datasheet  $\theta_{\text{JA}}\text{'s}$  are intended mainly for performance comparison of one packaged device against another.

- · Lower values indicate better performance.

- Since  $\theta_{JA}$  is highly dependent on board design, standardized test boards are used.

- Datasheet  $\theta_{JA}$ 's should be used only for 1st order approximation of performance (i.e.,  $T_J$  rise above  $T_A)$  in an application-specific environment.

#### APPLYING DATASHEET $\mathcal{O}_{JA}$ TO APPLICATION PCBs

It's safe to assume that a device that performs better in a standardized test will also perform better in an actual system of similar design. This helps in making component or package design choices, but when extending a vendor's standardized datasheet values to the end application, it's important to keep in mind that they're based on specific test conditions. It falls to the board/system designer to understand how the thermal test environment/board compare to the system under design. The various sections of this tech brief help by describing key details of thermal test boards and procedures.

It should not be assumed that a datasheet theta- $_{JA}$  value (for a single device on an standard test board) would predict the temperature rise of the device on a final application board. Performance will be affected by variations in board surface metal coverage, number of buried planes, heat-spreading area around each component, other surrounding "hot" devices, etc. The main differences between test and application boards should be understood before using datasheet theta $_{JA}$ 's to estimate T<sub>J</sub> of devices on application boards.

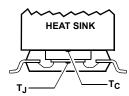

# Theta-JC

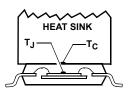

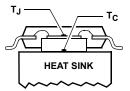

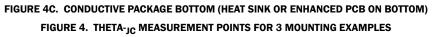

FIGURE 4A. CONDUCTIVE PACKAGE TOP (HEAT SINK ON TOP)-

#### DEFINITION: $\Theta_{JC} = (T_J - T_C / P)$

Where:

$\theta_{JC}$  = Thermal resistance junction-to-case, °C/W

$T_J$  = Die junction temperature, °C

T<sub>C</sub> = Package case temperature, °C

P = Power dissipated by device, watts

#### **USAGE FORMULA:**

With  $\theta_{\text{JC}},$  T\_C and P known, then:

$T_{J} = T_{C} + (\theta_{JC} * P)$

#### KEY POINTS FOR $\mathcal{O}_{JC}$ :

- Indicates ease of heat flow between die junction and either package top or bottom.

- Measured with package top or bottom surface mounted to a heatsink. If not obvious, the surface used should be reported.

- Datasheet  $\theta_{\text{JC}}$  values are intended for:

- Performance comparison of one packaged device against another (lower values indicate better performance).

- Calculation of T<sub>J</sub> rise above T<sub>C</sub>.

- Calculating a larger overall thermal resistance of which  $\theta_{\text{JC}}$  as a part.

- Generally relevant to:

- Plastic packages with top or bottom mounted to an external heatsink.

- Plastic packages with bottom e-pad soldered to a thermally enhanced PCB.

- Ceramic and metal cased packages with a surface mounted to an external heatsink or thermally enhanced PCB.

- Dependent mainly on thickness, area, and conductivity of device materials in the  $\theta_{\text{JC}}$  heat flow path.

#### **OTHER APPLICABLE FORMULA'S:**

For packages with a surface adhered or soldered to an epoxy-glass PCB, the total  $\theta_{\text{JA}}$  is:

$$\theta_{JA} = \theta_{JC} + \theta_{CA}$$

Note the  $\theta_{\text{CA}}$  term is the case-to-ambient resistance, which is controlled by the PCB design.

For packages with a surface adhered or soldered to a heatsink, the total  $\theta_{J\!A}$  through this path is:

$$\theta_{JA} = \theta_{JC} + \theta_{CS} + \theta_{SA}$$

Note the  $\theta_{\text{CS}}$  (case-to-sink) term is controlled by the thermal grease or mounting pad between the package and heatsink. The  $\theta_{\text{SA}}$  (sink-to-ambient) term is obtained from the heatsink manufacturer's datasheet.

# Theta-<sub>JB</sub>

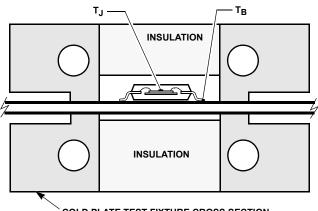

COLD PLATE TEST FIXTURE CROSS SECTION FIGURE 5. THETA-JB MEASUREMENT POINTS

### **DEFINITION:** $\Theta_{JB} = (T_J - T_B / P)$

Where:

$\theta_{IB}$  = Thermal resistance junction-to-board, °C/W

$T_J$  = Die junction temperature, °C

T<sub>B</sub> = Board temperature adjacent to package, °C

P = Power dissipated by device, watts

#### **USAGE FORMULA**

With  $\theta_{JB},$  T\_B and P known, then:

$T_{J} = T_{B} + (\theta_{JB} * P)$

#### KEY POINTS FOR $\Theta_{JB}$ :

- Datasheet  $\theta_{\text{JB}}$  values are intended for:

- Performance comparison of one packaged device against another.

- Calculation of  $T_{J}$  rise above Tb for devices on application PCBs.

- Calculating a larger overall thermal resistance of which  $\theta_{\text{JB}}$  is a part.

- Uses ring style cold plate to drive vast majority of heat into test board.

- Since  $\theta_{JB}$  is dependent on test board design, it's standardized on the style with 2 buried planes (1S2P or 1S2P+vias as applicable).

- Similar to  $\Psi_{JB},$  but  $\theta_{JB}$  will have a larger value (see  $\Psi_{JB}$  notes below).

### **ANOTHER APPLICABLE FORMULA:**

With the package mounted on an epoxy-glass PCB, the total thermal resistance is:

$\theta_{JA} = \theta_{JB} + \theta_{BA}$

Note the  $\theta_{\text{BA}}$  term is the board-to-ambient resistance, which is controlled by the PCB design.

#### Psi-<sub>JB</sub>

FIGURE 6. PSI-JB MEASUREMENT POINTS

### **DEFINITION:** $\Psi_{JB} = (T_J - T_B) / P$

Where:

$\Psi_{JB}$  (Psi-<sub>JB</sub>) = Junction-to-board characterization parameter, °C/W

T<sub>J</sub> = Die junction temperature, °C

T<sub>B</sub> = Board temperature adjacent to package, °C

P = Power dissipated by device, watts

#### USAGE

Knowing  $\Psi_{JB}$ , to obtain  $T_J$  of a device powered-up on an application PCB:

1) Measure the board temperature near the edge of the package, on a copper trace at the center of one side.

2) Determine the power dissipated by the device.

3) Calculate:  $T_J = T_B + (\Psi_{JB} * P)$

#### **KEY POINTS FOR** *Y***JB**

- · A characterization parameter, not a "true" thermal resistance.

- Intended for calculation of  $T_J$  rise above  $T_B$  for devices on application PCB's.

- + Optional test in JESD51-6  $\theta_{\text{JA}}$  standard.

- Generally measured using 1S2P or 1S2P+vias board.

- · Measured using setup same as for a theta-JA test.

- Similar to  $\theta_{JB},$  but  $\mathscr{\Psi}_{JB}$  will have a slightly smaller value.

#### $\Psi_{JB}$ VS $\mathcal{O}_{JB}$

The Greek letter "psi" is used to distinguish  $\Psi_{JB}$  from  $\theta_{JB}$  since not all heat is actually flowing between the points of temperature measurement (i.e., junction and board) like with  $\theta_{JB}$ . This is because the setup of the  $\Psi_{JB}$  test does not force all heat flow into the board like the  $\theta_{JB}$  ring style cold plate.  $\Psi_{JB}$  is not a "true" thermal resistance for this reason.

With  $\Psi_{JB}$  testing a certain amount of device heat can dissipate from the package top and sides; therefore  $\Psi JB$  will always have a smaller value than  $\theta_{JB}$ . It turns out however, that for most common small to medium sized packages, the two values will be similar - generally within 15%. Thus,  $\Psi_{JB}$  is sometimes reported in lieu of  $\theta_{JB}$ .

#### **BOARD TEMPERATURE MEASUREMENT**

When measuring  $T_B$  in an application, care should be taken to prevent accidental cooling of the thermocouple bead. We recommend use of a small ~40 gauge (3.15mil diameter) thermocouple soldered to the board trace. Cover the bead with a thermally conductive epoxy and route the wires along the board surface. This is important towards preventing "too cool"  $T_B$ measurements, which would lead to the calculated  $T_J$  also being too cool.

IR spot tools are not recommended for the  $T_B$  measurement. Even those with smaller spot (measurement area) diameters still typically have a ~100mil+ spot. This is much larger than the copper trace to be measured. If the IR tool emissivity is factory-fixed, it's generally ~0.95 which is accurate for epoxy-glass surfaces alone. But bare copper or copper covered with thin solder mask can have much lower emissivity. These issues make accurate measurement of the copper trace temperature difficult using IR spot tools.

### Psi-<sub>JT</sub>

FIGURE 7. PSI-JT MEASUREMENT POINTS

#### **DEFINITION:** $\Psi_{JT} = (T_J - T_T) / P$

Where:

$\Psi_{JT}$  (Psi-<sub>JT</sub>) = Junction-to-top (of package) characterization parameter, °C/W

$T_J$  = Die junction temperature, °C

T<sub>T</sub> = Top of package temperature at center, °C

P = Power dissipated by device, watts

#### USAGE

Knowing  $\Psi_{JT}$ , to obtain T<sub>J</sub> of a device powered-up on the application PCB:

1) Measure the top-of-package temperature at the center.

2) Determine the power dissipated by the device.

3) Calculate:  $T_J = T_T + (\Psi_{JT} * P)$

#### KEY POINTS FOR $\Psi_{\text{JT}}$

- A characterization parameter, not a "true" thermal resistance.

- Intended for calculation of T<sub>J</sub> rise above T<sub>T</sub> for devices on application PCBs.

- Optional test in JESD51-2A and JESD51-6  $\theta_{\text{JA}}$  standards.

- For plastic packages, depends mainly on thickness and thermal conductivity of plastic mold compound above die, and

die size  $(\Psi_{JT}$  increases as die size decreases-mainly affects smaller devices).

• Rises with increasing airflow, the speed of which is reported with  $\Psi_{\text{IT}}$  if not measured under natural convection.

#### $\Psi_{\mathrm{JT}}$ vs $\Theta_{\mathrm{JC}}$

It's worth noting that  $\Psi_{JT}$  is not the same as  $\theta_{JC}$ , which only applies when the package surface is mounted onto a heatsink. The test methods and resulting values are quite different. In fact, if  $\Psi_{JT}$  and  $\theta_{JC}$  (at the top surface) are measured on the same package,  $\Psi_{JT}$  will generally be much smaller than  $\theta_{JC}$ . The Greek letter "psi" is used to help clearly distinguish  $\Psi_{JT}$  from the  $\theta_{JC}$  thermal resistance.

#### TYPICAL PLASTIC PACKAGE *Y*JT VALUES

Under natural convection,  $\Psi_{JT}$  for a plastic package is generally a relatively low value. This means that  $T_J$  is usually just a little hotter than the top of the package,  $T_T$ . The die is physically separated from the top surface by only a thin region of plastic mold compound. So unless the top is forcibly cooled by significant airflow there will be very little delta-T between them.

The natural convection  $\Psi_{JT}$  value is often less than 1 °C/W for thin packages. For packages that are progressively thicker and/or have smaller body, die, or die paddle size, the value increases into the roughly 2 - 10+ °C/W range. These relatively low values suggest that knowing  $\Psi_{JT}$  accurately is often not essential. T<sub>T</sub> measurements are often so low that using any reasonable  $\Psi_{JT}$  value in the temperature rise calculations results in T<sub>J</sub> estimates within temperature limits.

#### TOP OF PACKAGE TEMPERATURE MEASUREMENT

When measuring  $T_T$  in an application, care should be taken to prevent accidental cooling of the package surface during the act of measuring it. This is especially important with a plastic package due to the low thermal conductivity of the surface.

We recommend use of a small ~40 gauge (3.15mil diameter) thermocouple. The bead and thermocouple wires should touch the top of the package and be covered with a minimal amount of thermally conductive epoxy. The wires should be routed closely along the package and board surfaces to help prevent cooling of the bead due to heat loss into the leads. This is important towards preventing "too cool" T<sub>T</sub> measurements, which would lead to the calculated T<sub>1</sub> also being too cool.

An IR spot method should be utilized only when using a tool with a small enough spot area to acquire the true top center "hot spot". Note the emissivity of plastic mold compound is ~0.95, which fortunately matches the common factory-fixed value found in some IR tools.

Many so-called "small spot size" tools still have a measurement area of ~100+ mils at "zero" distance of the tool from the surface. This spot area is too big for many smaller packages and likely would result in cooler readings than the small thermocouple method. The accuracy depends on the IR spot size in relation to the size of the device being measured.

For a thin package with a die size larger than ~125 mils square for example, the temperature will be relatively uniform across a ~100 mil IR spot. A reasonably accurate top center reading

#### Package Information

should be obtained. But for packages that are thicker or have smaller die sizes, the temperature distribution within the IR spot area may be very nonuniform. Cooler temperature bands surrounding the true hot spot will be averaged into the readout. In such cases, it's prudent to add at least a few degrees to the IR readout to better estimate the true top center temperature. If in doubt about the IR spot size or measurement accuracy, revert to the small thermocouple method.

# Additional PCB Design Considerations

#### **Spread the Heat Around... and Down**

To help understand the influence of the PCB on thermal performance, it's interesting to compare the "effective" thermal conductivity ("k") for the composite PCB after adding buried copper planes. These "effective" values are based on the parallel resistance formula for the "x" and "y" direction, and series formula for "z". The calculations use the thickness and conductivity of the FR-4 and the copper planes.

TABLE 2. COPPER PLANE EFFECTS

|                  | PCB EFFECTIVE THERMAL<br>CONDUCTIVITY, W/m-K |       |  |

|------------------|----------------------------------------------|-------|--|

| 1oz Cu PLANES    | x AND y                                      | Z     |  |

| NONE (FR-4 ONLY) | 0.87                                         | 0.310 |  |

| ONE PLANE (1P)   | 9.4                                          | 0.317 |  |

| TWO PLANES (2P)  | 18                                           | 0.324 |  |

The in-plane (x and y) value rises from 0.87 W/m-K for "FR-4 only" all the way up to 18 W/m-K with 2 planes. This ~2000% increase in the effective in-plane "k" value generally results in a ~20-40+% reduction in datasheet Theta-<sub>JA</sub> values.

Even as the in-plane "k" is increased 20x, the through-plane (z) value is nearly unchanged. Realizing this negligible z-direction effect is important when designing with a package with a bottom exposed metal pad.

For these e-pad packages, there's another PCB design option that takes better advantage of the high conductivity path through the bottom. This involves dropping thermal vias down beneath the e-pad to one or more of the buried planes to help overcome FR-4's poor thermal conductivity.

The closer thermal coupling of the device to the buried planes results in more efficient heat spreading and more uniform temperature distribution across the PCB. The larger effective cooling area around the device also allows its heat to be more efficiently dissipated off the board surfaces by convection and radiation. The overall cooling effect can be significant, especially in newer smaller exposed-pad packages where not much heat spreading can occur in the package itself.

### Think "Thermal", not "Electrical"

Thermal and electrical systems have analogies that many engineers draw upon, but there's an important difference that might make you want to think about thermal a little differently.

The ratio of high versus low conductivity items in the thermal world is typically on the order of hundred's-to-one, while in the electrical world it's trillion's-to-one or more. Because of this, an engineer's thermal "gut feel" may not be quite right when it's based mainly on electrical engineering experiences.

Heat doesn't tend to flow down metal traces from points "A" to "B" with little loss like electrical current. Rather, the heat flows much more easily into surrounding materials or the air. All this "leakage" of heat is generally nothing to complain about since we're usually trying to increase it even more, but it does add a good bit of complexity to the task of predicting how much heat is flowing where.

To nail down the required accuracy, simulation tools such as 3D FEA (Finite Element Analysis) and CFD (Computational Fluid Dynamics) are used by the industry to help take all the variables into account.

# **Appendix A**

# JESD51-X

Thermal Test Board Design Summary (See JEDEC Specs for Full Details)

# JESD51-3

<u>Low Effective</u> Thermal Conductivity Test Board for Leaded Surface Mount Packages

- Covers 1S0P boards.

- For leaded and leadless surface mount packages.

- Not for through-hole or BGA or WLCSP.

- Top surface copper traces only:

- Fanout: to at least 25mm from package.

- Width: 0.254mm (10 mils) ±10%

- Thickness: 2oz (0.070mm ±20%), typically 1oz clad + 1oz plated.

- Board thickness: 1.57mm (62 mils).

- Board size:

| PACKAGE LENGTH (L) | BOARD SIZE |

|--------------------|------------|

| Less than 27mm     | 3 x 4.5"   |

| 27 to 48mm         | 4 x 4.5"   |

### JESD51-7

#### <u>High Effective</u> Thermal Conductivity Test Board for Leaded Surface Mount Packages

- Covers 1S2P boards.

- For leaded and leadless surface mount packages.

- · Not for through-hole or BGA or WLCSP.

- Top surface trace layout: same as for 51-3.

- Adds 2 buried planes for "high effective" x-y conductivity.

- 1oz thick (0.035mm +0/-20%) each.

- Z-direction conductivity of PCB still poor.

- Board thickness: 1.60mm (63 mils).

- · Board and buried planes sizes:

| PACKAGE LENGTH (L) | BOARD SIZE | PLANE SIZE   |

|--------------------|------------|--------------|

| L ≤ 27mm           | 3 x 4.5"   | 2.92 x 2.92" |

| 27 < L ≤48mm       | 4 x 4.5"   | 3.92 x 3.92" |

### JESD51-5

# Extension of Thermal Test Board Standards for Packages with Direct Thermal Attachment Mechanisms

- Covers "1S2P+Vias" boards.

- For plastic leaded and leadless surface mount packages with an exposed metal pad on the package underside.

- For Ceramic/Metal packages when the base, whether ceramic or metal finish, is adhered or soldered to the PCB (no air gap).

- Not for through-hole or BGA or WLCSP.

- Defines PCB attach pad (thermal land) geometry to match package's mounting surface.

- Defines thermal vias (added to 1S2P) to make 1S2P+Vias board.

- 1.2 x 1.2mm array under attach pad.

- 0.3mm diameter.

- 0.025mm min Cu in via barrel.

- Vias contact upper buried plane only.

### JESD51-9

#### Test Boards for Area Array Surface Mount Package Thermal Measurements

- · Covers all 3 board types:

- 1S0P, 1S2P, 1S2P+vias

- For area array packages (e.g., BGA, WLCSP) only.

- Top surface traces:

- Fanout at least 25mm from package.

- Trace thickness and width:

| BALL PITCH    | TRACE Tkn          | TRACE WIDTH             |

|---------------|--------------------|-------------------------|

| >0.5mm        | 70µm (2oz) ± 20%   | 36 to 44% of ball pitch |

| 0.5mm or Less | 50µm (1.5oz) ± 20% | 45 to 55% of ball pitch |

- 2 Buried Planes (1S2P and 1S2P+Vias only):

- 1 oz thick (0.035mm +0/-20%) each

- Board thickness: 1.60mm (63 mils).

- · Board and buried planes sizes:

| PACKAGE LENGTH (L) | BOARD SIZE | PLANE SIZE (ONLY 1S2P<br>AND 1S2P + Vias) |

|--------------------|------------|-------------------------------------------|

| L ≤ 40mm           | 4 x 4.5"   | 3.92 x 3.92"                              |

| 40 < L ≤ 65mm      | 5 x 5.5"   | 4.92 x 4.92"                              |

| 65 < L ≤ 90mm      | 6 x 6.5"   | 5.92 x 5.92"                              |

#### **Package Information**

- Thermal vias (1S2P + Vias board only):

- Only for packages with thermal balls.

- Via diameter: Varies by ball pitch.

- 0.018mm min Cu in via barrel.

- Vias contact upper buried plane only.

### **JESD51-10**

#### Test Boards for Through-hole Perimeter Leaded Package Thermal Measurements

- Covers 1SOP and 1S2P board types.

- For through-hole perimeter leaded packages (e.g., DIP, SIP) only.

- Top surface copper traces:

- Fanout: to at least 25mm from package.

- Width: 0.25mm ±10%

- Thickness: 2oz (0.070mm ±20%), typically 1oz clad + 1oz plated.

- 2 Buried planes (for 1S2P board only):

- 1oz thick (0.035mm +0/-20%) each

- Isolation gaps in both buried planes for pin through-holes.

- Thermal pins directly attached to die pad are to be connected to top buried plane.

- Board thickness: 1.60mm (63 mils).

- · Board and buried planes sizes:

| PACKAGE LENGTH (L) | BOARD SIZE | PLANE SIZE (ONLY 1S2P<br>AND 1S2P + Vias) |

|--------------------|------------|-------------------------------------------|

| L ≤ 40mm           | 4 x 4.5"   | 3.92 x 3.92"                              |

| 40 < L ≤ 65mm      | 5 x 5.5"   | 4.92 x 4.92"                              |

| 65 < L ≤ 90mm      | 6 x 6.5"   | 5.92 x 5.92"                              |

#### JESD51-11

#### Test Boards for Through-hole Area Array Leaded Package Thermal Measurements

- Covers 1SOP and 1S2P board types.

- For through-hole area array leaded packages (e.g., PGA) only.

- Top surface copper traces:

- Fanout: to at least 25mm from package.

- Width: 36 to 44% of pin pitch.

- Thickness: 2oz (0.070mm ±20%), typically 1oz clad + 1oz plated.

- 2 Buried planes (for 1S2P board only):

- 1oz thick (0.035mm +0/-20%) each.

- Isolation gaps in both buried planes for pin through-holes.

- Board Thickness: 1.60mm (63 mils).

- · Board and buried planes sizes:

| PACKAGE LENGTH (L) | BOARD SIZE | PLANE SIZE<br>(1S2P ONLY) |

|--------------------|------------|---------------------------|

| L ≤ 40mm           | 4 x 4.5"   | 3.92 x 3.92"              |

| 40 < L ≤ 65mm      | 5 x 5.5"   | 4.92 x 4.92"              |

| 65 < L ≤ 90mm      | 6 x 6.5"   | 5.92 x 5.92"              |

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Renesas Electronics Corporation**

http://www.renesas.com

SALES OFFICES Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338