-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

9DB633

circle有效可提供样片6-output 3.3 V PCIe Gen1-2-3 Zero Delay / Fanout Buffer

概览

简介

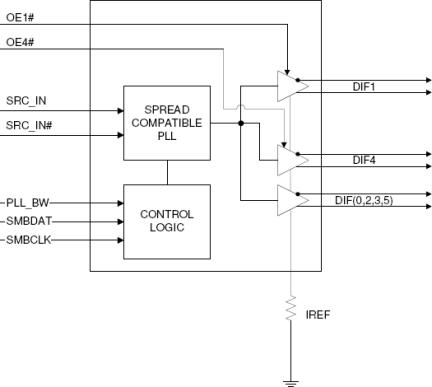

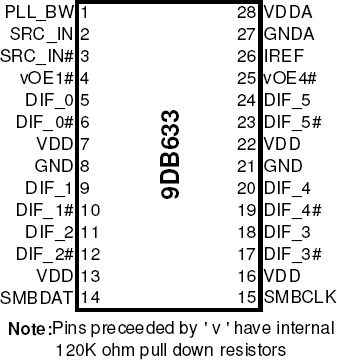

The 9DB633 zero-delay buffer supports PCIe Gen3 requirements, while being backwards compatible to PCIe Gen2 and Gen1. The 9DB633 is driven by a differential SRC output pair from an IDT 932S421 or 932SQ420 or equivalent main clock generator. It attenuates jitter on the input clock and has a selectable PLL bandwidth to maximize performance in systems with or without Spread-Spectrum clocking. An SMBus interface allows control of the PLL bandwidth and bypass options, while 2 clock request (OE#) pins make the 9DB633 suitable for Express Card applications.

特性

- 6 - 0.7 V current mode differential HCSL output pairs

- Cycle-to-cycle jitter < 50 ps

- Output-to-output skew < 50 ps

- PCIe Gen3 phase jitter < 1.0 ps RMS

- OE# pins/Suitable for Express Card applications

- PLL or bypass mode/PLL can dejitter incoming clock

- Selectable PLL bandwidth/minimizes jitter peaking in downstream PLL's

- Spread Spectrum Compatible/tracks spreading input clock for low EMI

- SMBus Interface/unused outputs can be disabled

产品对比

应用

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

产品选择

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product