-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

82V3398

circle有效可提供样片Synchronous Ethernet WAN PLL

跳转至页面部分:

arrow_drop_down

概览

简介

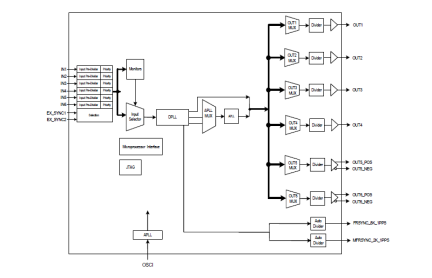

The 82V3398 is an integrated, single-chip solution for the Synchronous Equipment Timing Source for Stratum 3, 4E, 4, SMC, EECOption1, EEC-Option2 clocks in SONET / SDH / Synchronous Ethernet equipment, DWDM and Wireless base station. The device consists of a high quality and configurable DPLL to provide system clock for node timing synchronization within a SONET /SDH / Synchronous Ethernet network.

特性

- Integrated single-chip solution for Synchronous Equipment Timing Source, including Stratum 3, 4E, 4, SMC, EEC-Option 1 and EEC-Option 2 Clocks

- Hitless reference switching to minimize DPLL output phase transients

- Programmable input-to-output phase offset adjustment

- Provides 6 output clocks from 1 Hz (1PPS) to 644.53125 MHz

- Provides 6 input clocks from 1 Hz (1PPS) to 625 MHz

- Internal DCO controlled by an external processor for IEEE-1588 clock generation

- Free- Run, Locked and Holdover modes

- Automatic hitless selected input clock switch on clock failure

- 2 kHz, 4 kHz, 8 kHz, or 1PPS frame sync input, 2 kHz, 8 kHz, or 1PPS frame sync output

- Output clocks for BITS, GPS, 3G, GSM, etc.

- PECL/LVDS and CMOS input/output technologies

- Master/Slave feature for system protection against single chip failure

产品对比

应用

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

产品选择

请登录或注册购买

登录以添加到购物车

Processing table

Pkg. Type |

Lead Count (#) |

Pb (Lead) Free |

Carrier Type |

Price (USD) | 1ku |

购买 / 样片 |

|

|---|---|---|---|---|---|---|

| 器件号 | ||||||

| VFQFPN | 72 | Yes | Tray | 52.15 | 获取样片, | |

| VFQFPN | 72 | Yes | Reel |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product