# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# V850E/RS1<sup>™</sup>

# 32-/16-bit Single-Chip Microcontroller with CAN Interface

Hardware

$\mu$ PD70F3402,  $\mu$ PD70F3403,  $\mu$ PD70F3403A

Document No. U16702EE3V2UD00 Date Published April 2006

© NEC Electronics Corporation 2006 Printed in Germany

## NOTES FOR CMOS DEVICES —

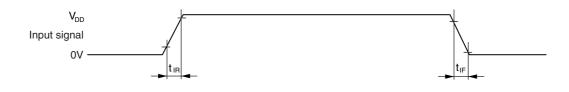

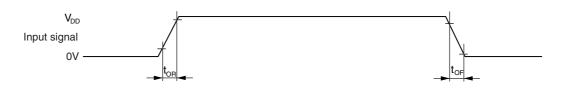

## (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

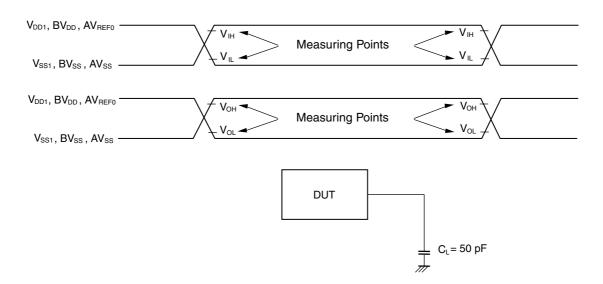

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (MAX) and  $V_{IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to V<sub>DD</sub> or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### **③** PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

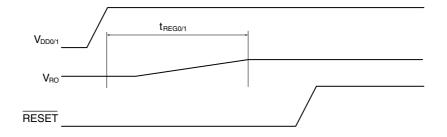

#### **④** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

# (5) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

All (other) product, brand, or trade names used in this pamphlet are the trademarks or registered trademarks of their respective owners.

Product specifications are subject to change without notice. To ensure that you have the latest product data, please contact your local NEC Electronics sales office.

- The information in this document is current as of April, 2006. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

# For further information, please contact:

#### NEC Electronics Corporation

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111 http://www.necel.com/

#### [America]

#### NEC Electronics America, Inc.

2880 Scott Blvd. Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782 http://www.am.necel.com/

#### [Europe]

#### NEC Electronics (Europe) GmbH

Arcadiastrasse 10 40472 Düsseldorf, Germany Tel: 0211-65030 http://www.eu.necel.com/

#### Hanover Office

Podbielski Strasse 166 B 30177 Hannover Tel: 0 511 33 40 2-0

#### **Munich Office**

Werner-Eckert-Strasse 9 81829 München Tel: 0 89 92 10 03-0

#### Stuttgart Office

Industriestrasse 3 70565 Stuttgart Tel: 0 711 99 01 0-0

#### United Kingdom Branch Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes

MK14 6NP, U.K. Tel: 01908-691-133

#### Succursale Française

9, rue Paul Dautier, B.P. 52180 78142 Velizy-Villacoublay Cédex France Tel: 01-3067-5800

#### Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787

#### Tyskland Filial

Täby Centrum Entrance S (7th floor) 18322 Täby, Sweden Tel: 08 638 72 00

#### Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02-667541

#### **Branch The Netherlands**

Limburglaan 5 5616 HR Eindhoven The Netherlands Tel: 040 265 40 10

### [Asia & Oceania]

NEC Electronics (China) Co., Ltd 7th Floor, Quantum Plaza, No. 27 ZhiChunLu Haidian District, Beijing 100083, P.R.China TEL: 010-8235-1155 http://www.cn.necel.com/

#### NEC Electronics Shanghai Ltd.

Room 2509-2510, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai P.R. China P.C:200120 Tel: 021-5888-5400 http://www.cn.necel.com/

#### NEC Electronics Hong Kong Ltd.

12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886-9318 http://www.hk.necel.com/

#### Seoul Branch

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737

#### NEC Electronics Taiwan Ltd.

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-2719-2377

#### NEC Electronics Singapore Pte. Ltd.

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253-8311 http://www.sg.necel.com/

G05.11-1A

# Preface

| Readers      | This User's Document is tions of the V850E/RS1 | s intended for users who want to understand the func-                                                                                                              |

|--------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose      | This User's Document p                         | presents the hardware manual of V850E/RS1.                                                                                                                         |

| Organization | This system specification                      | n describes the following sections:                                                                                                                                |

|              | Pin function                                   |                                                                                                                                                                    |

|              | CPU function                                   |                                                                                                                                                                    |

|              | Internal peripheral fu                         | inction                                                                                                                                                            |

|              | Flash memory                                   |                                                                                                                                                                    |

|              | Target Electrical Spe                          | cification                                                                                                                                                         |

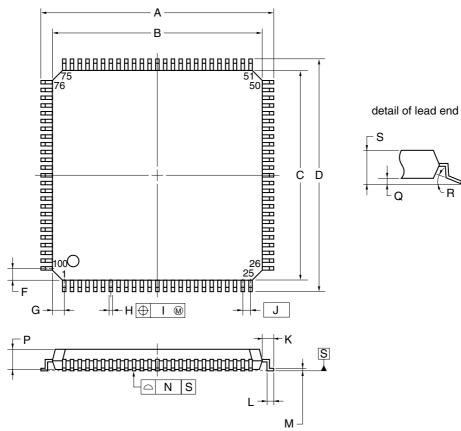

|              | Package Drawing                                |                                                                                                                                                                    |

|              | Recommended Sold                               | erina Conditions                                                                                                                                                   |

|              |                                                |                                                                                                                                                                    |

| Legend       | Symbols and notation a                         | re used as follows:                                                                                                                                                |

|              | Weight in data notation                        | : Left is high-order column, right is low order column                                                                                                             |

|              | Active low notation                            | : xxx (pin or signal name is over-scored) or /xxx (slash before signal name)                                                                                       |

|              | Memory map address:                            | : High order at high stage and low order at low stage                                                                                                              |

|              | Note                                           | : Explanation of (Note) in the text                                                                                                                                |

|              | Caution                                        | : Item deserving extra attention                                                                                                                                   |

|              | Remark                                         | : Supplementary explanation to the text                                                                                                                            |

|              | Numeric notation                               | : Binary xxxx or xxxB<br>Decimal xxxx<br>Hexadecimal xxxxH or 0x xxxx                                                                                              |

|              | Prefixes representing po                       | bwers of 2 (address space, memory capacity)<br>K (kilo): $2^{10} = 1024$<br>M (mega): $2^{20} = 1024^2 = 1,048,576$<br>G (giga): $2^{30} = 1024^3 = 1,073,741,824$ |

# **Table of Contents**

|            | Prefa          | ce                                                                 | 5     |

|------------|----------------|--------------------------------------------------------------------|-------|

| Chapter    | 1 Intro        | duction                                                            | 20    |

| Chapter    |                |                                                                    |       |

| 1.1<br>1.2 |                |                                                                    | -     |

|            |                | es                                                                 |       |

| 1.3        |                | ations                                                             |       |

| 1.4        |                | ng Information                                                     |       |

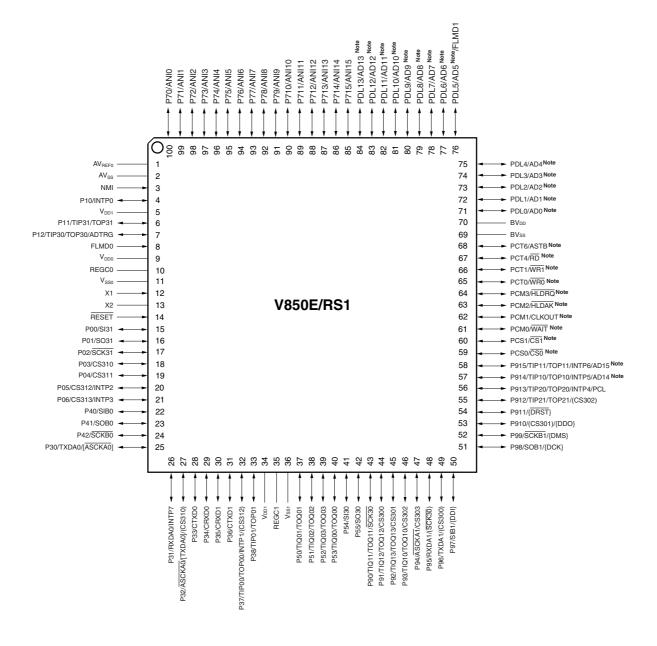

| 1.5        |                | nfiguration (Top View)                                             |       |

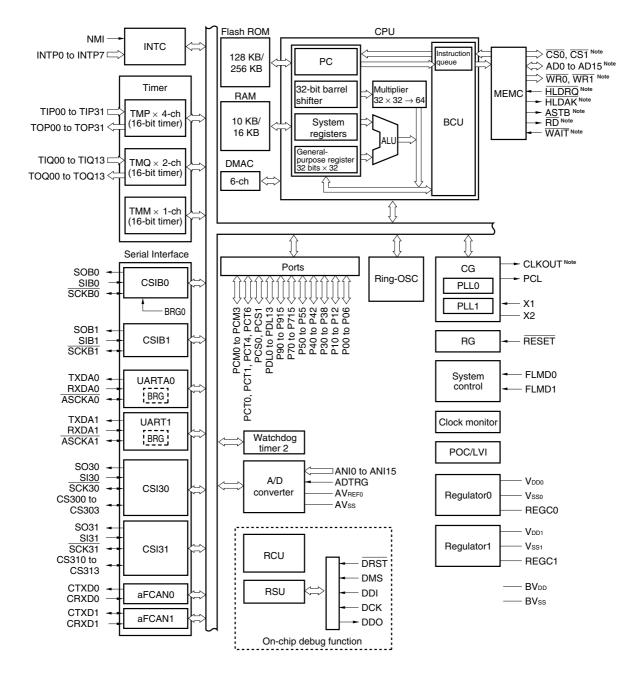

| 1.6        | -              | uration of Function Block                                          |       |

|            | 1.6.1          | Internal block diagram                                             |       |

|            | 1.6.2          | On-chip units.                                                     | 36    |

| Chapter    | 2 Pin F        | unctions                                                           | . 39  |

| . 2.1      |                | Pin Functions                                                      | 39    |

| 2.2        | Pin Sta        | tes                                                                | 44    |

| 2.3        | Descrip        | otion of Pin Functions                                             | 45    |

| 2.4        |                | Circuit Types, I/O Buffer Power Supply and Handling of Unused Pins |       |

|            |                |                                                                    |       |

| Chapter    | 3 CPU          | Function                                                           | . 61  |

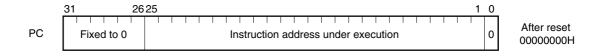

| 3.1        |                | es                                                                 | 61    |

| 3.2        | CPU Re         | egister Set                                                        | 62    |

|            | 3.2.1          | Program register set                                               |       |

|            | 3.2.2          | System register set                                                |       |

|            | 3.2.3          | Special registers                                                  |       |

| 3.3        |                | ion Modes                                                          |       |

|            | 3.3.1          | Operation modes                                                    |       |

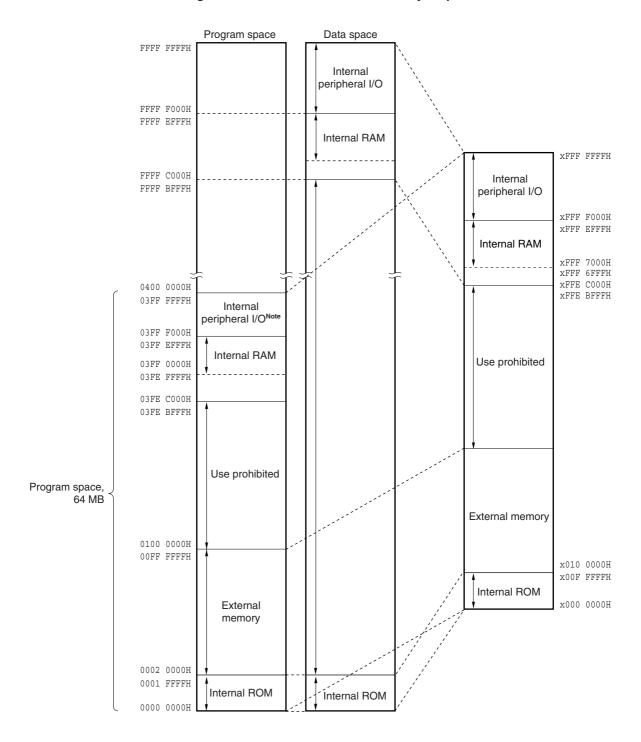

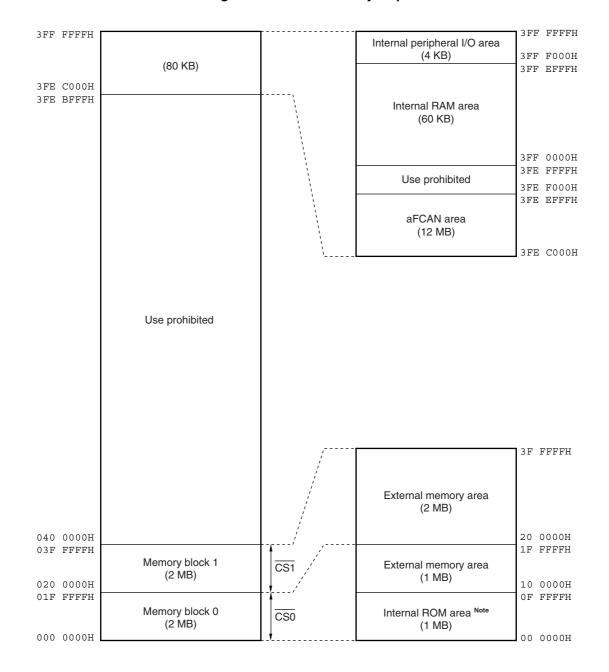

| 3.4        |                | s Space                                                            |       |

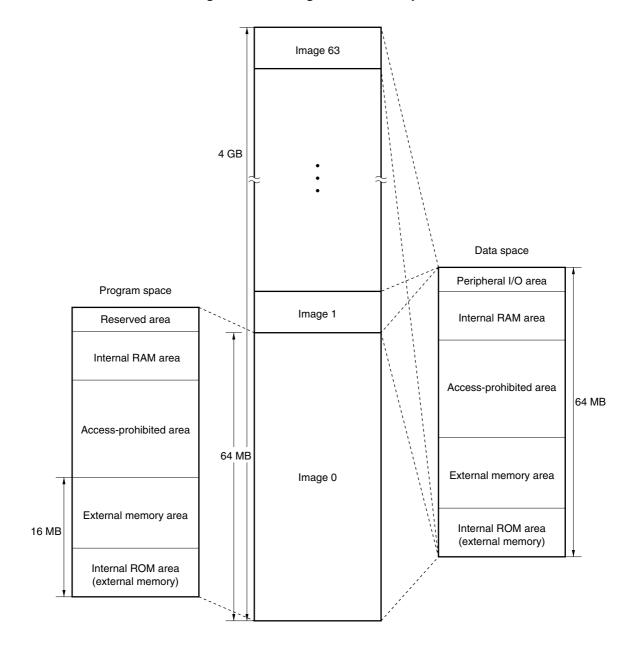

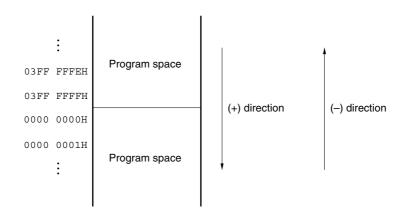

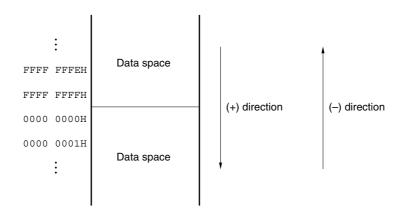

| 0.11       | 3.4.1          | CPU address space                                                  |       |

|            | 3.4.2          | Image                                                              |       |

|            | 3.4.3          | Wrap-around of CPU address space                                   |       |

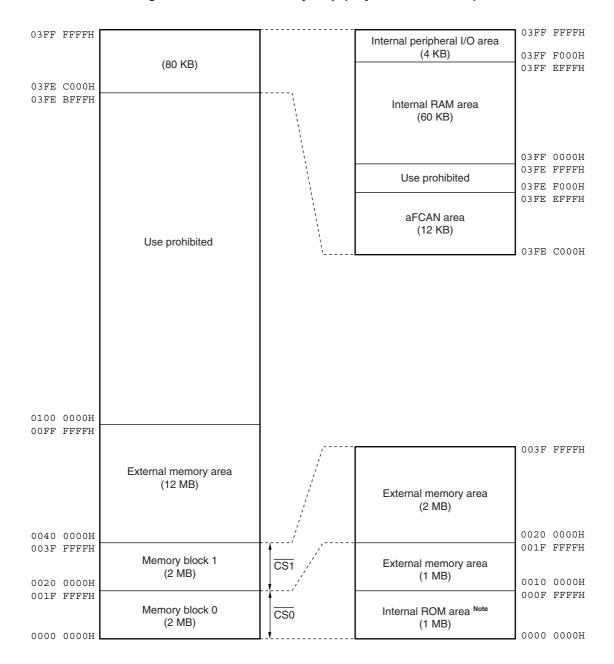

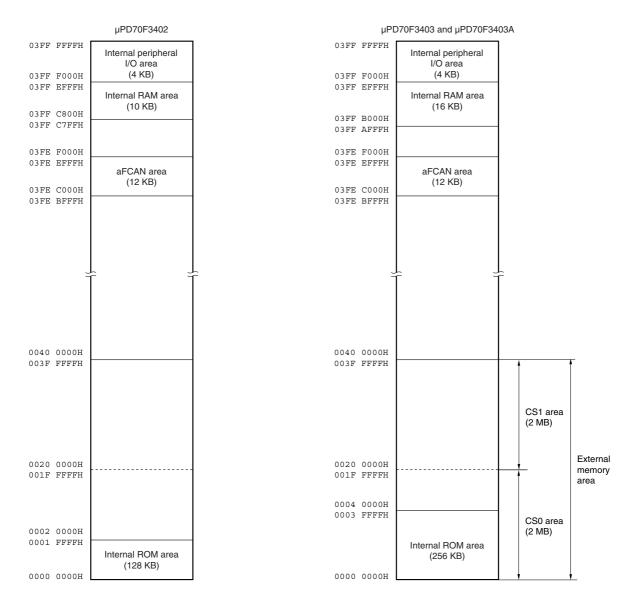

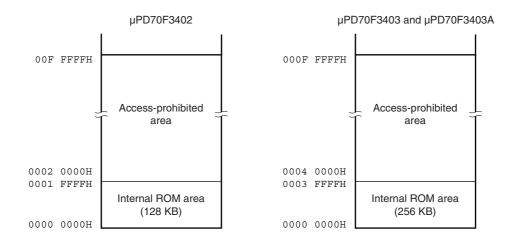

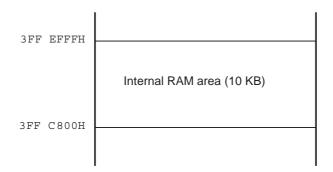

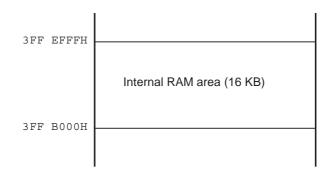

|            | 3.4.4          | Memory map.                                                        |       |

|            | 3.4.5          | Memory areas.                                                      |       |

|            | 3.4.6          | Recommended use of address space                                   |       |

|            | 3.4.7          | Cautions                                                           |       |

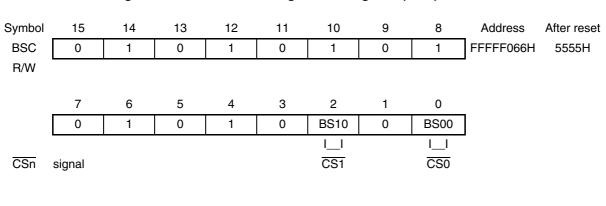

| 3.5        |                | mmable I/O Area                                                    |       |

| 0.0        | 3.5.1          | Programmable peripheral I/O control register (BPC)                 |       |

| 3.6        |                | eral I/O Registers                                                 |       |

| 0.0        | i cripit       |                                                                    |       |

| Chapter    | 4 Port I       | Functions                                                          | 105   |

| 4.1        |                | 28                                                                 |       |

| 4.1        |                | Port Configuration.                                                |       |

| 4.2        |                | onfiguration                                                       |       |

| 4.5        | 4.3.1          | Table of port configuration                                        |       |

|            | 4.3.1          | Port function swap control register                                |       |

|            | 4.3.2          | Port 0                                                             |       |

|            | 4.3.3          | Port 1                                                             |       |

|            | 4.3.4          | Port 3                                                             |       |

|            |                |                                                                    |       |

|            | 4.3.6<br>4.3.7 | Port 4 Port 5                                                      |       |

|            | -              |                                                                    |       |

|            | 4.3.8          | Port 7                                                             |       |

|            | 4.3.9          | Port 9                                                             |       |

|            | 4.3.10         | Port CM.                                                           |       |

|            | 4.3.11         | Port CS                                                            |       |

|            | 4.3.12         | Port CT                                                            |       |

|            | 4.3.13         | Port DL                                                            | . 166 |

| 4.4       | Port Fu | unction Operation                                                         | . 169 |

|-----------|---------|---------------------------------------------------------------------------|-------|

|           | 4.4.1   | Write to I/O ports.                                                       |       |

|           | 4.4.2   | Read from I/O port                                                        |       |

|           | 4.4.3   | I/O port calculation                                                      |       |

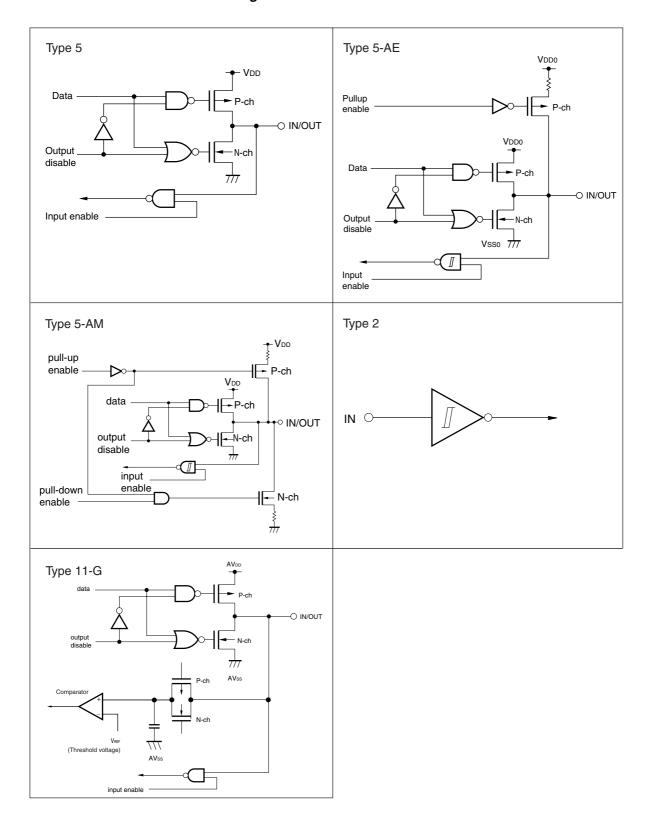

| 4.5       | Port T  | уре                                                                       |       |

| 4.6       | Port B  | lock Types                                                                | . 173 |

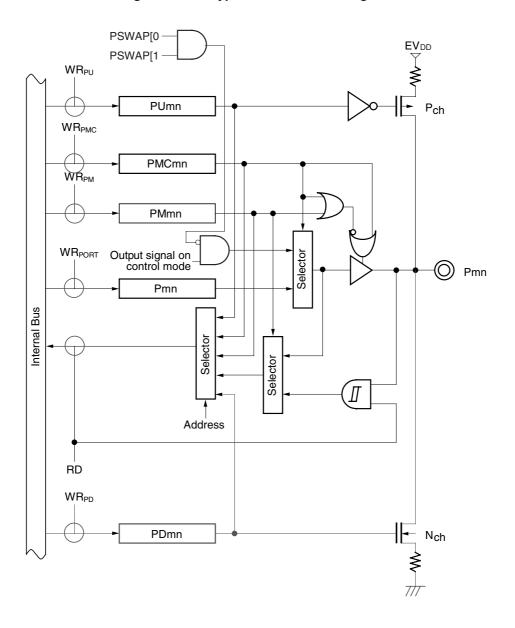

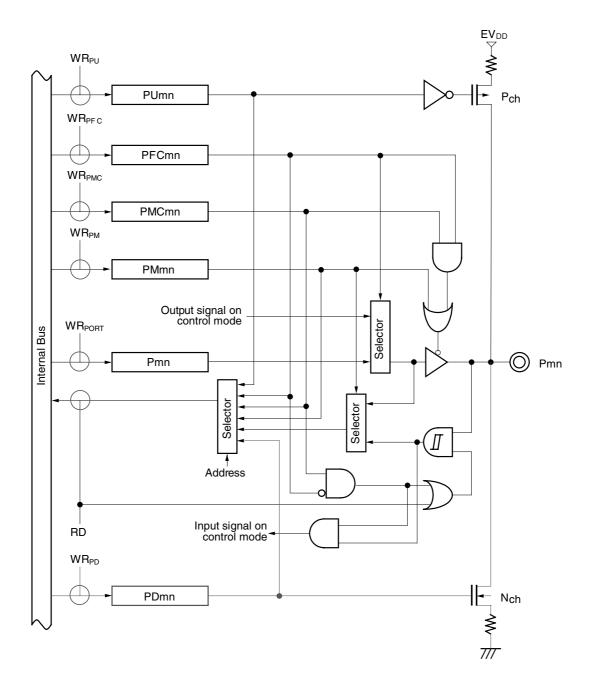

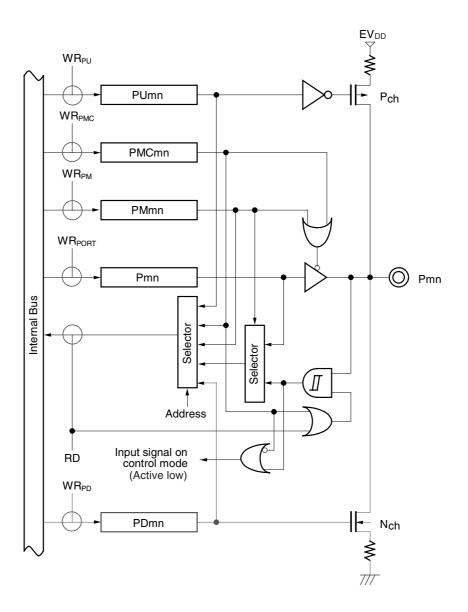

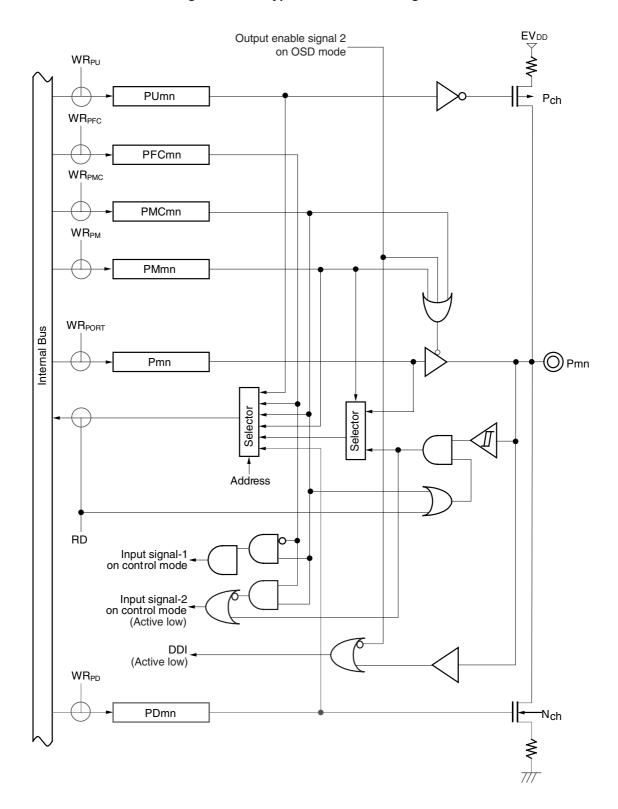

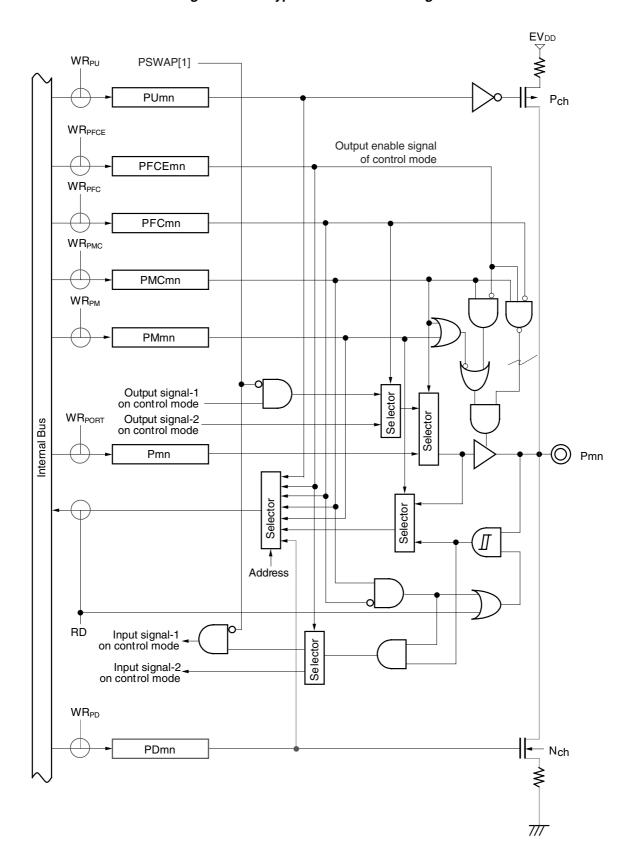

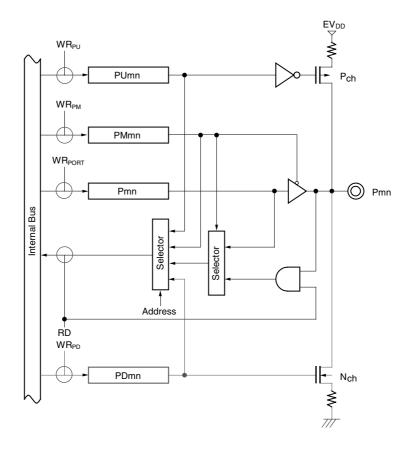

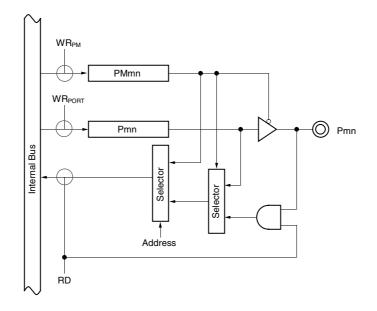

|           | 4.6.1   | Port block type E-SD1                                                     |       |

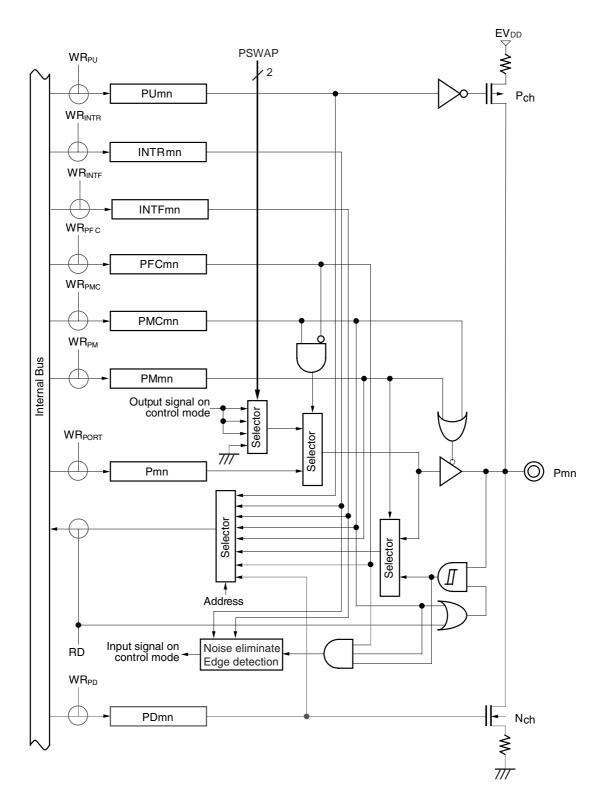

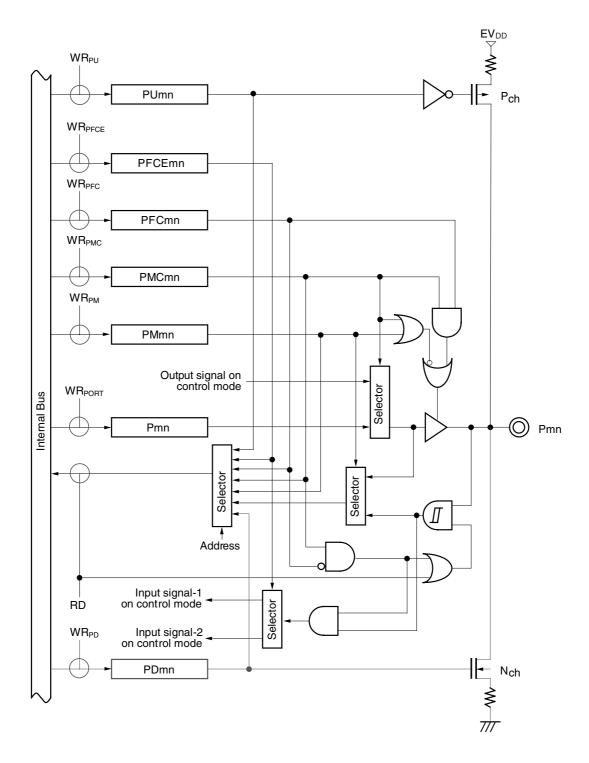

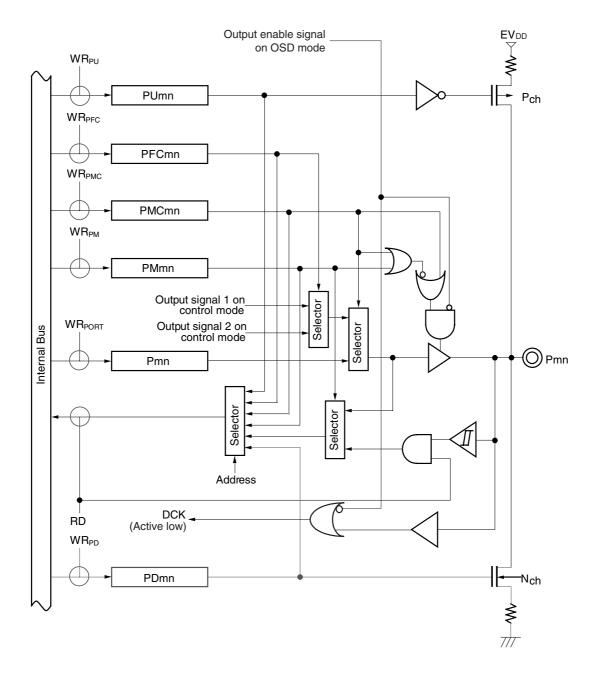

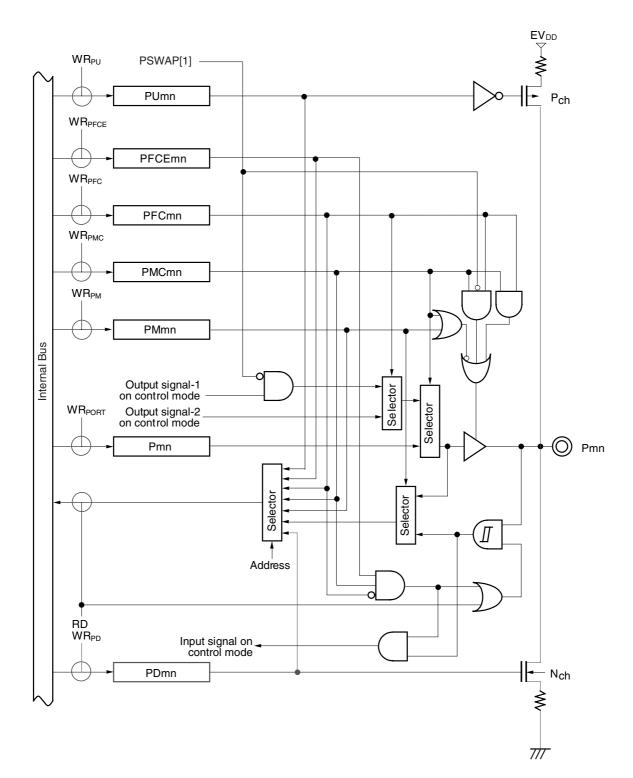

|           | 4.6.2   | Port block type E-SD4                                                     |       |

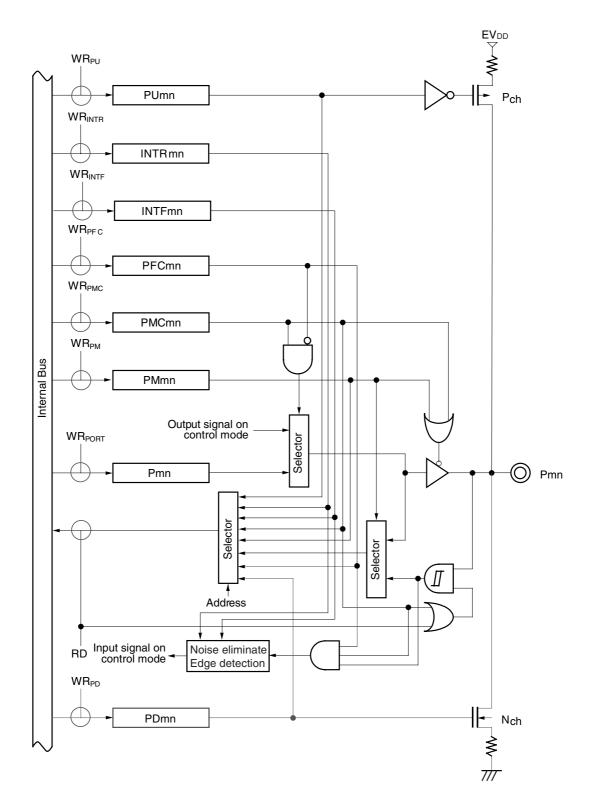

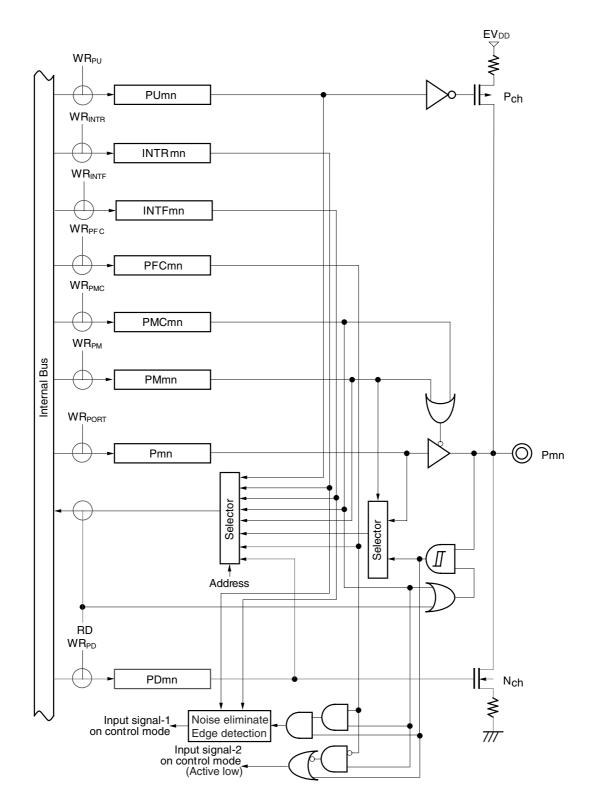

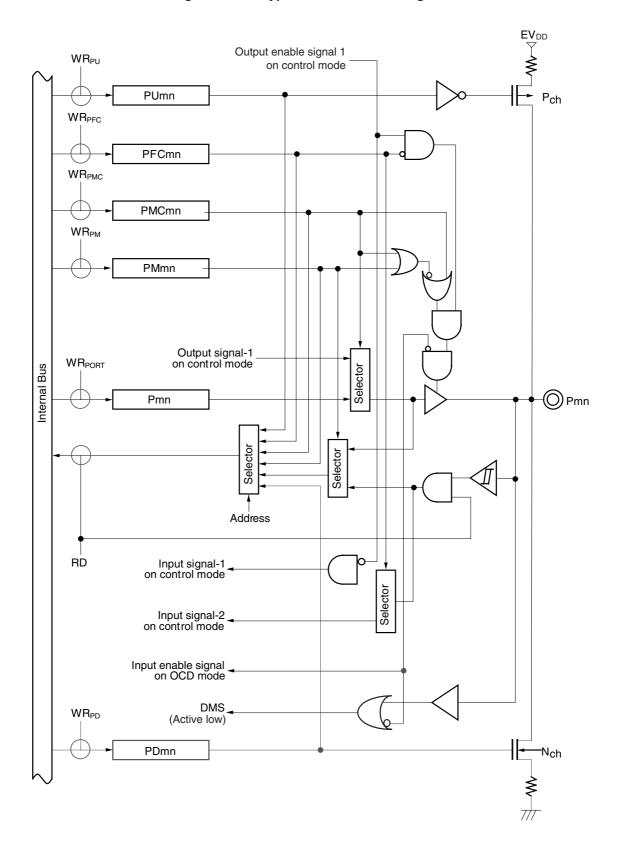

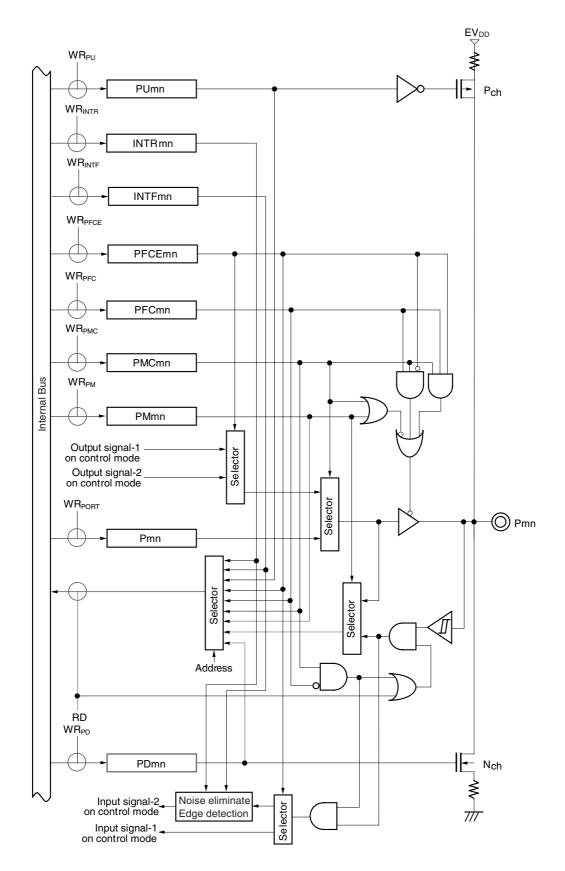

|           | 4.6.3   | Port block type E-SD7E                                                    | . 175 |

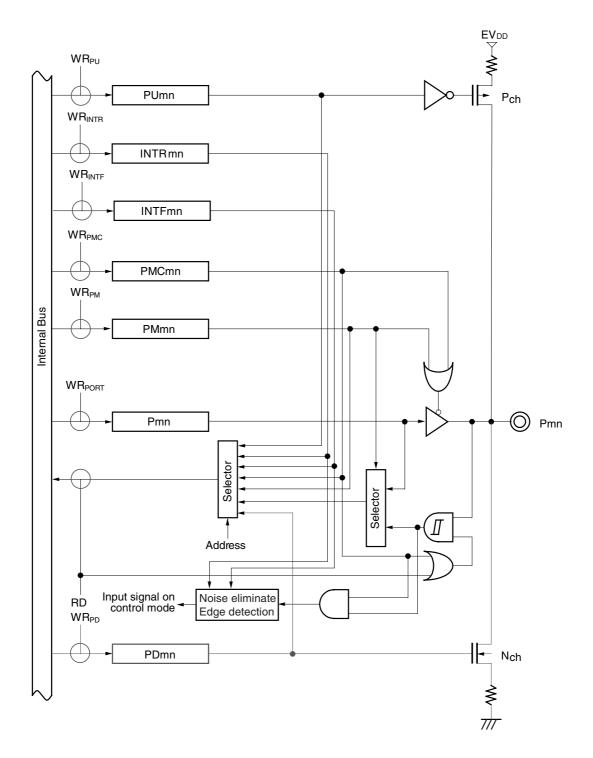

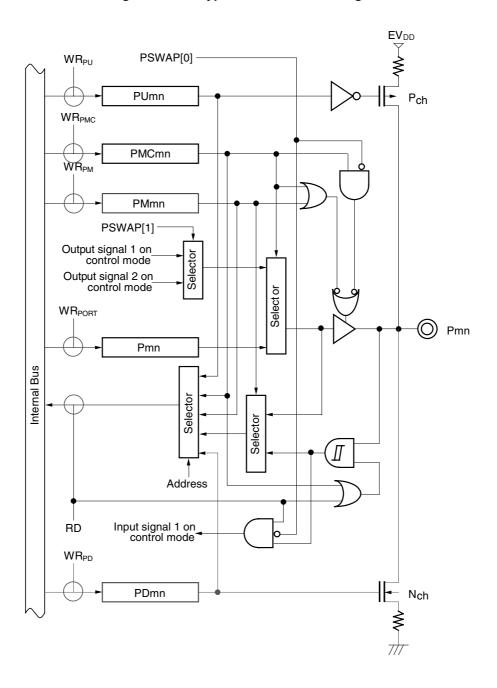

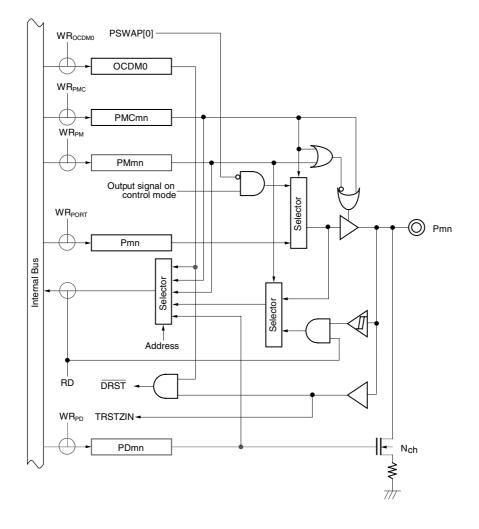

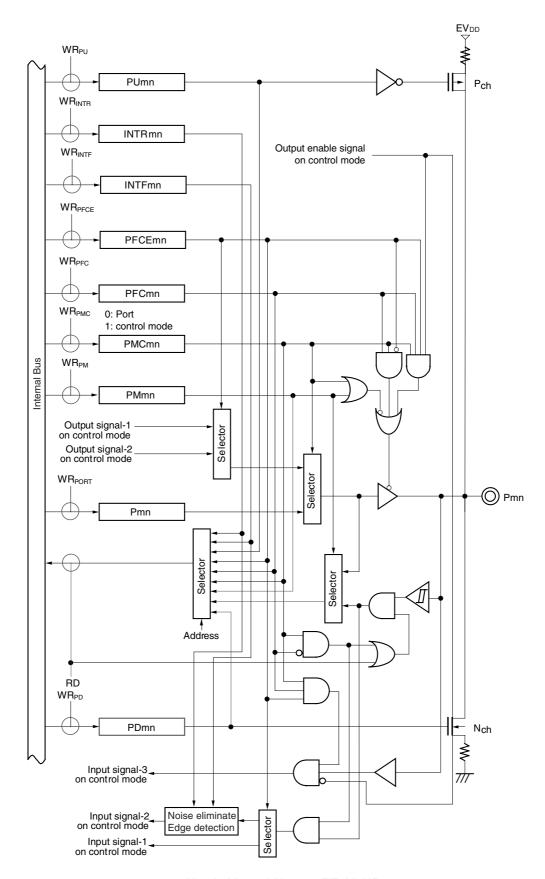

|           | 4.6.4   | Port block type E-SDW4                                                    | 176   |

|           | 4.6.5   | Port block type N-SDW7                                                    | . 177 |

|           | 4.6.6   | Port block type N-SD7                                                     | 178   |

|           | 4.6.7   | Port block type L-SD1                                                     | 179   |

|           | 4.6.8   | Port block type G-SD7                                                     | . 180 |

|           | 4.6.9   | Port block type U-SD8                                                     | . 181 |

|           | 4.6.10  | Port block type N-SD2                                                     | . 182 |

|           | 4.6.11  | Port block type E-SDW10                                                   | . 183 |

|           | 4.6.12  | Port block diagram E-SD1L                                                 | 184   |

|           | 4.6.13  | Port block type W-SDW11                                                   | . 185 |

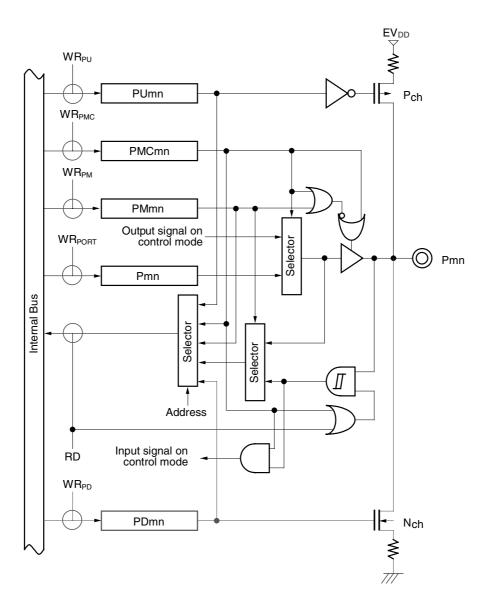

|           | 4.6.14  | Port block type E-SD7                                                     | 186   |

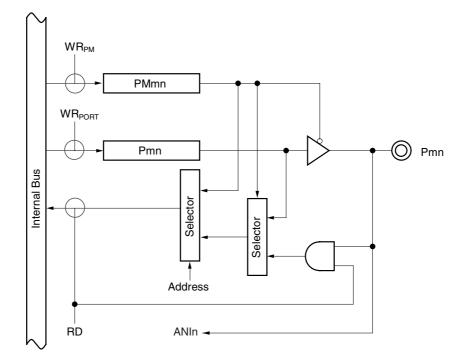

|           | 4.6.15  | Port block type A-1                                                       | 187   |

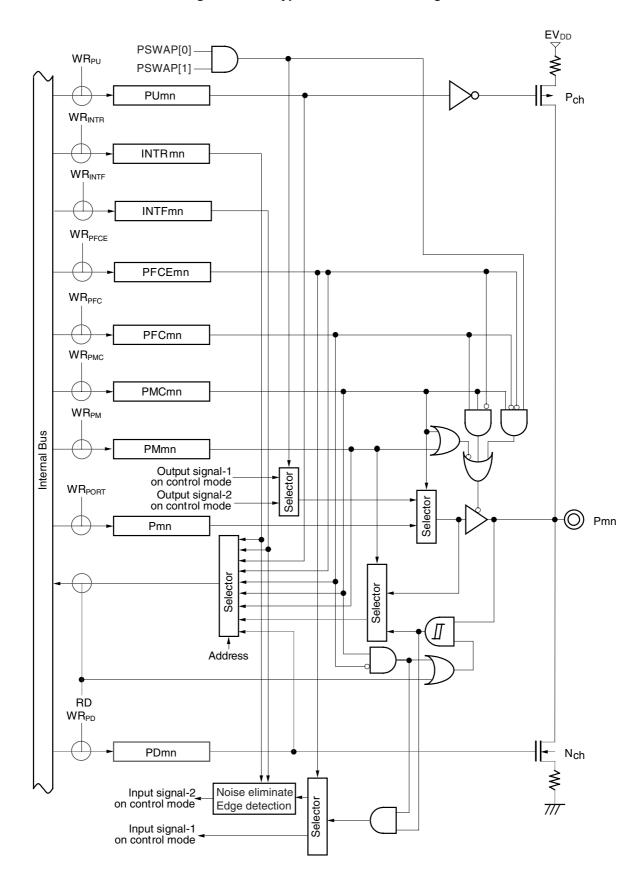

|           | 4.6.16  | Port block type U-SDW11E                                                  | 188   |

|           | 4.6.17  | Port block type G-SD7A                                                    | 189   |

|           | 4.6.18  | Port block type G-SDW8E                                                   | 190   |

|           | 4.6.19  | Port block type G-SD6                                                     | 191   |

|           | 4.6.20  | Port block type G-SDJ2                                                    | . 192 |

|           | 4.6.21  | Port block type G-SDJ5                                                    | . 193 |

|           | 4.6.22  | Port block type G-SDJ8E                                                   | . 194 |

|           | 4.6.23  | Port block type E-DWJ4                                                    | . 195 |

|           | 4.6.24  | Port block type U-SDW11                                                   | 196   |

|           | 4.6.25  | Port block type W-SD11                                                    | 197   |

|           | 4.6.26  | Port block type W-SD12E                                                   | . 198 |

|           | 4.6.27  | Port block type U-SDW10                                                   |       |

|           | 4.6.28  | Port Block type G-SDW6                                                    | 200   |

|           | 4.6.29  | Port block type E-D1                                                      | 201   |

|           | 4.6.30  | Port block type E-D4                                                      | 202   |

|           | 4.6.31  | Port block type D-7E                                                      |       |

|           | 4.6.32  | Port block type C-D1                                                      | 204   |

|           | 4.6.33  | Port block type B                                                         | 205   |

|           |         |                                                                           |       |

| Chapter : | 5 Bus   | Control Function                                                          | 207   |

| 5.1       |         | es                                                                        |       |

| 5.2       | Bus Co  | ontrol Pins                                                               |       |

|           | 5.2.1   | Pin status when internal ROM, internal RAM, or peripheral I/O is accessed |       |

|           | 5.2.2   | Pin status in each operation mode                                         |       |

| 5.3       | Memor   | ry Block Function                                                         |       |

|           | 5.3.1   | Chip select control function                                              |       |

| 5.4       |         | ccess                                                                     |       |

|           | 5.4.1   | Number of clocks for access.                                              |       |

|           | 5.4.2   | Bus size setting function                                                 |       |

|           | 5.4.3   | Access by bus size                                                        |       |

| 5.5       | Wait F  | unction                                                                   |       |

|           | 5.5.1   | Programmable wait function                                                |       |

|           | 5.5.2   | External wait function                                                    |       |

|           | 5.5.3   | Relationship between programmable wait and external wait                  |       |

|           | 5.5.4   | Programmable address wait function                                        |       |

| 5.6       | Idle St | ate Insertion Function.                                                   | 222   |

|      | 5.7  | Bus Hold Func   | ion                                           | 223 |

|------|------|-----------------|-----------------------------------------------|-----|

|      |      | 5.7.1 Function  | nal outline                                   | 223 |

|      |      |                 | 1 procedure                                   |     |

|      |      | •               | on in power save mode                         |     |

|      | 5.8  |                 |                                               |     |

|      | 5.9  | • •             | ation Conditions                              |     |

|      |      |                 | n space                                       |     |

|      | - 40 |                 | ace                                           |     |

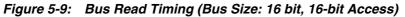

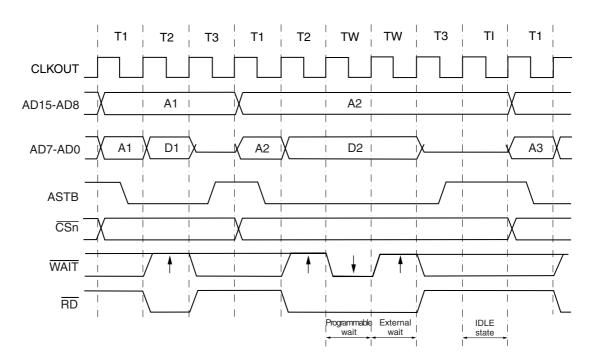

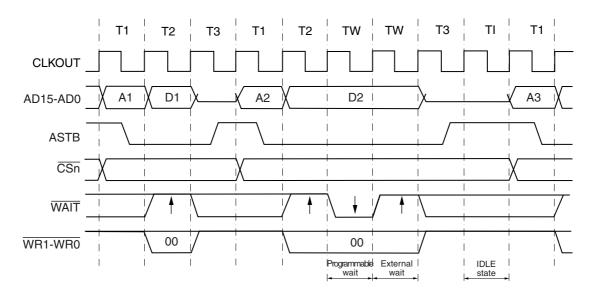

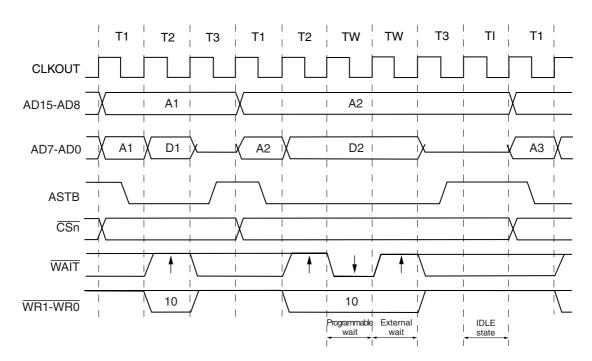

|      | 5.10 | Bus Timing      |                                               | 226 |

| Chan | tor  | Clock Conor     | ator                                          | ດວວ |

| Chap | 6.1  |                 | 101                                           |     |

|      | 6.2  |                 |                                               |     |

|      | 6.3  | •               | rs                                            |     |

|      | 6.4  |                 |                                               |     |

|      | 0.4  |                 | register                                      |     |

|      | 6.5  |                 | Clock output Function (PCL)                   |     |

|      | 0.0  |                 | registers                                     |     |

|      | 6.6  |                 |                                               |     |

|      |      |                 | PLL1                                          |     |

|      |      |                 | clock through mode                            |     |

|      |      |                 | ne programmable clock output function (PCL)   |     |

|      |      |                 |                                               |     |

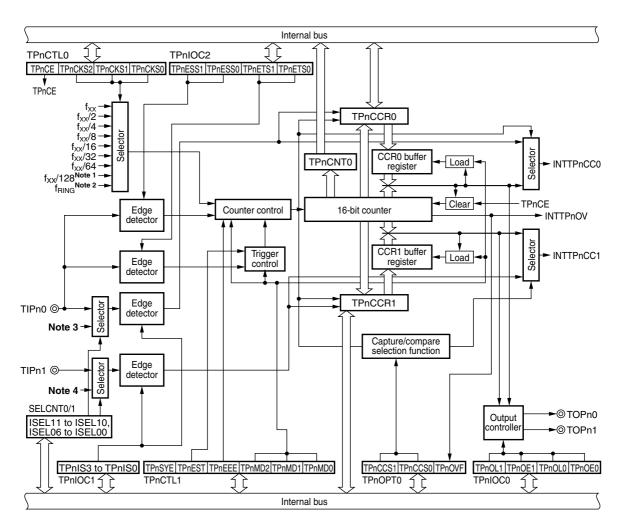

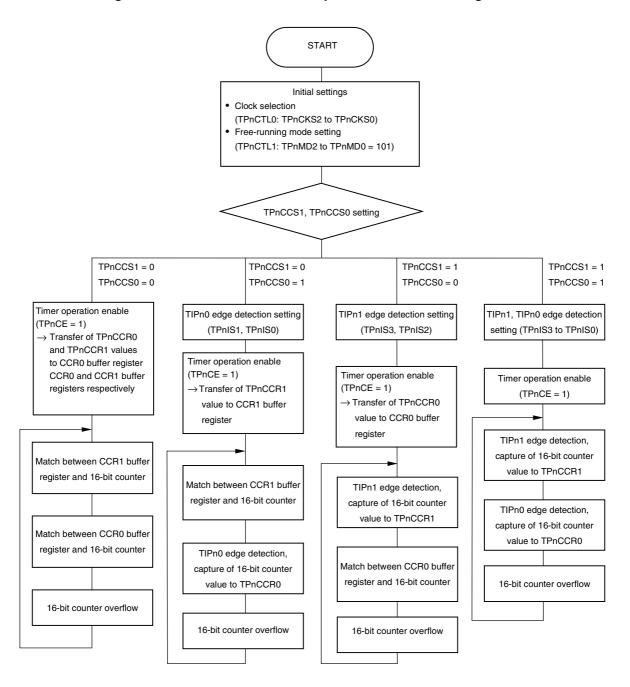

| Chap | ter  | 16-Bit Timer/   | Event Counter P                               | 255 |

|      | 7.1  | Features        |                                               | 255 |

|      | 7.2  |                 | e                                             |     |

|      | 7.3  | •               |                                               |     |

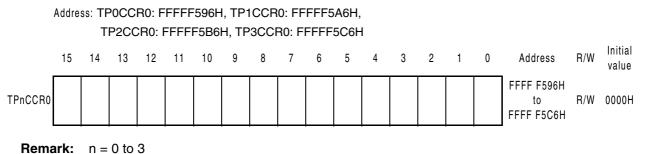

|      | 7.4  | -               | rs                                            |     |

|      | 7.5  | •               |                                               |     |

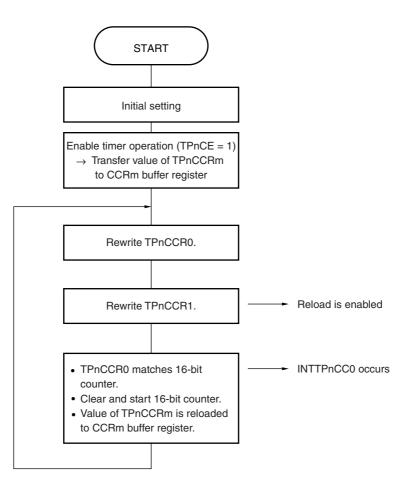

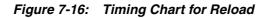

|      |      |                 | write and reload                              |     |

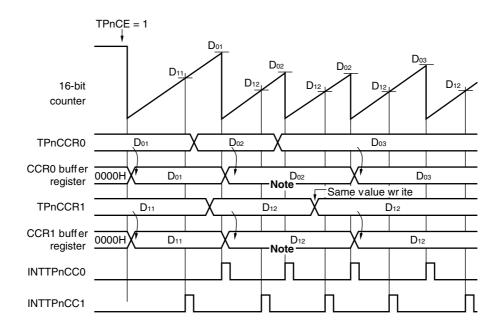

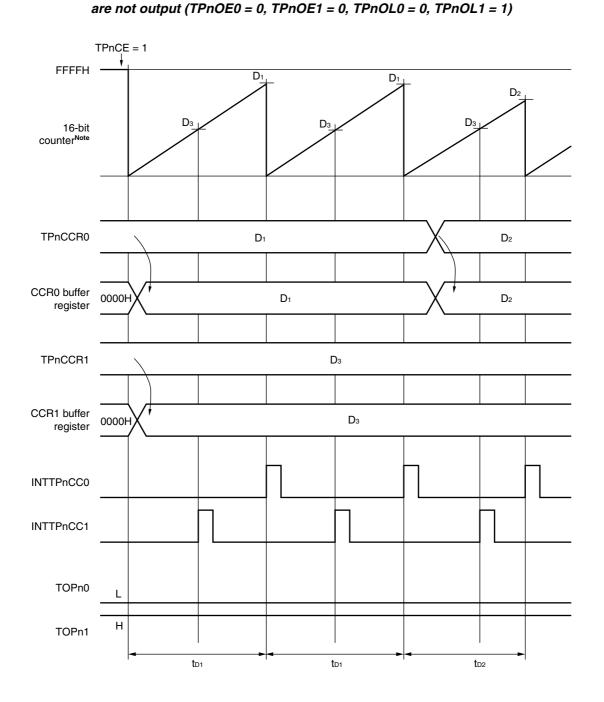

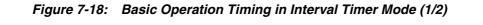

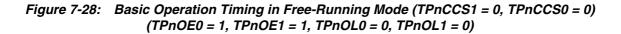

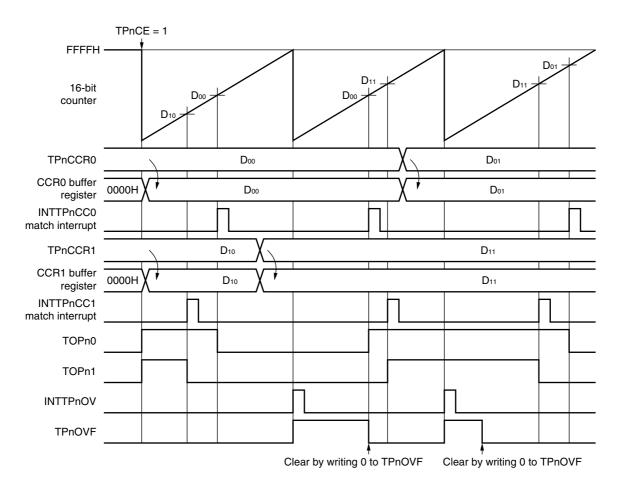

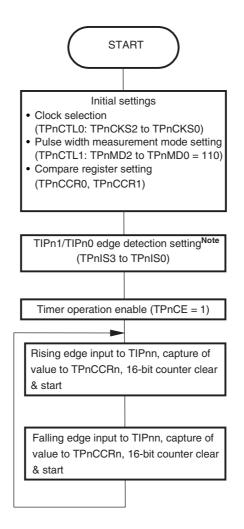

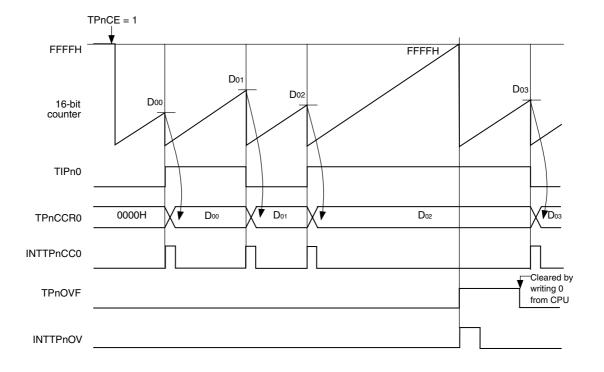

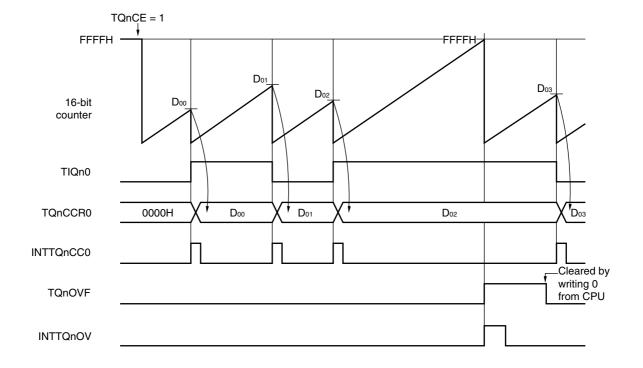

|      |      |                 | timer mode (TPnMD2 to TPnMD0 = 000)           |     |

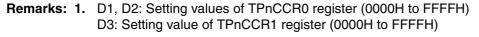

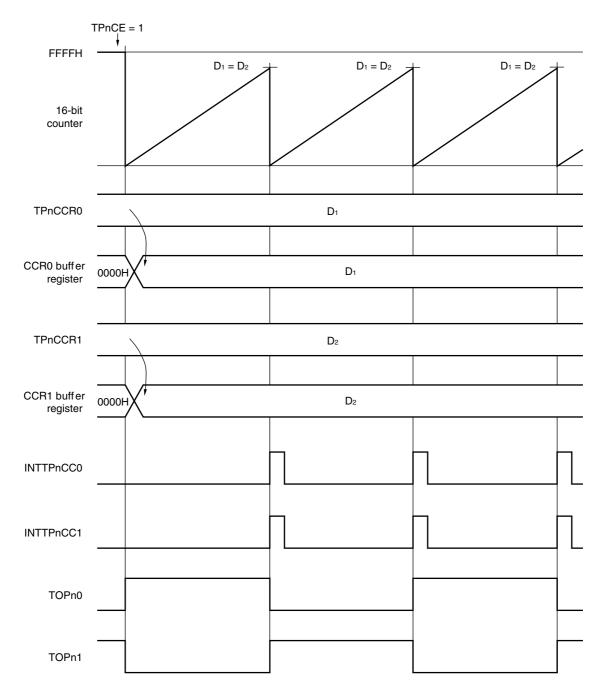

|      |      |                 | event counter mode (TPnMD2 to TPnMD0 = 001)   |     |

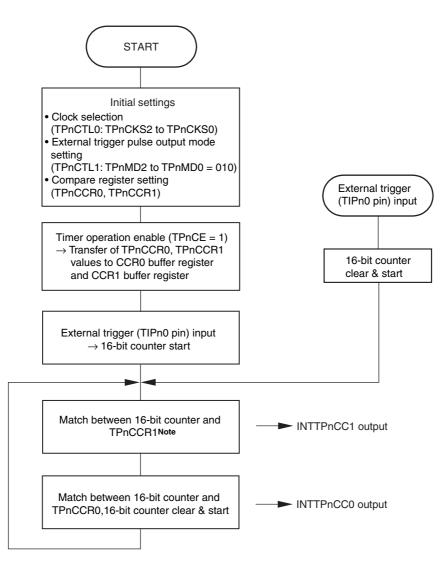

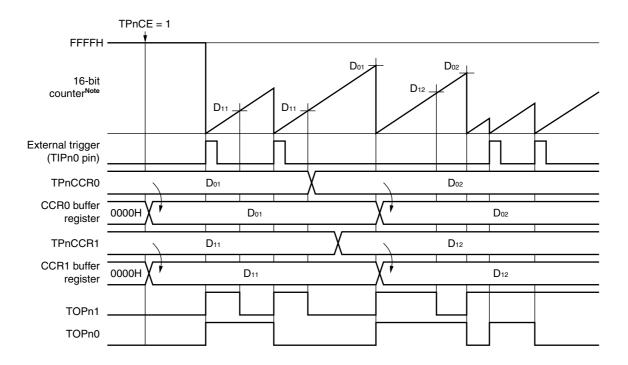

|      |      |                 | trigger pulse mode (TPnMD2 to TPnMD0 = 010)   |     |

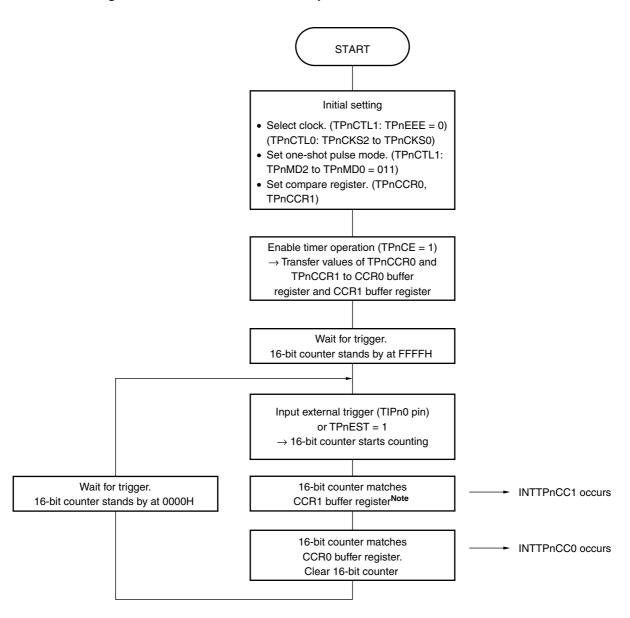

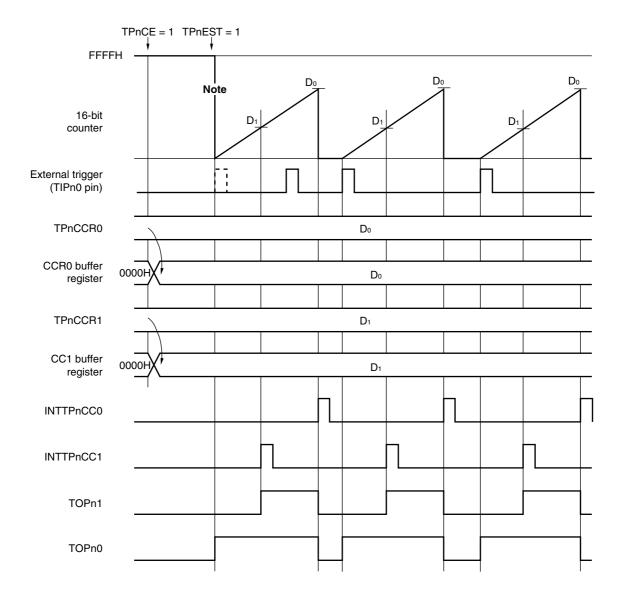

|      |      |                 | ot pulse mode (TPnMD2 to TPnMD0 = 011)        |     |

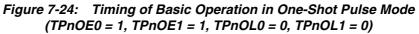

|      |      |                 | ode (TPnMD2 to TPnMD0 = 110)                  |     |

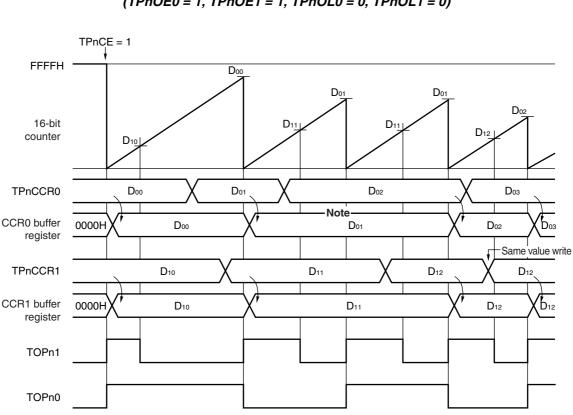

|      |      |                 | nning mode (TPnMD2 to TPnMD0 = 101)           |     |

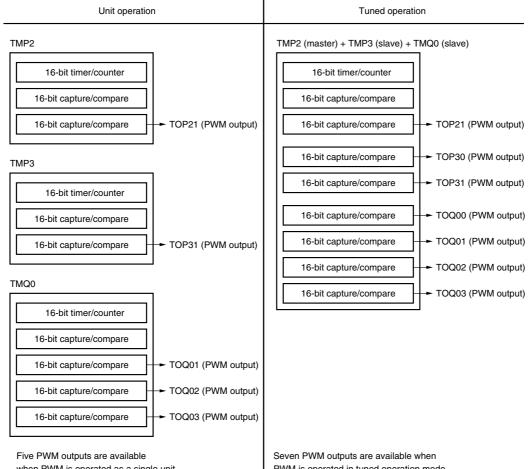

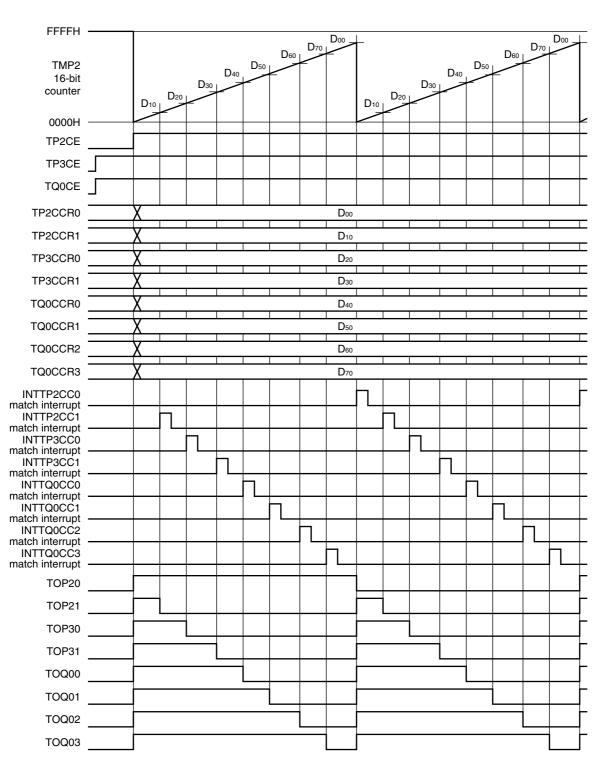

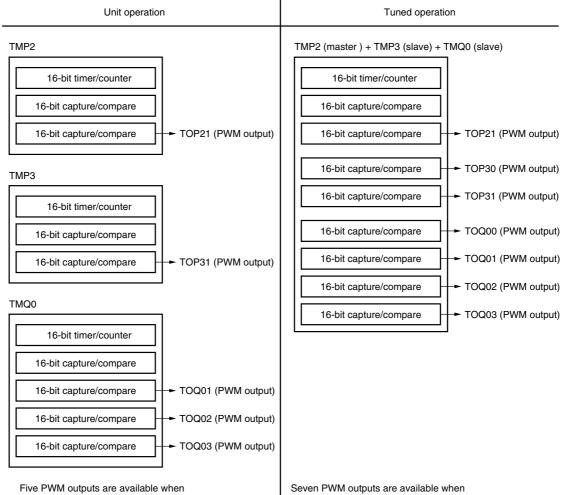

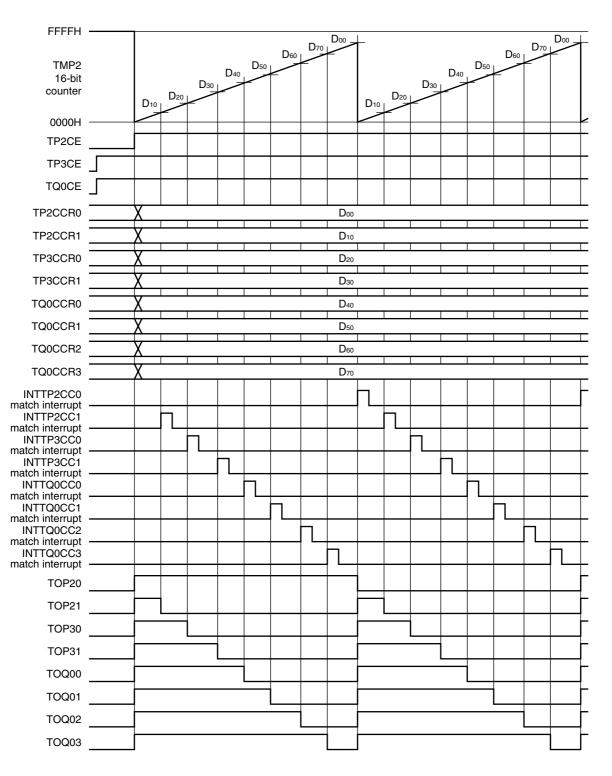

|      | 7.6  |                 | nization Operation Function                   |     |

|      | 1.0  | Timer Synchio   |                                               | 233 |

| Chap | ter  | 16-Bit Timer    | Event Counter Q                               | 303 |

| -    | 8.1  |                 |                                               |     |

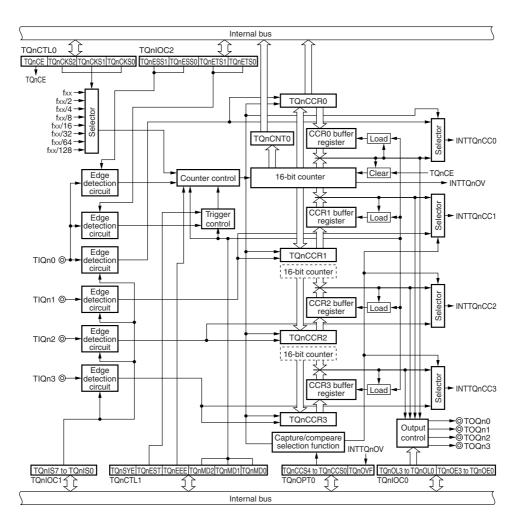

|      | 8.2  |                 | e                                             |     |

|      | 8.3  |                 |                                               |     |

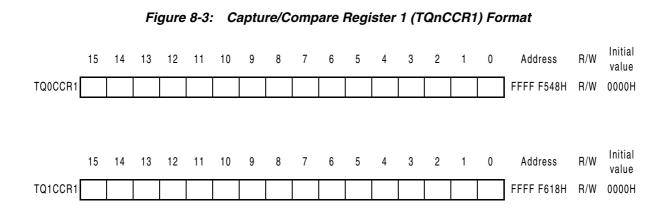

|      | 8.4  | Control Registe | rs                                            | 311 |

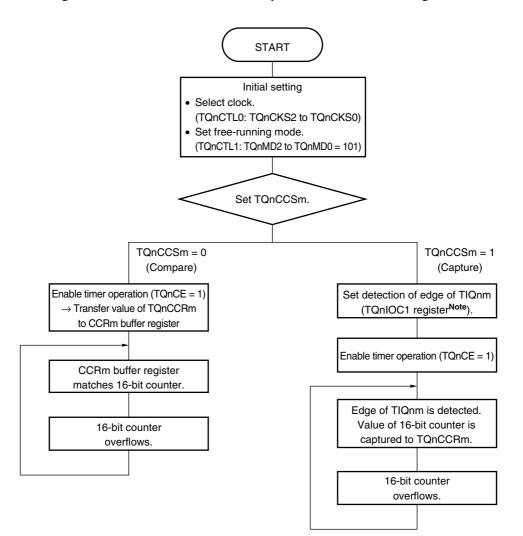

|      | 8.5  | Operation       |                                               | 319 |

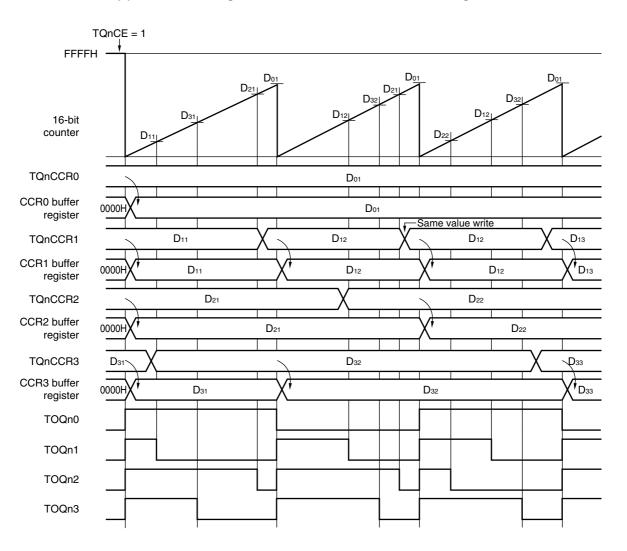

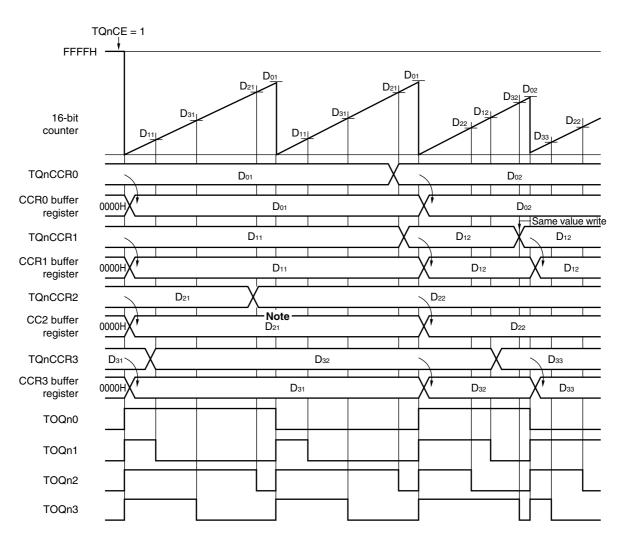

|      |      | 8.5.1 Anytime   | write and reload                              | 319 |

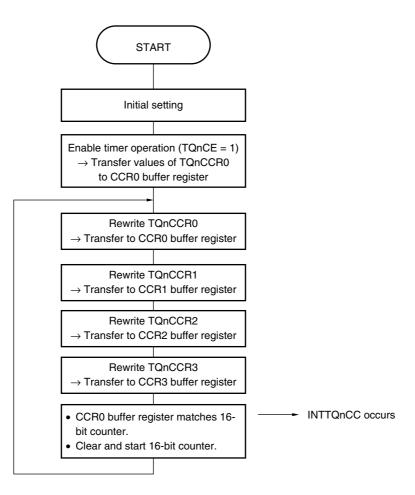

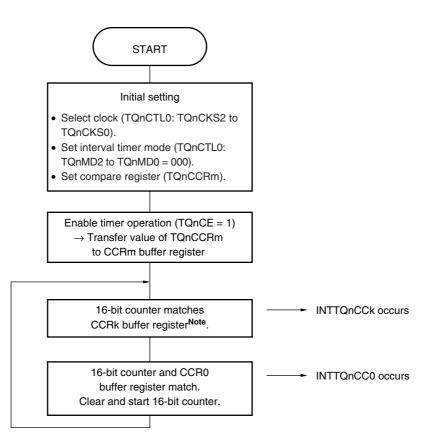

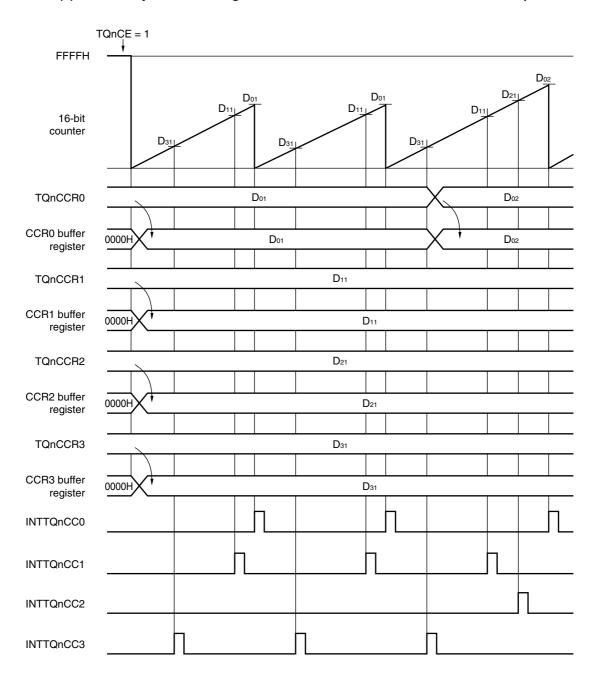

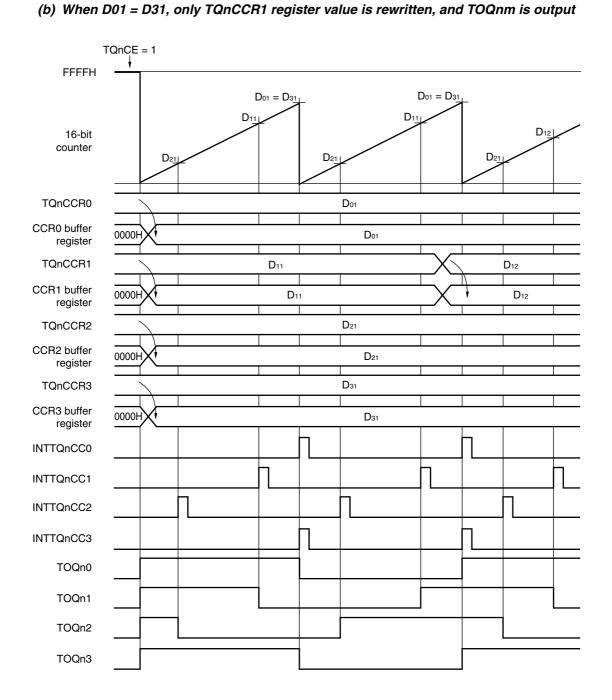

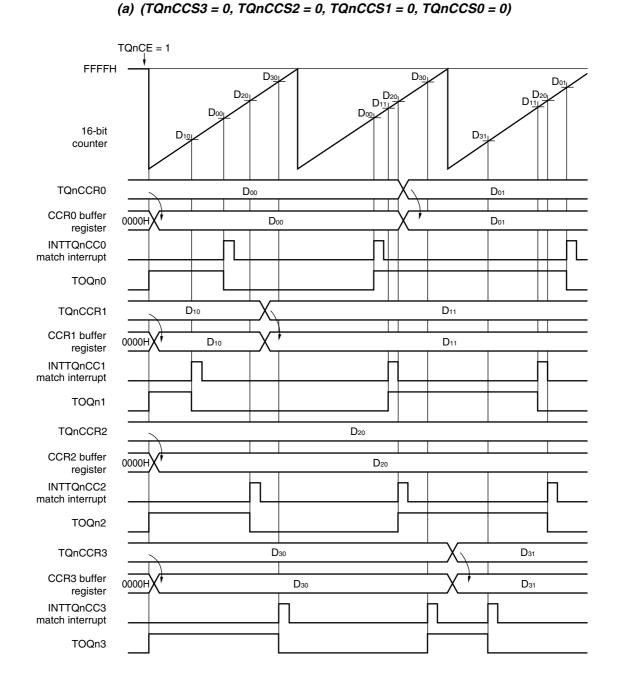

|      |      | 8.5.2 Interval  | timer mode (TQnMD2 to TQnMD0 = 000)           | 324 |

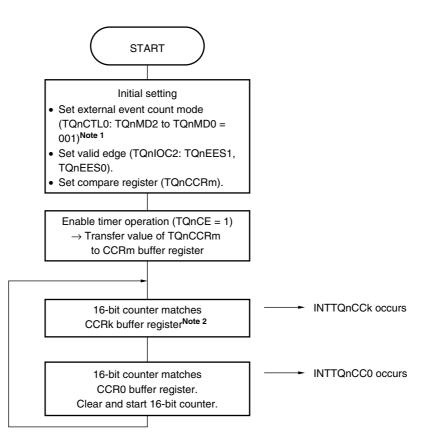

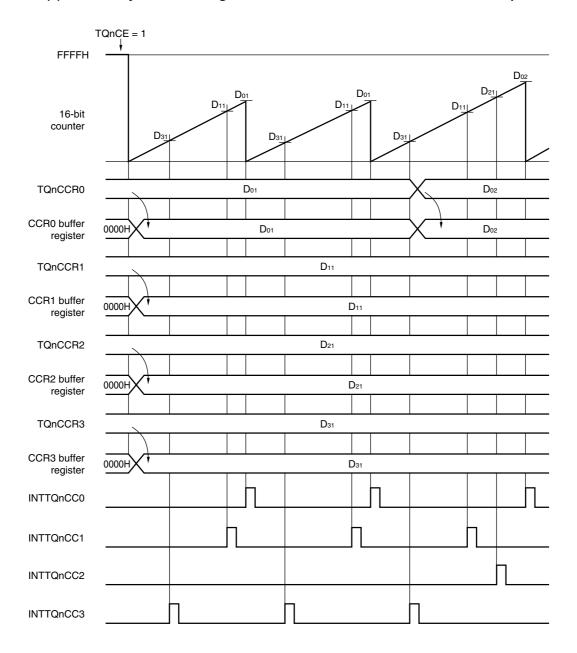

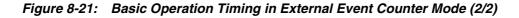

|      |      |                 | event counter mode (TQnMD2 to TQnMD0 = 001)   |     |

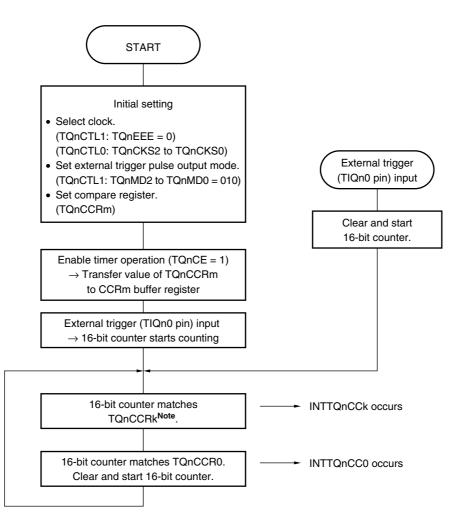

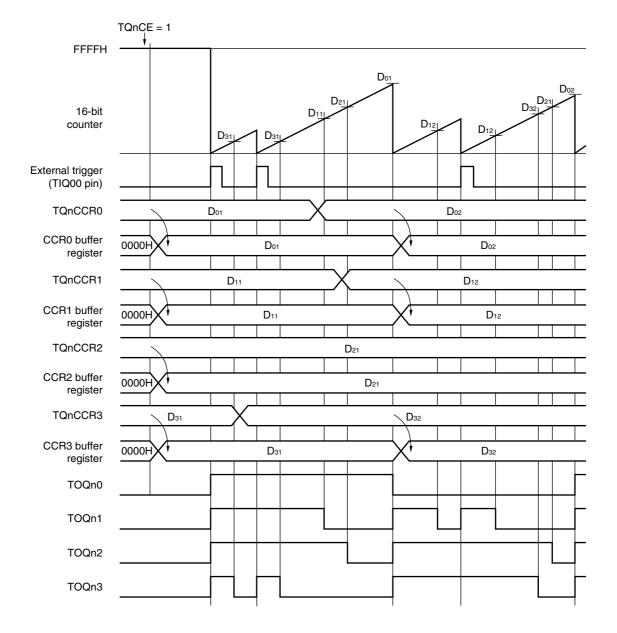

|      |      |                 | trigger pulse mode (TQnMD2 to TQnMD0 = 010)   |     |

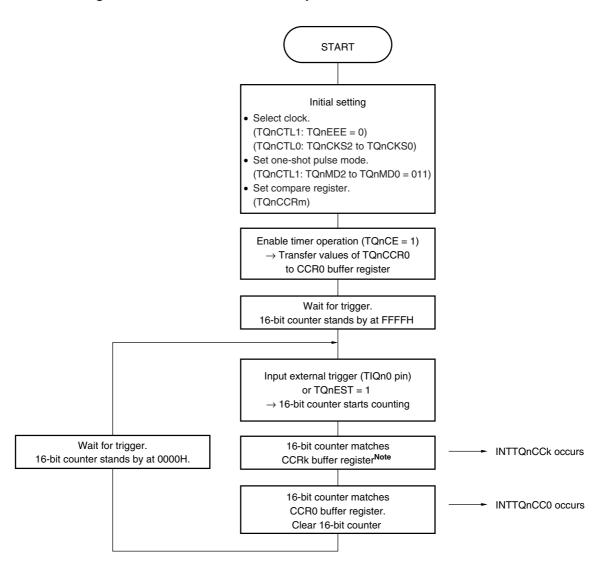

|      |      |                 | ot pulse mode (TQnMD2 to TQnMD0 = 011)        |     |

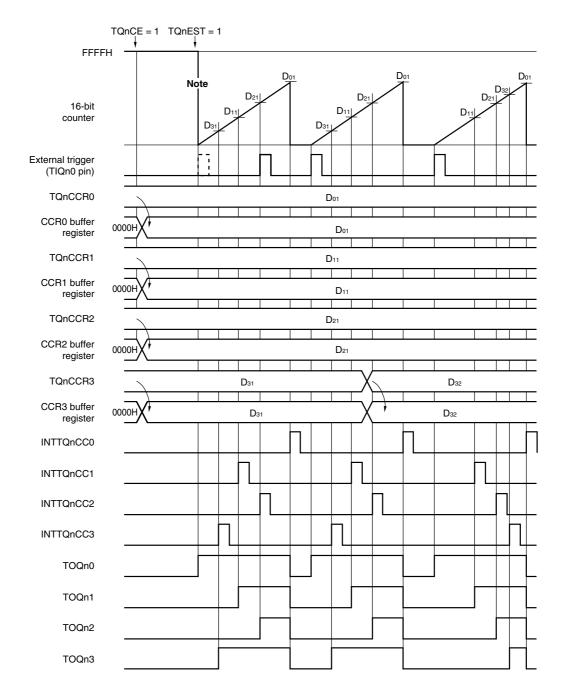

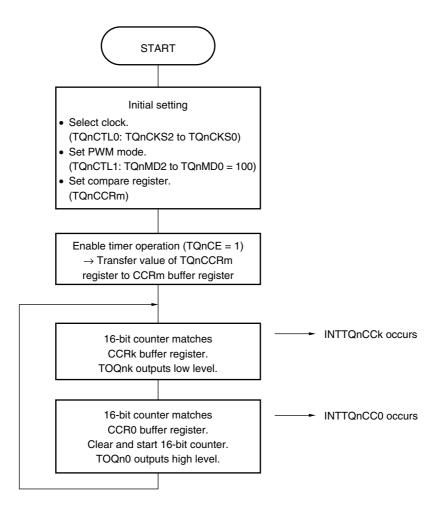

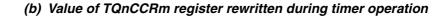

|      |      |                 | ode (TQnMD2 to TQnMD0 = 110)                  |     |

|      |      |                 | nning mode (TQnMD2 to TQnMD0 = 101)           |     |

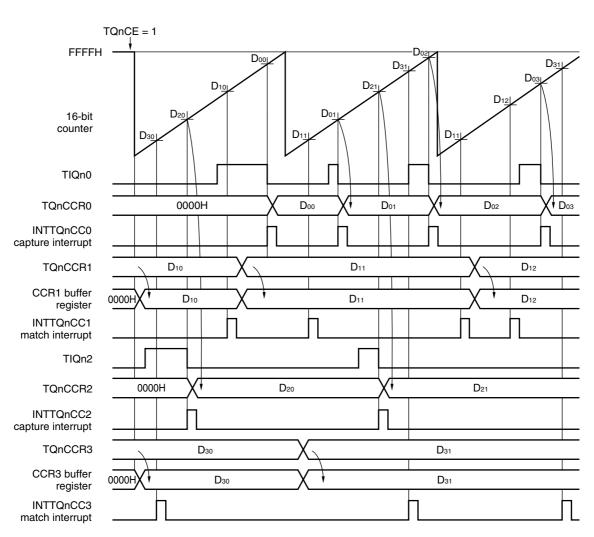

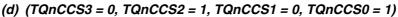

|      | _    |                 | dth measurement mode (TQnMD2 to TQnMD0 = 110) |     |

|      | 8.6  | Timer Synchro   | nization Operation Function                   | 351 |

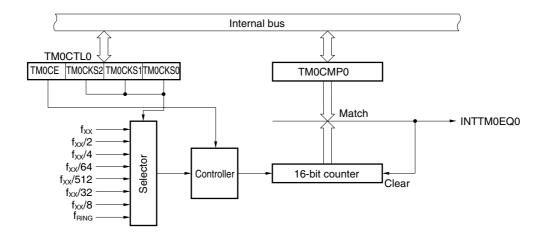

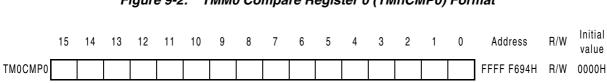

| Chapter 9 | 16-Bit Interval Timer M                                                      | . 355 |

|-----------|------------------------------------------------------------------------------|-------|

| 9.1       | Features                                                                     | 355   |

| 9.2       | Configuration                                                                | 356   |

| 9.3       | Control Register                                                             | 357   |

| 9.4       | Operation                                                                    |       |

|           | 9.4.1 Interval timer mode                                                    | 358   |

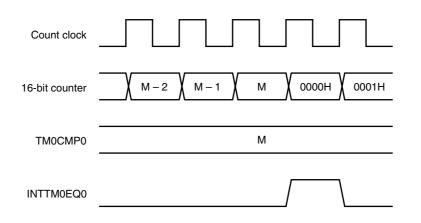

|           | 9.4.2 Clock generator and clock enable timing                                | 358   |

|           |                                                                              |       |

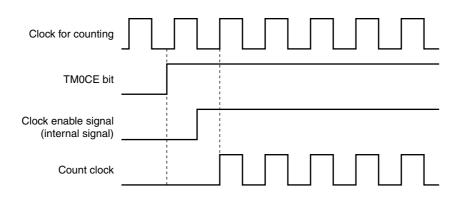

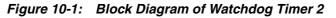

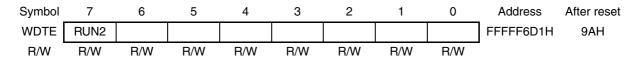

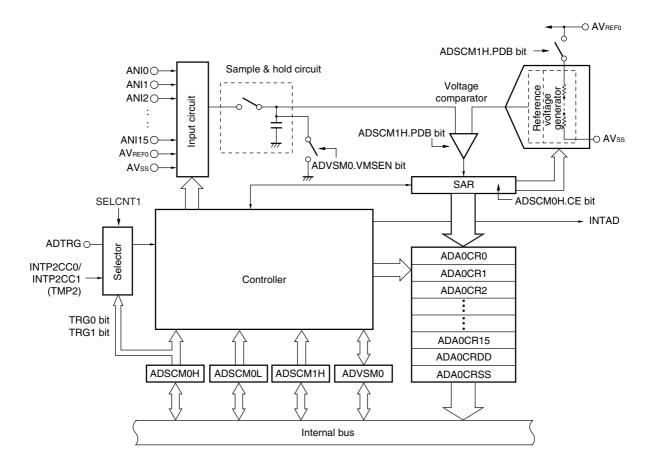

| Chapter 1 | 0 Functions of Watchdog Timer 2                                              | . 359 |

| 10.1      | Functions                                                                    |       |

| 10.2      | Configuration                                                                | 360   |

| 10.3      | Control Registers                                                            | 360   |

| 10.4      | Operation                                                                    | 364   |

|           | ·                                                                            |       |

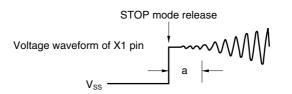

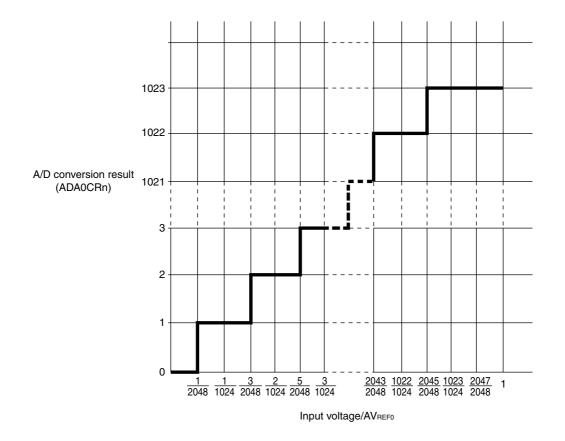

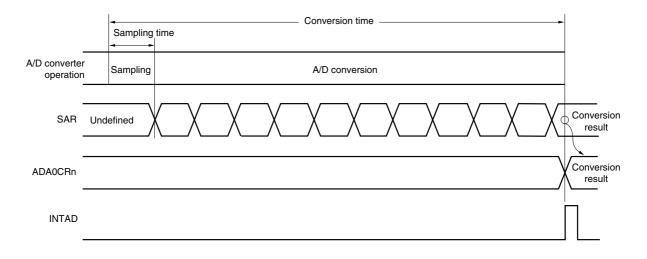

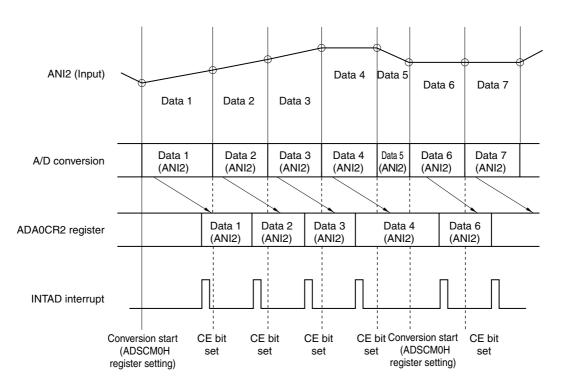

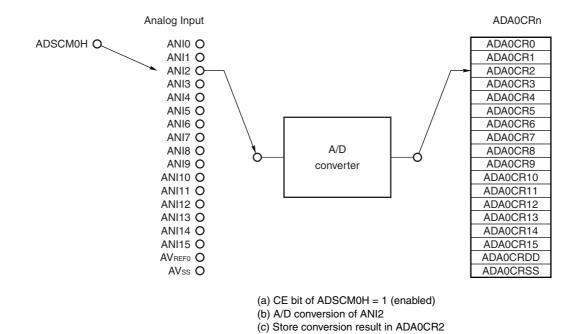

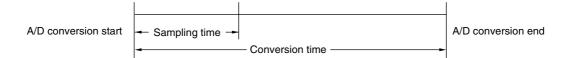

| Chapter 1 | 1 A/D Converter                                                              | . 367 |

| . 11.1    | Functions                                                                    |       |

| 11.2      | Configuration                                                                | 369   |

| 11.3      | •                                                                            |       |

| 11.4      | •                                                                            |       |

|           | 11.4.1 Basic operation                                                       |       |

|           | 11.4.2 Trigger mode                                                          |       |

|           | 11.4.3 Operation mode                                                        |       |

| 11.5      | Extended Functions                                                           |       |

|           | 11.5.1 Automatic discharge operation                                         | 391   |

|           | 11.5.2 Diagnostic mode                                                       |       |

| 11.6      | Precautions on Operation                                                     |       |

|           | 11.6.1 Stopping A/D                                                          | 392   |

|           | 11.6.2 Trigger input during A/D conversion operation                         |       |

|           | 11.6.3 External or timer trigger interval                                    |       |

|           | 11.6.4 Operation in standby modes                                            |       |

|           | 11.6.5 Compare match interrupt in timer trigger mode (External trigger mode) |       |

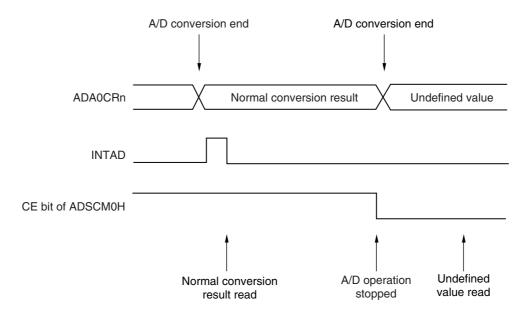

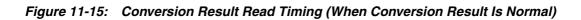

|           | 11.6.6 Timing that makes the A/D conversion result undefined                 |       |

| 11.7      | Cautions                                                                     |       |

| 11.8      | How to Read A/D Converter Characteristics Table                              | 398   |

|           |                                                                              |       |

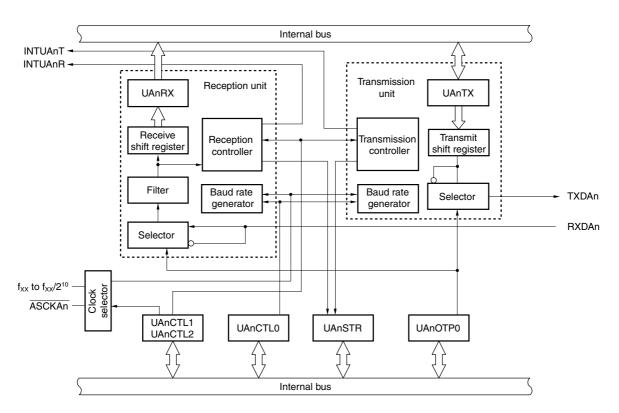

| Chapter 1 | 2 Asynchronous Serial Interface A (UARTA)                                    | . 403 |

| 12.1      | Features                                                                     | 403   |

| 12.2      | Configuration                                                                | 404   |

|           | 12.2.1 Control registers                                                     | 406   |

| 12.3      | Control Registers                                                            | 407   |

| 12.4      | Interrupt Request Signals                                                    | 415   |

| 12.5      | Operation                                                                    | 416   |

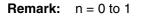

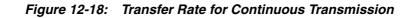

|           | 12.5.1 Data format                                                           | 416   |

|           | 12.5.2 UART transmission                                                     | 417   |

|           | 12.5.3 Procedure of continuous transmission                                  | 418   |

|           | 12.5.4 UART reception                                                        | 420   |

|           | 12.5.5 Reception errors                                                      |       |

|           | 12.5.6 Types and operation of parity                                         |       |

|           | 12.5.7 Noise filter of receive data                                          |       |

| 12.6      | Dedicated Baud Rate Generator                                                | 425   |

| 12.7      | Caution for Use in On-chip Debug Mode                                        | 430   |

|           |                                                                              |       |

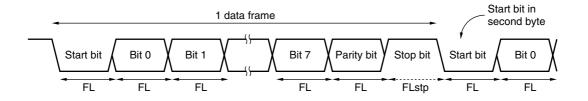

| -         | 3 3-Wire Serial Interface (CSIB)                                             |       |

| 13.1      | Features                                                                     |       |

| 13.2      | Configuration                                                                |       |

| 13.3      | Control Registers Overview                                                   |       |

| 13.4      | Control Registers Description                                                |       |

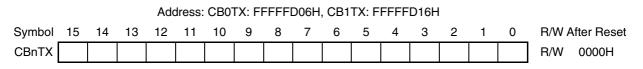

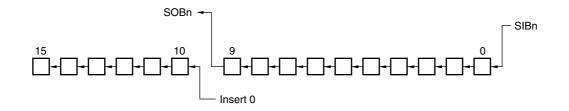

| 13.5      | Transfer Data Length Change Function.                                        | 441   |

|      | 13.6  | Interru | pt Request Signals                                              | 442   |

|------|-------|---------|-----------------------------------------------------------------|-------|

|      | 13.7  | Operati | ion                                                             | . 443 |

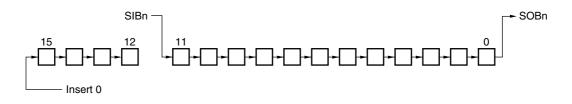

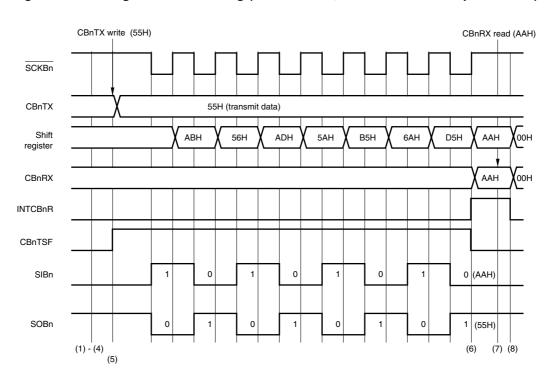

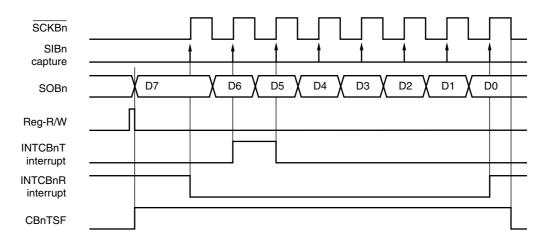

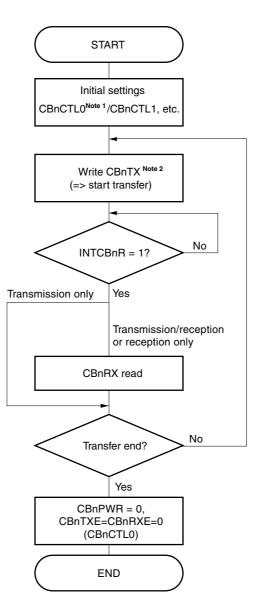

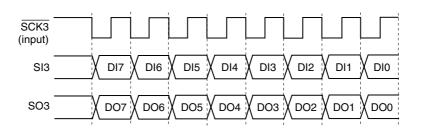

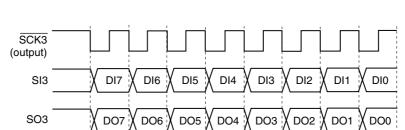

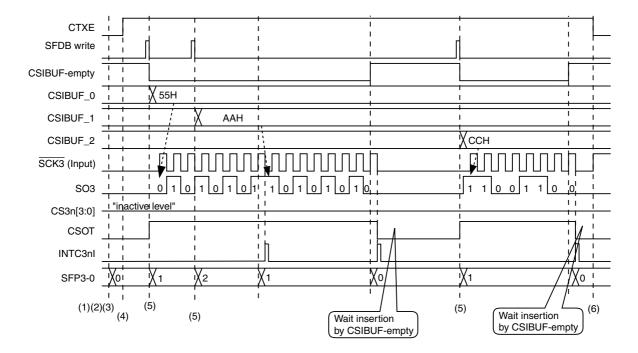

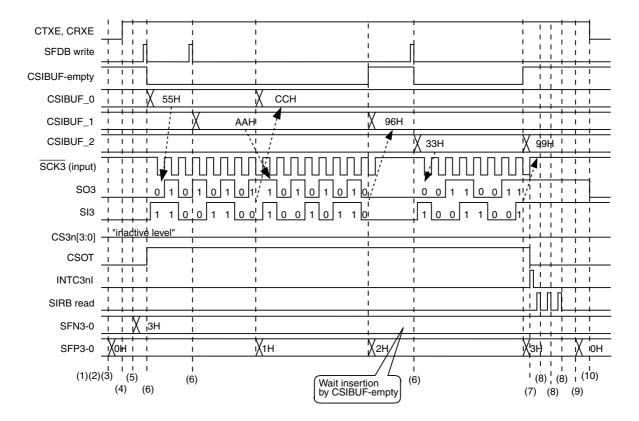

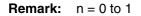

|      |       | 13.7.1  | Single transfer mode (master mode, transmission/reception mode) | . 443 |

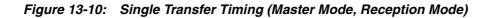

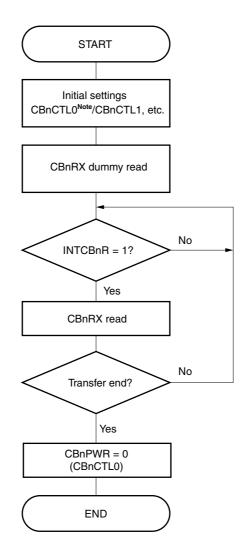

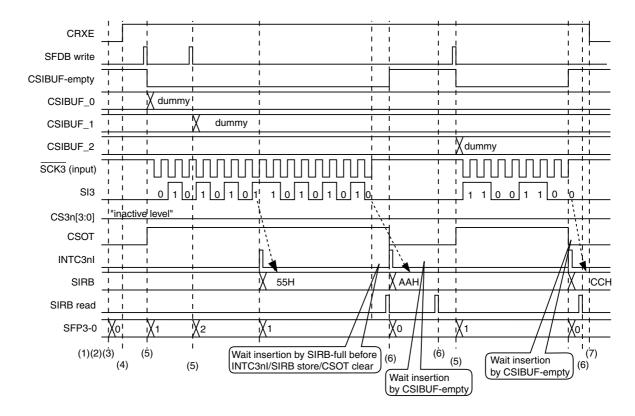

|      |       | 13.7.2  | Single transfer mode (master mode, reception mode)              | 444   |

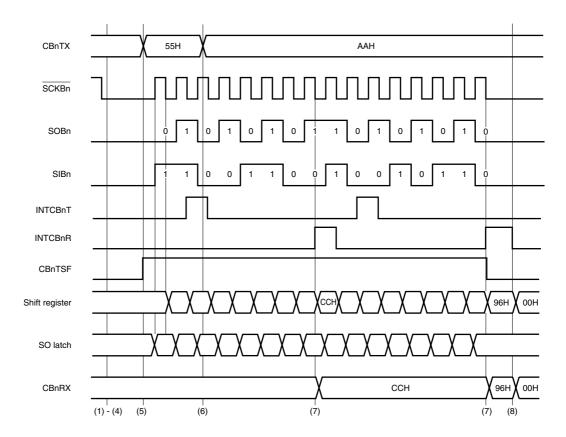

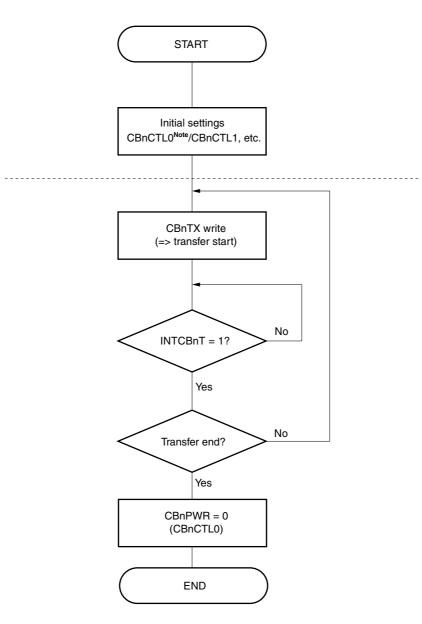

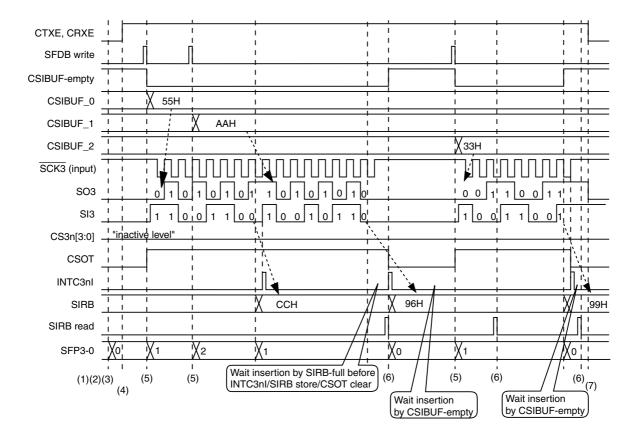

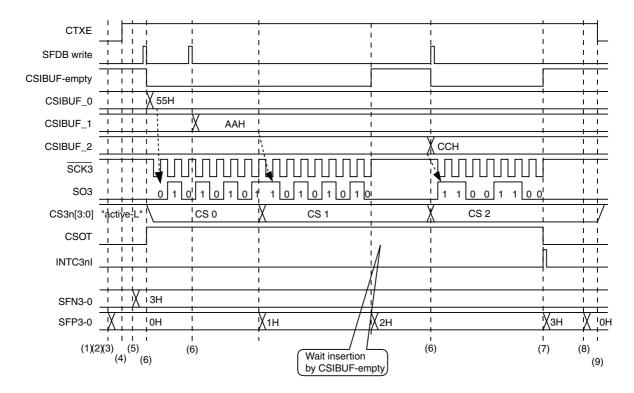

|      |       | 13.7.3  | Continuous mode (master mode, transmission/reception mode)      | 445   |

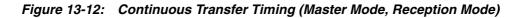

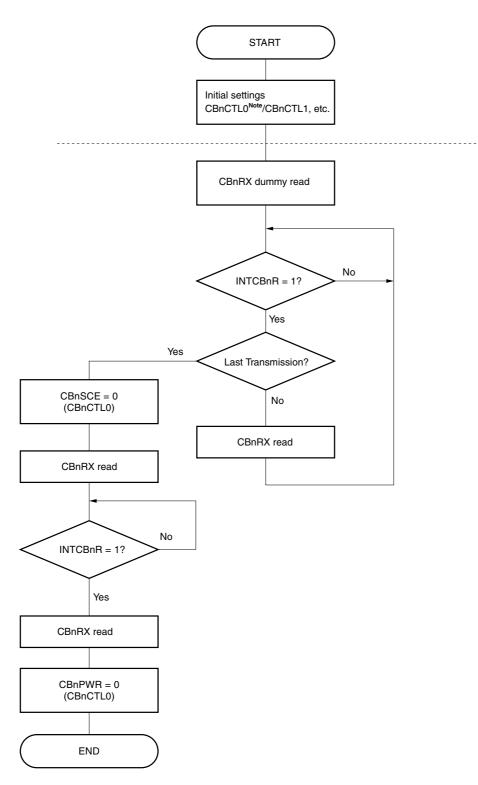

|      |       | 13.7.4  | Continuous mode (master mode, reception mode)                   | 446   |

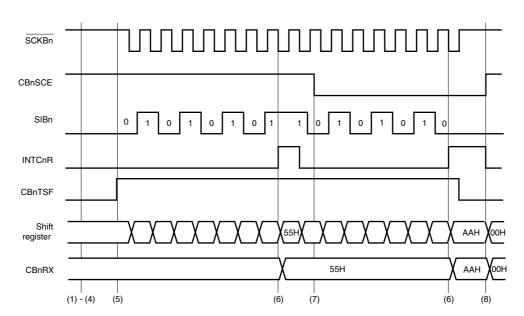

|      |       | 13.7.5  | Continuous reception mode (error)                               | 447   |

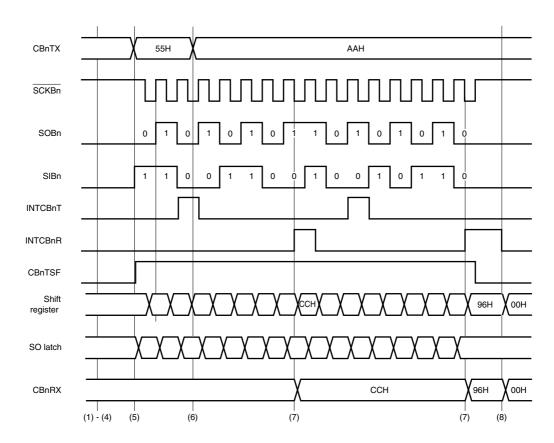

|      |       | 13.7.6  | Continuous mode (slave mode, transmission/reception mode)       | 448   |

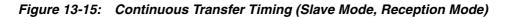

|      |       | 13.7.7  | Continuous mode (slave mode, reception mode)                    | 449   |

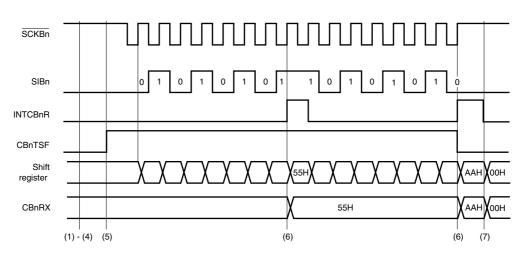

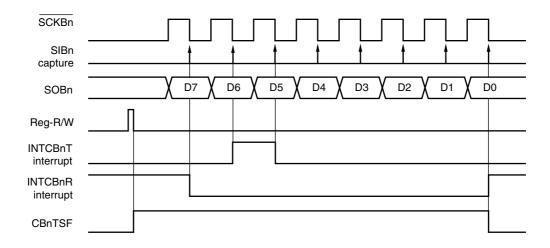

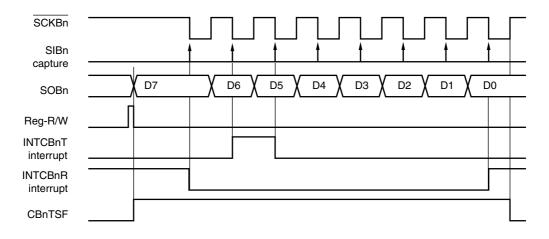

|      |       | 13.7.8  | Clock timing                                                    | 450   |

|      |       | 13.7.9  | Output pin status with operation disabled                       | 452   |

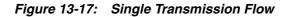

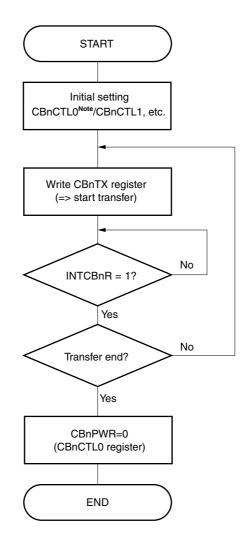

|      | 13.8  | Operati | ion Flow                                                        | 453   |

|      | 13.9  | Presca  | ler 3                                                           | 461   |

|      |       | 13.9.1  | Control registers of prescaler 3                                | 461   |

|      |       | 13.9.2  | Generation of count clock                                       | 462   |

|      |       |         |                                                                 |       |

| Chap | ter 1 |         | ed CSI (CSI30, CSI31)                                           |       |

|      | 14.1  |         | es                                                              |       |

|      |       | 14.1.1  | Queued CSI Block Diagram                                        |       |

|      |       | 14.1.2  | Input/Output Pins                                               |       |

|      |       |         | d CSI Control Registers                                         |       |

|      | 14.3  | -       | ation of Queued CSI Functions                                   |       |

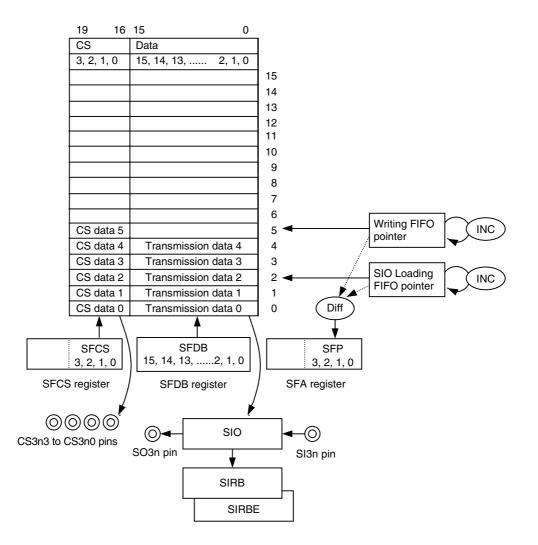

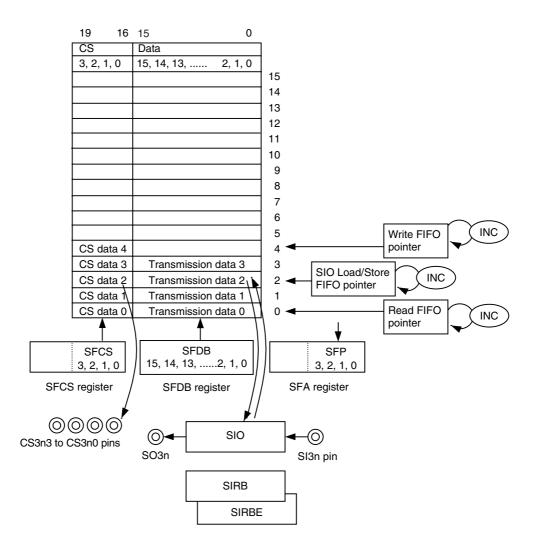

|      |       | 14.3.1  | Transmit Buffer                                                 |       |

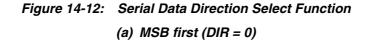

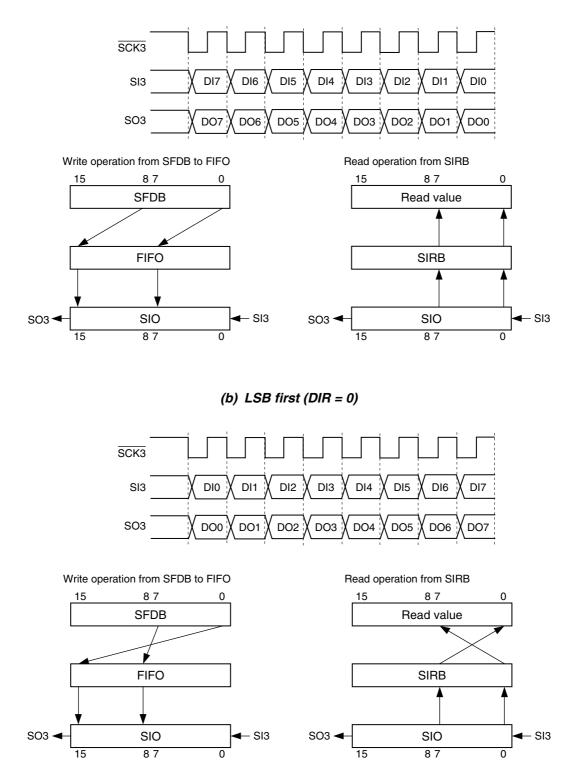

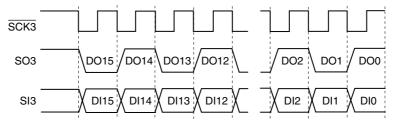

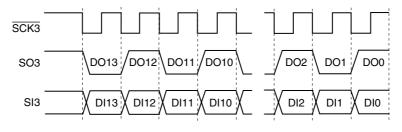

|      |       | 14.3.2  | Serial Data Direction Select Function                           |       |

|      |       | 14.3.3  | Data Length Select Function                                     |       |

|      |       | 14.3.4  | Slave Mode                                                      |       |

|      |       | 14.3.5  | Master Mode                                                     |       |

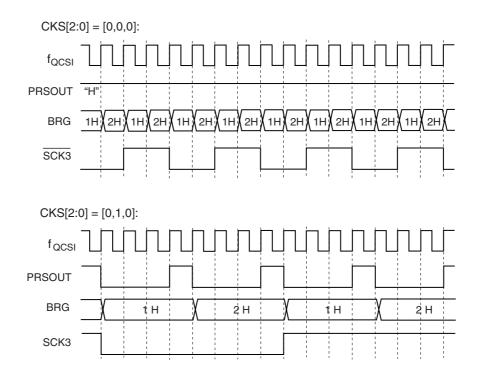

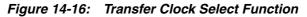

|      |       | 14.3.6  | Transmission Clock Select Function.                             |       |

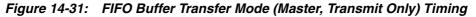

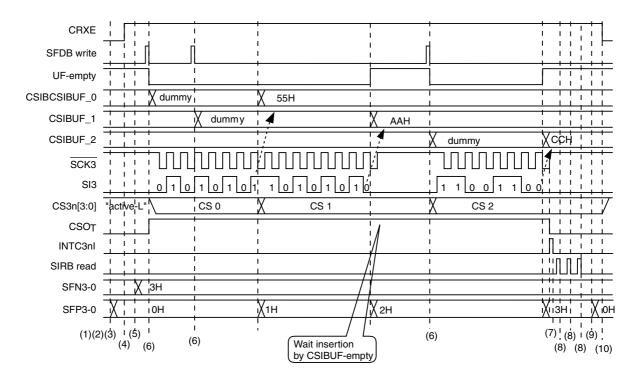

|      |       | 14.3.7  | Description of the Single Buffer Transfer Mode                  |       |

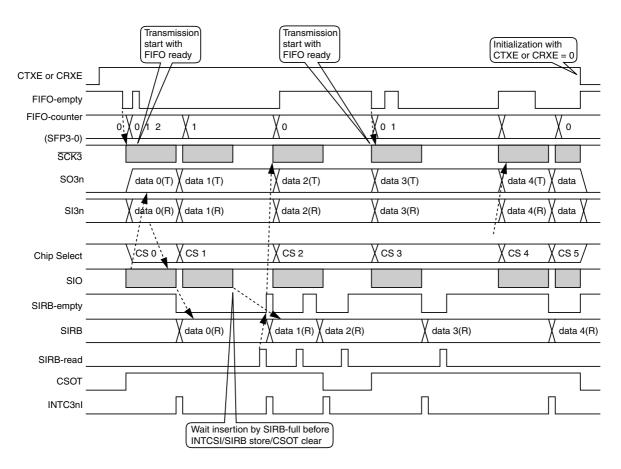

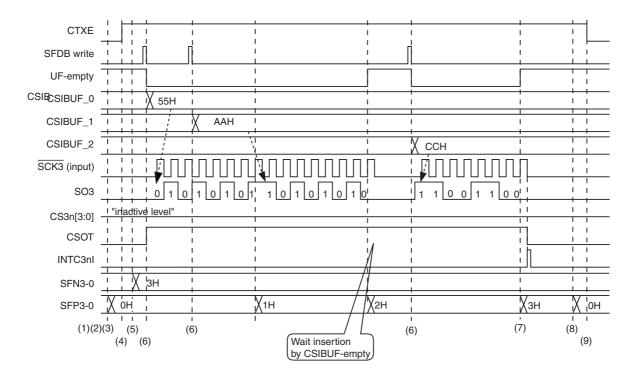

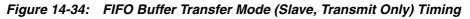

|      |       | 14.3.8  | Description of the FIFO Buffer Transfer Mode                    |       |

|      |       | 14.3.9  | Description of the Operation Modes                              |       |

|      |       | 14.3.10 | Additional Timing and Delay Selections                          |       |

|      |       | 14.3.11 | Default Pin Levels                                              |       |

|      |       | 14.3.12 | Transmit Buffer Overflow Interrupt Signal (INTC3nO)             |       |

|      | 14.4  | Operati | ing Procedure                                                   | . 491 |

|      |       |         |                                                                 |       |

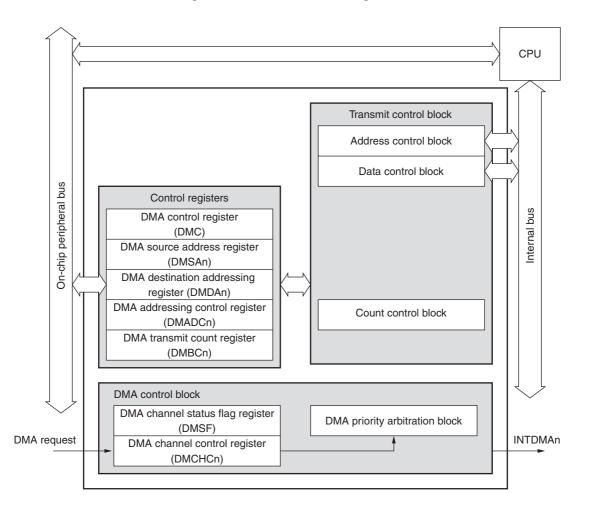

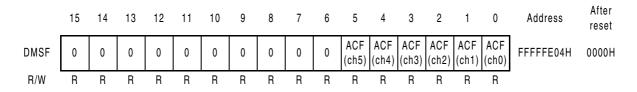

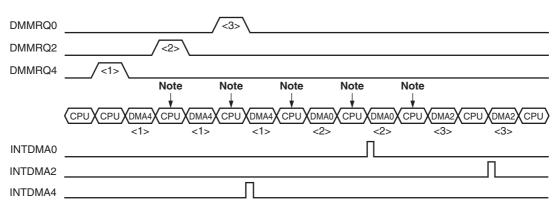

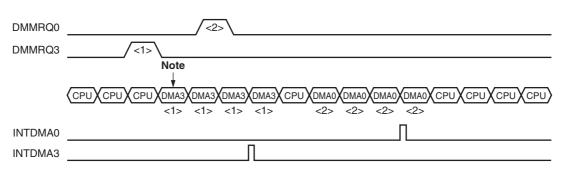

| Chap |       |         | Functions (DMA Controller)                                      |       |

|      | 15.1  |         | es                                                              |       |

|      | 15.2  |         | uration                                                         |       |

|      | 15.3  |         | I Registers                                                     |       |

|      | 15.4  |         | ransfer Rules                                                   |       |

|      |       | 15.4.1  | Transfer targets                                                |       |

|      |       | 15.4.2  | DMA channel priority                                            |       |

|      |       | 15.4.3  | DMA transfer start factors.                                     |       |

|      | 45.5  | 15.4.4  | DMA transfer end                                                |       |

|      | 15.5  |         | er Modes                                                        |       |

|      |       | 15.5.1  | Single transfer mode.                                           |       |

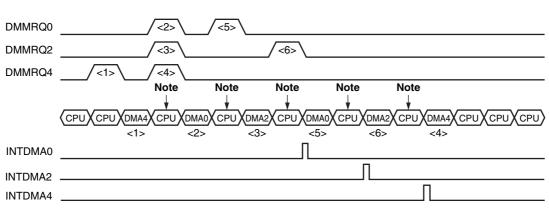

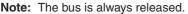

|      |       | 15.5.2  | Fixed channel transfer mode                                     |       |

|      |       | 15.5.3  | Block transfer mode                                             |       |

|      |       | 15.5.4  | Summary on the transfer modes                                   | 524   |

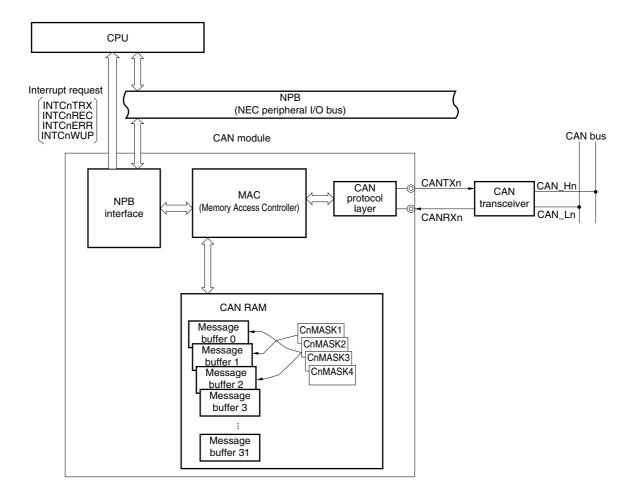

| pter 16 | FCAN    | Controller                                            | 525   |

|---------|---------|-------------------------------------------------------|-------|

| 16.1    | Overvie | W                                                     | . 525 |

| 1       | 6.1.1   | Features                                              | . 525 |

| 10      | 6.1.2   | Overview of Functions                                 | . 526 |

| 10      |         | Configuration                                         |       |

|         |         | otocol                                                |       |

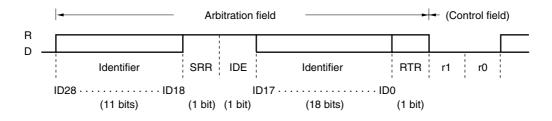

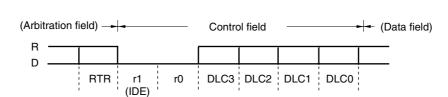

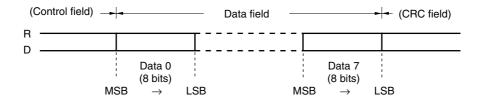

|         |         | Frame format                                          |       |

|         |         | Frame types                                           |       |

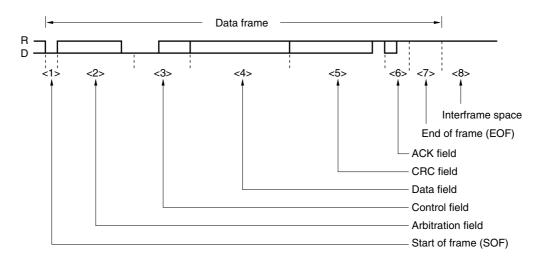

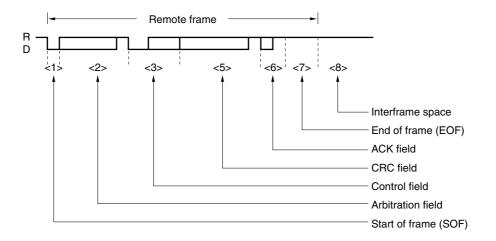

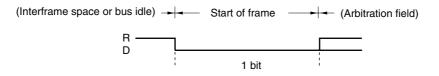

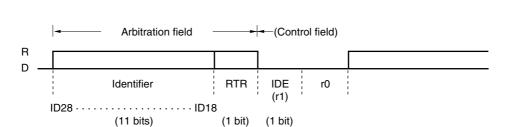

|         |         | Data frame and remote frame.                          |       |

|         |         |                                                       |       |

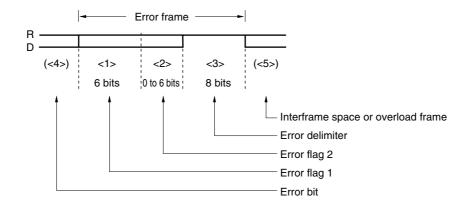

|         |         | Error frame                                           |       |

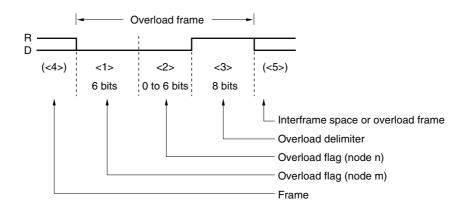

|         |         | Overload frame                                        |       |

|         |         | ns                                                    |       |

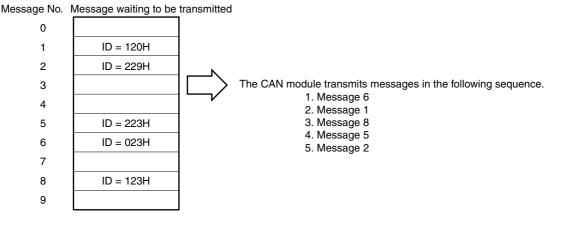

|         |         | Determining bus priority                              |       |

|         |         | Bit stuffing                                          |       |

|         |         | Multi masters                                         |       |

| 1       | 6.3.4   | Multi cast                                            | . 540 |

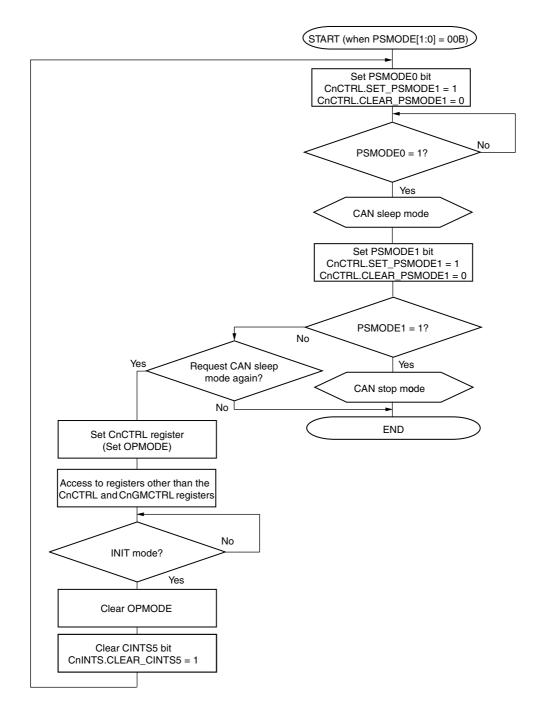

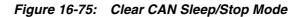

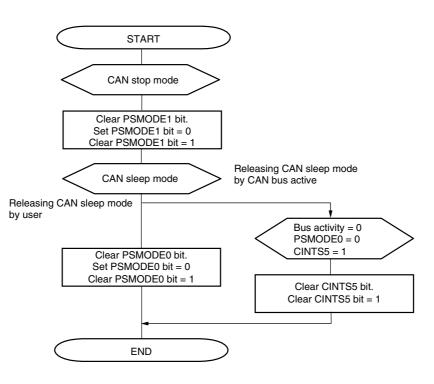

| 1       | 6.3.5   | CAN sleep mode/CAN stop mode function                 | . 540 |

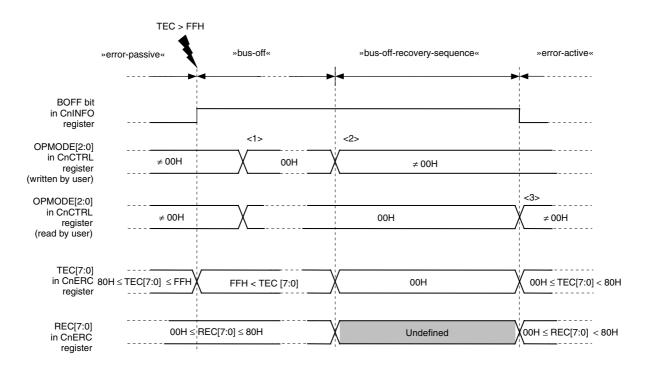

| 10      |         | Error control function                                |       |

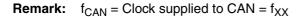

|         |         | Baud rate control function.                           |       |

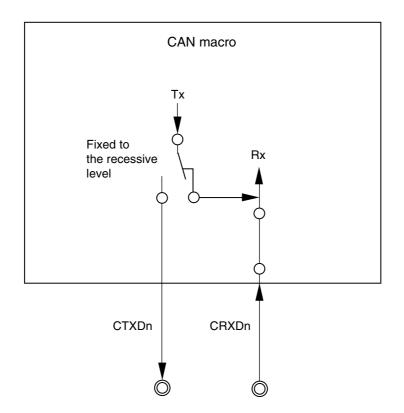

|         |         | tion with Target System                               |       |

|         |         | Registers of CAN controller                           |       |

|         |         | CAN controller configuration.                         |       |

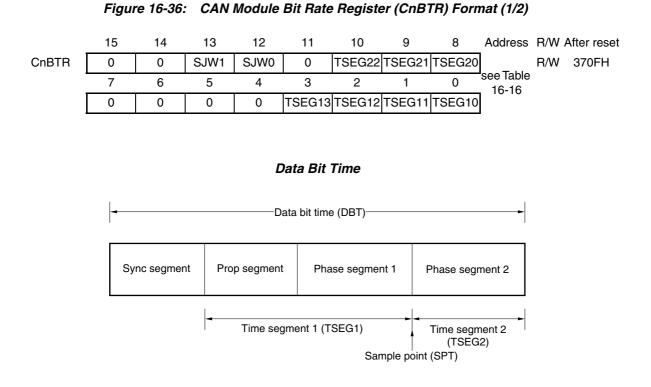

|         |         | Register access type                                  |       |

|         |         |                                                       |       |

|         |         | Register bit configuration                            |       |

|         |         | Registers                                             |       |

| 16.7    |         | Clear Function                                        |       |

|         |         | ontroller Initialization                              |       |

|         |         | Initialization of CAN module                          |       |

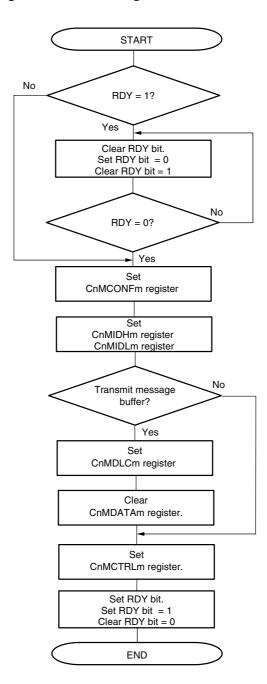

|         |         | Initialization of message buffer                      |       |

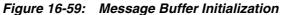

| 1       | 6.8.3   | Redefinition of message buffer                        | . 626 |

| 1       | 6.8.4   | Transition from initialization mode to operation mode | . 627 |

| 10      | 6.8.5   | Resetting error counter CnERC of CAN module           | . 628 |

| 16.9    |         | e Reception                                           |       |

|         |         | Message reception                                     |       |

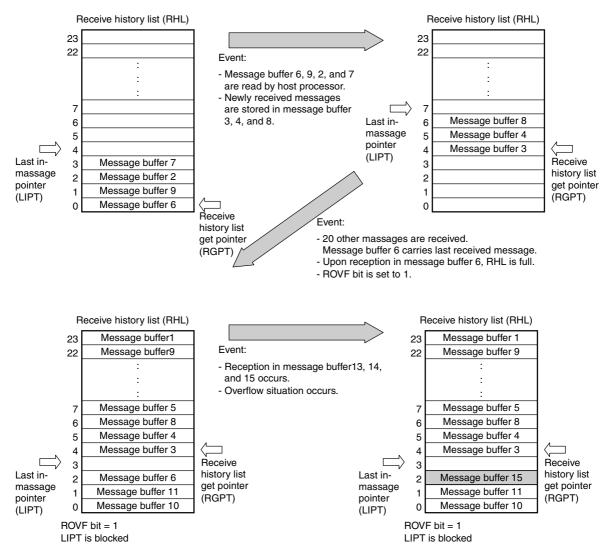

|         |         | Receive history list function                         |       |

|         |         | Mask function                                         |       |

|         |         | Multi buffer receive block function                   |       |

|         |         | Remote frame reception                                |       |

| -       |         |                                                       |       |

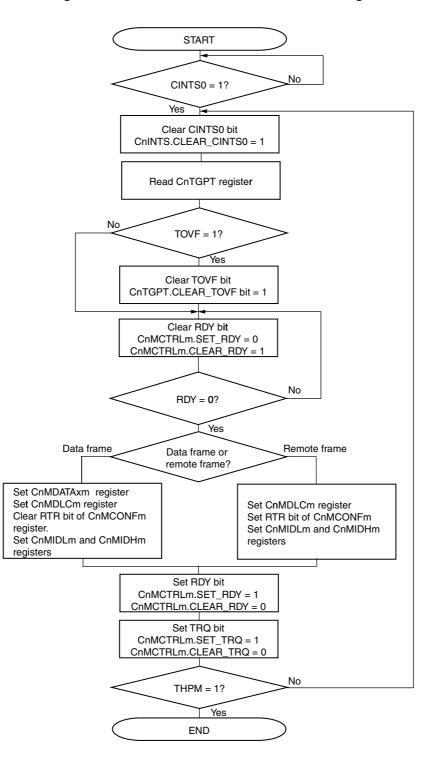

|         |         | e Transmission                                        |       |

|         |         | Message transmission                                  |       |

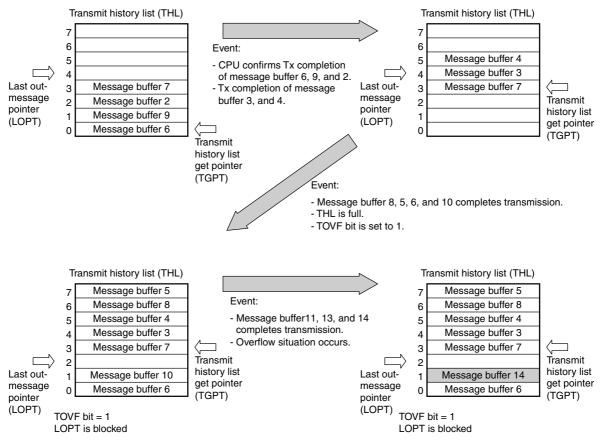

|         |         | Transmit history list function                        |       |

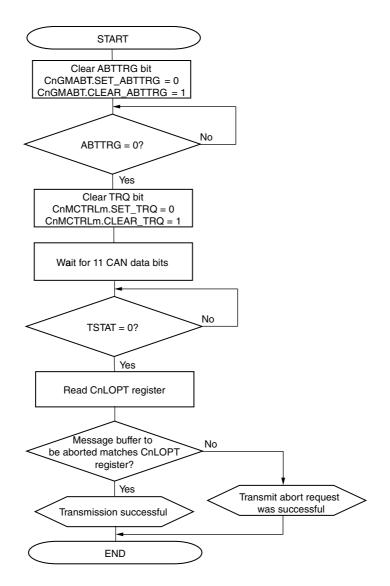

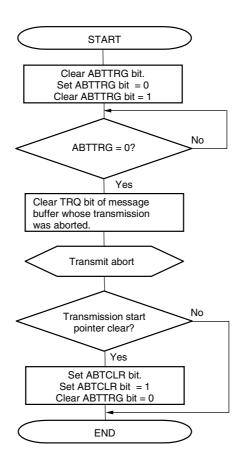

|         |         | Automatic block transmission (ABT)                    |       |

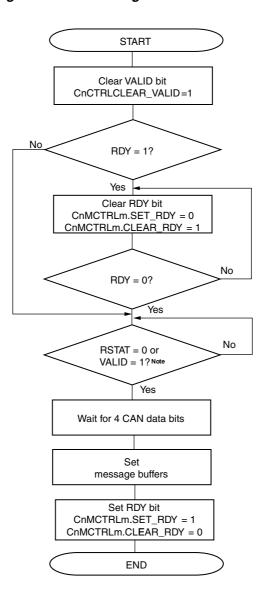

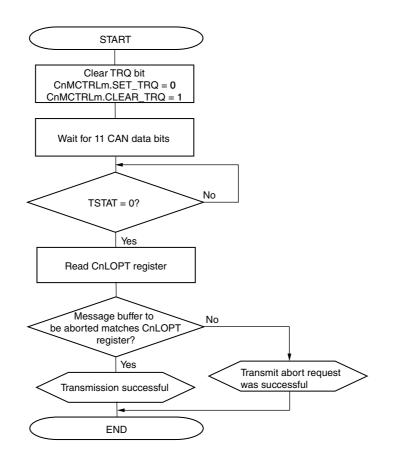

|         |         | Transmission abort process                            |       |

| 1       | 6.10.5  | Remote frame transmission                             | . 641 |

| 16.11   | Power S | Saving Modes                                          | . 642 |

|         |         | CAN sleep mode                                        |       |

|         |         | CAN stop mode                                         |       |

|         |         | Example of using power saving modes                   |       |

|         |         | t Function                                            |       |

|         |         | sis Functions and Special Operational Modes           |       |

|         | -       |                                                       |       |

|         |         | Receive-only mode                                     |       |

|         |         | Single-shot mode                                      |       |

|         |         | Self-test mode                                        |       |

|         |         | amp Function                                          |       |

| 10      | 6.14.1  | Time stamp function                                   | . 651 |

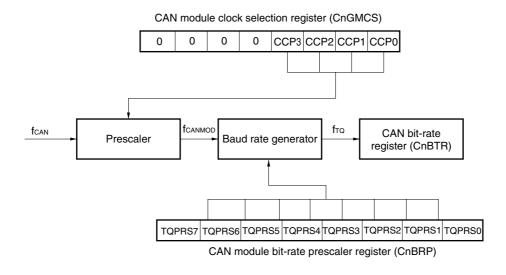

| 16.15   |         | ate Settings                                          |       |

|         |         | Bit rate setting conditions                           |       |

|         |         | Representative examples of baud rate settings         |       |

|         |         | on of CAN Controller.                                 |       |

|         |         |                                                       |       |

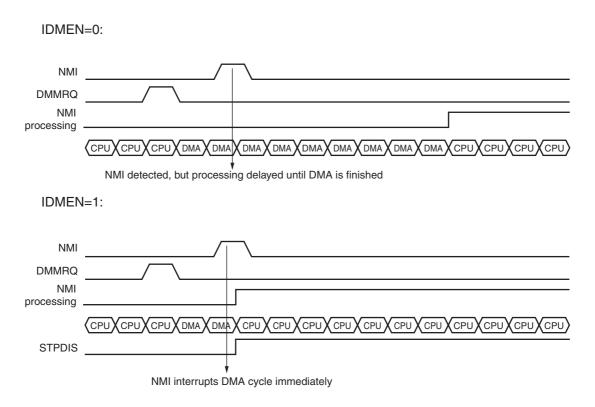

| Chap | ter 1                                                                                                                  | 7 Interi                                                                                                                                                                                                                              | rupt/Exception Processing Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 685                                                                                                                                                                                                                                                                                                              |

|------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 17.1                                                                                                                   | Feature                                                                                                                                                                                                                               | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 685                                                                                                                                                                                                                                                                                                              |

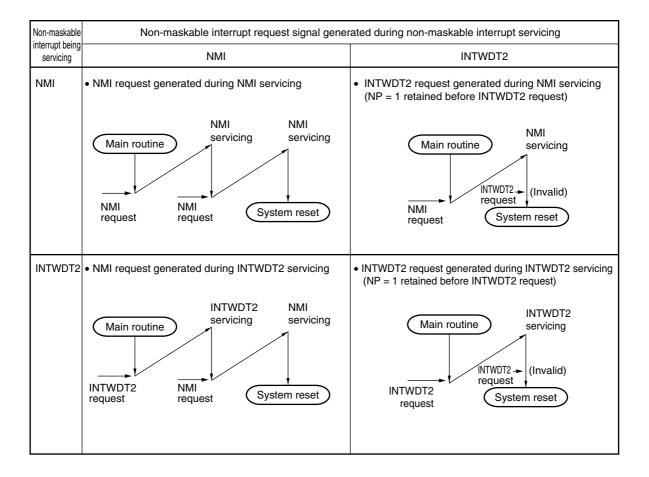

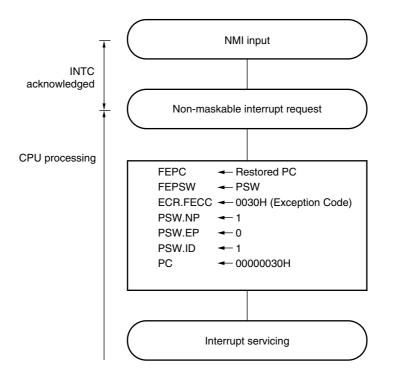

|      | 17.2                                                                                                                   | Non-M                                                                                                                                                                                                                                 | askable Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 688                                                                                                                                                                                                                                                                                                              |

|      |                                                                                                                        | 17.2.1                                                                                                                                                                                                                                | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                  |

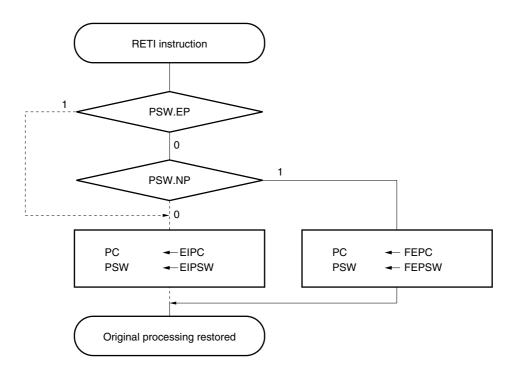

|      |                                                                                                                        | 17.2.2                                                                                                                                                                                                                                | Restore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                  |

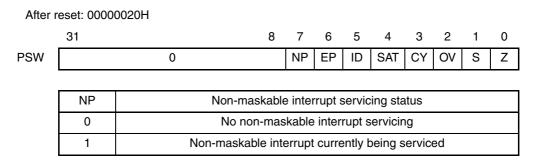

|      |                                                                                                                        | 17.2.3                                                                                                                                                                                                                                | NP flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                        | 17.2.4                                                                                                                                                                                                                                | Eliminating noise on NMI pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                        | 17.2.5                                                                                                                                                                                                                                | Function to detect edge of NMI pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                        |                                                                                                                                                                                                                                       | ble Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                  |

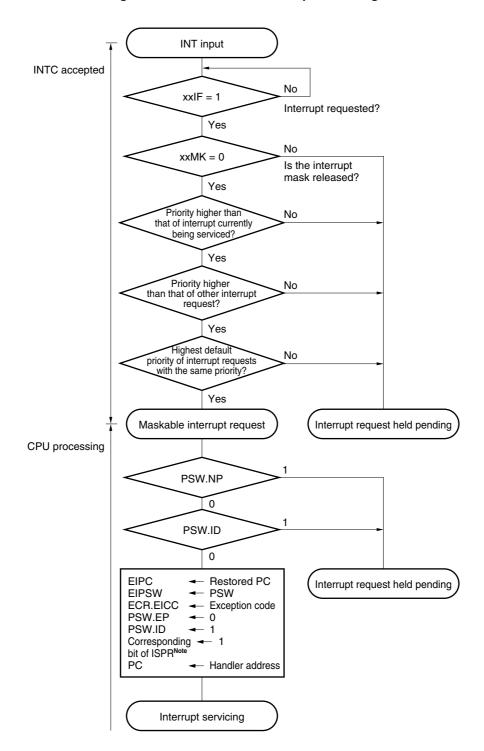

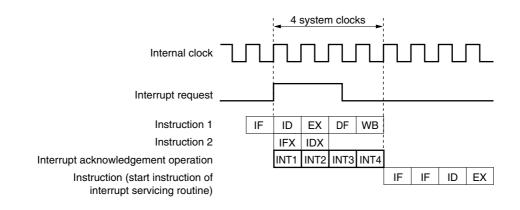

|      |                                                                                                                        | 17.3.1                                                                                                                                                                                                                                | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                  |

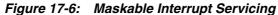

|      |                                                                                                                        | 17.3.2                                                                                                                                                                                                                                | Restore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                        | 17.3.3                                                                                                                                                                                                                                | Priorities of maskable interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                        | 17.3.4                                                                                                                                                                                                                                | Interrupt control register (xxICn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                  |

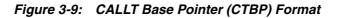

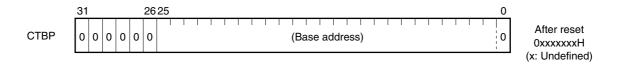

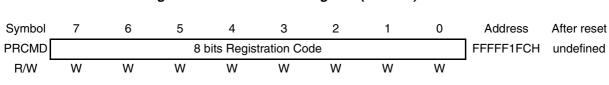

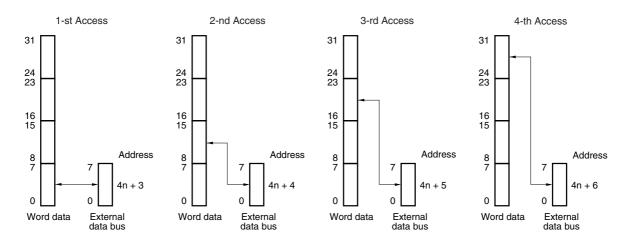

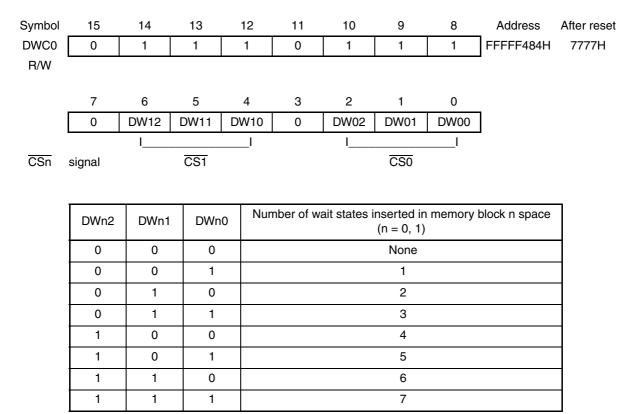

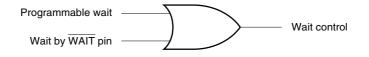

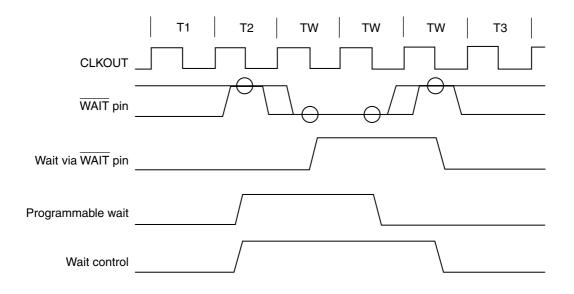

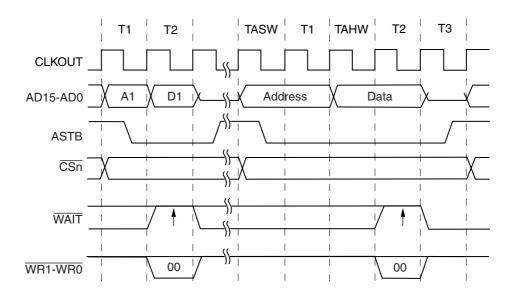

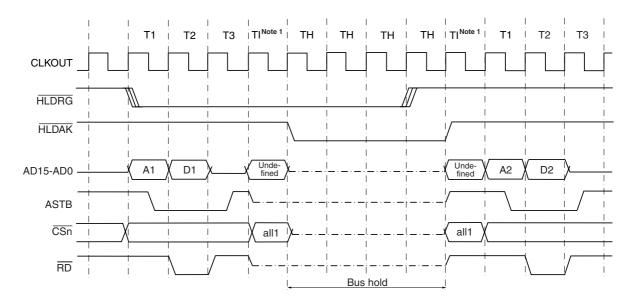

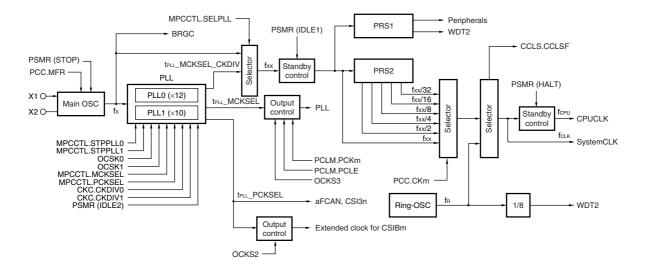

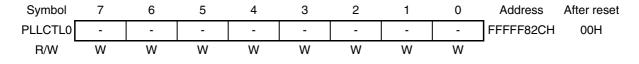

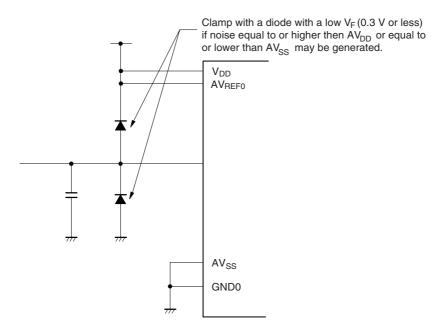

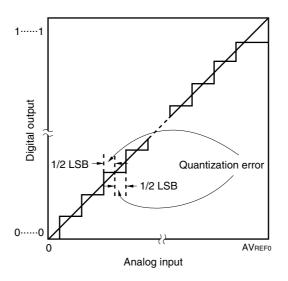

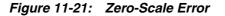

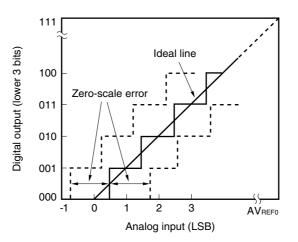

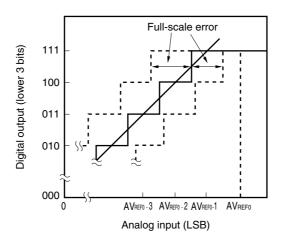

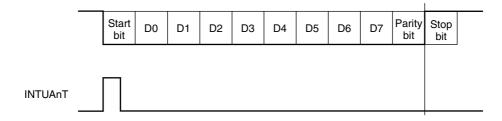

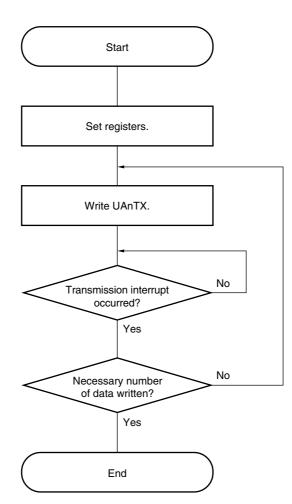

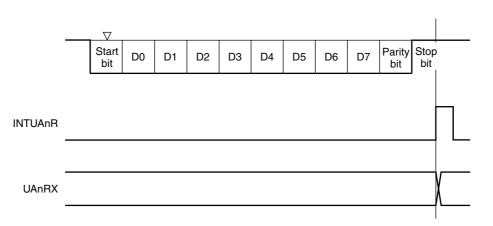

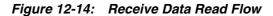

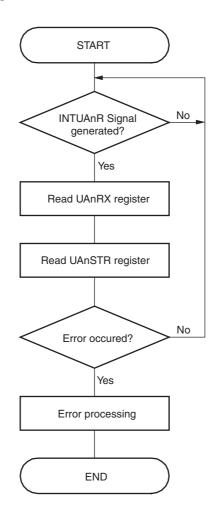

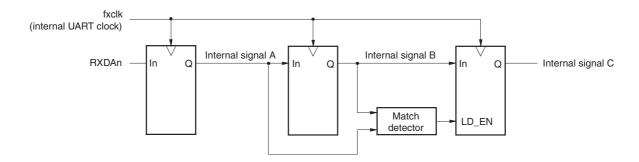

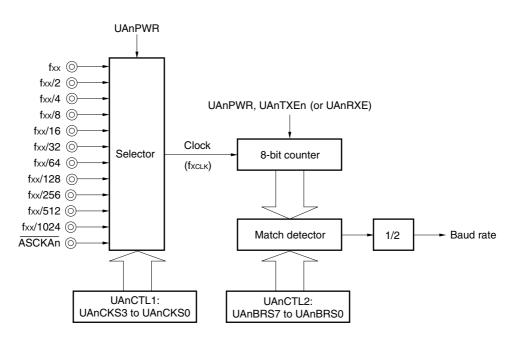

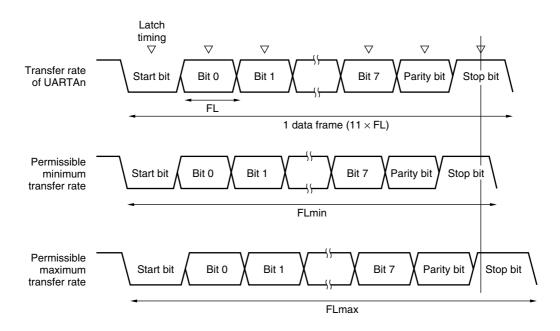

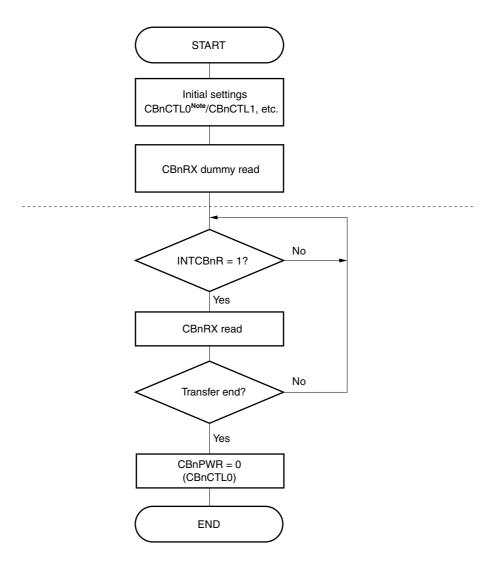

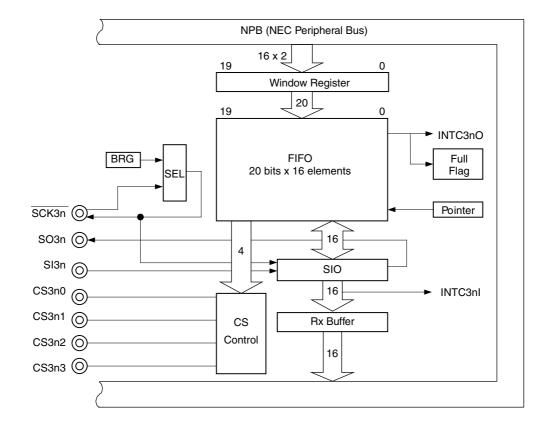

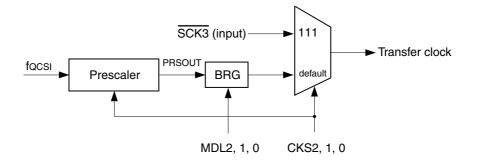

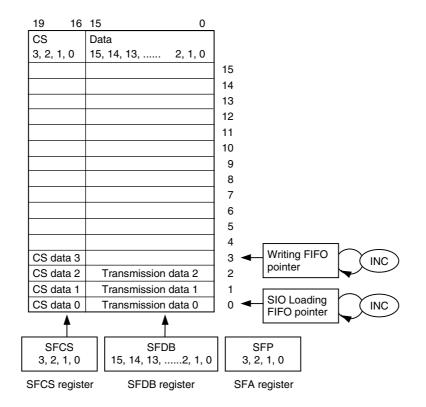

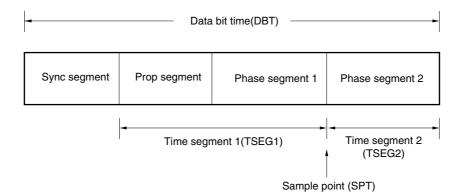

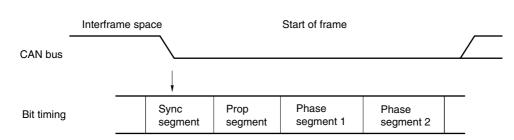

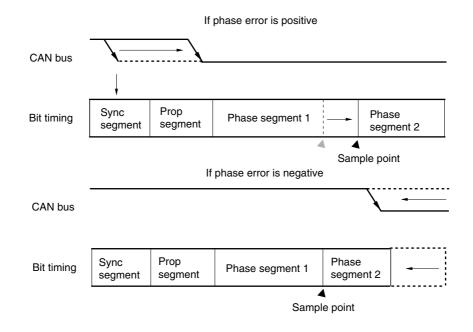

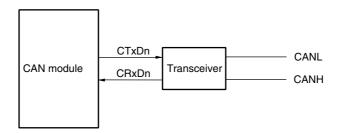

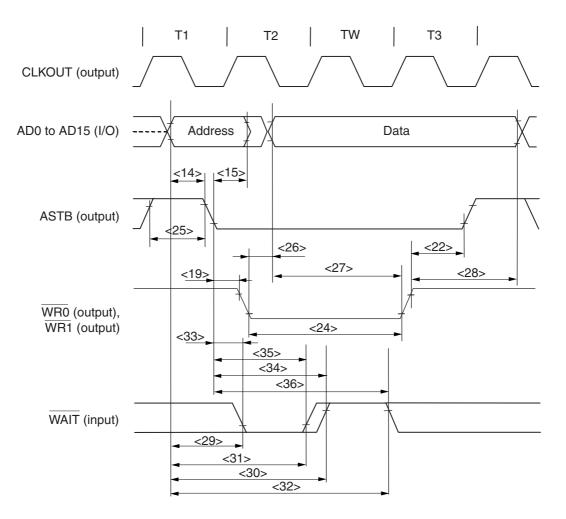

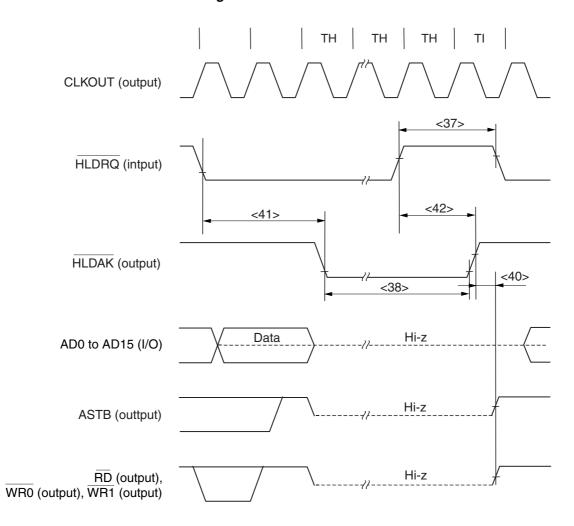

|      |                                                                                                                        | 17.3.5                                                                                                                                                                                                                                | Interrupt mask registers 0 to 3 (IMR0 to IMR3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                  |