The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH72531

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family

SH72531 R5F72531KFPU SH72531D R5F72531DKFPU

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics

does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages

incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

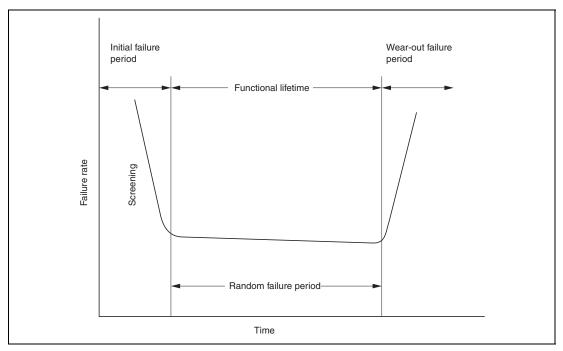

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

### 5. Reading from/Writing to Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

# **Preface**

This LSI is an RISC (Reduced Instruction Set Computer) microcontroller that includes a Renesas original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Target users are expected to understand the fundamentals of

electrical circuits, logical circuits, and microcontrollers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the target users.

Refer to the SH-2A, SH2A-FPU Software Manual for a detailed description of the

instruction set.

Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU's functions

Read the SH-2A, SH2A-FPU Software Manual.

• In order to understand the details of a register when its name is known

Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 29, List of Registers.

### Examples

The notation used for register names, bit names, numbers, and symbols in this manual is described below.

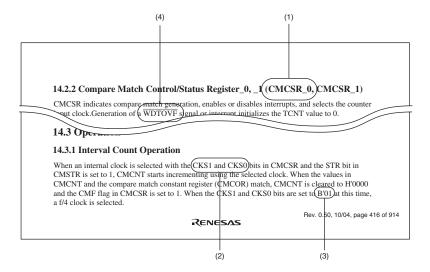

#### (1) Registers

The style (register name)\_(channel number) is used in cases where the same or a similar function is implemented on more than one channel.

Example: CMCSR\_0

#### (2) Bits

When bit names are given in this manual, the higher-order bits are to the left and the lower-order bits are to the right.

Example: CKS1, CKS0

#### (3) Numbers

Binary numbers are given as B'xxxx, hexadecimal are given as H'xxxx, and decimal are given as xxxx.

Examples: B'11 or 11, H'EFA0, 1234

#### (4) Symbols

An overbar is added to the names of active-low signals.

Example: WDTOVF

Note: The bit names and sentences in the above figure are examples, and have nothing to do with the contents of this manual.

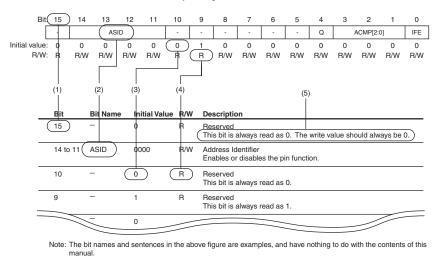

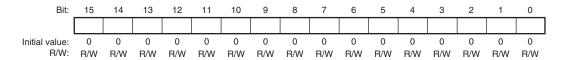

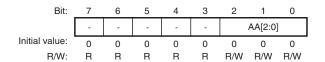

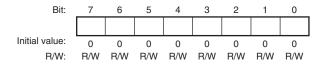

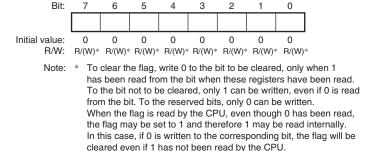

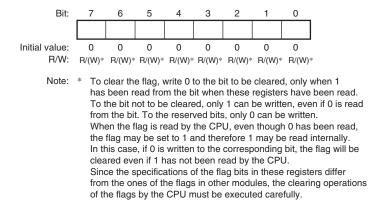

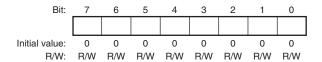

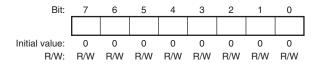

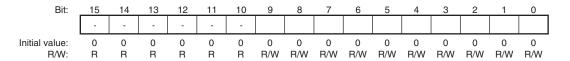

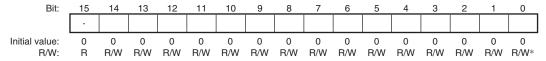

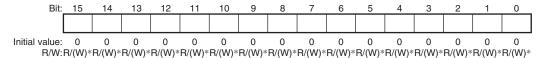

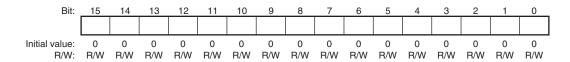

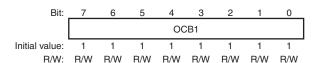

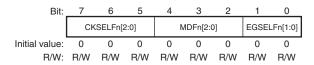

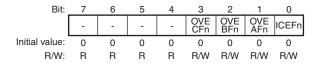

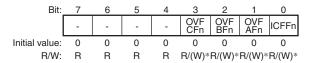

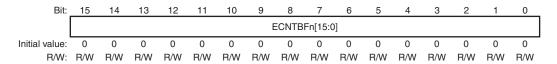

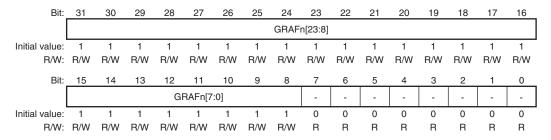

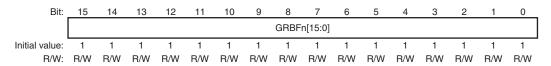

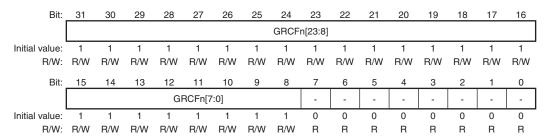

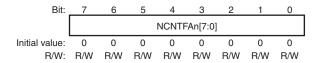

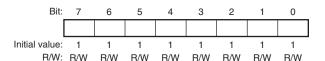

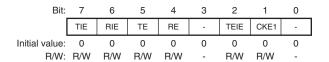

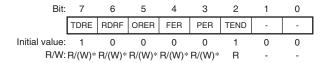

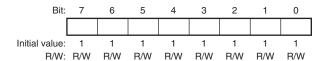

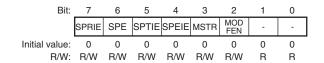

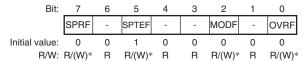

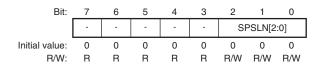

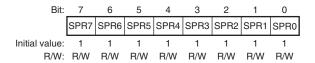

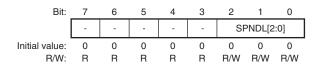

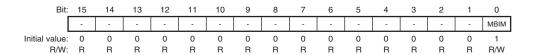

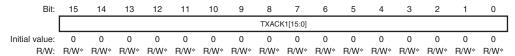

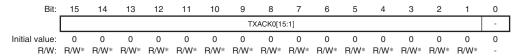

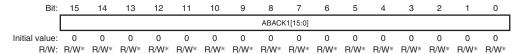

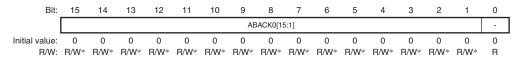

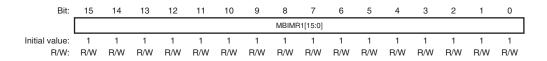

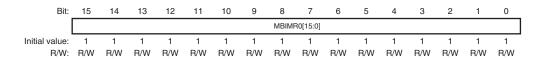

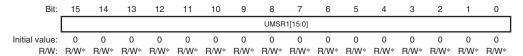

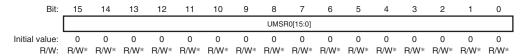

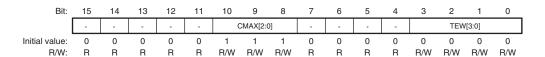

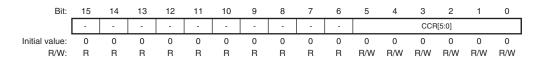

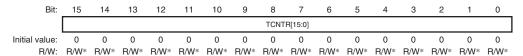

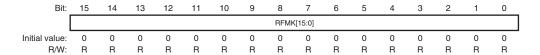

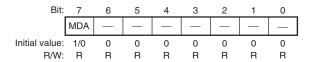

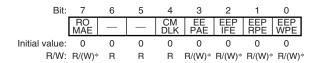

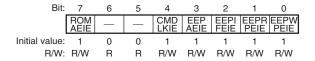

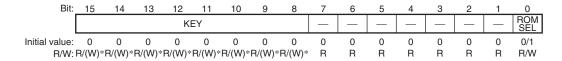

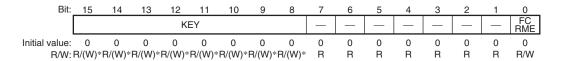

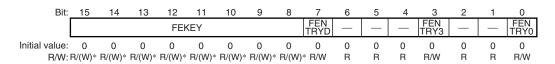

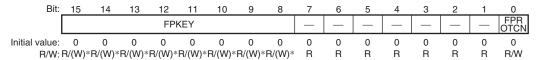

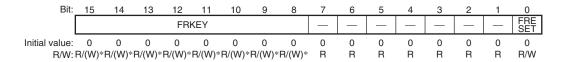

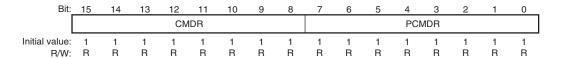

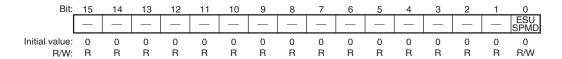

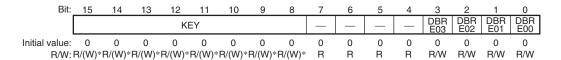

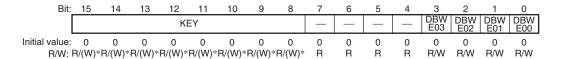

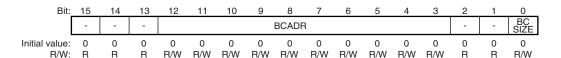

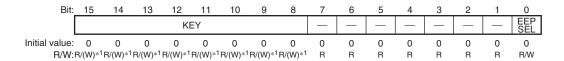

Notation in bit figures and tables describing arrangements of bits

Each register description includes a figure that illustrates the arrangement of bits and a table that describes the meanings of settings in the bits.

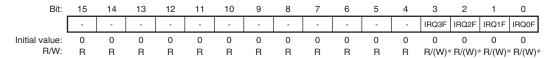

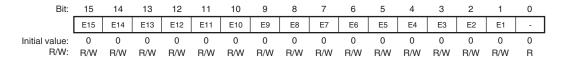

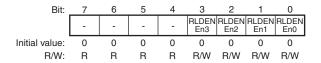

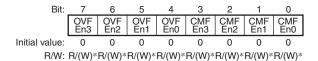

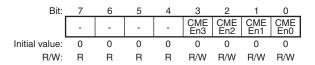

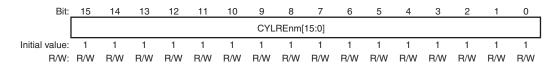

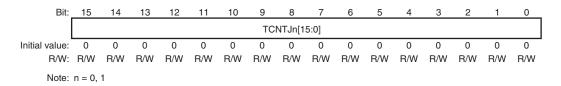

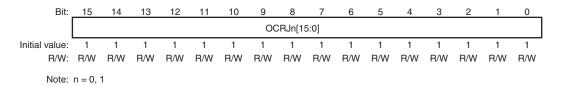

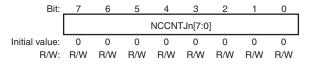

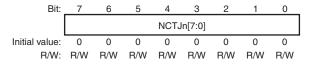

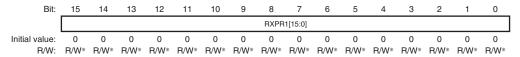

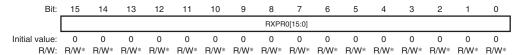

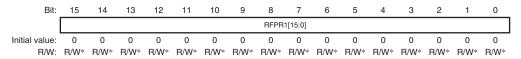

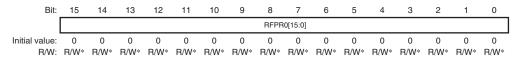

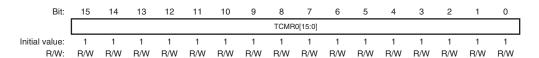

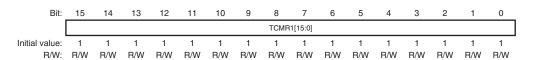

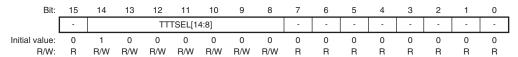

(1) Bit

Indicates the bit number.

In the case of a 32-bit register, the bits are arranged in order from 31 to 0, and in the case of a 16-bit register, the bits are arranged in the order from 15 to 0.

(2) Bit Name

The short form of the name of the bit or bit field within the register.

When the individual bits of bit fields have to be clearly indicated, notation allowing this is included (e.g., ASID[3:0]).

A reserved bit is indicated by -.

Instead of a bit name, a blank is used for some bits, such as those of timer counters.

(3) Initial Value

Indicates the value of each bit after a power-on reset, i.e., the initial value.

0: Initial value is 0

1: Initial value is 1

-: Initial value is undefined

(4) R/W

Indicates whether each bit is readable or writable, or either writing to or reading from the bit is prohibited.

The notation is as follows:

R/W: Bit or field is readable and writable.

R/(W): Bit or field is readable and writable.

However, writing is only performed to clear the flag.

R: Bit or field is readable and writable.

However, "R" is indicated for all reserved bits. When writing to the bit is required, write the value stated in the bit table or the initial value.

W: Bit or field is readable and writable.

However, only the value in the bit table is guaranteed when reading from the bit.

Description

Describes the function enabled by setting the bit.

All trademarks and registered trademarks are the property of their respective owners.

# Contents

| Secti | on I     | Jverview                              | I    |

|-------|----------|---------------------------------------|------|

| 1.1   | SH725    | 31 Features                           | 1    |

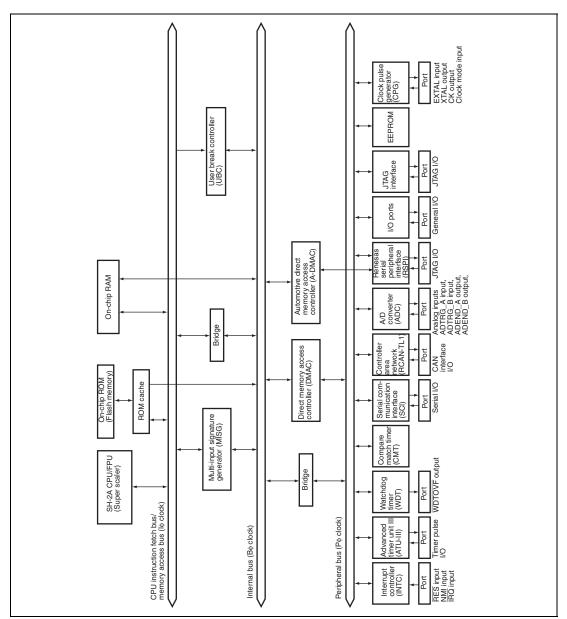

| 1.2   | Block I  | Diagram                               | . 10 |

| 1.3   | Pin Des  | scriptions                            | . 11 |

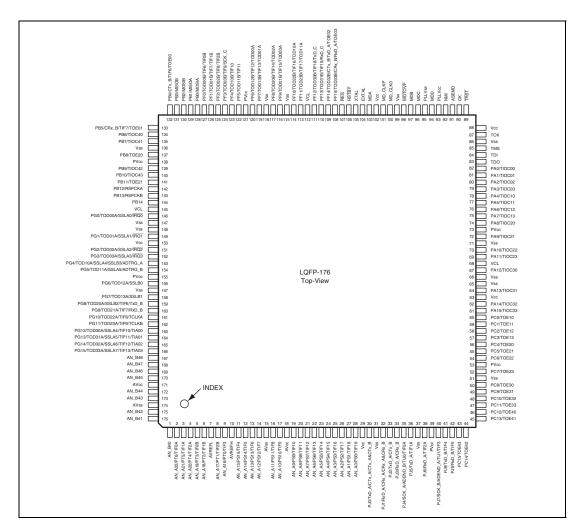

|       | 1.3.1    | Pin Arrangements                      | 11   |

|       | 1.3.2    | Pin Functions                         | 12   |

|       | 1.3.3    | List of Pins                          | . 19 |

| Secti | on 2     | CPU                                   | .25  |

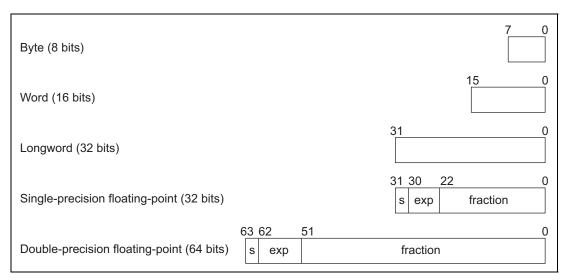

| 2.1   | Data Fo  | ormat                                 | 25   |

| 2.2   | Registe  | r Descriptions                        | 25   |

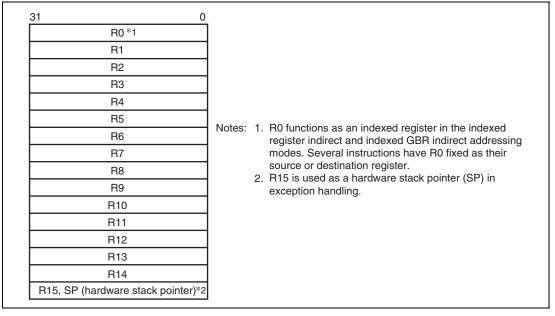

|       | 2.2.1    | General Registers                     | 25   |

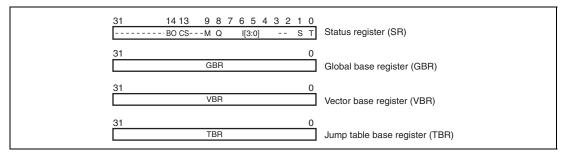

|       | 2.2.2    | Control Registers                     | 26   |

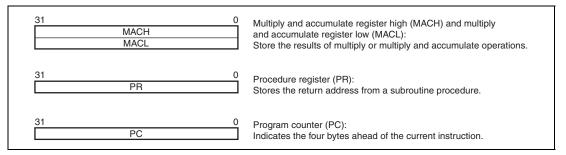

|       | 2.2.3    | System Registers                      | 28   |

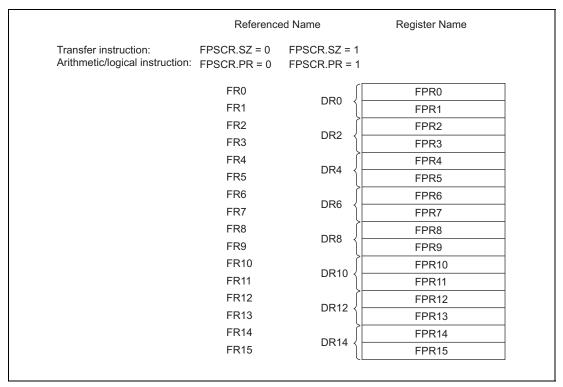

|       | 2.2.4    | Floating-Point Registers              | 29   |

|       | 2.2.5    | Floating-Point System Registers       | 30   |

|       | 2.2.6    | Register Bank                         | 33   |

|       | 2.2.7    | Initial Values of Registers           | 33   |

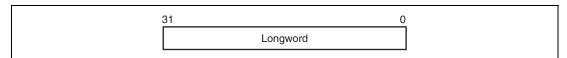

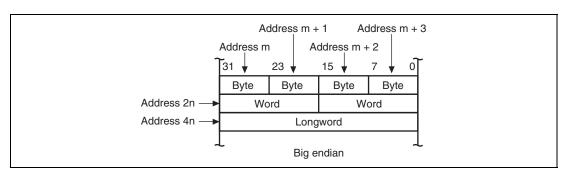

| 2.3   | Data Fo  | ormats                                | 34   |

|       | 2.3.1    | Data Format in Registers              | 34   |

|       | 2.3.2    | Data Formats in Memory                | 34   |

|       | 2.3.3    | Immediate Data Format                 | 35   |

| 2.4   | Instruct | tion Features                         | 36   |

|       | 2.4.1    | RISC-Type Instruction Set             | 36   |

|       | 2.4.2    | Addressing Modes                      | 40   |

|       | 2.4.3    | Instruction Format                    | 45   |

| 2.5   | Instruct | tion Set                              | 49   |

|       | 2.5.1    | Instruction Set by Classification     | 49   |

|       | 2.5.2    | Data Transfer Instructions            | 56   |

|       | 2.5.3    | Arithmetic Operation Instructions     | 60   |

|       | 2.5.4    | Logic Operation Instructions          | 63   |

|       | 2.5.5    | Shift Instructions                    | 64   |

|       | 2.5.6    | Branch Instructions                   | 65   |

|       | 2.5.7    | System Control Instructions           | 67   |

|       | 2.5.8    | Floating-Point Operation Instructions | . 69 |

|       | 2.5.9    | FPU-Related CPU Instructions          | 71   |

|       |          |                                       |      |

|      | 2.5.10 Bit Manipulation Instructions                     |     |

|------|----------------------------------------------------------|-----|

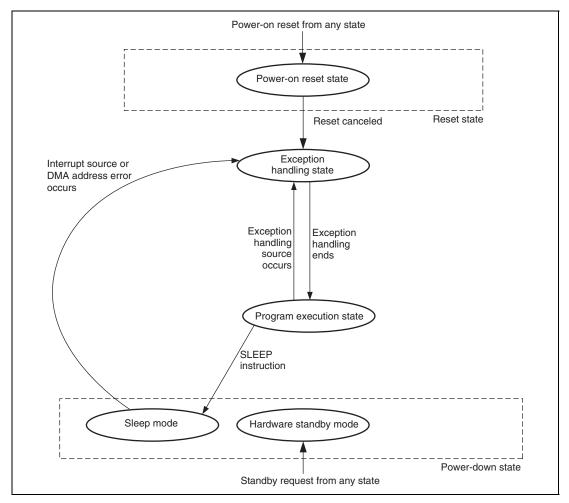

| 2.6  | Processing States                                        | 73  |

| Sec  | etion 3 Operating Modes                                  | 75  |

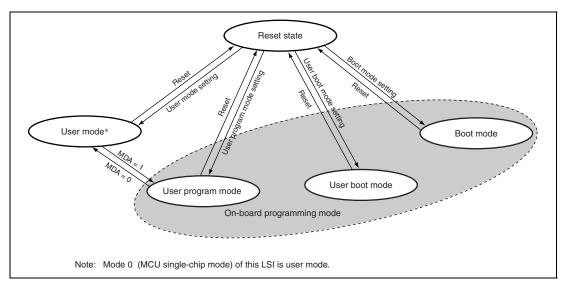

| 3.1  | Types of Operating Modes and Selection                   |     |

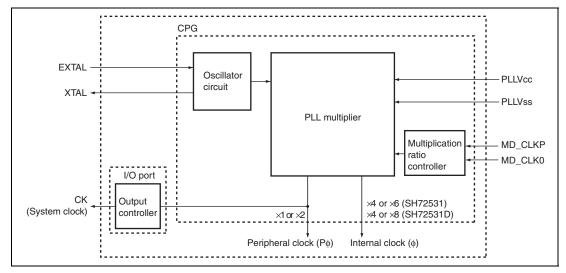

| Sacr | etion 4 Clock Pulse Generator (CPG)                      | 77  |

| 4.1  | Overview                                                 |     |

| 4.1  | Pin Configuration                                        |     |

| 4.3  | Frequency Ranges and Clock Selection                     |     |

| 4.4  | Clock Source                                             |     |

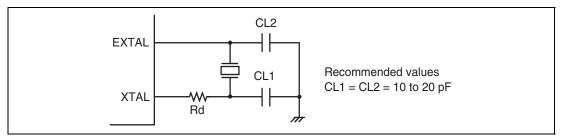

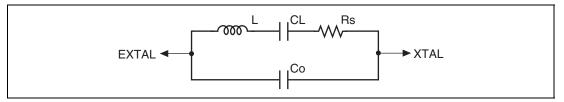

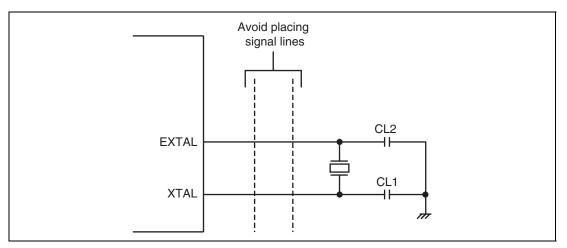

| 7.7  | 4.4.1 Connecting Crystal Resonator                       |     |

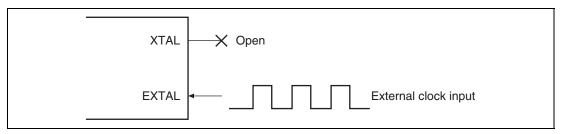

|      | 4.4.2 External Clock Input                               |     |

| 4.5  | Usage Notes                                              |     |

| 1.0  | 4.5.1 Note on Board Design                               |     |

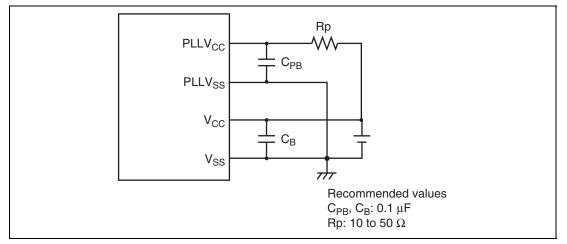

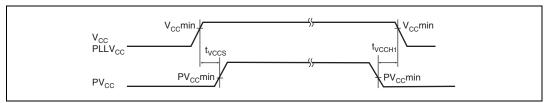

|      | 4.5.2 Note on Connecting Power Supply for PLL Oscillator |     |

| Sec  | etion 5 Address Space                                    | 85  |

| Sec  | etion 6 Reset                                            | 87  |

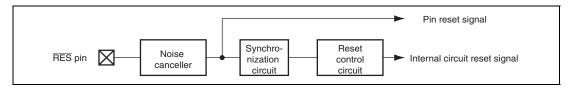

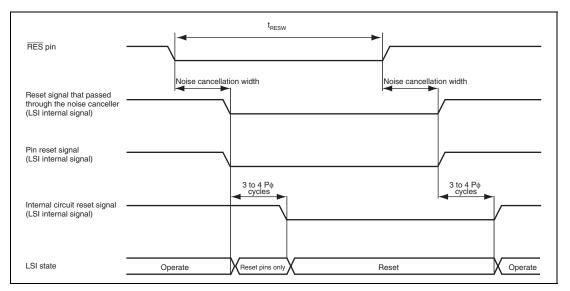

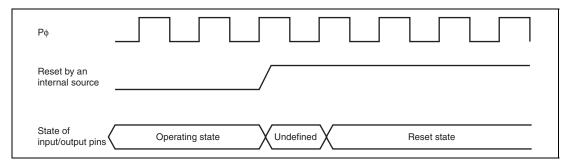

| 6.1  | Reset Operation                                          | 87  |

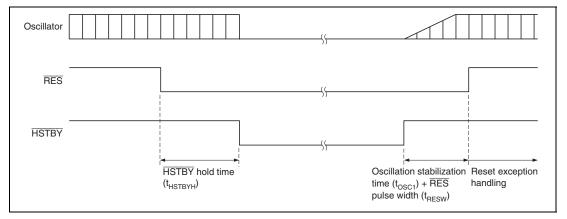

|      | 6.1.1 Reset at Power-On                                  | 88  |

|      | 6.1.2 Reset during Operation                             | 88  |

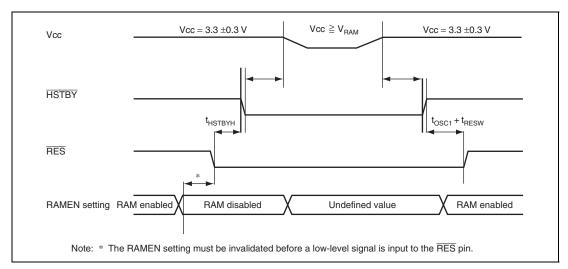

|      | 6.1.3 On-chip RAM Data Retention during Reset            | 88  |

| 6.2  | Internal State after Reset Cancellation                  | 89  |

| Sec  | etion 7 Exception Handling                               | 91  |

| 7.1  | Overview                                                 |     |

|      | 7.1.1 Types of Exception Handling and Priority           |     |

|      | 7.1.2 Exception Handling Operations                      |     |

|      | 7.1.3 Exception Handling Vector Table                    |     |

| 7.2  | Resets                                                   | 97  |

|      | 7.2.1 Types of Reset                                     | 97  |

|      | 7.2.2 Power-On Reset                                     | 97  |

| 7.3  | Address Errors                                           | 99  |

|      | 7.3.1 Address Error Sources                              | 99  |

|      | 7.3.2 Address Error Exception Handling                   | 100 |

| 7.4  | Register Bank Errors                                     | 101 |

|      | 7.4.1 Register Bank Error Sources                        | 101 |

|      | 7.4.2 Register Bank Error Exception Handling             | 101 |

| 7.5  | Interru | ıpts                                                                  | 102 |

|------|---------|-----------------------------------------------------------------------|-----|

|      | 7.5.1   | Interrupt Sources                                                     | 102 |

|      | 7.5.2   | Interrupt Priority Level                                              | 103 |

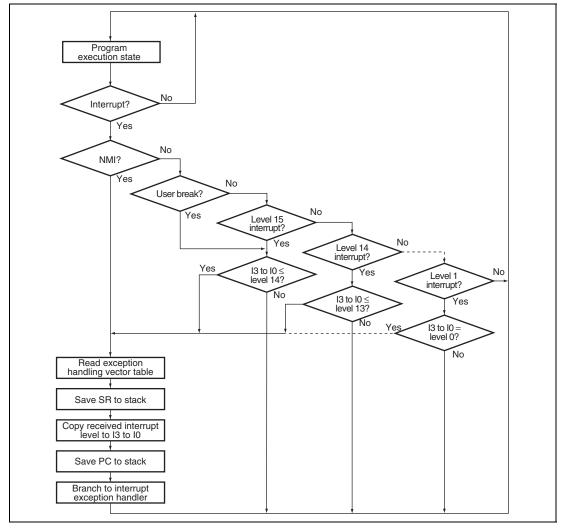

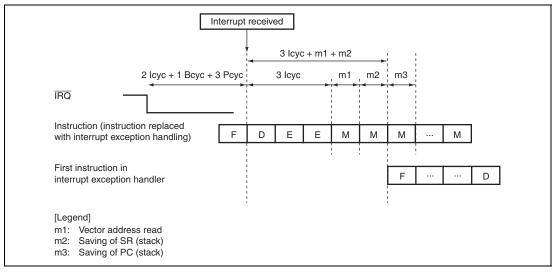

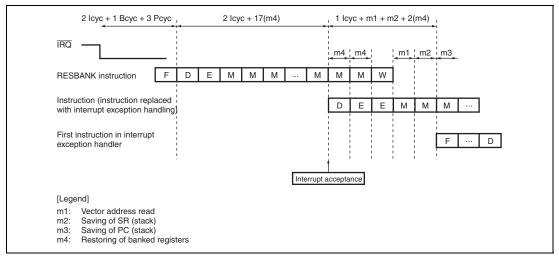

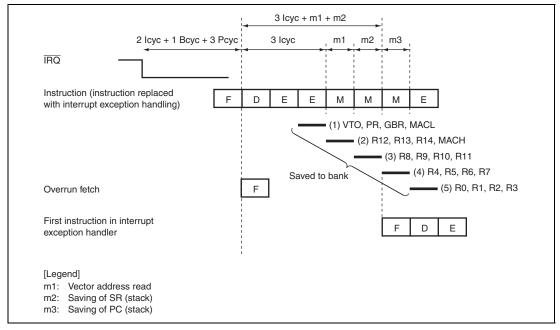

|      | 7.5.3   | Interrupt Exception Handling                                          | 104 |

| 7.6  | Excep   | tions Triggered by Instructions                                       | 105 |

|      | 7.6.1   | Types of Exceptions Triggered by Instructions                         | 105 |

|      | 7.6.2   | Trap Instructions                                                     | 106 |

|      | 7.6.3   | Slot Illegal Instructions                                             | 106 |

|      | 7.6.4   | General Illegal Instructions                                          | 107 |

|      | 7.6.5   | Integer Division Exceptions                                           | 107 |

|      | 7.6.6   | FPU Exceptions                                                        | 108 |

| 7.7  | When    | Exception Sources Are Not Accepted                                    | 109 |

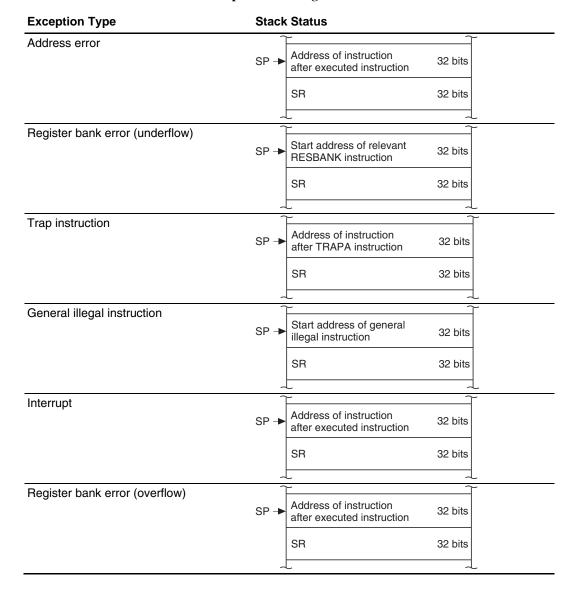

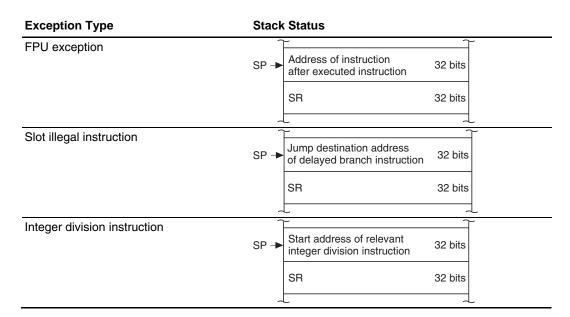

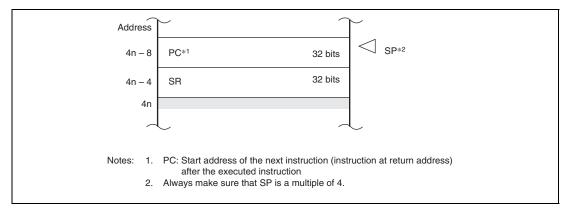

| 7.8  | Stack   | Status after Exception Handling Ends                                  | 110 |

| 7.9  | Usage   | Notes                                                                 | 112 |

|      | 7.9.1   | Value of Stack Pointer (SP)                                           | 112 |

|      | 7.9.2   | Value of Vector Base Register (VBR)                                   | 112 |

|      | 7.9.3   | Address Errors Caused by Stacking of Address Error Exception Handling | 112 |

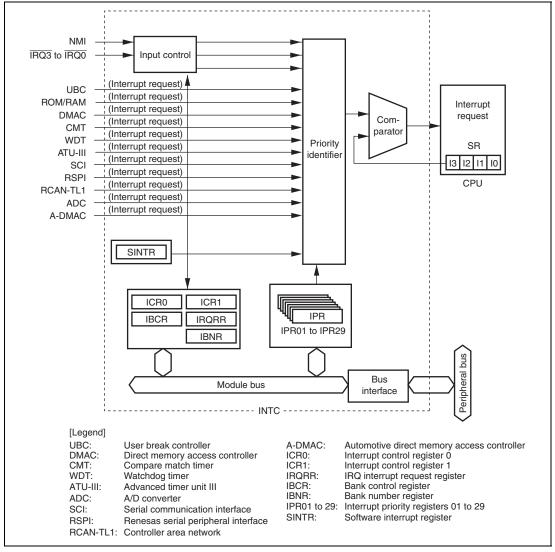

| Sect | tion 8  | Interrupt Controller (INTC)                                           | 113 |

| 8.1  |         | res                                                                   |     |

| 8.2  | Input/  | Output Pins                                                           | 115 |

| 8.3  | -       | rer Descriptions                                                      |     |

|      | 8.3.1   | Interrupt Priority Registers 01 to 29 (IPR01 to IPR29)                |     |

|      | 8.3.2   | Interrupt Control Register 0 (ICR0)                                   | 120 |

|      | 8.3.3   | Interrupt Control Register 1 (ICR1)                                   |     |

|      | 8.3.4   | IRQ Interrupt Request Register (IRQRR)                                |     |

|      | 8.3.5   | Bank Control Register (IBCR)                                          |     |

|      | 8.3.6   | Bank Number Register (IBNR)                                           |     |

|      | 8.3.7   | Software Interrupt Registers 1 to 15 (SINTR1 to SINTR15)              |     |

| 8.4  | Interru | ipt Sources                                                           |     |

|      | 8.4.1   | NMI Interrupt                                                         | 128 |

|      | 8.4.2   | User Break Interrupt                                                  |     |

|      | 8.4.3   | IRQ Interrupts                                                        | 128 |

|      | 8.4.4   | Memory Error Interrupt                                                | 129 |

|      | 8.4.5   | Software Interrupts (SINT)                                            |     |

|      | 8.4.6   | On-Chip Peripheral Module Interrupts                                  | 129 |

| 8.5  | Interru | upt Exception Handling Vector Table and Priority                      |     |

| 8.6  |         | tion                                                                  |     |

|      | 8.6.1   | Interrupt Operation Sequence                                          |     |

|      | 8.6.2   | Stack after Interrupt Exception Handling                              |     |

| 8.7  | Interru | pt Response Time                                                       | 150 |

|------|---------|------------------------------------------------------------------------|-----|

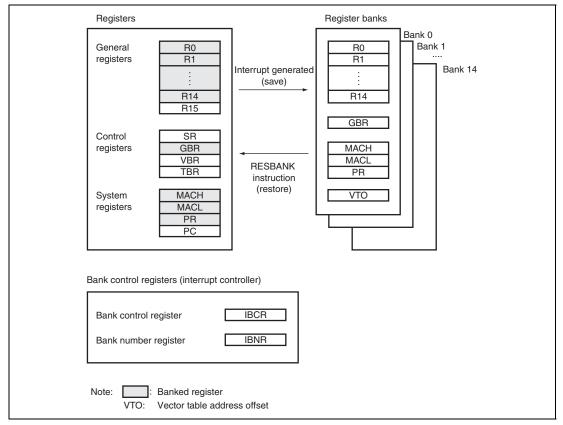

| 8.8  | Registe | er Banks                                                               | 155 |

|      | 8.8.1   | Banked Registers and Input/Output Method                               | 156 |

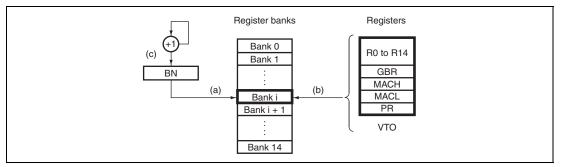

|      | 8.8.2   | Bank Saving and Restoring Operations                                   | 156 |

|      | 8.8.3   | Saving and Restoring Operations after Saving Registers to All Banks    |     |

|      | 8.8.4   | Register Bank Exception                                                |     |

|      | 8.8.5   | Register Bank Error Exception Handling                                 | 159 |

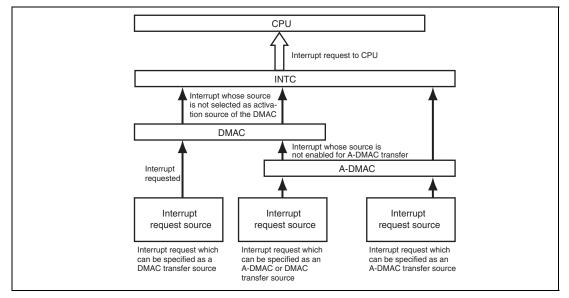

| 8.9  | Data T  | ransfer with Interrupt Request Signals                                 |     |

|      | 8.9.1   | Interrupt Request Signals as Sources for CPU (Not for Activating DMAC) | 161 |

|      | 8.9.2   | Interrupt Request Signals as Sources for Activating DMAC (Not for CPU) | 161 |

|      | 8.9.3   | Interrupt Request Signals as Sources for Activating A-DMAC             |     |

|      |         | (Not for CPU)                                                          | 162 |

| 8.10 | Usage   | Note                                                                   | 162 |

|      | 8.10.1  | Timing to Clear Interrupt Source                                       | 162 |

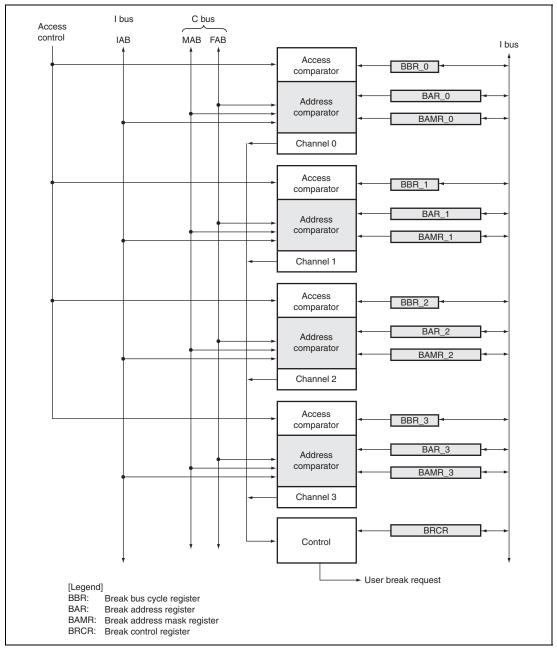

| Sect | ion 9   | User Break Controller (UBC)                                            | 163 |

| 9.1  |         | 28                                                                     |     |

| 9.2  | Registe | er Descriptions                                                        | 165 |

|      | 9.2.1   | Break Address Register_0 (BAR_0)                                       |     |

|      | 9.2.2   | Break Address Mask Register_0 (BAMR_0)                                 | 167 |

|      | 9.2.3   | Break Bus Cycle Register_0 (BBR_0)                                     | 168 |

|      | 9.2.4   | Break Address Register_1 (BAR_1)                                       | 170 |

|      | 9.2.5   | Break Address Mask Register_1 (BAMR_1)                                 |     |

|      | 9.2.6   | Break Bus Cycle Register_1 (BBR_1)                                     | 172 |

|      | 9.2.7   | Break Address Register_2 (BAR_2)                                       |     |

|      | 9.2.8   | Break Address Mask Register_2 (BAMR_2)                                 | 175 |

|      | 9.2.9   | Break Bus Cycle Register_2 (BBR_2)                                     | 176 |

|      | 9.2.10  | Break Address Register_3 (BAR_3)                                       | 178 |

|      | 9.2.11  | Break Address Mask Register_3 (BAMR_3)                                 |     |

|      | 9.2.12  | Break Bus Cycle Register_3 (BBR_3)                                     |     |

|      | 9.2.13  | Break Control Register (BRCR)                                          | 182 |

| 9.3  | Operat  | ion                                                                    |     |

|      | 9.3.1   | Flow of the User Break Operation                                       | 186 |

|      | 9.3.2   | Break on Instruction Fetch Cycle                                       | 187 |

|      | 9.3.3   | Break on Data Access Cycle                                             |     |

|      | 9.3.4   | Value of Saved Program Counter                                         |     |

|      | 9.3.5   | Usage Examples                                                         |     |

| 9.4  | Usage   | Notes                                                                  |     |

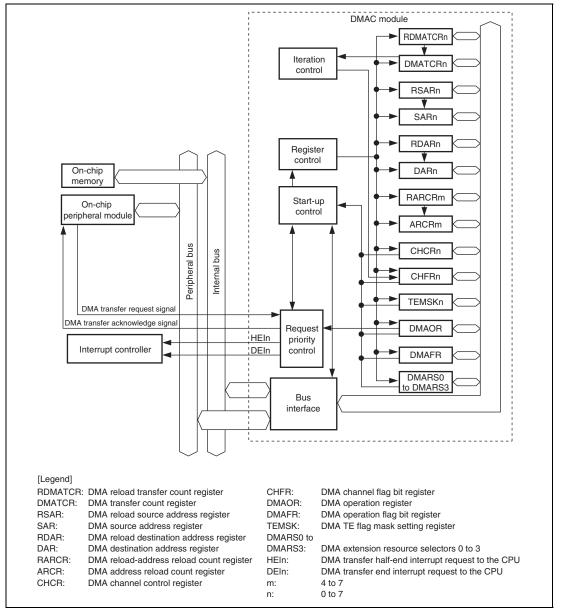

| Sect | ion 10  | Direct Memory Access Controller (DMAC)                           | 195 |

|------|---------|------------------------------------------------------------------|-----|

| 10.1 |         | 98                                                               |     |

| 10.2 |         | er Descriptions                                                  |     |

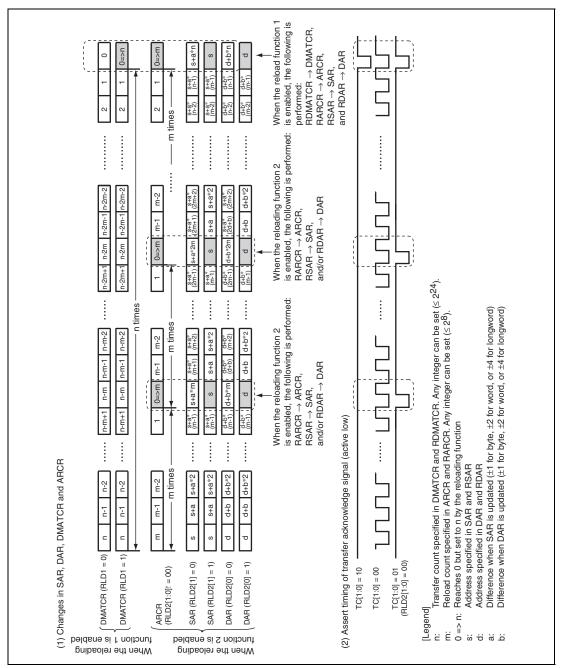

|      | 10.2.1  | DMA Source Address Registers 0 to 7 (SAR0 to SAR7)               | 204 |

|      | 10.2.2  | DMA Destination Address Registers 0 to 7 (DAR0 to DAR7)          | 204 |

|      | 10.2.3  | DMA Transfer Count Registers 0 to 7 (DMATCR0 to DMATCR7)         | 205 |

|      | 10.2.4  | DMA Channel Control Registers 0 to 7 (CHCR0 to CHCR7)            | 205 |

|      | 10.2.5  | DMA Channel Flag Bit Registers 0 to 7 (CHFR0 to CHFR7)           | 211 |

|      | 10.2.6  | DMA TE Flag Mask Setting Registers 0 to 7 (TEMSK0 to TEMSK7)     | 214 |

|      | 10.2.7  | DMA Reload Source Address Registers 0 to 7 (RSAR0 to RSAR7)      | 216 |

|      | 10.2.8  | DMA Reload Destination Address Registers 0 to 7 (RDAR0 to RDAR7) | 217 |

|      | 10.2.9  | DMA Reload Transfer Count Registers 0 to 7                       |     |

|      |         | (RDMATCR0 to RDMATCR7)                                           | 218 |

|      | 10.2.10 | DMA Address Reload Count Registers 4 to 7 (ARCR4 to ARCR7)       | 219 |

|      | 10.2.11 | DMA Reload-Address Reload Count Registers 4 to 7                 |     |

|      |         | (RARCR4 to RARCR7)                                               | 220 |

|      | 10.2.12 | 2 DMA Operation Register (DMAOR)                                 | 221 |

|      |         | B DMA Operation Flag Bit Register (DMAFR)                        |     |

|      |         | DMA Extension Resource Selectors 0 to 3 (DMARS0 to DMARS3)       |     |

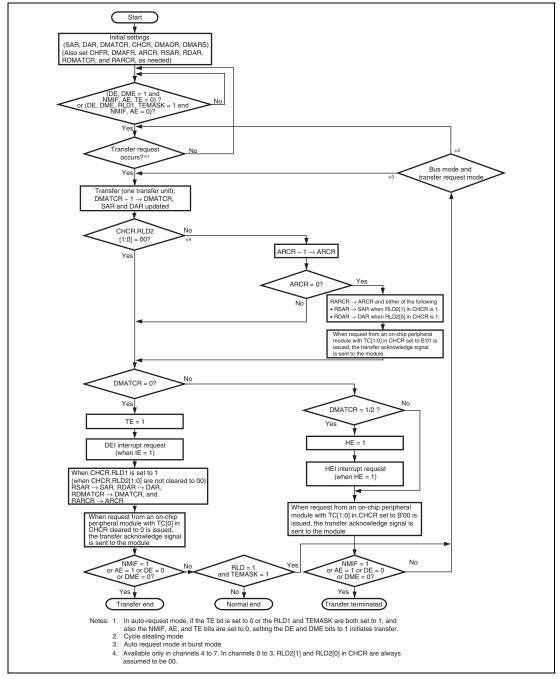

| 10.3 | Operati | ion                                                              | 229 |

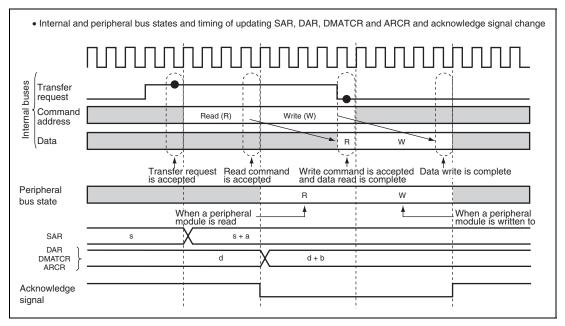

|      | 10.3.1  | Transfer Flow                                                    | 229 |

|      | 10.3.2  | DMA Transfer Requests                                            | 232 |

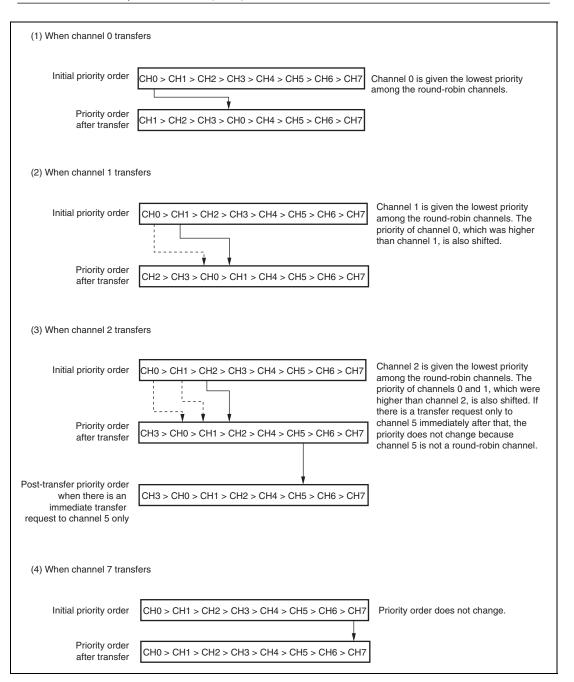

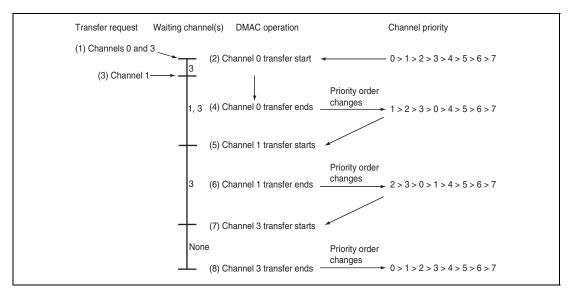

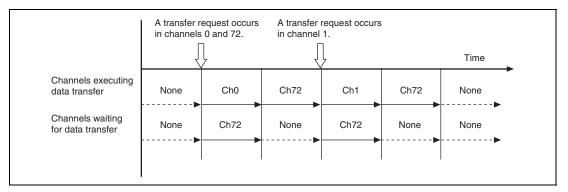

|      | 10.3.3  | Channel Priority                                                 | 236 |

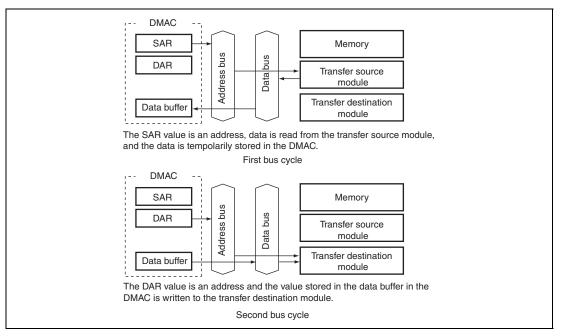

|      | 10.3.4  | DMA Transfer Types                                               | 240 |

| 10.4 | Special | Operations                                                       | 246 |

|      | 10.4.1  | Address Error Operation                                          | 246 |

|      | 10.4.2  | Operation on NMI                                                 | 246 |

|      |         | Operation of Reloading Function 1                                |     |

|      | 10.4.4  | Operation of Reloading Function 2                                | 247 |

|      | 10.4.5  | Interface with On-Chip Peripheral Module                         | 247 |

|      | 10.4.6  | Integer to Floating-Point Conversion Operation                   | 247 |

| 10.5 | Usage   | Note                                                             | 250 |

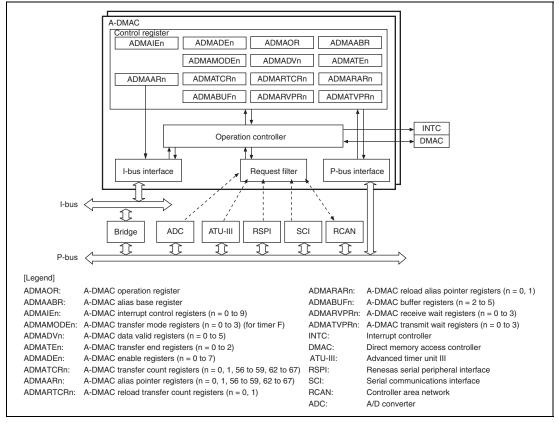

| Sect | ion 11  | Automotive Direct Memory Access Controller (A-DMAC)              | 251 |

| 11.1 |         | es                                                               |     |

|      |         | Input/Output Pins                                                |     |

| 11.2 |         | er Descriptions                                                  |     |

|      | _       | A-DMAC Operation Register (ADMAOR)                               |     |

|      |         | A-DMAC Alias Base Register (ADMAABR)                             |     |

|                                               | 11.2.3 A-DMAC Interrupt Control Registers (ADMAIE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 264                                                                                     |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                               | 11.2.4 A-DMAC Data Valid Registers (ADMADV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 265                                                                                     |

|                                               | 11.2.5 A-DMAC Transfer End Registers (ADMATE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 266                                                                                     |

|                                               | 11.2.6 A-DMAC Enable Registers (ADMADE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 267                                                                                     |

|                                               | 11.2.7 A-DMAC Transfer Mode Registers (ADMAMODE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 268                                                                                     |

|                                               | 11.2.8 A-DMAC Transfer Count Registers (ADMATCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 269                                                                                     |

|                                               | 11.2.9 A-DMAC Alias Pointer Registers (ADMAAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 270                                                                                     |

|                                               | 11.2.10 A-DMAC Reload Transfer Count Registers (ADMARTCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 271                                                                                     |

|                                               | 11.2.11 A-DMAC Reload Alias Pointer Registers (ADMARAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

|                                               | 11.2.12 A-DMAC Buffer Registers (ADMABUF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 272                                                                                     |

|                                               | 11.2.13 A-DMAC Receive Wait Registers (ADMARVPR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 273                                                                                     |

|                                               | 11.2.14 A-DMAC Transmit Wait Registers (ADMATVPR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 274                                                                                     |

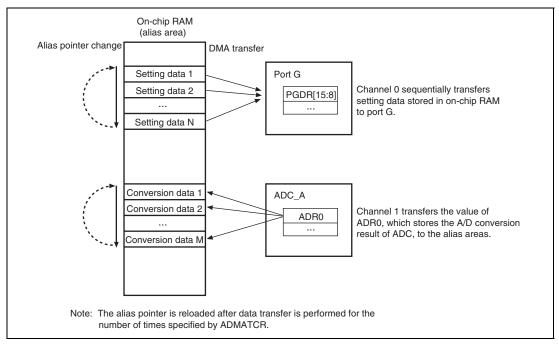

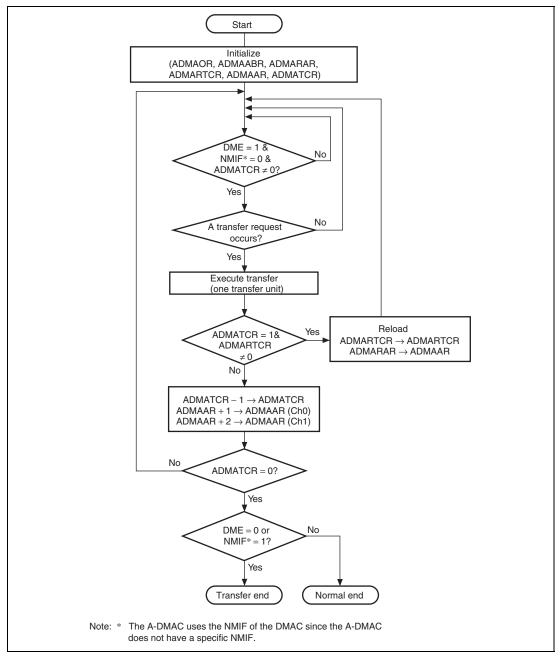

| 11.3                                          | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 275                                                                                     |

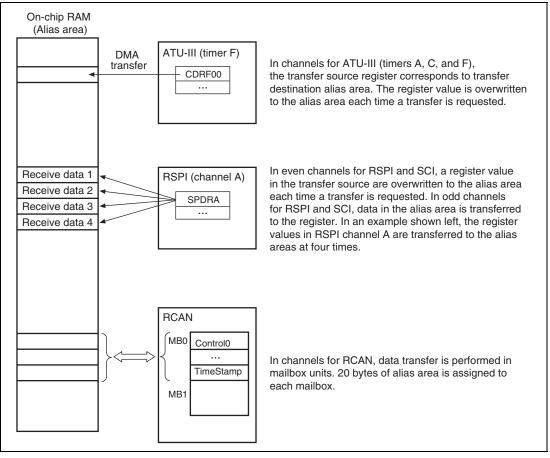

|                                               | 11.3.1 Alias Areas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 275                                                                                     |

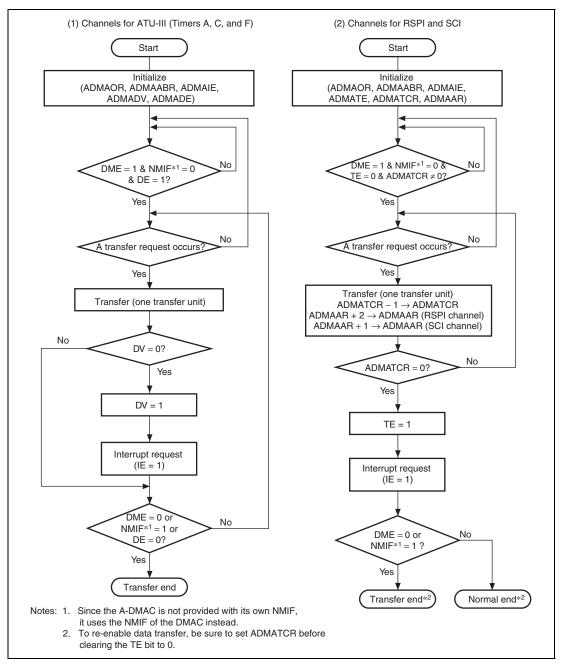

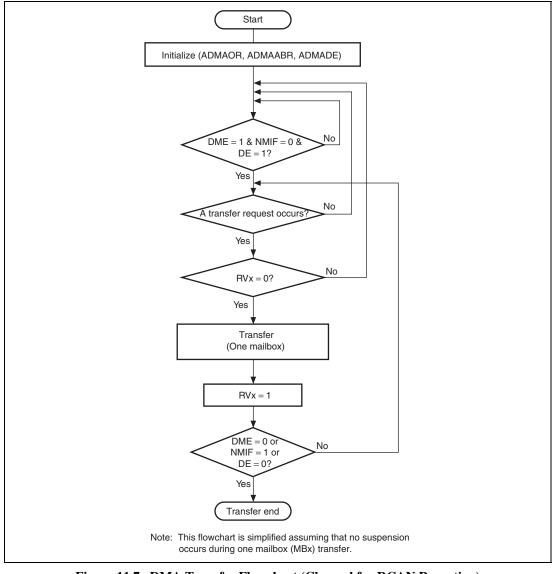

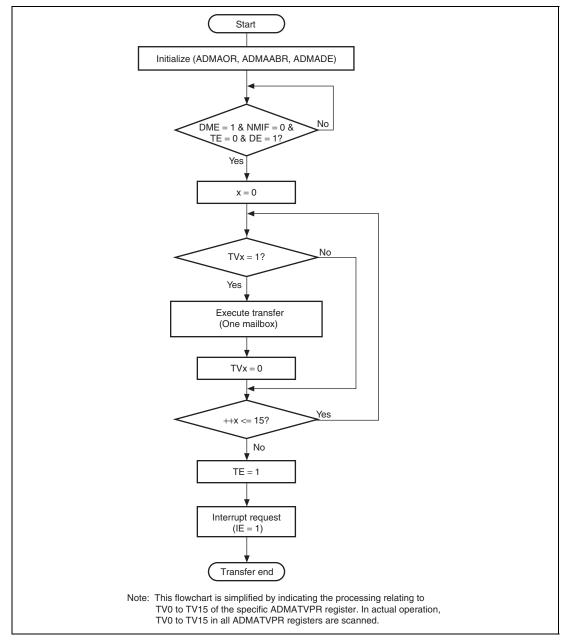

|                                               | 11.3.2 Each A-DMAC Channel Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 276                                                                                     |

|                                               | 11.3.3 Transfer Suspension and Resumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 292                                                                                     |

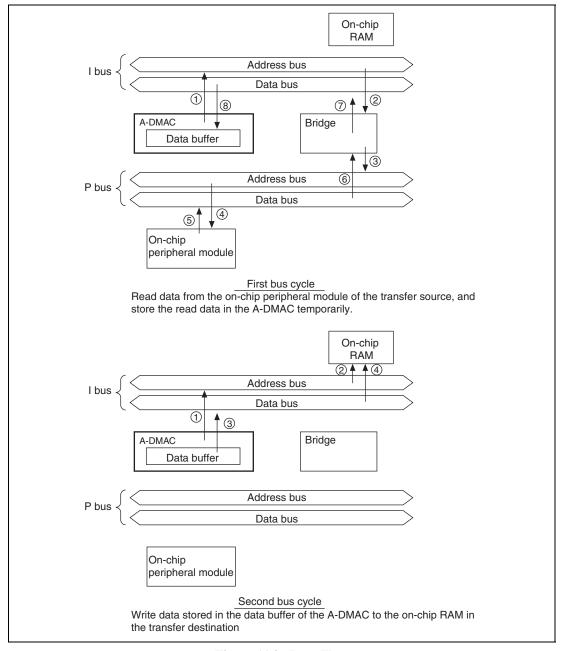

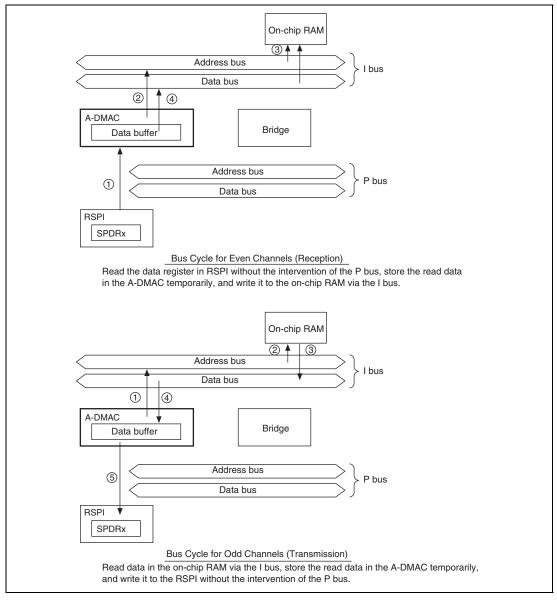

|                                               | 11.3.4 Bus Operation in Data Transfer by A-DMAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 293                                                                                     |

|                                               | 11.3.5 Channel Priorities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 298                                                                                     |

|                                               | 11.3.6 Transfer Enable/Disable Conditions and Interrupt Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 298                                                                                     |

| 11.4                                          | Usage Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 301                                                                                     |

| 11                                            | C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

|                                               | ion 12 Advanced Timer Unit III (ATU-III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 303                                                                                     |

|                                               | ion 12 Advanced Timer Unit III (ATU-III) Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 303                                                                                     |

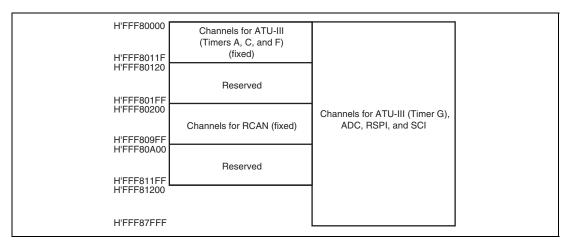

| Secti                                         | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 303<br>303                                                                              |

| Secti<br>12.1                                 | ion 12 Advanced Timer Unit III (ATU-III) Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 303<br>303                                                                              |

| Secti<br>12.1<br>12.2                         | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 303<br>303<br>307<br>327                                                                |

| Secti<br>12.1<br>12.2<br>12.3                 | ion 12 Advanced Timer Unit III (ATU-III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 303<br>303<br>307<br>327<br>328                                                         |

| Secti<br>12.1<br>12.2<br>12.3                 | ion 12 Advanced Timer Unit III (ATU-III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4         | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4         | ion 12 Advanced Timer Unit III (ATU-III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4         | ion 12 Advanced Timer Unit III (ATU-III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

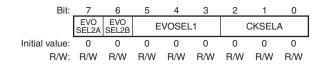

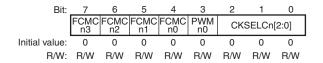

| Secti<br>12.1<br>12.2<br>12.3<br>12.4         | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus  Register Description of Common Controller  12.5.1 ATU-III Master Enable Register (ATUENR)  12.5.2 Clock Bus Control Register (CBCNT)                                                                                                                                                                                                                                                                |                                                                                         |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus  Register Description of Common Controller  12.5.1 ATU-III Master Enable Register (ATUENR)  12.5.2 Clock Bus Control Register (CBCNT)  12.5.3 Noise Cancellation Mode Register (NCMR)                                                                                                                                                                                                                |                                                                                         |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ion 12 Advanced Timer Unit III (ATU-III)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus  Register Description of Common Controller  12.5.1 ATU-III Master Enable Register (ATUENR)  12.5.2 Clock Bus Control Register (CBCNT)  12.5.3 Noise Cancellation Mode Register (NCMR)  Overview of Prescalers  Register Description of Prescalers                                                                                                                                                    |                                                                                         |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus  Register Description of Common Controller  12.5.1 ATU-III Master Enable Register (ATUENR)  12.5.2 Clock Bus Control Register (CBCNT)  12.5.3 Noise Cancellation Mode Register (NCMR)  Overview of Prescalers  Register Description of Prescalers  Register Description of Prescalers  12.7.1 Prescaler Registers 0 to 3 (PSCR0 to PSCR3)                                                            |                                                                                         |

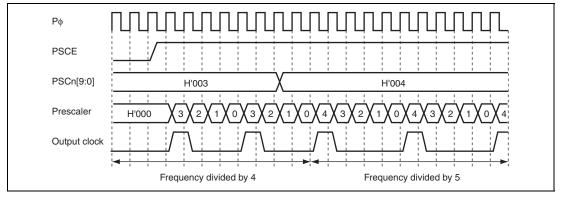

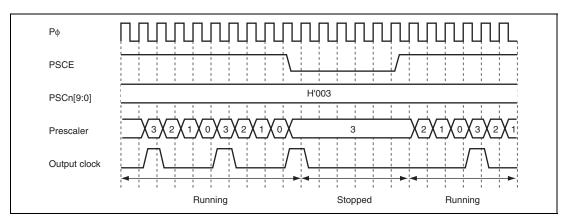

| Secti<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus  Register Description of Common Controller  12.5.1 ATU-III Master Enable Register (ATUENR)  12.5.2 Clock Bus Control Register (CBCNT)  12.5.3 Noise Cancellation Mode Register (NCMR)  Overview of Prescalers  Register Description of Prescalers  12.7.1 Prescaler Registers 0 to 3 (PSCR0 to PSCR3)  Operation of Prescalers                                                                       | 303<br>303<br>307<br>327<br>328<br>329<br>329<br>329<br>332<br>334<br>338<br>339<br>339 |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus  Register Description of Common Controller  12.5.1 ATU-III Master Enable Register (ATUENR)  12.5.2 Clock Bus Control Register (CBCNT)  12.5.3 Noise Cancellation Mode Register (NCMR)  Overview of Prescalers  Register Description of Prescalers  12.7.1 Prescaler Registers 0 to 3 (PSCR0 to PSCR3)  Operation of Prescalers  12.8.1 Starting Prescalers                                           | 303<br>303<br>307<br>327<br>328<br>329<br>329<br>332<br>334<br>338<br>339<br>339<br>339 |

| Secti<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5 | ion 12 Advanced Timer Unit III (ATU-III)  Features  Register Addresses  Input/Output Pins  Overview of Common Controller  12.4.1 Clock Bus  Register Description of Common Controller  12.5.1 ATU-III Master Enable Register (ATUENR)  12.5.2 Clock Bus Control Register (CBCNT)  12.5.3 Noise Cancellation Mode Register (NCMR)  Overview of Prescalers  Register Description of Prescalers  12.7.1 Prescaler Registers 0 to 3 (PSCR0 to PSCR3)  Operation of Prescalers  12.8.1 Starting Prescalers  12.8.2 Stopping and Restarting Operation |                                                                                         |

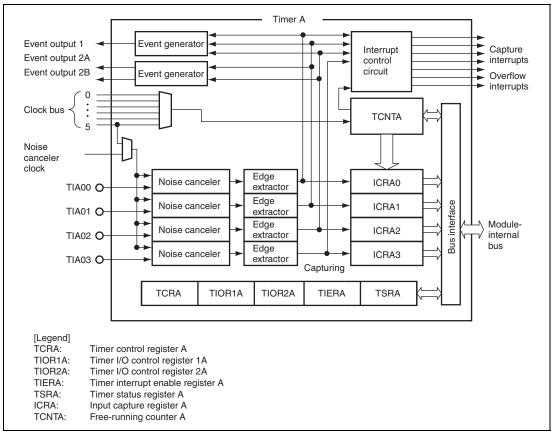

|       | 12.10.1 Timer Control Register A (TCRA)                                | 343 |

|-------|------------------------------------------------------------------------|-----|

|       | 12.10.2 Timer I/O Control Register 1A (TIOR1A)                         | 345 |

|       | 12.10.3 Timer I/O Control Register 2A (TIOR2A)                         | 346 |

|       | 12.10.4 Timer Status Register A (TSRA)                                 | 348 |

|       | 12.10.5 Timer Interrupt Enable Register A (TIERA)                      | 350 |

|       | 12.10.6 Input Capture Registers A0 to A3 (ICRA0 to ICRA3)              | 351 |

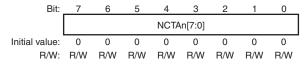

|       | 12.10.7 Free-Running Counter A (TCNTA)                                 |     |

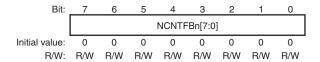

|       | 12.10.8 Noise Canceler Counters A0 to A3 (NCNTA0 to NCNTA3)            | 353 |

|       | 12.10.9 Noise Canceler Registers A0 to A3 (NCRA0 to NCRA3)             | 355 |

| 12.11 | Operations of Timer A                                                  |     |

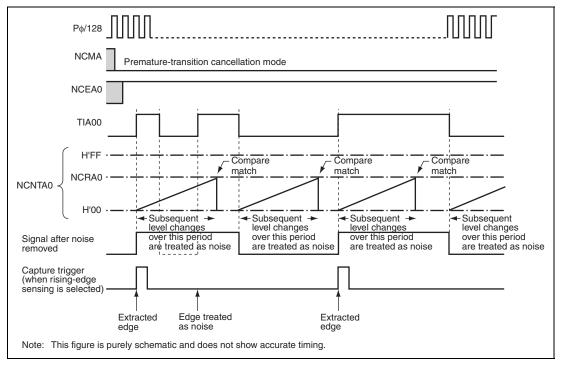

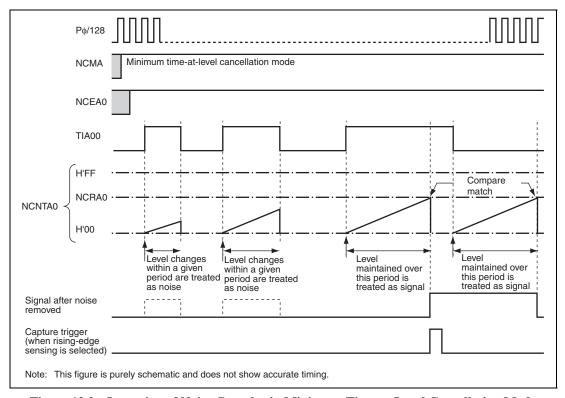

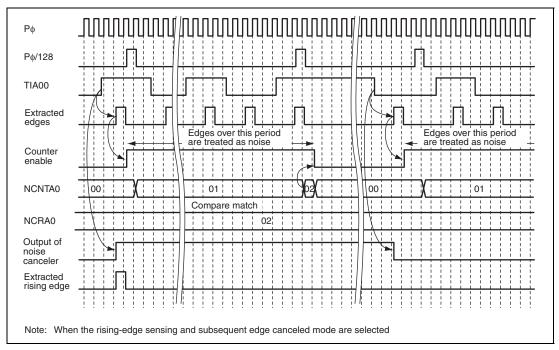

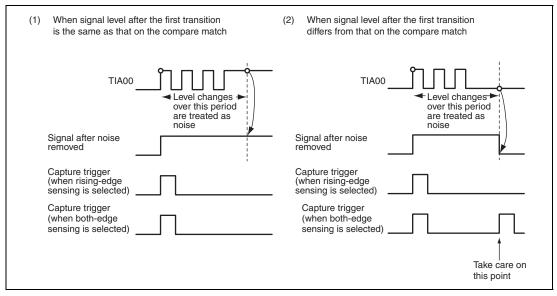

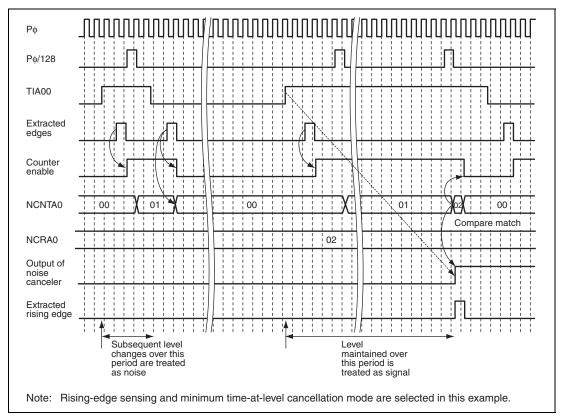

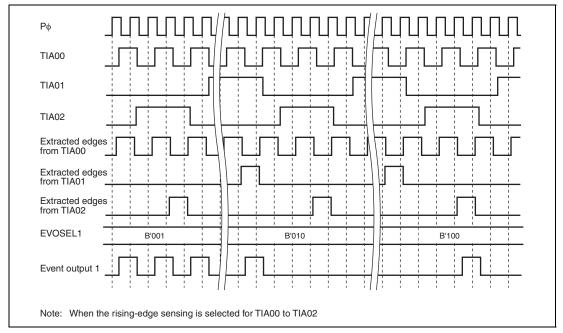

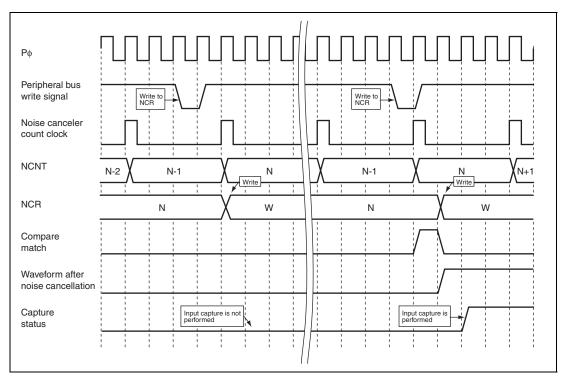

|       | 12.11.1 Operation of Noise Canceler                                    | 356 |

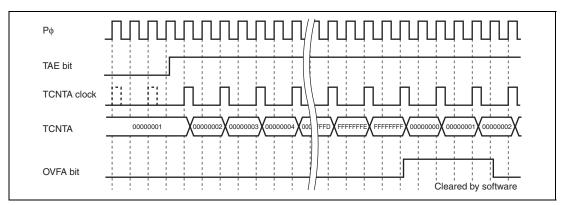

|       | 12.11.2 Operation of Free-Running Counter                              | 359 |

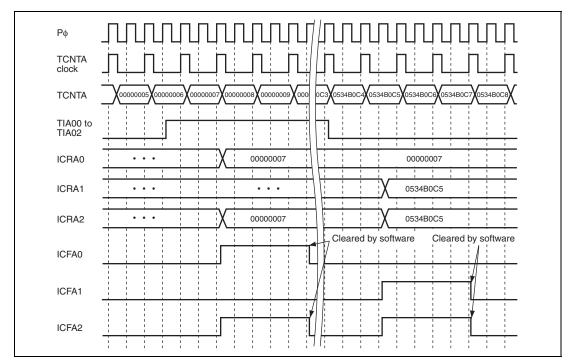

|       | 12.11.3 Input Capture                                                  | 360 |

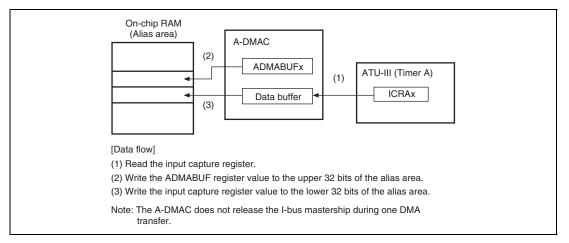

|       | 12.11.4 DMA Transfer.                                                  | 362 |

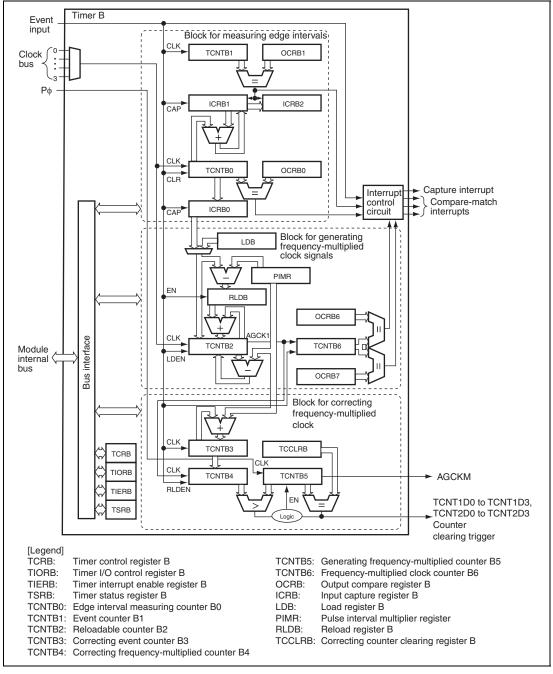

| 12.12 | Overview of Timer B                                                    | 362 |

|       | 12.12.1 Block Diagram of Timer B                                       | 363 |

| 12.13 | Descriptions of Timer B Registers                                      | 365 |

|       | 12.13.1 Timer Control Register B (TCRB)                                | 365 |

|       | 12.13.2 Timer I/O Control Register B (TIORB)                           | 366 |

|       | 12.13.3 Timer Status Register B (TSRB)                                 | 368 |

|       | 12.13.4 Timer Interrupt Enable Register B (TIERB)                      |     |

|       | 12.13.5 Edge Interval Measuring Counter B0 (TCNTB0)                    | 372 |

|       | 12.13.6 Input Capture Register B0 (ICRB0)                              |     |

|       | 12.13.7 Output Compare Register B0 (OCRB0)                             | 373 |

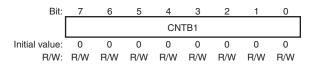

|       | 12.13.8 Event Counter B1 (TCNTB1)                                      |     |

|       | 12.13.9 Output Compare Register B1 (OCRB1)                             | 374 |

|       | 12.13.10 Input Capture Register B1 (ICRB1)                             |     |

|       | 12.13.11 Input Capture Register B2 (ICRB2)                             | 376 |

|       | 12.13.12 Load Register B (LDB)                                         |     |

|       | 12.13.13 Reload Register B (RLDB)                                      | 378 |

|       | 12.13.14 Reloadable Counter B2 (TCNTB2)                                |     |

|       | 12.13.15 Pulse Interval Multiplier Register (PIMR)                     | 380 |

|       | 12.13.16 Multiplied Clock Counter B6 (TCNTB6)                          | 381 |

|       | 12.13.17 Output Compare Register B6 (OCRB6)                            | 382 |

|       | 12.13.18 Output Compare Register B7 (OCRB7)                            | 383 |

|       | 12.13.19 Correcting Event Counter B3 (TCNTB3)                          |     |

|       | 12.13.20 Multiplied-and-Corrected Clock Counter B4 (TCNTB4)            |     |

|       | 12.13.21 Multiplied-and-Corrected Clock Generating Counter B5 (TCNTB5) |     |

|       | 12.13.22 Correcting Counter Clearing Register B (TCCLRB)               |     |

| 12.14 | Operations of Timer B                                                  | 388 |

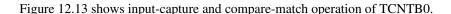

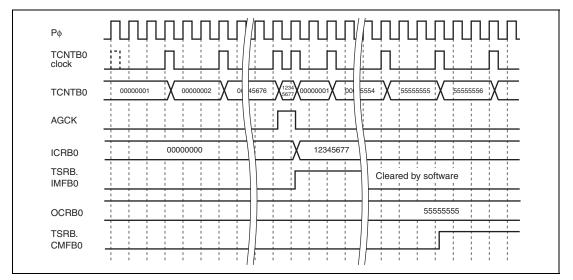

|       | 12.14.1 Edge Interval Measuring Function and Edge Input Stopping Function | 388 |

|-------|---------------------------------------------------------------------------|-----|

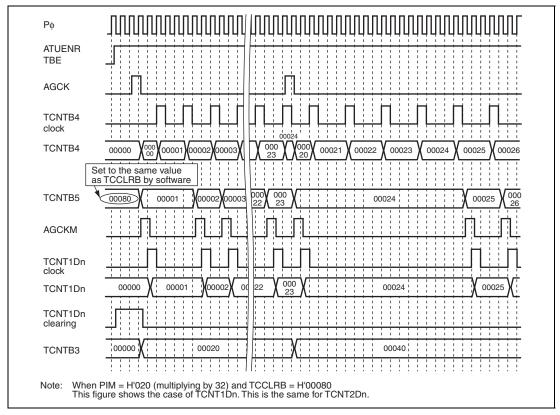

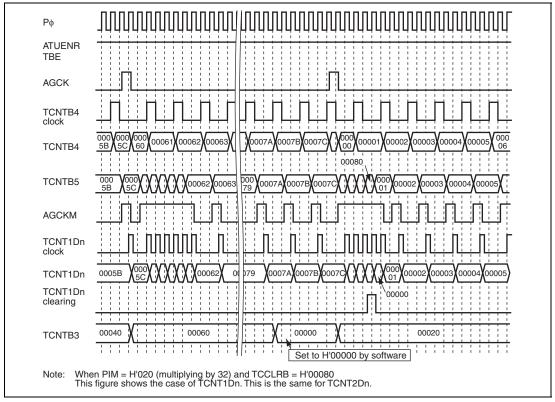

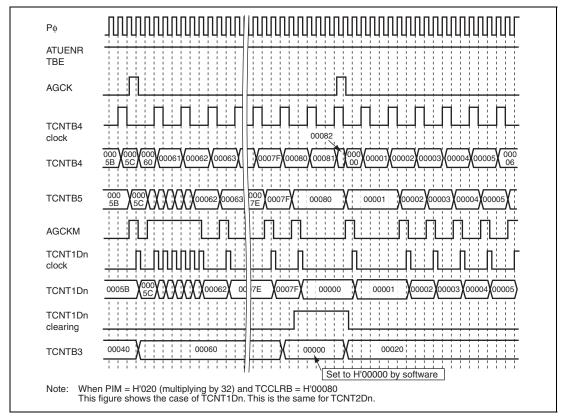

|       | 12.14.2 Frequency-Multiplied Clock Generator                              | 390 |

|       | 12.14.3 Frequency-Multiplied Clock Signal Corrector                       | 395 |

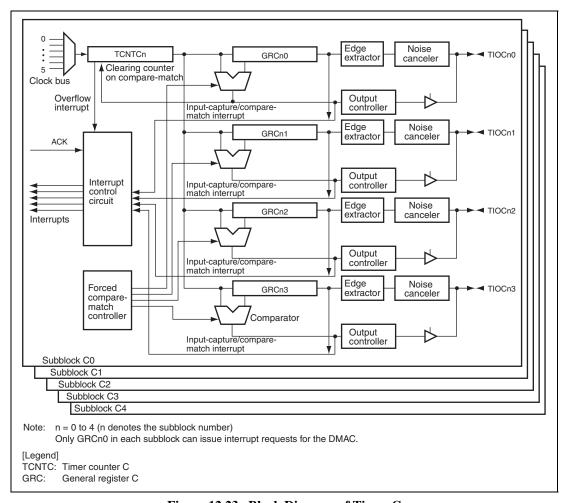

| 12.15 | Overview of Timer C                                                       | 400 |

|       | 12.15.1 Block Diagram of Timer C                                          | 400 |

| 12.16 | Description of Timer C Registers                                          |     |

|       | 12.16.1 Timer Start Register C (TSTRC)                                    | 402 |

|       | 12.16.2 Noise Canceler Control Register C0 to C4 (NCCRC0 to NCCRC4)       | 403 |

|       | 12.16.3 Timer Control Registers C0 to C4 (TCRC0 to TCRC4)                 | 405 |

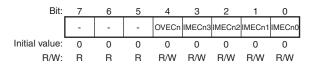

|       | 12.16.4 Timer Status Registers C0 to C4 (TSRC0 to TSRC4)                  | 408 |

|       | 12.16.5 Timer Interrupt Enable Registers C0 to C4 (TIERC0 to TIERC4)      | 411 |

|       | 12.16.6 Timer I/O Control Registers C0 to C4 (TIORC0 to TIORC4)           | 412 |

|       | 12.16.7 Timer Counters C0 to C4 (TCNTC0 to TCNTC4)                        |     |

|       | 12.16.8 General Registers C00 to C43 (GRC00 to GRC43)                     | 416 |

|       | 12.16.9 Noise Canceler Counters C00 to C43 (NCNTC00 to NCNTC43)           | 417 |

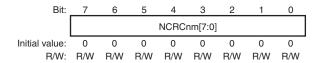

|       | 12.16.10 Noise Cancel Registers C00 to C43 (NCRC00 to NCRC43)             | 419 |

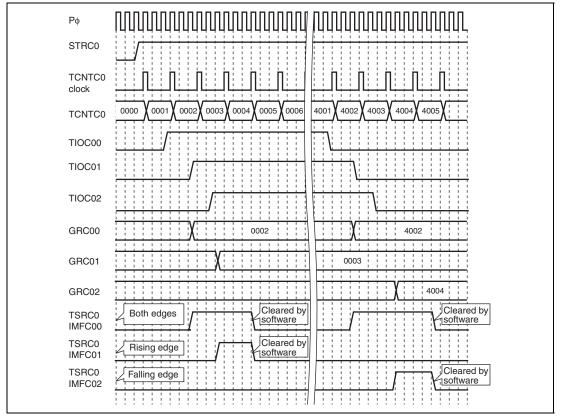

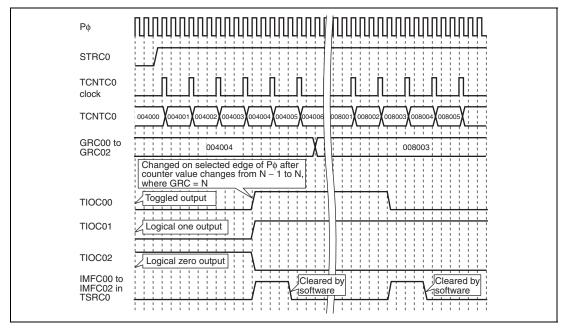

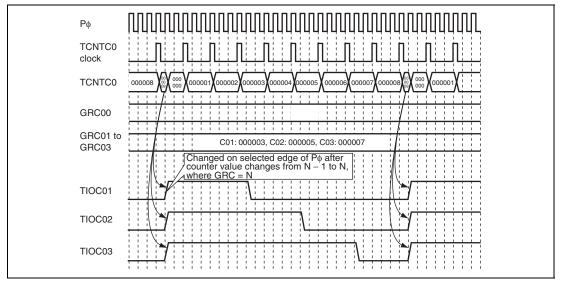

| 12.17 | Operations of Timer C                                                     | 420 |

|       | 12.17.1 Input Capture Function                                            | 420 |

|       | 12.17.2 Compare Match Function                                            |     |

|       | 12.17.3 PWM Function                                                      |     |

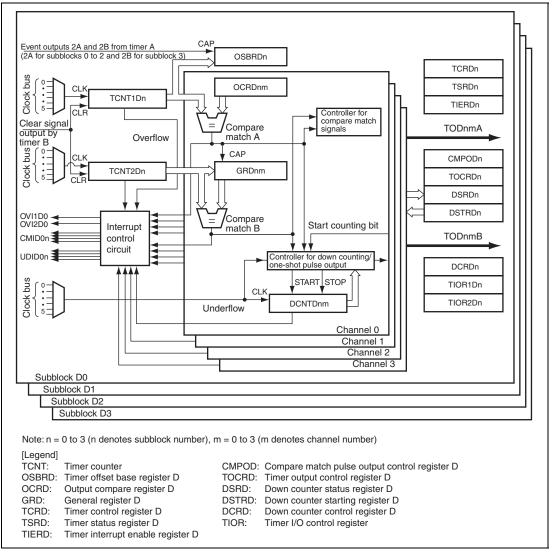

| 12.18 | Overview of Timer D.                                                      |     |

|       | 12.18.1 Block Diagram of Timer D                                          |     |

| 12.19 | Description of Timer D Registers                                          |     |

|       | 12.19.1 Timer Start Register (TSTRD)                                      |     |

|       | 12.19.2 Timer Control Registers D0 to D3 (TCRD0 to TCRD3)                 |     |

|       | 12.19.3 Timer I/O Control Registers 1D0 to 1D3 (TIOR1D0 to TIOR1D3)       |     |

|       | 12.19.4 Timer I/O Control Registers 2D0 to 2D3 (TIOR2D0 to TIOR2D3)       |     |

|       | 12.19.5 Down Counter Starting Registers D0 to D3 (DSTRD0 to DSTRD3)       |     |

|       | 12.19.6 Down Counter Status Registers D0 to D3 (DSRD0 to DSRD3)           |     |

|       | 12.19.7 Down Counter Control Registers D0 to D3 (DCRD0 to DCRD3)          |     |

|       | 12.19.8 Timer Status Registers D0 to D3 (TSRD0 to TSRD3)                  |     |

|       | 12.19.9 Timer Interrupt Enable Registers D0 to D3 (TIERD0 to TIERD3)      | 448 |

|       | 12.19.10 Compare Match Pulse Output Control Registers D0 and D1           |     |

|       | (CMPOD0 and CMPOD1)                                                       |     |

|       | 12.19.11 Timer Output Control Registers D0 to D3 (TOCRD0 to TOCRD3)       |     |

|       | 12.19.12 Timer Offset Base Registers D0 to D3 (OSBRD0 to OSBRD3)          |     |

|       | 12.19.13 Timer Counter 1D0 to 1D3 (TCNT1D0 to TCNT1D3)                    |     |

|       | 12.19.14 Timer Counters 2D0 to 2D3 (TCNT2D0 to TCNT2D3)                   |     |

|       | 12.19.15 Output Compare Registers D00 to D33 (OCRD00 to OCRD33)           |     |

|       | 12.19.16 General Registers D00 to D33 (GRD00 to GRD33)                    | 456 |

|       | 12.19.17 Timer Down Counters D00 to 33 (DCNTD00 to DCNTD33)                | 457 |

|-------|----------------------------------------------------------------------------|-----|

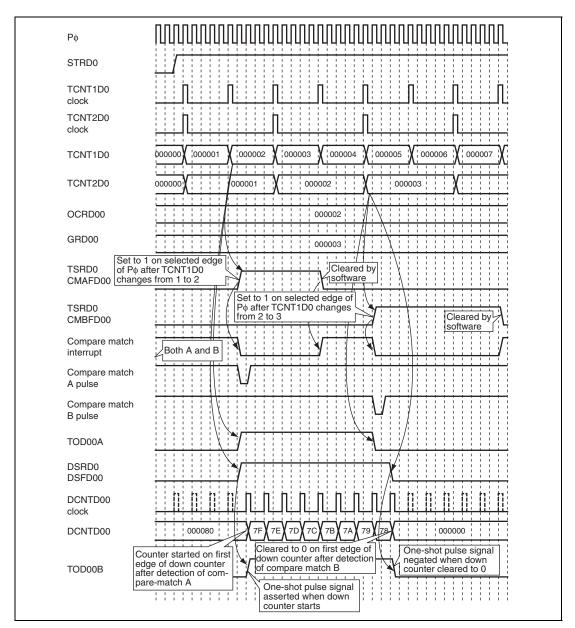

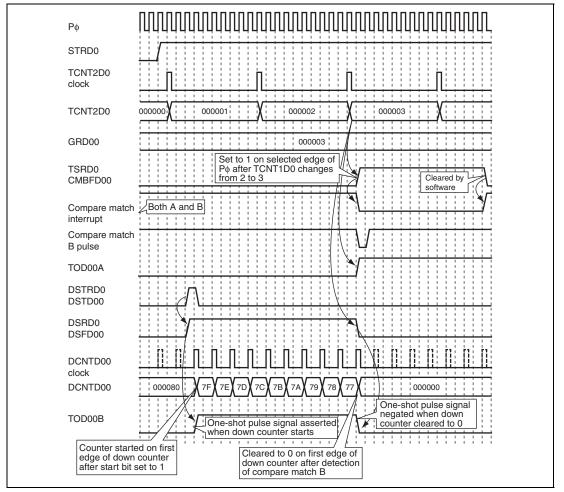

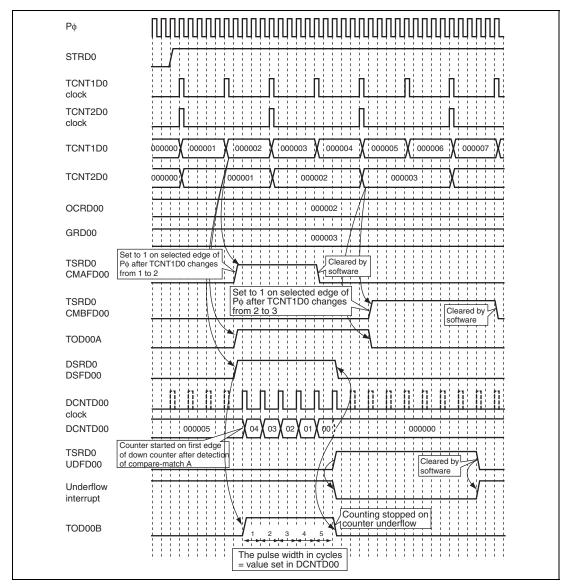

| 12.20 | Operations of Timer D                                                      | 459 |

| 12.21 | Overview of Timer E                                                        | 466 |

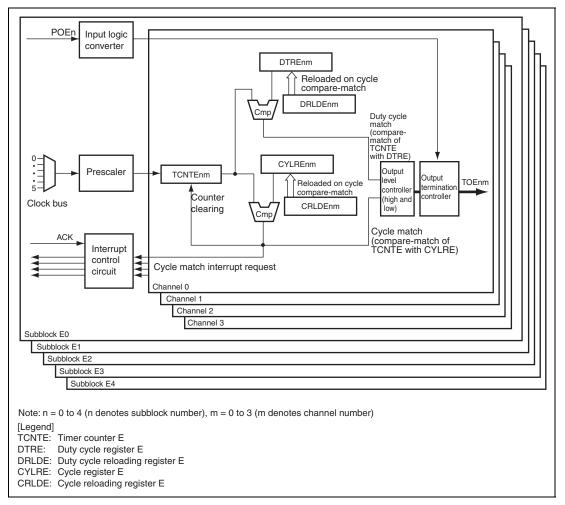

|       | 12.21.1 Block Diagram of Timer E                                           | 466 |

| 12.22 | Description of Timer E Registers                                           | 469 |

|       | 12.22.1 Timer Start Register E (TSTRE)                                     | 469 |

|       | 12.22.2 Subblock Starting Registers E0 to E4 (SSTRE0 to SSTRE4)            | 470 |

|       | 12.22.3 Prescaler Registers E0 to E4 (PSCRE0 to PSCRE4)                    |     |

|       | 12.22.4 Timer Control Register E0 to E4 (TCRE0 to TCRE4)                   | 473 |

|       | 12.22.5 Reload Control Registers E0 to E4 (RLDCRE0 to RLDCRE4)             | 474 |

|       | 12.22.6 Output Termination Control Registers E0 to E4 (POECRE0 to POECRE4) | 475 |

|       | 12.22.7 Output Termination Level Setting Registers E0 to E4                |     |

|       | (SOLVLE0 to SOLVLE4)                                                       | 476 |

|       | 12.22.8 Timer Status Registers E0 to E4 (TSRE0 to TSRE4)                   | 477 |

|       | 12.22.9 Timer Interrupt Enable Registers E0 to E4 (TIERE0 to TIERE4)       | 480 |

|       | 12.22.10 Timer Output Control Registers E0 to E4 (TOCRE0 to TOCRE4)        | 481 |

|       | 12.22.11 Timer Counters E00 to E43 (TCNTE00 to TCNTE43)                    | 482 |

|       | 12.22.12 Cycle-Setting Registers E00 to E43 (CYLRE00 to CYLRE43)           | 483 |

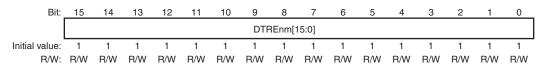

|       | 12.22.13 Duty Cycle Setting Registers E00 to E43 (DTRE00 to DTRE43)        | 484 |

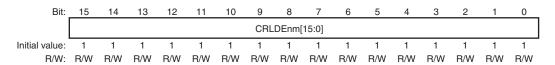

|       | 12.22.14 Cycle Reload Registers E00 to E43 (CRLDE00 to CRLDE43)            |     |

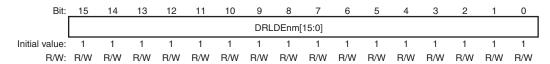

|       | 12.22.15 Duty Cycle Reload Registers E00 to E43 (DRLDE00 to DRLDE43)       | 485 |

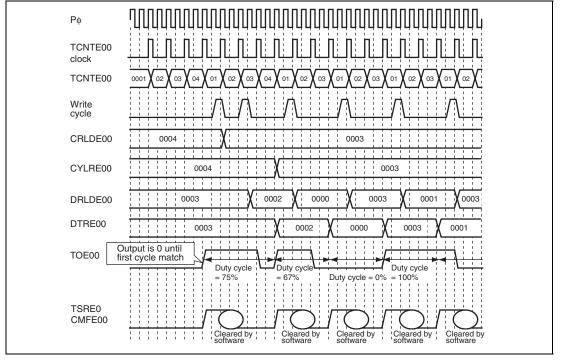

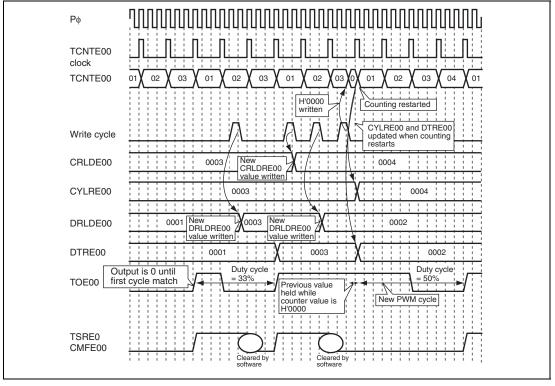

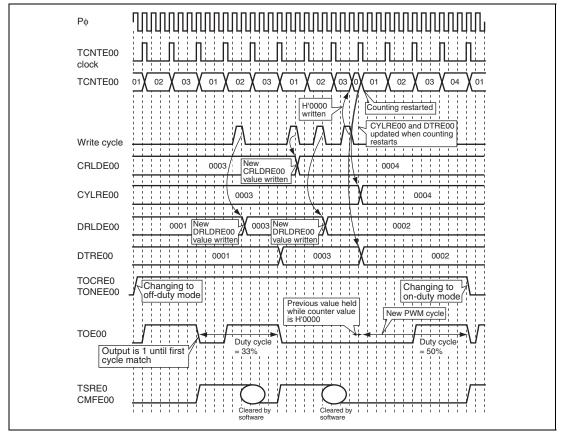

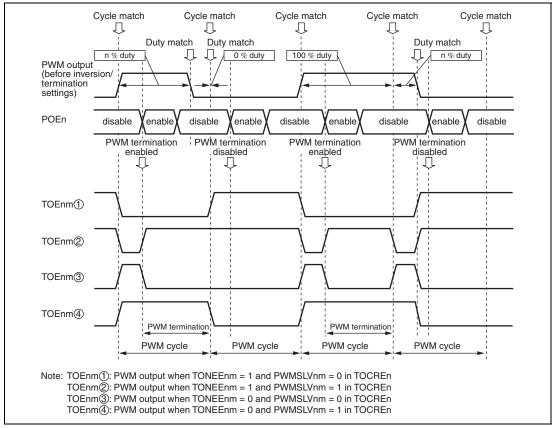

| 12.23 | Operations of Timer E                                                      | 486 |

| 12.24 | Overview of Timer F                                                        |     |

|       | 12.24.1 Block Diagram of Timer F                                           |     |

|       | 12.24.2 Interrupts                                                         |     |

| 12.25 | Description of Timer F Registers                                           |     |

|       | 12.25.1 Timer Start Register F (TSTRF)                                     |     |

|       | 12.25.2 Noise Canceller Control Register F (NCCRF)                         |     |

|       | 12.25.3 Timer Control Registers F0 to F19 (TCRF0 to TCRF19)                |     |

|       | 12.25.4 Timer Interrupt Enable Registers F0 to F19 (TIERF0 to TIERF19)     | 501 |

|       | 12.25.5 Timer Status Registers F0 to F19 (TSRF0 to TSRF19)                 |     |

|       | 12.25.6 Timer Counters AF0 to AF19 (ECNTAF0 to ECNTAF19)                   |     |

|       | 12.25.7 Event Counters F0 to F19 (ECNTBF0 to ECNTBF19)                     |     |

|       | 12.25.8 Time Counters CF0 to CF19 (ECNTCF0 to ECNTCF19)                    |     |

|       | 12.25.9 General Registers AF0 to AF19 (GRAF0 to GRAF19)                    |     |

|       | 12.25.10 General Registers BF0 to BF19 (GRBF0 to GRBF19)                   |     |

|       | 12.25.11 General Registers CF0 to CF19 (GRCF0 to GRCF19)                   |     |

|       | 12.25.12 General Registers DF12 to DF15 (GRDF12 to GRDF15)                 |     |

|       | 12.25.13 Capture Output Registers F0 to F19 (CDRF0 to CDRF19)              |     |

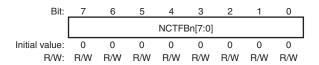

|       | 12.25.14 Noise Canceler Counters FA0 to FA19 (NCNTFA0 to NCNTFA19)         | 514 |

|       | 12.25.15 Noise Canceler Counters FB0 to FB2 (NCNTFB0 to NCNTFB2)       | 516 |

|-------|------------------------------------------------------------------------|-----|

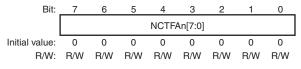

|       | 12.25.16 Noise Cancel Registers FA0 to FA19 (NCRFA0 to NCRFA19)        | 518 |

|       | 12.25.17 Noise Cancel Registers FB0 to FB2 (NCRFB0 to NCRFB2)          | 519 |

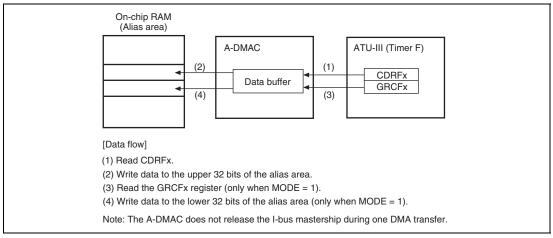

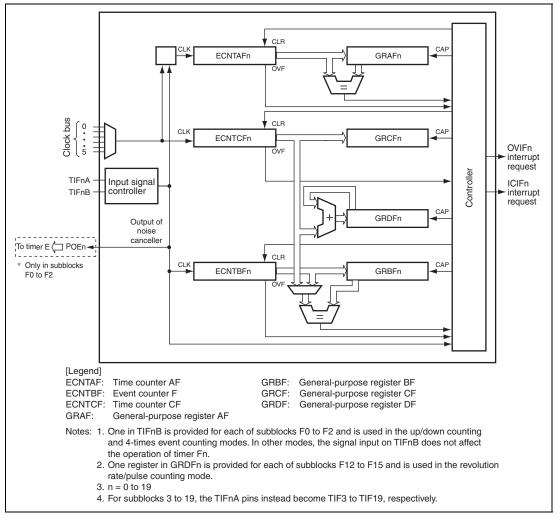

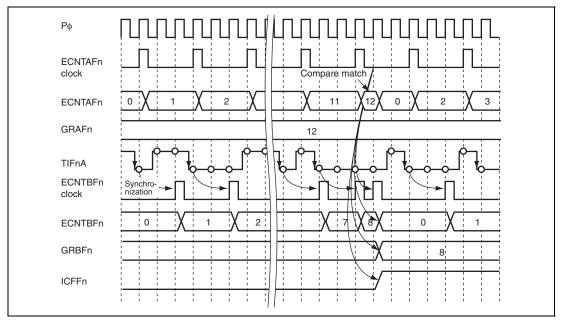

| 12.26 | Operations of Timer F                                                  | 520 |

|       | 12.26.1 Edge Counting                                                  | 520 |

|       | 12.26.2 Valid Edge Interval Counting                                   | 522 |

|       | 12.26.3 Measurement of Time during High/Low Input Levels               | 523 |

|       | 12.26.4 Measurement of PWM Input Waveform Timing                       | 525 |

|       | 12.26.5 Rotation Speed/Pulse Measurement                               | 527 |

|       | 12.26.6 Up/Down Event Count                                            | 530 |

|       | 12.26.7 Four-time Multiplication Event Count                           | 532 |

|       | 12.26.8 Overflow and Underflow                                         | 534 |

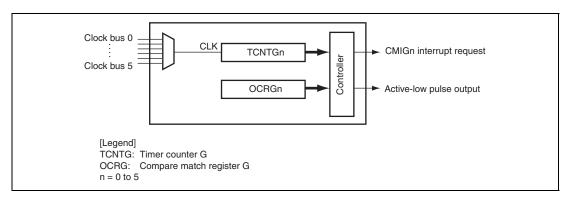

| 12.27 | Overview of Timer G                                                    | 535 |

|       | 12.27.1 Block Diagram of Timer G                                       | 535 |

|       | 12.27.2 Interrupt Requests                                             | 535 |

| 12.28 | Description of Timer G Registers                                       | 536 |

|       | 12.28.1 Timer Start Register G (TSTRG)                                 | 536 |

|       | 12.28.2 Timer Control Register G0 to G5 (TCRG0 to TCRG5)               | 537 |

|       | 12.28.3 Timer Status Registers G0 to G5 (TSRG0 to TSRG5)               | 538 |

|       | 12.28.4 Timer Counters G0 to G5 (TCNTG0 to TCNTG5)                     |     |

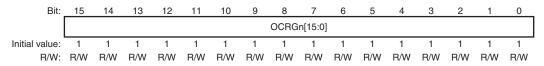

|       | 12.28.5 Compare Match Registers G0 to G5 (OCRG0 to OCRG5)              | 541 |

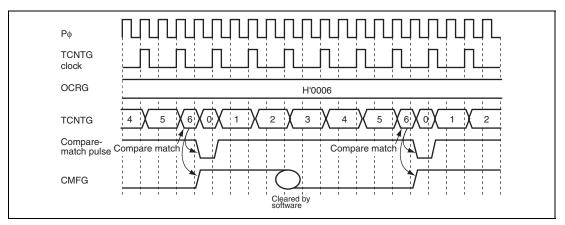

| 12.29 | Operations of Timer G                                                  | 542 |

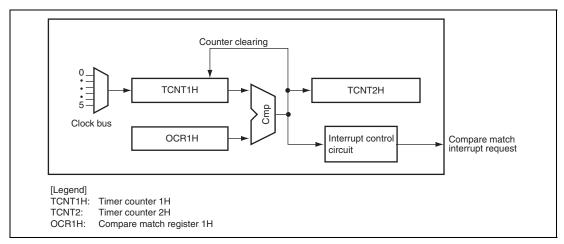

| 12.30 | Overview of Timer H                                                    |     |

|       | 12.30.1 Block Diagram of Timer H                                       | 543 |

|       | 12.30.2 Interrupts                                                     |     |

| 12.31 | Description of Timer H Registers                                       |     |

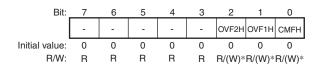

|       | 12.31.1 Timer Control Register H (TCRH)                                |     |

|       | 12.31.2 Timer Status Register H (TSRH)                                 |     |

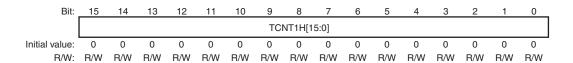

|       | 12.31.3 Timer Counter 1H (TCNT1H)                                      |     |

|       | 12.31.4 Compare Match Register 1H (OCR1H)                              |     |

|       | 12.31.5 Timer Counter 2H (TCNT2H)                                      |     |

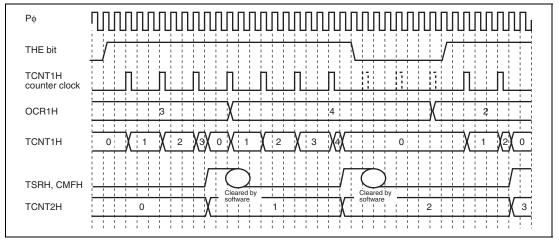

|       | Operations of Timer H                                                  |     |

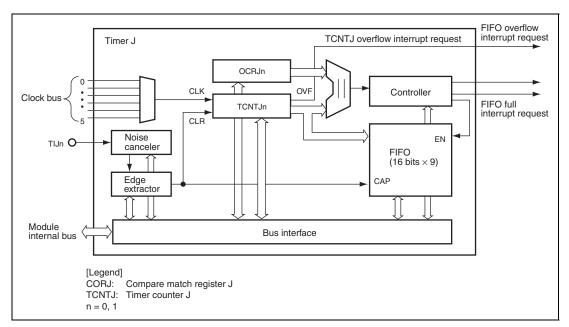

| 12.33 | Overview of Timer J                                                    |     |

|       | 12.33.1 Block Diagram of Timer J                                       |     |

| 12.34 | Description of Timer J Registers                                       |     |

|       | 12.34.1 Timer Start Register J (TSTRJ)                                 |     |

|       | 12.34.2 Timer Control Registers J0 and J1 (TCRJ0 and TCRJ1)            |     |

|       | 12.34.3 FIFO Control Registers J0 and J1 (FCRJ0 and FCRJ1)             |     |

|       | 12.34.4 Timer Status Register J0 and J1 (TSRJ0 and TSRJ1)              |     |

|       | 12.34.5 Timer Interrupt Enable Registers J0 and J1 (TIERJ0 and TIERJ1) | 562 |

|       | 12.34.6 | Timer Counter J0 and J1 (TCNTJ0 and TCNTJ1)             | 563 |

|-------|---------|---------------------------------------------------------|-----|

|       |         | Compare Match Registers J0 and J1 (OCRJ0 and OCRJ1)     |     |

|       | 12.34.8 | FIFO Registers J0 and J1 (FIFOJ0 and FIFOJ1)            | 564 |

|       | 12.34.9 | FIFO Data Count Registers J0 and J1 (FDNRJ0 and FDNRJ1) | 565 |

|       | 12.34.1 | 0 Noise Canceler Counters J0 and J1 (NCNTJ0 and NCNTJ1) | 566 |

|       | 12.34.1 | 1 Noise Cancel Registers J0 and J1 (NCRJ0 and NCRJ1)    | 567 |

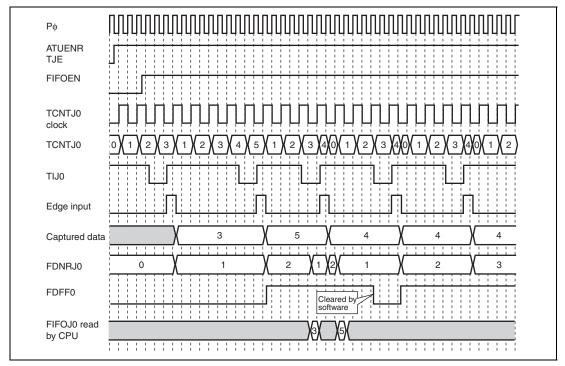

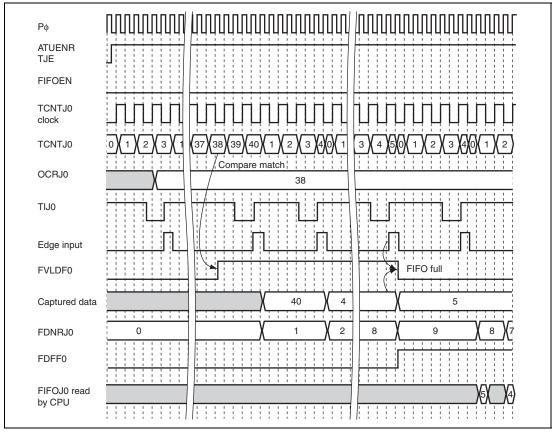

| 12.35 | Operat  | ions of Timer J                                         | 568 |

| 12.36 | Usage   | Notes                                                   | 571 |

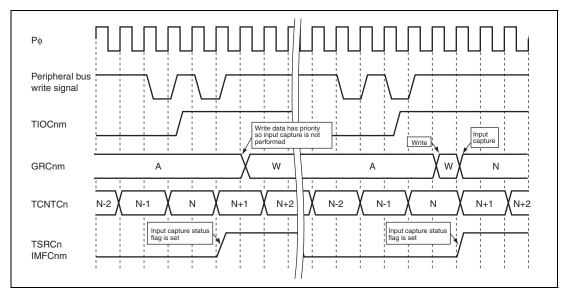

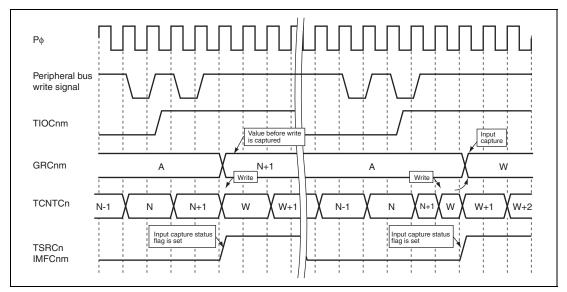

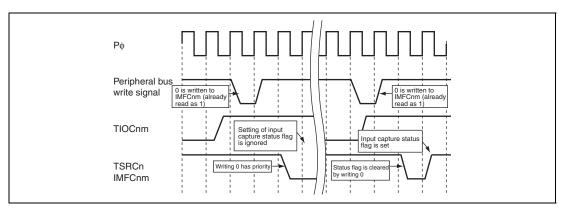

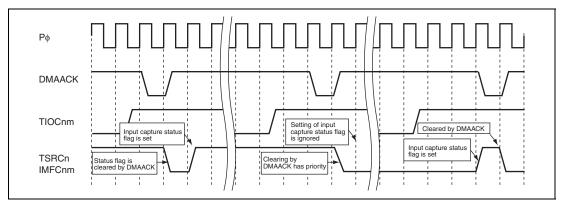

|       | 12.36.1 | Input Capture Conflict Operation                        | 571 |

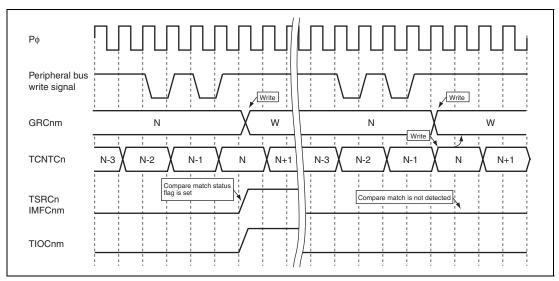

|       | 12.36.2 | Compare Match Conflict Operation                        | 575 |

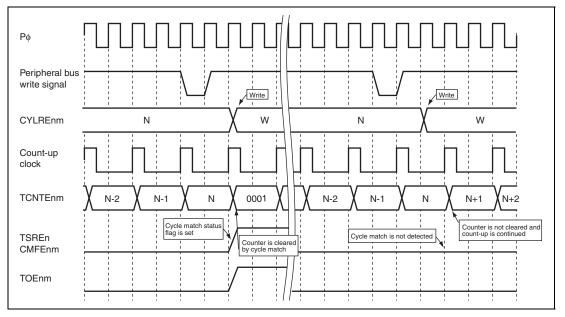

|       | 12.36.3 | Load/Reload Conflict Operation                          | 587 |

|       | 12.36.4 | Counter Conflict Operation                              | 590 |

|       | 12.36.5 | Noise Canceler Conflict Operation                       | 595 |

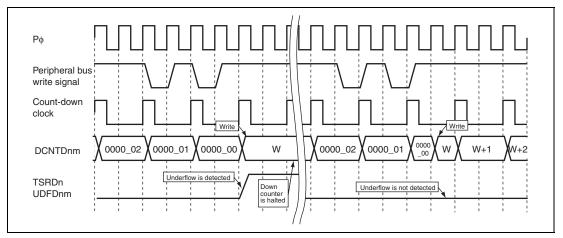

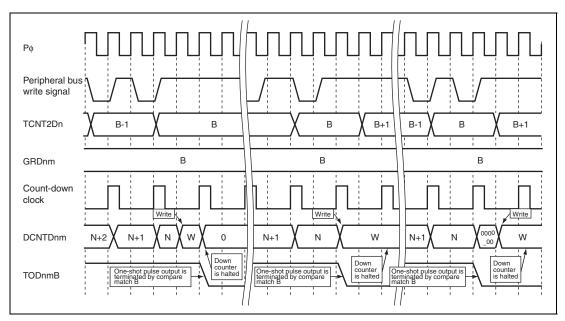

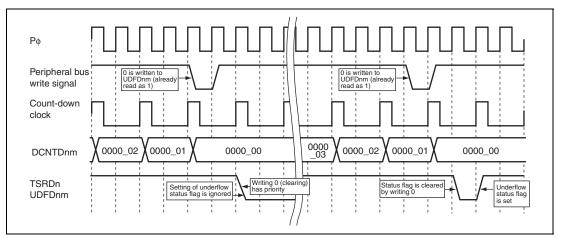

|       | 12.36.6 | Conflict Regarding Down Counter D                       | 598 |

|       | 12.36.7 | Conflict between Timer B and Timer D                    | 603 |

|       | 12.36.8 | Compare-match Operation Specification                   | 607 |

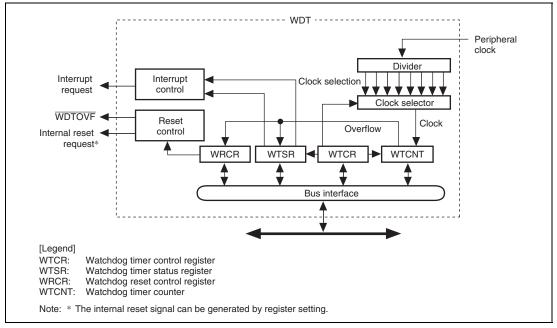

| Secti | on 13   | Watchdog Timer (WDT)                                    | 609 |

| 13.1  |         | 28                                                      |     |

| 13.2  |         | Output Pin                                              |     |

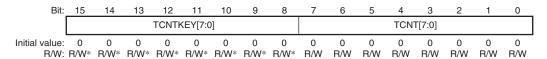

| 13.3  | Registe | er Descriptions                                         | 611 |

|       | _       | Watchdog Timer Control Register (WTCR)                  |     |

|       |         | Watchdog Timer Counter (WTCNT)                          |     |

|       | 13.3.3  | Watchdog Timer Status Register (WTSR)                   | 615 |

|       |         | Watchdog Reset Control Register (WRCR)                  |     |

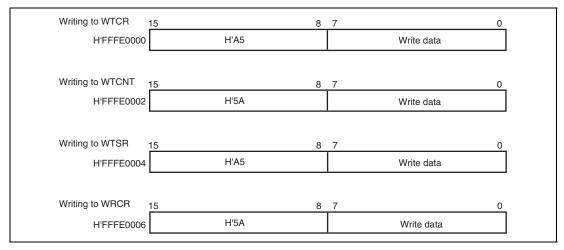

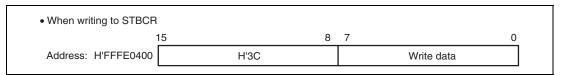

|       |         | Notes on Register Access                                |     |

| 13.4  |         | Jsage                                                   |     |

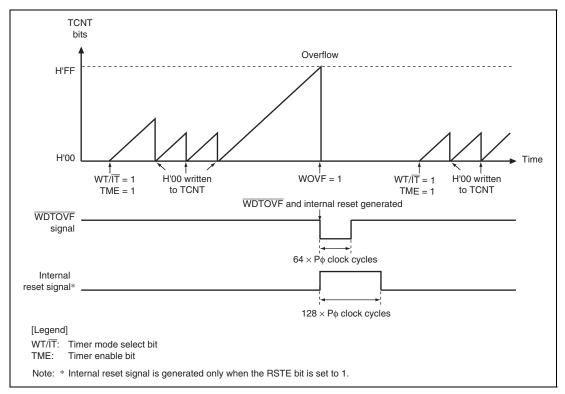

|       | 13.4.1  | Using WDT in Watchdog Timer Mode                        | 620 |

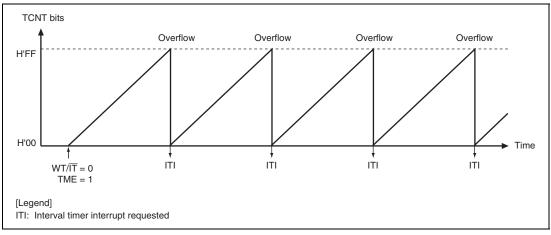

|       | 13.4.2  | Using WDT in Interval Timer Mode                        | 622 |

| 13.5  | Usage   | Notes                                                   | 623 |

|       | 13.5.1  | Timer Error                                             | 623 |

|       | 13.5.2  | Changing of Division Ratio                              | 623 |

|       | 13.5.3  | Switching between Watchdog and Interval Timer Modes     | 623 |

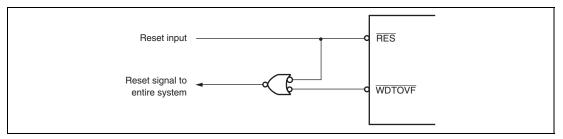

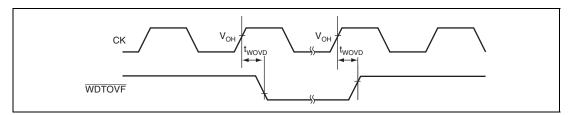

|       | 13.5.4  | System Reset by WDTOVF Signal                           | 624 |

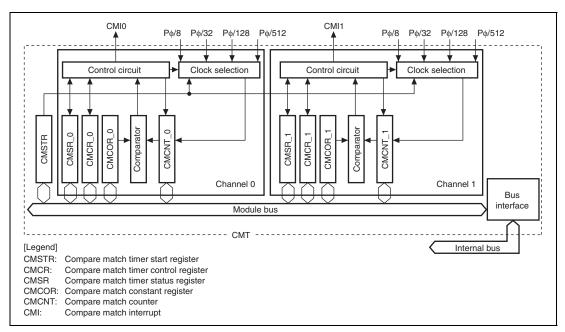

| Secti | on 14   | Compare Match Timer (CMT)                               | 625 |

|       |         | 28                                                      |     |

| 14.2  |         | er Descriptions                                         |     |

|       | _       | Compare Match Timer Start Register (CMSTR)              |     |

|       |         | Compare Match Timer Control Register (CMCR)             |     |

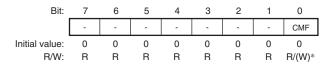

|      | 14.2.3  | Compare Match Timer Status Register (CMSR)                             | 629 |

|------|---------|------------------------------------------------------------------------|-----|

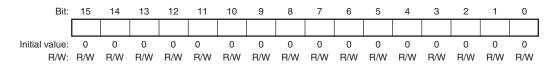

|      | 14.2.4  | Compare Match Counter (CMCNT)                                          | 630 |

|      | 14.2.5  | Compare Match Constant Register (CMCOR)                                | 630 |

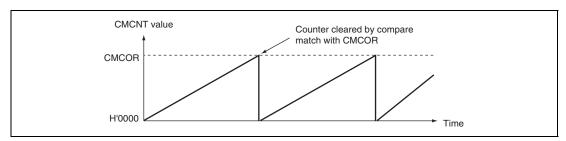

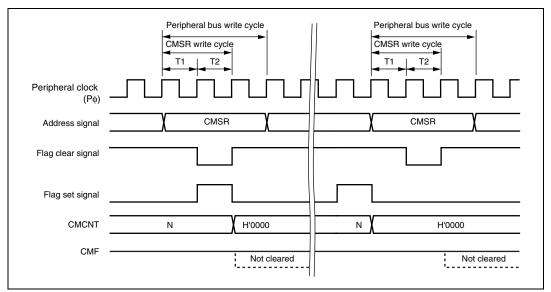

| 14.3 | Operat  | ion                                                                    | 631 |

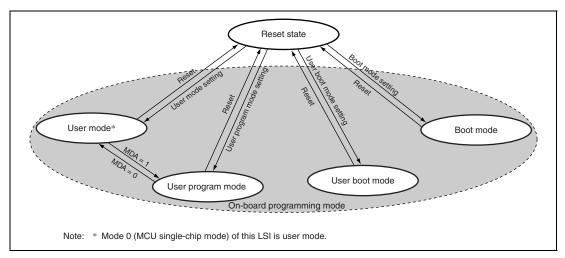

|      | 14.3.1  | Interval Count Operation                                               | 631 |