## 关于产品目录等资料中的旧公司名称

NEC电子公司与株式会社瑞萨科技于2010年4月1日进行业务整合(合并),整合后的新公司暨"瑞萨电子公司"继承两家公司的所有业务。因此,本资料中虽还保留有旧公司名称等标识,但是并不妨碍本资料的有效性,敬请谅解。

瑞萨电子公司网址: http://www.renesas.com

2010年4月1日 瑞萨电子公司

【发行】瑞萨电子公司(http://www.renesas.com)

【业务咨询】http://www.renesas.com/inquiry

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# SH7137群

瑞萨32位RISC单片机 SuperH<sup>TM</sup> RISC engine族

SH7136 R5F7136 SH7137 R5F7137

### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### 注意

本文只是参考译文,前页所载英文版"Cautions"具有正式效力。

### 关于利用本资料时的注意事项

- 本资料是为了让用户根据用途选择合适的本公司产品的参考资料,对于本资料中所记载的技术信息,并非意味着对本公司或者第三者的知识产权及其他权利做出保证或对实施权力进行的承诺。

- 2. 对于因使用本资料所记载的产品数据、图、表、程序、算法及其他应用电路例而引起的损害或者对第三者的知识产权及其他权利造成侵犯,本公司不承担任何责任。

- 3. 不能将本资料所记载的产品和技术用于大规模破坏性武器的开发等目的、军事目的或其他的军需用途方面。 另外,在出口时必须遵守日本的《外汇及外国贸易法》及其他出口的相关法令并履行这些法令中规定的必要 手续。

- 4. 本资料所记载的产品数据、图、表、程序、算法以及其他应用电路例等所有信息均为本资料发行时的内容,本公司有可能在未做事先通知的情况下,对本资料所记载的产品或者产品规格进行更改。所以在购买和使用本公司的半导体产品之前,请事先向本公司的营业窗口确认最新的信息并经常留意本公司通过公司主页(http://www.renesas.com)等公开的最新信息。

- 对于本资料中所记载的信息,制作时我们尽力保证出版时的精确性,但不承担因本资料的叙述不当而致使顾客遭受损失等的任何相关责任。

- 6. 在使用本资料所记载的产品数据、图、表等所示的技术内容、程序、算法及其他应用电路例时,不仅要对所使用的技术信息进行单独评价,还要对整个系统进行充分的评价。请顾客自行负责,进行是否适用的判断。本公司对于是否适用不负任何责任。

- 7. 本资料中所记载的产品并非针对万一出现故障或是错误运行就会威胁到人的生命或给人体带来危害的机器、系统(如各种安全装置或者运输交通用的、医疗、燃烧控制、航天器械、核能、海底中继用的机器和系统等)而设计和制造的,特别是对于品质和可靠性要求极高的机器和系统等(将本公司指定用于汽车方面的产品用于汽车时除外)。如果要用于上述的目的,请务必事先向本公司的营业窗口咨询。另外,对于用于上述目的而造成的损失等,本公司概不负责。

- 8. 除上述第7项内容外,不能将本资料中记载的产品用于以下用途。如果用于以下用途而造成的损失,本公司概不负责。

- 1) 生命维持装置。

- 2) 植埋于人体使用的装置。

- 3) 用于治疗(切除患部、给药等)的装置。

- 4) 其他直接影响到人的生命的装置。

- 9. 在使用本资料所记载的产品时,对于最大额定值、工作电源电压的范围、放热特性、安装条件及其他条件请在本公司规定的保证范围内使用。如果超出了本公司规定的保证范围使用时,对于由此而造成的故障和出现的事故,本公司将不承担任何责任。

- 10. 本公司一直致力于提高产品的质量和可靠性,但一般来说,半导体产品总会以一定的概率发生故障、或者由于使用条件不同而出现错误运行等。为了避免因本公司的产品发生故障或者错误运行而导致人身事故和火灾或造成社会性的损失,希望客户能自行负责进行冗余设计、采取延烧对策及进行防止错误运行等的安全设计(包括硬件和软件两方面的设计)以及老化处理等,这是作为机器和系统的出厂保证。特别是单片机的软件,由于单独进行验证很困难,所以要求在顾客制造的最终的机器及系统上进行安全检验工作。

- 11. 如果把本资料所记载的产品从其载体设备上卸下,有可能造成婴儿误吞的危险。顾客在将本公司产品安装到顾客的设备上时,请顾客自行负责将本公司产品设置为不容易剥落的安全设计。如果从顾客的设备上剥落而造成事故时,本公司将不承担任何责任。

- 12. 在未得到本公司的事先书面认可时,不可将本资料的一部分或者全部转载或者复制。

- 13. 如果需要了解关于本资料的详细内容,或者有其他关心的问题,请向本公司的营业窗口咨询。

## 产品使用时的注意事项

本文对适用于单片机所有产品的"使用时的注意事项"进行说明。有关个别的使用时的注意事项请参照 正文。此外,如果在记载上有与本手册的正文有差异之处,请以正文为准。

### 1. 未使用的引脚的处理

【注意】将未使用的引脚按照正文的"未使用引脚的处理"进行处理。

CMOS产品的输入引脚的阻抗一般为高阻抗。如果在开路的状态下运行未使用的引脚,由于感应现象,外加LSI周围的噪声,在LSI内部产生穿透电流,有可能被误认为是输入信号而引起误动作。 未使用的引脚,请按照正文的"未使用引脚的处理"中的指示进行处理。

### 2. 通电时的处理

【注意】通电时产品处于不定状态。

通电时,LSI内部电路处于不确定状态,寄存器的设定和各引脚的状态不定。通过外部复位引脚对产品进行复位时,从通电到复位有效之前的期间,不能保证引脚的状态。

同样,使用内部上电复位功能对产品进行复位时,从通电到达到复位产生的一定电压的期间,不能保证引脚的状态。

### 3. 禁止存取保留地址 (保留区)

【注意】禁止存取保留地址 (保留区)

在地址区域中,有被分配将来用作功能扩展的保留地址 (保留区)。因为无法保证存取这些地址时的运行,所以不能对保留地址 (保留区)进行存取。

### 4. 关于时钟

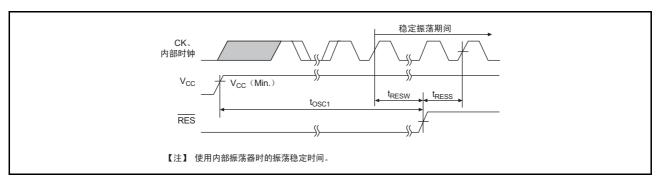

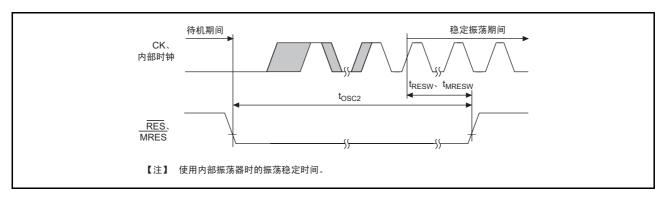

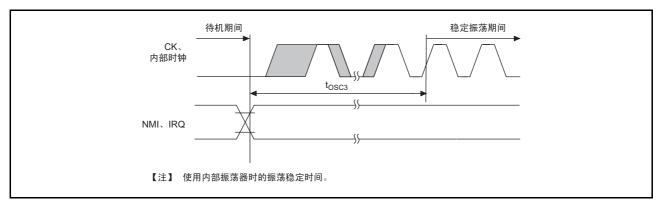

【注意】复位时,请在时钟稳定后解除复位。

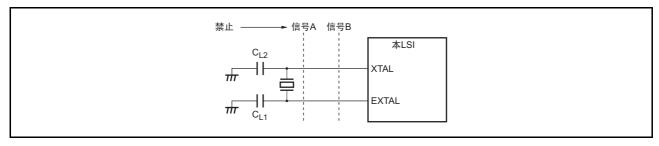

在程序运行中切换时钟时,请在要切换成的时钟稳定之后进行。复位时,在通过使用外部振荡器(或者外部振荡电路)的时钟开始运行的系统中,必须在时钟充分稳定后解除复位。另外,在程序运行中,切换成使用外部振荡器(或者外部振荡电路)的时钟时,在要切换成的时钟充分稳定后再进行切换。

### 5. 关于产品间的差异

【注意】在变更不同型号的产品时,请对每一个产品型号进行系统评价测试。

即使是同一个群的单片机,如果产品型号不同,由于内部ROM、版本模式等不同,在电特性范围内有时特性值、动作容限、噪声耐量、噪声辐射量等也不同。因此,在变更不认同型号的产品时,请对每一个型号的产品进行系统评价测试。

## 本手册的构成

本手册由以下内容构成:

- 1. 产品使用时的注意事项

- 2. 本手册的构成

- 3. 前言

- 4. 目录

- 5. 概要

- 6. 各功能模块的说明

- CPU 和系统控制

- 内部外围模块

各模块功能说明的构成因各模块而不同,一般由①特点、②输入/输出引脚、③寄存器的说明、 ④运行说明、⑤使用时的注意事项等章节构成。

设计采用本 LSI 的应用系统时,请在充分确认了注意事项的基础上进行设计。 请务必阅读各章中有关说明的注事事项和各章最后的使用时的注意事项 (使用时的注意事项根据需要进行记载)。

- 7. 寄存器一览

- 8. 电特性

- 9. 附录

- 产品型号和封装尺寸图等

- 10. 本版中修订或者追加的部分 (只适用于修订版)

修订记录汇总了对前版内容进行修改和追加的主要部分,并非全部的修订内容。请在本手册的正文中确认 有关详细内容。

11. 索引

## 前言

SH7136/SH7137 是以瑞萨独创的 RISC 方式 CPU 为核心,聚集了系统结构所需外围功能的 RISC 单片机。

对 象 本手册是以"采用 SH7136/SH7137 的应用系统"的用户为对象。 使用本手册的读者需要具备电路、逻辑电路以及单片机的基础知识。

目 的 本手册是以"能让用户理解 SH7136/SH7137 的硬件功能和电特性"为目的。 执行指令的详细内容记述在《SH-1/ SH-2/SH-DSP 软件手册》,请对照阅读。

### 阅读方法

- 希望了解全部功能时

- → 请按照目录的顺序进行阅读。 本书大致按CPU、系统控制功能、外围功能、电特性等的顺序进行分类。

- · 希望了解FPU功能的详细内容时

- → 请参照《SH-1/SH-2/SH-DSP软件手册》。

- 知道寄存器名,希望了解详细功能时

- → 在本手册的后面附有"索引",请从索引检索页号。 地址、位内容及其初始化汇总在"第25章 寄存器一览"。

范 例 寄存器的表示:如同或者类似于串行通信接口等的功能存在于多个通道时,使用以下的表示方法:

XXX N (XXX 为基本寄存器名, N 为通道号)

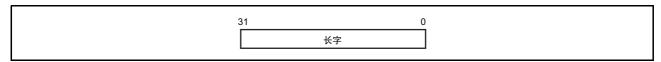

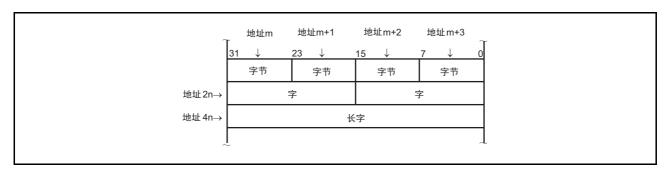

位的表示 : 以左侧为高位、右侧为低位的顺序进行表示。

数字的表示 : 2 进制数为 B'XXXX, 16 进制数为 H'XXXX, 10 进制数为 XXXX。

信号的表示 : 对低电平有效的信号加上划线 (XXXX)。

相关资料一览 最新的资料刊登在网站上,请确认现有的资料是否为最新版 (http://www.renesas.com)。

## • 有关SH7136/SH7137的用户手册

| 资料名                    | 资料编号       |

|------------------------|------------|

| SH7137 群硬件手册           | 本手册        |

| SH-1/ SH-2/SH-DSP 软件手册 | RCJ09B0065 |

## • 有关开发工具的用户手册

| 资料名                                                                                         | 资料编号       |

|---------------------------------------------------------------------------------------------|------------|

| SuperH <sup>TM</sup> RISC engine C/C++Compiler,Assembler,Optimizing Linkage Editor Compiler | REJ10B0152 |

| Package V.9.00 User's Manual                                                                |            |

| SuperH <sup>TM</sup> RISC engine High-performance Embedded Workshop 3 Use's Manual          | REJ10B0025 |

| SuperH RISC engine High-performance Embedded Workshop 3 Tutorial                            | REJ10B0023 |

## • 应用说明

| 资料名                                                        | 资料编号       |

|------------------------------------------------------------|------------|

| SuperH RISC engine C/C++ Compiler Package Application Note | REJ05B0463 |

所有的商标及注册商标分别归属于其所有者。

## 目 录

| 第1章               | 概要                  | 1  |

|-------------------|---------------------|----|

| 1.1               | SH7136/SH7137 的特点   | 1  |

| 1.2               | 框图                  | 5  |

| 1.3               | 引脚排列图               | 6  |

| 1.4               | 引脚功能                | 8  |

| 第2章               | CPU                 | 12 |

| <b>おと早</b><br>2.1 | 特点                  |    |

| 2.1               | 寄存器结构               |    |

| 2.2.              |                     |    |

| 2.2.              |                     |    |

| 2.2.              |                     |    |

| 2.2.              |                     |    |

| 2.3               | 数据格式                |    |

| 2.3.              |                     |    |

| 2.3.              |                     |    |

| 2.3.              |                     |    |

| 2.4               | 指令特点                | 16 |

| 2.4.              | 1 RISC 方式           | 16 |

| 2.4.              | 2 寻址方式              | 19 |

| 2.4.              | 3 指令格式              | 22 |

| 2.5               | 指令系统                | 24 |

| 2.5.              | 1 指令系统的分类           | 24 |

| 2.5.              | - 3,00 N. O. A.     |    |

| 2.5.              | 27 1 = 21 1         |    |

| 2.5.              |                     |    |

| 2.5.              |                     |    |

| 2.5.              |                     |    |

| 2.5.              | 74 (704 ± 444 f)    |    |

| 2.6               | 处理状态                | 32 |

| 第3章               | MCU 运行模式            | 33 |

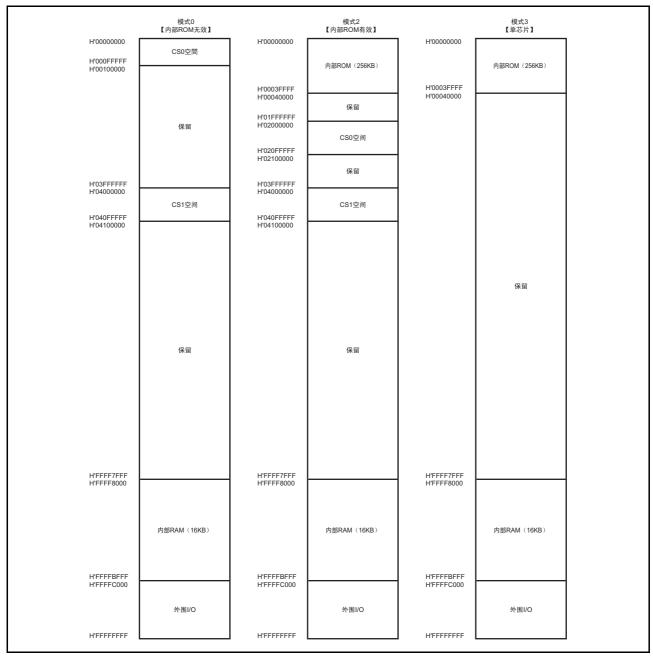

| 3.1               | 运行模式的选择             | 33 |

| 3.2               | 输入 / 输出引脚           |    |

| 3.3               | 各运行模式的说明            |    |

| 3.3.              | 10. 5.              |    |

| 3.3.              | 2 模式 2 (MCU 扩展模式 2) | 34 |

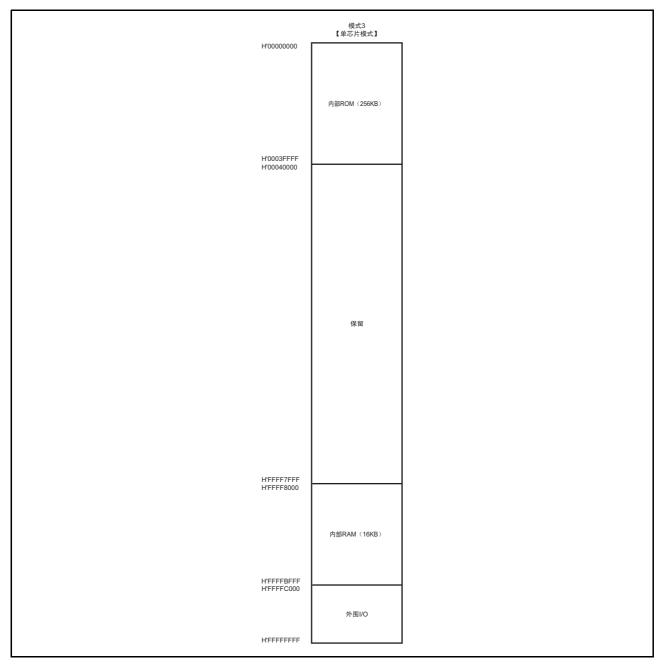

| 3.3.              | 3 模式 3 (单芯片模式)      | 34 |

| 3.4               | 地址映像                | 34 |

| 3.5               | 本 LSI 的初始状态         |    |

| 3.6               | 更改运行模式时的注意事项        | 36 |

| 第4章               | 时钟振荡器 (CPG)         | 37 |

| 4.1               | 特点                  |    |

| 4.2               | 输入 / 输出引脚           |    |

| 4.3               | 时钟工作模式              |    |

| 4.4               | 寄存器说明               |    |

| 4.4.              |                     |    |

| 4.4.              |                     |    |

| 4.5               | 更改频率的方法             |    |

| 4.6 振荡                     | 器                                                                               |     |

|----------------------------|---------------------------------------------------------------------------------|-----|

| 4.6.1                      | 连接晶体谐振器的方法                                                                      |     |

| 4.6.2                      | 输入外部时钟的方法                                                                       |     |

|                            | <b>5</b> 停止的检测功能                                                                |     |

| 4.8 使用                     | 时的注意事项                                                                          |     |

| 4.8.1                      | 有关谐振器的注意事项                                                                      |     |

| 4.8.2                      | 电路板设计的注意事项                                                                      | 47  |

| 第5章                        | 异常处理                                                                            | 40  |

|                            |                                                                                 |     |

| 5.1 概要<br>5.1.1            | ·<br>异常处理的种类和优先级                                                                |     |

| 5.1.1                      | 异常处理的符关和优先级                                                                     |     |

| 5.1.2                      | 异常处理向量表                                                                         |     |

|                            | 开市处连问里衣                                                                         |     |

| 5.2.1                      | 复位的种类                                                                           |     |

| 5.2.1                      | 上电复位                                                                            |     |

| 5.2.3                      | 手动复位                                                                            |     |

|                            | - 情误                                                                            |     |

| 5.3.1                      | 地址错误的发生源                                                                        |     |

| 5.3.2                      | 地址错误的异常处理                                                                       |     |

|                            |                                                                                 |     |

| 5.4.1                      | 中断源                                                                             |     |

| 5.4.2                      | 中断优先级                                                                           |     |

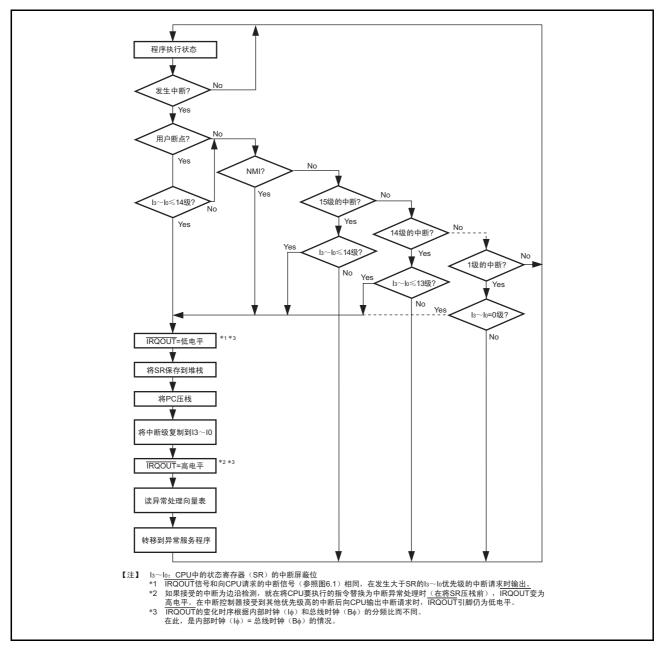

| 5.4.3                      | 中断异常处理                                                                          |     |

| 5.5 指令                     | 的异常                                                                             |     |

| 5.5.1                      | 指令异常的种类                                                                         | 55  |

| 5.5.2                      | 陷阱指令                                                                            | 55  |

| 5.5.3                      | 槽非法指令                                                                           |     |

| 5.5.4                      | 一般非法指令                                                                          | 56  |

| 5.6 异常                     | ·<br>沙理的接受                                                                      | 56  |

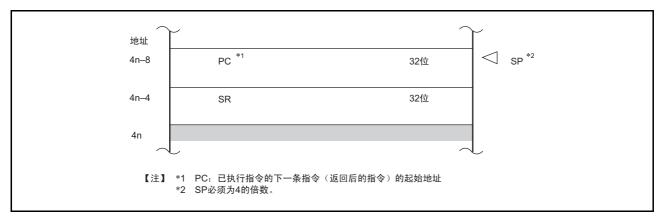

| 5.7 异常                     | ·<br>/处理后的堆栈状态                                                                  | 57  |

| 5.8 使用                     | 时的注意事项                                                                          | 57  |

| 5.8.1                      | 堆栈指针 (SP) 的值                                                                    | 57  |

| 5.8.2                      | 向量基址寄存器 (VBR)的值                                                                 | 57  |

| 5.8.3                      | 地址错误异常处理的堆栈存取中发生的地址错误                                                           | 57  |

| 5.8.4                      | 有关槽非法指令异常处理的注意事项                                                                | 58  |

| <i>t</i> /τ ο <del>÷</del> | → 咖啡 → ★山田 (INTO)                                                               | = 0 |

| 第6章                        | 中断控制器 (INTC)                                                                    |     |

|                            | , #A do 71 Thm                                                                  |     |

|                            | . / 输出引脚                                                                        |     |

|                            | - 器说明                                                                           |     |

| 6.3.1                      | 中断控制寄存器 0 (ICR0)                                                                |     |

| 6.3.2                      | IRQ 控制寄存器 (IRQCR)                                                               |     |

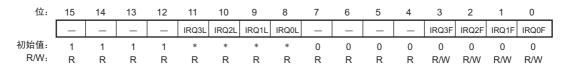

| 6.3.3                      | IRQ 状态寄存器 (IRQSR)<br>中断优先级寄存器 A、D ~ F、H ~ M(IPRA、IPRD ~ IPRF、IPRH ~ IPRM)       |     |

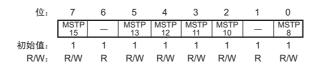

| 6.3.4                      | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                          |     |

|                            | /源<br>                                                                          |     |

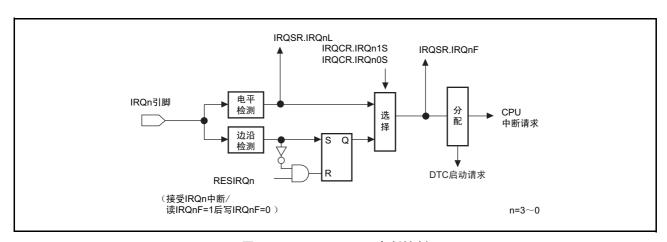

| 6.4.1                      | 外部中断源                                                                           |     |

| 6.4.2<br>6.4.3             | 内部外围模块中断<br>田白斯克内斯                                                              |     |

|                            | 用户断点中断                                                                          |     |

|                            | 7 并吊处理问重表                                                                       |     |

| 6.6.1                      | 中断运行的流程                                                                         |     |

|                            | 中断异常处理结束后的堆栈状态                                                                  |     |

| V.V.                       | 1 BULLET BURKER STORE ALL AN ALL HELDER AND |     |

| 6.7        | 中断响应时间                                    | 71  |

|------------|-------------------------------------------|-----|

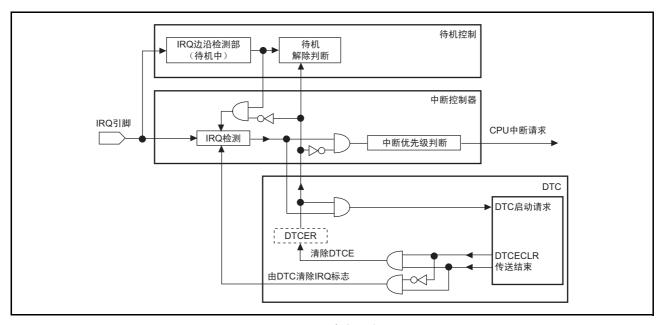

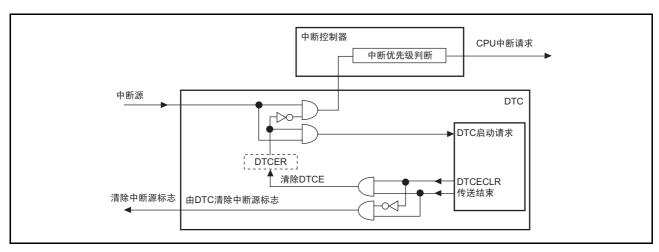

| 6.8        | 通过中断请求信号进行的数据传送                           |     |

| 6.8        | 3.1 中断请求信号作为 DTC 启动源和 CPU 中断源的情况          | 73  |

| 6.8        |                                           |     |

| 6.8        | 3.3 中断请求信号作为 CPU 中断源而不作为 DTC 启动源          | 73  |

| 6.9        | 使用时的注意事项                                  | 73  |

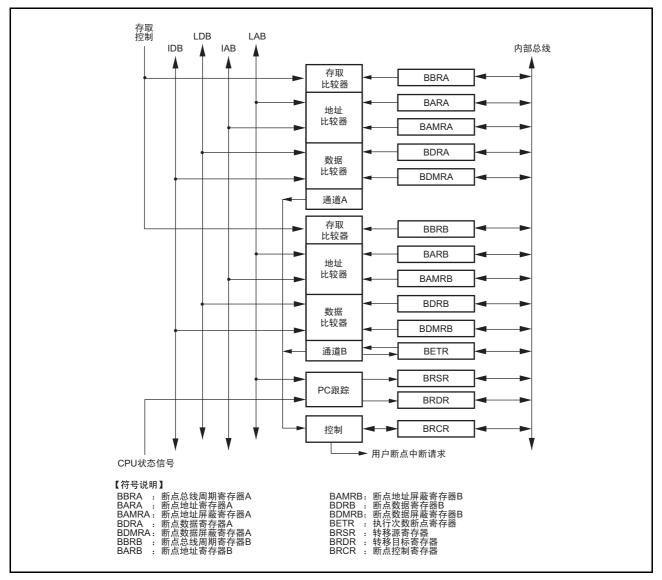

| 第7章        | 用户断点控制器 (UBC)                             | 74  |

| 7.1        | 特点                                        | 74  |

| 7.2        | 输入/输出引脚                                   | 75  |

| 7.3        | 寄存器说明                                     | 76  |

| 7.3        | 5.1 断点地址寄存器 A (BARA)                      | 76  |

| 7.3        | 5.2 断点地址屏蔽寄存器 A (BAMRA)                   | 77  |

| 7.3        | 5.3 断点总线周期寄存器 A (BBRA)                    | 77  |

| 7.3        | .4 断点数据寄存器 A (BDRA)                       | 78  |

| 7.3        | 5.5 断点数据屏蔽寄存器 A (BDMRA)                   | 79  |

| 7.3        | 5.6 断点地址寄存器 B (BARB)                      | 79  |

| 7.3        | 7 · · · · · = — · · · · · · · · · · · · · |     |

| 7.3        | 1.8 断点数据寄存器 B (BDRB)                      | 80  |

| 7.3        | , , , , , , , , , , , , , , , , , , ,     |     |

| 7.3        | 5.10 断点总线周期寄存器 B (BBRB)                   |     |

| 7.3        |                                           |     |

| 7.3        | 5.12 执行次数断点寄存器 (BETR)                     |     |

|            | 5.13 转移源寄存器 (BRSR)                        |     |

|            | 5.14 转移目标寄存器 (BRDR)                       |     |

| 7.4        | = 1                                       |     |

| 7.4        | 747 51XIII C 14 B4 VIC IE                 |     |

| 7.4        | - 100 (7 47) 41700                        |     |

| 7.4        | 23044 14 00 4774 847 47                   |     |

| 7.4        |                                           |     |

| 7.4        |                                           |     |

| 7.4        |                                           |     |

| 7.4        |                                           |     |

| 7.5        | 使用时的注意事项                                  | 93  |

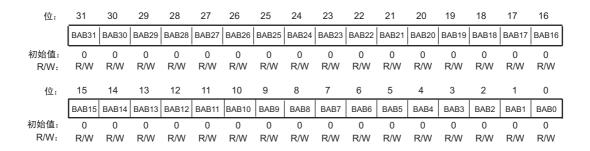

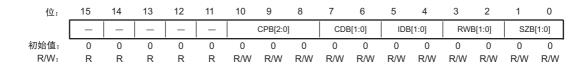

| 第8章        |                                           |     |

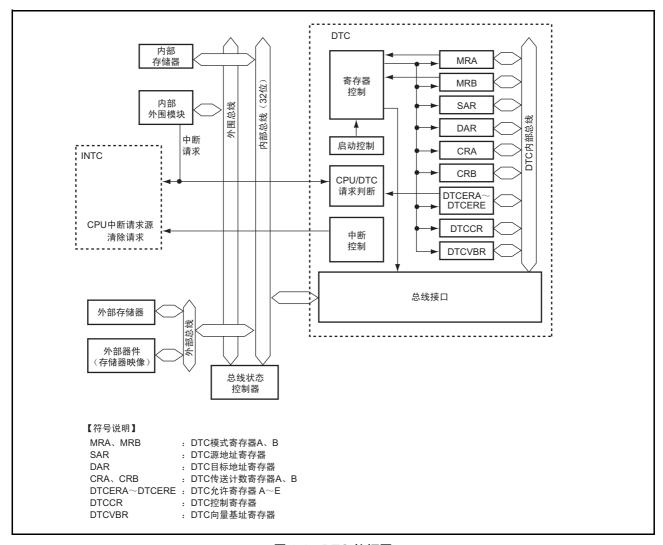

| 8.1        | 特点                                        |     |

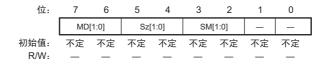

| 8.2        | 寄存器说明                                     |     |

| 8.2        |                                           |     |

| 8.2        |                                           |     |

| 8.2        |                                           |     |

| 8.2        |                                           |     |

| 8.2        | 7.7 = 7.7 22 - 7.7 200                    |     |

| 8.2        |                                           |     |

| 8.2        | - 2 - 1 - 1 - 1 - 1                       |     |

| 8.2        |                                           |     |

| 8.2        | , , , , ,                                 |     |

|            | 2.10 总线功能扩展寄存器 (BSCEHR)                   |     |

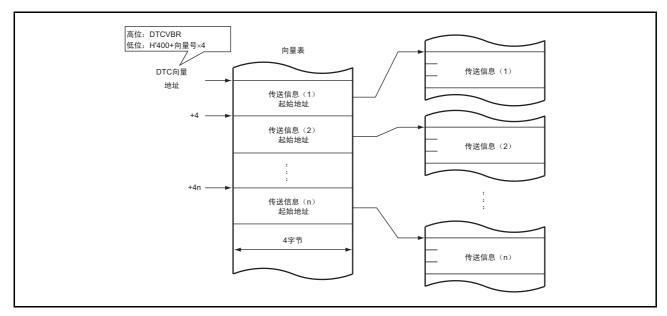

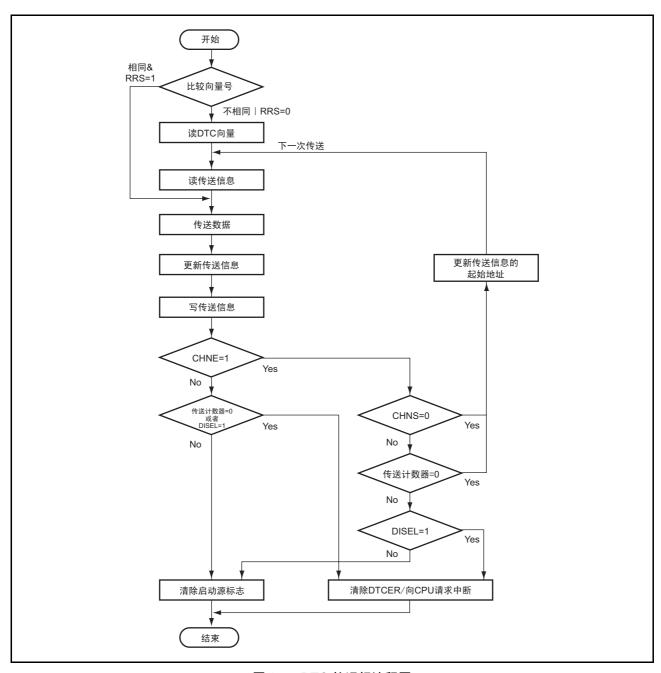

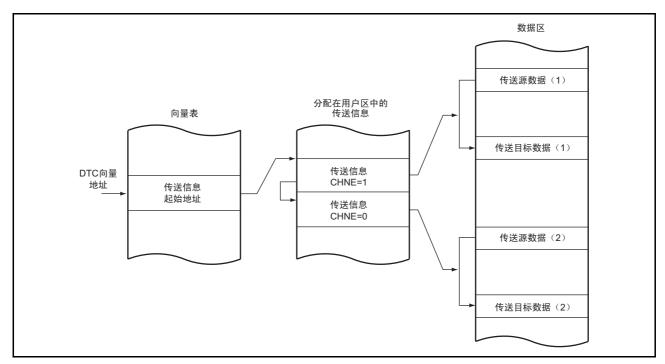

| 8.3        | 启动源<br>传送信息的分配和 DTC 向量表                   |     |

| 8.4<br>8.5 | 传达信息的分配和 DIC 问量表                          |     |

| 8.5<br>8.5 |                                           |     |

| 8.5<br>8.5 |                                           |     |

| 0.5        |                                           | 100 |

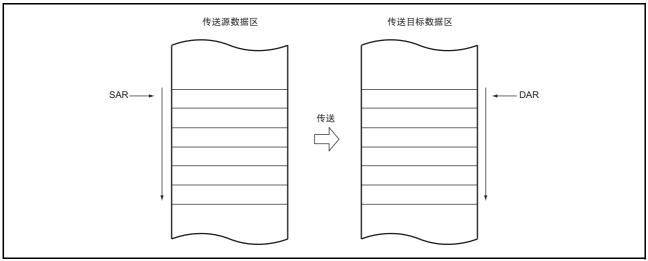

| 8.5.3   | 正常传送模式                         | 108 |

|---------|--------------------------------|-----|

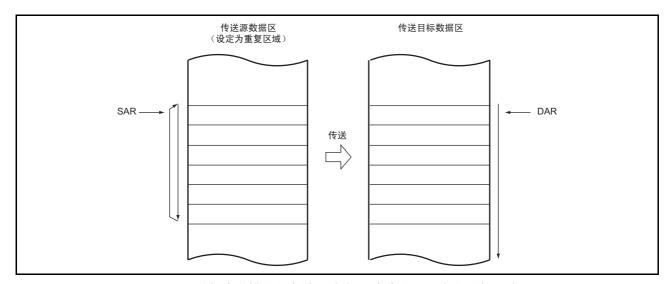

| 8.5.4   | 重复传送模式                         | 109 |

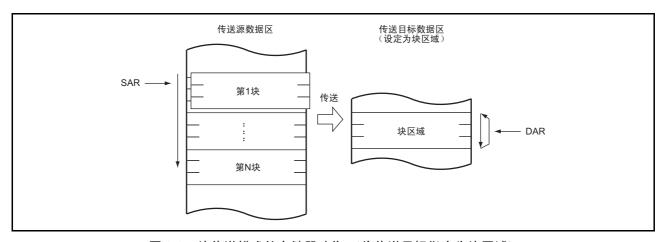

| 8.5.5   | 块传送模式                          | 110 |

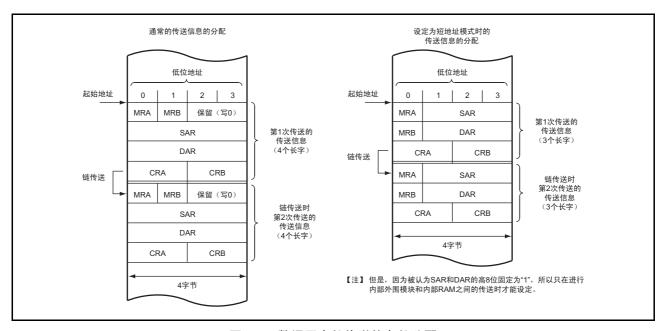

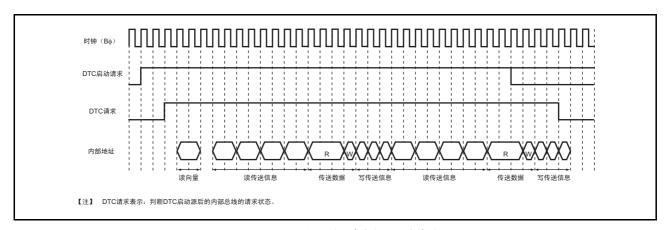

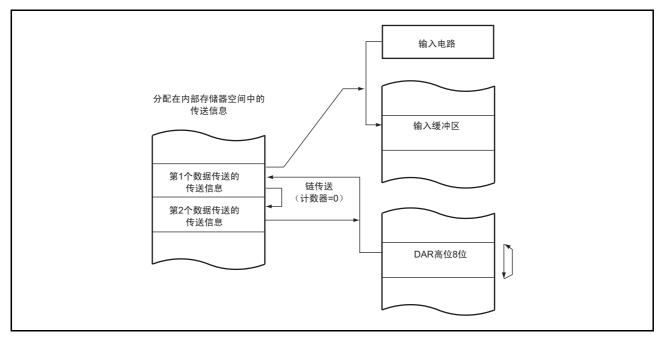

| 8.5.6   | 链传送                            | 111 |

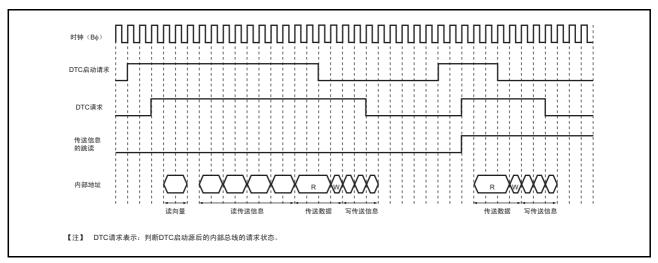

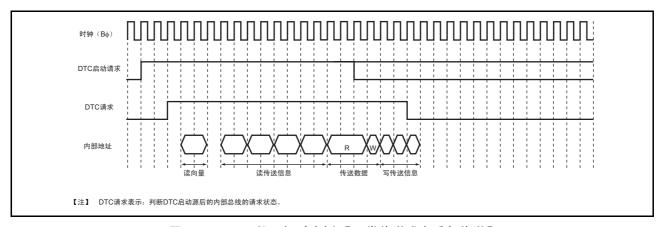

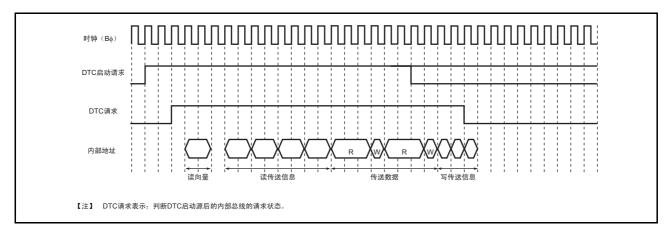

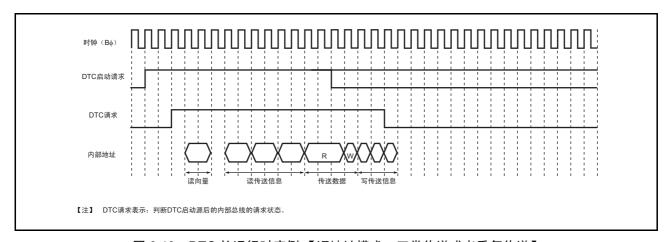

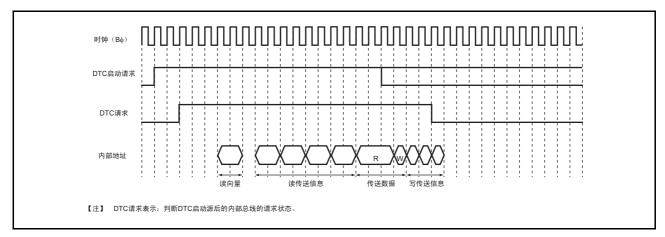

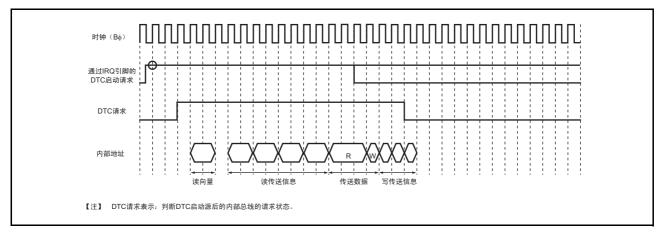

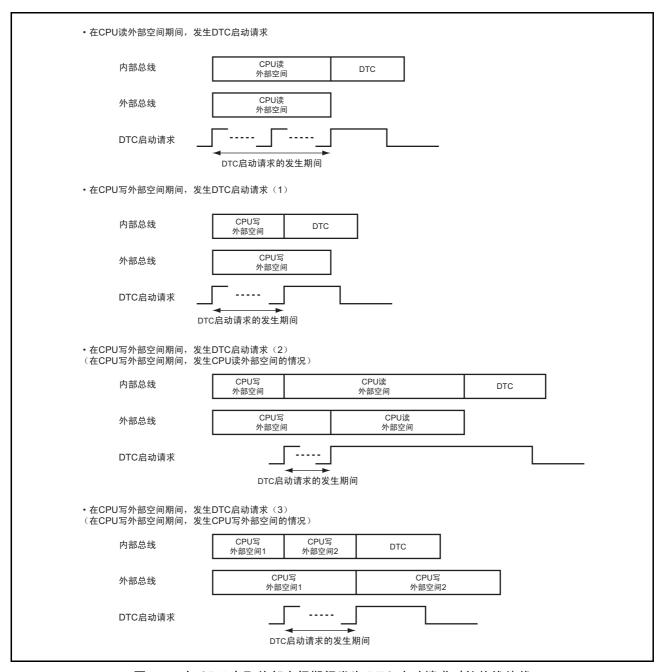

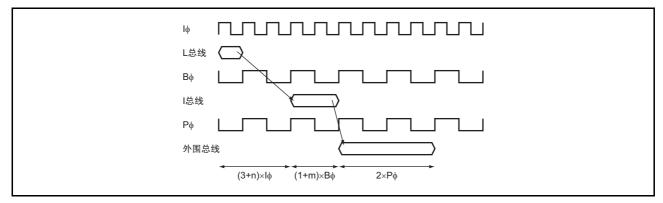

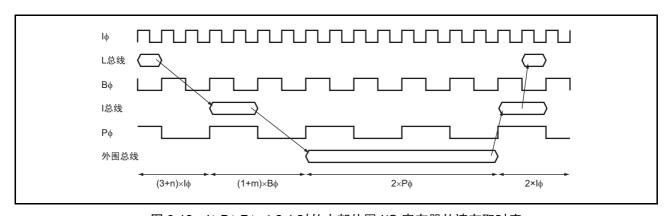

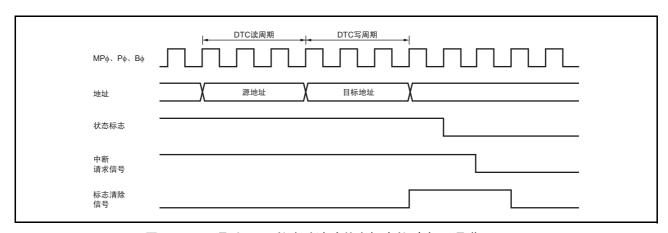

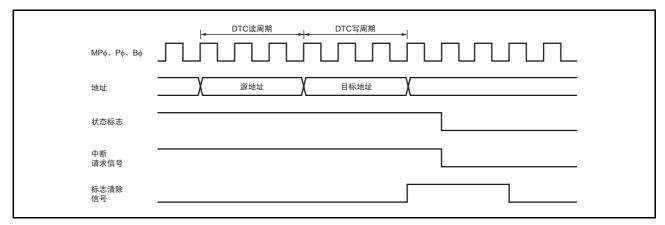

| 8.5.7   | 运行时序                           | 111 |

| 8.5.8   | DTC 的执行状态                      | 113 |

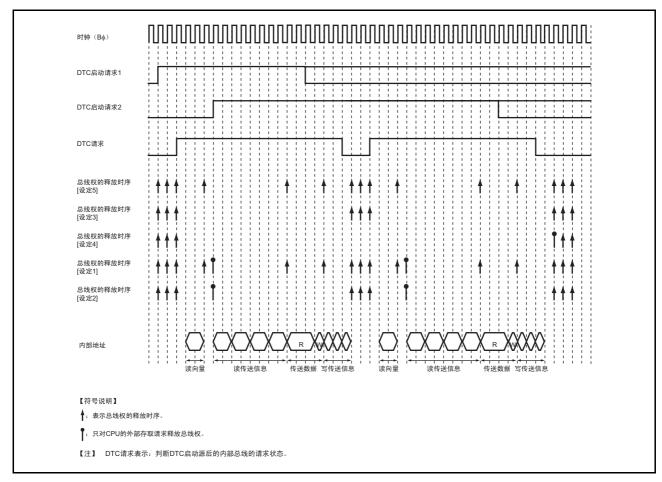

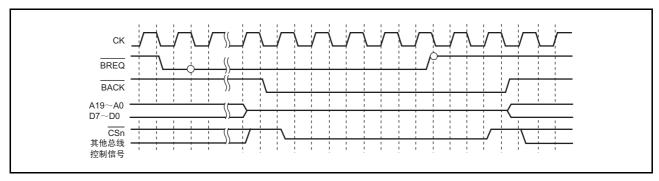

| 8.5.9   | DTC 的总线权释放时序                   | 114 |

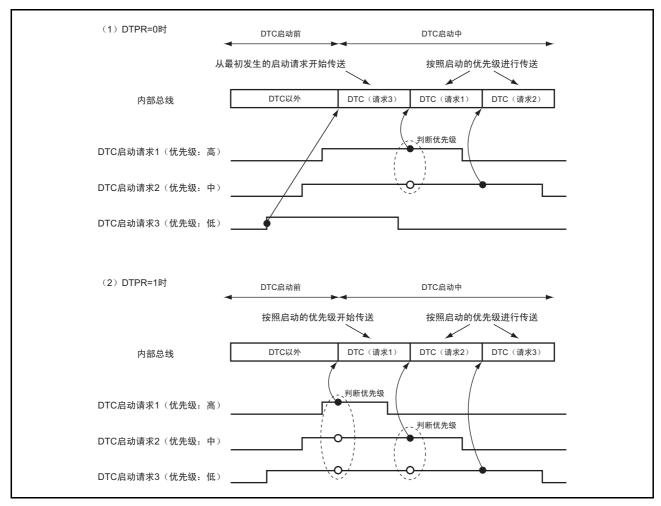

| 8.5.10  | DTC 启动优先级的设定                   | 116 |

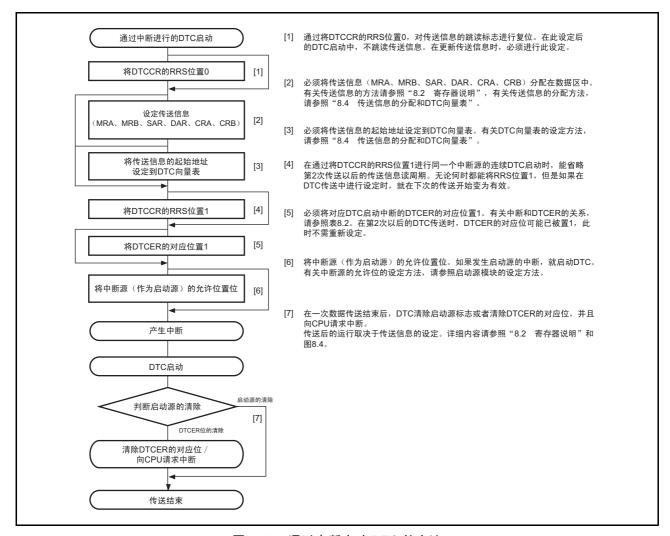

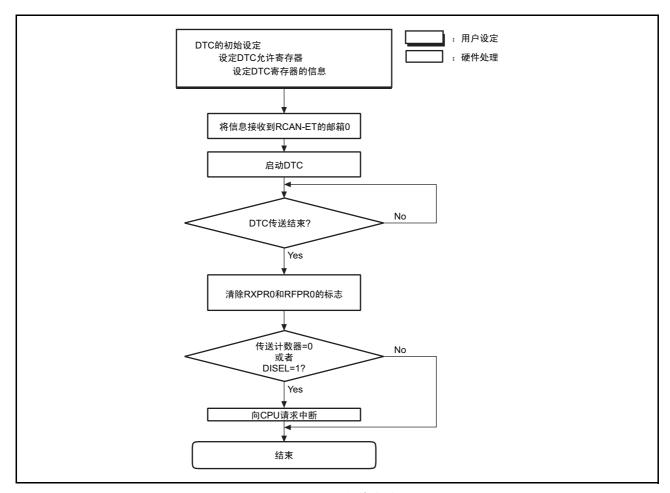

| 8.6 通道  | 过中断启动 DTC                      | 117 |

| 8.7 DT  | C 使用例                          | 118 |

| 8.7.1   | 正常传送                           | 118 |

| 8.7.2   | 计数器 =0 的链传送                    | 118 |

| 8.8 中間  | 析源                             | 119 |

| 8.9 使月  | 目时的注意事项                        | 119 |

| 8.9.1   | 模块待机模式的设定                      | 119 |

| 8.9.2   | 内部 RAM                         | 119 |

| 8.9.3   | DTCE 位的设定                      | 119 |

| 8.9.4   | 链传送                            | 119 |

| 8.9.5   | 传送信息的起始地址 / 源地址 / 目标地址         | 120 |

| 8.9.6   | 通过 DTC 存取 DTC 寄存器              |     |

| 8.9.7   | IRQ 中断作为 DTC 传送源时的注意事项         |     |

| 8.9.8   | SCI 作为 DTC 启动源时的注意事项           | 120 |

| 8.9.9   | 中断源标志的清除                       |     |

| 8.9.10  | NMI 中断和 DTC 启动的竞争              |     |

| 8.9.11  | 中途取消 DTC 启动请求时的运行              |     |

|         |                                |     |

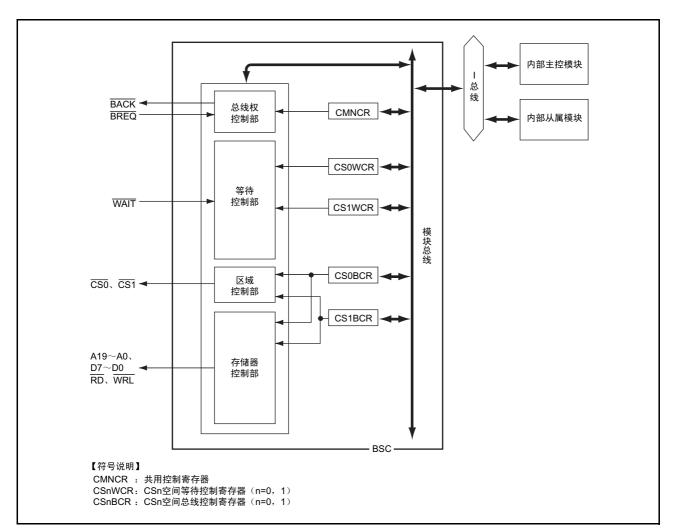

| 第9章     | 总线状态控制器 (BSC)                  | 121 |

| 9.1 特力  | <u> </u>                       | 121 |

| 9.2 输力  | 入/输出引脚                         | 122 |

| 9.3 区均  | 或概要                            | 122 |

| 9.3.1   | 空间分割                           | 122 |

| 9.3.2   | 地址映像                           | 122 |

| 9.4 寄石  | 存器说明                           | 123 |

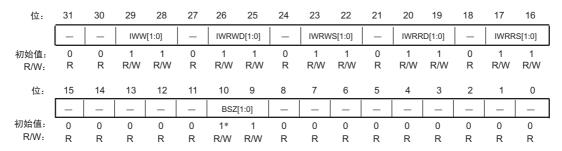

| 9.4.1   | 共用控制寄存器 (CMNCR)                | 124 |

| 9.4.2   | CSn 空间总线控制寄存器 (CSnBCR) (n=0、1) | 124 |

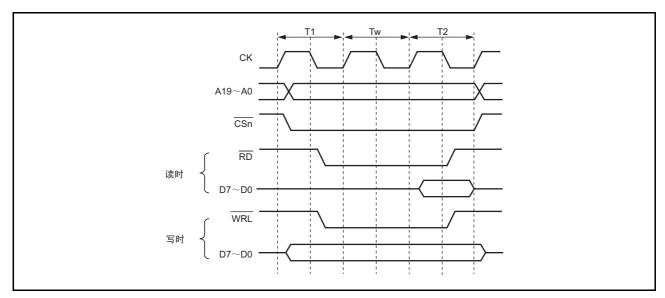

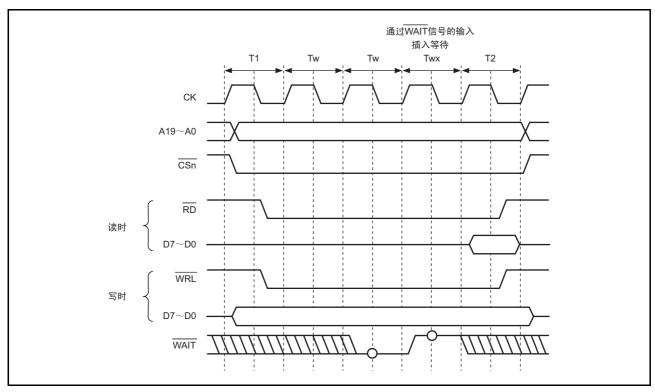

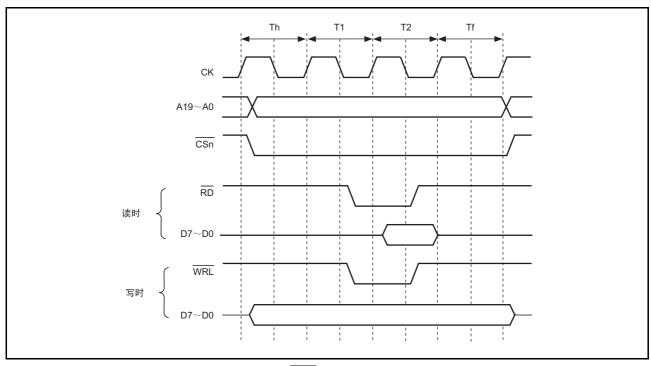

| 9.4.3   | CSn 空间等待控制寄存器 (CSnWCR) (n=0、1) | 126 |

| 9.4.4   | 总线功能扩展寄存器 (BSCEHR)             |     |

| 9.5 运行  | <b>亍说明</b>                     |     |

| 9.5.1   | 字节排序 / 存取长度和数据调整               | 130 |

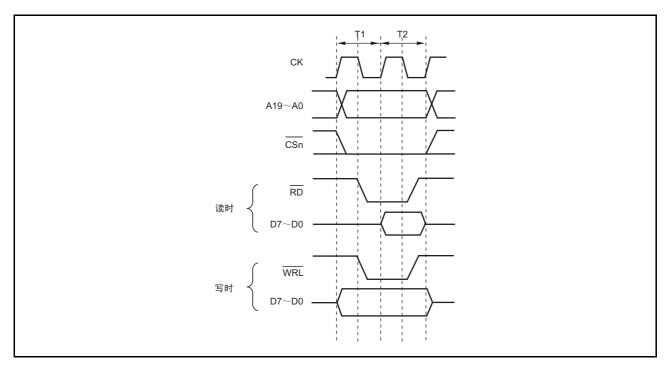

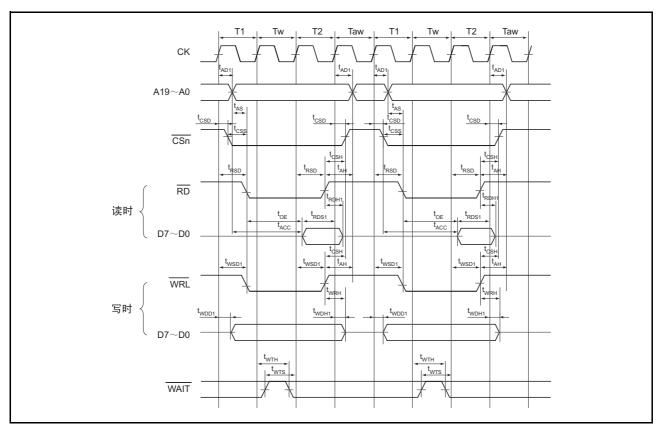

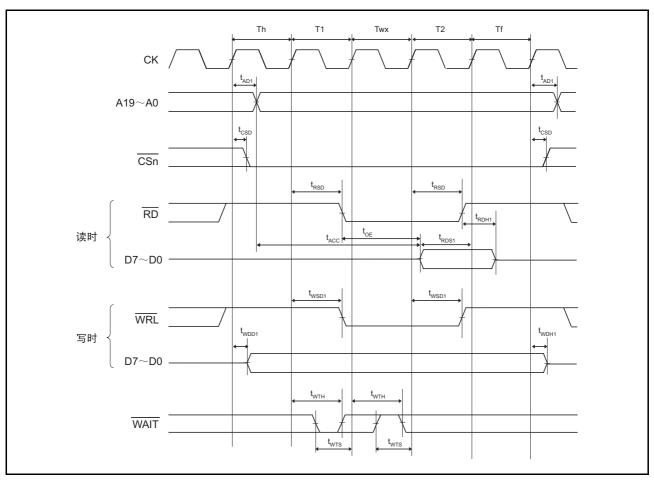

| 9.5.2   | 通常空间接口                         |     |

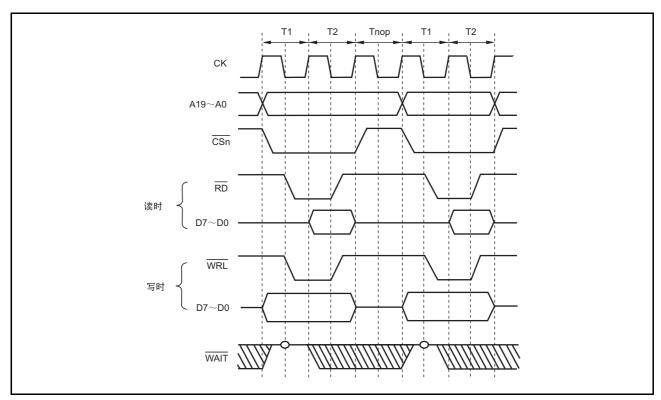

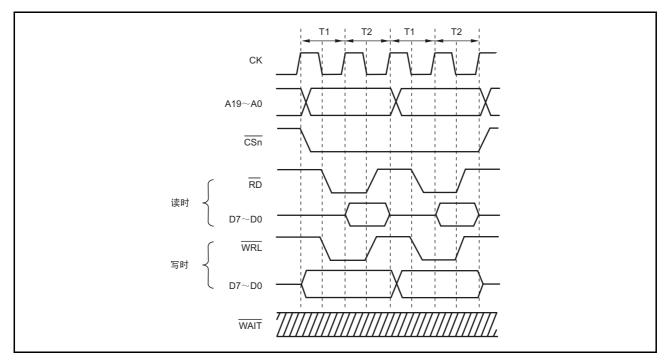

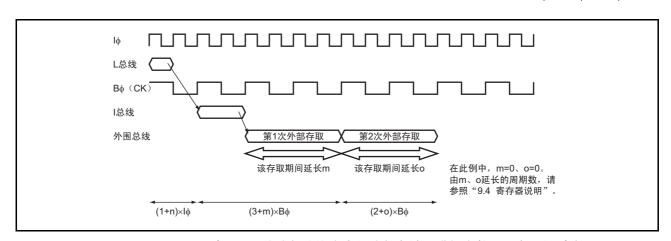

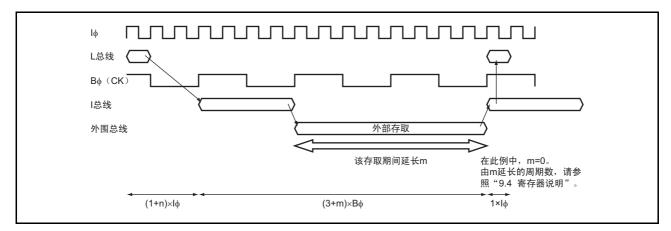

| 9.5.3   | 存取等待的控制                        |     |

| 9.5.4   |                                |     |

| 9.5.5   | 存取周期之间的等待                      |     |

| 9.5.6   | 总线仲裁                           |     |

| 9.5.7   | 其他                             |     |

| 9.5.8   | CPU 存取内部 FLASH 和内部 RAM         |     |

| 9.5.9   | CPU 存取内部外围 I/O 寄存器             |     |

| 9.5.10  | CPU 存取外部存储器                    |     |

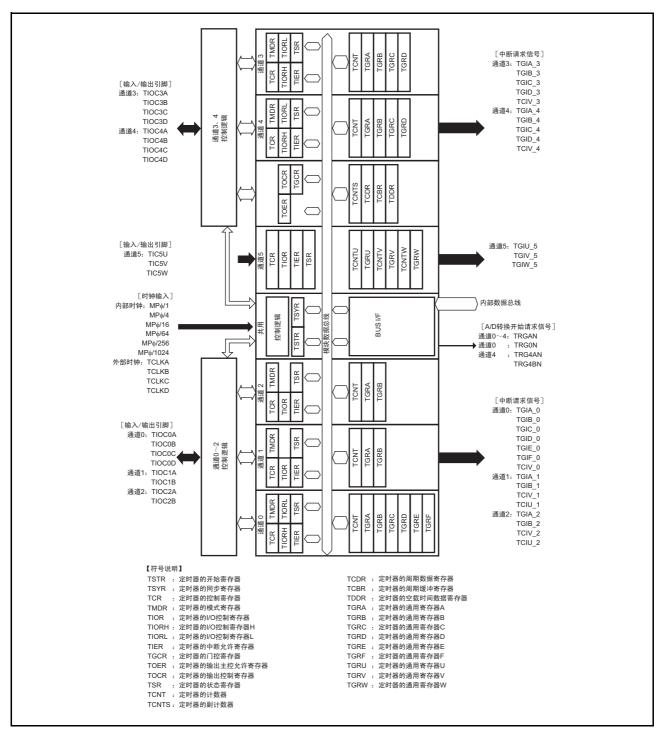

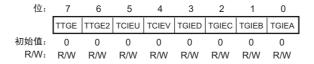

| 第 10 章  | 多功能定时器脉冲单元 2 (MTU2)            | 142 |

| 10.1 特別 | <u> </u>                       | 142 |

| 10.2 输力 | <br>入/输出引脚                     | 146 |

|         | 字器说明                           |     |

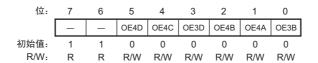

| 10.3.1  | 定时器的控制寄存器 (TCR)                         | 150 |

|---------|-----------------------------------------|-----|

| 10.3.2  | 定时器的模式寄存器 (TMDR)                        | 153 |

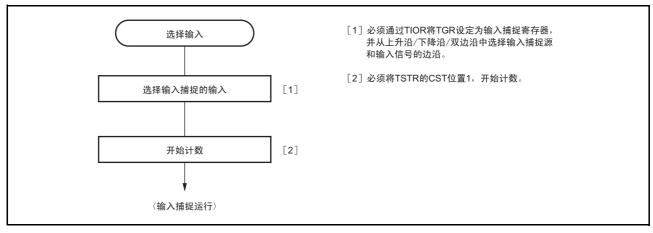

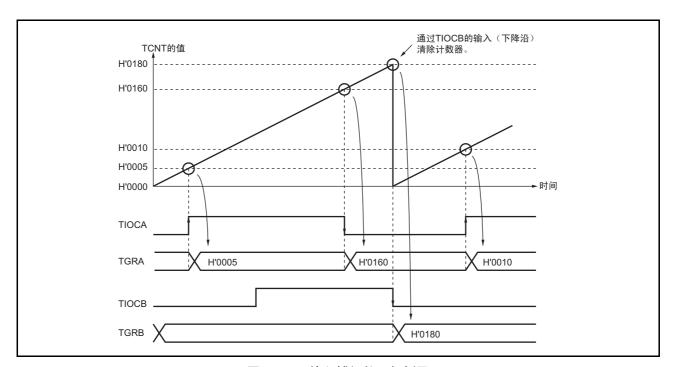

| 10.3.3  | 定时器的 I/O 控制寄存器 (TIOR)                   |     |

| 10.3.4  | 定时器的比较匹配清除寄存器(TCNTCMPCLR)               |     |

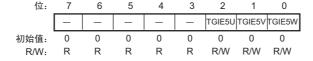

| 10.3.5  | 定时器的中断允许寄存器 (TIER)                      |     |

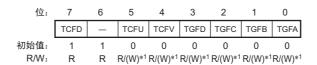

| 10.3.6  | 定时器的状态寄存器 (TSR)                         |     |

| 10.3.7  | 定时器的缓冲运行传送模式寄存器(TBTM)                   |     |

| 10.3.8  | 定时器的输入捕捉控制寄存器 (TICCR)                   |     |

| 10.3.9  | 定时器的同步清除寄存器 (TSYCR)                     |     |

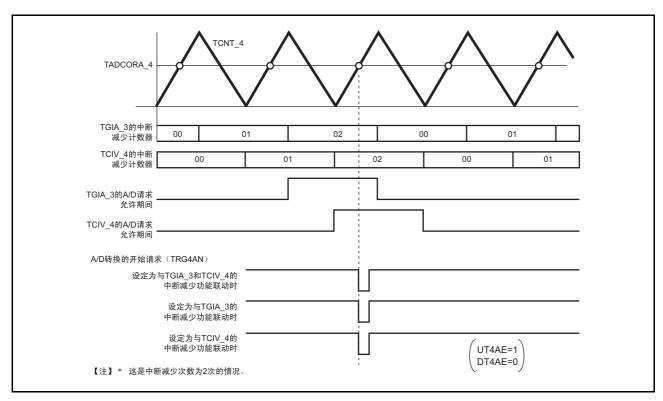

| 10.3.10 | 定时器的 A/D 转换开始请求的控制寄存器 (TADCR)           |     |

| 10.3.11 | 定时器的 A/D 转换开始请求的周期设定寄存器(TADCORA/B_4)    |     |

| 10.3.12 | 定时器的 A/D 转换开始请求的周期设定缓冲寄存器(TADCOBRA/B_4) |     |

| 10.3.13 | 定时器的计数器 (TCNT)                          |     |

| 10.3.14 | 定时器的通用寄存器 (TGR)                         |     |

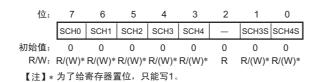

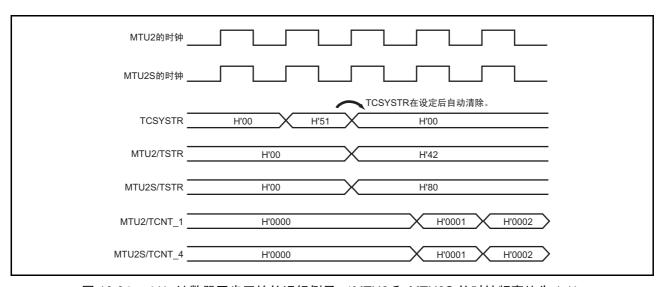

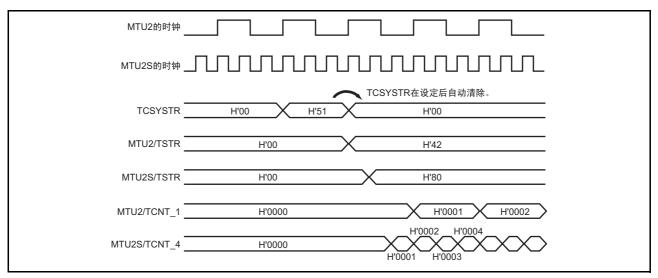

| 10.3.15 | 定时器的开始寄存器 (TSTR)                        |     |

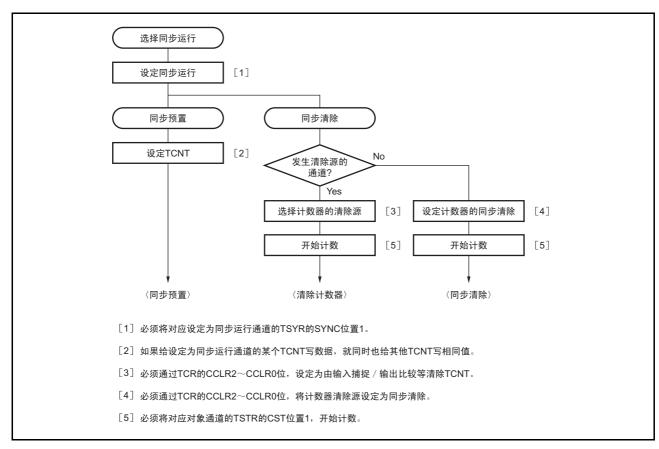

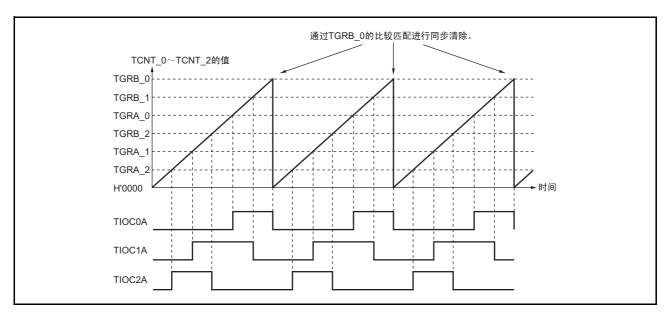

| 10.3.16 | 定时器的同步寄存器 (TSYR)                        |     |

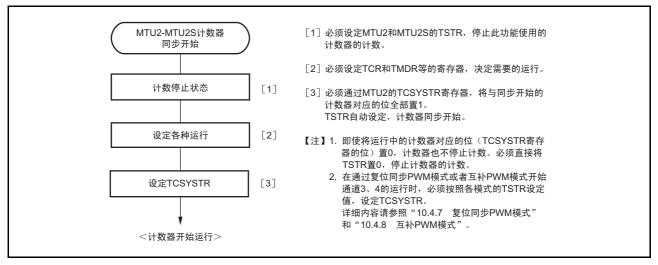

| 10.3.17 | 定时器的计数器同步开始寄存器(TCSYSTR)                 |     |

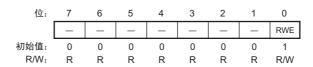

| 10.3.18 | 定时器的读写允许寄存器 (TRWER)                     |     |

| 10.3.19 | 定时器的输出主控允许寄存器 (TOER)                    |     |

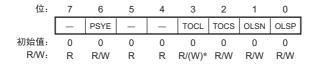

| 10.3.20 | 定时器的输出控制寄存器 1 (TOCR1)                   |     |

| 10.3.21 | 定时器的输出控制寄存器 2 (TOCR2)                   |     |

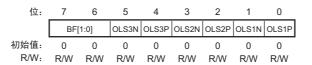

| 10.3.22 | 定时器的输出电平缓冲寄存器(TOLBR)                    |     |

| 10.3.23 | 定时器的门控寄存器(TGCR)                         |     |

| 10.3.24 | 定时器的子计数器(TCNTS)                         |     |

| 10.3.24 | 定时器的空载时间数据寄存器 (TDDR)                    |     |

| 10.3.26 | 定时器的周期数据寄存器 (TCDR)                      |     |

| 10.3.20 | 定时器的周期缓冲寄存器(TCBR)                       |     |

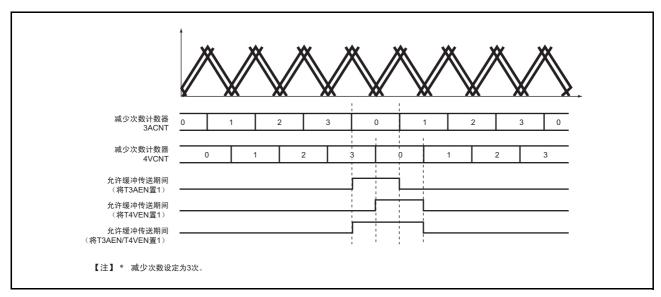

| 10.3.27 | 定时器的中断减少设定寄存器(TITCR)                    |     |

| 10.3.29 | 定时器的中断减少次数计数器(TITCNT)                   |     |

| 10.3.20 | 定时器的缓冲传送设定寄存器(TBTER)                    |     |

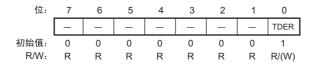

| 10.3.31 | 定时器的空载时间允许寄存器 (TDER)                    |     |

| 10.3.31 | 定时器的波形控制寄存器(TWCR)                       |     |

| 10.3.32 | 和总线主控的接口                                |     |

|         | · · · · · · · · · · · · · · · · · · ·   |     |

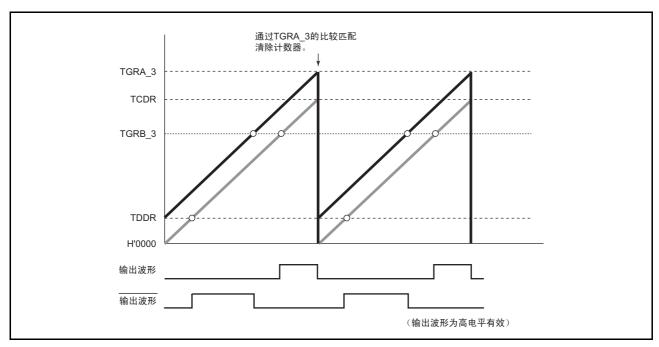

|         | 基本运行                                    |     |

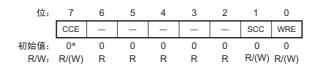

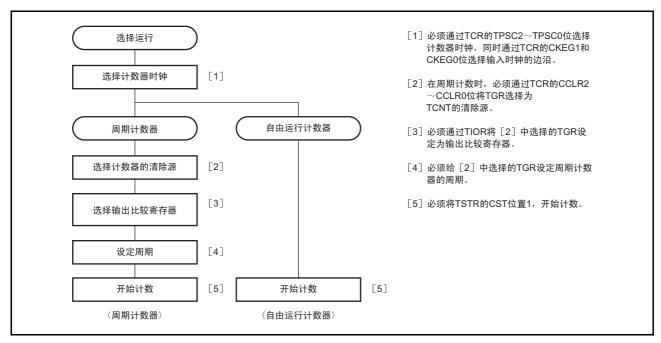

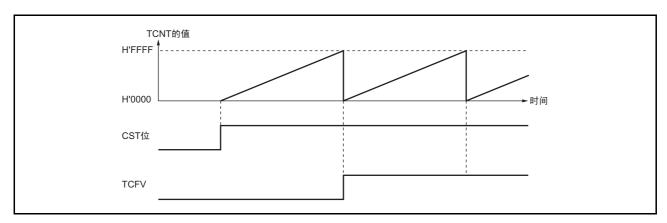

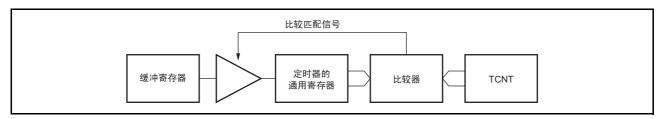

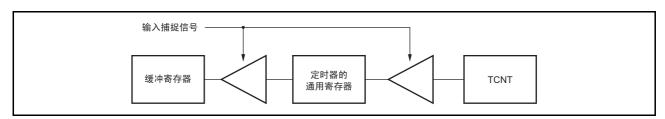

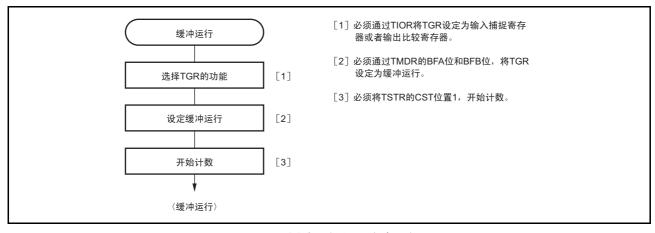

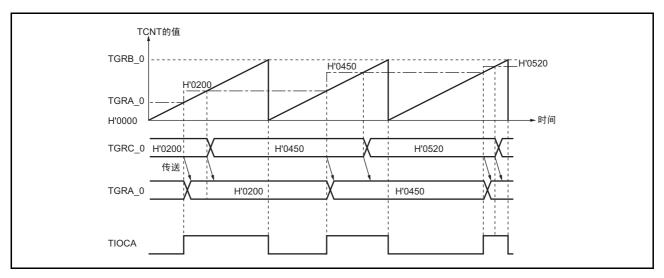

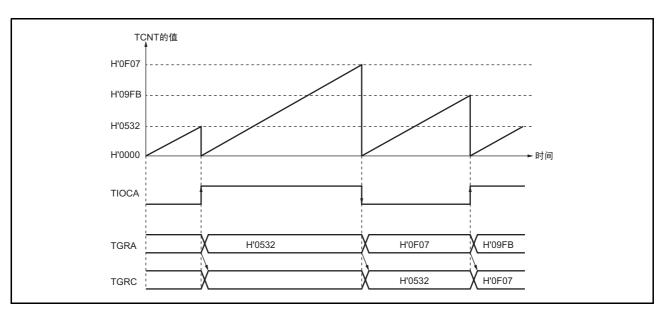

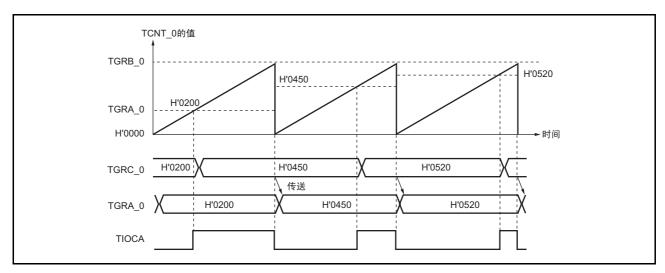

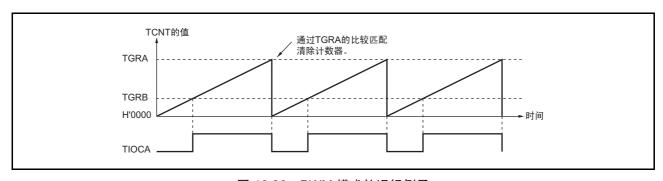

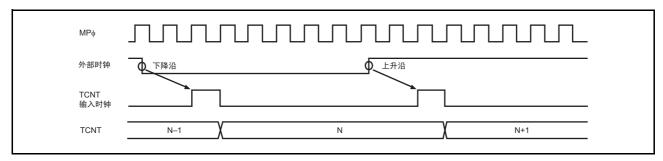

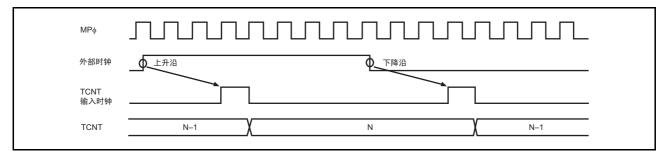

| 10.4.1  |                                         |     |

| 10.4.2  | 例少运行                                    |     |

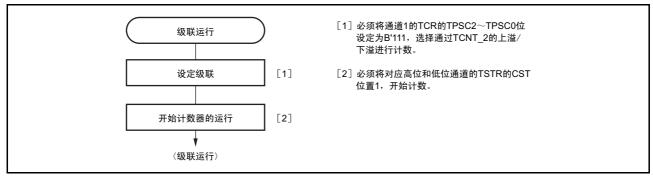

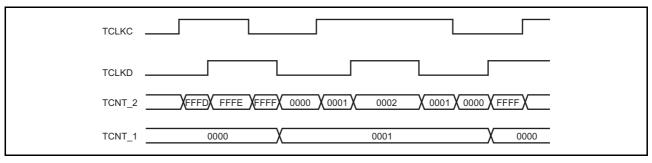

| 10.4.3  | 级联运行                                    |     |

| 10.4.4  | -                                       |     |

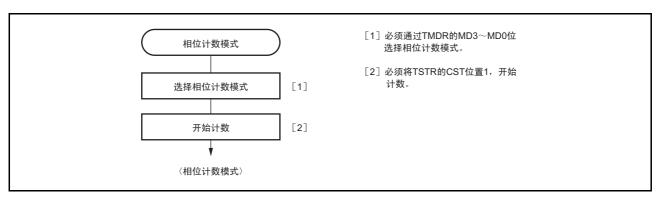

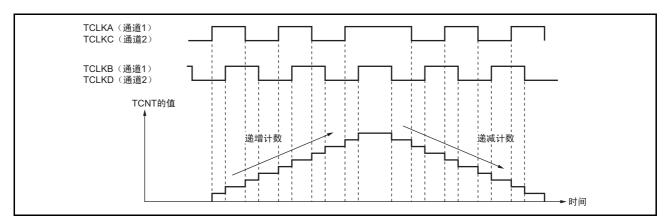

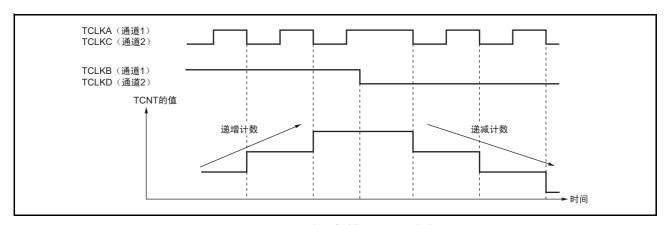

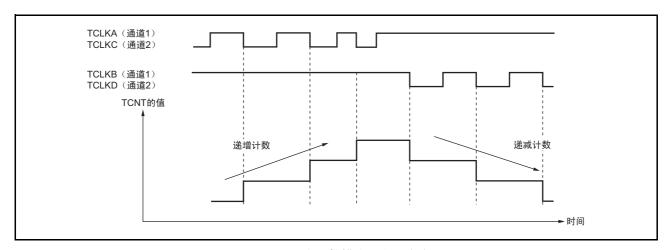

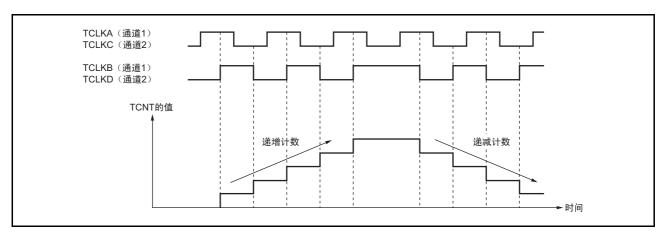

| 10.4.5  | 相位计数模式                                  |     |

| 10.4.0  | 何位り数侯式                                  |     |

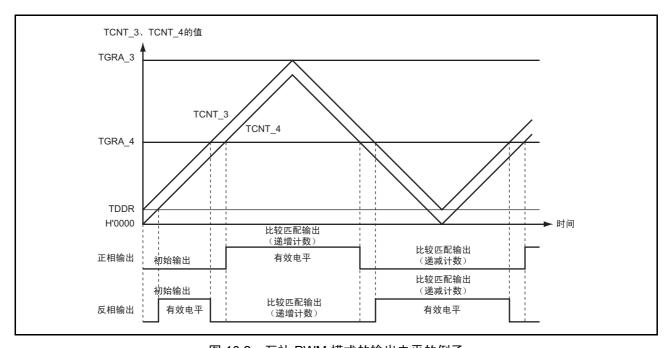

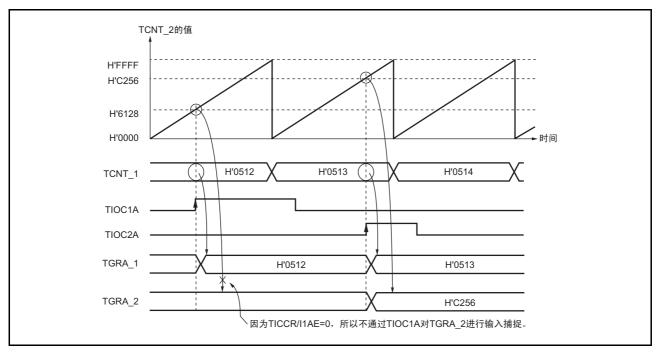

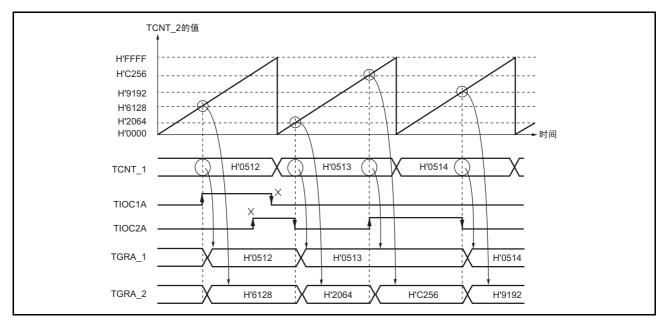

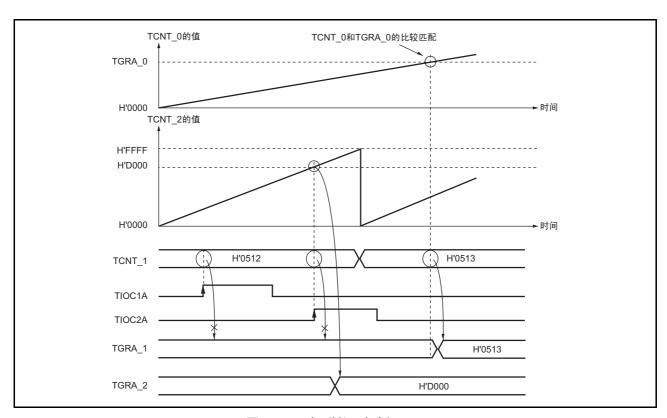

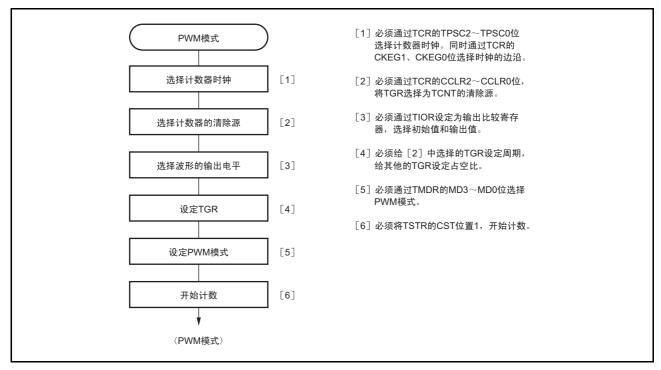

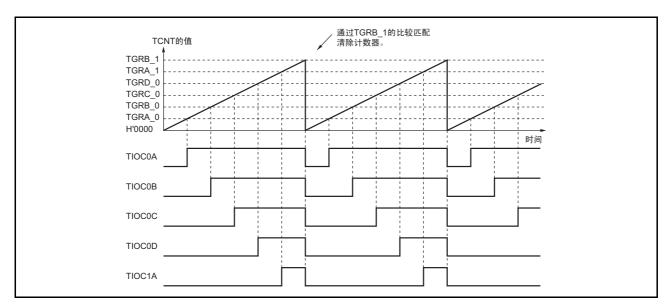

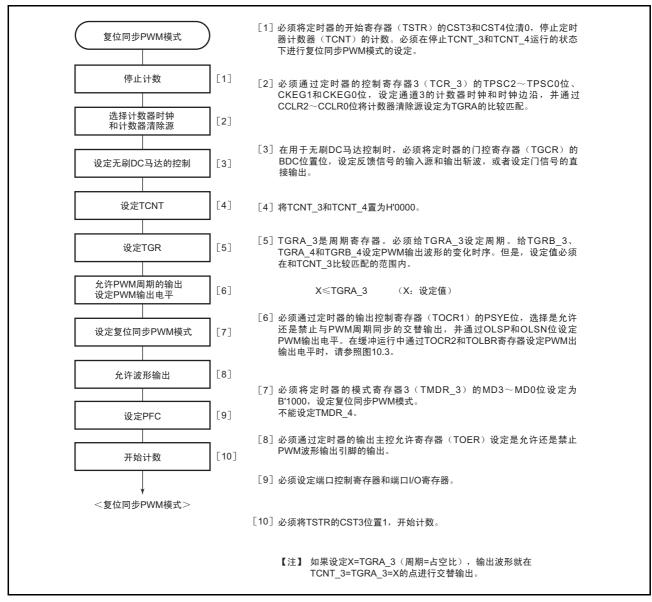

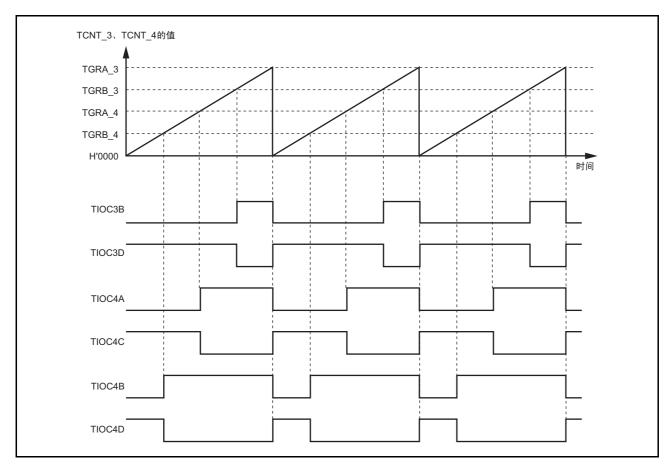

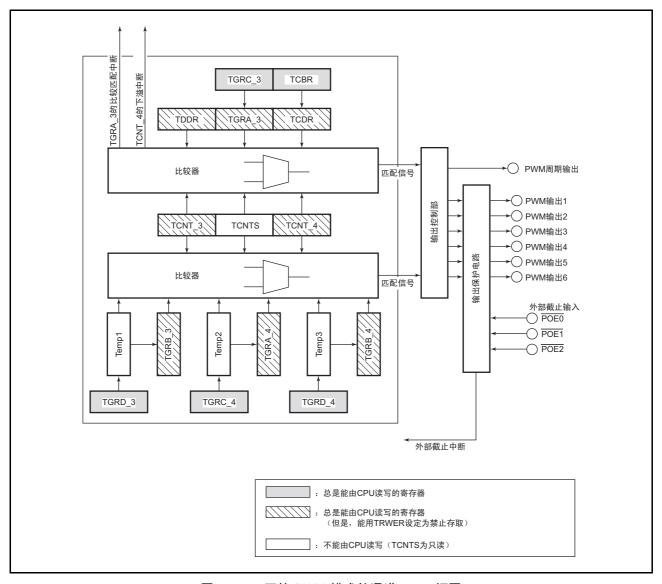

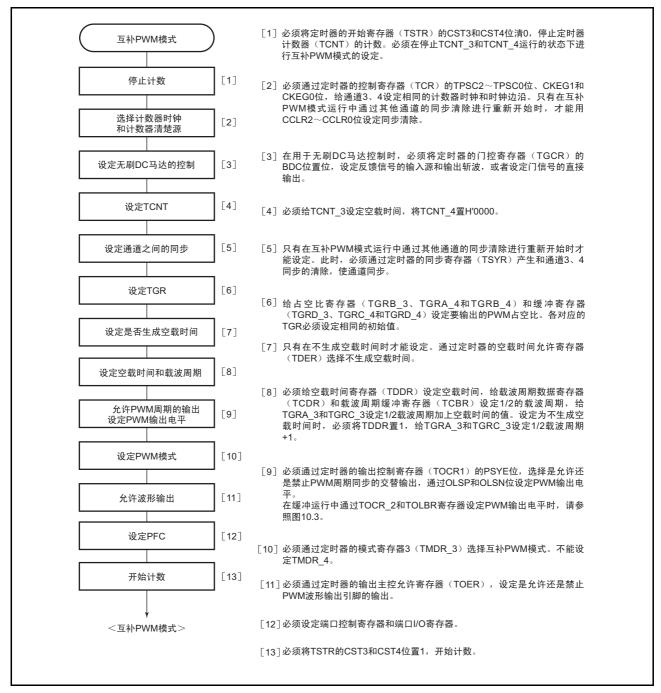

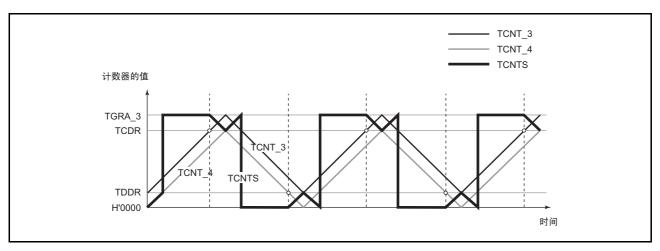

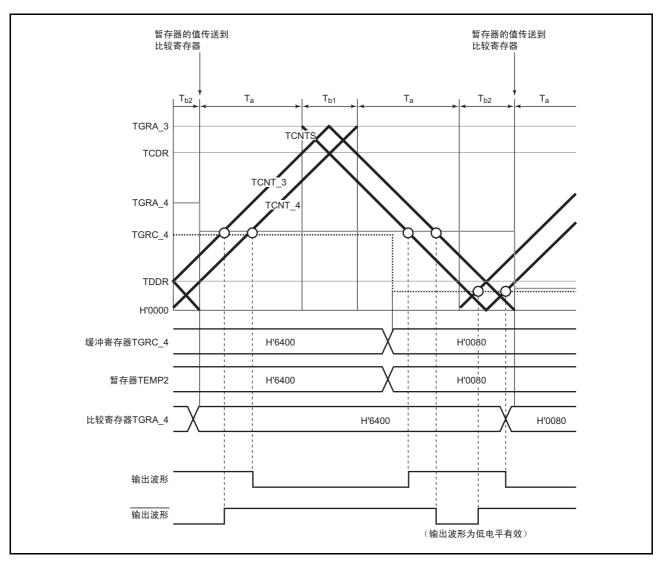

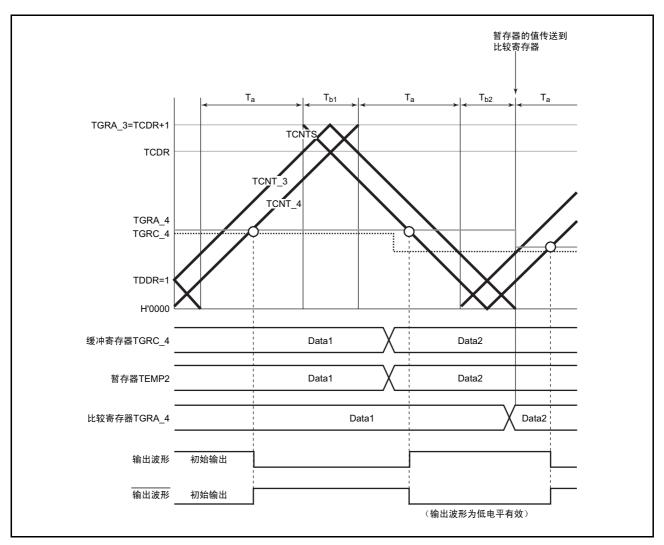

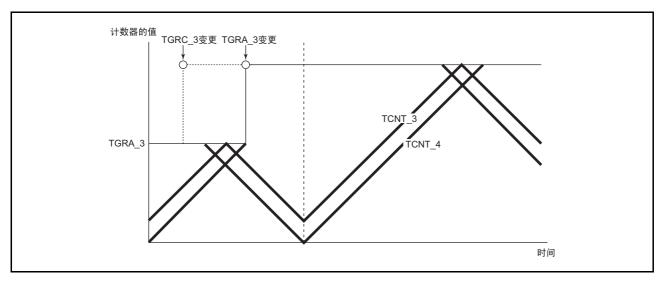

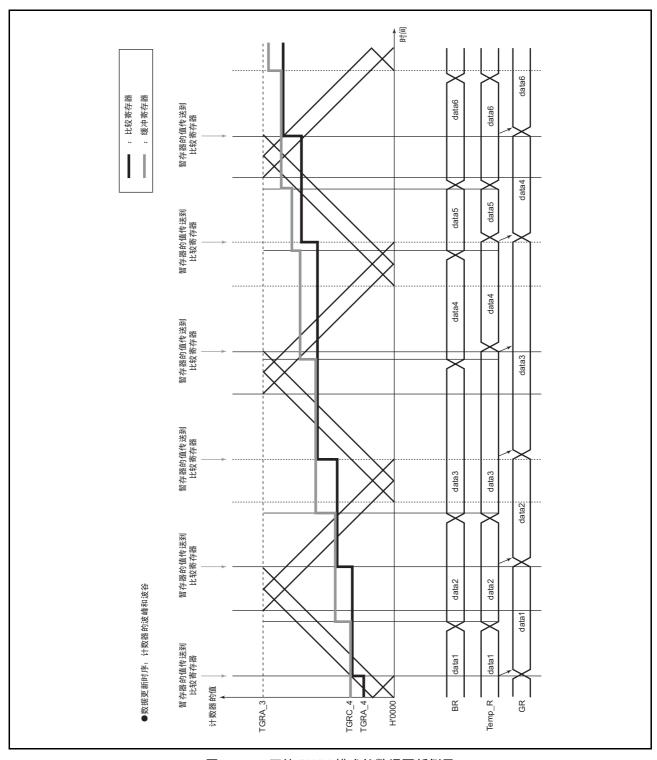

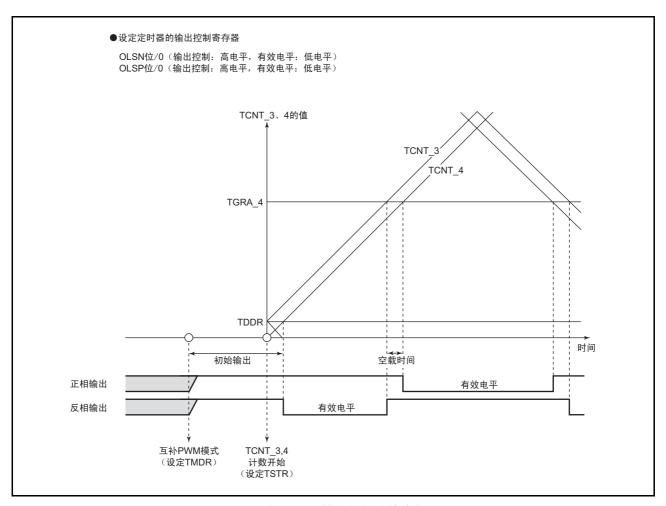

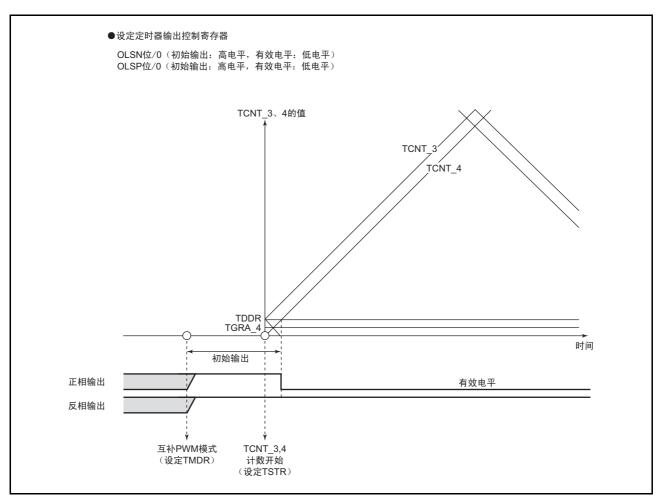

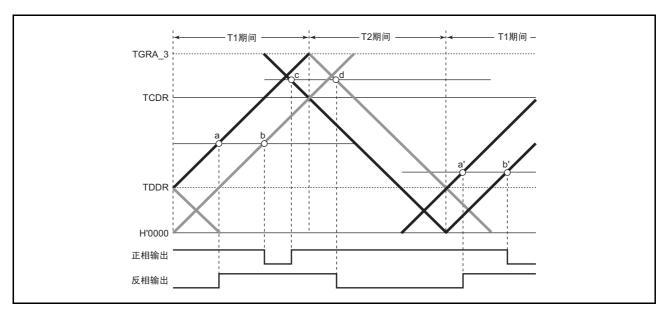

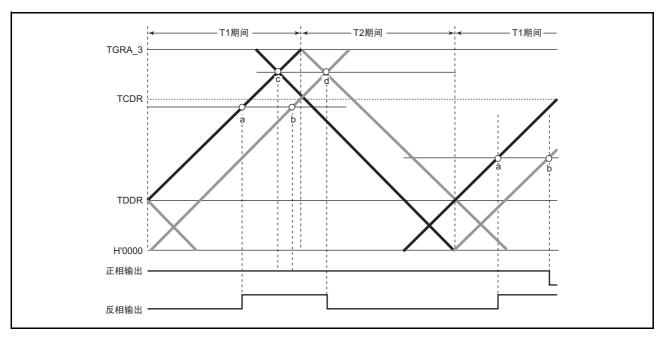

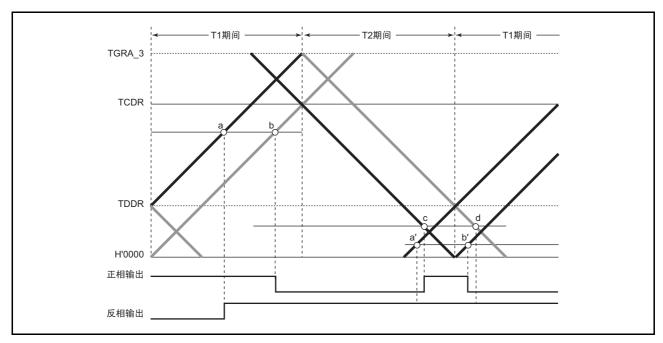

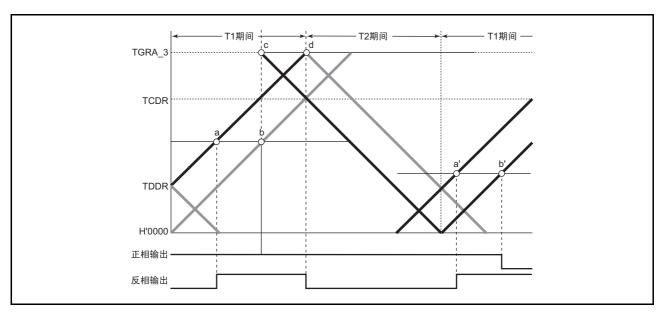

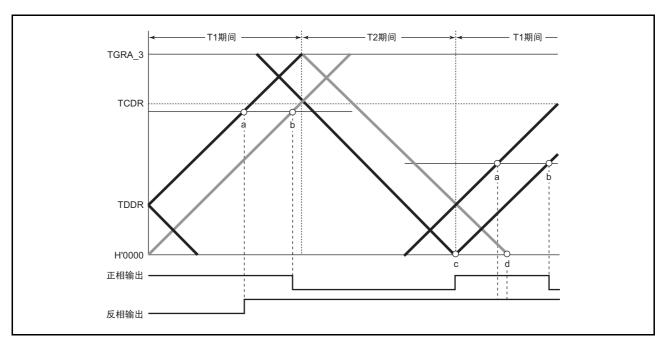

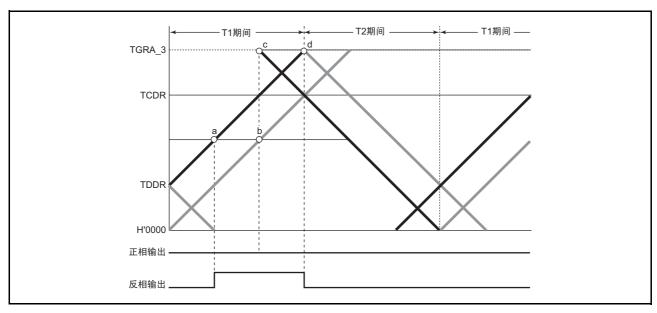

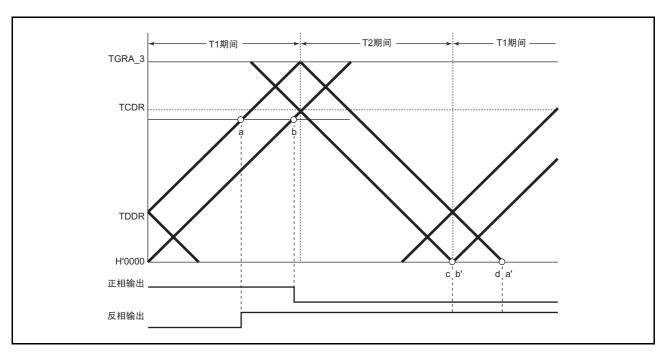

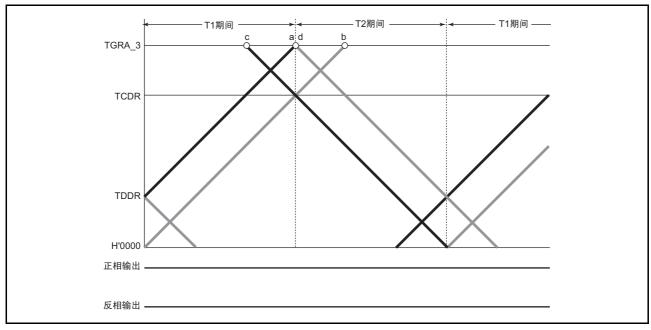

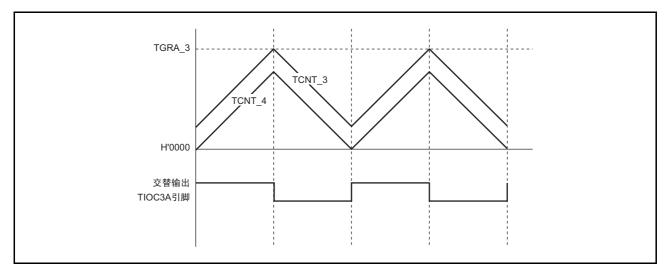

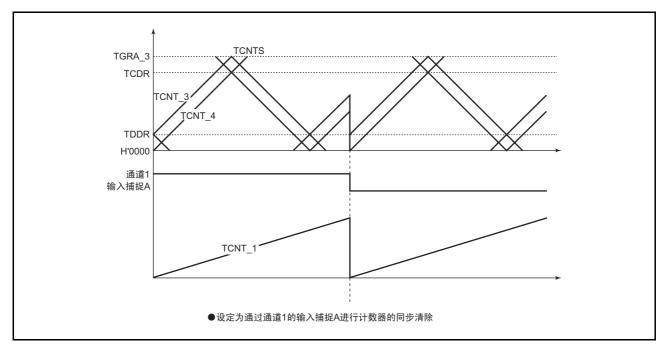

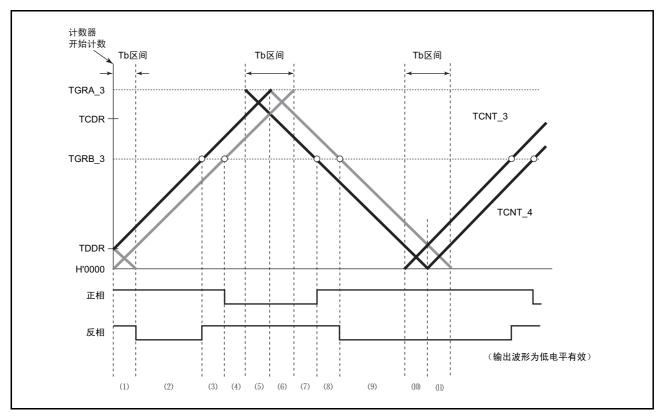

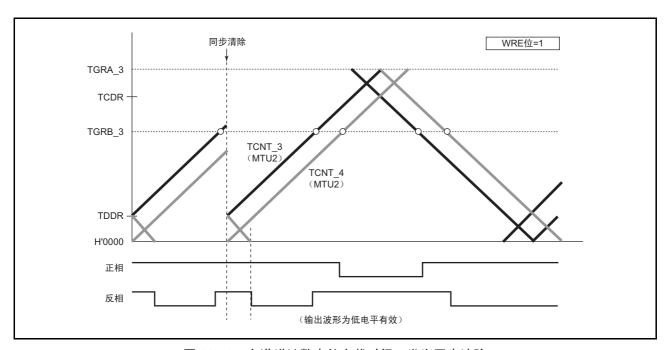

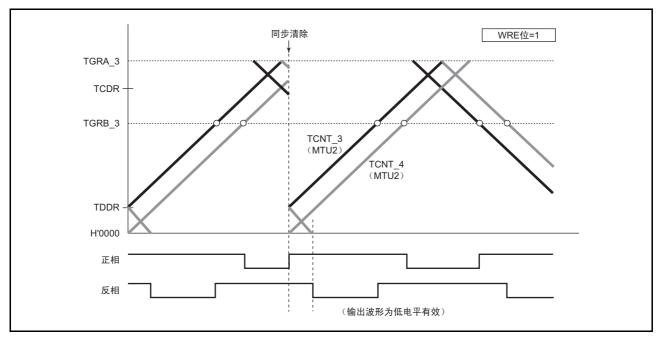

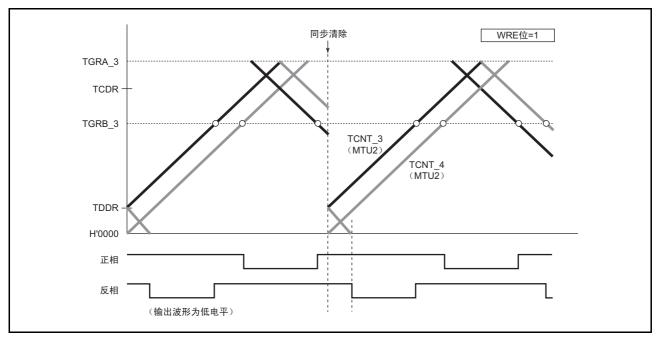

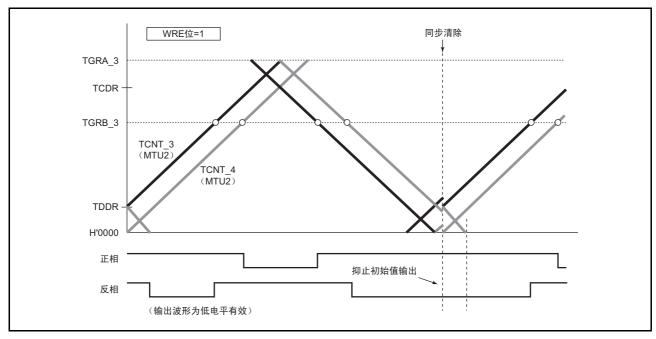

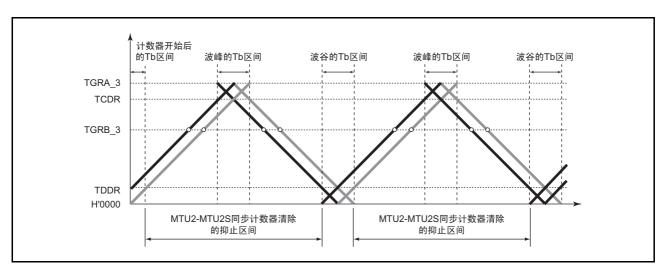

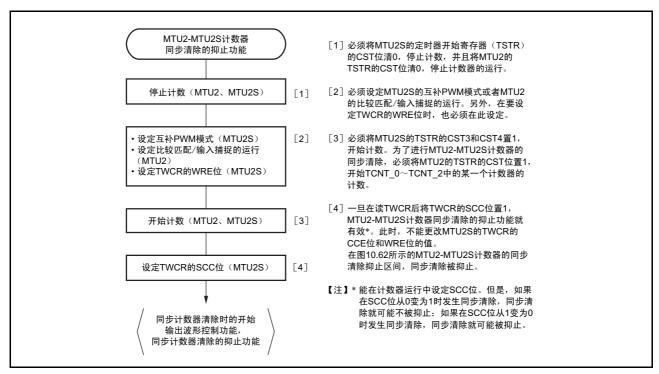

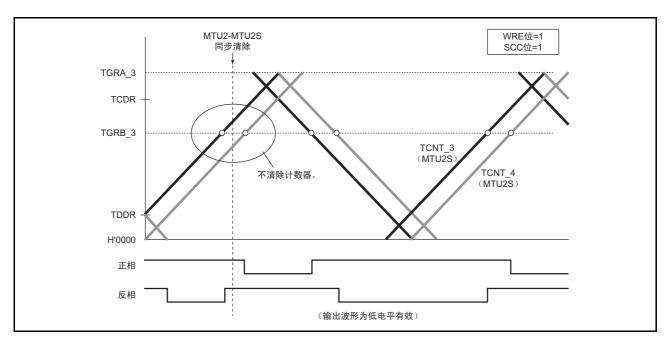

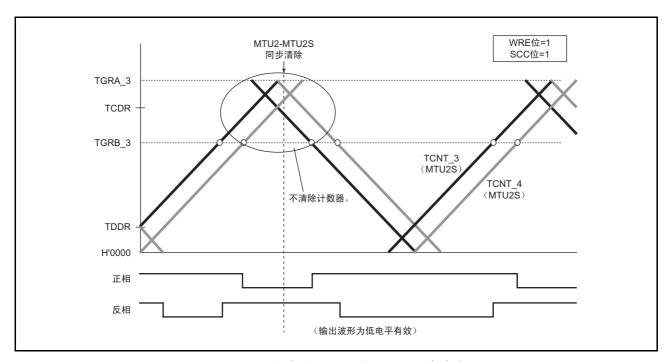

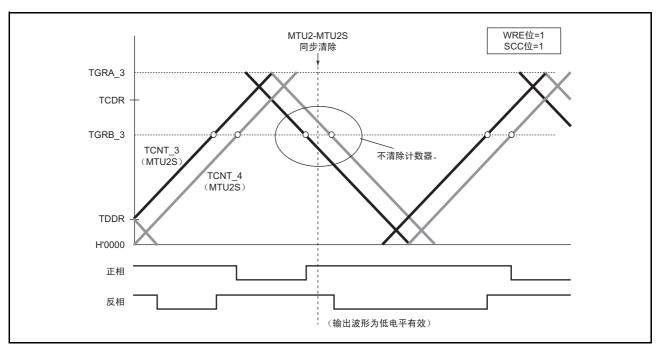

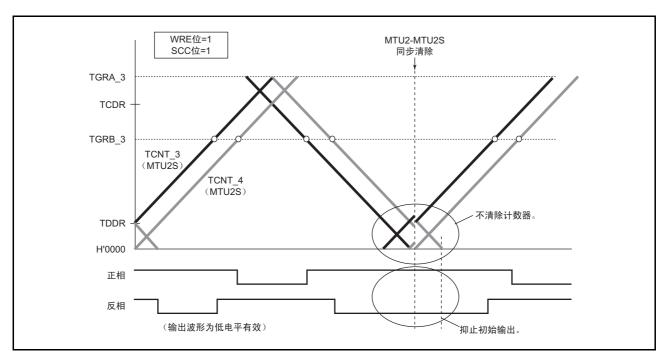

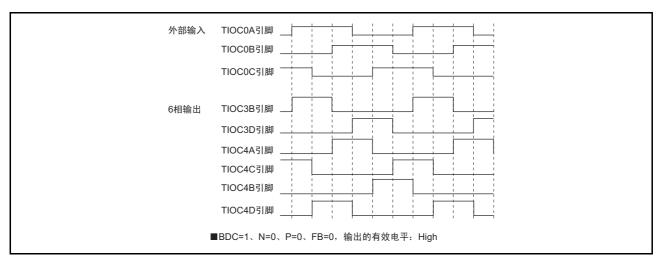

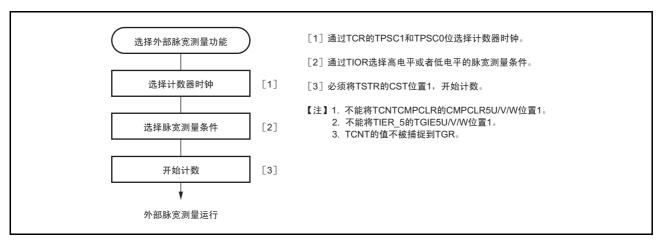

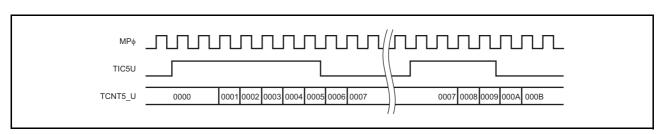

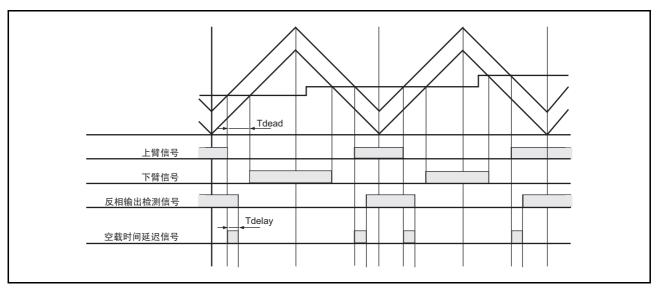

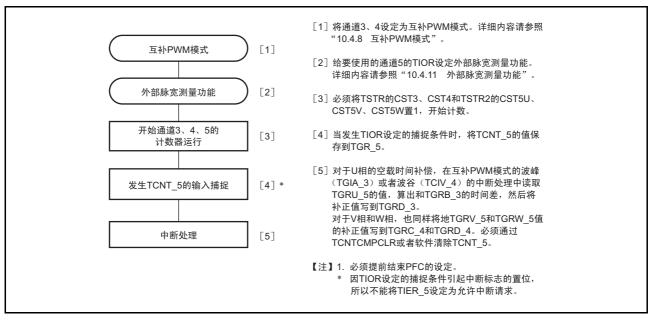

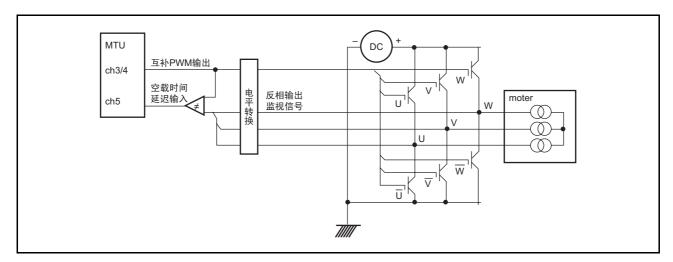

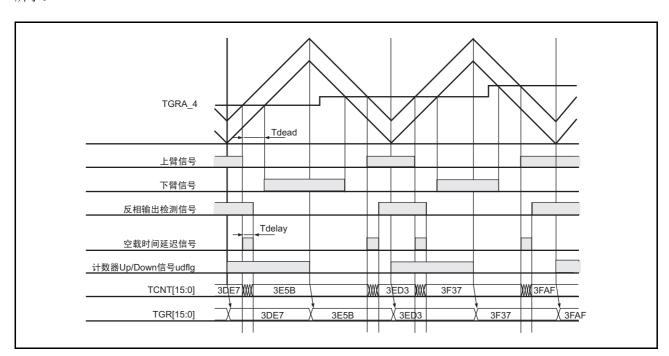

| 10.4.7  | 夏亚问少 PWM 模式<br>互补 PWM 模式                |     |

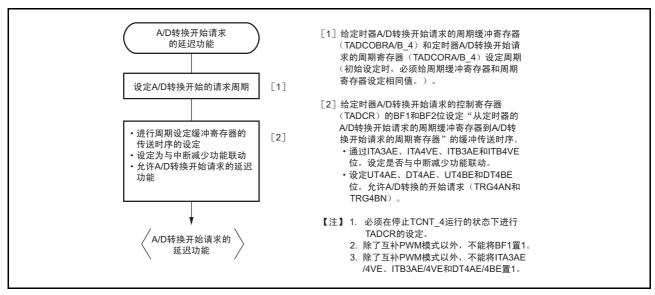

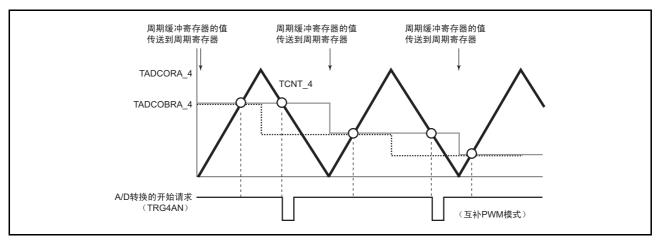

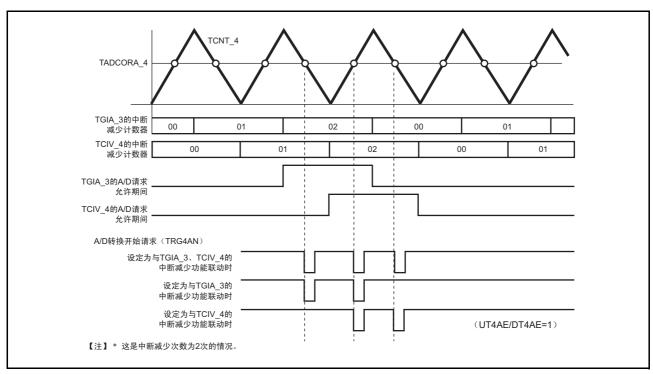

| 10.4.8  | 4/D 转换开始请求的延迟功能                         |     |

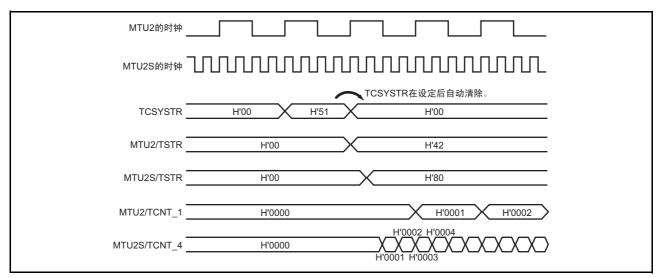

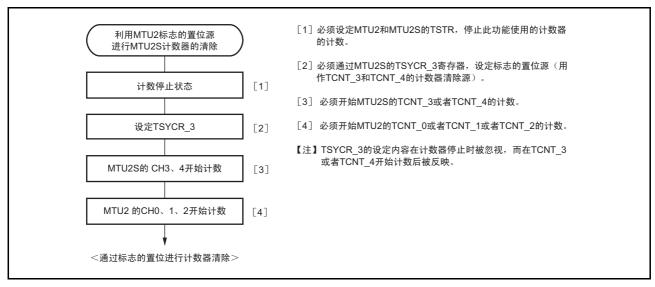

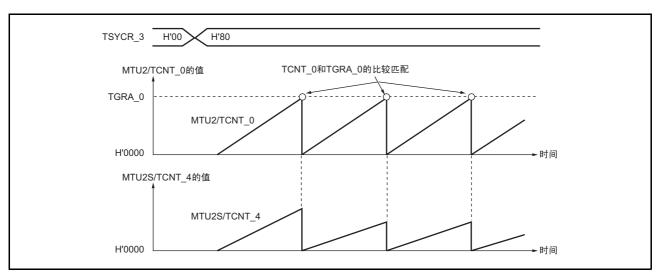

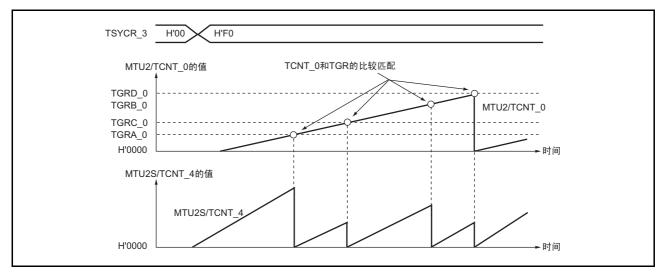

|         | MTU2-MTU2S 的同步运行                        |     |

| 10.4.10 | M1U2-M1U2S 的问少运1]                       |     |

| 10.4.11 | · / · · · · · · · · · · · · · · · · · · |     |

| 10.4.12 | 空载时间的补偿功能                               |     |

| 10.4.13 | 互补 PWM 在 "波峰 / 波谷"的 TCNT 捕捉运行           |     |

|         |                                         |     |

| 10.5.1  | 中断源和优先级                                 |     |

| 10.5.2  | DTC 的启动                                 |     |

| 10.5.3  | A/D 转换器的启动                              |     |

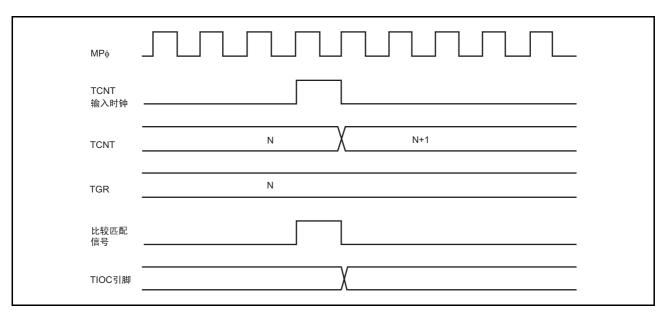

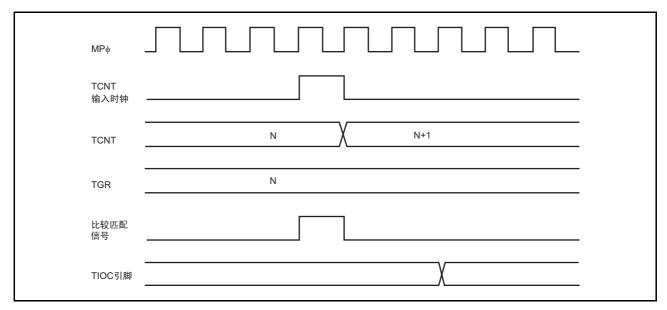

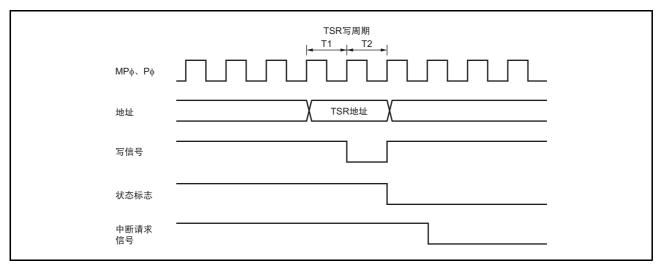

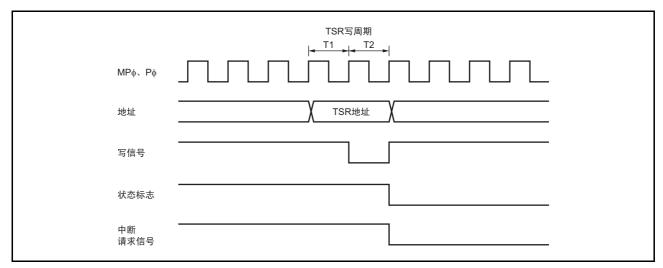

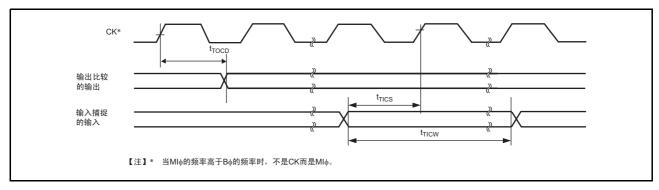

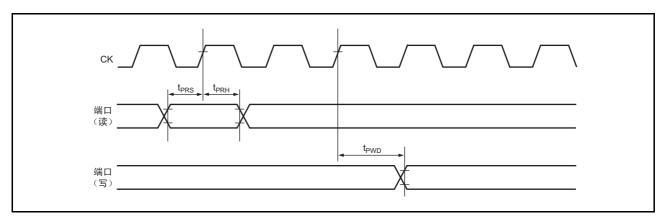

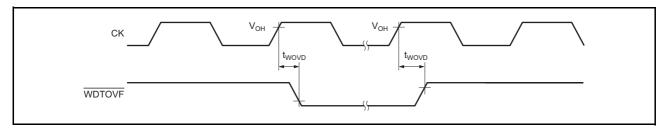

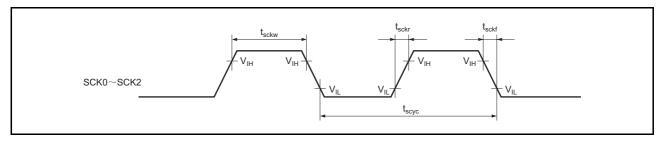

|         | - 时序                                    | 261 |

| 11161   | trong // / trong to the last Life       | 761 |

| 10.6.2  | 中断信号的时序                                 | 267 |

|---------|-----------------------------------------|-----|

|         | 中的注意事项                                  |     |

| 10.7 使用 | 模块待机模式的设定                               |     |

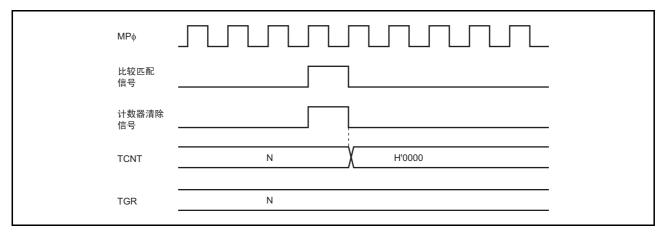

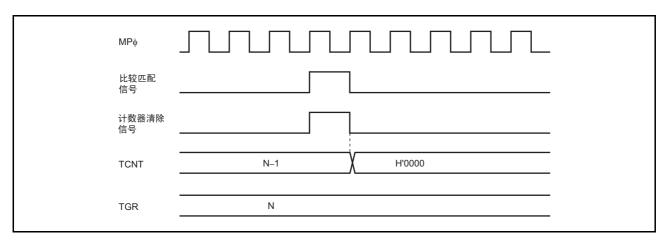

| 101711  | * · · · · · · · · · · · · · · · · · · · |     |

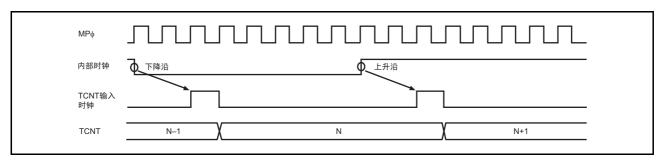

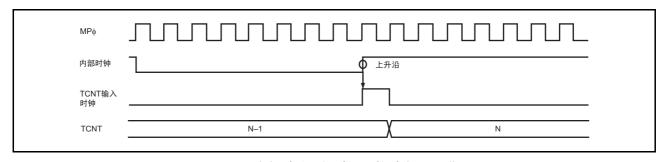

| 10.7.2  | 输入时钟的限制事项                               |     |

| 10.7.3  | 周期设定的注意事项                               |     |

| 10.7.4  | TCNT 的写操作和清除的竞争                         |     |

| 10.7.5  | TCNT 的写操作和递增计数的竞争                       |     |

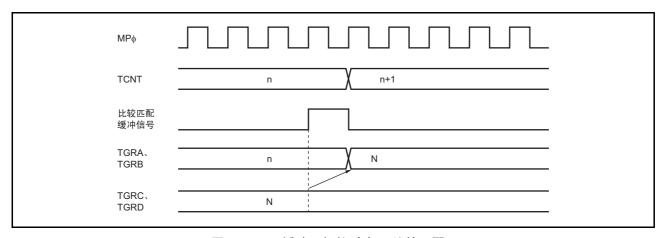

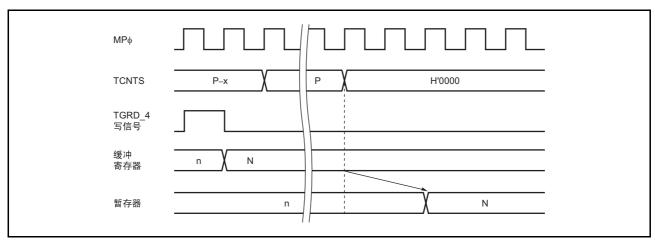

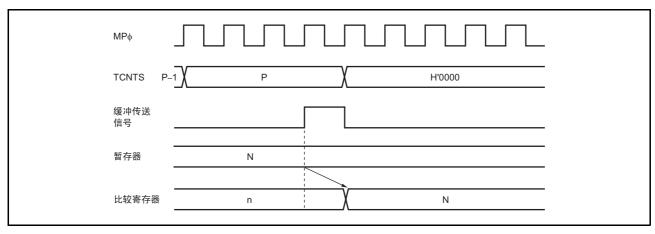

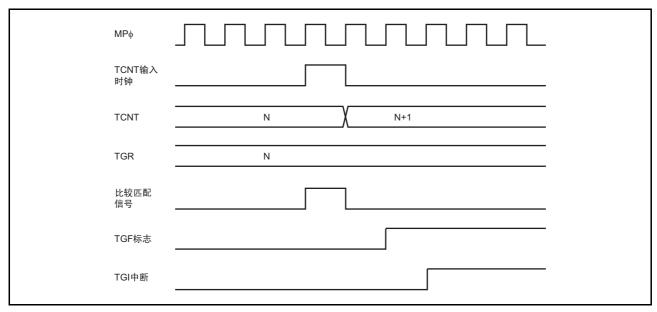

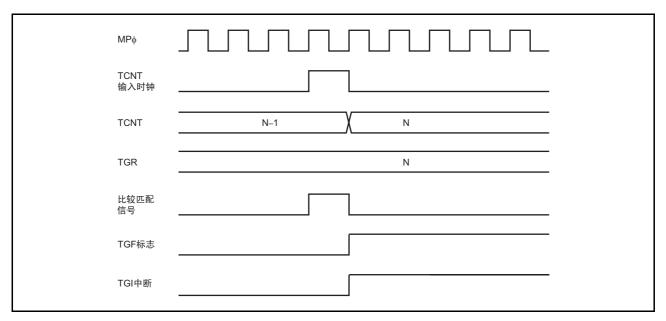

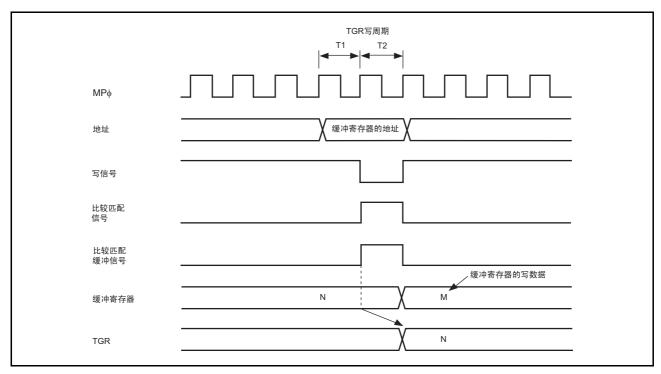

| 10.7.6  | TGR 的写操作和比较匹配的竞争                        |     |

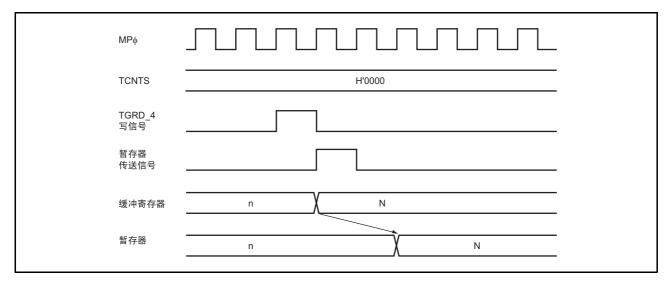

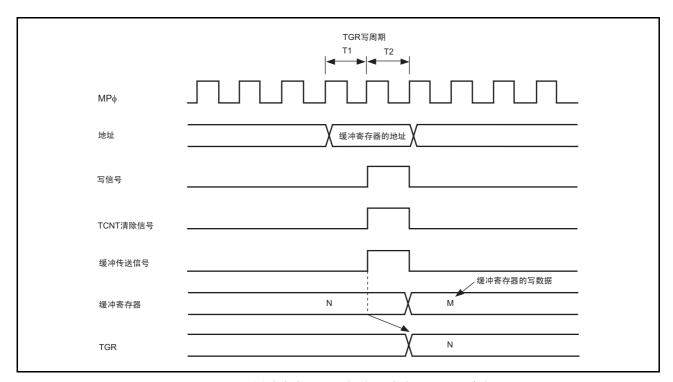

| 10.7.7  | 缓冲寄存器的写操作和比较匹配的竞争                       |     |

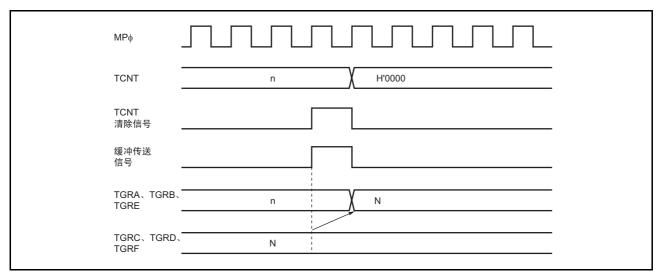

| 10.7.8  | 缓冲寄存器的写操作和清除 TCNT 的竞争                   |     |

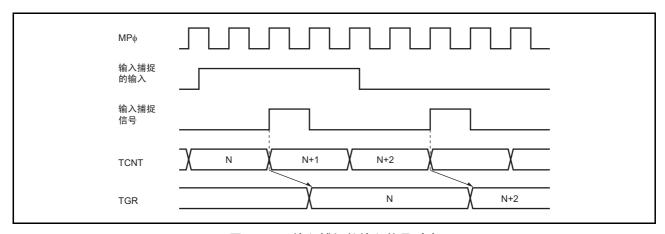

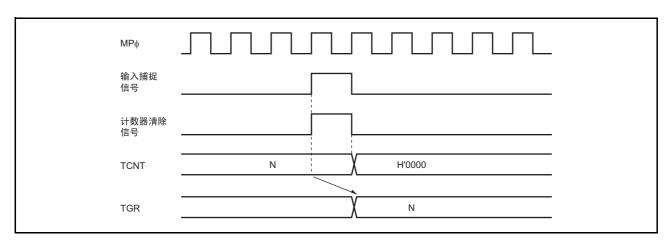

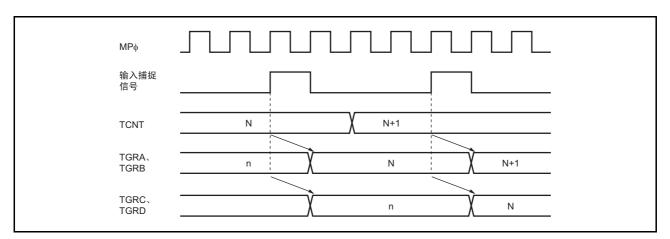

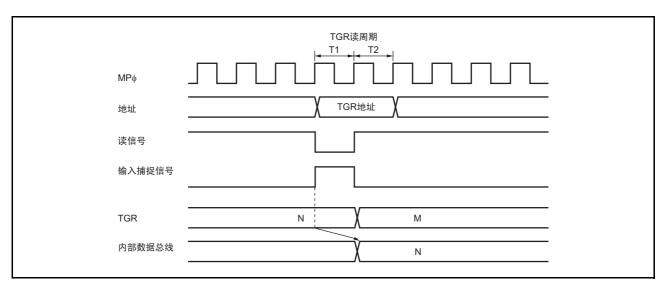

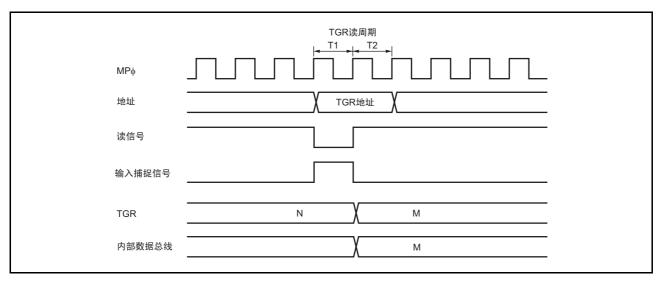

| 10.7.9  | TGR 的读操作和输入捕捉的竞争                        |     |

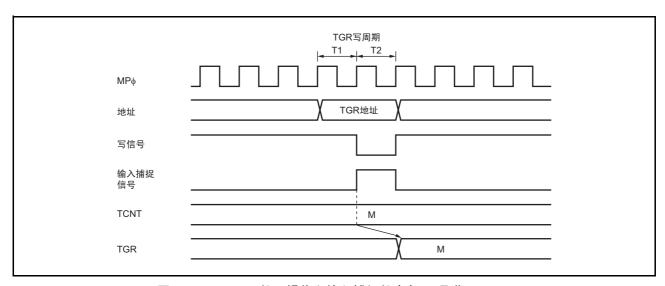

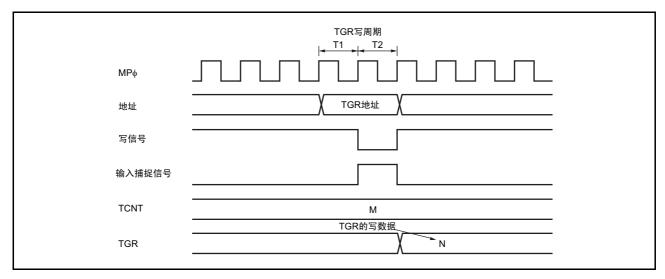

| 10.7.10 | TGR 的写操作和输入捕捉的竞争                        | 275 |

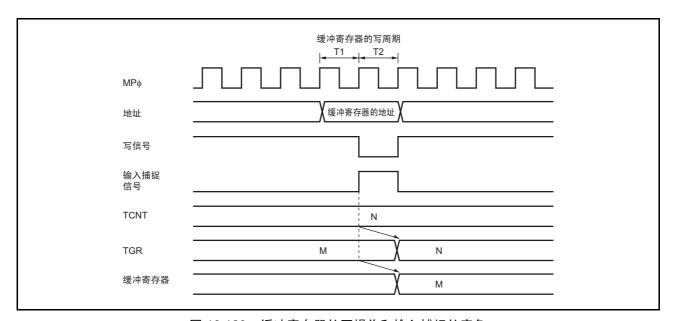

| 10.7.11 | 缓冲寄存器的写操作和输入捕捉的竞争                       | 276 |

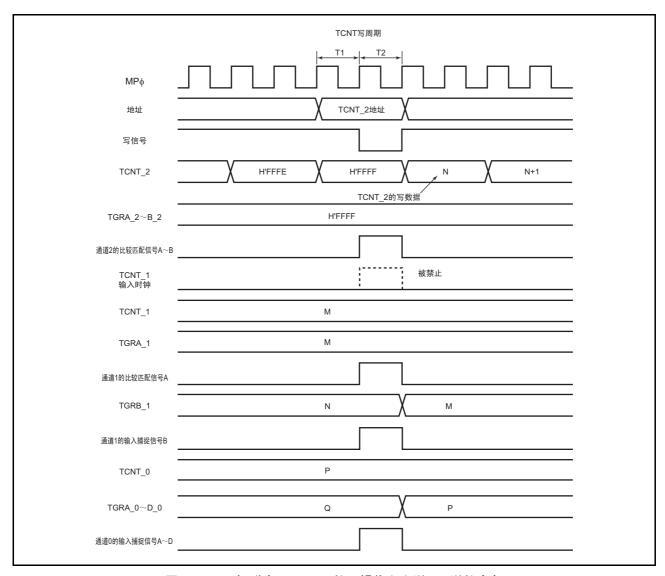

| 10.7.12 | 级联中 TCNT_2 的写操作和上溢 / 下溢的竞争              | 277 |

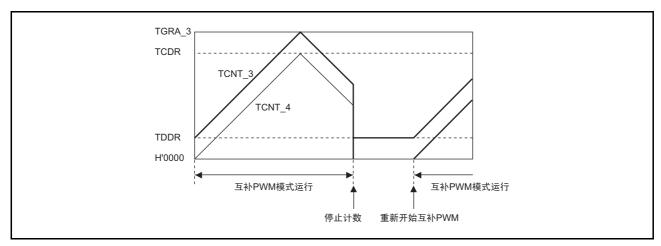

| 10.7.13 | 互补 PWM 模式停止时的计数器值                       | 278 |

| 10.7.14 | 互补 PWM 模式的缓冲运行设定                        | 278 |

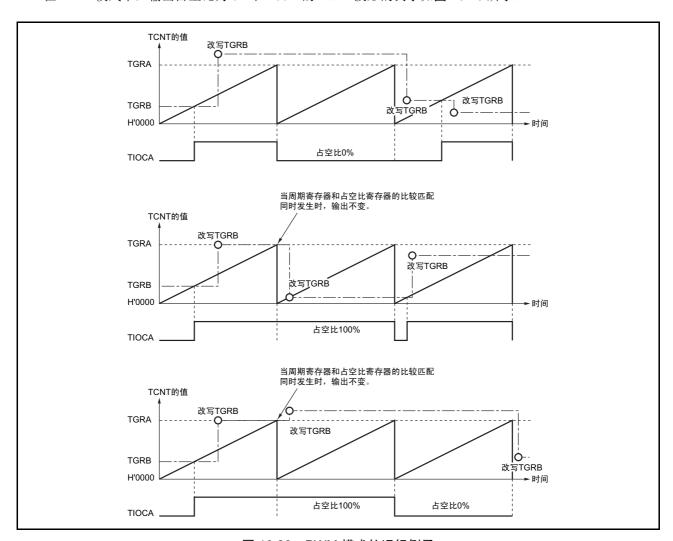

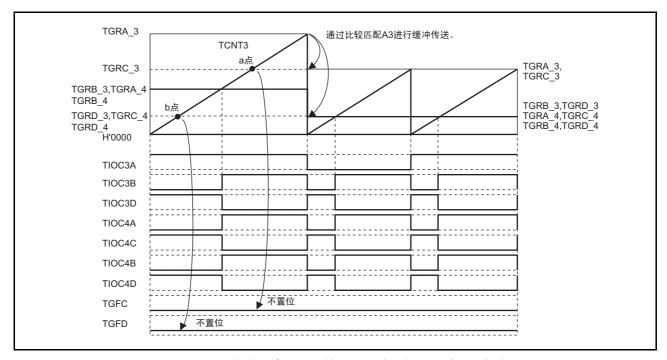

| 10.7.15 | 复位同步 PWM 模式的缓冲运行和比较匹配标志                 | 278 |

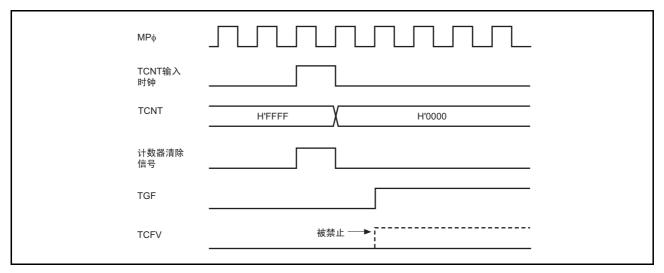

| 10.7.16 | 复位同步 PWM 模式的上溢标志                        |     |

| 10.7.17 | 上溢/下溢和计数器清除的竞争                          |     |

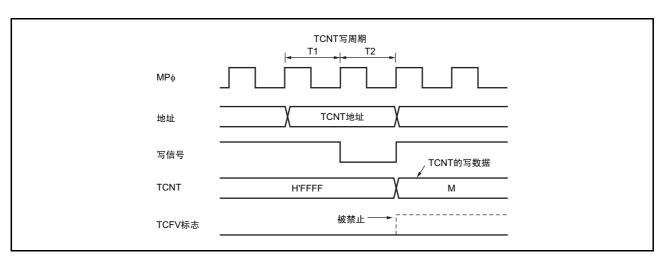

| 10.7.18 | TCNT 的写操作和上溢 / 下溢的竞争                    |     |

| 10.7.19 | 从正常模式或者 PWM 模式 1 转移到复位同步 PWM 模式时的注意事项   |     |

| 10.7.19 | 互补 PWM 模式或者复位同步 PWM 模式的输出电平             |     |

| 10.7.20 | 模块待机时的中断模块待机时的中断                        |     |

|         | 级联中 TCNT_1 和 TCNT_2 的同时输入捕捉             |     |

| 10.7.22 |                                         |     |

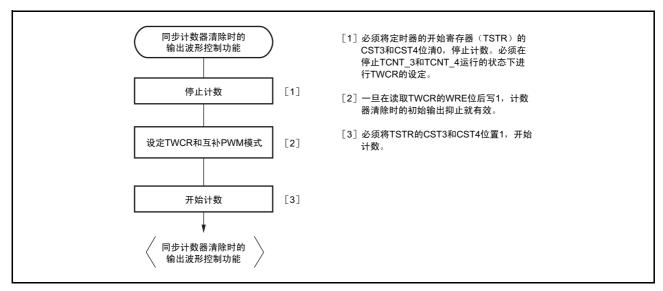

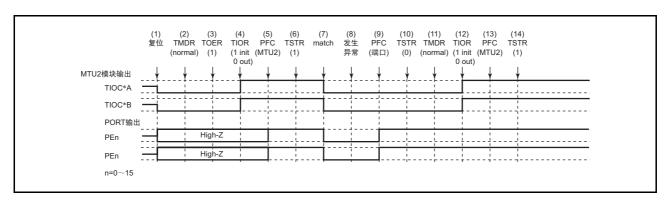

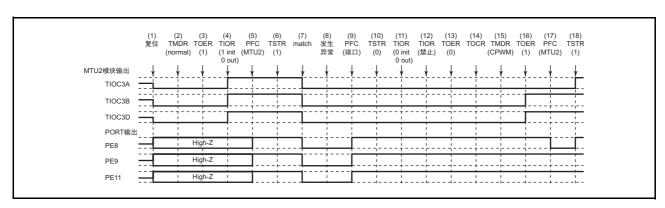

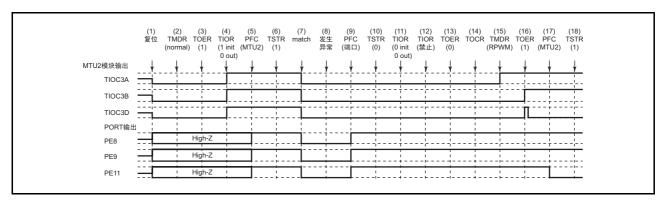

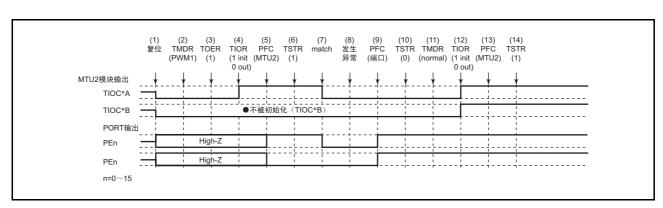

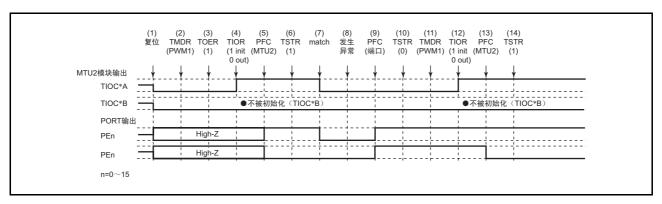

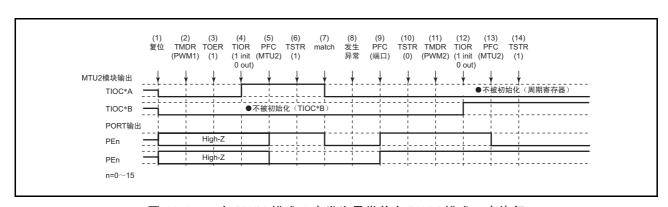

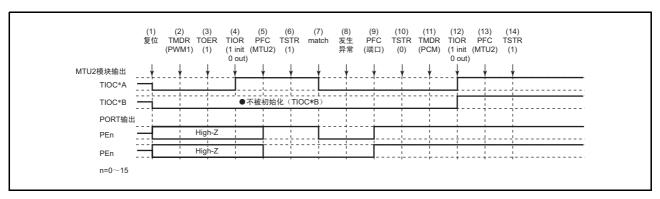

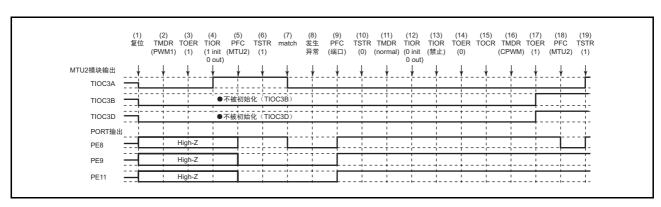

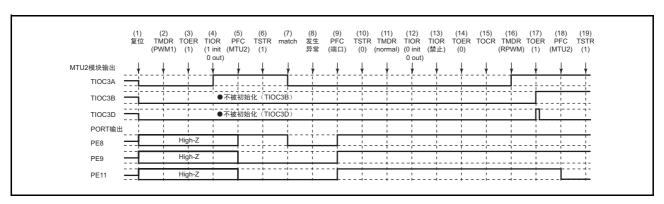

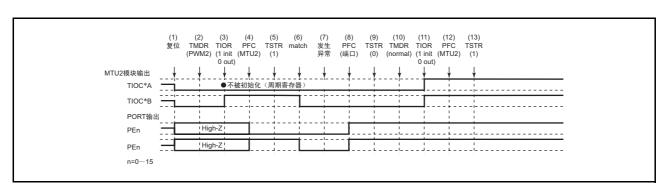

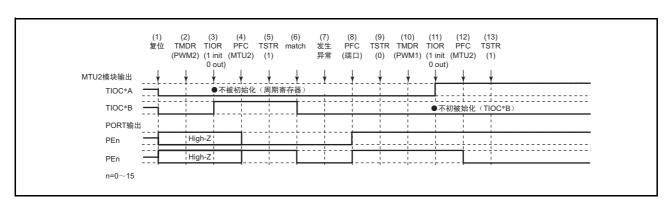

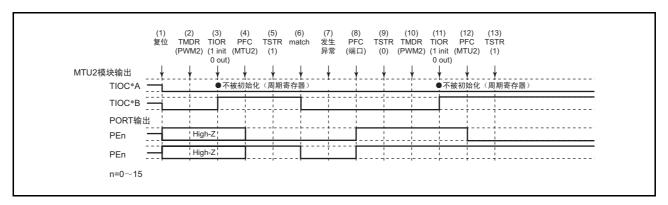

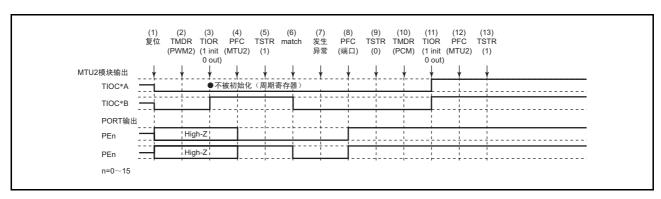

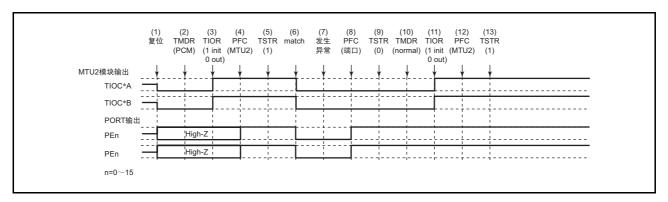

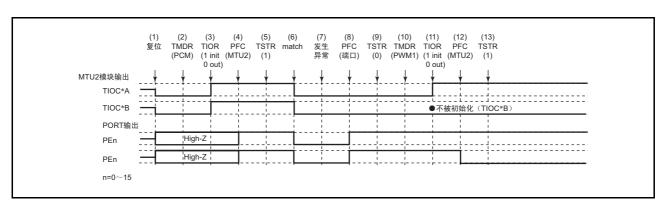

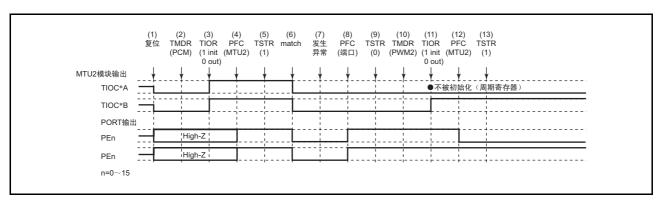

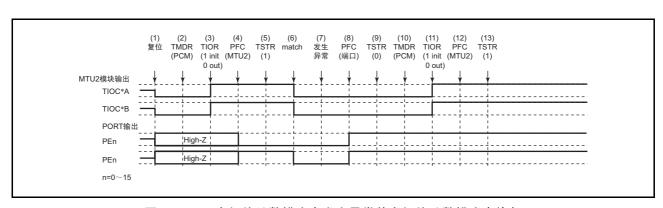

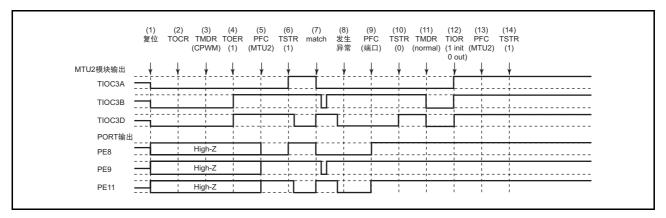

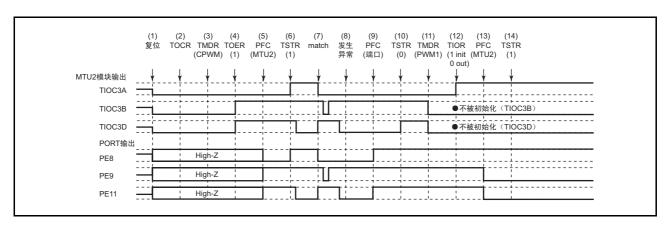

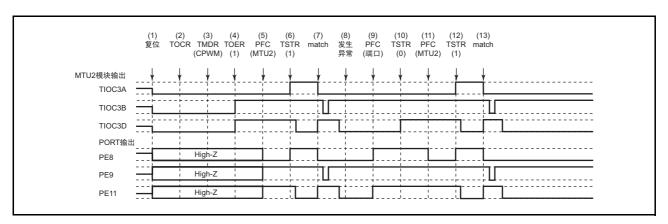

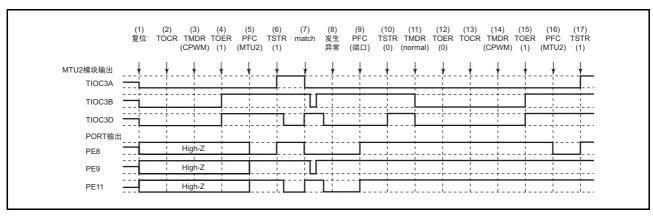

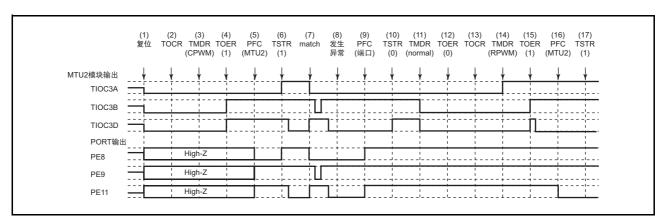

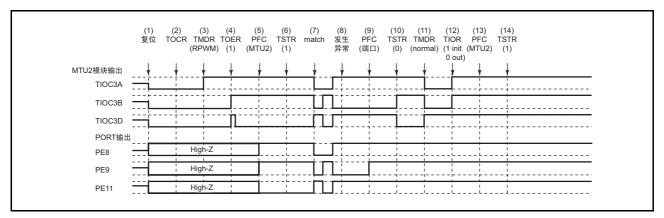

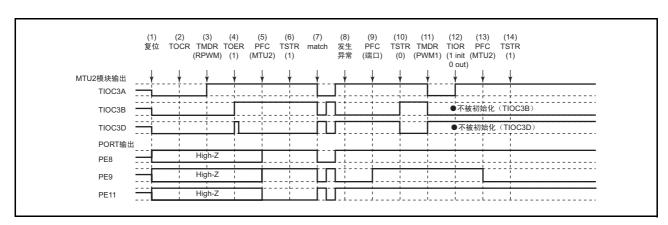

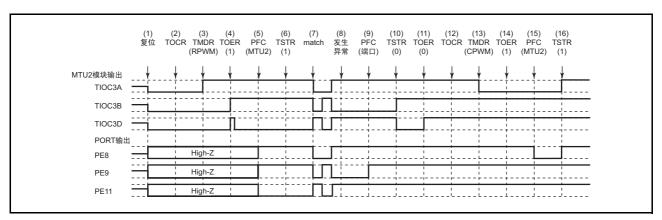

|         | 2 输出引脚的初始化方法                            |     |

| 10.8.1  | 运行模式                                    |     |

| 10.8.2  | 复位开始时的运行                                |     |

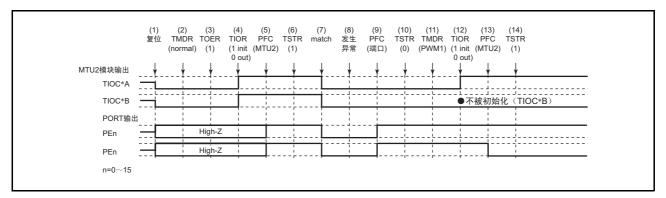

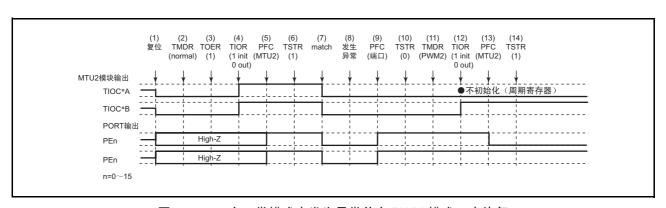

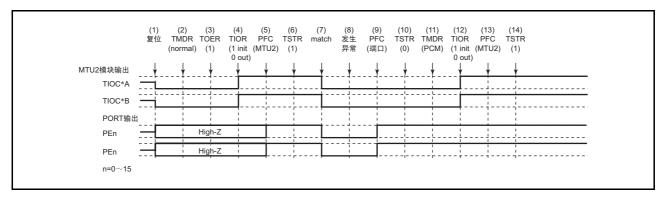

| 10.8.3  | 因运行中的异常等而重新设定时的运行                       |     |

| 10.8.4  | 因运行中的异常等而初始化引脚的步骤和模式转移的概要               | 282 |

| 第 11 章  | 多功能定时器脉冲单元 2S (MTU2S)                   | 300 |

|         | タ 37 Ht 2 C T                           |     |

|         |                                         |     |

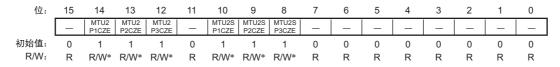

| 11.2 寄存 | 器说明                                     | 302 |

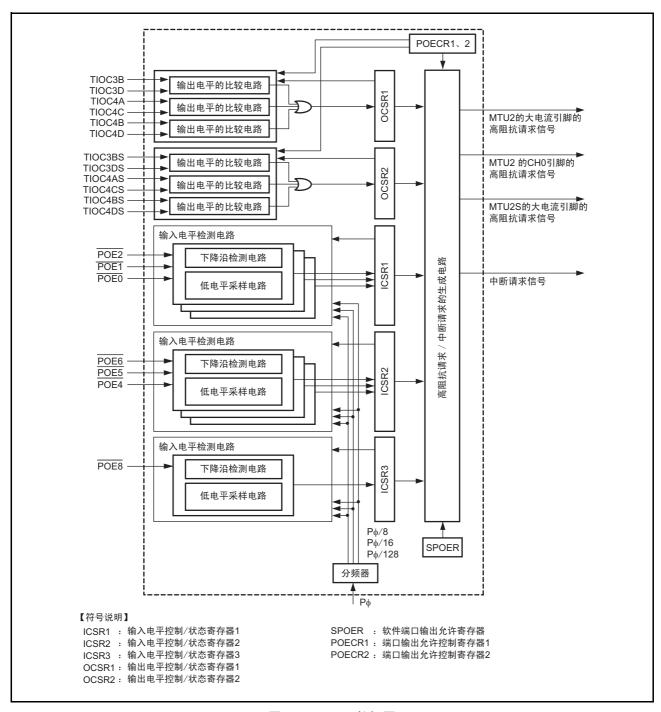

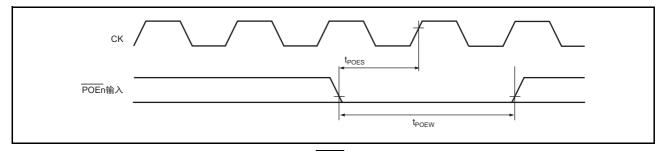

| 第 12 章  | 端口输出的允许 (POE)                           | 304 |

|         |                                         |     |

|         | / 输出引脚                                  |     |

| ****    | 7 捆 凸 寸 / I/I/I                         |     |

|         | 爺吃呀                                     |     |

| 12.3.1  |                                         |     |

| 12.3.2  | 输出电平控制 / 状态寄存器 1 (OCSR1)                |     |

| 12.3.3  | 输入电平控制 / 状态寄存器 2 (ICSR2)                |     |

| 12.3.4  | 输出电平控制 / 状态寄存器 2 (OCSR2)                |     |

| 12.3.5  | 输入电平控制 / 状态寄存器 3 (ICSR3)                |     |

| 12.3.6  | 软件端口的输出允许寄存器(SPOER)                     |     |

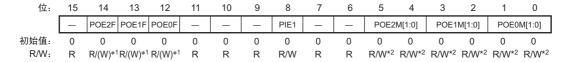

| 12.3.7  | 端口输出的允许控制寄存器 1 (POECR1)                 |     |

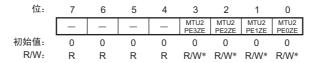

| 12.3.8  | 端口的输出的允许控制寄存器 2 (POECR2)                |     |

| 12.4 运行 | 说明                                      | 317 |

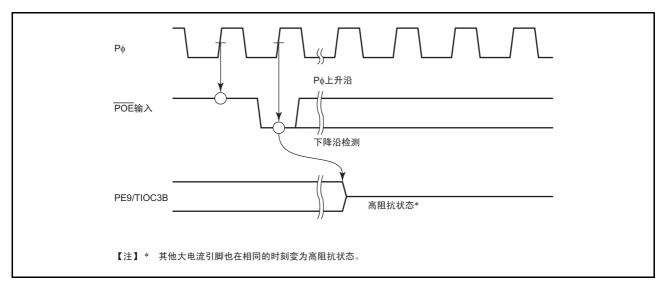

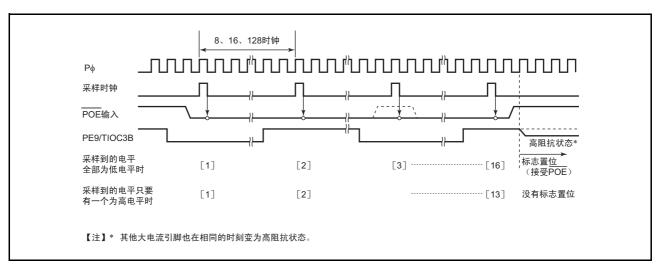

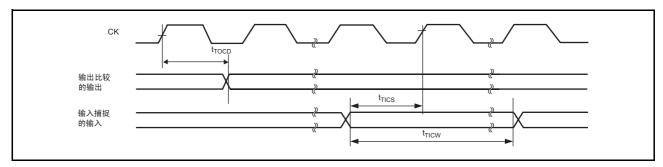

| 12.4.1  | 输入电平的检测                                 | 318 |

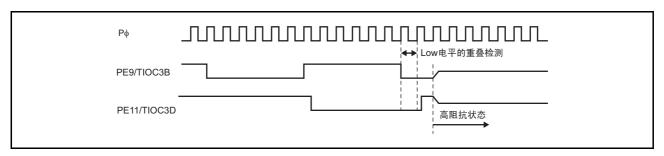

| 12.4.2  | 输出电平的比较                                 | 319 |

| 12.4.3  | 高阻抗状态的解除                                | 319 |

| 12.5 中断 |                                         | 319 |

|         | 时的注意事项                                  |     |

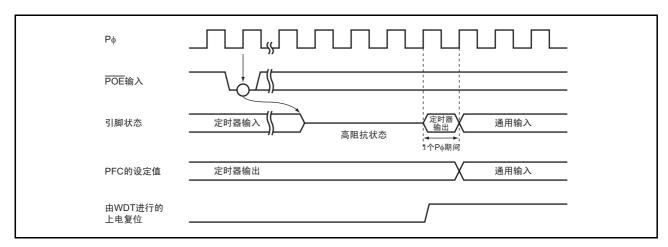

|         | 从看门狗定时器产生上电复位时的引脚状态                     |     |

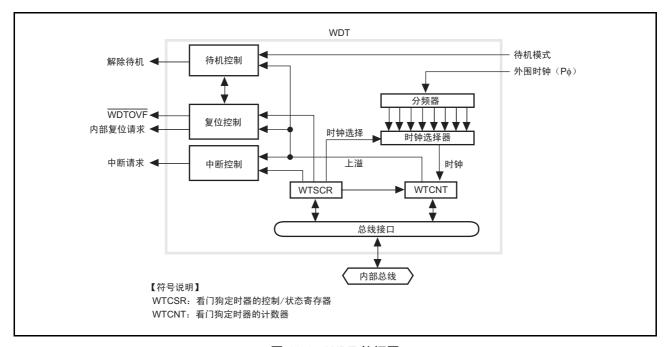

| 第 13 章  | 看门狗定时器 (WDT)              | 321 |

|---------|---------------------------|-----|

| 13.1 特  | 点                         | 321 |

| 13.2 输  | :入/输出引脚                   | 322 |

| 13.3 寄  | 存器说明                      |     |

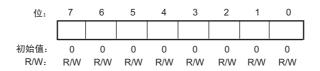

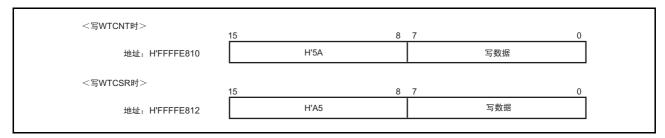

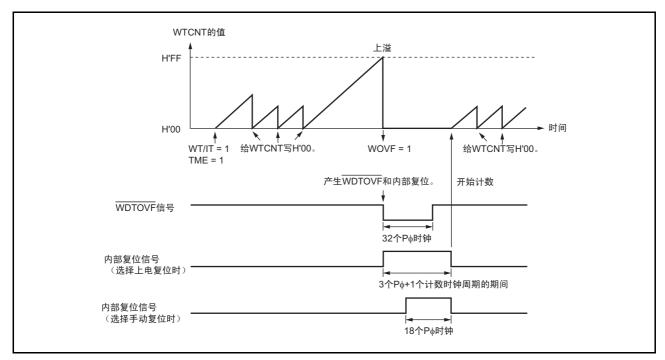

| 13.3.1  | 看门狗定时器的计数器 (WTCNT)        | 322 |

| 13.3.2  | 看门狗定时器的控制 / 状态寄存器 (WTCSR) | 322 |

| 13.3.3  | 寄存器存取时的注意事项               | 324 |

| 13.4 运  | 行说明                       |     |

| 13.4.1  | 软件待机模式的解除步骤               | 324 |

| 13.4.2  | 看门狗定时器模式的用法               | 324 |

| 13.4.3  | 间隔定时器模式的用法                | 325 |

| 13.5 使  | 用时的注意事项                   |     |

| 13.5.1  | WTCNT 的设定值                |     |

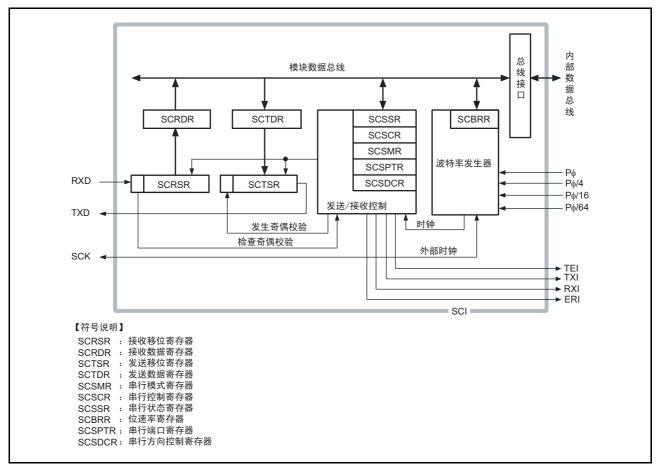

| 第 14 章  | 串行通信接口 (SCI)              | 326 |

| 14.1 特  | 点                         | 326 |

| 14.2 输  | :入/输出引脚                   | 327 |

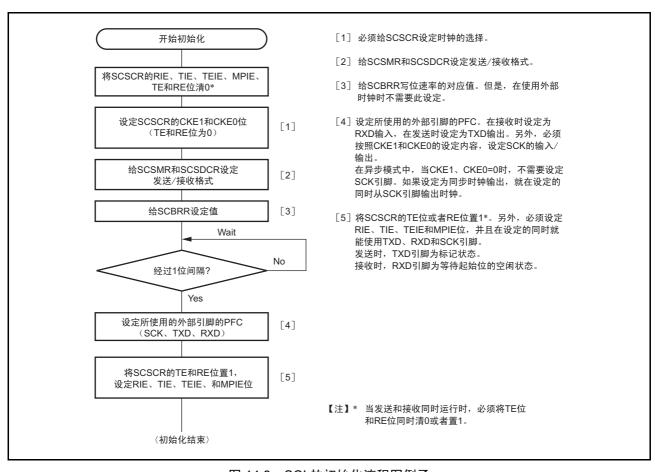

| 14.3 寄  | 存器说明                      | 328 |

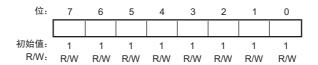

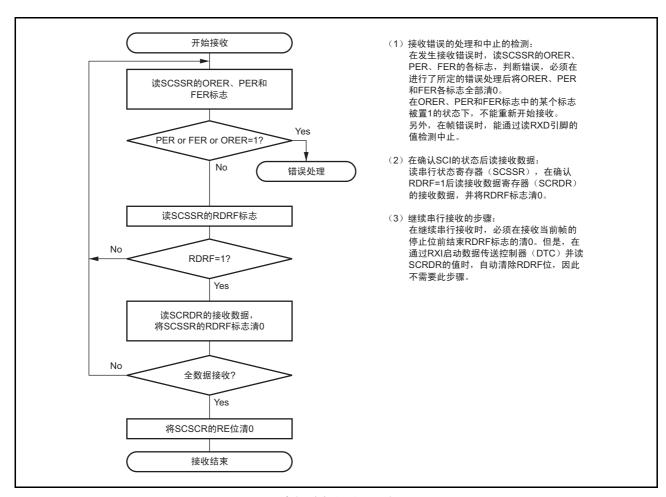

| 14.3.1  | 接收移位寄存器 (SCRSR)           | 328 |

| 14.3.2  | 接收数据寄存器 (SCRDR)           | 329 |

| 14.3.3  | 发送移位寄存器 (SCTSR)           | 329 |

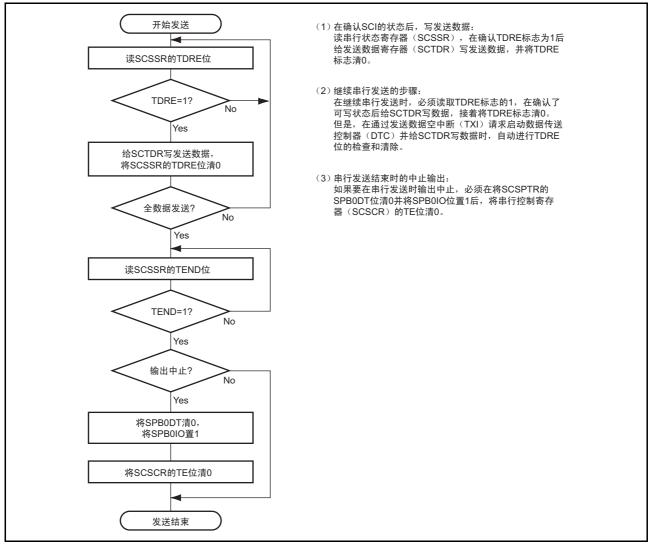

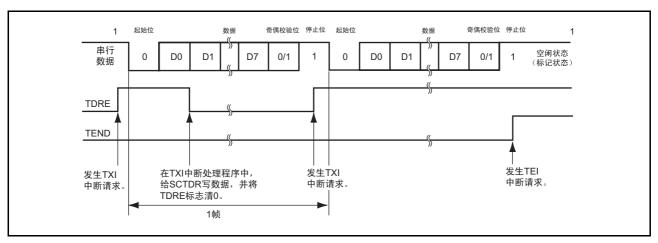

| 14.3.4  | 发送数据寄存器 (SCTDR)           | 329 |

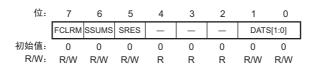

| 14.3.5  | 串行模式寄存器 (SCSMR)           | 329 |

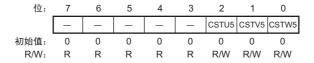

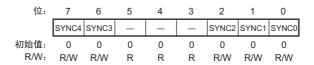

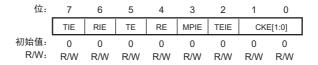

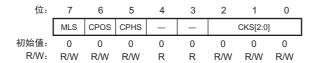

| 14.3.6  | 串行控制寄存器 (SCSCR)           | 331 |

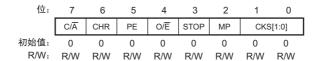

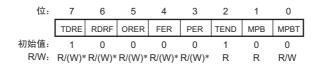

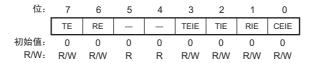

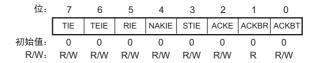

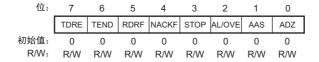

| 14.3.7  | 串行状态寄存器 (SCSSR)           | 333 |

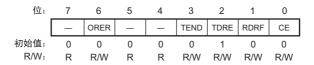

| 14.3.8  | 串行端口寄存器 (SCSPTR)          | 335 |

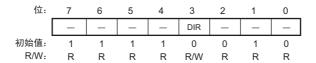

| 14.3.9  | 串行方向控制寄存器 (SCSDCR)        | 336 |

| 14.3.10 | ) 位速率寄存器(SCBRR)           | 337 |

| 14.4 运  | 行说明                       |     |

| 14.4.1  | 概要                        | 343 |

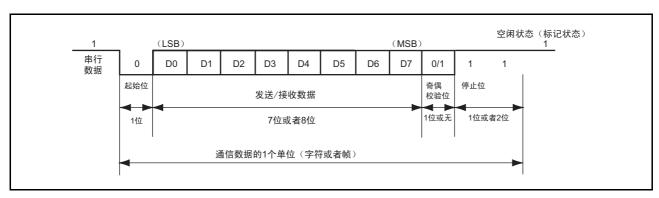

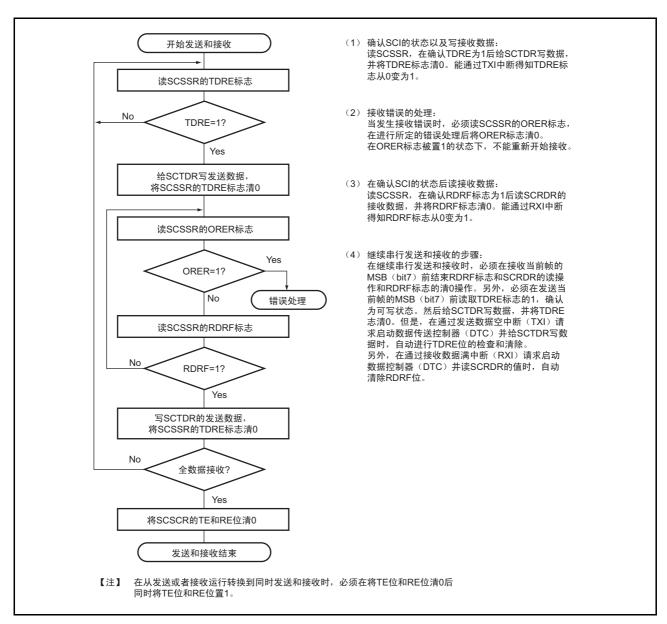

| 14.4.2  | 异步模式的运行                   |     |

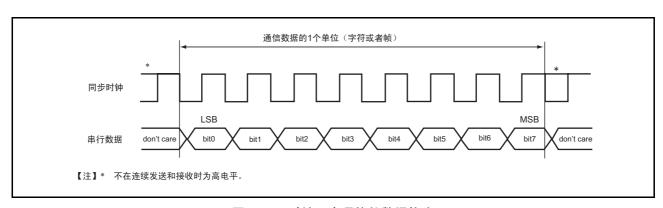

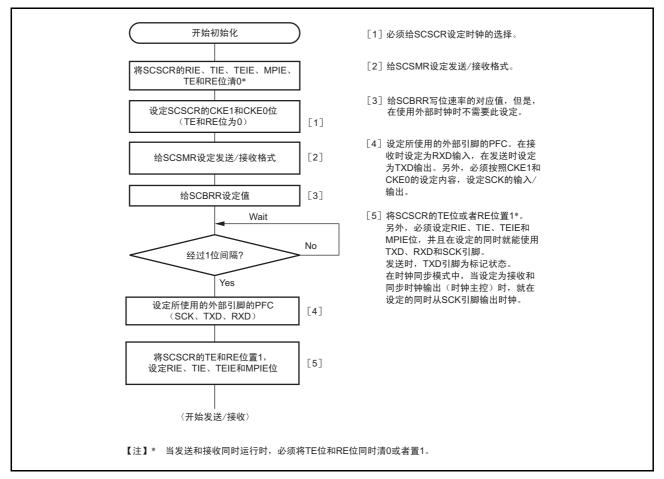

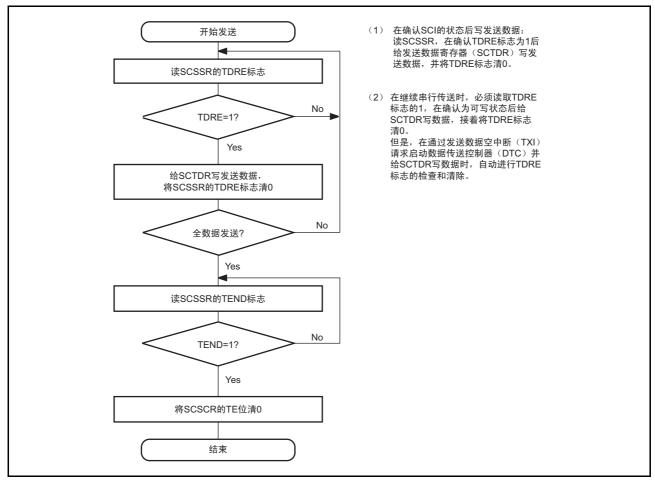

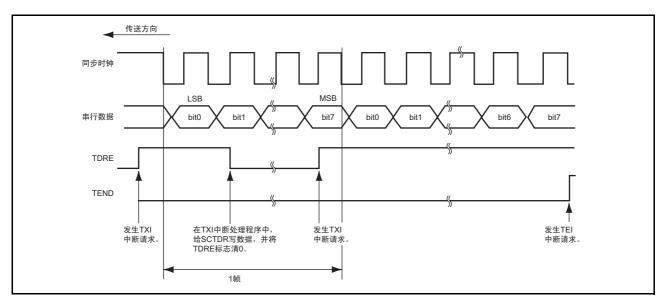

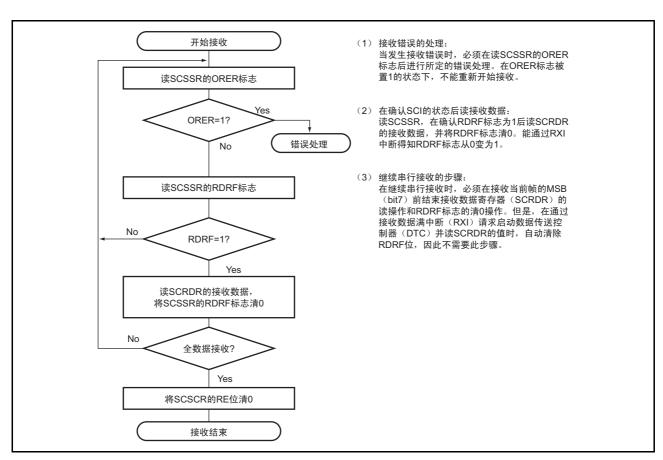

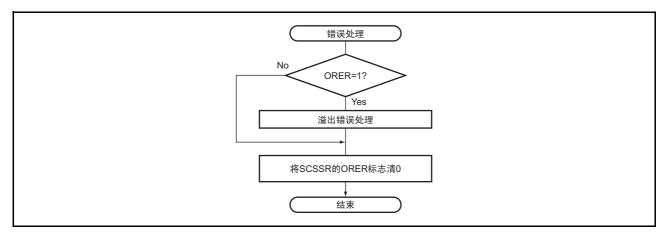

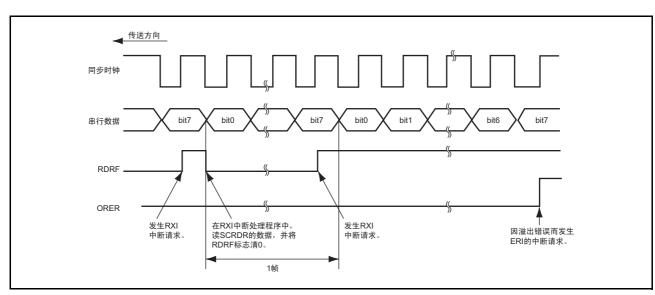

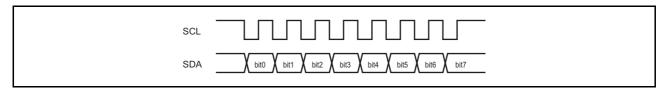

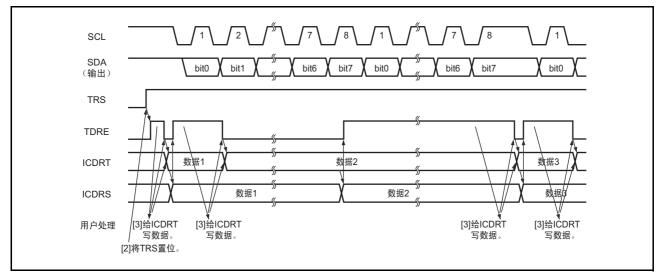

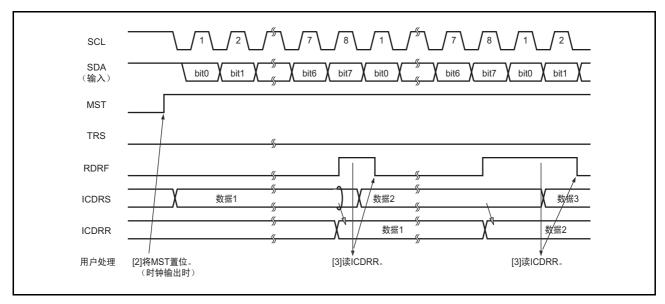

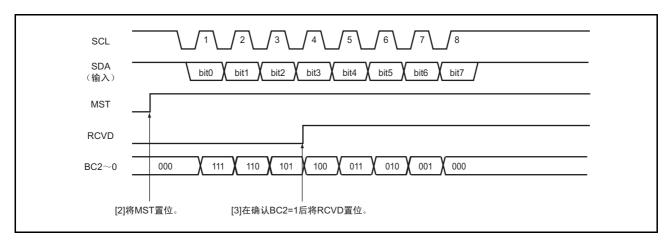

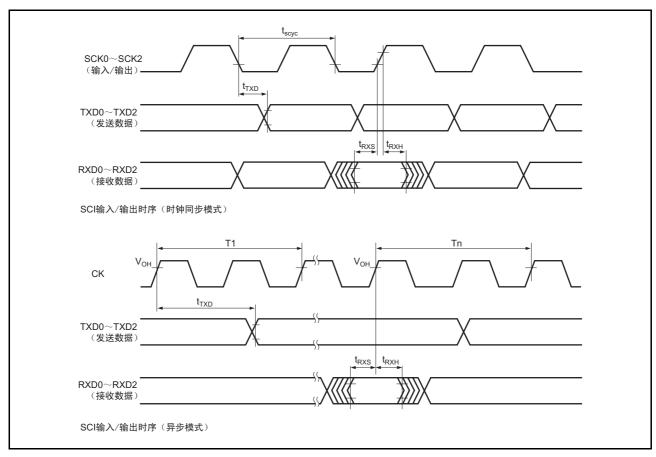

| 14.4.3  | 时钟同步模式的运行                 |     |

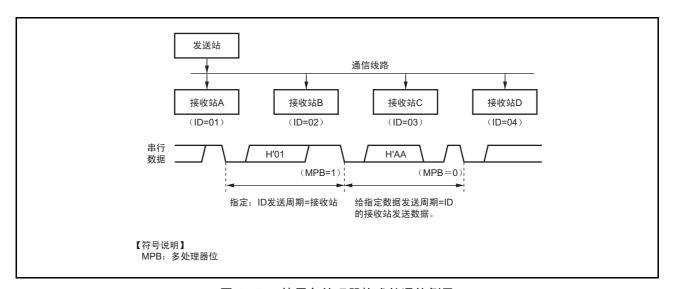

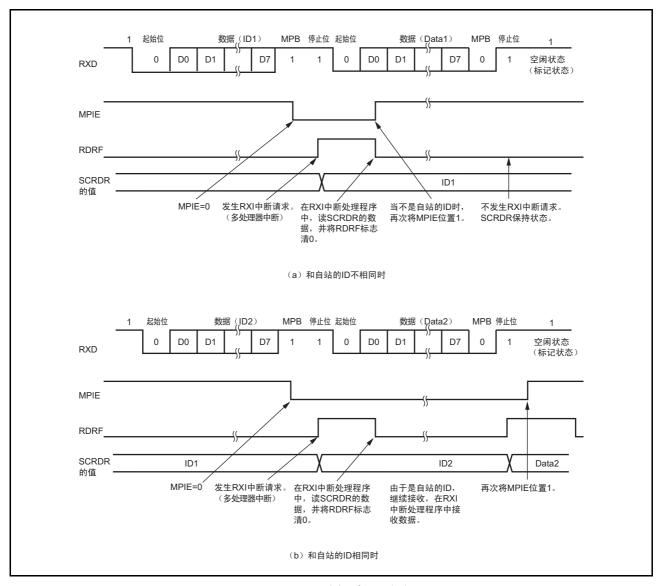

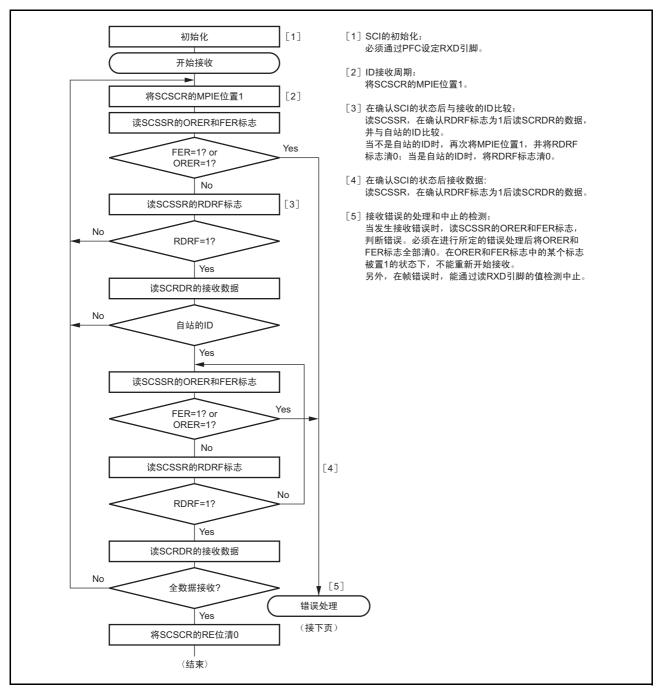

| 14.4.4  | 多处理器通信功能                  |     |

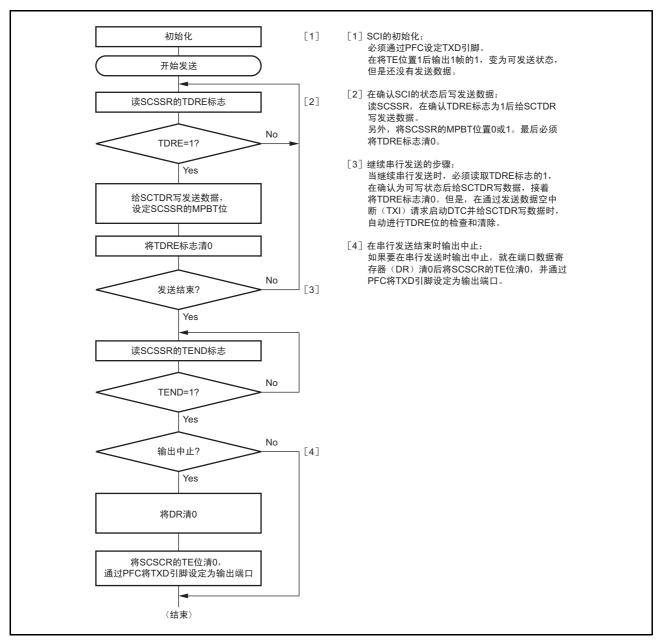

| 14.4.5  | 多处理器串行数据的发送               |     |

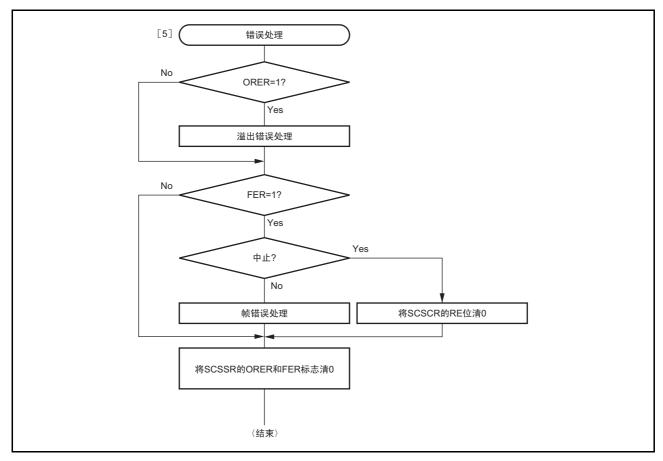

| 14.4.6  | 少人生ய中自然和自我化               |     |

|         | CI 的中断源和 DTC              |     |

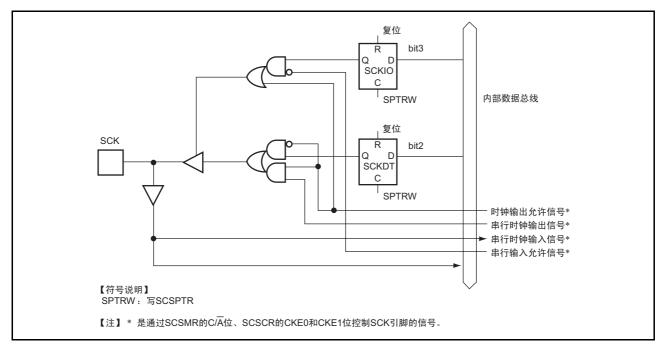

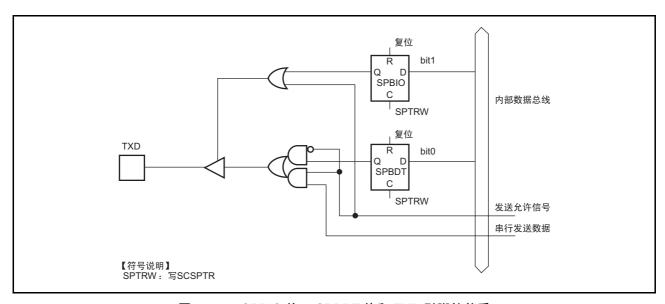

|         | 行端口寄存器(SCSPTR)和 SCI 引脚的关系 |     |

|         | 用时的注意事项                   |     |

| 14.7.1  | 有关 SCTDR 的写操作和 TDRE 标志的关系 |     |

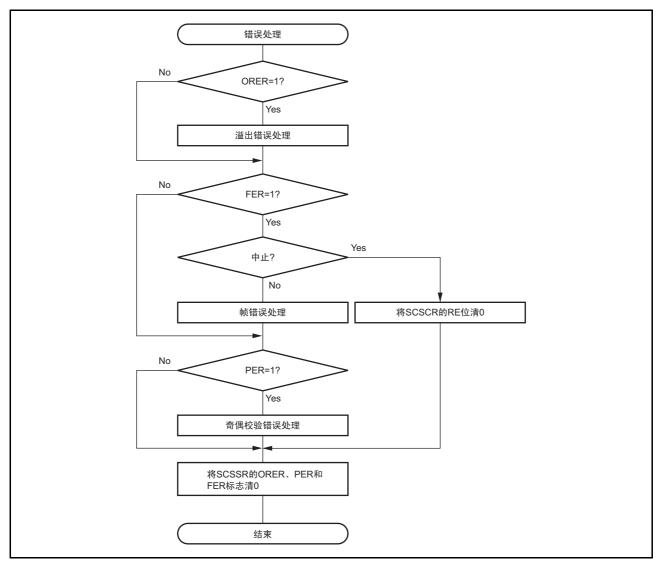

| 14.7.2  | 有关同时发生多个接收错误时的运行          |     |

| 14.7.3  | 中止的检测和处理                  |     |

| 14.7.4  | 中止的发送                     |     |

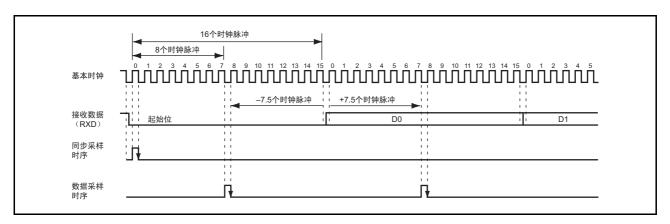

| 14.7.5  | 异步模式的接收数据采样时序和接收容限        |     |

| 14.7.6  | DTC 使用时的注意事项              |     |

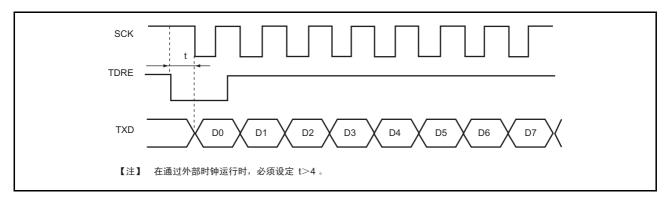

| 14.7.7  | 时钟同步外部时钟模式的注意事项           |     |

| 14.7.8  | 模块待机模式的设定                 | 365 |

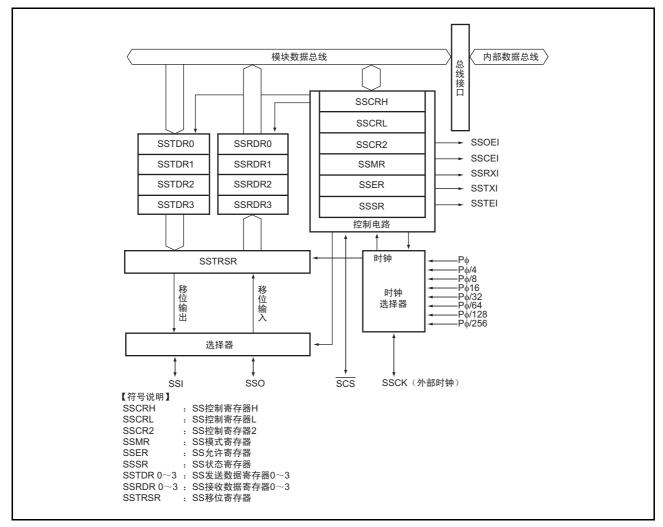

| 第 15 章  | 同步串行通信单元 (SSU)            |     |

|         | ·点                        |     |

|         | :入/输出引脚                   |     |

| 15.3 寄  | 存器说明                      |     |

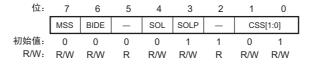

| 15.3.1  | SS 控制寄存器 H (SSCRH)        |     |

| 15 3 2  | SS 控制寄存器 L (SSCRL)        | 369 |

| 15.3.3   | SS 模式寄存器 (SSMR)                             | 370 |

|----------|---------------------------------------------|-----|

| 15.3.4   | SS 允许寄存器 (SSER)                             | 371 |

| 15.3.5   | SS 状态寄存器 (SSSR)                             | 371 |

| 15.3.6   | SS 控制寄存器 2 (SSCR2)                          | 373 |

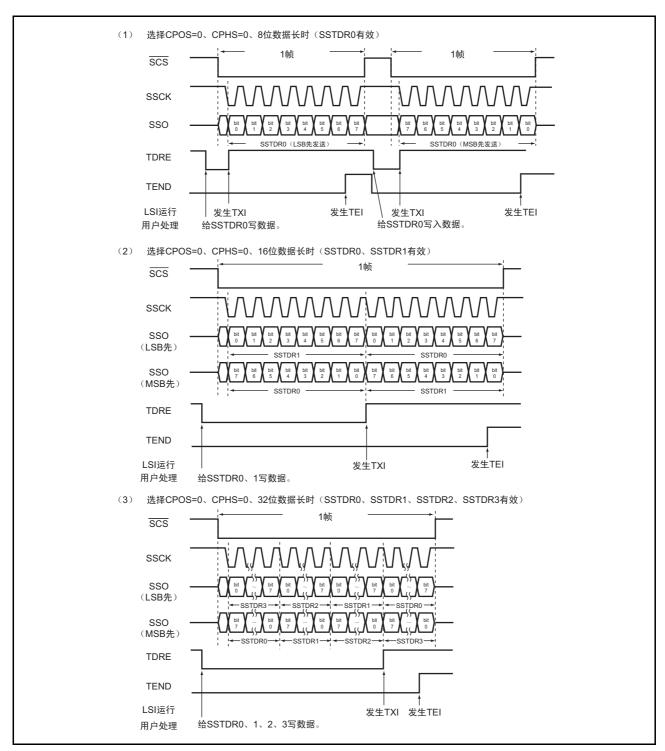

| 15.3.7   | SS 传送数据寄存器 0 ~ 3 (SSTDR0 ~ SSTDR3)          | 373 |

| 15.3.8   | SS 接收数据寄存器 0~3 (SSRDR0~SSRDR3)              | 374 |

| 15.3.9   | SS 移位寄存器 (SSTRSR)                           | 375 |

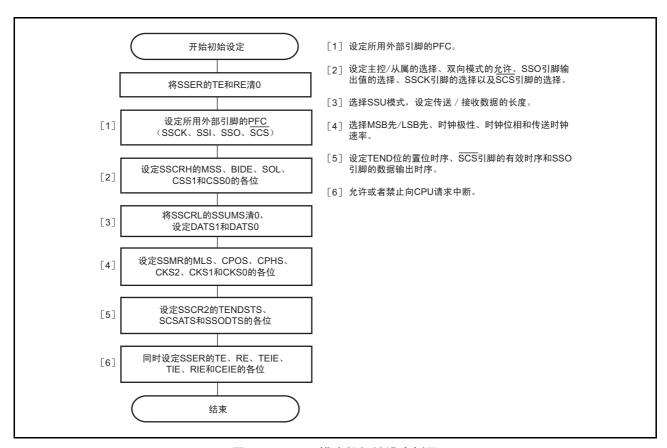

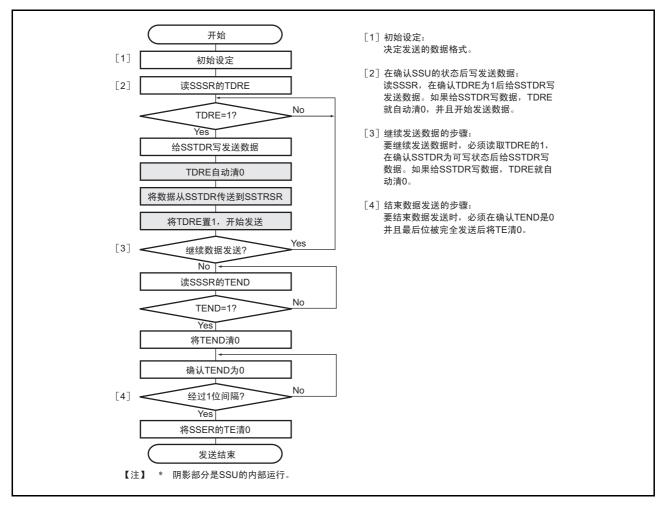

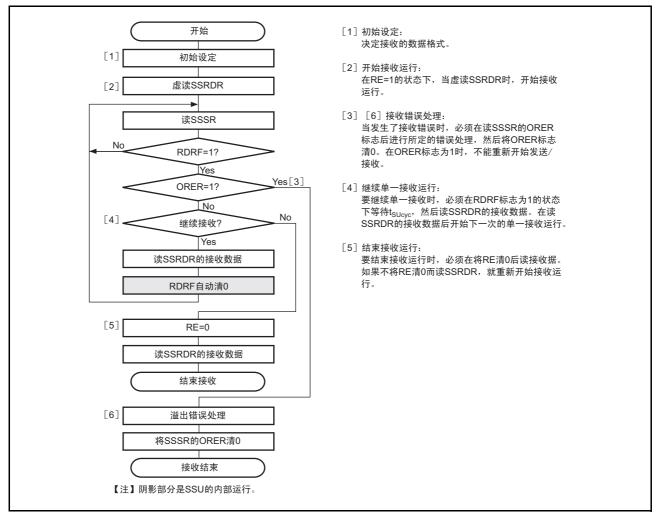

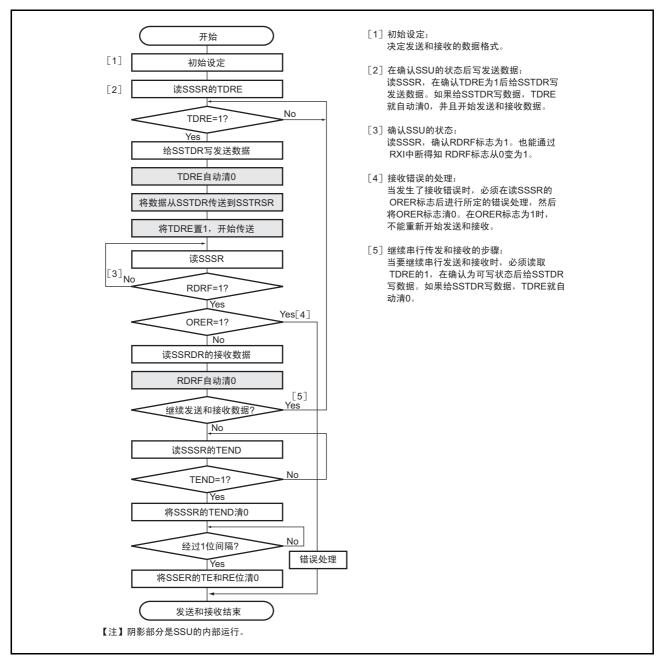

| 15.4 运行  | 亍说明                                         | 375 |

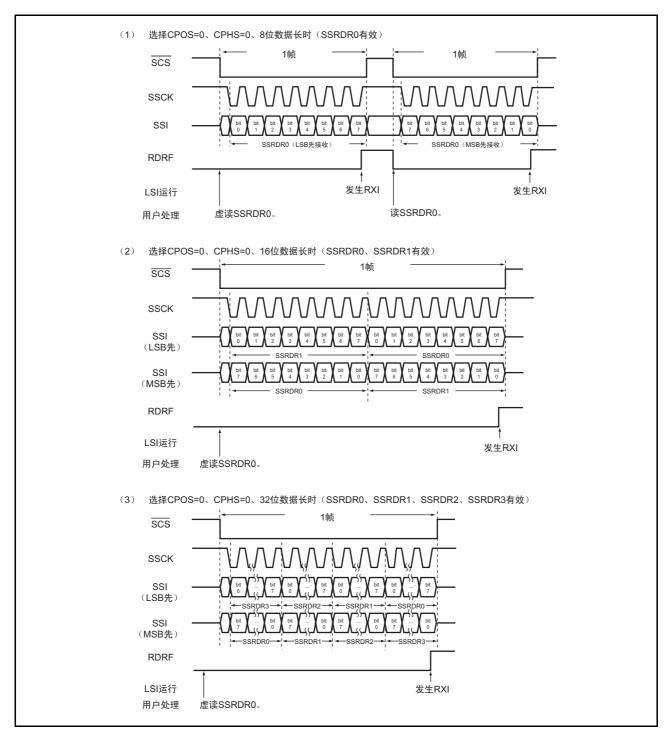

| 15.4.1   | 传送时钟                                        | 375 |

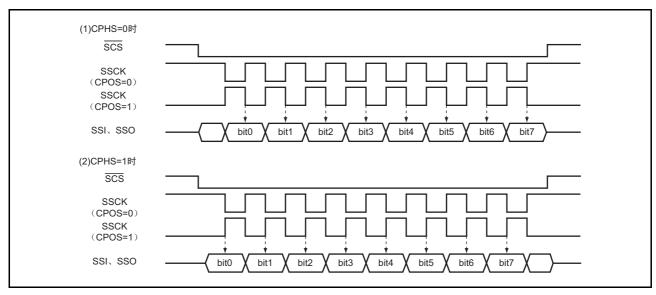

| 15.4.2   | 时钟的相位、极性和数据的关系                              | 375 |

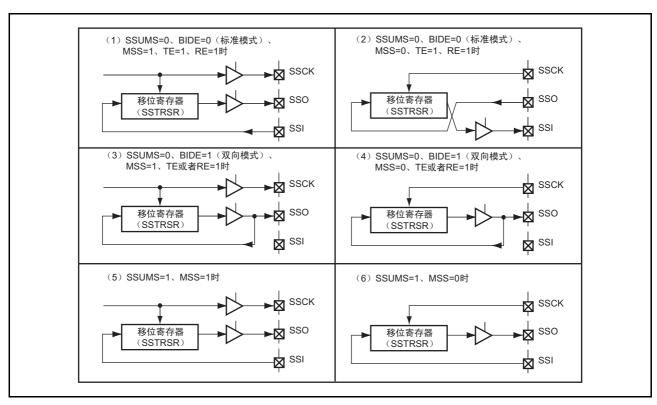

| 15.4.3   | 数据输入/输出引脚和移位寄存器的关系                          | 376 |

| 15.4.4   | 各通信模式和引脚功能                                  | 376 |

| 15.4.5   | SSU 模式                                      | 378 |

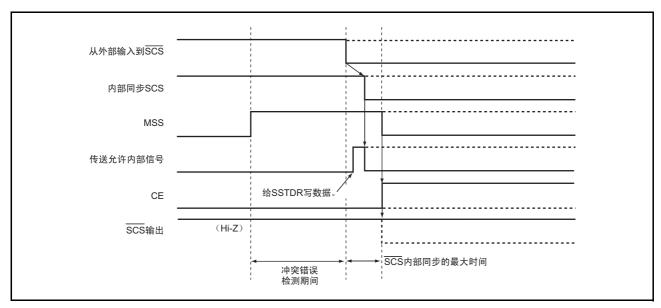

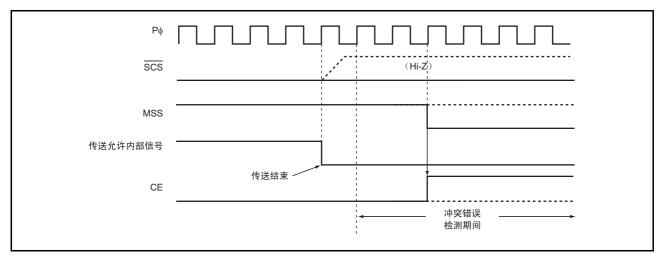

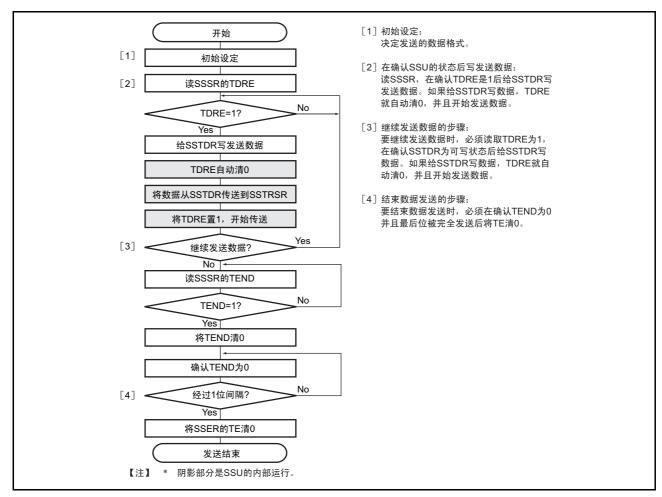

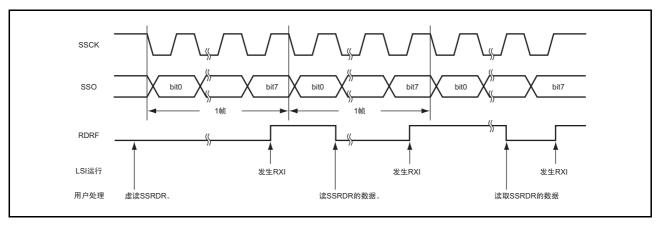

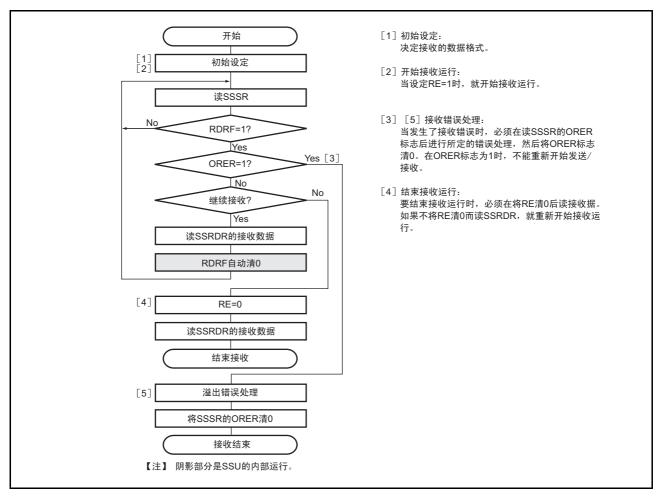

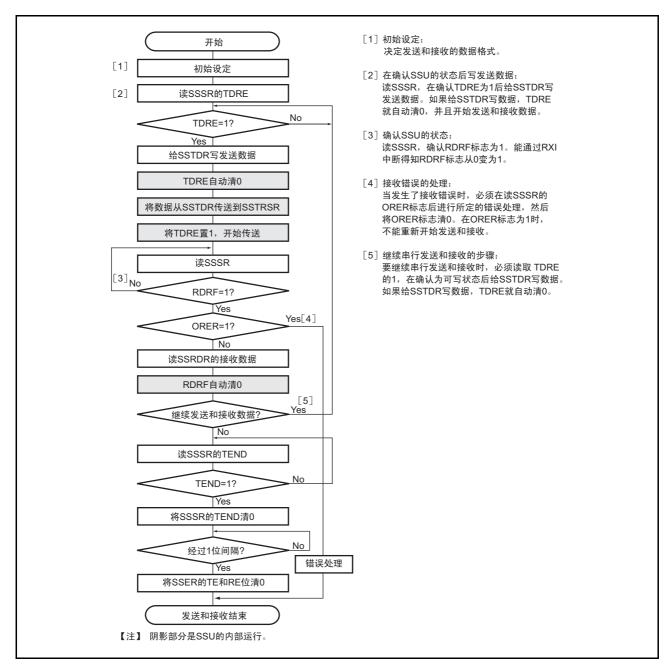

| 15.4.6   |                                             | 383 |

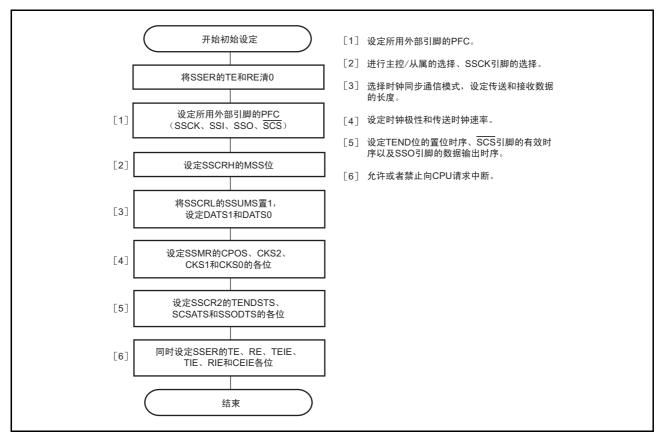

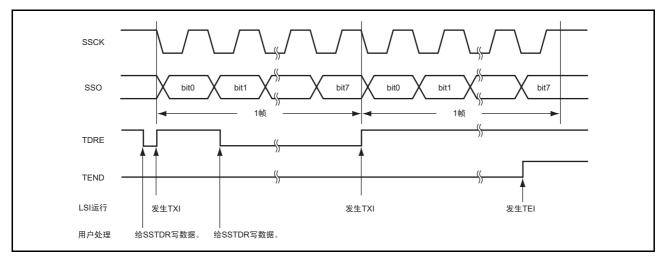

| 15.4.7   | 时钟同步通信模式                                    | 384 |

| 15.5 SSU | U 的中断源和 <b>DTC</b>                          |     |

| 15.6 使月  | 目时的注意事项                                     | 389 |

| 15.6.1   | 模块待机模式的设定                                   | 389 |

| 15.6.2   | SSTDR 和 SSRDR 寄存器的存取                        | 389 |

| 15.6.3   | SSU 从属模式中的连续发送和接收时的注意事项                     | 389 |

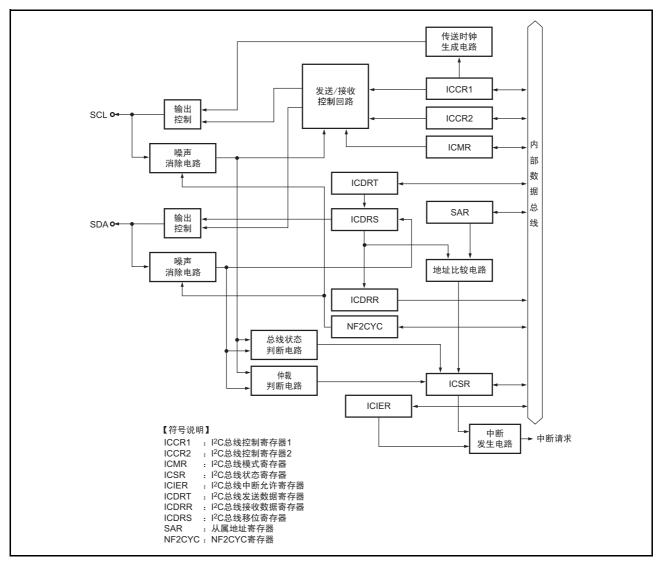

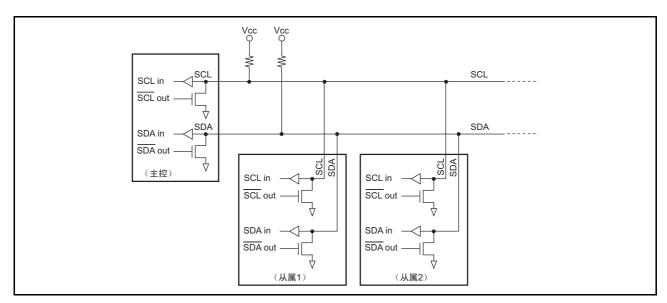

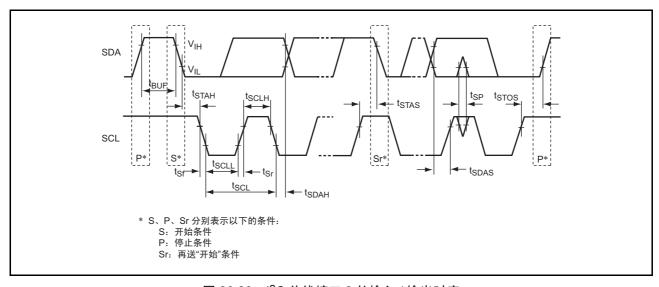

| 第 16 章   | I <sup>2</sup> C 总线接口 2 (I <sup>2</sup> C2) | 390 |

|          | <u>5</u>                                    |     |

|          | …<br>入/输出引脚                                 |     |

|          | 字器说明                                        |     |

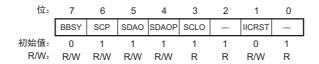

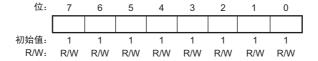

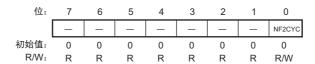

| 16.3.1   | I <sup>2</sup> C 总线控制寄存器 1(ICCR1)           |     |

| 16.3.2   | I <sup>2</sup> C 总线控制寄存器 2(ICCR2)           |     |

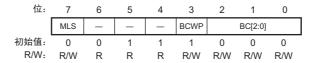

| 16.3.3   | I <sup>2</sup> C 总线模式寄存器(ICMR)              |     |

| 16.3.4   | I <sup>2</sup> C 总线中断允许寄存器(ICIER)           |     |

| 16.3.5   | I <sup>2</sup> C 总线状态寄存器(ICSR)              |     |

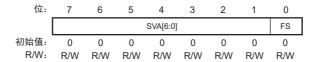

| 16.3.6   | 从属地址寄存器 (SAR)                               |     |

| 16.3.7   | I <sup>2</sup> C 总线发送数据寄存器(ICDRT)           |     |

| 16.3.8   | I <sup>2</sup> C 总线接收数据寄存器(ICDRR)           |     |

| 16.3.9   | I <sup>2</sup> C 总线移位寄存器(ICDRS)             |     |

| 16.3.10  | On the Pin                                  |     |

| 10.0.10  | 〒说明                                         |     |

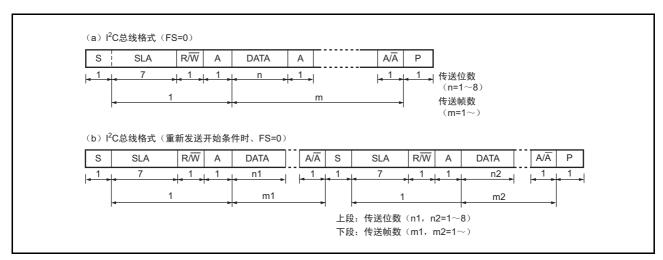

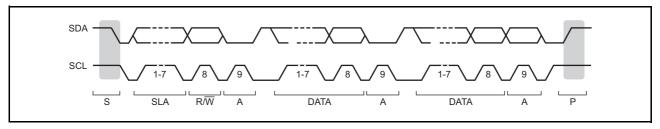

| 16.4.1   | I <sup>2</sup> C 总线格式                       |     |

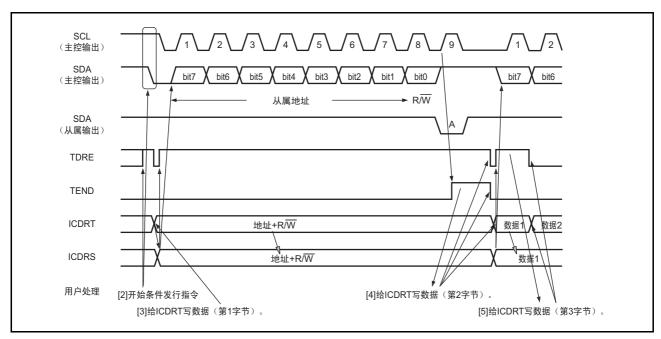

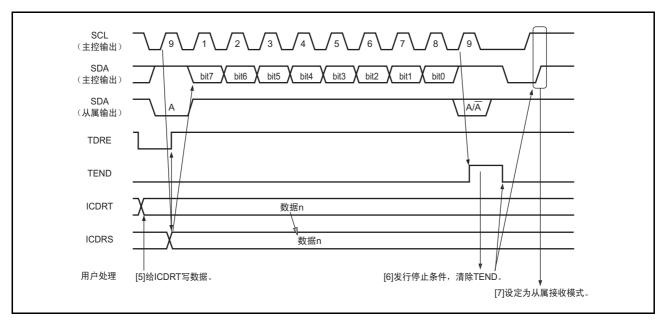

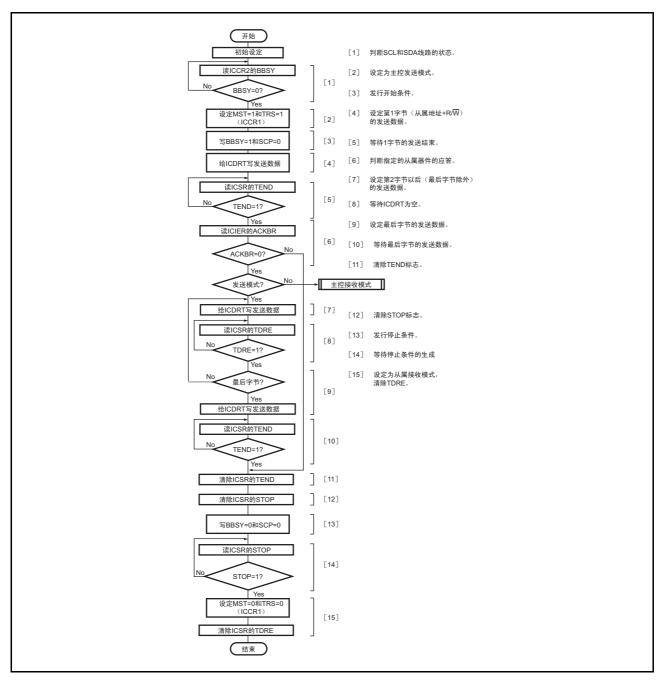

| 16.4.2   | 主控发送                                        |     |

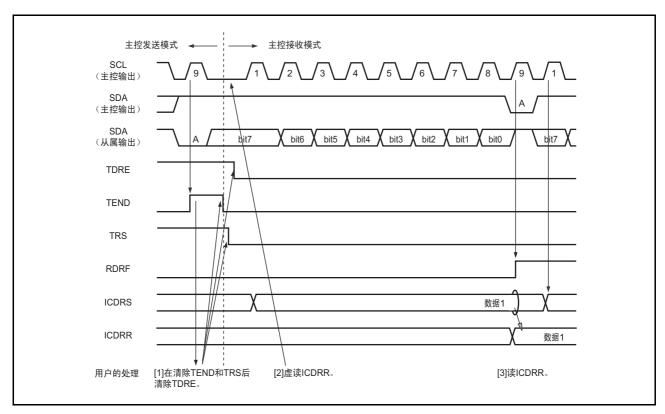

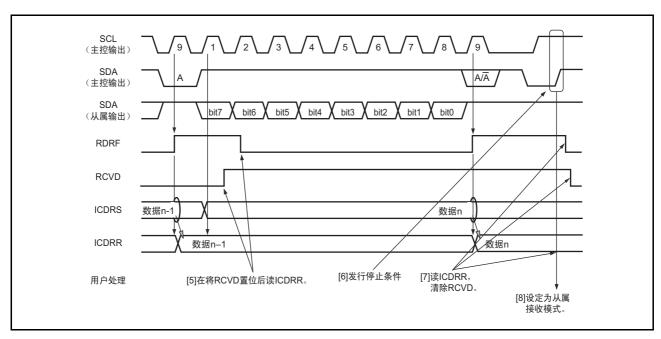

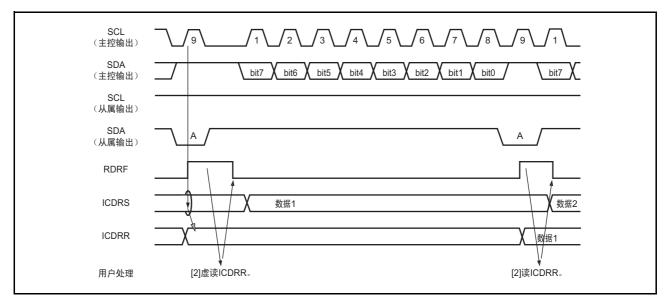

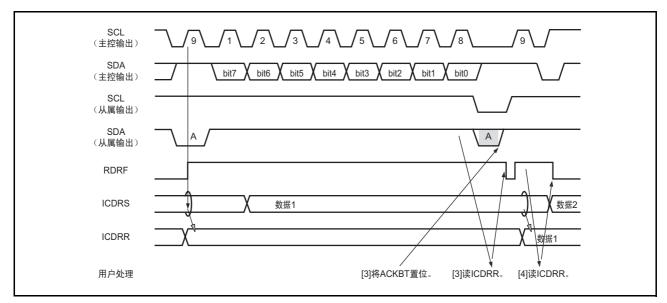

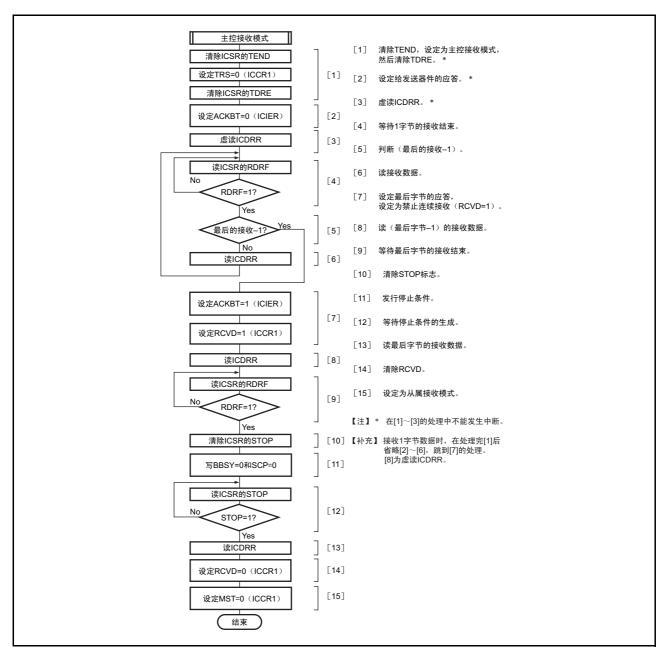

| 16.4.3   | 主控接收                                        |     |

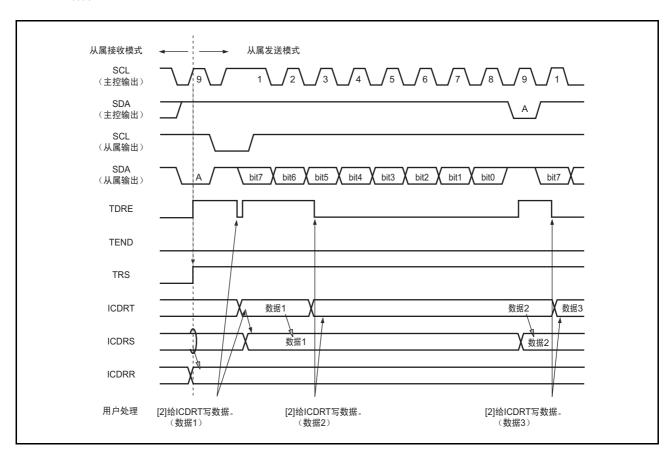

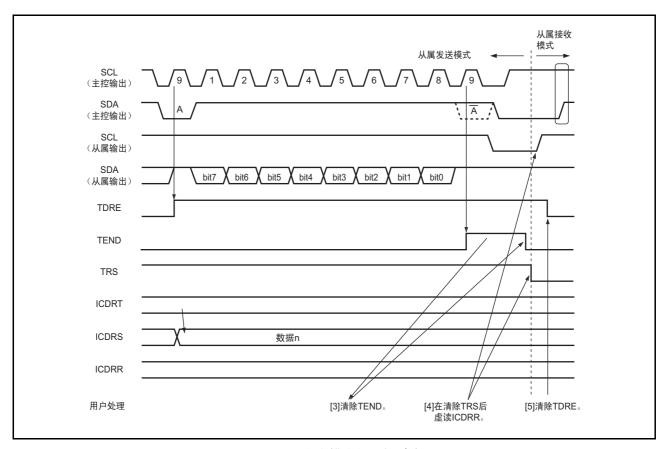

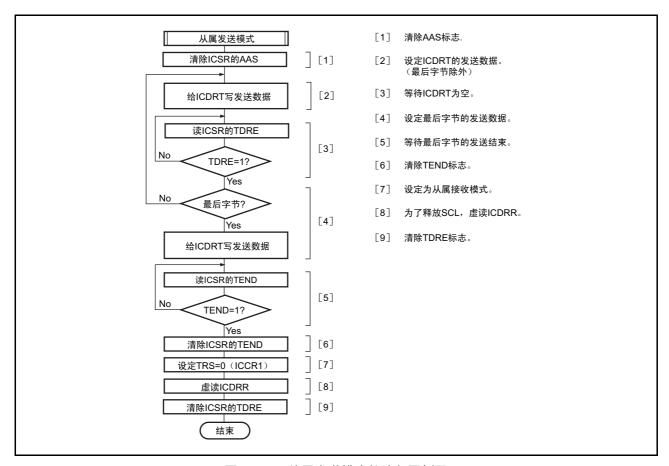

| 16.4.4   | 从属发送                                        |     |

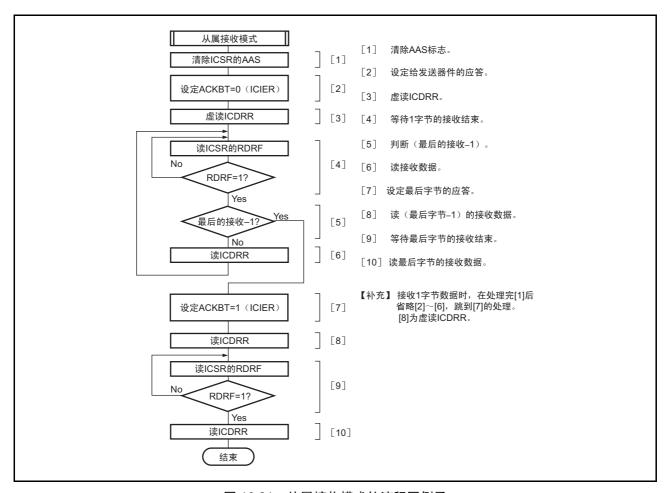

| 16.4.5   | 从属接收                                        |     |

| 16.4.6   | 时钟同步串行格式                                    |     |

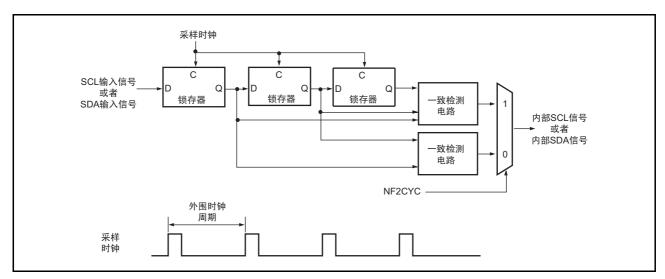

| 16.4.7   | 噪声消除电路                                      |     |

| 16.4.8   | 使用例                                         |     |

|          | 2 的中断源                                      |     |

|          | C 的运行                                       |     |

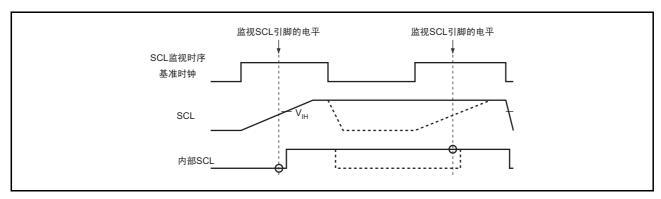

|          | 司步电路                                        |     |

|          | 刊 り 宅 ロ                                     |     |

| 16.8.1   | 模块待机模式的设定                                   |     |

| 16.8.2   | 停止条件和开始条件 (重新传送)的发行                         |     |

| 16.8.3   | 开始条件与停止条件的连续发行                              |     |

| 16.8.4   | 使用多主控时的设定                                   |     |

|          | 主控接收模式中的 ICDRR 的读操作                         |     |

| 16.8.6  | 仿真器的支持                                                                   | 417 |

|---------|--------------------------------------------------------------------------|-----|

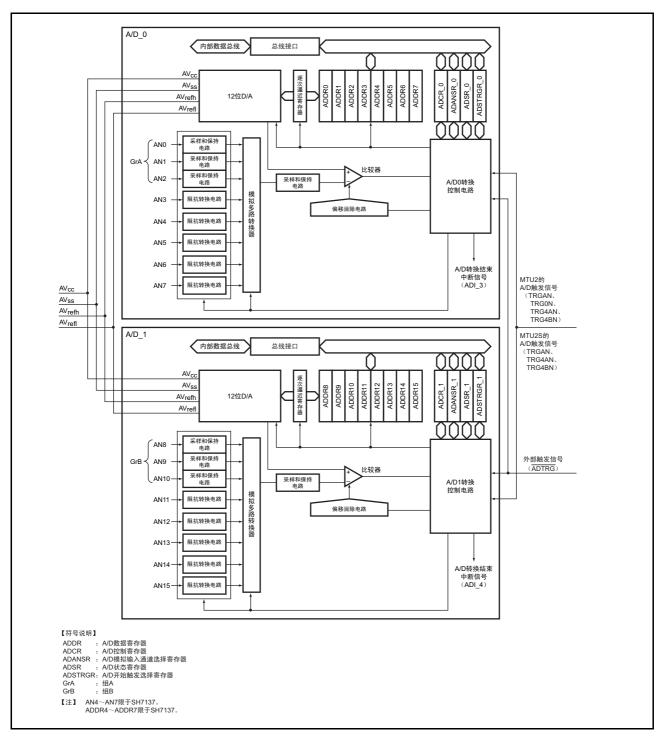

| 第 17 章  | A/D 转换器 (ADC)                                                            | 418 |

| 17.1 特点 | <u></u>                                                                  | 418 |

| 17.2 输力 | 入/输出引脚                                                                   | 420 |

| 17.3 寄花 | 字器说明                                                                     |     |

| 17.3.1  | A/D 控制寄存器 _0、_1(ADCR_0、ADCR_1)                                           | 422 |

| 17.3.2  | A/D 状态寄存器 _0、_1 (ADSR_0、ADSR_1)                                          |     |

| 17.3.3  | A/D 开始触发选择寄存器 _0、_1(ADSTRGR_0、ADSTRGR_1)                                 |     |

| 17.3.4  | A/D 模拟输入通道选择寄存器 _0、_1 (ADANSR_0、 ADANSR_1)                               |     |

| 17.3.5  | A/D 数据寄存器 0 ~ 15 (ADDR0 ~ ADDR15)                                        |     |

| 17.3.6  | 和 CPU 的接口                                                                |     |

|         | テ说明                                                                      |     |

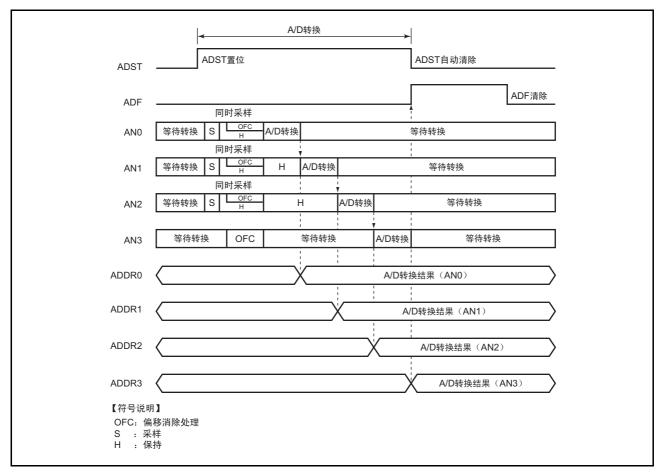

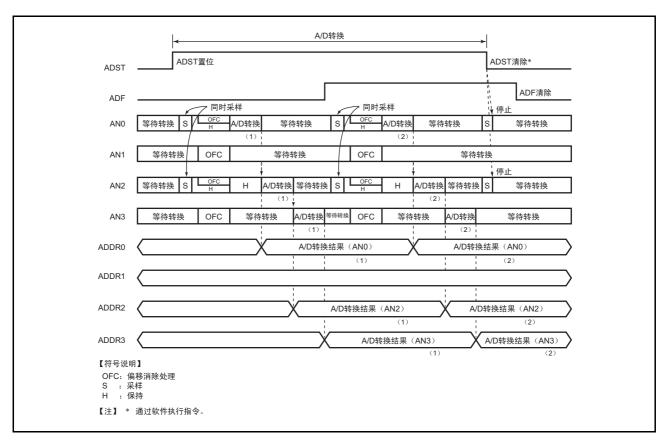

| 17.4.1  | 单周期扫描模式                                                                  |     |

| 17.4.2  | 连续扫描模式                                                                   |     |

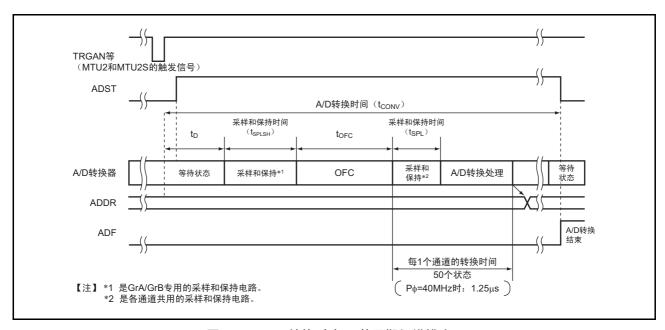

| 17.4.3  | 输入采样和 A/D 转换时间                                                           |     |

| 17.4.4  | 通过 MTU2 和 MTU2S 启动 A/D 转换器                                               |     |

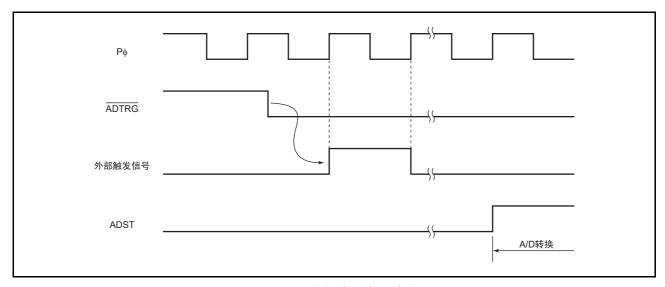

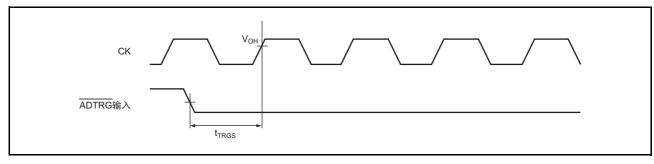

| 17.4.5  | 外部触发输入时序                                                                 |     |

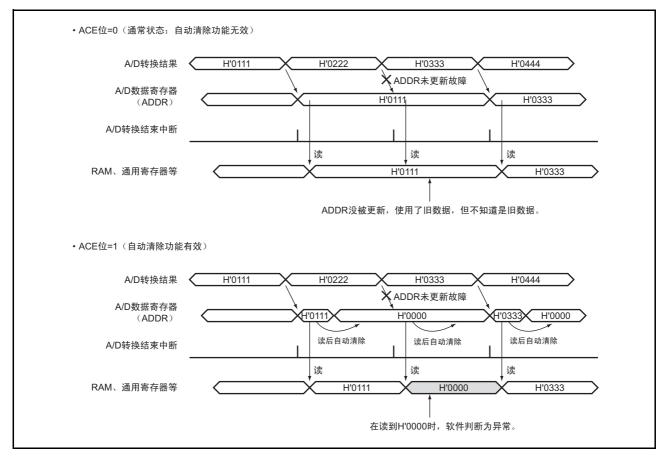

| 17.4.6  | ADDR 寄存器自动清除功能的使用例子                                                      |     |

|         | 斯源和 DTC 传送请求                                                             |     |

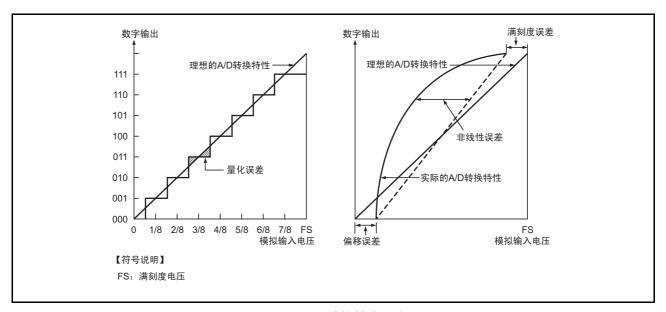

|         | <b>)</b> 转换精度的定义                                                         |     |

|         | 目时的注意事项                                                                  |     |

| 17.7.1  | 模拟输入电压的设定范围                                                              |     |

| 17.7.2  | AV <sub>CC</sub> 、AV <sub>SS</sub> 与V <sub>CC</sub> 、V <sub>SS</sub> 的关系 |     |

| 17.7.3  | AV <sub>refh</sub> 和 AV <sub>refl</sub> 引脚的设定范围                          |     |

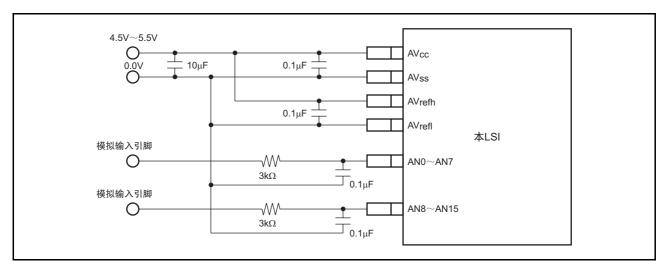

| 17.7.4  | 电路板设计的注意事项                                                               |     |

| 17.7.5  | 噪声对策的注意事项                                                                |     |

| 17.7.6  | 寄存器设定时的注意事项                                                              | 433 |

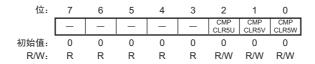

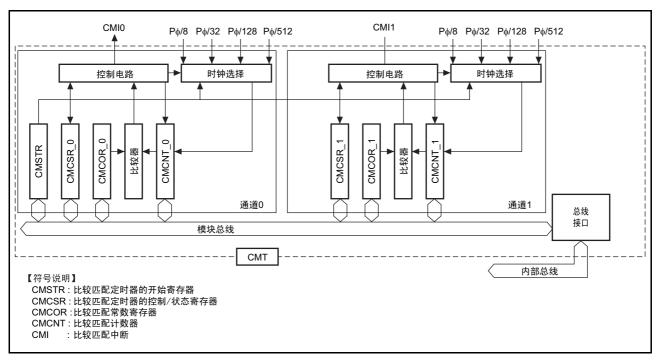

| 第 18 章  | 比较匹配定时器 (CMT)                                                            | 434 |

| 18.1 特点 | 片                                                                        | 434 |

| 18.2 寄花 | 字器说明                                                                     |     |

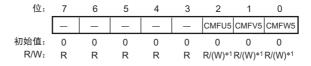

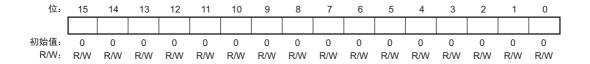

| 18.2.1  | 比较匹配定时器的开始寄存器 (CMSTR)                                                    |     |

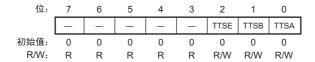

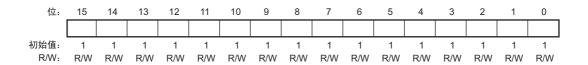

| 18.2.2  | 比较匹配定时器的控制 / 状态寄存器 (CMCSR)                                               | 436 |

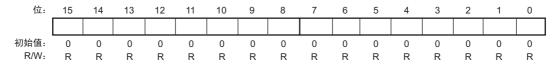

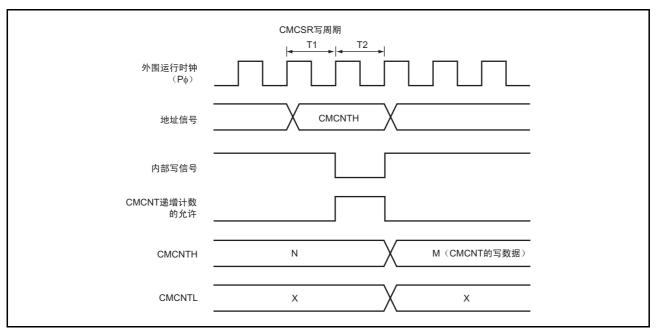

| 18.2.3  | 比较匹配计数器 (CMCNT)                                                          |     |

| 18.2.4  | 比较匹配常数寄存器 (CMCOR)                                                        |     |

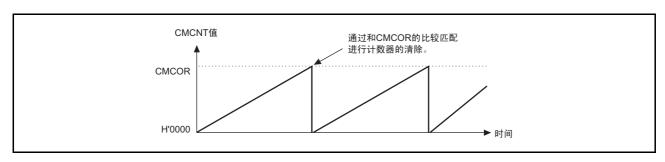

| 18.3 运行 | 亍说明                                                                      |     |

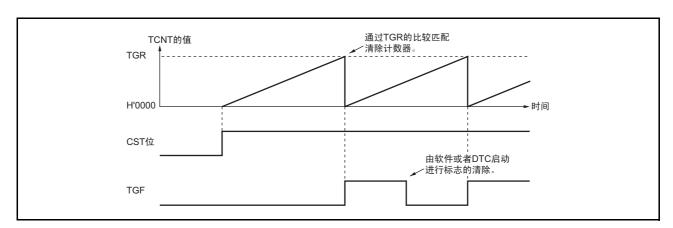

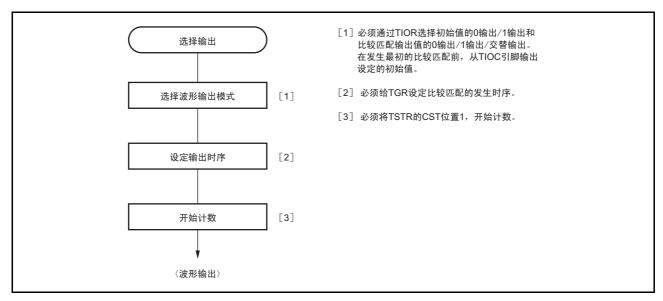

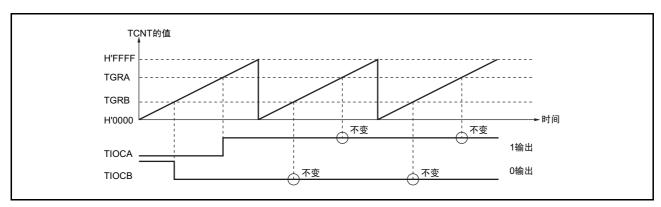

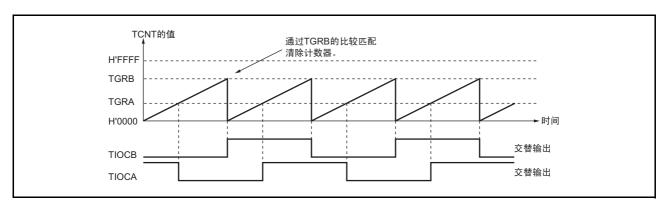

| 18.3.1  | 周期计数运行                                                                   |     |

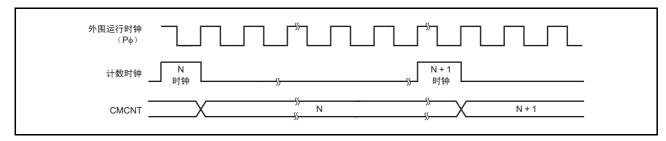

| 18.3.2  | CMCNT 的计数时序                                                              |     |

|         | 斯                                                                        |     |

| 18.4.1  | CMT 的中断源和 DTC                                                            |     |

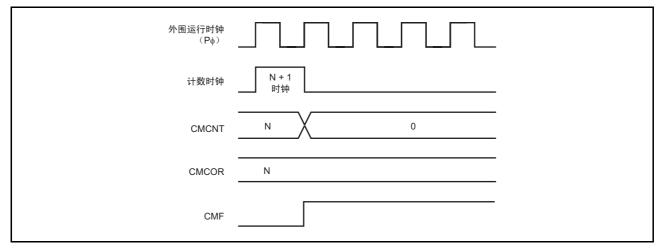

| 18.4.2  | 比较匹配标志的置位时序                                                              |     |

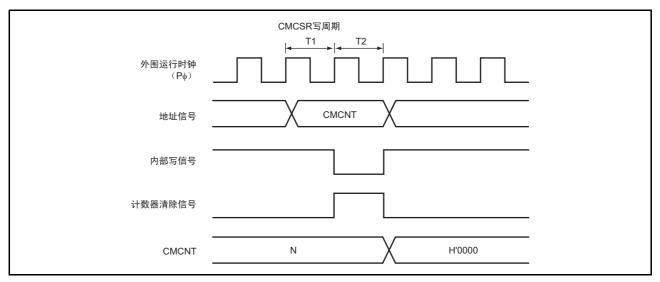

| 18.4.3  | 比较匹配标志的清除时序                                                              |     |

|         | 目时的注意事项                                                                  |     |

| 18.5.1  | 模块待机模式的设定                                                                |     |

| 18.5.2  | CMCNT 的写操作和比较匹配的竞争                                                       |     |

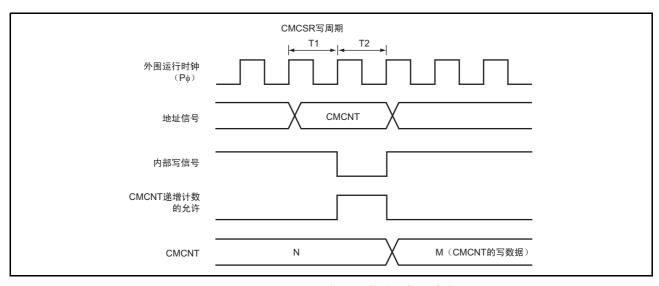

| 18.5.3  | CMCNT 的字写和递增计数的竞争                                                        |     |

| 18.5.4  | CMCNT 的字节写和递增计数的竞争                                                       |     |

| 18.5.5  | CMCNT 和 CMCOR 的比较匹配                                                      | 440 |

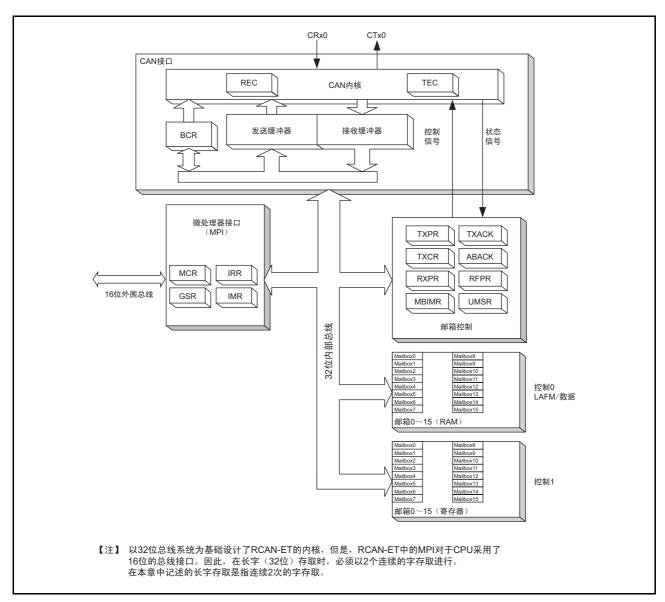

| 第 19 章  | 控制器局域网 (RCAN-ET)                                                         | 441 |

| 19.1 特点 | 点                                                                        | 441 |

| 19.2 结构 | $\Delta$                                                                 | 447 |

| 19.2.1   | 框图                                                             | 442         |

|----------|----------------------------------------------------------------|-------------|

| 19.2.2   | 各块的功能                                                          | 443         |

| 19.2.3   | 引脚结构                                                           | 443         |

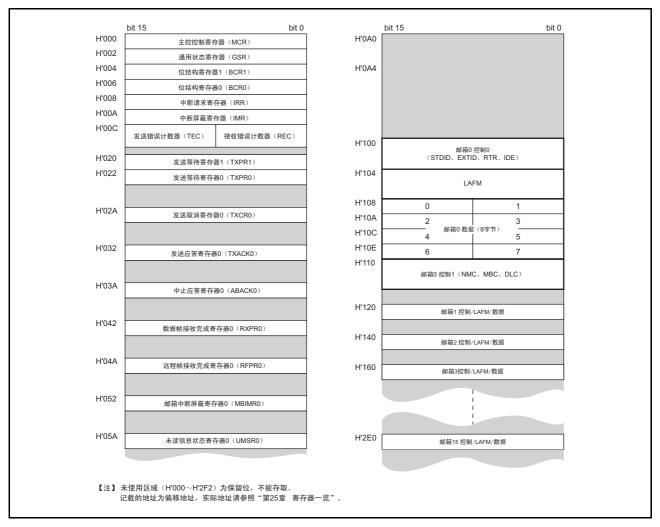

| 19.2.4   | 存储器映像                                                          | 444         |

| 19.3 邮箱  |                                                                | 444         |

| 19.3.1   | 邮箱的结构                                                          | 444         |

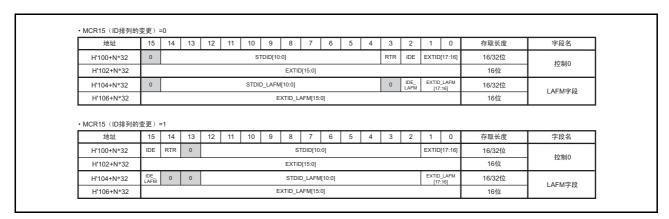

| 19.3.2   | 信息控制字段                                                         | 44 <i>6</i> |

| 19.3.3   | 局部接收过滤屏蔽 (LAFM)                                                | 449         |

| 19.3.4   | 信息数据字段                                                         | 449         |

| 19.4 RCA | N-ET 的控制寄存器                                                    | 450         |

| 19.4.1   | 主控控制寄存器 (MCR)                                                  | 450         |

| 19.4.2   | 通用状态寄存器 (GSR)                                                  | 454         |

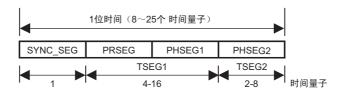

| 19.4.3   | 位结构寄存器 0、1(BCR0、BCR1)                                          | 45 <i>6</i> |

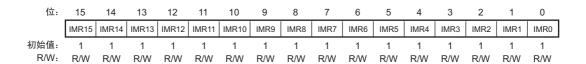

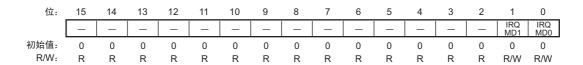

| 19.4.4   | 中断请求寄存器 (IRR)                                                  |             |

| 19.4.5   | 中断屏蔽寄存器 (IMR)                                                  |             |

| 19.4.6   | 发送错误计数器 (TEC) / 接收错误计数器 (REC)                                  | 463         |

| 19.5 RCA | N-ET 的邮箱寄存器                                                    |             |

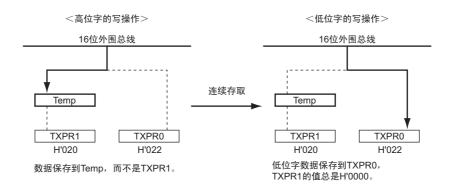

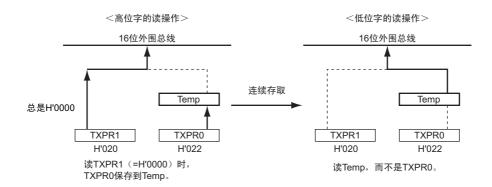

| 19.5.1   | 发送等待寄存器 1、0 (TXPR1、TXPR0)                                      |             |

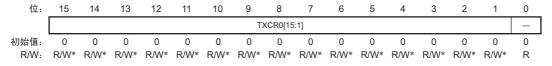

| 19.5.2   | 发送取消寄存器 0 (TXCR0)                                              | 466         |

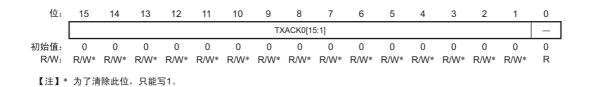

| 19.5.3   | 发送应答寄存器 0 (TXACK0)                                             |             |

| 19.5.4   | 中止应答寄存器 0 (ABACKO)                                             |             |

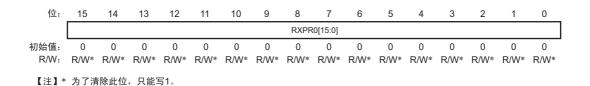

| 19.5.5   | 数据帧接收完成寄存器 0 (RXPR0)                                           |             |

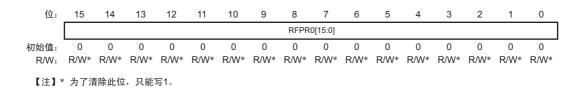

| 19.5.6   | 远程帧接收完成寄存器 0 (RFPR0)                                           |             |

| 19.5.7   | 邮箱中断屏蔽寄存器 0 (MBIMR0)                                           |             |

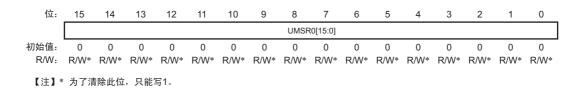

| 19.5.8   | 未读信息状态寄存器 0 (UMSR0)                                            |             |

|          | 说明                                                             |             |

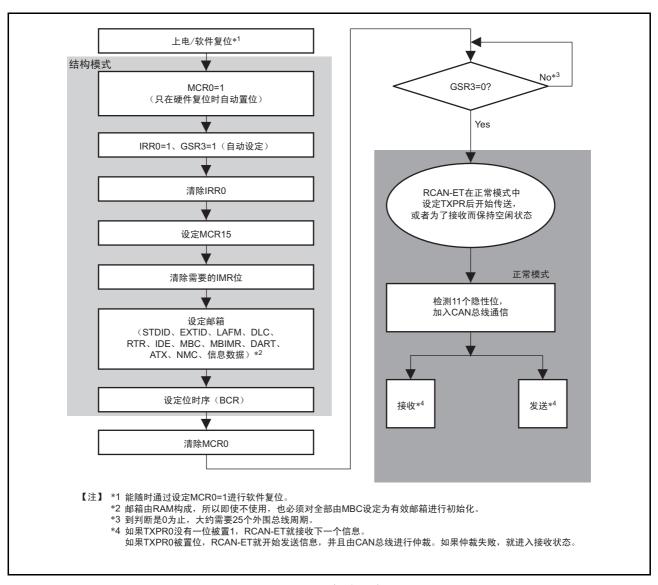

| 19.6.1   | RCAN-ET 的设定                                                    |             |

| 19.6.2   | 测试模式的设定                                                        |             |

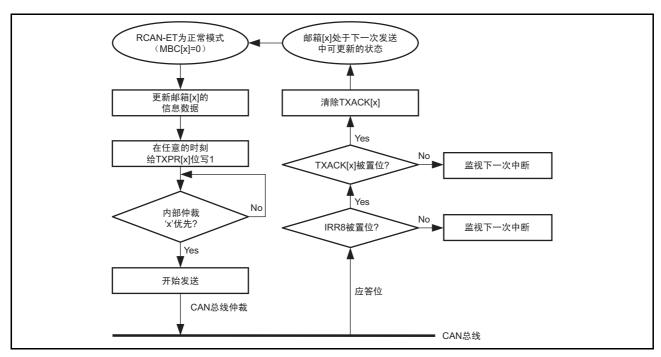

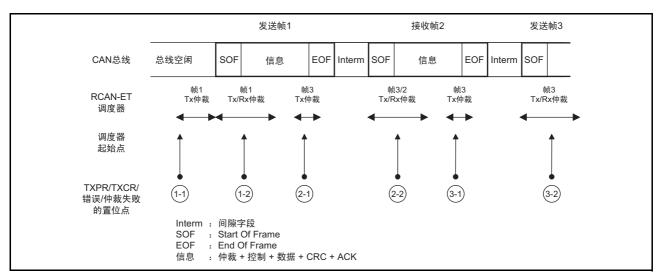

| 19.6.3   | 信息的发送顺序                                                        |             |

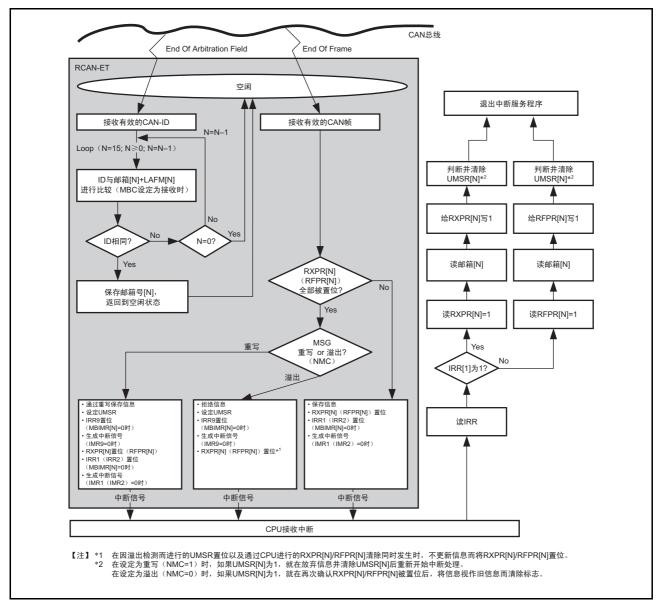

| 19.6.4   | 信息的接收顺序                                                        |             |

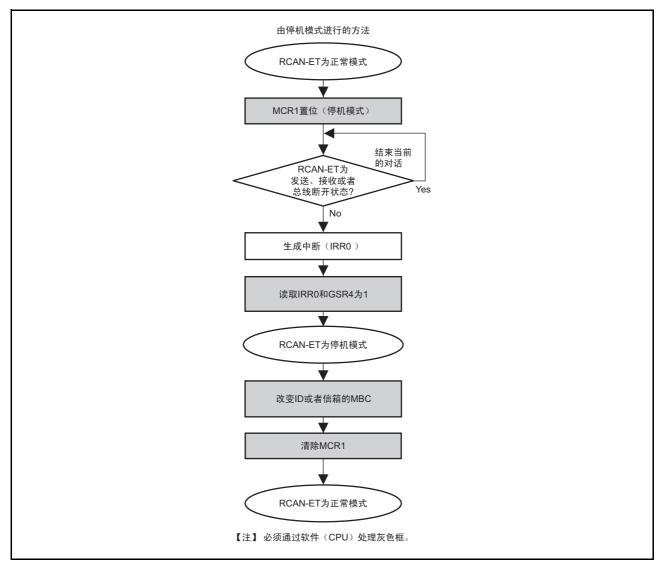

| 19.6.5   | 邮箱的重新设定                                                        |             |

|          | 源                                                              |             |

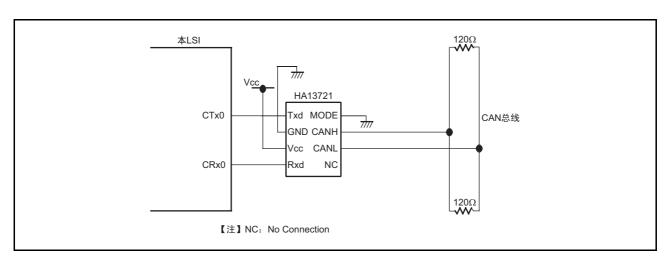

|          | ·<br>接口                                                        |             |

|          | 总线接口                                                           |             |

|          |                                                                |             |

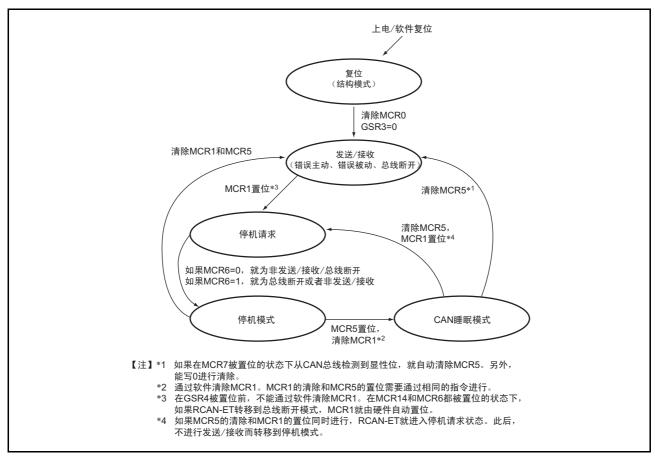

| 19.10.1  | 模块停止模式                                                         |             |

| 19.10.2  | 复位                                                             |             |

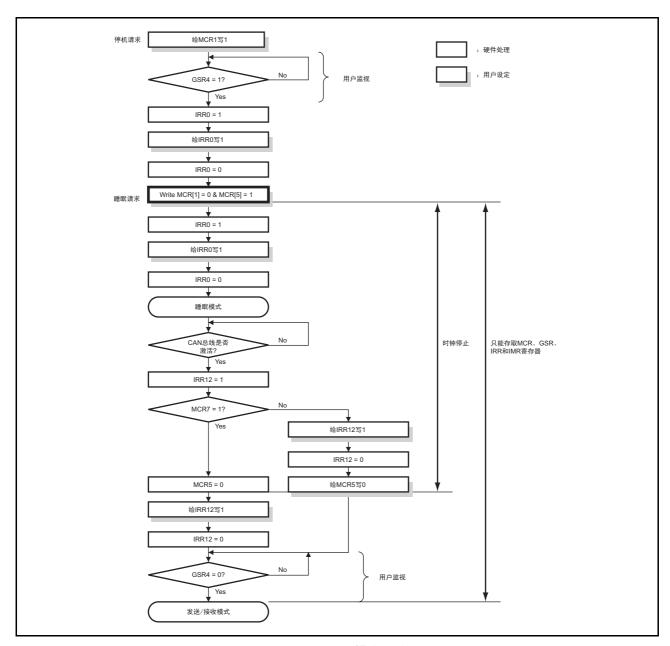

| 19.10.3  | CAN 睡眠模式                                                       |             |

| 19.10.4  | 寄存器的存取                                                         |             |

| 19.10.5  | 中断                                                             |             |

|          |                                                                |             |

| 第 20 章   | 引脚功能控制器 (PFC)                                                  | 482         |

| 20.1 寄存  | 器说明                                                            | 495         |

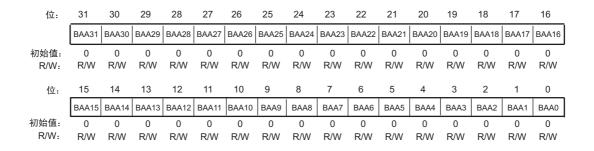

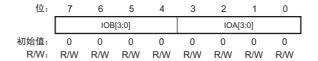

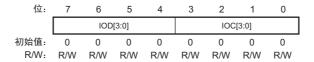

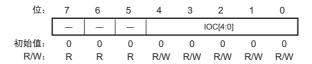

| 20.1.1   | 端口A的IO寄存器L(PAIORL)                                             | 495         |

| 20.1.2   | 端口 A 的控制寄存器 L1 ~ L4 (PACRL1 ~ PACRL4)                          | 496         |

| 20.1.3   | 端口B的IO寄存器L(PBIORL)                                             | 504         |

| 20.1.4   | 端口B的控制寄存器L1、L2(PBCRL1、PBCRL2)                                  | 505         |

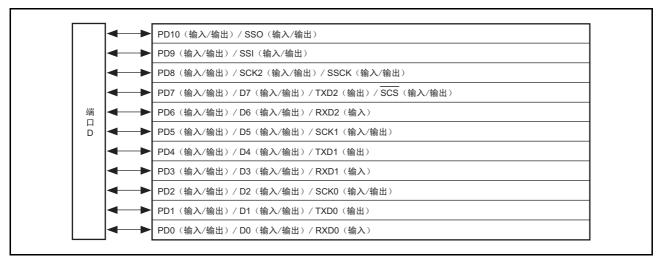

| 20.1.5   | 端口 D 的 IO 寄存器 L (PDIORL) (只限 SH7137)                           | 509         |

| 20.1.6   | 端口 D 的控制寄存器 L1 $\sim$ L3 (PDCRL1 $\sim$ PDCRL3)(只限 SH7137)     | 509         |

| 20.1.7   | 端口 E 的 IO 寄存器 L、 H (PEIORL 和 PEIORH)                           |             |

| 20.1.8   | 端口 E 的控制寄存器 L1 ~ L4、 H1、 H2 (PECRL1 ~ PECRL4、 PECRH1 和 PECRH2) | 513         |

| 20.1.9   | IRQOUT 功能的控制寄存器(IFCR)                                          | 523         |

| 20.2 使田  | 时的注音重项                                                         | 52/         |

| 第 21 章 | : 1/ | /O 端口                              | . 525 |

|--------|------|------------------------------------|-------|

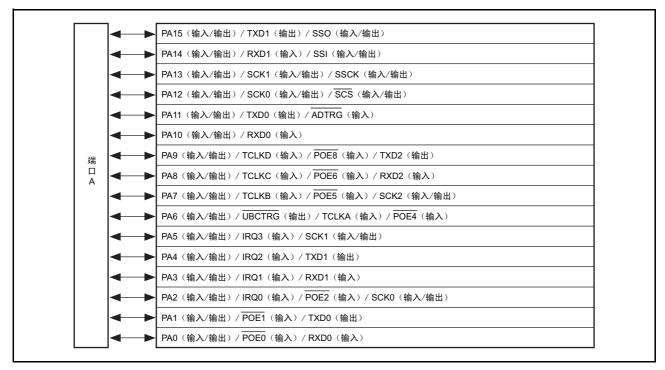

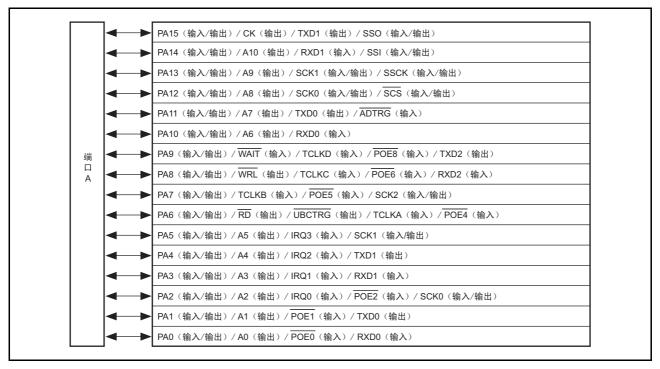

| 21.1   | 端口。  | A                                  | . 525 |

| 21.1.  | .1   | 寄存器说明                              | 526   |

| 21.1.  | .2   | 端口 A 的数据寄存器 L (PADRL)              | 526   |

| 21.1.  | .3   | 端口 A 的端口寄存器 L (PAPRL)              | 527   |

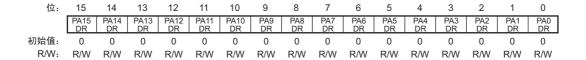

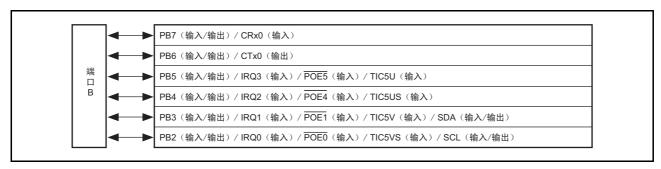

| 21.2   | 端口]  | В                                  | . 529 |

| 21.2.  | .1   | 寄存器说明                              | 529   |

| 21.2.  | .2   | 端口 B 的数据寄存器 L (PBDRL)              | 529   |

| 21.2.  | .3   | 端口 B 的端口寄存器 L (PBPRL)              | 531   |

| 21.3   | 端口]  | D (只限 SH7137)                      | . 533 |

| 21.3.  | .1   | 寄存器说明                              | 533   |

| 21.3.  | .2   | 端口 D 的数据寄存器 L (PDDRL)              | 533   |

| 21.3.  | .3   | 端口 D 的端口寄存器 L (PDPRL)              | 534   |

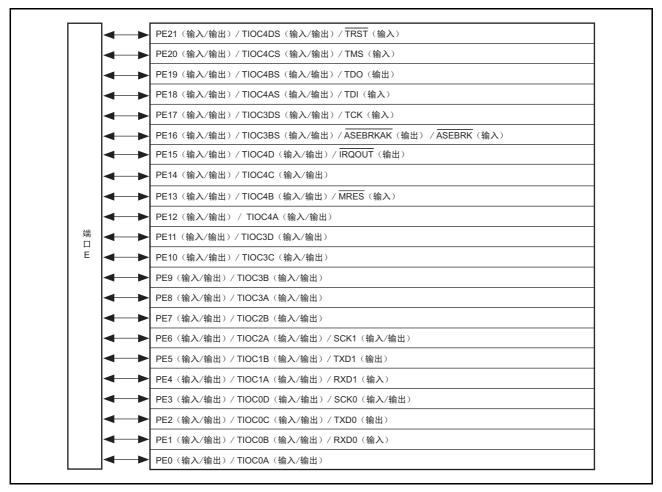

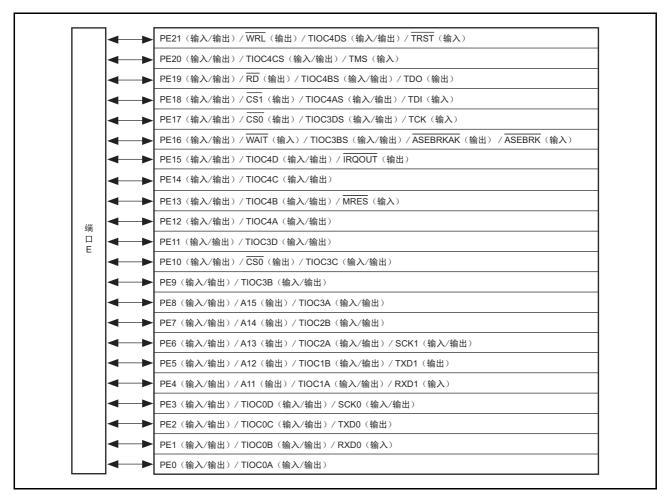

| 21.4   |      | E                                  |       |

| 21.4.  |      | 寄存器说明                              |       |

| 21.4.  | .2   | 端口 E 的数据寄存器 H、L (PEDRH、 PEDRL)     | 537   |

| 21.4.  | .3   | 端口 E 的端口寄存器 H、L(PEPRH、PEPRL)       | 538   |

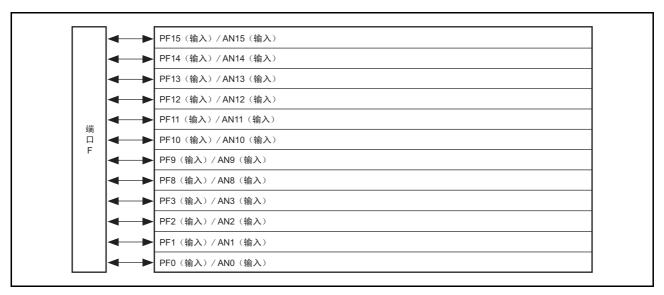

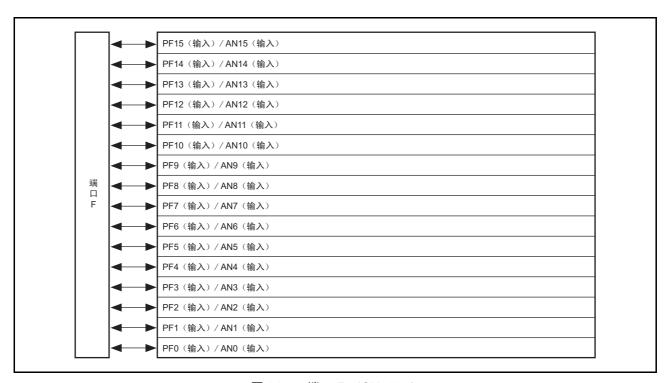

| 21.5   | 端口]  | F                                  | . 540 |

| 21.5.  | -    | 寄存器说明                              |       |

| 21.5.  | .2   | 端口 F 的数据寄存器 L (PFDRL)              | 541   |

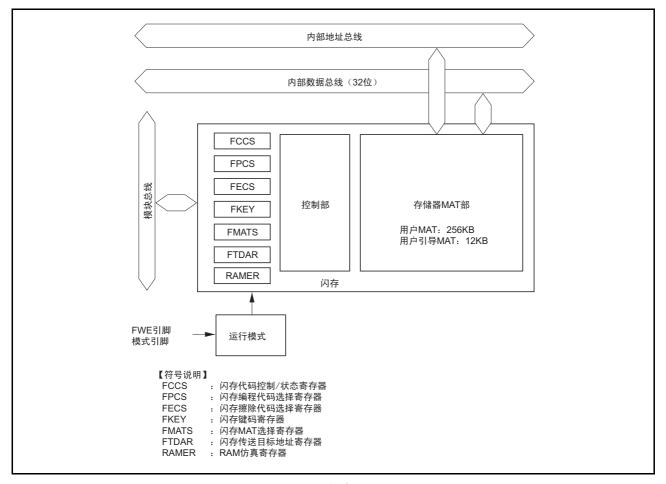

| 第 22 章 | ì    | Ŋ存                                 | 543   |

|        |      | 11.                                |       |

|        |      |                                    |       |

| 22.2   |      | 框图                                 |       |

| 22.2.  |      | 性間                                 |       |

| 22.2.  |      | 模式比较                               |       |

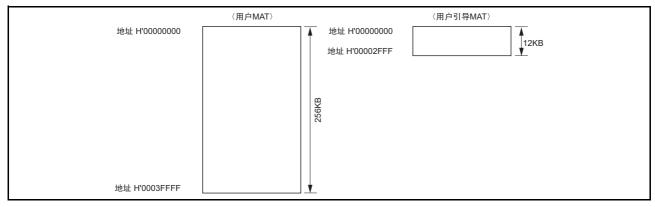

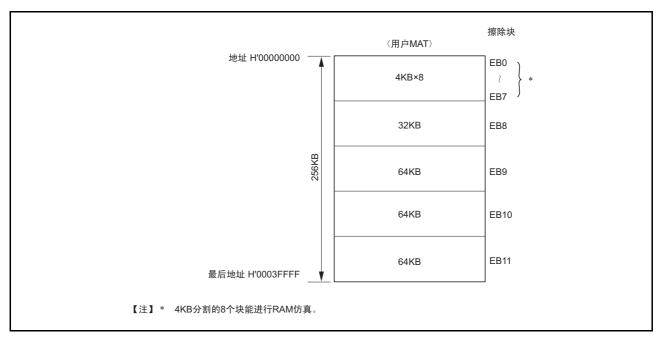

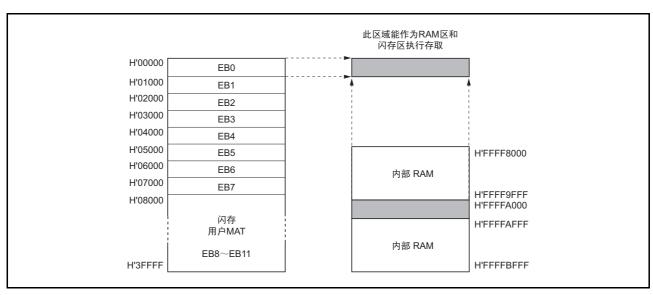

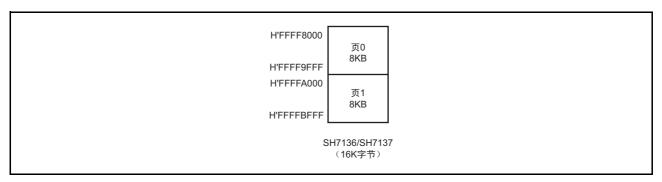

| 22.2.  |      | 闪存结构                               |       |

| 22.2.  |      | 块分割                                |       |

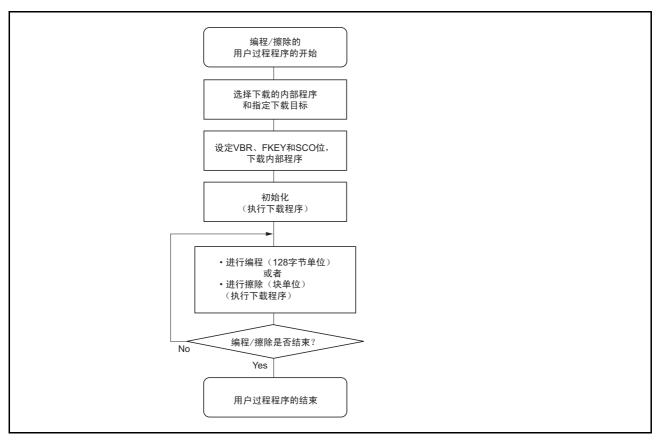

| 22.2.  |      | 编程 / 擦除的接口                         |       |

|        |      | /输出引脚                              |       |

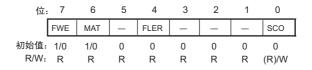

|        |      | 器说明                                |       |

| 22.4   |      | 寄存器一览表                             |       |

| 22.4.  |      | 编程 / 擦除接口寄存器                       |       |

|        |      | 编程/擦除接口参数                          |       |

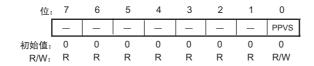

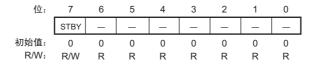

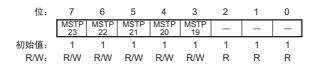

| 22.4.  |      | RAM 仿真寄存器(RAMER)                   |       |

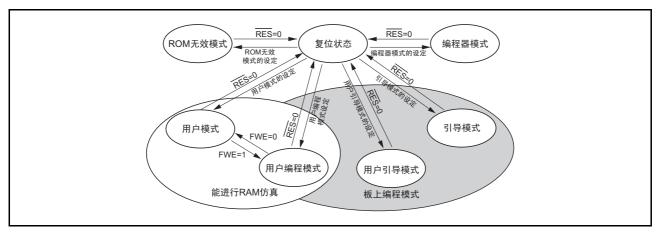

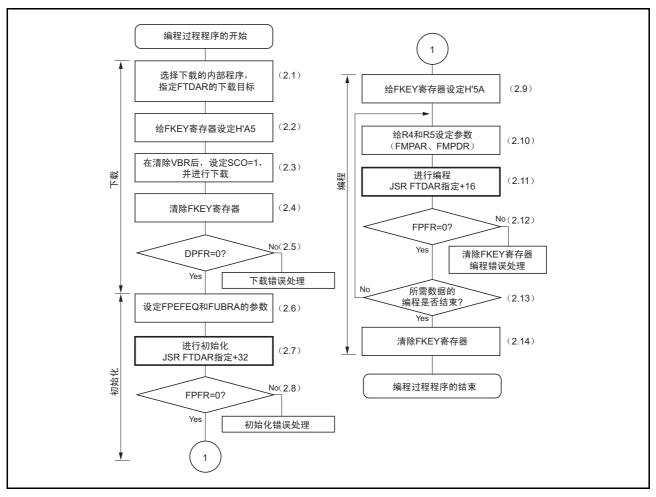

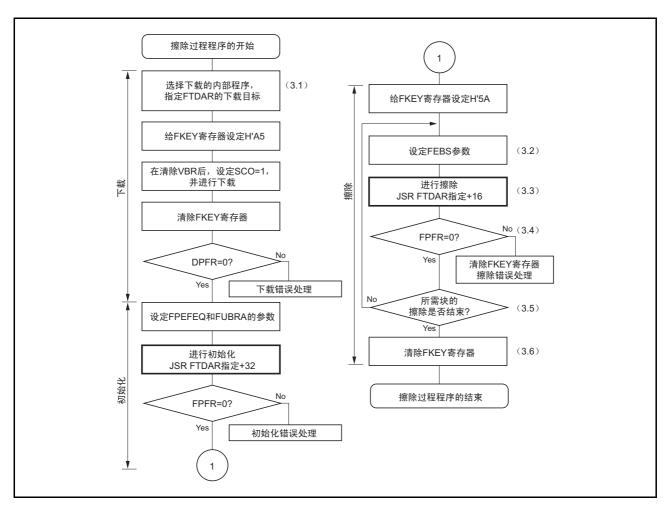

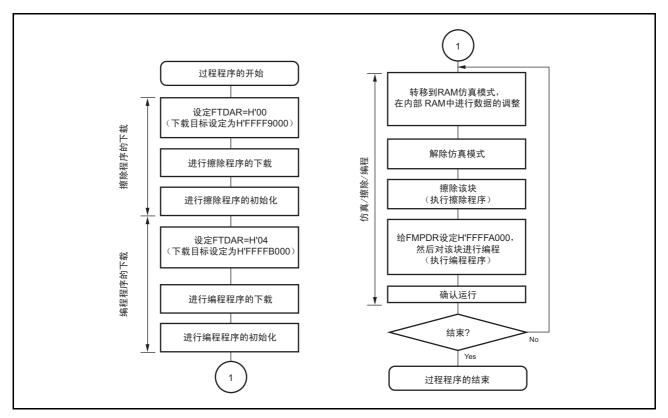

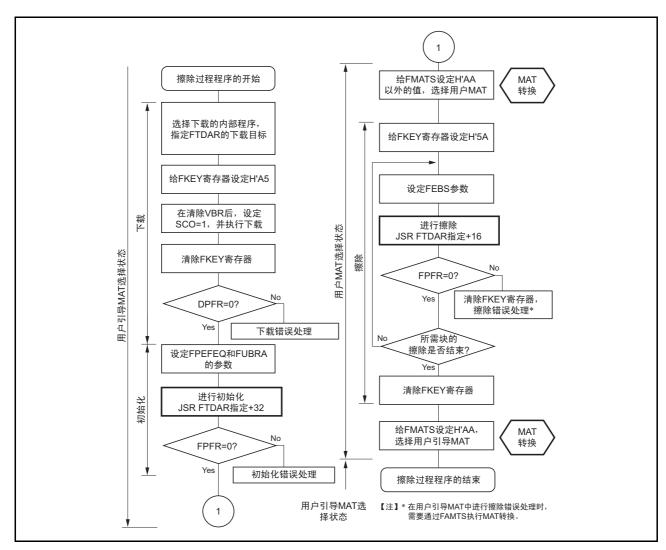

|        |      | 扁程模式                               |       |

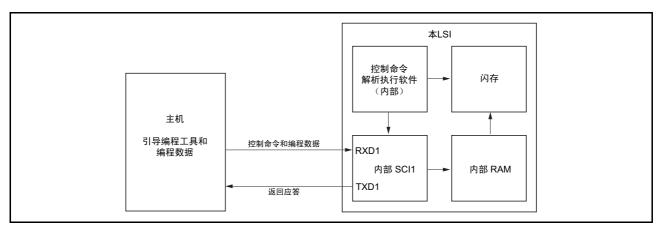

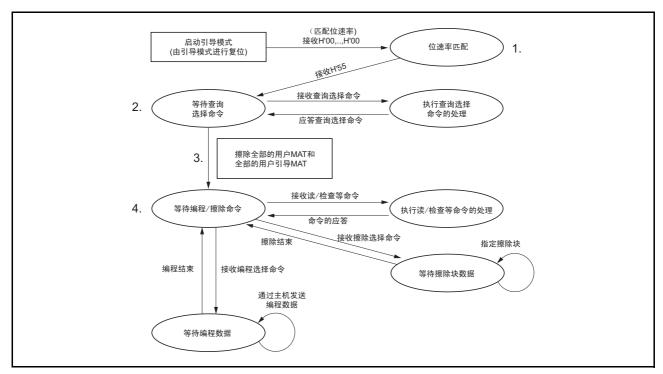

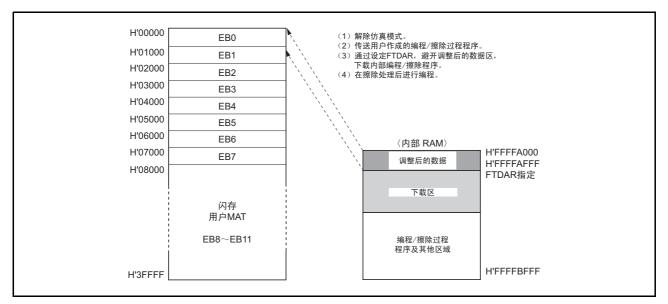

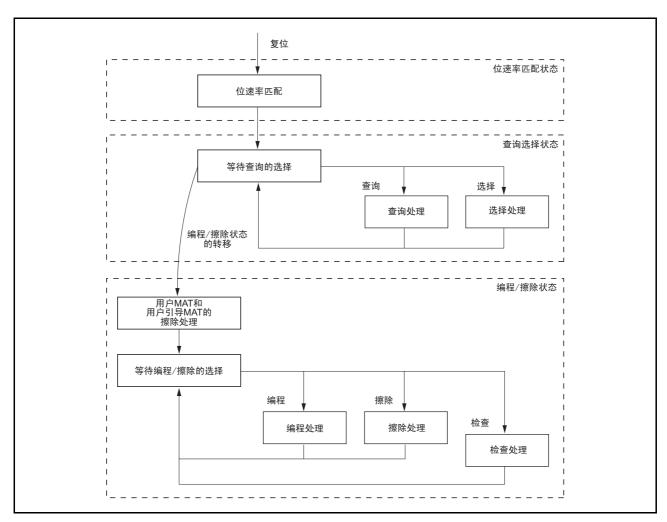

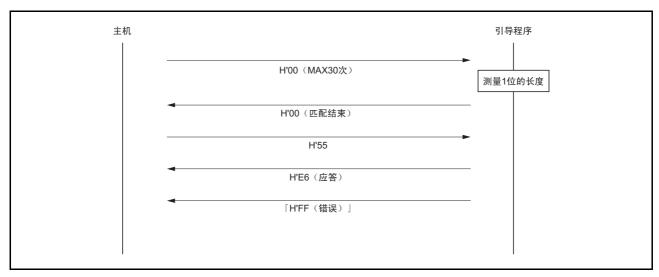

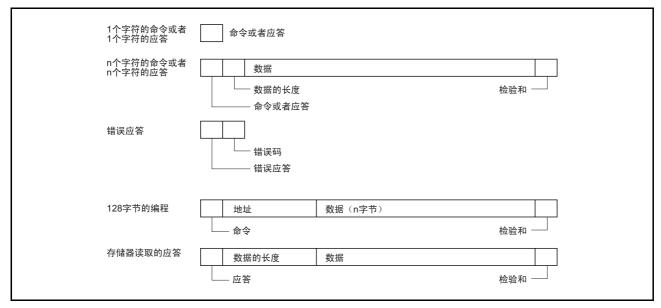

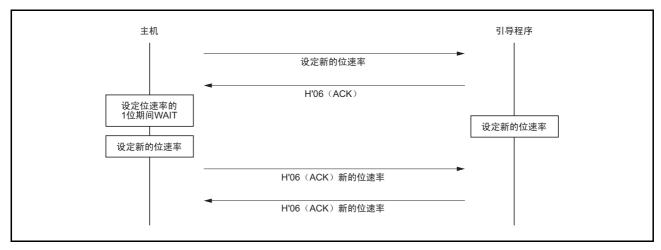

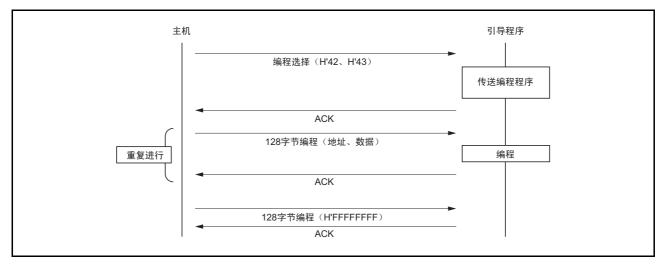

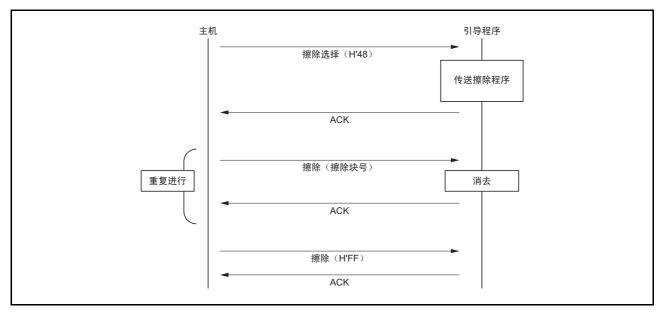

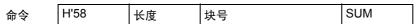

| 22.5.  |      | 引导模式                               |       |

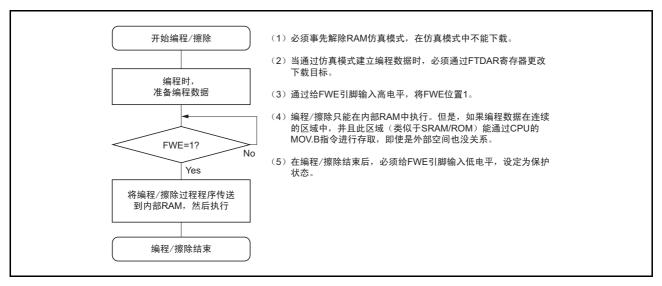

| 22.5.  |      | 用户编程模式                             |       |

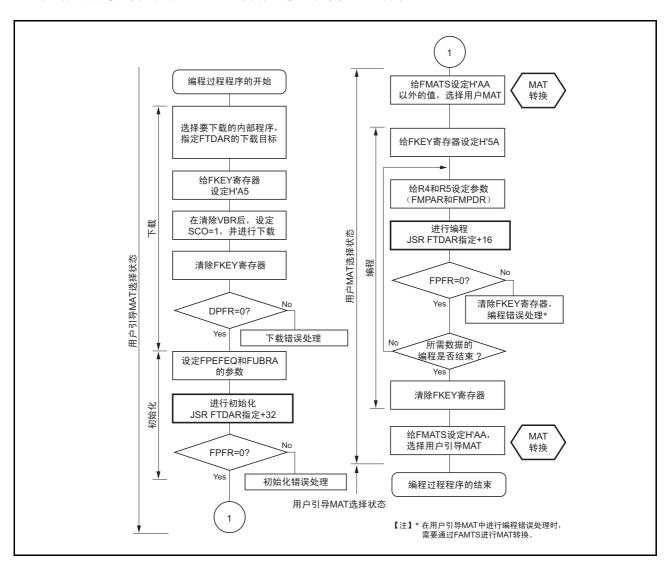

| 22.5.  |      | 用户引导模式                             |       |

| 22.6   |      |                                    |       |

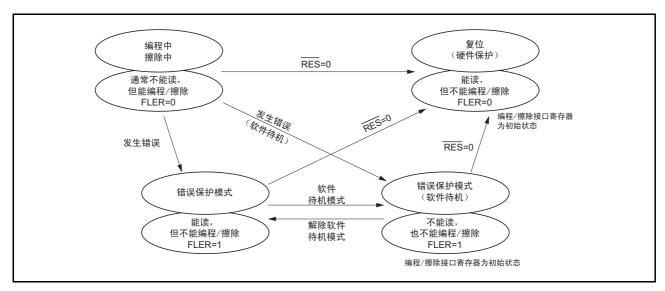

| 22.6.  |      | 硬件保护                               |       |

| 22.6.  |      | 软件保护                               |       |

| 22.6.  |      | 错误保护                               |       |

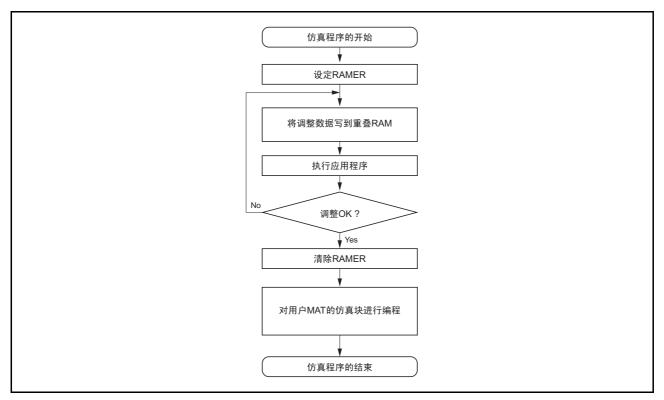

|        |      | RAM 对闪存进行的仿真                       |       |

|        |      | 寸的注意事项                             |       |

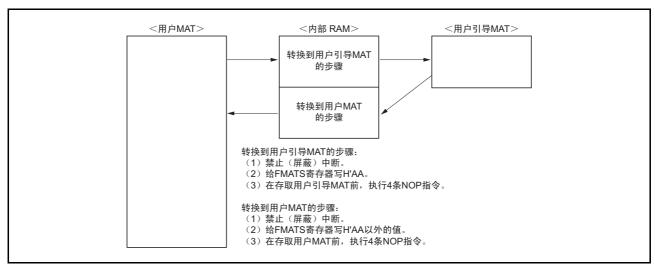

| 22.8.  |      | 用户 <b>MAT</b> 和用户引导 <b>MAT</b> 的转换 |       |

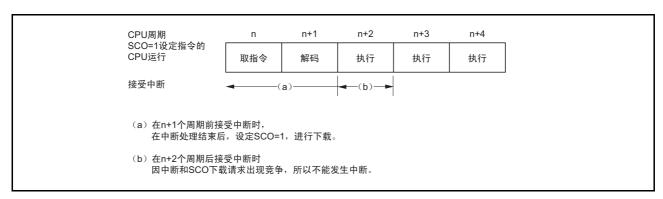

| 22.8.  |      | 编程 / 擦除过程中的中断                      |       |

| 22.8.  |      | 其他注意事项                             |       |

|        |      | X (                                |       |

| 22.9.  |      | 引导模式的标准串行通信接口规格                    |       |

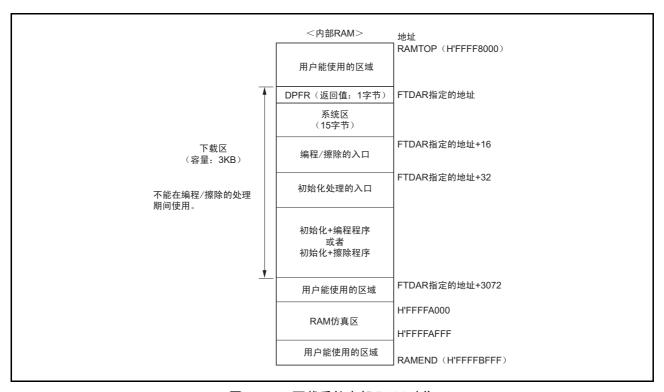

| 22.9.  |      | 过程程序和编程数据的可保存区域                    |       |

| 22.10  | 编程器  | B模式                                | . 604 |

| 第 23 章 | RAM                                       | 605 |

|--------|-------------------------------------------|-----|

| 23.1   | 使用时的注意事项                                  | 605 |

| 23.1.  | .1 模块待机模式的设定                              | 605 |

| 23.1.  | 2 地址错误                                    | 605 |

| 23.1.  | .3 RAM 的初始值                               |     |

| 第 24 章 | 低功耗模式                                     | 606 |

| 24.1   | 特点                                        |     |

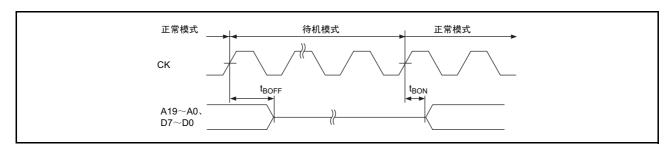

| 24.1.  | .1 低功耗模式的种类                               | 606 |

|        | 输入/输出引脚                                   |     |

|        | 寄存器说明                                     |     |

| 24.3.  | 14 h 44 = 14 HB = 7 = ==== 1              |     |

| 24.3.  | - 14 hearthand 14 HB - (~                 |     |

| 24.3.  |                                           |     |

| 24.3.  | , , , , , , , , , , , , , , , , , , ,     |     |

| 24.3.  | 14 h 24 = 114 14 HB 5 ( = = = = = )       |     |

| 24.3.  | 14 h 44 = 114 HB 4 (10 = 10 = 10)         |     |

| 24.3.  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |     |

| 24.4   | 睡眠模式                                      |     |

| 24.4.  |                                           |     |

|        | · 软件待机模式                                  |     |

| 24.5   | A A A A A A A A A A A A A A A A A A A     |     |

| 24.5.  |                                           |     |

|        | 深度软件待机模式                                  |     |

| 24.6.  |                                           |     |

| 24.6.  |                                           |     |

|        | 模块待机功能                                    |     |

| 24.7.  |                                           |     |

| 24.7.  |                                           |     |

| 24.8   | 使用时的注意事项                                  | 615 |

| 24.8.  | 1 振荡稳定待机中的消耗电流                            | 615 |

| 24.8.  | .2 深度软件待机模式                               | 615 |

| 24.8.  | .3 执行 SLEEP 指令时                           | 615 |

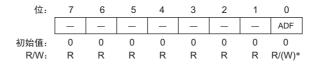

| 第 25 章 | 寄存器一览                                     | 616 |

| 25.1   | 寄存器地址一览 (地址顺序)                            | 617 |

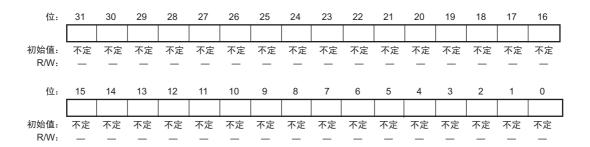

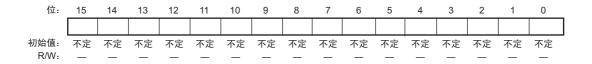

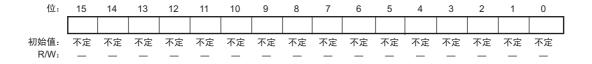

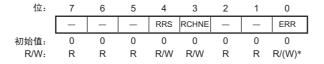

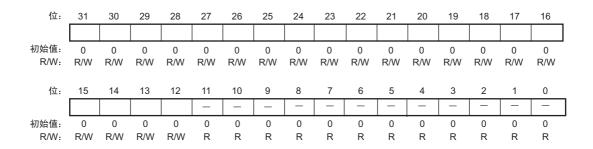

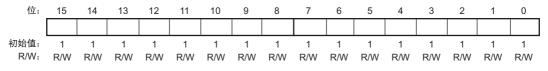

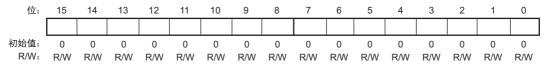

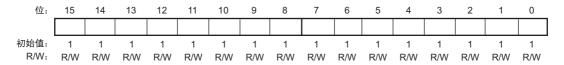

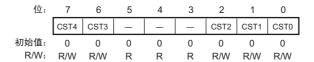

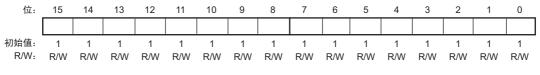

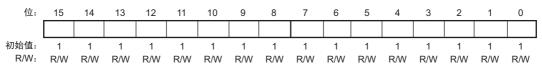

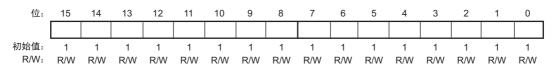

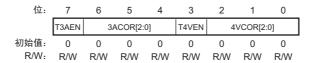

| 25.2   | 寄存器位一览                                    | 632 |

| 25.3   | 各运行模式的寄存器状态                               | 648 |

| 第 26 章 | 电特性                                       | 658 |

| 26.1   | 绝对最大额定值                                   | 658 |

| 26.2   | DC 特性                                     | 659 |

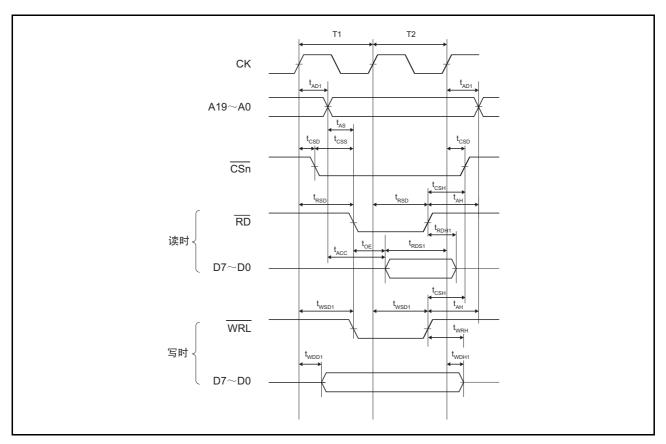

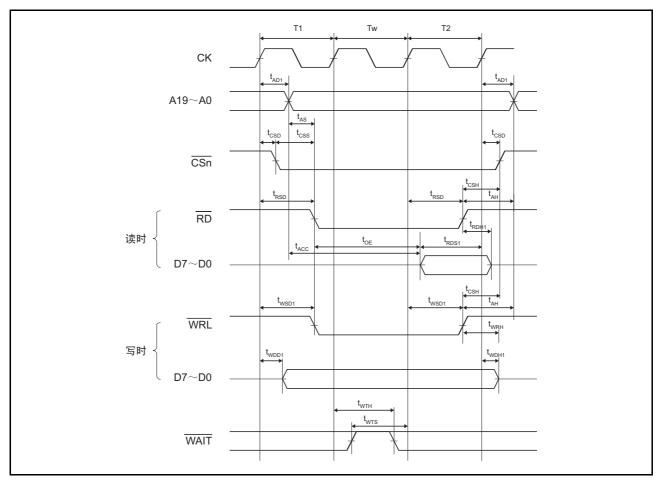

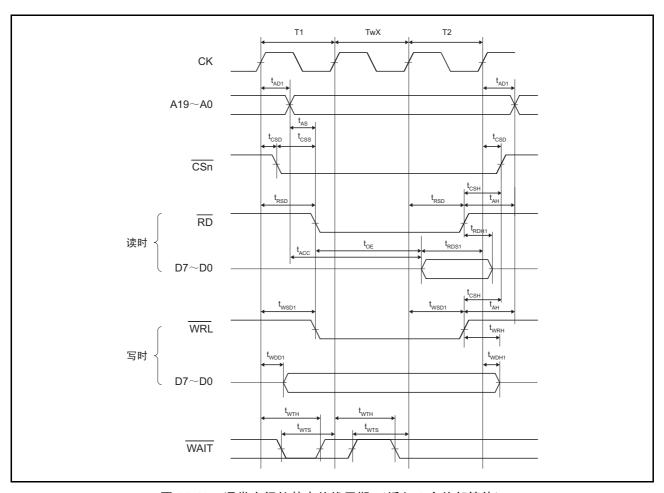

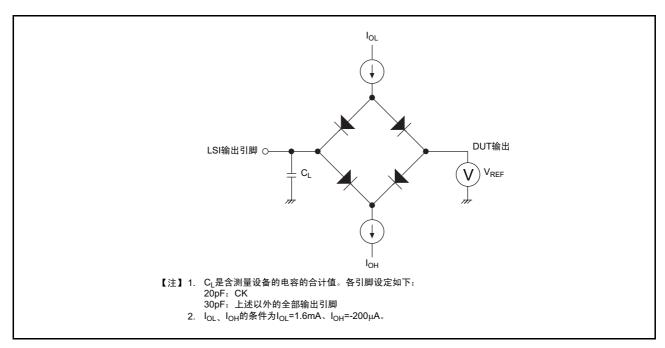

| 26.3   | AC 特性                                     | 663 |

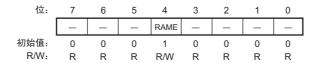

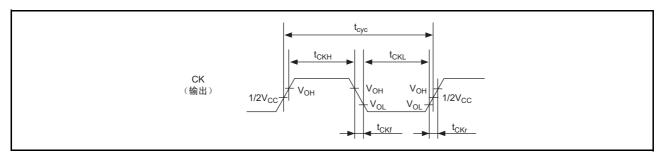

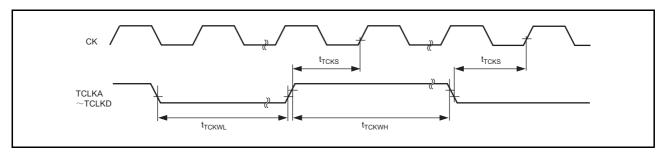

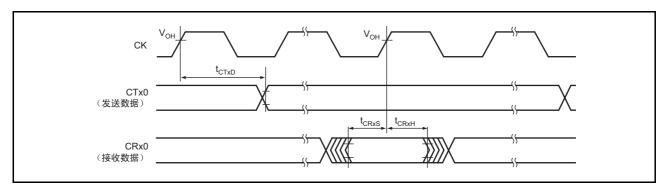

| 26.3.  | .1 时钟时序                                   | 663 |

| 26.3.  | * ****                                    |     |

| 26.3.  | = : ::: ::: ::: ::: ::: ::: : ::: : ::: : |     |

| 26.3.  |                                           |     |

| 26.3.  |                                           |     |

| 26.3.  |                                           |     |

| 26.3.  |                                           |     |

| 26.3.  |                                           |     |

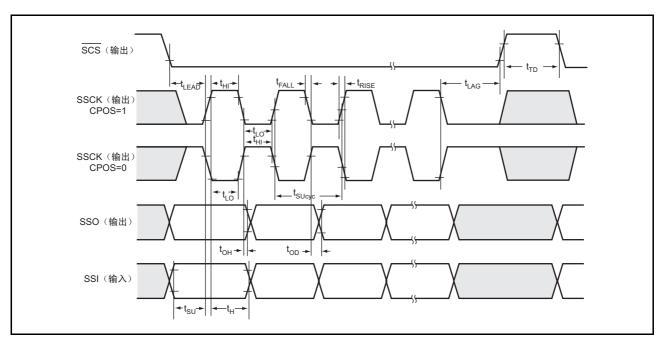

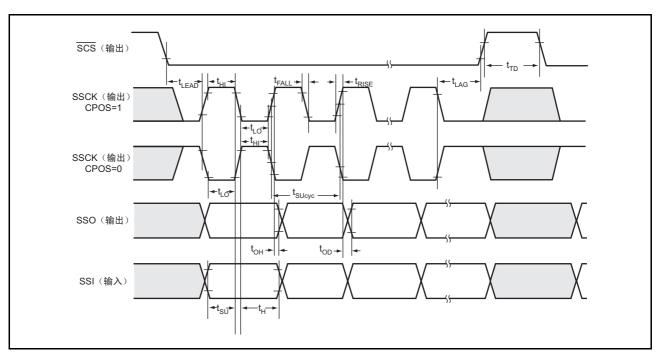

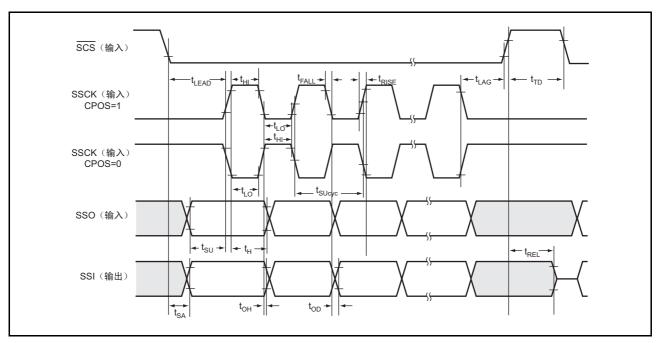

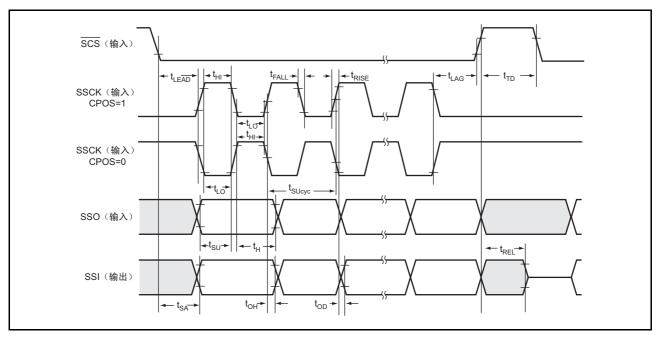

| 26.3.  | .9  串行通信单元 (SSU)的时序                       | 678 |

| 26.3.10 |                         | 68  |

|---------|-------------------------|-----|

| 26.3.11 |                         |     |

| 26.3.12 |                         |     |

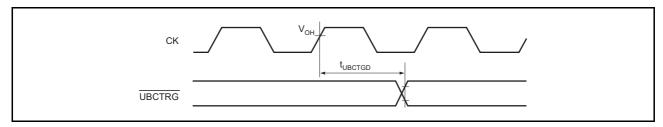

| 26.3.13 | 3 UBC 的触发时序             | 683 |

| 26.3.14 |                         |     |

| 26.3.15 |                         | 684 |

| 26.4 A  | /D 转换器特性                | 684 |

| 26.5 闪  | 存特性                     | 685 |

| 26.6 使  | [用时的注意事项                | 685 |

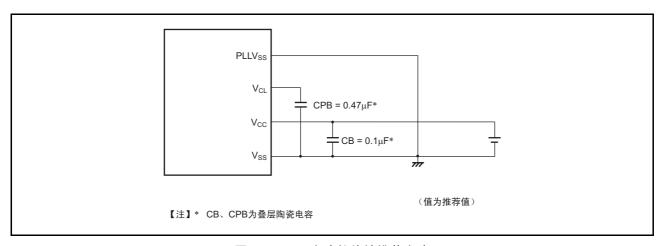

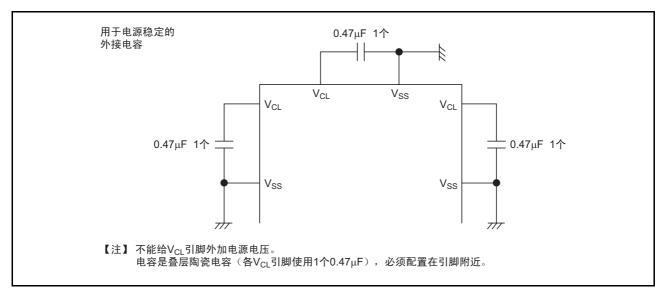

| 26.6.1  | V <sub>CL</sub> 电容的连接方法 | 685 |

| 附录      |                         | 686 |

| 附录 A.   | 引脚状态                    | 680 |

| 附录 B.   | 有关总线信号的引脚状态             | 690 |

| 附录 C.   | 型号一览                    | 69  |

| 附录 D.   | 封装尺寸图                   | 692 |

| 索引      |                         | 693 |

### 第1章 概要

#### 1.1 SH7136/SH7137 的特点

本 LSI 是以瑞萨科技的 RISC 方式 CPU 为内核,集聚了系统构成所需外围功能的 RISC 单片机。

本 LSI 的 CPU 有 RISC (Reduced Instruction Set Computer) 方式的指令系统,因为以 1 条指令 1 个状态 (1 个系统时钟周期)执行基本指令,所以飞跃性地提高了指令的执行速度。另外,采用了内部 32 位系统结构,增 强了数据处理能力。对于以往的单片机不能实现的高速性实时控制等应用系统,通过本 LSI 的 CPU 能构成低成 本、高性能和高功能的系统。

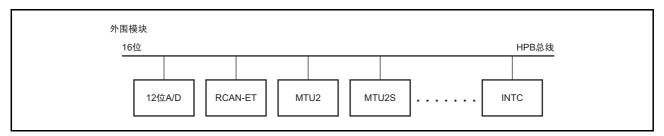

本 LSI 内置了大容量 ROM、 RAM、数据传送控制器 (DTC)、定时器、串行通信接口 (SCI)、同步串 行通信单元 (SSU)、A/D 转换器、中断控制器 (INTC)、I/O 端口、I<sup>2</sup>C 总线接口 2 (I<sup>2</sup>C2) 和控制器局域 网(RCAN-ET)等系统构成所需的外围功能。

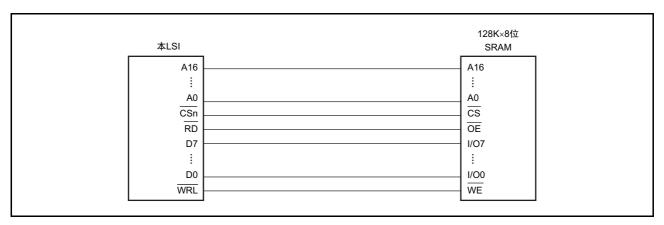

另外,本 LSI 通过外部存储器的存取支持功能,能直接连接存储器和外围 LSI (只限 SH7137),因此能大 幅度地降低系统成本。

内部 ROM 是内置闪存的 F-ZTAT<sup>TM</sup> (Flexible Zero Turn Around Time)版 \*。除了能使用支持本 LSI 的编 程器对闪存进行编程外,还能通过软件进行编程和擦除,因此用户能在 LSI 安装于电路板上的状态下进行改写。 本 LSI 的特点如表 1.1 所示。

【注】 \* F-ZTAT<sup>TM</sup> 是 (株) 瑞萨科技的商标。

SH7137 群 第1章 概要

## 表 1.1 SH7136/SH7137 的特点

| 项目            | 特点                                                                                                                                                                                                                                                                                                                                                   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU           | <ul> <li>32 位 RISC (Reduced Instruction Set Computer)方式 CPU</li> <li>指令长度:通过固定为 16 位来提高编码效率</li> <li>加载 / 存储体系结构 (在寄存器之间进行基本运算)</li> <li>通用寄存器: 32 位 ×16 个</li> <li>流水线: 5 段流水线方式</li> <li>内部乘法器:以 2 ~ 5 个周期进行 32×32→64 的乘法运算</li> <li>基本指令: 62 种面向 C 语言的指令系统</li> <li>【注】 必须注意: 槽非法指令的规格和传统的 SH-2 有所不同。详细内容请参照 "5.8.4 有关槽非法指令异常处理的注意事项"。</li> </ul> |

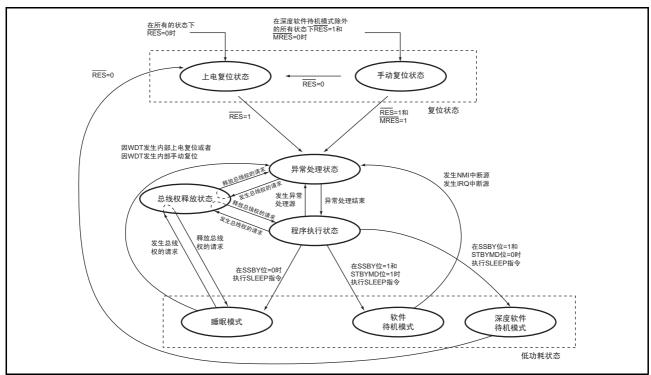

| 运行模式          | 运行模式     单芯片模式     扩展 ROM 有效模式 (只限 SH7137)     扩展 ROM 无效模式 (只限 SH7137)      处理状态     程序执行状态     异常处理状态     总线权释放状态 (只限 SH7137)      低功耗状态     睡眠模式     软件待机模式     深度软件待机模式     模块待机模式                                                                                                                                                                |

| 用户断点控制器(UBC)  | <ul><li>能将地址、数值、存取类型和数据长度全部作为断点条件进行设定</li><li>支持连续断点功能</li><li>2个断点通道</li></ul>                                                                                                                                                                                                                                                                      |

| 内部 ROM        | • 256K 字节                                                                                                                                                                                                                                                                                                                                            |

| 内部 RAM        | <ul><li>16K 字节</li></ul>                                                                                                                                                                                                                                                                                                                             |

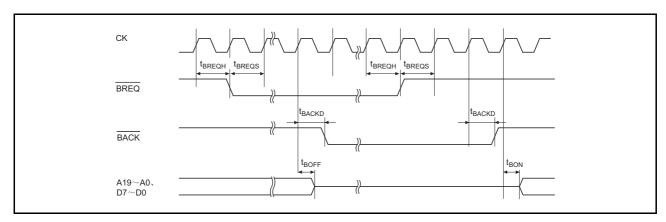

| 总线状态控制器(BSC)  | <ul> <li>分别支持最大 1M 字节的 2 个区域 (CS0 和 CS1) 的地址空间 (只限 SH7137)</li> <li>8 位外部总线 (只限 SH7137)</li> <li>各区域能独立设定以下功能:<br/>存取的等待周期数<br/>空闲等待周期的设定<br/>支持 SRAM</li> <li>将片选信号输出到对应的区域</li> </ul>                                                                                                                                                              |

| 数据传送控制器 (DTC) | <ul> <li>能通过外围 I/O 的中断请求进行独立于 CPU 的数据传送</li> <li>能按各中断源设定传送模式 (设定存储器中的传送模式)</li> <li>能对 1 个启动源进行多个数据的传送</li> <li>丰富的传送模式</li> <li>能选择正常模式 / 重复模式 / 块传送模式</li> <li>能将传送单位设定为字节 / 字 / 长字</li> <li>向 CPU 请求启动 DTC 的中断<br/>能在 1 次数据传送结束后向 CPU 产生中断<br/>能在指定的数据传送全部结束后向 CPU 产生中断</li> </ul>                                                               |

| 项目             | 特点                                                |

|----------------|---------------------------------------------------|

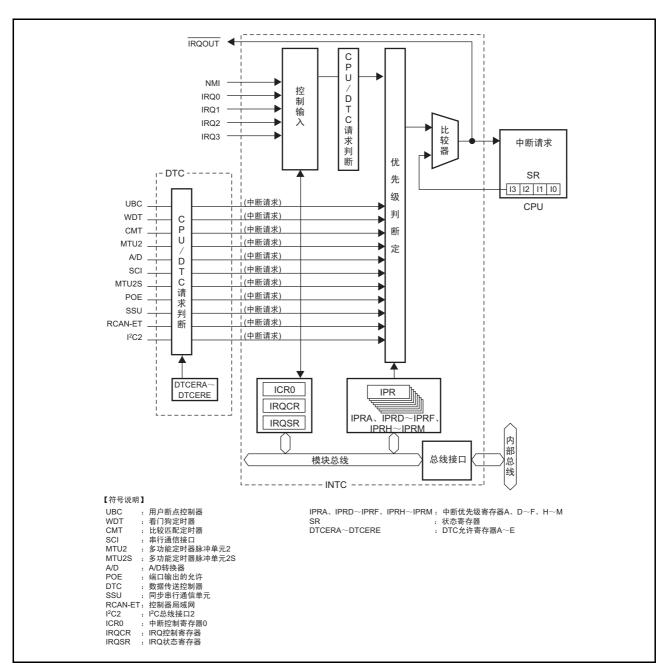

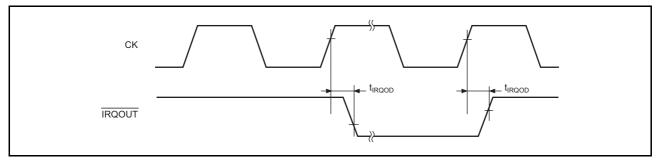

| 中断控制器 (INTC)   | • 5 个外部中断引脚 (NMI、IRQ3 ~ IRQ0)                     |

|                | • 内部外围中断:设定各模块的优先级                                |

|                | • 向量地址:各中断源固有的向量地址                                |

| 用户调试接口 (H-UDI) | ・ 支持 E10A 仿真器                                     |

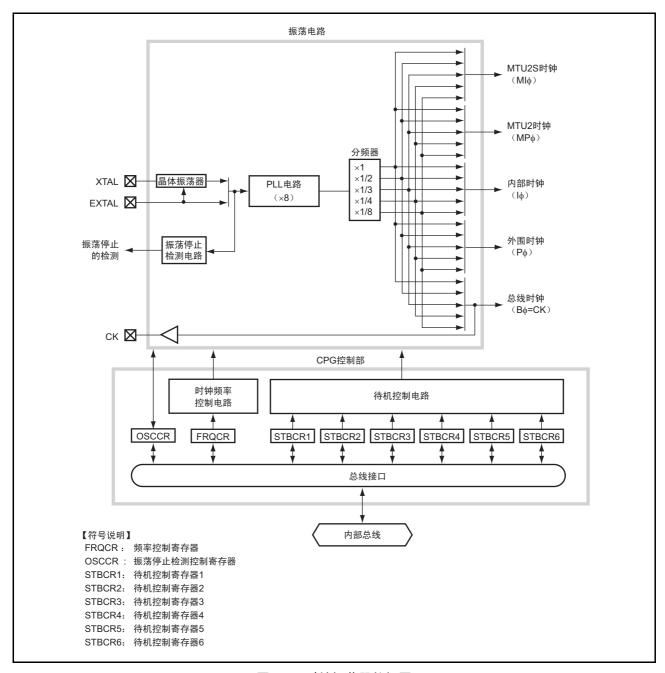

| 时钟振荡器 (CPG)    | • 时钟模式: 能选择外部输入或者晶体振荡器作为输入时钟                      |

|                | • 生成 5 种时钟                                        |

|                | CPU 时钟: 80MHz (Max.)                              |

|                | 总线时钟:40MHz (Max.)                                 |

|                | 外围时钟: 40MHz (Max.)                                |

|                | MTU2 专用时钟: 40MHz (Max.)                           |

|                | MTU2S 专用时钟: 80MHz (Max.)                          |

| 看门狗定时器 (WDT)   | • 1个通道的看门狗定时器                                     |

|                | • 能请求中断                                           |

| 多功能定时器脉冲单元 2   | • 以 6 个通道的 16 位定时器为基础,最多能输入 / 输出 16 种脉冲以及输入 3 个脉冲 |

| (MTU2)         | • 21 个输出比较匹配寄存器兼输入捕捉寄存器                           |

|                | • 共有 21 个独立的比较器                                   |

|                | • 能选择 8 种计数器输入时钟                                  |

|                | • 输入捕捉功能                                          |

|                | • 脉冲输出模式                                          |

|                | 交替 /PWM/ 互补 PWM/ 复位同步 PWM                         |

|                | • 多个计数器的同步功能                                      |

|                | • 互补 PWM 输出模式                                     |

|                | 输出用于控制 6 相反相器的非重叠波形                               |

|                | 自动设定空载时间                                          |

|                | 能在 $0\sim 100\%$ 范围内任意设定 PWM 占空比<br>输出 OFF 功能     |

|                | A/D 转换请求的延迟功能                                     |

|                | 空载时间的补偿功能                                         |

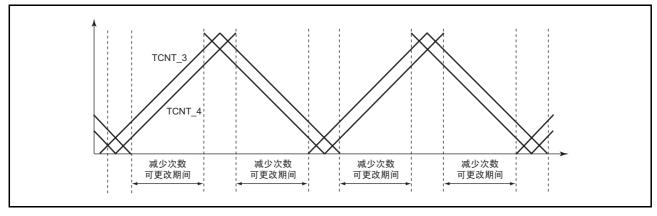

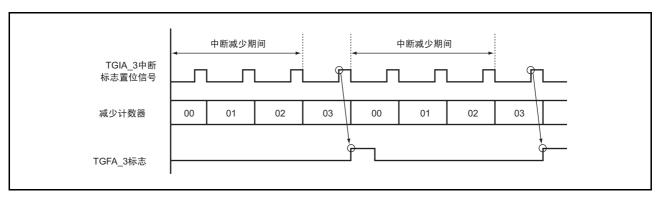

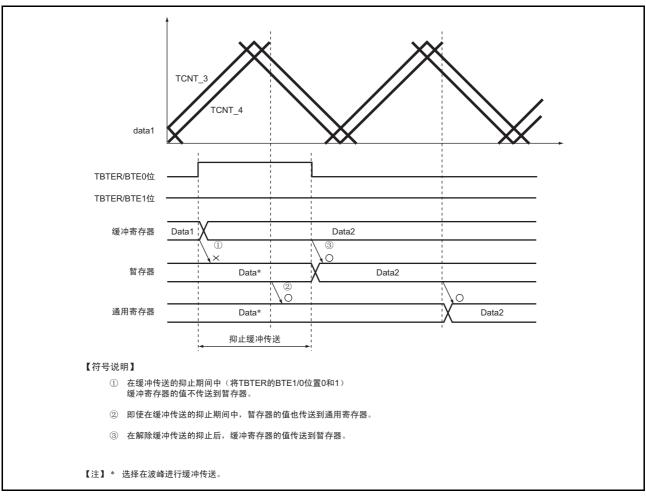

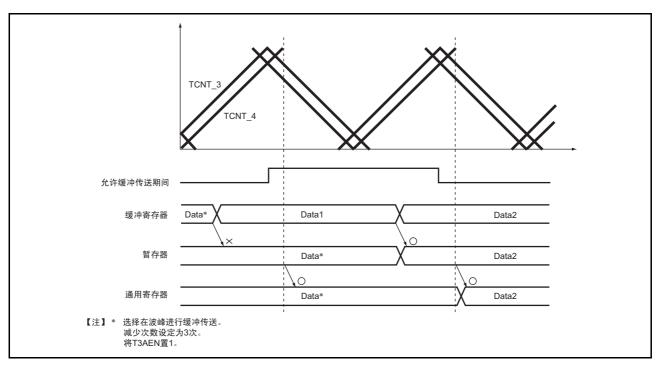

|                | 波峰 / 波谷的中断减少功能                                    |

|                | ・ 复位同步 PWM 模式                                     |

|                | 3 相输出任意占空比的正相 / 反相 PWM 波形                         |

|                | • 相位计数模式                                          |

|                | 能对 2 相编码器进行计数处理                                   |

| 多功能定时器脉冲单元 2S  | 只限 MTU2 的通道 3 、 4 、 5 的子集版                        |

| (MTU2S)        | • 最大工作频率为 80MHz                                   |

| 端口输出允许 (POE)   | MTU2/MTU2S 波形输出引脚的高阻抗控制                           |

| 比较匹配定时器 (CMT)  | • 16 位计数器                                         |

|                | • 产生比较匹配中断                                        |

|                | • 2个通道                                            |

| 串行通信接口 (SCI)   | • 时钟同步 / 异步模式                                     |

|                | • 3 个通道                                           |

| 项目                                          | 特点                                                                                      |

|---------------------------------------------|-----------------------------------------------------------------------------------------|

| 同步串行通信单元                                    | • 能选择主控模式 / 从属模式                                                                        |

| (SSU)                                       | • 能选择标准模式 / 双向模式                                                                        |

|                                             | • 能从 8/16/32 位中选择接收和发送数据的长度                                                             |

|                                             | • 能同时接收和发送 (全双工)                                                                        |

|                                             | • 能连续进行串行通信                                                                             |

|                                             | • 1 个通道                                                                                 |

| I <sup>2</sup> C 总线接口 2 (I <sup>2</sup> C2) | • 符合 Philips 公司提倡的 I <sup>2</sup> C 总线接口方式                                              |

|                                             | • 内置主控模式 / 从属模式                                                                         |

|                                             | • 能连续接收和发送                                                                              |

|                                             | • 能选择 I <sup>2</sup> C 总线格式 / 时钟同步串行格式                                                  |

|                                             | • 1 个通道                                                                                 |

| 控制器局域网 (RCAN-ET)                            | • CAN 版本:对应 Bosch 2.0B active                                                           |

|                                             | • 缓冲器个数:接收/发送×15个、接收专用×1个                                                               |

|                                             | • 1个通道                                                                                  |

| A/D 转换器 (ADC)                               | • SH7137: 12 位 ×16 个通道, SH7136: 12 位 ×12 个通道                                            |

|                                             | • 能通过外部触发或者 MTU2/MTU2S 请求转换                                                             |

|                                             | • 内置 3 个单元 ×2 组的采样和保持功能 (1 组能同时进行 3 个通道的采样)                                             |

| I/O 端口                                      | • SH7137: 57 个通用输入 / 输出引脚和 16 个通用输入引脚                                                   |

|                                             | SH7136: 44 个通用输入 / 输出引脚和 12 个通用输入引脚                                                     |

|                                             | • 能对输入/输出兼用端口按位进行输入/输出的转换                                                               |

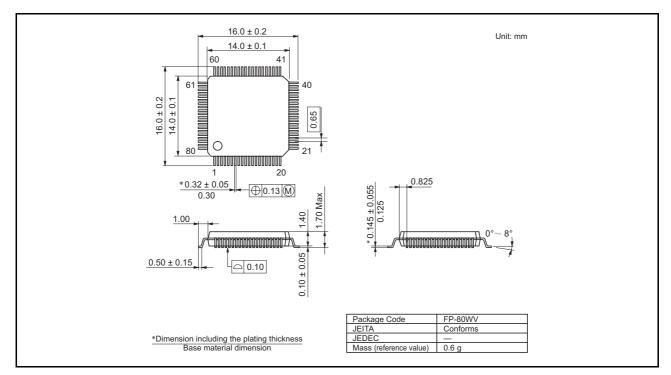

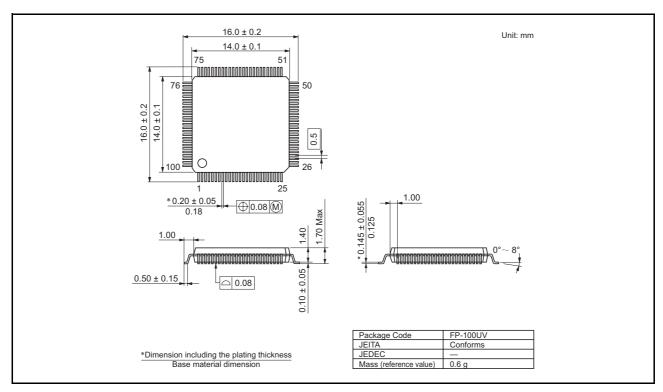

| 封装                                          | • SH7137: LQFP1414-100 (0.5 节距)                                                         |

|                                             | SH7136: LQFP1414-80 (0.65 节距)                                                           |

| 电源电压                                        | • V <sub>CC</sub> : $3.0\sim3.6$ V 或者 $4.0\sim5.5$ V, AV <sub>CC</sub> : $4.5\sim5.5$ V |

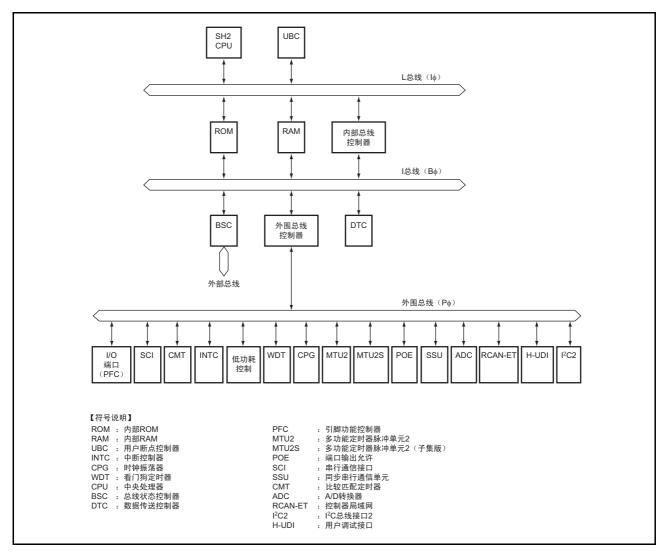

### 1.2 框图

SH7136/SH7137 的框图如图 1.1 所示。

图 1.1 框图

SH7137 群 第 1 章 概要

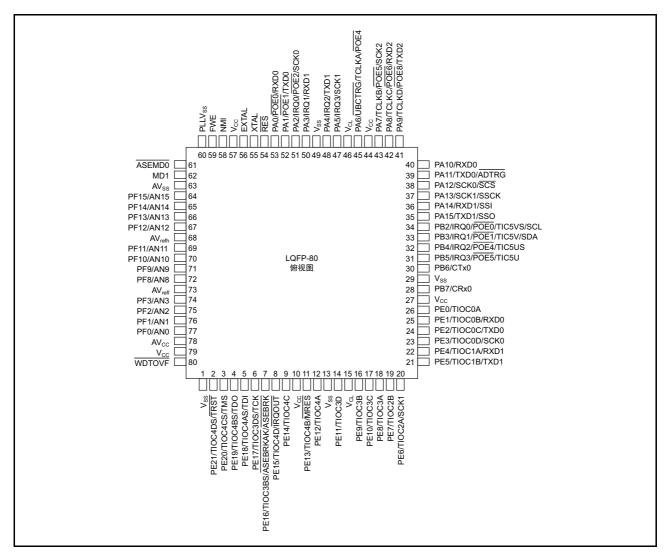

## 1.3 引脚排列图

图 1.2 SH7136 的引脚排列图

SH7137 群 第 1 章 概要

图 1.3 SH7137 的引脚排列图

SH7137 群 第1章 概要

### 引脚功能 1.4

各引脚的功能如表 1.2 所示。

表 1.2 引脚功能

| 分类     | 引脚名                          | 输入/输出 | 名称        | 功能                                                                      |

|--------|------------------------------|-------|-----------|-------------------------------------------------------------------------|

| 电源     | Vcc                          | 输入    | 电源        | 是电源引脚。必须将全部 V <sub>CC</sub> 引脚连接到系统电源。如果有开路引脚就不工作。                      |

|        | Vss                          | 输入    | 接地        | 是接地引脚。必须将全部 Vss 引脚连接到系统电源 (0V)。如果有开路引脚就不工作。                             |

|        | VcL                          | 输出    | 内部降压电源    | 是内部降压电源的外接电容引脚。必须通过 $0.47 \mu F$ 的电容将全部 $V_{CL}$ 引脚连接到 $V_{SS}$ (靠近引脚)。 |

| 时钟     | PLLVss                       | 输入    | PLL 接地    | 是内部 PLL 振荡器的接地引脚。                                                       |

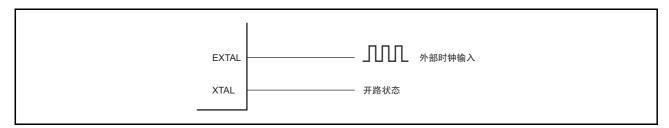

|        | EXTAL                        | 输入    | 外部时钟      | 连接晶体振荡器,也能输入外部时钟。                                                       |

|        | XTAL                         | 输出    | 晶体        | 连接晶体振荡器。                                                                |

|        | СК                           | 输出    | 系统时钟      | 给外部器件提供系统时钟。<br>SH7136 无此引脚。                                            |

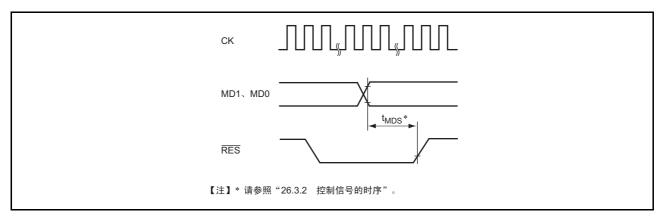

| 运行模式控制 | MD1、MD0                      | 输入    | 模式设定      | 设定运行模式。在运行中不能改变这些引脚的信号。<br>SH7136 只有 MD1。                               |

|        | FWE                          | 输入    | 闪存的编程允许   | 是闪存的引脚。能保护闪存的编程 / 擦除。                                                   |

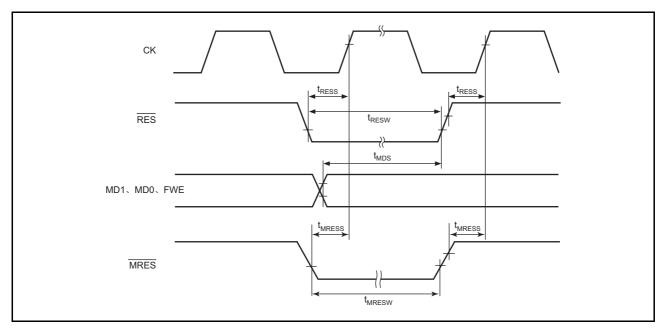

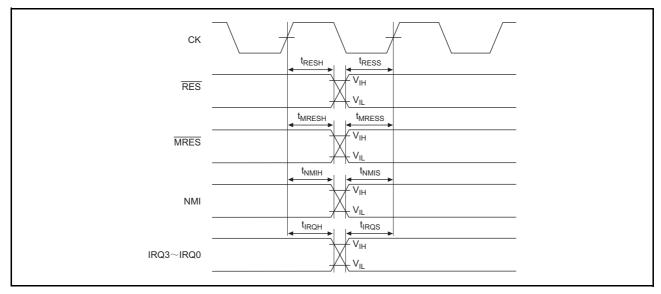

| 系统控制   | RES                          | 输入    | 上电复位      | 当此引脚为低电平时,进入上电复位状态。                                                     |

|        | MRES                         | 输入    | 手动复位      | 当此引脚为低电平时,进入手动复位状态。                                                     |

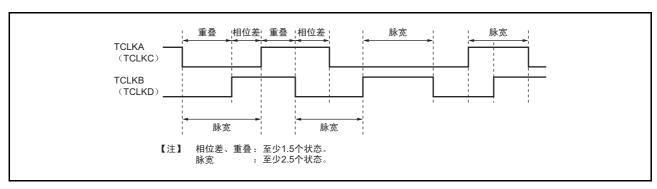

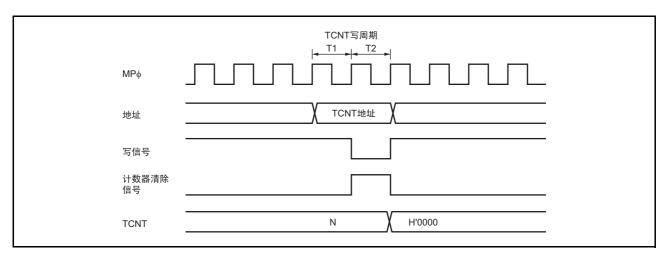

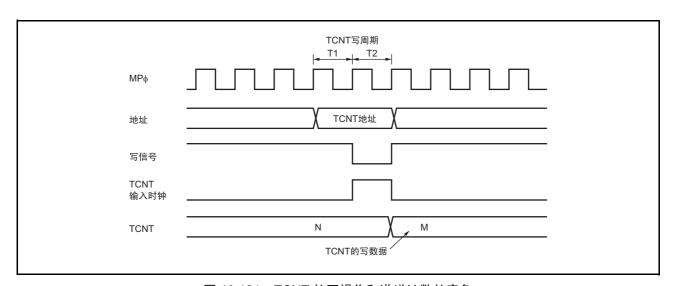

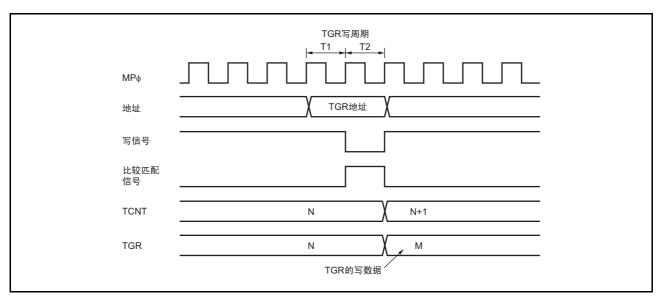

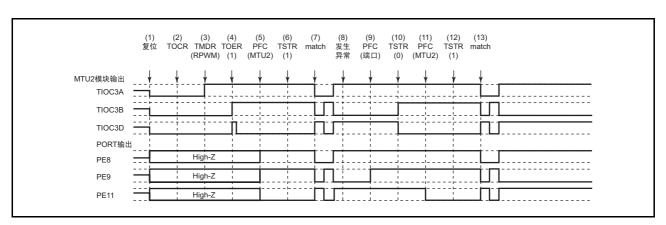

|        | WDTOVF                       | 输出    | 看门狗定时器的上溢 | 是 WDT 的上溢输出信号。<br>如果需要下拉,就必须使用至少 1MΩ 的电阻。                               |