#### Abstract

The world is full of choice, not least when it comes to choosing a Microcontroller for your next design. However do you choose an exact fit for the application but limited future expansion, CISC or RISC architecture, high performance, low power and not least, which of the ten or more manufacturers do you choose?

#### Introduction

This paper examines the merits of the world's number 1 MCU supplier, Renesas Electronics, RX microcontroller series providing the concept of *"one core"* across a range of products featuring common CPU core, instructions and many peripherals.

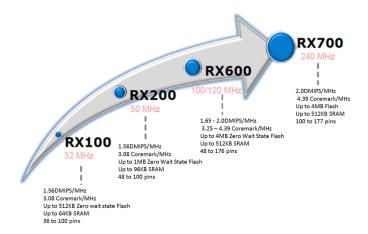

The current roadmap of products as at 2015 (figure 1 below) now includes four sub families ranging from the entry level RX100 up to the recently released high end RX700 providing the designer with "countless options" allowing flexibility and easy migration for future expansion and new designs.

#### Figure 1 – RX Family Roadmap

Each sub-family outlined above are based on the same innovative combination of RISC and CISC architecture producing an enhanced 32-bit Harvard CPU core designed to provide both the highest levels of performance and compact efficient code. A number of hardware units including multiply accumulator (MAC) and barrel shifter are included for integer and DSP operations across all products and with the RX600 and RX700 including a hardware IEEE-754 compliant Floating Point Unit (FPU) and extended instruction set provides fast precise operation. All RX family products include multiple instruction, data and dedicated peripheral busses maximising instruction and data throughput and peripheral performance, making the RX one of the highest performance and most efficient MCU families available. With the introduction of the 2nd generation RX CPU core (RXv2) available on later generations of the RX600 and the new RX700, while retaining instruction set compatibility with the 1st generation core (RXv1) provides 25% more calculation performance with reduced memory usage due to higher code efficiency.

A short description of each RX sub families is provided below together with a block diagram showing the functionality.

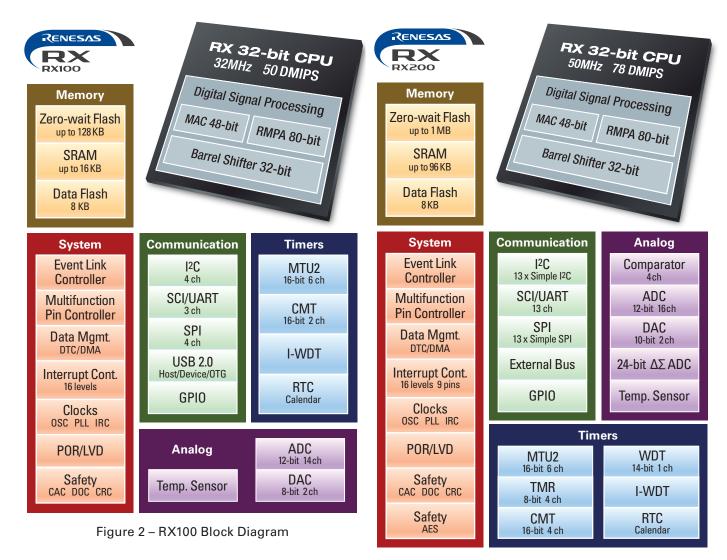

#### **RX100**

The RX100 is the latest RX family to be introduced as the entry level of the 32-bit RX MCU roadmap extending the portfolio to the low end of the spectrum with lower clock speed, less flash and SRAM memory and package sizes, with pin counts from 100 pins down to 32 pins. The RX100 family while considered as "entry level" the family still features a number of highly integrated products combining 32 MHz zero wait state flash up to 512 KB, 8 KB E2Data Flash and low power consumption of 100 µA/MHz over a voltage range of 1.8 V to 3.6 V, 350 nA standby current combined with fast wake up (standby) of only 4.8 µs. As well as the "normal" wide range of peripherals available additional functions have been added including USB (host OTG and charger), temperature sensor and timer functions supporting 3-phase motor control. Additional hardware and safety support such as data compare and CRC modules used to accelerate self-test operations as required by the IEC60730 appliance standard. The RX100 is targeted at home appliance, building automation and environmental sensor applications.

# RX200

The RX200 family is based on the same 32-bit RX CPU core as the RX100, delivers increased performance up to 50 MHz (zero wait state flash) and operates over a wider voltage range of 1.62 V to 5 V, while still providing low power consumption of 200  $\mu$ A/MHz and 900 nA in standby. The Rx200 features larger Flash up to 1 MB, SRAM (96 KB) memory and E2Data Flash. As can be seen from the block diagram the RX200 has a similar set of peripherals and operation as the RX100 with additional analogue functions (24-bit  $\Delta\Sigma$  ADC and analogue comparator), a second watchdog with independent clock and hardware security AES encoding are also included.

The RX200 is targeted at portable medical equipment, home appliances, domestic metering, industrial automation and sensor applications.

Figure 3 – RX200 Block Diagram

# RX600

The RX600 is a high performance highly integrated family with zero wait state on chip flash memory up to 120 MHz, with increased on chip Flash (4 MB), SRAM (512 KB) and E2Data Flash (64 KB) memory over the RX100 and 200. While offering higher performance the RX600 still maintains low power with 300  $\mu$ A/MHz operation and 1.4  $\mu$ A in standby. To improve calculation precision and performance the RX600 includes a hardware IEEE-754 floating point unit (FPU) as well as the compatible core functionality of the RX100 and RX200. An extended instruction set takes advantage of the FPU, but also maintains instruction compatibility with the other RX MCU families.

The RX600 maintains the core set of peripheral functions as seen in the previous RX families but now integrates many advanced interfaces (Ethernet, USB, CAN, Memory Card and Image Capture etc.) and additional security and safety modules as can be seen from the block diagram. The RX600 is targeted at motion control, graphics, connectivity and industrial automation.

| Memory                                                                                                             | RX 32-bit CPU (V2 Core)<br>120MHz 2000MIPS                                                                                                                           |                                                      |                                                 |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|

| Flash<br>up to 4 MB                                                                                                | Floating-Point Operation Unit                                                                                                                                        |                                                      |                                                 |

| SRAM<br>512 KB                                                                                                     | DSP Instructions<br>Register Indirect Multiply-and-Accumulate (Result: 80-bit)<br>Register Direct Multiply-and-Accumulate (Result: 48-bit)<br>Barrel Shifter: 32-bit |                                                      |                                                 |

| ECC RAM: 32 KB<br>Standby RAM: 8 KB                                                                                |                                                                                                                                                                      |                                                      |                                                 |

| Data Flash<br>64 KB                                                                                                |                                                                                                                                                                      |                                                      |                                                 |

| System                                                                                                             | Timers                                                                                                                                                               | Communication                                        | Encryption/Safety                               |

| Data Transfer<br>Controller,<br>ExDMA Controller x 2 ch                                                            | Multifunction Timer<br>Pulse Unit (MTU3)<br>16-bit: 8 ch                                                                                                             | Ethernet Controller: 2 ch                            | Encryption Modules<br>AES/DES/SHA/RNG           |

| DMA Controller x 8 ch                                                                                              | 32-bit: 1 ch<br>General PWM Timer                                                                                                                                    | IEEE 1588<br>Clock Synchronization                   | Memory Protection<br>Unit                       |

| Interrupt Control<br>16 levels, 16 pins                                                                            | (GPT)<br>16-bit: 4 ch                                                                                                                                                | Control<br>USB Full-Speed: 2 ch                      | Register Write<br>Protection Unit               |

| Clock Generation Circuit<br>PLL<br>High-Speed<br>On-Chip Oscillator<br>Power-On Reset<br>Voltage Detection Circuit | Timer Pulse Unit (TPU)<br>16-bit: 6 ch                                                                                                                               | CAN: 3 ch                                            | Clock Frequency Accuracy<br>Measurement Circuit |

|                                                                                                                    | Programmable Pulse<br>Generator (PPG)                                                                                                                                | I2C Bus Interface                                    | CRC Calculator                                  |

|                                                                                                                    | 8-bit Timer (TMR)                                                                                                                                                    | x 2 ch<br>Serial Communications<br>Interface x 13 ch | Data Operation Circuit                          |

| Event Link<br>Controller                                                                                           | 8-bit: 4 ch                                                                                                                                                          | (incl. 4 ch with FIFO)                               | Watchdog Timer<br>8-bit: 1 ch                   |

| Controller                                                                                                         | 16-bit Timer (CMT) x 2 ch<br>32-bit Timer (CMTW) x 1 ch                                                                                                              | Serial Peripheral<br>Interface                       | Independent<br>Watchdog Timer<br>14-bit: 1 ch   |

| Analog                                                                                                             | Real-Time Clock                                                                                                                                                      | Quad Serial<br>Peripheral Interface                  | Image Capture                                   |

| 12-bit A/D: 21 ch                                                                                                  | Calendar Function                                                                                                                                                    | SD Host<br>Interface                                 |                                                 |

| 12-bit A/D: 8 ch                                                                                                   |                                                                                                                                                                      | MMC Host<br>Interface                                | Capture Unit                                    |

| 12-bit DAC: 2 ch                                                                                                   |                                                                                                                                                                      | Serial Sound<br>Interface                            |                                                 |

| Temperature Sensor                                                                                                 |                                                                                                                                                                      |                                                      |                                                 |

Figure 4 – RX600 Block Diagram

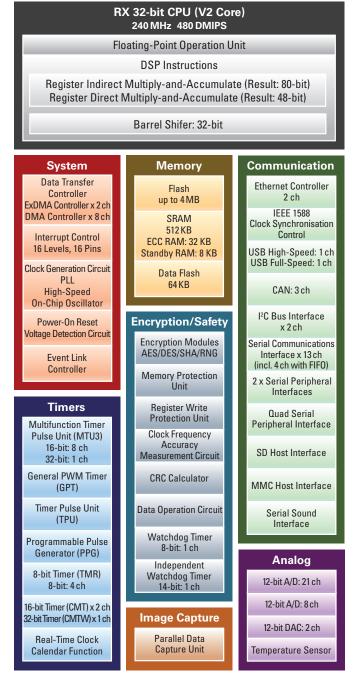

#### **RX700**

The RX700 is the latest family of high performance highly integrated products with large on chip Flash memory (4 MB) and increased operating frequency of 240 MHz. The family achieves low power consumption of only 200  $\mu$ A/MHz and standby currents as low as 600 nA.

As well as including the IEEE-754 FPU, the RX700 includes two high precision (72-bit) MAC units, with the extended instruction set maximising FPU and DSP operations, but still maintains core hardware and software compatibility with the RX100, RX200 and RX600 families.

As you might expect the RX700 still provides the fundamental peripheral functions compatibility from the other RX families and RX600, but has an increased number of advanced peripheral and security functions aimed at advanced communications, sound, safety and battery backup operation. The RX700 is targeted at motion control, graphics, connectivity and industrial automation applications.

Figure 5 – RX700 Block Diagram

### Compatibility

As can be seen from the outline descriptions and block diagrams above, the RX certainly meets the title criteria, "One Core – Countless Options", with a high degree of compatibility across the four families including many common peripheral functions. Maybe a question remains: *"How fully compatible are the four RX sub families cores?"* The table in figure 6 below details much of the key aspects of the CPU core architecture (registers, instructions speed etc.) highlighting the compatibilities between the families and the two core generations.

| Core Version                   | RXv1                                        | RXv2                                                                       |

|--------------------------------|---------------------------------------------|----------------------------------------------------------------------------|

| CPU Architecture               | 32-bit pipelined CISC, Harvard architecture |                                                                            |

| General-Purpose Registers      | 32-bit x 16ch                               | 32-bit x 16ch                                                              |

| Accumulators                   | 1 x 48-bit                                  | 2x 72-bit                                                                  |

| Pipeline                       | Five-stage                                  | Five stage with improved parallel execution                                |

| Instruction Fetch RX100, RX200 | 32-bits x 4                                 | -                                                                          |

| Instruction Fetch RX600        | 64-bits x 4                                 | 64-bits x 4                                                                |

| Instruction Fetch RX700        | -                                           | Advanced Fetch Unit (AFU), Instruction – 16 Bytes x 16, Data – 8 Bytes x 8 |

| Instruction Set RX100, RX200   | 82                                          | -                                                                          |

| Instruction Set RX600          | 82 + 8 FPU                                  | -                                                                          |

| Instruction Set RX600, RX700   | _                                           | 82 + 9 (FPU) + 19 new (109)                                                |

| DSP Instructions               | 9                                           | 9 + 14 new                                                                 |

| FPU                            | IEEE754 compliant Single Precision          |                                                                            |

| FPU RX100, RX200               | -                                           | -                                                                          |

| FPU RX600                      | 1                                           | -                                                                          |

| FPU RX600, RX700               | -                                           | 1                                                                          |

| Core Operating Frequency       | Up to 100 MHz                               | Up to 240 MHz (Current level)                                              |

| Compatibility (Core)           | RXv1                                        | RXv2 upwardly compatible from RXv1                                         |

| RX100/RX200 Core               | RXv1                                        | _                                                                          |

| RX600 Core                     | RXv1                                        | RXv2                                                                       |

| RX700 Core                     | -                                           | RXv2                                                                       |

Figure 6 – Compatibility comparisons

# **Development Tools**

Having considered the hardware and software commonality across the families, one area that cannot be ignored are the development and support tools. A key requirement of any range of MCU families is that there is a common platform of development tools and application or API software, so that migrating from one family to another is seamless. The RX families are no exception in that from the RX100 through to the RX700 all are supported by the same hardware and software tools and a common concept of promotion boards (RPB), starter kits (RSK) and solution kits covering applications such as motor control, graphics LCD and communications (Ethernet, CAN and USB etc.). Examples of the "kit" are shown in figure 7. Development tools range from Renesas own tools for code development, debugging and programming to state of the art third party tools from partners such as IAR and Segger as shown in figure 8 below.

Figure 8 - RX Development tools

In addition to the debugging/programming tools and compilers, Renesas also provide peripheral API driver libraries (Renesas Peripheral Driver Library (RPDL)) and IDE code generator plugins covering all RX product families. All Renesas kits include a complete hardware platform, full documentation, example or solution code (depending on the kit), IDE compiler (Renesas) such as e2studio and in many cases an E1 module for on chip debugging and programming.

Plus there are a vast range of third party partner support covering compilers, RTOS, middleware libraries and dedicated hardware platforms for complex applications including Wi-Fi, graphics, Java and advanced peripheral functions such as Ethernet, USB, and CAN etc. Like the Renesas products third party solution kits come complete with a full hardware platform together with application software libraries developed and tested for the RX.

#### Conclusion

The theme of this paper was to look at the Renesas RX microcontroller families and the compatibilities of each of the sub families. Compatibility is not only about the integration of the core and peripherals but also the ability to migrate application code easily from one family to another. This requires common peripherals and instruction set as well as the toolchain environment so that any family product can be developed using the same hardware and software tools. The availability of code generators and peripheral libraries greatly assists users especially where there are additional or new peripherals and when a designer moves to an unfamiliar product.

The Renesas RX lives up to the tag "One Core – Countless Options" providing a wide range of compatible products and tools allowing designers to future proof designs and protect software investment. Exactly what you would expect from the world's leading MCU supplier.

For further information on the RX families please visit our website and design resources centre.

Written by: David Parsons – Consultant to Renesas Electronics (Europe) GmbH David can be contacted at DCP Electronics and Software Services.

Before purchasing or using any Renesas Electronics products listed herein, please refer to the latest product manual and/or data sheet in advance.

Renesas Electronics Europe