# Datasheet

# RENESAS

# ISL78264

Automotive Dual Synchronous Buck Controller with Integrated Drivers

The <u>ISL78264</u> is a dual buck controller that can operate across a wide  $V_{IN}$  range of 3.75V to 42V. It is designed to support wide duty-cycle operation for switching frequencies from 200kHz up to 2.2MHz. To mitigate EMI, it supports synchronization to an external clock or programmable spread spectrum clocking. Its current-mode modulator is ideally suited to tolerate severe line transients. Also, the ISL78264 supports dropout operation and low 25ns on-time to operate through automotive cranking and load dump pulses.

The ISL78264 integrates robust MOSFET drivers and readily supports step-down applications requiring high output currents in normal operation. For applications that must also sustain extremely low power, always-on operation, its energy conservation mode can reduce operating current to  $6\mu$ A. Integrated feedback for VOUT1 is provided for 3.3V or 5V applications to eliminate the current otherwise flowing in external feedback resistors. An automatic switchover to an external supply is also supported to maximize efficiency. A blocking diode is activated after startup to prevent the external supply from back-biasing a low input voltage at VIN.

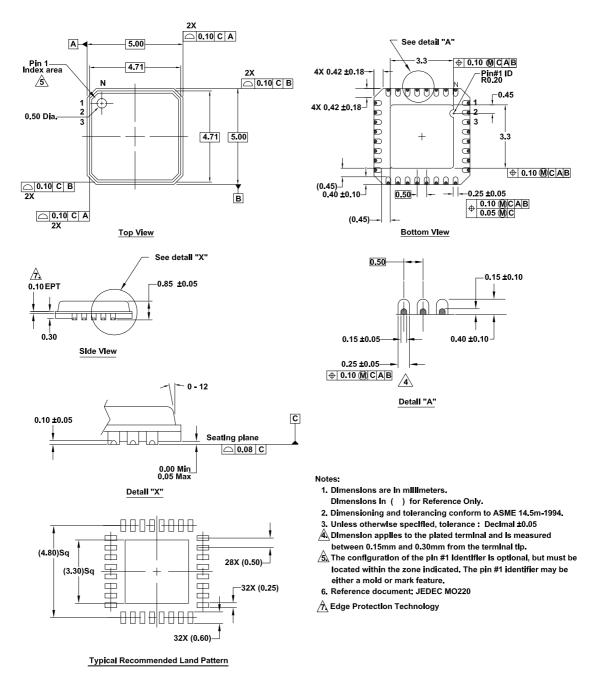

The ISL78264 is qualified to <u>AEC-Q100</u> Grade 1, specified to operate across an ambient temperature range of -40°C to 125°C, and is available in a 5mmx5mm, 32 Ld WFQFN (Wettable Flank) package.

## Features

- V<sub>IN</sub> operating range: 3.75V to 42V

- · Low quiescent current: 6µA typical, one channel

- Switching frequency: 200kHz to 2.2MHz

- Dropout mode for high duty-cycle operation

- 25ns on-times for low duty-cycle operation

- External synchronization

- Programmable spread spectrum clocking

- 180° phase shift between channels

- 2A Sourcing/3A sinking MOSFET drivers

- · Boot UVLO and programmable boot refresh time

- Extensive protection mechanisms for OV/UV/OC/OT

#### Table 1. Output Configurations

| VOUT1 Selection       | VOUT2 Selection        |

|-----------------------|------------------------|

| 3.3V                  | Adjustable 0.8V to 32V |

| 5.0V                  |                        |

| Adjustable 0.8V to 5V |                        |

# Applications

- Automotive 12V Systems

- Infotainment/Multimedia Systems

- · Cockpit safety systems

- Advanced Driver Assist Systems (ADAS)

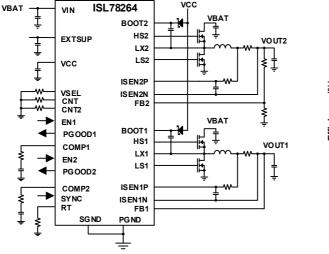

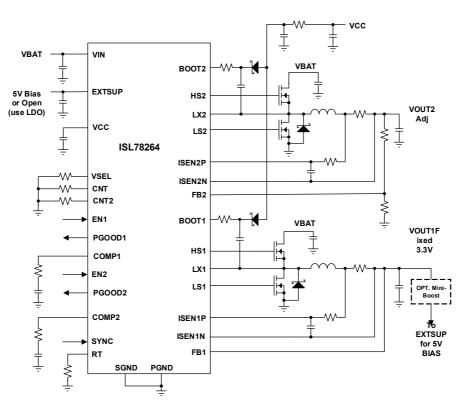

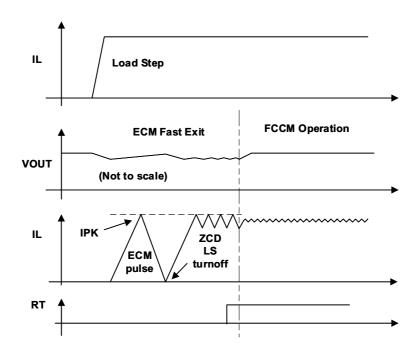

Figure 1. Typical Application Schematic

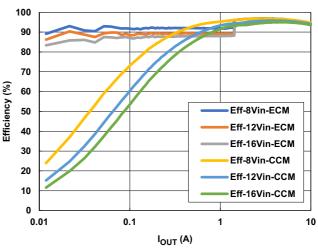

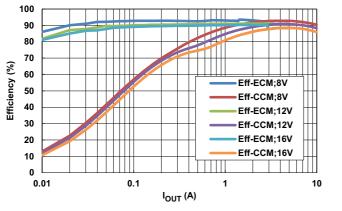

Figure 2. Buck 1 Efficiency VOUT1 = 5V at 400 kHz

# Contents

| 1.  | Overview                                          | 3  |

|-----|---------------------------------------------------|----|

| 1.1 | Typical Application Schematics                    | 3  |

| 1.2 | Block Diagram                                     | 5  |

| 1.3 | Ordering Information                              | 5  |

| 1.4 | Pin Configuration                                 | 6  |

| 1.5 | Pin Descriptions                                  | 6  |

| 2.  | Specifications                                    | 8  |

| 2.1 | Absolute Maximum Ratings                          | 8  |

| 2.2 | Thermal Information                               | 8  |

| 2.3 | Recommended Operation Conditions                  |    |

| 2.4 | Electrical Specifications                         | 9  |

| 3.  | Typical Performance Curves                        | 13 |

| 4.  | Functional Description                            | 17 |

| 4.1 | Functional Overview                               | 17 |

| 4.2 | Buck Stage (Converter 1)                          | 18 |

| 4.3 | Buck Stage (Converter 2)                          | 20 |

| 4.4 | Over-Temperature Shutdown                         | 21 |

| 4.5 | Energy Conservation Mode (ECM) 2                  | 21 |

| 5.  | Application Information.                          | 24 |

| 5.1 | Buck Converter                                    | 24 |

| 6.  | Control Loop Compensation for the Buck Regulators | 27 |

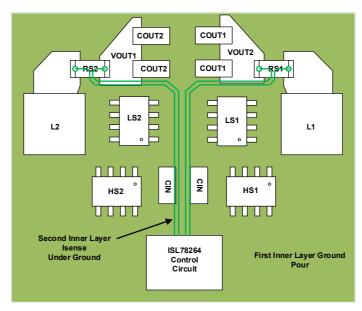

| 7.  | Recommended PCB Layout                            | 28 |

| 8.  | Revision History                                  | 30 |

| 9.  | Package Outline Drawing                           | 31 |

# 1. Overview

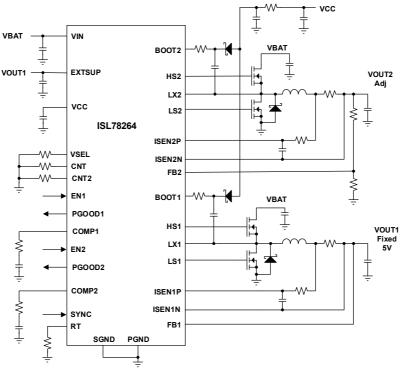

# 1.1 Typical Application Schematics

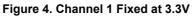

Figure 5. Both Channels Adjustable Output

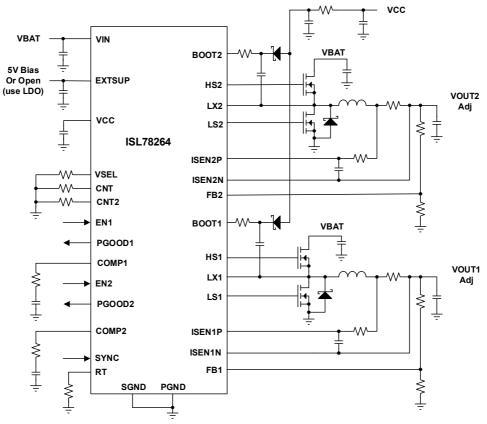

#### 1.2 Block Diagram

Figure 6. Block Diagram

## 1.3 Ordering Information

| Part Number<br>( <u>Notes 2, 3</u> ) | Part Marking     | Package<br>(RoHS Compliant) | Pkg. Dwg. # | Carrier Type<br>( <u>Note 1</u> ) | Temp Range (°C) |

|--------------------------------------|------------------|-----------------------------|-------------|-----------------------------------|-----------------|

| ISL78264ARZ                          | ISL7826 4ARZ     | 32 Ld 5x5 WFQFN             | L32.5x5H    | Tube                              | -40 to +125°C   |

| ISL78264ARZ-T                        |                  |                             |             | 6k                                |                 |

| ISL78264ARZ-T7A                      |                  |                             |             | 250                               |                 |

| ISL78264EVAL1Z                       | Evaluation Board |                             |             |                                   |                 |

#### Notes:

1. See <u>TB347</u> for details about reel specifications.

2. These Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu-Ag plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

3. For Moisture Sensitivity Level (MSL), see the ISL78264 device page. For more information about MSL see TB363.

|          | 5         |           | •                               |                        |

|----------|-----------|-----------|---------------------------------|------------------------|

| Part #   | Channel 1 | Channel 2 | Channel 1 Output Range          | Channel 2 Output Range |

| ISL78263 | Buck      | Boost     | 3.3V, 5V, 0.8V to 5V Adjustable | 5V to 40V Adjustable   |

| ISL78264 | Buck      | Buck      | 3.3V, 5V, 0.8V to 5V Adjustable | 0.8V to 32V Adjustable |

#### Table 2. Key Differences Between Family of Parts

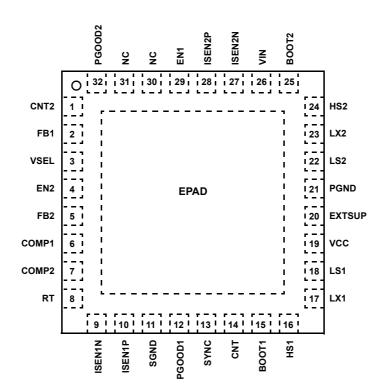

# 1.4 Pin Configuration

#### 32 Ld, 5x5 WFQFN

# 1.5 Pin Descriptions

| Pin # | Pin Names | Description                                                                                                                                                                                                                                                                               |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CNT2      | This pin sources a current at startup and reads the voltage across a resistor to ground to program internal boot refresh on-time of the low-side switch for 180ns or 360ns (see <u>Table 5 on page 18</u> ).                                                                              |

| 2     | FB1       | Feedback pin for Channel 1 buck. For fixed output voltages of 5.0V or 3.3V, this pin is connected directly to the output of Channel 1 buck. For an adjustable output, this pin connects to a resistive divider from Channel 1 output to ground, and the FB1 voltage is regulated to 0.8V. |

| 3     | VSEL      | This pin sources a current at startup and reads the voltage across a resistor to ground to program the Channel 1 buck output to a fixed voltage of 5.0V or 3.3 V, or as an adjustable voltage in the range of 0.8V to 5.0V (see <u>Table 3 on page 17</u> ).                              |

| 4     | EN2       | Enable control pin of Channel 2 with a logic high voltage enabling operation of Channel 2.                                                                                                                                                                                                |

| 5     | FB2       | Feedback pin for Channel 2 buck regulator with adjustable output. This pin connects to a resistive divider from Channel 2 output to ground, and the FB2 voltage is regulated to 0.8V.                                                                                                     |

| 6     | COMP1     | Loop compensation pin for Channel 1 with a resistor/capacitor network connected to ground to provide control loop compensation for Channel 1 buck regulator.                                                                                                                              |

| 7     | COMP2     | Loop compensation pin for Channel 2 with a resistor/capacitor network connected to ground to provide control loop compensation for Channel 2 buck regulator.                                                                                                                              |

| Pin #  | Pin Names                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

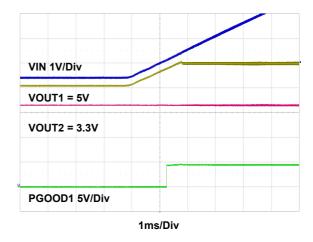

| 8      | RT                                                                                                                                                                                                                                    | A resistor from RT to GND programs the buck switching frequency for Channel 1 and Channel 2, with Channel 2 shifted 180° in phase from Channel 1 to minimize input ripple current. This pin is pulled to ground while in ECM and is otherwise 0.5V.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9      | ISEN1N                                                                                                                                                                                                                                | Output current sense pin connected to the negative terminal of the current sense resistor, also connected to the output voltage of Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10     | ISEN1P                                                                                                                                                                                                                                | Output current sense pin connected to the junction of the positive terminal of the current sense resistor and the power inductor of Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11     | SGND                                                                                                                                                                                                                                  | Analog GND for the IC, connect to the PGND pin in the top copper trace under the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12     | PGOOD1 Power-good pin for Channel 1 with an open-drain output, producing a low output if the Channel 1 output is not v<br>±7% (typical) of the programmed output voltage, and a logic high output if the output is within regulation. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13     | SYNC                                                                                                                                                                                                                                  | Connect SYNC to an external clock in the range of 200kHz to 2.4MHz to synchronize the internal clock with operation<br>in FCCM.<br>Connect to VCC to force the part into Fixed frequency Continuous Conduction Mode (FCCM) operation using the<br>internal oscillator.<br>Connect to GND to allow the controller to automatically switch between Continuous Conduction Mode, and Diode<br>Emulation Mode (DEM), or ECM mode depending on load current level. In DEM and CCM, the device uses the internal<br>oscillator programmed by RT pin. The pin can be switched during operation (VCC to GND, or GND to VCC) to change<br>the mode of operation. |

| 14     | CNT                                                                                                                                                                                                                                   | This pin sources a current at startup and reads the voltage across a resistor to ground to program the spread spectrum (ON/OFF, and frequency variation) and dead time (see <u>Table 4 on page 17</u> ).                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15     | BOOT1                                                                                                                                                                                                                                 | Provides connection point for a ceramic boot capacitor providing high-side gate voltage supply for Channel 1. The capacitor is charged through an external diode connected to VCC through an R-C filter.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16     | HS1                                                                                                                                                                                                                                   | The output of Channel 1 high-side MOSFET gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 17     | LX1                                                                                                                                                                                                                                   | Connected to the Channel 1 switch node, providing the return path for the high-side MOSFET gate driver back to BOOT1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18     | LS1                                                                                                                                                                                                                                   | The output of Channel 1 low-side MOSFET gate driver swinging between VCC and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19     | VCC                                                                                                                                                                                                                                   | Bias supply (5V typical) for the IC and MOSFET gate drivers, and should be decoupled with a ceramic capacitor of 10µF. This pin is supplied by internal LDO during start-up and can be powered from EXTSUP after initial start-up, using the automatic switchover function.                                                                                                                                                                                                                                                                                                                                                                            |

| 20     | EXTSUP                                                                                                                                                                                                                                | Accepts external bias input of 5V typical that can be supplied from Channel 1 or Channel 2 output of 5V, or an independent supply derived from other sources. If the external bias is applied before VIN is applied then the startup enable circuit should be powered from the external bias source (and not VIN).                                                                                                                                                                                                                                                                                                                                     |

| 21     | PGND                                                                                                                                                                                                                                  | Connection point for power ground of the switching circuits for Channel 1 and Channel 2, and serves as the return path for the low-side MOSFET gate drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22     | LS2                                                                                                                                                                                                                                   | The output of Channel 2 low-side MOSFET gate driver swinging between VCC and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23     | LX2                                                                                                                                                                                                                                   | Connected to the Channel 2 switch node, providing the return path for the high-side MOSFET gate driver back to BOOT2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24     | HS2                                                                                                                                                                                                                                   | The output of Channel 2 high-side MOSFET gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 25     | BOOT2                                                                                                                                                                                                                                 | Provides connection point for a ceramic boot capacitor providing high-side gate voltage supply for Channel 2. The capacitor is charged through an external diode connected to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 26     | VIN                                                                                                                                                                                                                                   | Connected to the high voltage input supply for the buck regulators, and is normally supplied from a battery. This pin is decoupled using a 0.1µF or larger ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 27     | ISEN2N                                                                                                                                                                                                                                | Output current sense pin connected to the negative terminal of the current sense resistor, also connected to the output voltage of Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 28     | ISEN2P                                                                                                                                                                                                                                | Output current sense pin connected to the junction of the positive terminal of the current sense resistor and the power inductor of Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 29     | EN1                                                                                                                                                                                                                                   | Enable control pin of Channel 1 with a logic high voltage enabling operation of Channel 1. For the initial start-up, this pin can be connected to the VIN supply through a $100k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 30, 31 | NC                                                                                                                                                                                                                                    | Not internally connected; leave unconnected or tie to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 32     | PGOOD2                                                                                                                                                                                                                                | Power-good pin for Channel 2 with an open-drain output, producing a low output if the Channel 2 output is not within $\pm 7\%$ (typical) of the programmed output voltage, and a logic high output if the output is within regulation.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|        | EPAD                                                                                                                                                                                                                                  | The bottom pad of the IC, to be connected to PGND and SGND under the IC. Connect to internal PCB GND layers using multiple vias.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

RENESAS

# 2. Specifications

# 2.1 Absolute Maximum Ratings

| Parameter                                            | Minimum | Maximum | Unit |

|------------------------------------------------------|---------|---------|------|

| VIN, EN1, FB2, ISEN2N and ISEN2P                     | -0.3    | 45      | V    |

| HS1, HS2, LX1, LX2, BOOT1, BOOT2                     | -0.3    | 65      | V    |

| EN2, FB1,COMP1, COMP2, PGOOD1, PGOOD2, CNT, RT, SYNC | -0.3    | 6.5     | V    |

| ISEN1N and ISEN1P, LS1, LS2, VCC, EXTSUP, VSEL, CNT2 | -0.3    | 6.5     | V    |

| All Other Pins                                       | -0.3    | 6.5     | V    |

| ESD Rating                                           | Va      | lue     | Unit |

| Human Body Model (Tested per AEC-Q100-002)           | :       | 2       | kV   |

| Charged Device Model (Tested per AEC-Q100-001)       | 7       | 50      | V    |

| Latch-Up (Tested per AEC-Q100-004)                   | 1       | 00      | mA   |

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

# 2.2 Thermal Information

| Thermal Resistance (Typical)                          | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------------------------------|------------------------|------------------------|

| 32 Ld 5x5 WFQFN Package ( <u>Notes 4</u> , <u>5</u> ) | 30                     | 1.2                    |

#### Notes:

4. θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See <u>TB379</u>.

5. For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                         | Minimum | Maximum          | Unit |

|-----------------------------------|---------|------------------|------|

| Maximum Junction Temperature      |         | +150             | °C   |

| Maximum Storage Temperature Range | -65     | +150             | °C   |

| Pb-Free Reflow Profile            |         | see <u>TB493</u> |      |

#### 2.3 Recommended Operation Conditions

| Parameter                                                          | Minimum | Maximum | Unit |

|--------------------------------------------------------------------|---------|---------|------|

| Ambient Temperature Range                                          | -40     | +125    | °C   |

| Start-Up Voltage Range V <sub>IN</sub>                             | 6.0     | 42      | V    |

| Supply Voltage Range V <sub>IN</sub> (EXTSUP ≥4.2V after start-up) | 3.75    | 42      | V    |

| Buck CH1 V <sub>OUT</sub> Fixed options                            | 3.3     | 5.0     | V    |

| Buck CH1 V <sub>OUT</sub> Adjustable Range                         | 0.8     | 5       | V    |

| Buck CH2 V <sub>OUT</sub> Adjustable Range                         | 0.8     | 32      | V    |

# 2.4 Electrical Specifications

$V_{IN}$  = 12V,  $T_A$  = +25°C. Boldface limits apply across the operating temperature range, -40°C to +125°C and input voltage range (4.5V to 42V) unless specified otherwise.

| Parameter                                                                   | Symbol                | Test Conditions                                                                                                      | Min<br>( <u>Note 6</u> ) | Typ<br>( <u>Note 7</u> ) | Max<br>( <u>Note 6</u> ) | Unit |

|-----------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| Power Supply                                                                |                       |                                                                                                                      |                          |                          | -                        |      |

| V <sub>IN</sub> Undervoltage Lockout Threshold                              | V <sub>IN,UVLO</sub>  | Rising                                                                                                               | 5.455                    | 5.650                    | 5.845                    | V    |

| V <sub>IN</sub> Supply Current in Low Power<br>Mode                         | I <sub>QLPM</sub>     | ECM mode, no external load on V <sub>OUT</sub> ( <u>Note 8</u> )                                                     |                          | 6                        |                          | μA   |

| V <sub>IN</sub> Supply Current During Normal<br>Switching (includes EXTSUP) | Ι <sub>Q</sub>        | PWM mode, no external load on V <sub>OUT,</sub><br>EN1 = EN2 = HIGH, f <sub>SW</sub> = 2.2MHz, gate drive<br>no load |                          | 11                       | 25                       | mA   |

| V <sub>IN</sub> Supply Current, Shutdown                                    | I <sub>SD</sub>       | EN1 = EN2 = SGND                                                                                                     |                          | 0.3                      | 6                        | μA   |

| LDO and EXTSUP                                                              |                       |                                                                                                                      |                          |                          |                          |      |

| Output Voltage of Internal LDO                                              | V <sub>VCC</sub>      | V <sub>IN</sub> = 6.0V to 42V, I <sub>OUT</sub> = 130mA                                                              | 4.75                     | 5                        | 5.25                     | V    |

| Output Current of Internal Regulator                                        | I <sub>VCC</sub>      | V <sub>IN</sub> = 6.0V to 42V                                                                                        |                          |                          | 0.13                     | Α    |

| Dropout Voltage of Internal Regulator                                       | D <sub>VCC</sub>      | V <sub>IN</sub> = 4.5V, I <sub>LDO</sub> = 130mA                                                                     |                          |                          | 1                        | V    |

| LDO Current Limit                                                           | I <sub>LMTLDO</sub>   | V <sub>CC</sub> = 4.5V                                                                                               | 130                      |                          | 250                      | mA   |

| LDO Current Limit                                                           | I <sub>LMTLDO</sub>   | V <sub>CC</sub> = 0V                                                                                                 | 130                      |                          | 250                      | mA   |

| VCC Undervoltage Lockout Threshold                                          | V <sub>CC,UVLO</sub>  | Falling                                                                                                              | 3.8                      | 4.0                      | 4.1                      | V    |

| External Bias Voltage                                                       | V <sub>EXTSUP</sub>   | For $V_{OUT}$ buck = 5V ±5%                                                                                          | 4.75                     | 5                        | 5.25                     | V    |

| External Bias Voltage Switchover                                            | VTH <sub>EXTSUP</sub> | Rising                                                                                                               | 4.462                    | 4.6                      | 4.738                    | V    |

| Threshold                                                                   | _                     | Falling                                                                                                              | 4.268                    | 4.4                      | 4.532                    | V    |

|                                                                             |                       | Hysteresis                                                                                                           | 0.15                     | 0.2                      | 0.25                     | V    |

| Oscillator, Spread Spectrum                                                 |                       |                                                                                                                      |                          |                          |                          |      |

| Internal Switching Frequency                                                | f <sub>SW</sub>       | RT to GND resistor = $86.6k\Omega$                                                                                   | 0.18                     | 0.2                      | 0.22                     | MHz  |

| Internal Switching Frequency                                                | f <sub>SW</sub>       | RT to GND resistor = $6.81k\Omega$                                                                                   | 2.0                      | 2.2                      | 2.4                      | MHz  |

| External Switching Frequency                                                | f <sub>SW</sub>       | Applied to SYNC pin                                                                                                  | 0.2                      |                          | 2.4                      | MHz  |

| RT Pin Voltage                                                              | V <sub>RT</sub>       |                                                                                                                      |                          | 0.5                      |                          | V    |

| Spread Spectrum Narrow Mode                                                 | F <sub>SSNAR</sub>    | Spread Spectrum ON narrow mode, see CNT configuration <u>Table 4 on page 17</u>                                      |                          | +6                       |                          | %    |

| Spread Spectrum Wide Mode                                                   | F <sub>SSWID</sub>    | Spread Spectrum ON wide mode, see CNT configuration <u>Table 4 on page 17</u>                                        |                          | +12                      |                          | %    |

| Controller 1 Specification (Buck)                                           | l                     | •                                                                                                                    |                          | •                        | I                        |      |

| Output Voltage                                                              | V <sub>OUTCH1</sub>   | VSEL to GND resistor = $6.04k\Omega$ , see VSEL configuration <u>Table 3 on page 17</u>                              | 3.2505                   | 3.3                      | 3.3495                   | V    |

| Output Voltage                                                              | V <sub>OUTCH1</sub>   | VSEL to GND resistor = $75k\Omega$ , see VSEL configuration <u>Table 3 on page 17</u>                                | 4.925                    | 5.0                      | 5.075                    | V    |

| FB1 Pin Voltage Regulation (Adjustable)                                     | V <sub>FBCH1ADJ</sub> | VSEL to GND resistor = 37.4kΩ, see VSEL configuration <u>Table 3 on page 17</u>                                      | 0.788                    | 0.8                      | 0.812                    | V    |

| V <sub>OUT</sub> Comparator Threshold at ECM                                | V <sub>FBCH1</sub>    | V <sub>OUT</sub> = 3.3V                                                                                              | 3.234                    | 3.3                      | 3.366                    | V    |

|                                                                             | V <sub>FBCH1</sub>    | V <sub>OUT</sub> = 5.0V                                                                                              | 4.9                      | 5.0                      | 5.1                      | V    |

|                                                                             | V <sub>FBCH1ECM</sub> | V <sub>FB</sub> = 0.8V in adjustable VOUT mode                                                                       | 0.784                    | 0.80                     | 0.816                    | V    |

| FB Pin Leakage Current                                                      | I <sub>FBCH1</sub>    |                                                                                                                      |                          |                          | 0.25                     | μA   |

| Forward CH1 Cycle-by-Cycle Current<br>Limit                                 | I <sub>LMT1CH1+</sub> |                                                                                                                      | 64                       | 80                       | 100                      | mV   |

| Forward CH1 Hiccup Current Limit                                            | I <sub>LMT2CH1+</sub> |                                                                                                                      | 80                       | 100                      | 124                      | mV   |

| V <sub>IN</sub> = 12V, T <sub>A</sub> = +25°C. Boldface limits apply across the operating temperature range, -40°C to +125°C and input voltage range |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| (4.5V to 42V) unless specified otherwise. (Continued)                                                                                                |

| Parameter                                   | Symbol                 | Test Conditions                                                                 | Min<br>( <u>Note 6</u> ) | Typ<br>( <u>Note 7</u> ) | Max<br>( <u>Note 6</u> ) | Unit                                         |

|---------------------------------------------|------------------------|---------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|----------------------------------------------|

| Reverse CH1 Current Limit                   | I <sub>LMTCH1-</sub>   |                                                                                 | -50                      | -40                      | -33                      | mV                                           |

| CH1 Zero Cross                              | I <sub>ZCDCH1</sub>    |                                                                                 | -4                       | 2                        | 9                        | mV                                           |

| CH1 Dead Time                               | T <sub>DTLH1S</sub>    | Low-side low to high-side high, see CNT configuration <u>Table 4 on page 17</u> | 15                       | 27                       | 40                       | ns                                           |

|                                             | T <sub>DTHL1S</sub>    | High-side low to low-side high, see CNT configuration <u>Table 4 on page 17</u> | 30                       | 43                       | 70                       | ns                                           |

|                                             | T <sub>DTLH1L</sub>    | Low-side low to high-side high, see CNT configuration <u>Table 4 on page 17</u> | 70                       | 100                      | 120                      | ns                                           |

|                                             | T <sub>DTHL1L</sub>    | High-side low to low-side high, see CNT configuration <u>Table 4 on page 17</u> | 70                       | 100                      | 120                      | ns                                           |

| CH1 Max Duty                                | T <sub>DTMAXCH1</sub>  | V <sub>IN</sub> = 4.5V                                                          | 97                       | 98.75                    |                          | %                                            |

| CH1 Min ON Time                             | T <sub>ONMINCH1</sub>  |                                                                                 | 15                       | 25                       | 35                       | ns                                           |

| CH1 Min OFF Time                            | T <sub>OFFMINCH1</sub> |                                                                                 | 30                       | 40                       | 55                       | ns                                           |

| CH1 Soft-Start Time                         | T <sub>SSCH1</sub>     |                                                                                 |                          | 4.5                      |                          | ms                                           |

| CH1 Buck Error Amp (OTA) GM                 | CH1 <sub>EAOTA</sub>   |                                                                                 |                          | 1.7                      |                          | mS                                           |

| Boot Refresh                                | V <sub>BRFRESH</sub>   | Rising                                                                          | 3.3                      | 3.5                      | 3.7                      | V                                            |

|                                             |                        | Falling                                                                         | 3.2                      | 3.4                      | 3.6                      | V                                            |

|                                             |                        | Hysteresis                                                                      | 0.04                     | 0.08                     | 0.160                    | V                                            |

| CH1 Overvoltage Protection                  | CH1 <sub>OVP</sub>     | Rising                                                                          | 105                      | 107                      | 109                      | %                                            |

|                                             |                        | Falling                                                                         | 103                      | 105                      | 107                      | %                                            |

|                                             |                        | Hysteresis                                                                      | 1.5                      | 2.2                      | 3                        | %                                            |

| CH1 Undervoltage Protection                 | CH1 <sub>UVP</sub>     | Rising                                                                          | 93                       | 95                       | 97                       | %                                            |

|                                             |                        | Falling                                                                         | 91                       | 93                       | 95                       | %                                            |

|                                             |                        | Hysteresis                                                                      | 1.5                      | 2.2                      | 3                        | %                                            |

| V <sub>IN</sub> Pulse Skip Threshold        | VTH <sub>PSKIP</sub>   | Rising                                                                          | 18                       | 18.6                     | 19.5                     | V                                            |

|                                             |                        | Falling                                                                         | 17.7                     | 18.2                     | 18.7                     | V                                            |

|                                             |                        | Hysteresis                                                                      | 0.4                      | 0.55                     | 0.7                      | V                                            |

| ECM Entry Threshold                         | VTH <sub>ECMENT</sub>  | Rising VIN                                                                      | 5.6                      | 5.7                      | 5.85                     | V                                            |

|                                             |                        | Falling VIN                                                                     | 5.3                      | 5.4                      | 5.55                     | V                                            |

|                                             |                        | Hysteresis                                                                      | 0.2                      | 0.27                     | 0.35                     | V                                            |

| Controller 2 Specification (Buck)           |                        |                                                                                 |                          |                          |                          | <u>.                                    </u> |

| FB2 Pin Voltage Regulation                  | V <sub>FBCH2</sub>     |                                                                                 | 0.788                    | 0.8                      | 0.812                    | V                                            |

| FB2 Pin Leakage Current                     | I <sub>FBCH2</sub>     |                                                                                 |                          |                          | 0.25                     | μA                                           |

| Forward CH2 Cycle-by-Cycle Current<br>Limit | I <sub>LMT1CH2+</sub>  |                                                                                 | 64                       | 80                       | 100                      | mV                                           |

| Forward CH2 Hiccup Current Limit            | I <sub>LMT2CH2+</sub>  |                                                                                 | 80                       | 100                      | 124                      | mV                                           |

| Reverse CH2 Current Limit                   | I <sub>LMTCH2-</sub>   |                                                                                 | -50                      | -40                      | -33                      | mV                                           |

| CH2 Zero Cross                              | I <sub>ZCDCH2</sub>    |                                                                                 | -4                       | 2                        | 9                        | mV                                           |

| Parameter                              | Symbol                 | Test Conditions                                                                      | Min<br>( <u>Note 6</u> ) | Typ<br>( <u>Note 7</u> ) | Max<br>( <u>Note 6</u> ) | Unit |

|----------------------------------------|------------------------|--------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| CH2 Dead Time                          | T <sub>DTLH2S</sub>    | Low-side low to high-side high, see CNT configuration Table 4 on page 17             | 15                       | 27                       | 40                       | ns   |

|                                        | T <sub>DTHL2S</sub>    | High-side low to low-side high, see CNT configuration <u>Table 4 on page 17</u>      | 30                       | 43                       | 70                       | ns   |

|                                        | T <sub>DTLH2L</sub>    | Low-side low to high-side high, see CNT configuration <u>Table 4 on page 17</u>      | 70                       | 100                      | 120                      | ns   |

|                                        | T <sub>DTHL2L</sub>    | High-side low to low-side high, see CNT configuration <u>Table 4 on page 17</u>      | 70                       | 100                      | 120                      | ns   |

| CH2 Maximum Duty                       | T <sub>DTMAXCH2</sub>  |                                                                                      | 97                       | 98.75                    |                          | %    |

| CH2 Minimum ON Time                    | T <sub>ONMINCH2</sub>  |                                                                                      | 15                       | 25                       | 35                       | ns   |

| CH2 Minimum OFF Time                   | T <sub>OFFMINCH2</sub> |                                                                                      | 30                       | 40                       | 55                       | ns   |

| CH2 Soft-Start Time                    | T <sub>SSCH2</sub>     |                                                                                      |                          | 4.5                      |                          | ms   |

| Buck Error Amp (OTA) GM                | CH2EA <sub>OTA</sub>   |                                                                                      |                          | 1.7                      |                          | mS   |

| Boot Refresh                           | V <sub>BRFRESH</sub>   | Rising                                                                               | 3.3                      | 3.5                      | 3.7                      | V    |

|                                        |                        | Falling                                                                              | 3.2                      | 3.4                      | 3.6                      | V    |

|                                        |                        | Hysteresis                                                                           | 0.04                     | 0.1                      | 0.16                     | V    |

| CH2 Overvoltage Protection             | CH2 <sub>OVP</sub>     | Rising                                                                               | 105                      | 107                      | 109                      | %    |

|                                        |                        | Falling                                                                              | 103                      | 105                      | 107                      | %    |

|                                        |                        | Hysteresis                                                                           | 1.5                      | 2.2                      | 3                        | %    |

| CH2 Undervoltage Protection            | CH2 <sub>UVP</sub>     | Rising                                                                               | 93                       | 95                       | 97                       | %    |

|                                        |                        | Falling                                                                              | 91                       | 93                       | 95                       | %    |

|                                        |                        | Hysteresis                                                                           | 1.5                      | 2.2                      | 3                        | %    |

| V <sub>IN</sub> Pulse Skip Threshold   | VTH <sub>PSKIP</sub>   | Rising                                                                               | 18                       | 18.6                     | 19.5                     | V    |

|                                        |                        | Falling                                                                              | 17.7                     | 18.2                     | 18.7                     | V    |

|                                        |                        | Hysteresis                                                                           | 0.4                      | 0.55                     | 0.7                      | V    |

| ECM Entry Threshold                    | VTH <sub>ECMENT</sub>  | Rising V <sub>IN</sub>                                                               | 5.6                      | 5.7                      | 5.85                     | V    |

|                                        |                        | Falling V <sub>IN</sub>                                                              | 5.3                      | 5.4                      | 5.55                     | V    |

|                                        |                        | Hysteresis                                                                           | 0.2                      | 0.27                     | 0.35                     | V    |

| Output Drivers                         |                        |                                                                                      |                          |                          |                          | 1    |

| High-Side Drive Source Current         | I <sub>HS,SRC</sub>    | V <sub>HS</sub> - V <sub>LX</sub> = 2.5V, V <sub>BOOT</sub> - V <sub>LX</sub> = 4.4V |                          | 2                        |                          | Α    |

| High-Side Drive Source Resistance      | R <sub>HS,SRC</sub>    | 100mA source current, V <sub>BOOT</sub> - V <sub>LX</sub> = 4.4V                     |                          | 1.2                      |                          | Ω    |

| High-Side Drive Sink Current           | I <sub>HS,SNK</sub>    | V <sub>HS</sub> - V <sub>LX</sub> = 2.5V, V <sub>BOOT</sub> - V <sub>LX</sub> = 4.4V |                          | 2                        |                          | Α    |

| Hide-Side Drive Source Resistance      | R <sub>HS,SNK</sub>    | 100mA sink current, V <sub>BOOT</sub> - V <sub>LX</sub> = 4.4V                       |                          | 0.6                      |                          | Ω    |

| Low-Side Drive Source Current          | I <sub>LS,SRC</sub>    | V <sub>LS</sub> - V <sub>PGND</sub> = 2.5V, VCC = 5V                                 |                          | 2                        | ·                        | Α    |

| Low-Side Drive Source Resistance       | R <sub>LS,SRC</sub>    | 100mA source current, VCC = 5V                                                       |                          | 1.2                      |                          | Ω    |

| Low-Side Drive Sink Current            | I <sub>LS,SNK</sub>    | V <sub>LS</sub> - V <sub>PGND</sub> = 2.5V, VCC = 5V                                 |                          | 3                        | ·                        | Α    |

| Low-Side Drive Sink Resistance         | R <sub>LS,SNK</sub>    | 100mA sink current, VCC = 5V                                                         |                          | 0.55                     | ·                        | Ω    |

| Input Pins                             | ,                      | 1                                                                                    | 1                        | I                        |                          | 1    |

| ENABLE Input Low Voltage Threshold     | VIL <sub>EN1</sub>     | EN1 = CH1) = buck turned OFF; CH2 can be<br>ON/OFF                                   | 0.4                      | 1.0                      |                          | V    |

| ENABLE Input High Voltage<br>Threshold | VIH <sub>EN1</sub>     | EN1 = CH1 = buck turned ON; CH2 can be<br>ON/OFF                                     |                          | 1.2                      | 1.4                      | V    |

# $V_{IN}$ = 12V, $T_A$ = +25°C. Boldface limits apply across the operating temperature range, -40°C to +125°C and input voltage range (4.5V to 42V) unless specified otherwise. (Continued)

| Parameter                              | Symbol                | Test Conditions                                   | Min<br>( <u>Note 6</u> ) | Typ<br>( <u>Note 7</u> ) | Max<br>( <u>Note 6</u> ) | Unit |

|----------------------------------------|-----------------------|---------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| ENABLE Leakage Current                 | ILK <sub>EN1</sub>    |                                                   | -0.5                     |                          | 0.5                      | μA   |

| ENABLE Input Low Voltage Threshold     | VIL <sub>EN2</sub>    | EN2 = CH2 = buck turned OFF; CH1 can be<br>ON/OFF | 0.4                      | 1.0                      |                          | V    |

| ENABLE Input High Voltage<br>Threshold | VIH <sub>EN2</sub>    | EN2 = CH2 = buck turned ON; CH1 can be<br>ON/OFF  |                          | 1.2                      | 1.4                      | V    |

| ENABLE Leakage Current                 | ILK <sub>EN2</sub>    |                                                   | -0.5                     |                          | 0.5                      | μA   |

| SYNC Input Low Voltage                 | VIL <sub>SYNC</sub>   |                                                   |                          |                          | 0.3xVCC                  | V    |

| SYNC Input High Voltage                | VIH <sub>SYNC</sub>   |                                                   | 0.7xVCC                  |                          |                          | V    |

| SYNC Pulse Width High                  | T <sub>SYNCMINH</sub> |                                                   | 50                       |                          |                          | ns   |

| SYNC Pulse Width Low                   | T <sub>SYNCMINL</sub> |                                                   | 50                       |                          |                          | ns   |

| Switching Frequency SYNC Range         | F <sub>SYNC</sub>     |                                                   | 0.2                      |                          | 2.2                      | MHz  |

| CNT/CNT2/VSEL Level 0 Voltage          | V <sub>0</sub>        |                                                   |                          |                          | 35                       | mV   |

| CNT/CNT2/VSEL Level 1 Voltage          | V <sub>1</sub>        |                                                   | 75                       |                          | 180                      | mV   |

| CNT/CNT2/VSEL Level 2 Voltage          | V <sub>2</sub>        |                                                   | 225                      |                          | 360                      | mV   |

| CNT/CNT2/VSEL Level 3 Voltage          | V <sub>3</sub>        |                                                   | 415                      |                          | 560                      | mV   |

| CNT/CNT2/VSEL Level 4 Voltage          | V <sub>4</sub>        |                                                   | 615                      |                          | 870                      | mV   |

| CNT/CNT2/VSEL Level 5 Voltage          | V <sub>5</sub>        |                                                   | 940                      |                          | 1240                     | mV   |

| CNT/CNT2/VSEL Level 6 Voltage          | V <sub>6</sub>        |                                                   | 1.33                     |                          | 1680                     | V    |

| CNT/CNT2/VSEL Level 7 Voltage          | V <sub>7</sub>        |                                                   | 1.78                     |                          | vcc                      | V    |

| Output Pins                            |                       | •                                                 |                          |                          |                          |      |

| PGOOD1 Pin Voltage                     | VOL <sub>PGOOD1</sub> | V <sub>OUT1</sub> = OFF; sink current = 3mA       | -                        | 0.3                      | 0.6                      | V    |

| PGOOD2 Pin Voltage                     | VOL <sub>PGOOD2</sub> | V <sub>OUT2</sub> = OFF; sink current = 3mA       | -                        | 0.3                      | 0.6                      | V    |

| PGOOD1 Pin Leakage Current             | ILK <sub>PGOOD1</sub> | V <sub>PULLUP</sub> = 5V                          |                          | 0.01                     | 1                        | μΑ   |

| PGOOD2 Pin Leakage Current             | ILK <sub>PGOOD2</sub> | V <sub>PULLUP</sub> = 5V                          |                          | 0.01                     | 1                        | μA   |

| PGOOD1 Pin Filter Delay                | T <sub>PGOOD1</sub>   |                                                   | 10                       | 15                       | 20                       | μs   |

| PGOOD2 Pin Filter Delay                | T <sub>PGOOD2</sub>   |                                                   | 10                       | 15                       | 20                       | μs   |

| Thermal Shutdown                       | T <sub>OTP</sub>      | Rising                                            |                          | 160                      |                          | °C   |

|                                        |                       | Falling                                           |                          | 145                      |                          | °C   |

|                                        | 1                     | Hysteresis                                        |                          | 15                       |                          | °C   |

$V_{IN}$  = 12V,  $T_A$  = +25°C. Boldface limits apply across the operating temperature range, -40°C to +125°C and input voltage range (4.5V to 42V) unless specified otherwise. (Continued)

#### Notes:

6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

7. Typical values are for  $T_{A}$  = +25°C and  $V_{IN}$  = 12V.

8. Quiescent current measurements are taken when the output is not switching.

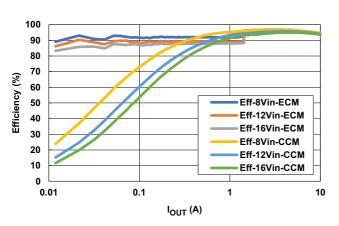

# 3. Typical Performance Curves

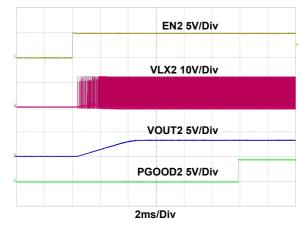

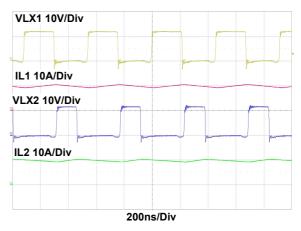

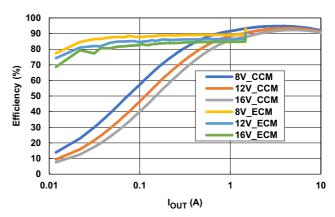

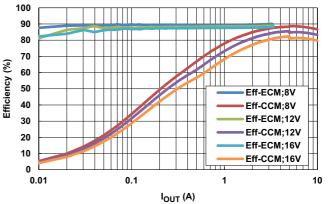

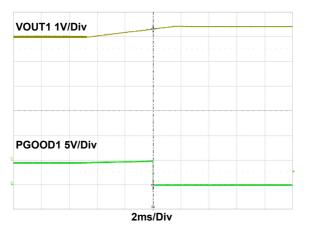

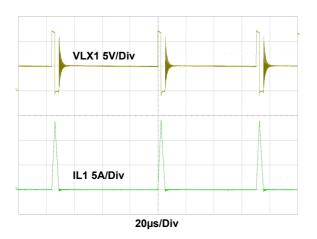

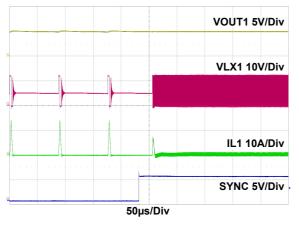

Unless otherwise noted, operating conditions are:  $T_A = +25^{\circ}C$ ,  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$

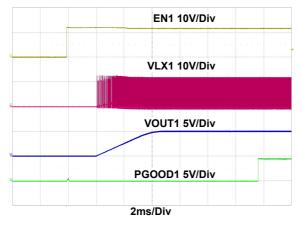

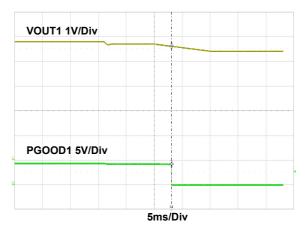

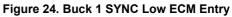

Figure 7. Buck 1 Start-Up with 10 A Load

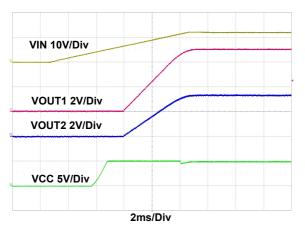

Figure 9. Buck 1/2 Start-Up with  $V_{\rm IN}$  Rising

Figure 11. Buck 1 Efficiency VOUT1 = 5V at 400 kHz

Figure 8. Buck 2 Start-Up with 10 A Load

Figure 10. Buck 1/2 with 180 degree Phase Shift)

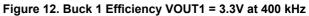

Unless otherwise noted, operating conditions are:  $T_A$  = +25°C,  $V_{IN}$  = 12V,  $V_{OUT1}$  = 5V,  $V_{OUT2}$  = 3.3V (Continued)

Figure 13. Buck 1 Efficiency VOUT1 = 5V at 2.2MHz

Figure 14. Buck 2 Efficiency VOUT2 = 3.3V at 2.2MHz

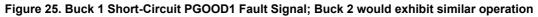

Figure 15. Buck 1 Overvoltage Detection

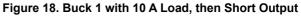

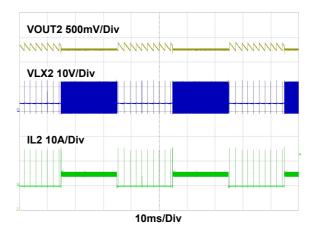

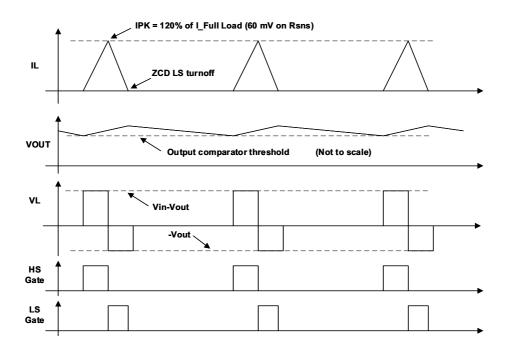

Figure 17. Steady State ECM Operation with Io1 = 0.5 A

Figure 16. Buck 1 Undervoltage Detection

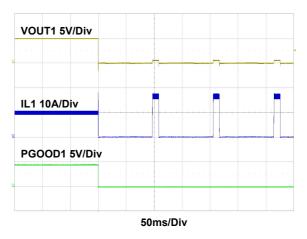

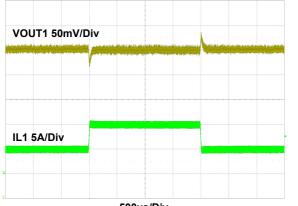

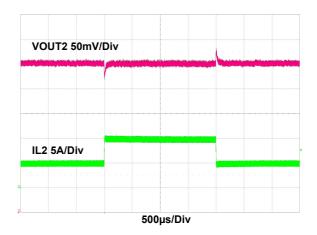

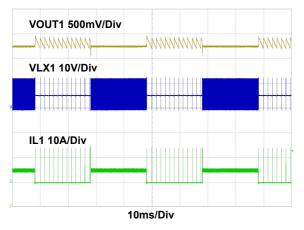

Unless otherwise noted, operating conditions are:  $T_A = +25^{\circ}C$ ,  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$  (Continued)

500µs/Div

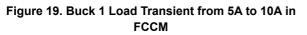

Figure 20. Buck 2 Load Transient from 5A to 10A

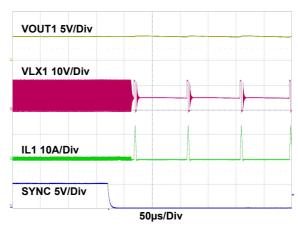

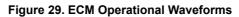

Figure 23. Buck 1 SYNC High ECM Exit

Unless otherwise noted, operating conditions are:  $T_A$  = +25°C,  $V_{IN}$  = 12V,  $V_{OUT1}$  = 5V,  $V_{OUT2}$  = 3.3V (Continued)

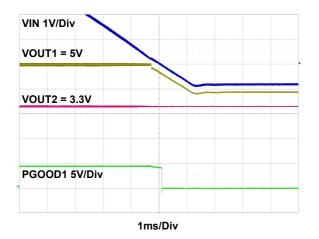

Figure 26. V<sub>IN</sub> Falling below 4.5V with CH1 Dropout, Ch2 no Dropout

Figure 27.  $V_{IN}$  rising from 4.4V after Ch1 in Dropout

# 4. Functional Description

#### 4.1 Functional Overview

The ISL78264 has controllers that support two DC/DC converters Buck 1 and Buck 2 that can be configured in various modes and operate across a  $V_{IN}$  range of 3.75V to 42V. Buck Converter 1 can be configured as a fixed 3.3V, fixed 5.0V, or as an adjustable output buck regulator from 0.8V to 5.0V. Buck Converter 2 has an adjustable output that can be set in the range of 0.8V to 32V. If the proper external components are selected, the ISL78264 can support significantly more than 10 A of load current with each buck converter.

# 4.1.1 Configurations for VSEL, CNT, and CNT2

Before operation, the ISL78264 has three configuration pins (VSEL, CNT, and CNT2) that must be individually programmed with a resistor to ground. During start-up procedure (before power pulses begin) the IC sources a small current from these three pins, and the internal circuitry reads the resultant voltage and implements configuration settings according to <u>Tables 3</u>, <u>4</u>, and <u>5</u>.

#### 4.1.1.1 VSEL

The VSEL pin allows the Channel 1 voltage selection as fixed at 5V or 3.3V using an internal voltage divider or adjustable with an external voltage divider. Select values for the VSEL configuration resistor to ground are listed in Table 3.

| Resistor (kΩ) | Ch1 V <sub>OUT</sub> | Note |

|---------------|----------------------|------|

| 75            | 5V                   | -    |

| 37.4          | Adjustable           | -    |

| 6.04          | 3.3V                 | -    |

#### Table 3. VSEL Configuration Values

#### 4.1.1.2 CNT

The CNT pin allows the spread spectrum ON or OFF selection and dead time between gate pulses that control external MOSFETs. If the spread spectrum is selected as ON, the modulation depth can be +6% or +12%. The dead time choices of SHORT (30ns) or LONG (100ns) are available to facilitate the usage of various external MOSFETs or switching frequency selections. For example, for the smallest solution size, a high switching frequency of 2.2MHz can be selected and external MOSFETs with a small gate charge can be used with SHORT dead time. For highest efficiency designs, a lower switching frequency can be selected, and MOSFETs with lower  $r_{DS(ON)}$  values can require LONG dead time selection. Select values for CNT configuration are listed in Table 4.

#### Table 4.CNT Configuration Values

| Resistor (kΩ) | Spread Spectrum | Dead Time (ns) |

|---------------|-----------------|----------------|

| 75            | +12%            | Short 30       |

| 54.9          | +12%            | Long 100       |

| 37.4          | +6%             | Short 30       |

| 24.9          | +6%             | Long 100       |

| 14.7          | Off             | Short 30       |

| 6.04          | Off             | Long 100       |

#### 4.1.1.3 CNT2

The CNT2 pin allows the minimum boot refresh time selection of 180ns or 360ns, with a longer time preferable for typical applications. Resistor values for CNT2 configuration are listed in <u>Table 5</u>.

| Resistor (kΩ) | Boot Refresh Time (ns) |

|---------------|------------------------|

| 54.9          | 360                    |

| 14.7          | 180                    |

| 6.04          | Does not start         |

#### Table 5. CNT2 Configuration Values

# 4.1.2 Start-Up Operation