# Interfacing the PowerSpan II™ with the Wintegra Winpath™

80A1010\_AN005\_05

November 4, 2009

6024 Silver Creek Valley Road San Jose, California 95138 Telephone: (408) 284-8200 • FAX: (408) 284-3572 Printed in U.S.A. ©2009 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

GENERAL DISCLAIMER Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright  $^{\odot}$  2009 Integrated Device Technology, Inc. All Rights Reserved.

The IDT logo is registered to Integrated Device Technology, Inc. IDT is a trademark of Integrated Device Technology, Inc.

## **1. Interfacing the PowerSpan II with the Wintegra** Winpath

This application note details the interface requirements for using the Wintegra WinPath and the PowerSpan II in an application. The following sections are detailed in the application note:

- "Overview" on page 4

- "Hardware Connection" on page 6

- "Clock, Reset, and Power-up Options" on page 12

- "Arbitration" on page 15

- "Bus Pipelining Support" on page 17

- "Interrupt Control" on page 18

- "Memory Interface" on page 18

- "Power Supplies" on page 24

- "Typical Applications" on page 28

- "Register Configuration" on page 37

- "AC Timing" on page 52

#### 1.1 **Overview**

The Wintegra WinPath and the IDT PowerSpan II can be used in a wide range of system applications. This application note only focuses on the requirements for connecting the host bus interface between the two devices. In "Typical Applications" on page 28 of this document, specific applications such as host and adapter card implementations are discussed in detail.

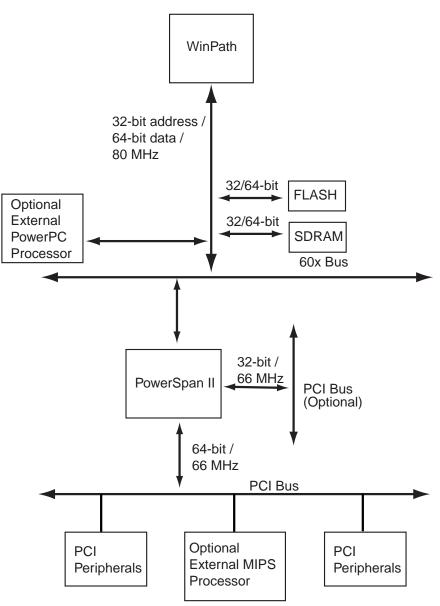

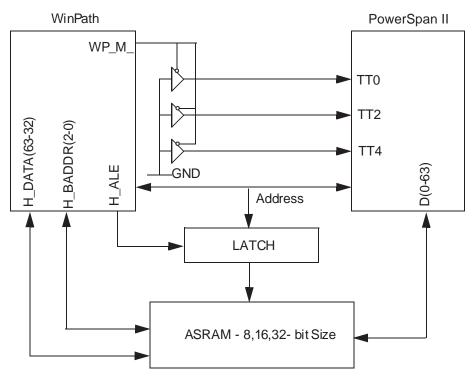

Figure 1 illustrates a simplified block diagram between the WinPath and the PowerSpan II.

#### Figure 1: System Diagram

#### 1.1.1 Architectural Components

The major components of this application note are the WinPath and the PowerSpan II.

#### 1.1.1.1 WinPath

The WinPath is the flagship semiconductor product family from Wintegra. Targeted for the Access Infrastructure, WinPath offers designers a comprehensive method to handle the data path. ATM and IP can be independently selected as a transport protocol per port. A full set of IP services may be offered over any L2 protocol, including ATM, PPP and Ethernet. Any port can instantly migrate from ATM to IP transport with zero hardware changes.

The WinPath provides a world-class set of ATM features for both termination and switching. It also includes interworking from ATM to TDM and from ATM to IP transport media.

The WinPath complements the protocol offering with an ideal mix of IP quality-of-service support, Layer 2/3 Ethernet switching and Point-to-Point protocol (PPP) support features, all which are increasingly important in access equipment designs.

#### 1.1.1.2 PowerSpan II

The IDT PowerSpan II is a Multi-port PCI Bus Switch that bridges PCI to PowerPC<sup>TM</sup> processors and the Wintegra WinPath<sup>TM</sup> processor. PowerSpan II is available in either a single PCI or dual PCI variant. PowerSpan II defines a new level of PCI bus switch flexibility.

PowerSpan II has a Switched PCI architecture, which maximizes transfer concurrency and improves the efficiency and burst performance on the PCI and processor buses. Along with a revolutionary Switched PCI architecture, PowerSpan II features integrated PCI-to-PCI bridging, concurrent prefetch read capability, multi-port Direct Memory Access (DMA) operation and CompactPCI Hot Swap support. It is now available in 23mm and 27mm BGA packages.

### **1.2 Hardware Connection**

This section defines how the signals must be connected between the WinPath and the PowerSpan II devices to ensure proper operation.

#### 1.2.1 Host Bus Signal Connection

The host bus interface signals between the WinPath and the PowerSpan II can be directly connected. External pull-up resistors must be connected to all bus control signals to ensure that they are held in an inactive state.

The host bus interface implements the PowerPC 60x bus protocol.

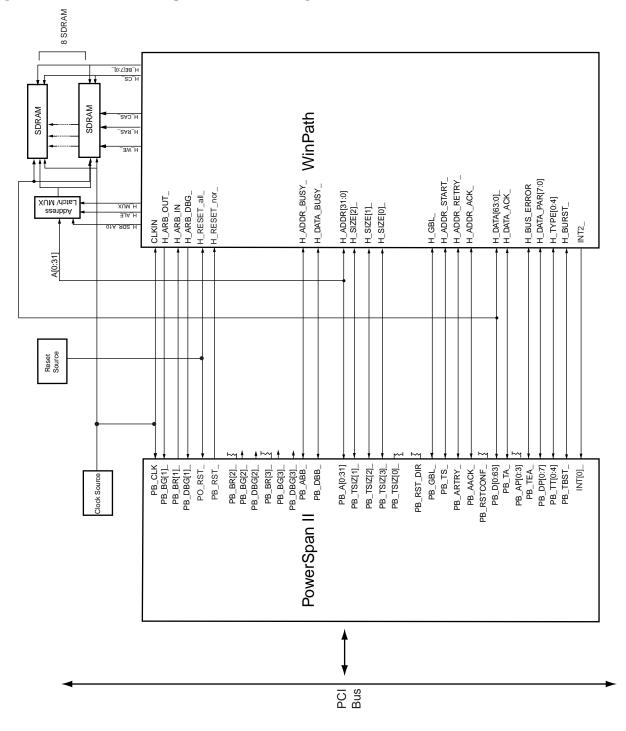

Figure 2 illustrates the signals that must be connected in a joint WinPath and PowerSpan II application. The WinPath processor is the arbiter in the system diagram.

Figure 2 does not illustrate the external pull-up resistors for the directly connected signals. For pull-up resistor information, refer to Table 1.

Figure 2: WinPath and PowerSpan II Connection Diagram

Figure 2 assumes WinPath's arbiter is enabled. The routing of the interrupts is dependent on the application. This diagram shows the interrupts being routed from the WinPath processor through PowerSpan II to the PCI host.

The SDRAM memory is controlled by the WinPath SDRAM memory controller. This memory must be 64-bit in a WinPath and PowerSpan II application. The SDRAM interface requires external address multiplexing to support accesses by the PowerSpan II.

The FLASH memory is controlled by the WinPath memory controller. This memory must be 64-bit in a WinPath and PowerSpan II application.

WinPath includes an optimized interface for controlling latch and multiplexing devices. For example, an integrated latch/mux device, such as the 74AVCLH16260 device, can be used to limit the delay through two devices.

#### 1.2.1.1 **Signal Connection and Terminations**

The processor bus signals in Table 1 are connected between the WinPath and the PowerSpan II. The table also shows termination requirements for the connections.

Pull-up resistors are not required on the processor bus address (PB\_A[0:31]) and data (PB\_D[0:63]) signals to guarantee functional operation of the PowerSpan II. However, adding resistors to the address and data signals minimizes the current drawn by the PowerSpan II's tristated buffers when the bus is in an idle condition. The system designer must decide whether to add these resistors to the address and data bus.

| WinPath Signal               | PowerSpan II Signal | Termination    |

|------------------------------|---------------------|----------------|

| H_ADDR[31:0] <sup>a</sup>    | PB_A[0:31]          | No requirement |

| H_DATA[63:0] <sup>b</sup>    | PB_D[0:63]          | No requirement |

| H_DATA_PAR[7:0] <sup>c</sup> | PB_DP[0:7]          | No requirement |

| H_ADDR_PAR[3:0] <sup>d</sup> | PB_AP[0:3]          | No requirement |

| H_TYPE_4                     | PB_TT[4]            | No requirement |

| H_TYPE_3                     | PB_TT[3]            | No requirement |

| H_TYPE_2                     | PB_TT[2]            | No requirement |

| H_TYPE_1                     | PB_TT[1]            | No requirement |

| H_TYPE_0                     | PB_TT[0]            | No requirement |

| H_SIZE_2                     | PB_TSIZ[1]          | No requirement |

| H_SIZE_1                     | PB_TSIZ[2]          | No requirement |

Table 1: Signal Connection between WinPath and PowerSpan II

| WinPath Signal | PowerSpan II Signal | Termination                |

|----------------|---------------------|----------------------------|

| H_SIZE_0       | PB_TSIZ[3]          | No requirement             |

| H_ADDR_START_  | PB_TS_              | Pull-up 10 Kohm resistor   |

| H_ADDR_BUSY_   | PB_ABB_             | Pull-up: 10 Kohm resistor  |

| H_ADDR_ACK_    | PB_AACK_            | Pull-up: 10 Kohm resistor  |

| H_ADDR_RETRY_  | PB_ARTRY_           | Pull-up: 10 Kohm resistor  |

| H_DATA_ACK_    | PB_TA_              | Pull-up: 10 Kohm resistor  |

| H_BUS_ERROR_   | PB_TEA_             | Pull-up: 10 Kohm resistor  |

| H_BURST_       | PB_TBST_            | Pull-up: 10 Kohm resistor  |

| H_DATA_BUSY_   | PB_DBB_             | Pull-up: 10 Kohm resistor  |

| H_GBL_         | PB_GBL_             | Pull-up: 10 Kohm resistor  |

| INT2_          | INT[0]              | Pull-up: 10 Kohm resistor  |

| H_RESET_all    | PO_RST_             | Pull-up: 1.2 Kohm resistor |

| H_RESET_nor    | PB_RST_             | Pull-up: 1.2 Kohm resistor |

Table 1: Signal Connection between WinPath and PowerSpan II (Continued)

a. Mapping for the address signals: H\_ADD[31] - PB\_A[0], H\_ADDR[0] - PB\_A[31]

b. Mapping for the data signals: H\_DATA[63] - PB\_D[0], H\_DATA[0] - PB\_D[63]

c. Mapping for the data parity signals: H\_DATA\_PAR[7] - H\_DATA\_PAR[0], PB\_DP[0] - PB\_DP[7].

d. Mapping for the address parity signals: H\_ADDR\_PAR[3] - H\_ADDR\_PAR[0], PB\_AP[0] - PB\_AP[3]. Available on WinPath Revision B and later devices.

#### 1.2.1.2 PowerSpan II Specific Signals

PowerSpan II has signals on its host bus interface that are not supported on the WinPath.

| PowerSpan II<br>Processor Bus Signal | Signal Description                                                                                                                                     | Termination                                                                                                                                                                                                       |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB_FAST                              | Input (multiplexed pin): Used for<br>PowerSpan II power-up<br>configuration/PB clock PLL frequency<br>range.                                           | This signal can be driven by an external<br>CPLD or pulled-up/ pulled-down to a<br>fixed level (depends on the system<br>configuration).<br>Refer to the <i>PowerSpan II User Manual</i><br>for more information. |

| PB_RSTCONF_                          | Input: Used for PowerSpan II<br>configuration slave mode.This mode is<br>not a supported configuration by<br>WinPath.                                  | Pull-up: 10 Kohm resistor                                                                                                                                                                                         |

| PB_RST_DIR                           | Input: Used for determining PB_RST_<br>pin direction.<br>1= PB_RST_ is an output<br>0= PB_RST_ is an input                                             | Pull-up (10 Kohm resistor) or pull-down (1.0 Kohm resistor) depending on where the host resides.                                                                                                                  |

| PB_AP[0:3]                           | Bidirectional: Use for the processor<br>supporting address parity check.This<br>functionality is supported by WinPath<br>Revision B and later devices. | Pull-up: 10 Kohm resistor if function is not used.                                                                                                                                                                |

| PB_CI_                               | Output: Use for cache inhibit<br>functionality. This functionality is not<br>supported by WinPath.                                                     | Open                                                                                                                                                                                                              |

| PB_DVAL_                             | Bidirectional: Used for extended cycles<br>on the host bus. This functionality is not<br>a supported by WinPath.                                       | Pull-up: 10 Kohm resistor                                                                                                                                                                                         |

| PB_TSIZ[0]                           | Bidirectional: Used for PowerSpan II to<br>specify the type of the transaction. This<br>functionality is not a supported by<br>WinPath.                | Pull-down: 1.0 Kohm resistor                                                                                                                                                                                      |

| INT[5:1]                             | Bidirectional (multiplexed pin): Used for<br>PowerSpan II power-up<br>configuration/General purpose interrupt<br>pins.                                 | If not using for interrupt purpose, pull-up<br>(10 Kohm resistor) or pull-down (1.0<br>Kohm resistor) depending on the system<br>configuration.                                                                   |

#### **PCI Signals**

PowerSpan II's PCI signals can be directly connected to the appropriate PCI signal on the motherboard or the PCI connector. Pull-up resistors may, depending on the application, need to be added to the PCI bus control signals. If a local PCI bus is designed on the motherboard, then pull-up resistors are required (refer to the *PCI 2.2 Specification* for more information). For host bridging applications, the PowerSpan II P1\_IDSEL and P2\_IDSEL signals are not required to be implemented. In this application, the P1\_IDSEL and P2\_IDSEL signals must be pulled low through a pull-down resistor.

### 1.3 Clock, Reset, and Power-up Options

#### 1.3.1 Resets

In a WinPath and PowerSpan II system, reset control is a requirement for proper operation. Both devices require various resets including a power-on reset and processor bus reset signals.

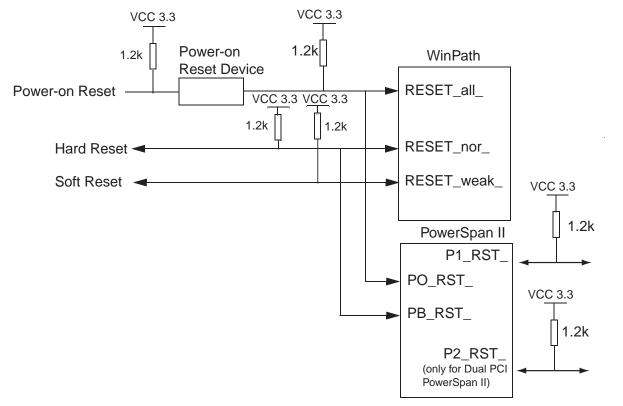

Figure 3 shows one possible system reset circuit for a WinPath and PowerSpan II system. Refer to "Typical Applications" on page 28 for additional details on how reset signals should be connected in certain applications.

#### Figure 3: System Reset Circuit

During power up, a Power-on Reset device asserts RESET\_all and PO\_RST\_ until the power supplies are stable. During this phase, both device's PLL clocking mechanisms gain lock and execute their reset configuration routine.

If a bus error condition occurs during normal operation the hard reset can be asserted by the Software watchdog time-out in the WinPath, or another PowerPC processor, to bring the system back to a known state.

In PCI adapter card application, the central reset resource is on the PCI host side. The PowerSpan II PB\_RST\_ can be configured as an output to drive the host bus' hard reset signal when it detects PCI bus reset from its PCI interface.

While in the PCI host application, the PowerSpan II propagates the host bus hard reset to its PCI bus in order to reset all the other PCI peripheral devices.

#### **1.3.2 Power-up Options**

The WinPath processor requires configuration from a serial I<sup>2</sup>C bus or flash memory.

Some of PowerSpan II's features must be configured before the completion of the power-up reset sequence. PowerSpan II's. Multiplexed System Pins mode is used in this WinPath and PowerSpan II application. This configuration mode uses the following system pins: PB\_FAST, P1\_M66EN, P2\_M66EN, and INT[5:1]. Either resistors (pull-up or pull-down) or external programmable logic can be used to ensure the signals are in the correct state during the power-up reset sequence to configure PowerSpan II's power-up options.

For more information on PowerSpan II power-up options refer to the *PowerSpan II User Manual*.

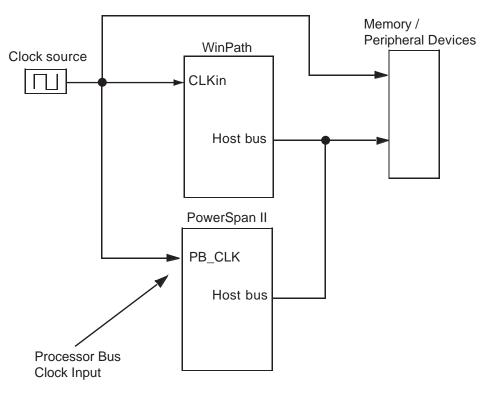

#### 1.3.3 Clocks

The external clock generator provides the host bus clock to the WinPath, PowerSpan II, and memory devices. The WinPath processor feeds the input clock source to its PLL to generate clock sources for internal, packet and parameter bus interface clocks. The recommended mode to program the WinPath host bus clock generator is in synchronous multi-master bus mode with externally generated system clock. This mode ensures that accesses by each device to the host bus are synchronized. Refer to the WinPath *Hardware Developers Guide* for more information.

The PowerSpan II clock input should be connected to the WinPath CLK\_in pin because the WinPath must work in multi-master mode with the PowerSpan II. A PLL-based clock driver can be used to ensure the zero clock skew between the devices (see Figure 4).

PowerSpan II P1\_CLK, P2\_CLK, and PB\_CLK clock frequencies must be stable before PO\_RST\_ is deasserted. If a frequency change is required, a new power-up sequence (with the assertion of PO\_RST\_) must be initiated in order for the PLLs to lock.

Figure 4: Multi-master with DLL-based Processor Bus Clock

### 1.4 Arbitration

In a WinPath and PowerSpan II system, either of the devices can be programmed as the host bus arbiter. Both devices have internal host bus arbiters which support multiple masters, and can also work with external bus arbiters.

Either the WinPath or PowerSpan II arbiter can be used effectively in any application. However, when considering system level performance the use of the WinPath arbiter is recommended because of its flexibility in allocating bus bandwidth between internal WinPath resources and external resources.

#### 1.4.1 WinPath as Host (60x) Bus Arbiter

The WinPath arbiter controls up to two external masters.

Table 3 shows the required signal connection between the WinPath and PowerSpan II devices when the WinPath is the arbiter in the system.

Table 3: Signal Connection When WinPath is the Bus Arbiter

|                                           | WinPath Arbitration Signal               |                                          |

|-------------------------------------------|------------------------------------------|------------------------------------------|

| PowerSpan II Arbitration Signal           | PowerSpan II as Master One <sup>a</sup>  | PowerSpan II as Master Two <sup>a</sup>  |

| PB_BR[1]_                                 | H_ARB_IN_                                | H_ABR2_                                  |

| This signal is an output when the         | This signal is an input when WinPath is  | This signal is an input when WinPath is  |

| PowerSpan II 60x bus arbiter is disabled. | the arbiter.                             | the arbiter.                             |

| PB_BG[1]_                                 | H_ARB_OUT_                               | H_ABG2_                                  |

| This signal is an input when the          | This signal is an output when WinPath is | This signal is an output when WinPath is |

| PowerSpan II 60x bus arbiter is disabled. | the arbiter.                             | the arbiter.                             |

| PB_DBG[1]_                                | H_ARB_DBG_                               | H_DBG2_                                  |

| This signal is an input when the          | This signal is an output when WinPath is | This signal is an output when WinPath is |

| PowerSpan II 60x bus arbiter is disabled. | the arbiter.                             | the arbiter.                             |

a. The WinPath arbiter controls up to two external masters. When PowerSpan II is the first external bus master (master one) it connects through the following WinPath signals: H\_ARB\_IN\_, H\_ARB\_OUT\_, H\_ARB\_DBG\_. When PowerSpan II is the second external bus master (master two) it connects through the following WinPath signals: H\_ABG2\_, H\_DBG2\_. The WinPath H\_DATA\_BUSY\_ signal connects to PB\_DBB\_ signal of PowerSpan II.

#### 1.4.2 Configuring PowerSpan II as Host (60x) Bus Arbiter

The PowerSpan II host (60x) bus arbiter is enabled through a power-up option. The Arbiter Enable (PB\_ARB\_EN) bit (read-only) in the PowerSpan II Reset Control and Status register reflects this option. The bit is set to 1 during power-up when PowerSpan II internal arbiter is enabled.

When PowerSpan II is sharing the host bus with two or more WinPath processors, the WinPath's host bus arbiter must be used.

The following functions can be programmed in the Arbiter Control Register:

- Bus Parking

- External Master Enable

- Priority Level

Table 4 shows the point-to-point signal connection required between the WinPath PowerSpan II when the PowerSpan II is the arbiter in the system.

| PowerSpan II Arbitration Signal                   | WinPath Arbitration Signal                           |  |

|---------------------------------------------------|------------------------------------------------------|--|

| PB_BR[n]_ <sup>a</sup>                            | H_ARB_OUT_                                           |  |

| This signal is an input when PowerSpan II is the  | This signal is an output when the WinPath arbiter is |  |

| arbiter.                                          | disabled.                                            |  |

| PB_BG[n]_                                         | H_ARB_IN_                                            |  |

| This signal is an output when PowerSpan II is the | This signal is an input when the WinPath arbiter is  |  |

| arbiter.                                          | disabled.                                            |  |

| PB_DBG[ <i>n</i> ]_                               | H_ARB_DBG_                                           |  |

| This signal is an output when PowerSpan II is the | This signal is an input when the WinPath arbiter is  |  |

| arbiter.                                          | disabled.                                            |  |

#### Table 4: Signal Connection when PowerSpan II is the Bus Arbiter

a. PowerSpan II's internal 60x bus arbiter can support up to three external bus masters. The value of n can equal 1,2, or 3 depending on the arbitration signal connection.

### **1.5 Bus Pipelining Support**

In joint WinPath and PowerSpan II applications bus pipelining mode is supported but must be used under certain constraints.

#### **1.5.1 Programming Requirements**

The pipeline depth field (PDEPTH) in the WinPath External Bus Arbiter Control register defines how many address tenure grants are generated by the arbiter relative to data tenure. The following list shows the programmable values in the PDEPTH field:

- 001: One address grant is generated before one data phase is completed (No pipeline mode).

- 010: Two address grants may be asserted before one data phase is completed. (One-level pipeline mode).

- 000: Four address grants may be asserted before one data phase was completed.

PowerSpan II does not allow more than level-one address pipelining. Assuming a transaction (Transaction A) takes place on the host (60x) bus, the PowerSpan II allows the next transaction's address phase (Transaction B) to begin after the Address Phase of the Transaction A was acknowledged by the assertion of AACK. The PowerSpan II's pipeline allows the address phase of Transaction B to start before the data phase of Transaction A has finished. However, PowerSpan II's pipeline does not allow the address phase of Transaction B to be acknowledged before the data phase of Transaction A has finished.

This characteristic applies not only to the PowerSpan II itself, but for every device in the system, therefore the pipeline size is not only limited by the arbiter itself (for WinPath, the host (60x) bus arbiter can be configured to support three different levels of pipelining), but it is limited by all the slaves in the bus.

The WinPath Bus Arbiter can grant the bus to any master if the number of Address Phases waiting for their corresponding Data Phase does not exceed a specific number. The Multi-master Slave Module in the WinPath has an internal buffer of four locations that allows it to support of a bus pipeline of four.

In a WinPath and PowerSpan II system, if a pipeline depth of four is enabled within the WinPath, the host bus interface could hang.

To avoid a situation where the pipeline mode is set to a level PowerSpan II does not support, the WinPath processor includes a configuration bit that will force the Multi-master Slave Module to work with a pipeline of reduced depth. The RSPD (Reduced Slave Pipeline Depth) bit in the BIU\_EBACR register enables or disables this capability. If this bit is 0, the WinPath Multi-master Slave Interface limits the maximum pipeline depth to four. If this bit is 1, the pipeline depth is limited to one.

## **1.6 Interrupt Control**

The WinPath processor can both generate and process interrupt requests to and from PowerSpan II.

The PowerSpan II has six individual bidirectional interrupt pins INT[5:0] that can be connected to the WinPath or the PowerPC processor.

PowerSpan II's INT[5:1] signals are also the multiplexed input signals for PowerSpan II power-up configuration options (see "Power-up Options" on page 13).

If only one interrupt signal is required in the system, the INT[0] signal can be directly connected to aWinPath interrupt input with a pull-up resistor to the 3.3 V I/O power supply. The WinPath MIPs core can then process these interrupts which are routed through the internal interrupt controller.

Interrupt Routing is discussed in "Typical Applications" on page 28.

## **1.7 Memory Interface**

The memory implementation for a WinPath and PowerSpan II system can be controlled by the WinPath host bus memory controller. In addition to WinPath's ability to master the host bus, the PowerSpan II's internal DMA engine or PCI target image channel can be used for mastering the host bus to access both SDRAM and FLASH memory.

#### **1.7.1 Flash Memory Interface**

The Flash memory is controlled by the asynchronous memory controller. This memory is 64 bits wide to meet the requirements of the PowerPC device for boot port size and is controlled by host chip select 0 (H\_CS0) the WinPath boot chip select. The reset configuration routine reprograms the chip select to the address area of the reset vector associated with the boot microprocessor. For MIPS based boot the address is 0x1FC00000, for PowerPC based boot the address is 0xFFF00100.

### RENESAS

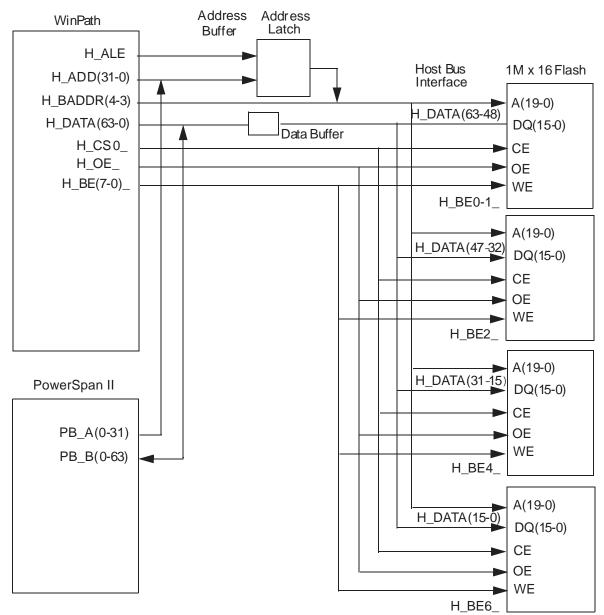

Figure 5 illustrates the connectivity of the memory interface.

#### Figure 5: Flash Memory Interface

#### 1.7.1.1 FLASH Read Cycle

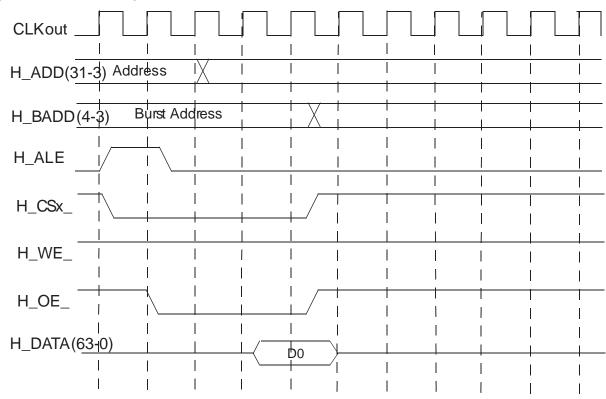

Figure 6 illustrates the data phase of a single 64-bit read cycle initiated by either WinPath or the PowerSpan II device. The bus master drives the address until is it acknowledged. WinPath drives the burst address line and the ASRAM controller strobes the transaction by asserting the chip select (H\_CSx) and output enable (H\_OE) according to chip select programming. The transaction terminates and the data is latched by the data bus master.

20

#### Figure 6: FLASH Read Cycle

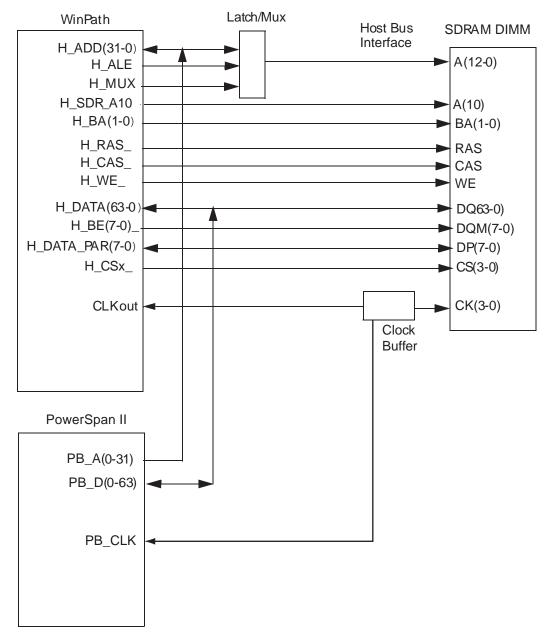

#### **1.7.2 SDRAM Memory Interface**

The SDRAM memory is controlled by the SDRAM memory controller. The memory is 64 bits wide taking advantage of the data bus width supported by WinPath and the PowerSpan II device.

The SDRAM interface requires external address multiplexing to support accesses by the PowerSpan II. WinPath includes an optimized interface for controlling latch and multiplexing devices. An integrated latch/mux device (for example, 74AVCLH16260) can be used to limit the delay through two devices.

Figure 7 illustrates the connectivity of this interface.

#### Figure 7: SDRAM Memory Interface

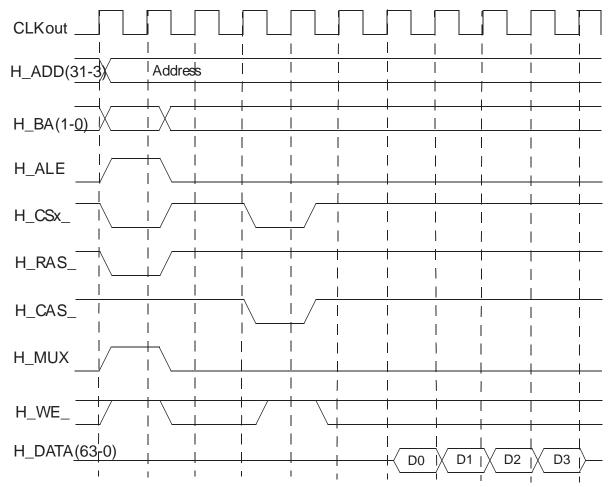

Figure 8 illustrates the timing relationships of the address latch and multiplex control. The address latch control signal (H\_ALE) and multiplexor control signal (H\_MUX) assert during the row address phase in the same clock cycle as the chip select (H\_CSx) and row address strobe (H\_RAS\_) assertion. These signals de-assert in the following clock cycle. The latched address is multiplexed during the column address phase with the assertion of the chip select and column address strobe (H\_CAS\_).

#### Figure 8: SDRAM Cycle- Address Latch and Multiplex Control

#### 1.7.3 Application Supporting Smaller Asynchronous Memory Port Sizes

In an interface configuration with the PowerSpan II, a typical application is a PCI mezzanine card where PCB space is a premium. WinPath supports small port sizes on its asynchronous memory interface and this may be exploited when interfacing to Flash memory. The size of this memory can be tailored to meet the exact requirements for code storage. Since the code will be typically copied to faster memory e.g. SDRAM, for execution during runtime, the flash port size can be minimized since it has little effect on the system performance. The Host bus burst address pins H\_BADDR(2-0) are required to support access decomposition to the smaller port size.

However due to pin multiplexing on the Host bus where the burst address pins 2,1,0 are multiplexed with 60x transfer type pins TT0, TT2, TT4 there is a requirement to implement logic to overcome the fact that transfer type pins become unavailable when burst addresses are selected. The transfer type signals must be driven with the appropriate logic level for proper operation. WinPath however only samples TT1,TT3, these signals convey all the information required for transactions supported by WinPath.

Figure 9 illustrates the recommended logic. The signal WP\_M is asserted by WinPath indicating it is mastering the current transaction on the Host bus. The signal is used as the tristate enable to a set of buffers which drive the logic level (logic 0) to transfer type pins.

#### Figure 9: Small Port Size Implementation

The smaller asynchronous memory port sizes (8, 16. and 32-bit) are supported by WinPath on the host bus for SDRAM and ASRAM memory. These port sizes only apply if WinPath is the only device that can access the memory. When the memory can be accessed by another device, for example PowerPC processor or PowerSpan II, the memory port size must be 64-bit.

#### 1.7.4 Multi-master Operation - Shared Data

The WinPath and PowerSpan II devices operate together in a multi-master configuration. However, global data between the processors cannot be shared as cacheable. The WinPath processor does not implement cache snooping of external masters and therefore all shared data must be non-cached. The WinPath drives the host (60x) bus global signal (GBL\_) high for all initiated transactions; it never samples this signal. The WinPath Memory Management Units (MMU) must be used to create an area of non-cached memory to allow data to be shared between the WinPath and the PowerSpan II.

The PowerSpan II PB\_GBL\_ is an output only signal. PowerSpan II never samples this signal. Whether PB\_GBL\_ is asserted during the transaction can be controlled by the PB\_GBL\_ bit in the control register.

Refer to the PowerSpan II User Manual for more information.

### **1.8 Power Supplies**

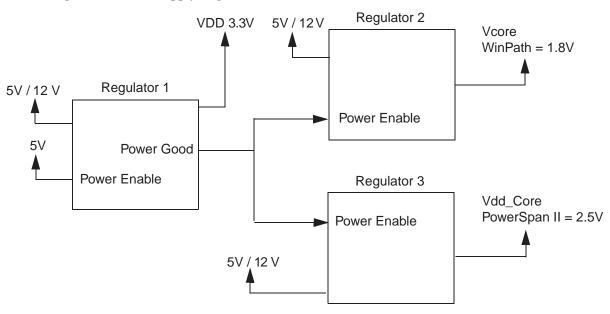

When designing a WinPath and PowerSpan II system, there are different power supply requirements for each device. Both of these devices use the same 3.3 V I/O power voltage. However, WinPath specifies a 1.8 V core supply while PowerSpan II's core voltage is 2.5 V.

Flexible power distribution can be implemented with programmable regulators providing voltage selection via sets of input configuration pins. The regulators are used to generate the core and I/O voltages and provide the sequencing of the power supply. The sequencing is important to meet specifications of each device.

Figure 10 illustrates the architecture of an implementation for a WinPath and PowerSpan II system. Each regulator has 5V and 12 volt supply.

Figure 10: Power Supply Regulation Circuit

Regulator 1 generates the I/O voltage for both devices as well as the general 3.3 V supply. Regulator 1 has an output pin (Power Good) indicating power has reached it nominal value. This signal enables Regulator 2 and Regulator 3, which then generate their output voltages. During power down phase, as the 3.3 V supply drops the Power Good signal is negated. The negation of the Power Good signal turns off Regulator 2 and Regulator 3. This circuit ensures that power sequencing is adhered to for each supply.

Refer to the WinPath and PowerSpan II documentation to determine the required current rating for each regulator.

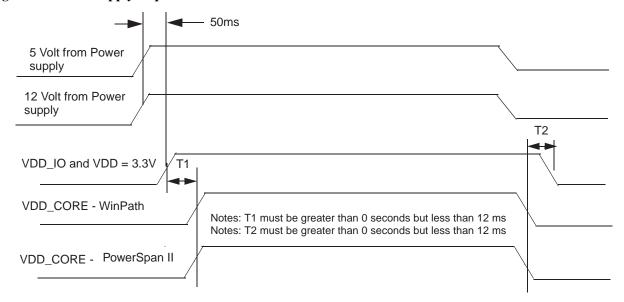

#### **1.8.1 Power Sequencing**

The voltages are supplied to the device sub-modules in sequence. The power supply ensures that VDD\_IO rises to full voltage before VDD\_CORE is applied. For power-down VDD\_CORE should fall before VDD\_IO.

#### Figure 11: Power Supply Sequence

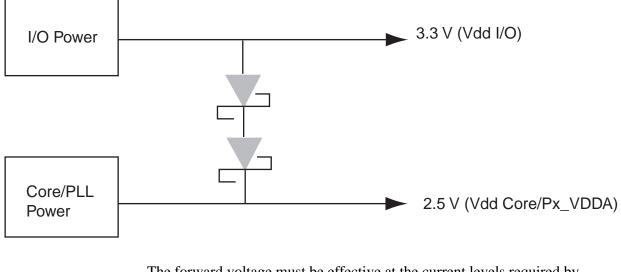

#### **1.8.2 PowerSpan II Recommended Bootstrap Diode**

IDT recommends the use of a bootstrap diode between the power rails. The bootstrap diodes that are used in the system must be configured so that a nominal Core Supply Voltage (Vdd Core) is sourced from the I/O Supply Voltage (Vdd I/O) until the power supply is active. In Figure 12, two Schottky barrier diodes are connected in series. Each of the diodes has a forward voltage ( $V_F$ ) of 0.6V at high currents which provides a 1.2V current drop. This drop maintains 2.1V on the 2.5V power line. Once the Core/PLL power supply stabilizes at 2.5V, the bootstrap diode(s) are reverse biased with small leakage current.

### RENESAS

#### Figure 12: Bootstrap Diodes for Power-up Sequencing

The forward voltage must be effective at the current levels required by PowerSpan II (< 1 amp). Do not use diodes with only a nominal  $V_F$  which drops too low at high current.

### **1.9** Typical Applications

PowerSpan II is able to support the WinPath processor as both a PCI host bridge and a PCI peripheral bridge. Section 1.2 on page 6 described the connections between WinPath's host bus interface and PowerSpan II's processor bus interface. The following section discusses in greater detail how the clocks, resets, and interrupt signals should be connected based on the application.

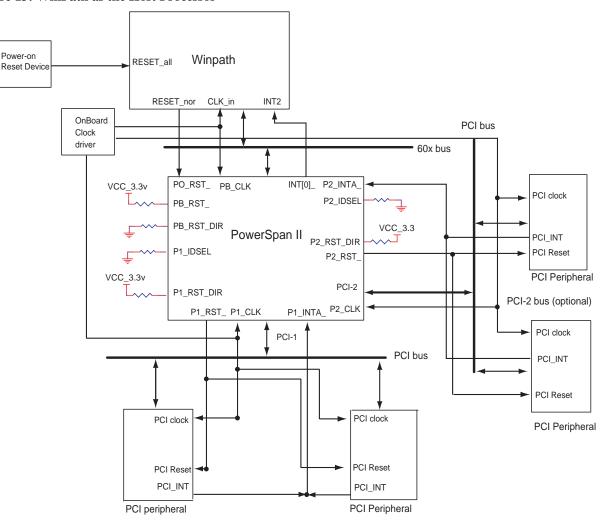

### **1.9.1** WinPath as the Host Processor in the System

Figure 13 illustrates an typical application where the WinPath processor is using PowerSpan II as a host bridge. In this design, the internal MIPs core is enabled within the WinPath processor.

In this application there is an on-board clock generator to distribute all the necessary clocks to the WinPath, PowerSpan II, and memory devices (including the PowerSpan II PCI clocks).

#### Figure 13: WinPath as the Host Processor

The routing of the interrupts is dependent on the application. This diagram shows the interrupts being routed from the PCI Peripheral to the WinPath through PowerSpan II. The interrupt input pin to the WinPath processor can occur on any one of four maskable interrupts pins: INT1, INT2, INT3, or INT4.

The PowerSpan II also drives the PCI reset signal and the REQ64\_ signal during the power reset sequences. This is a host feature according to the *PCI Local Bus Specification*. When the WinPath processor asserts the hard reset (RESET\_nor) signal, which is connected to PowerSpan II's PB\_RST\_, PowerSpan II drives the P1\_RST\_ and the P2\_RST\_ signal low.

Make sure the PowerSpan II power-up option pins are driven to the correct value during each assertion of its PO\_RST\_ caused by the WinPath's RESET\_nor signal.

During the board initialization, the PowerSpan II is initialized by the MIPS processor core within the WinPath device.

In order to configure PowerSpan II in this application, the following design considerations must be reviewed:

- 1. Pull-up the P1\_RST\_DIR pin to allow PowerSpan II to drive PCI reset from its P1\_RST\_ pin.

- 2. Pull-down the PB\_RST\_DIR pin and pull-up the PB\_RST\_ signal because WinPath drives the host bus reset to PowerSpan II's PO\_RST\_ signal.

- 3. Pull-down the P1\_IDSEL signal to ground to disable PowerSpan II from receiving PCI configuration cycle. This is required because PowerSpan II is the PCI host bridge device in this application.

- 4. Select power-up option (PWRUP\_BOOT) as PB\_BOOT to allow PowerSpan II to be initialized from the host bus.

- This option can be implemented either by pulling-up the INT[3] signal or, alternatively, using a CPLD to drive it to a logic high during the negation of PO\_RST\_.

- 5. Enable power-up option PWRUP\_P1\_R64\_EN to allow PowerSpan II to drive P1\_REQ64\_when it drives PCI reset out.

- This option programs whether PowerSpan II drives the P1\_REQ64\_ during the negation of P1\_RST\_. This is a PCI host feature in 64-bit mode according to the PCI Local Bus Specification.

- Enable PWRUP\_P1\_R64\_EN either by pulling-down the INT[4] signal or, alternatively, the signal can be driven by any CPLD to ensure its at a logic low during the negation of PO\_RST\_.

- 6. Optionally, configure the interrupt pin INT[0] as a output and P1\_INTA as a input to route the hardware interrupt request from the PCI peripheral devices to the WinPath host processor.

- The interrupt pins direction can be individually configured by the PowerSpan II register IDR (offset 0x444) through a host software access after power-up configuration.

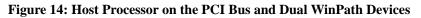

### **1.9.2** WinPath Application with the Host Processor Residing on the PCI bus

Figure 14 illustrates a typical application where the host processor in the system resides on the PCI bus. In this design, PowerSpan II is used as a PCI bridge to communicate between the WinPath devices and the host processor.

The routing of the interrupts is dependent on the application. This diagram shows the interrupts being routed from the WinPath to the PCI System Host through PowerSpan II. The interrupt input pin to the WinPath processor can occur on any one of four maskable interrupts pins: INT1, INT2, INT3, or INT4. In this application an on-board clock generator distributes the necessary clocks to the WinPath, PowerSpan II, and memory devices. The only clock not supplied by the clock generator is PowerSpan II's P1\_CLK.

According to the *PCI Specification*, the PCI host system is responsible to provide the clock and reset signals for the devices on the primary PCI interface.

The PCI host system initializes the WinPath and PowerSpan II peripheral device after power-up.

When the PCI host asserts the bus reset, PowerSpan II monitors the P1\_RST\_ signal and propagates the signal to its processor bus by asserting its PB\_RST\_ signal (this signal is connected to WinPath's RESET\_nor signal) and P2\_RST\_ signal (when the Dual PCI PowerSpan II device it used). This reset configuration scheme allows the WinPath and PowerSpan II peripheral card to be reset by the PCI host.

In order to configure PowerSpan II in this application, the following design considerations must be reviewed:

- 1. Pull-down P1\_RST\_DIR pin to allow PowerSpan II to propagate PCI reset from its P1\_RST\_ pin.

- 2. Pull-up PB\_RST\_DIR pin to allow PowerSpan II to drive PB\_RST\_ to reset WinPath.

The PowerSpan II's PB\_RST\_ signal is a bidirectional signal. Even when PB\_RST\_ is configured as a output, the PowerSpan II still monitors PB\_RST\_ and reset its PB interface accordingly to the appropriate status when the hard reset is asserted from external host bus processor. For example, when WinPath loads the boot code from FLASH memory it drives the H\_ADDR\_START\_ signal and the H\_ADDR\_ACK\_ signal while asserting the RESET\_nor signal. PowerSpan II's PB\_RST\_ signal must be connected to RESET\_nor to make sure its PB interface is kept in reset during the loading period.

- 3. Connect the P1\_IDSEL signal to one of the PCI-1 bus address lines (P1\_AD[31:16]) to allow PowerSpan II to receive PCI configuration cycle (Type 0) issued by the PCI host device. Review the manual of the PCI bridge device on host side of the application to make sure the proper AD bus line is used for generating PCI configuration cycle.

- 4. Select the power-up option (PWRUP\_BOOT) as PCI\_BOOT to enable PowerSpan II to be initialized first from the PCI bus.

- This option can be implemented by pulling-down the INT[3] signal or using a CPLD to drive it to a logic low during the negation of PO\_RST\_.

- 5. Disable the power-up option PWRUP\_P1\_R64\_EN to allow PowerSpan II to sample P1\_REQ64\_ signal during the negation of PCI reset.

- This option supports PowerSpan II driving the P1\_REQ64\_ signal during the negation of P1\_RST\_. This is a PCI host feature, according to the *PCI Local Bus Specification*.

- In the application shown in Figure 14, this option must be disabled by pulling-up the INT[4] signal, or alternatively using a CPLD to drive it to logic high during the negation of PO\_RST\_.

- 6. Optionally, configure the INT[0] interrupt pin as an input and P1\_INTA interrupt pin as output. This routes the hardware interrupt from WinPath to the PCI host.

This application uses both the PowerSpan II's INT[0] and INT[1] signals as inputs and the P1\_INTA signal as an output to route the hardware interrupt from the two WinPath devices to the PCI host processor. Please note, the INT[1] signal is also used for the multiplexed system pin mode for the power-up option, which is sampled during the negation of PO\_RST\_. Therefore, the design must ensure INT[1] is at a logic high during the negation of PO\_RST\_. The INT[1] pin must not be driven by any device attached to this interrupt signal during the PowerSpan II power-up period.

On the PowerSpan II the multiplexed system pin mode power-up option, INT[5:1] has a 10 ns the setup time before the negation of PO\_RST\_ and a 10 ns hold time after the negation of PO\_RST\_.

The direction of the interrupt pins can be individually configured by the PowerSpan II register IDR (offset 0x444). They can be configured through a host software access after power-up configuration.

For a complete design reference, refer to the *PowerSpan II User Manual* and the WinPath *Hardware Developer's Guide*.

#### 1.9.2.1 Alternative Reset Strategy

For a design which requires the PCI Host to completely reset WinPath, one solution is to route ta PowerSpan II general purpose interrupt pin (one of the INT[5:0] signals), and the WinPath's RESET\_all signal to a CPLD device. Inside the CPLD, the interrupt output status is latched to drive the WinPath RESET\_all signal.

The PCI Host can access either PowerSpan II's mailbox or doorbell register which is mapped to one of the interrupt signals to completely reset the WinPath processor through the CPLD.

The CPLD must latch the interrupt signal status long enough to reset WinPath. This is necessary because the PowerSpan II tristates the interrupt output when its PB\_RST\_ signal is asserted by WinPath during power-up.

Another recommended solution to create a flexible system reset strategy is to route all of PowerSpan II's and WinPath's reset signals to an external CPLD. When using this CPLD solution, the board designer has more control of the reset sequence while prototyping the board.

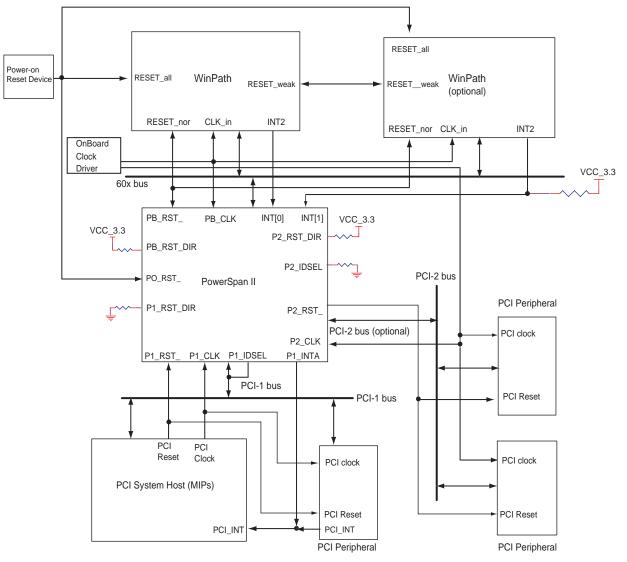

### 1.9.3 WinPath Application with a PowerPC Host Processor

Figure 15 illustrates an application where the internal MIPS core within the WinPath device is disabled and the PowerPC processor is the host in the system. The PowerSpan II device is providing PCI host bridging capability to the I/O peripherals.

The routing of the interrupts is dependent on the application. This diagram shows the interrupts being routed from the PCI Peripheral to the Host PowerPC through PowerSpan II. The interrupt input pin to the WinPath processor can occur on any one of four maskable interrupts pins: INT1, INT2, INT3, or INT4.

In this application, there is an on-board clock generator to distribute all the necessary clocks to the WinPath, PowerSpan II, and memory devices.

The PowerSpan II drives the PCI reset signal and the REQ64\_ signal during the power reset sequence. This functionality is a host feature according to the *PCI Local Bus Specification*. When the PowerPC processor asserts the hard reset (HRESET\_) signal, which is connected to PowerSpan II's PO\_RST\_ signal, PowerSpan II drives the P1\_RST\_ and the P2\_RST\_ signal low accordingly.

During the board initialization, both the WinPath and the PowerSpan II are initialized from the PowerPC host processor through their host bus interfaces.

In order to configure PowerSpan II in this application, the following design considerations must be reviewed:

- 1. Pull-up the P1\_RST\_DIR pin to allow PowerSpan II to drive PCI reset from its P1\_RST\_ pin.

- 2. Pull-down the PB\_RST\_DIR pin and pull-up PB\_RST\_ signal because the PowerPC processor and WinPath drives the host bus reset to PowerSpan II's PO\_RST\_ signal.

- 3. Pull-down the P1\_IDSEL signal to ground to disable PowerSpan II from receiving PCI configuration cycle. This is required because PowerSpan II is the PCI host bridge device in this application.

- 4. Select power-up option (PWRUP\_BOOT) as PB\_BOOT to allow PowerSpan II to be initialized from the host bus.

- This option can be implemented by pulling-up the INT[3] signal or, alternatively, using a CPLD to drive it to a logic high during the negation of PO\_RST\_.

- 5. Enable power-up option PWRUP\_P1\_R64\_EN to allow PowerSpan II to drive P1\_REQ64\_when it drives PCI reset out.

- This option programs whether PowerSpan II drives the P1\_REQ64\_ during the negation of P1\_RST\_. This is a PCI host feature in 64-bit mode according to the PCI Local Bus Specification.

- The PWRUP\_P1\_R64\_EN option can be implemented either by pulling-down the INT[4] signal, or using a CPLD to drive it to a logic low during the negation of PO\_RST\_.

- 6. Optionally, configure the interrupt pin INT[0] as a output and P1\_INTA as a input to route the hardware interrupt request from the PCI peripheral devices to the PowerPC host processor.

- These interrupt pins direction can be individually configured by the PowerSpan II register IDR (offset 0x444) through a host software access after power-up configuration.

# 1.10 Register Configuration

In a system that has both the WinPath and PowerSpan II, particular registers in both devices must be set to specific values in order to ensure proper operation. The information in this application note is based on the testing of the WinPath and PowerSpan II configurations. The system can still work with other register settings, but the values represented in Table 5 and Table 6 are derived from extensive testing.

# 1.10.1 WinPath Register Settings

Table 5 shows which registers in the WinPath processor must be set to the corresponding value in order for a WinPath and PowerSpan II system to function properly.

Table 5: WinPath Required Register Setting for PowerSpan II Applications

| WinPath Host<br>Bus (SIU4)<br>Register | Register<br>Description                         | Required<br>Bit                     | Bit Description                                                                                                                                                                                                                                                                                                                                                                  | Bit Setting<br>for WinPath                                                                                                                                                                                                                                        |

|----------------------------------------|-------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIU_CONF<br>(SIU4)                     | BIU General<br>Configuration<br>Register        | Multi-<br>Master<br>(MM)            | Indicates if the bus is multi-master bus or a stand alone<br>bus.<br>0= stand alone bus<br>1= Multi master bus (default)                                                                                                                                                                                                                                                         | MM=1                                                                                                                                                                                                                                                              |

| BIU_PCR<br>(SIU4)                      | BIU Pin<br>Configuration<br>register            | Active Pull<br>up Enable<br>(ACTPU) | 0= Host bus signal is tristated normally (default)<br>1= host bus signal is actively driven before tristating                                                                                                                                                                                                                                                                    | ACTPU= 1                                                                                                                                                                                                                                                          |

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Setup Time<br>Control<br>(SUTC)     | The field define the setup time options for Host bus<br>signal H_DACK, H_ADDR_RETRY,<br>H_BUS_ERROR, H_ADDR_ACK, H_ADDR_BUSY,<br>H_ADDR_START, H_ARB_IN, H_DATA_ACK.<br>0= Standard setup time. No additional clock cycles<br>added for memory control signals assertion (default)<br>1= Reduced setup time. Additional clock cycle added<br>for memory control signal assertion | Set SUTC=1<br>when one of<br>the following<br>conditions is<br>met:<br>• Working<br>with non-<br>registered<br>SDRAM on<br>the Host<br>bus.<br>• Host bus<br>frequency is<br>above<br>66 MHz.<br>Set SUTC=0<br>when neither<br>of these<br>conditions are<br>met. |

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Retry<br>Disable<br>(RTD)           | Defines if ARTRY supported signal active in the<br>system. Disabling ARTRY allows a master to initiate<br>back to back transactions without disconnecting from<br>the bus for one clock cycle.<br>0=ARTRY supported (default)<br>1=ARTRY not supported                                                                                                                           | RTD=0                                                                                                                                                                                                                                                             |

© 2019 Renesas Electronics Corporation

| WinPath Host<br>Bus (SIU4)<br>Register | Register<br>Description                         | Required<br>Bit                                           | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit Setting<br>for WinPath                                                                |

|----------------------------------------|-------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Data Bus<br>Busy<br>internally<br>generated<br>(DBBI)     | Defines if an external DBB signal is used in the<br>system. In the case it is not used, DBB is internally<br>generated so that it is asserted in the cycle immediately<br>following the assertion of DBG and negated in the<br>cycle immediately following the assertion of the last<br>TA of the current transaction.<br>0=DBB external (default)<br>1=DBB internally generated                                                                                                                    | DBBI=0                                                                                    |

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Address Bus<br>Busy<br>Internally<br>generated.<br>(ABBI) | Defines if an external ABB signal is used in the<br>system.<br>In the case it is not used, ABB is internally generated<br>such that it is asserted in the cycle immediately<br>following the assertion of ABG and negated in the<br>cycle immediately following the assertion of AACK of<br>the current transaction.<br>0=ABB external (default)<br>1=ABB internally generated                                                                                                                      | ABBI=0                                                                                    |

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | DBGTS                                                     | When the pipeline is empty, the WinPath (acting as the arbiter) can normally assert H_DBG_ in the same cycle as H_ADDR_START_ (TS_)<br>0 = H_DBG_ can be asserted in the same cycle as H_ADDR_START_ (TS_)<br>1 = H_DBG_ can be asserted at least one cycle after H_ADDR_START_ (TS_). In this mode,<br>H_DATA_BUSY_ must be deasserted in the cycle immediately following the last data phase of the transaction. H_DATA_BUSY_ may not be extended to provide additional turn-off time on the bus. | DBGTS = 1<br>Note: This<br>setting is only<br>valid for Rev.<br>B0 and later<br>revisions |

#### Table 5: WinPath Required Register Setting for PowerSpan II Applications

#### Table 5: WinPath Required Register Setting for PowerSpan II Applications

| WinPath Host<br>Bus (SIU4)<br>Register | Register<br>Description                         | Required<br>Bit                                       | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bit Setting<br>for WinPath                                                                                                                                                    |

|----------------------------------------|-------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Pipeline<br>Depth<br>(PDEPTH)                         | Defines the maximum pipeline depth allowed in the<br>system. This is limited by the system mechanism in<br>each 60x device that tracks correspondence of the<br>address-phase to data-phase. This defines for the<br>internal arbiter when an additional ABG can be<br>asserted without overflowing the number of<br>address-phases initiated that have not yet completed<br>their corresponding data phases.<br>001 = 1 transaction pending allowed<br>010 = 2 transactions pending allowed<br>011 = Reserved<br>000 = 4 transactions pending allowed (default)<br>1xx = Reserved | PDEPTH =<br>000<br>Note: The<br>RSPD bit in<br>the BIU<br>External Bus<br>Arbiter<br>Control<br>register must<br>be set to 1<br>when the<br>PDEPTH<br>field is set to<br>000. |

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Data Bus<br>Grant<br>transition<br>from IDLE<br>(DGI) | Defines how the Data Bus Grant is asserted by the Bus<br>Arbiter when the bus transitions from the IDLE state<br>(no current transaction running).<br>0=DBG will be asserted together with ABG (default)<br>1=DBG will be asserted one clock cycle after the<br>assertion of the ABG line.                                                                                                                                                                                                                                                                                         | When<br>WinPath<br>arbiter is<br>enabled<br>DGI=1                                                                                                                             |

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Reduced<br>Slave<br>Pipeline<br>Depth<br>(RSPD)       | 0= the WinPath Multi-master Slave Interface will work<br>with a maximum pipeline depth of four. (default)<br>1=the pipeline depth is limited to one. This adds<br>compatibility for device that have a maximum address<br>pipeline depth of 1, such as PowerSpan II.<br>Caution: If the WinPath RSPD bit is not set to 1 and<br>data pipelining is enabled in a PowerSpan II system,<br>the host bus could hang.                                                                                                                                                                   | RSPD=1<br>Note: The<br>RSPD bit<br>must be set to<br>1.                                                                                                                       |

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Arbitration<br>Mode<br>(ARM)                          | Defines the priority mechanism for masters requesting<br>bus ownership.<br>0 = Strict Priority (default)<br>1 = Weighted Round Robin                                                                                                                                                                                                                                                                                                                                                                                                                                               | When the<br>WinPath<br>arbiter is<br>enabled<br>ARM=1                                                                                                                         |

© 2019 Renesas Electronics Corporation

| WinPath Host<br>Bus (SIU4)<br>Register | Register<br>Description                         | Required<br>Bit                                    | Bit Description                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit Setting<br>for WinPath                                                                                                                                                                                                                                            |

|----------------------------------------|-------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIU_EBACR<br>(SIU4)                    | BIU External Bus<br>Arbiter Control<br>Register | Internal Bus<br>Arbiter<br>Enable<br>(IABE)        | <ul> <li>0 = Internal arbiter disabled</li> <li>1 = Internal arbiter enabled</li> <li>Note: Either the WinPath or PowerSpan II internal<br/>arbiter can be used effectively in any application.</li> <li>However, when considering system level performance<br/>the use WinPath arbiter is recommended because of its<br/>flexibility in allocating bus bandwidth between internal<br/>WinPath resources and external resources.</li> </ul> | IABE = 1                                                                                                                                                                                                                                                              |

| MC_B_x_MSK<br>(Chip Select)            | Address Mask<br>Register                        | Turn-off<br>Time on<br>Read<br>Operation<br>(TOFF) | 00 = 0 clock cycles<br>01 = 1 clock cycle<br>10 = 4 clock cycles<br>11 = 8 clock cycles                                                                                                                                                                                                                                                                                                                                                     | TOFF=00                                                                                                                                                                                                                                                               |

| MC_B_x_MSK<br>(Chip Select)            | Address Mask<br>Register                        | Wait State<br>(WS)                                 | Number of additional cycles (Wait states) inserted<br>during read or write cycle where external termination<br>is not enabled.<br>00000 = 0 wait states<br>00001 = 1 wait states<br>11111 = 46 wait states<br>Note: The programming options for this field continue<br>up to 46 wait states.                                                                                                                                                | When<br>working with<br>ASRAM<br>memory on<br>the 60x bus<br>the WS field<br>must be set to<br>a value<br>greater, or<br>equal to, 1<br>when the<br>SUTC bit is<br>set to 0.<br>The WS field<br>can be set to<br>any value<br>when the<br>SUTC bit is is<br>set to 1. |

#### Table 5: WinPath Required Register Setting for PowerSpan II Applications

#### 1.10.1.1 Special Register Considerations

#### SUTC Bit Setting

WinPath must have the SUTC bit set to 1 when PowerSpan II accesses non-registered SDRAM through the host bus. This requirement is caused because PowerSpan II does not function properly with minimum cycle 60x bus systems where the TA signal occurs in the cycle immediately following the TS signal. Setting the SUTC bit to 0 may cause WinPath to generate minimum 60x bus cycles.

#### **TOFF Bit Setting**

When working with PowerSpan II, any memory peripheral device placed on the host bus that is controlled by a WinPath chip select and configured as a ASRAM device must have a TOFF parameter in the MC\_B\_x\_MSK register set to zero clock cycles (00). When a peripheral requires a non-zero turn-off time, the data buffers must be used to isolate the data bus connected to the peripheral. The buffers can then be turned off without requiring a positive value programmed into the TOFF field.

#### **TS/DBG** Interaction

In a system with both the WinPath and PowerSpan II devices, the host bus can hang under the following conditions:

- WinPath is the 60x bus arbiter with the pipeline depth set 1.

- PowerSpan II initiates two consecutive transactions to the 60x bus. Two consecutive transactions can be initiated in the following ways:

- PowerSpan II is doing DMA from one bus to the other with sizes other than 8 bytes or 32 bytes

- A PCI master is performing access to the 60x bus with size other than 8 bytes or 32 bytes

For the first case, assume a PCI master request 16 bytes to read from the 60x bus, since the 60x bus can transfer only up to 8 bytes (single) or 32 bytes (burst), PowerSpan II will initiate two consecutive single transactions.

For the second case, assume a PCI master request 8 bytes to write from address 0x1 (not align to 8 bytes), the PowerSpan II will initiate two consecutive single transactions, first from address 0x1 with size of 7 and the second from address 0x8 with size of 1.

In the above two examples there is no difference if the initiator is the PCI master or the PowerSpan II's DMA.

#### Workaround (All WinPath revisions)

In order to avoid these situations the following actions can be taken:

- Ensure the PCI master (or PowerSpan II's DMA) is performing only 8 byte single or 32 byte burst transactions. The transactions starting address must be aligned to the address boundary.

- Enable WinPath's internal arbiter and configure it to pipe 0 (set PDEPTH field in BIU\_EBACR register to '001').

- Use the PowerSpan II's internal 60x bus arbiter instead of the internal WinPath arbiter.

#### Workaround (WinPath Revision B.0 and Later Revisions)

In order to avoid these situations the following actions can be taken:

• When using the WinPath's internal arbiter, set the DBGTS bit in the BIU\_EBACR register (see Table 5).

# 1.10.2 PowerSpan II Register Settings

Table 6 shows what registers in PowerSpan II must be set to the corresponding value in order for a WinPath and PowerSpan II system to function properly.

| Table 6: PowerSpan   | II Required   | Register S   | ettings for 1 | PowerSnan II     | Annlications   |

|----------------------|---------------|--------------|---------------|------------------|----------------|

| Table 0. I Ower Span | i ii nequirea | i Register D | cumes for a   | i owei opan ii z | applications – |

| PowerSpan II<br>Register                                                       | Register Description                                                        | Required Bit                              | Bit Description                                                                                                                                                                                        | Bit Setting for<br>PowerSpan II                                                          |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Processor Bus<br>Miscellaneous Control<br>and Status register<br>(PB_MISC_CSR) | The PB_MISC_CSR<br>register contains<br>general control and<br>status bits. | Extended<br>Cycle Enable<br>(EXTCYC)      | Determines of the PowerSpan II Master<br>is able to generate extended cycles of<br>16 bytes or 24 bytes.<br>0=does not generate extended cycles<br>(default)<br>1= generates extended cycles           | EXTCYC =0                                                                                |

| Processor Bus<br>Miscellaneous Control<br>and Status register<br>(PB_MISC_CSR) | The PB_MISC_CSR<br>register contains<br>general control and<br>status bits. | Address Retry<br>Enable<br>(ARTRY_<br>EN) | Controls PowerSpan II's use of the<br>PB_ARTRY_ signal during the<br>servicing of transactions.<br>0= PowerSpan III does not assert<br>PB_ARTRY_ (default)<br>1=PowerSpan II does assert<br>PB_ARTRY_  | ARTRY_EN =1                                                                              |

| Processor Bus<br>Miscellaneous Control<br>and Status register<br>(PB_MISC_CSR) | The PB_MISC_CSR<br>register contains<br>general control and<br>status bits. | Address Parity<br>Enable<br>(AP_EN)       | Controls<br>PowerSpan II's use of the PB_AP_<br>signal during the servicing of<br>transactions.<br>0= PowerSpan II does not support<br>Address Parity<br>1=PowerSpan II does support Address<br>Parity | AP_EN = 0 if<br>address parity is<br>not used<br>AP_EN=1 if<br>address parity is<br>used |

## 1.10.2.1 Example PowerSpan II Configuration Register Programming

Table 7 and Table 8 show specific registers that must be programmed in PowerSpan II.However, the list of registers is only a sub-set of all the possible registers that can beconfigured in the PowerSpan II device. Refer to the *PowerSpan II User Manual* and thePowerSpan II *initialization Application Note* for a complete listing of all processor bus andPCI registers and configuration requirements.

#### PowerSpan II Register Programming - Host on the Processor Bus

Table 7 shows what registers in PowerSpan II must be programmed when the host is on the60x bus. The example values shown in the table are system dependent and are meant only as aguide when programming PowerSpan II.

#### Table 7: Host on the Processor Bus

| PowerSpan II Register                                                 | <b>Register Description</b>                                                                                                                               | Register Values                                                                                |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Processor Bus Register Image Base Address<br>Register<br>PB_REG_BADDR | WinPath internal core or PowerPC processor<br>writes to this register can relocate<br>PowerSpan II PB register space within 32-bit<br>host address space. | BA=0x30000000 (default)                                                                        |

| PCI-1 Control and Status Register<br>P1_CSR                           |                                                                                                                                                           | The bus master bit (BM) must be<br>set to 1 to enable PowerSpan II to<br>master the PCI-1 bus  |

| PCI-2 Control and Status Register<br>P2_CSR                           |                                                                                                                                                           | The bus master bit (BM) must be<br>set to 1 to enable PowerSpan II to<br>master the PCI-2 bus. |

#### Table 7: Host on the Processor Bus

| PowerSpan II Register                                                                                                                                   | Register Description                                                                                                                                                                                                                                                               | Register Values                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor Bus PCI Configuration Cycle<br>Information Register<br>PB_CONF_INFO<br>Processor Bus PCI Configuration Cycle Data<br>Register<br>PB_CONF_DATA | WinPath internal MIPs core or PowerPC<br>processor writes to these two registers to<br>generate PCI configuration cycle to initialize<br>PCI peripherals residing on the PCI-1 or<br>PCI-2 bus.                                                                                    |                                                                                                                                                                                                                               |

| Processor Bus Slave Image Control Register<br>PB_SIx_CTL<br>Processor Bus Slave<br>Image Base Address<br>PB_SIx_BADDR                                   | WinPath internal MIPs core or PowerPC<br>processor writes to these registers to<br>configure the PB slave image. The PB slave<br>interface compares the address and<br>transaction type of any 60x bus cycle and<br>acknowledges it if it falls in the configured<br>address range | For more information about<br>possible register values that<br>enable specific features, see<br>"Processor Bus Slave Image<br>Programming Register Values"<br>on page 47. Also refer to the<br>PowerSpan II User Manual for a |

| Processor Bus Slave Image Translation<br>Address<br>PB_SIx_TADDR                                                                                        | address range.<br>PowerSpan II then completes the transaction<br>on either the PCI-1 or PCI-2 bus. The bus<br>that PowerSpan II completes the transaction<br>on is programmed in the Destination (DEST)<br>bit in the PB_SIx_CTL register.                                         | <i>PowerSpan II User Manual</i> for a complete listing of all processor bus and PCI registers                                                                                                                                 |

#### Processor Bus Slave Image Programming Register Values

The following register examples show how to set-up the PowerSpan II's Processor Bus Slave Image 0. PowerSpan II has a total of eight independent images. The slave images must not have overlapping addresses.

In these examples Master-based decode is disabled and the Endian (END) field must be set to Big Endian in the PB\_SIx\_CTL register.

## Register Setting Example One

When the PowerSpan II Processor Bus Slave Image is programmed with the following values, PowerSpan II maps 60x bus transactions within address range 0xA0000000~0xA0007FFF (image size is 32 Kbytes) to the memory space of the PCI-1 bus at the address of 0xA0000000~0xA0007FFF. The prefetching size is 32 bytes.

Register settings:

- PB\_SI0\_BADDR: 0xA0000000

- PB\_SI0\_CTL: 0x830000C2

The programming value for the PB\_SI0\_TADDR register is not specified because address translation is not enabled in this example (TA\_EN is set to 0 in the PB\_SI0\_CTL register).

## Register Setting Example Two