-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

無線ユニットクロック シンクロナイザ、JESD204B/Cクロックジッタ減衰器、RFシンセサイザおよびRFバッファ

ルネサスの先進のRFタイミングポートフォリオは、低位相ノイズと低スプリアス性能に特化した設計のデバイスで構成されています。これらのRF-PLLベースの製品は、ジッタ減衰、JESD204B/C規格準拠のクロック生成、局部発振器(LO)クロックの生成をサポートします。非常に低い付加位相ノイズ性能を持つRFバッファはRF-PLL製品を補完し、高品質クロックの分配に対応します。

シングルチップ無線シンク機器

業界初のシングルチップ無線シンク機器はデジタルPLL(DPLL)と高性能のRF-PLLを内蔵しています。 高精度タイミングプロトコル(PTP、IEEE 1588)、同期イーサネット、およびJESD204B/Cのサポートにより、このデバイスはワイヤレスインフラストラクチャ無線向けの高精度な周波数と位相同期の設計を簡素化します。 デバイスは複数の周波数発生とクロックジッタ減衰、独立した周波数領域を実装します。例えば、物理層イーサネットおよびJESD204B/C対応の無線クロックがあります。 対応の同期規格にはIEEE 1588-2019および ITU-T同期イーサネット(SyncE)があり、T-TSC(Telecom Time Slave Clock)およびG8262.1 強化クロック同期装置(eSEC)の一部として ITU-T G.8273.2 Class Cに準拠します。 統合型RF-PLLはDAC/ADC回路へのレファレンスとして複数の低位相ノイズと低スプリアス特性のクロックを生成し、可能な限り最高のADC/DAC変換を実現します。 周波数、位相、および1日の時刻を同期するには、1PPS入力信号を使用することができます。 デバイスはPTPハードウェアクロックとしても適切で、そこで位相が外部IEEE 1588ソフトウェアスタックによって設定されるか、ソフトウェアサーボによってDCOとして直接制御されます。 周波数変換機能には広い範囲の入力周波数と出力周波数が含まれます。

業界トップのJESD204B/Cクロックジッタ減衰器

ルネサスは低位相ノイズクロックの生成と位相管理が必要な用途向けに高性能のJESD204B/Cジッタ減衰器を提供します。 デバイスは一般には、統合型でスタンドアロンのA/DおよびD/C変換回路向けのJESD204B/Cに準拠するクロックとSYSREF信号のソースで、中心として使用されます。 二段構成のPLLアーキテクチャはジッタ減衰と周波数生成の両方をサポートしています。 クロック周波数が最大6GHzまで、位相ノイズが80fs RMS未満、スプリアス減衰が90dBの機能により、デバイスはすべてのデータサンプリングの用途で可能な限り最高のシステム性能を可能にします。 高信号のファンアウト、柔軟性のある差動I/O、信号位相操作機能、および入力監視/切り替え機能は優れたAC性能を補完します。

RFシンセサイザ

RFシンセサイザは広範、設定可能でかつ継続的な周波数範囲で1つか2つのRF周波数クロック信号を生成します。 内部PLLはさまざまなクロック周波数のニーズがある用途をサポートする少数または整数フィードバックを使用します。 所望の出力周波数はシリアルインターフェースによってデジタルで設定されています。 出力位相ノイズは35fs RMS(整数フィードバック)、66fs RMS(少数フィードバック)と可能な限り低くなっています。 最高サポートの出力周波数は18GHzです。 RFシンセサイザは一般に、昇降圧コンバータ回路向けの リファレンスクロックデバイスとしての無線用途で、またADC/DACデバイス向けの柔軟な周波数源としてデータサンプリング用途でも使用されます。

低付加位相ノイズRFバッファ

ルネサスのRFバッファは周波数3000MHzまでをサポートし、無線シンクロナイザー、JESD204B/Cクロックジッタ減衰器、およびRFシンセサイザのファンアウトを拡張します。 シングルチャネルおよびデュアルチャネルのRFバッファはシリコンゲルマニウム(SiGe)技術を利用して付加位相ノイズや過熱伝搬遅延の変動を最小限に抑えます。 ルネサスは高速JESD204B/Cクロックを完全にサポートする世界初のRFバッファを実現します。 RFバッファはデバイスクロックと同期信号(SYSREF)の独立した信号経路を特長としています。 設定可能な位相遅延、分周器、マルチチップ位相同期はシステムと基板の設計の柔軟性を最大に高めます。 これは極めて低い付加位相ノイズ、高周波数機能、低出力スキューと優れたチャンネル分離を組み合わせています。

JESD204B/Cクロックについて

JESD204B/CクロックはJESD204BおよびJESD204C高速シリアルインターフェースを実装するシステムで使用されます。 JESD204C規格はその4回の反復で、高調波フレームクロックと確定的レイテンシのサポートにより、チャンネルあたりの最大レーン速度32Gbpsまでを規定します。 JESD204の旧バージョンでは、フレームクロックはシステムの絶対的なタイミング基準でした。 通常は、フレームクロックとデータコンバータのサンプリングクロックの両者は同じで、システムの柔軟性が制限され、マルチデバイス同期を非常に複雑にします。 JESD204B/Cでは、デバイスクロックはシステム内の各デバイスに対するタイミング基準です。 ルネサスJESD204B/Cクロックジッタ減衰器と無線シンクロナイザーはこれらタイミング信号に対して高品質のソースを提供し、優れたシステム性能と信頼性をもたらします

カテゴリ

RFシンセサイザ

RFバッファ

無線シンクロナイザ&JESD204B/Cクロックジッタ減衰器

セレクションテーブル

サブカテゴリ |

Temp. Range |

Pkg. Type |

Lead Count (#) |

Pkg. Dimensions (mm) |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|

| 型名 | ||||||

| Low Skew,1-to-6,Differential-to-2.5V,3.3V LVPECL/ECL Fanout Buffer | Clock Buffers & Drivers | -40 to 85°C | TSSOP | 20 | 6.5 x 4.4 x 1.0 | 5.222 |

| Low Skew,1-to-2,Differential-to-2.5V,3.3V LVPECL/ECL Fanout Buffer | Clock Buffers & Drivers | -40 to 85°C | SOIC, TSSOP | 8 | 3.0 x 3.0 x 0.97, 4.9 x 3.9 x 1.5 | 3.082 |

| Low Skew,1-to-5 Differential-to-2.5V,3.3V LVPECL/ECL Fanout Buffer | Clock Buffers & Drivers | -40 to 85°C | TSSOP | 20 | 6.5 x 4.4 x 1.0 | 7.092 |

| Low Skew,1-to-12,Differential-to-3.3V,2.5V LVPECL Fanout Buffer | Clock Buffers & Drivers | -40 to 85°C | VFQFPN | 32 | 5.0 x 5.0 x 0.9 | 26.3 |

| 2:1 Differential-to-LVDS Multiplexer | Clock Multiplexers (MUX) | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 8.14 |

| 1:2 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | RF Buffers | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 6.856 |

| 1:6 LVDS Output 1.8V Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 20 | 4.0 x 4.0 x 1.0 | 6.756 |

| 2:4 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | RF Buffers | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 5.972 |

| 2:8 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | RF Buffers | -40 to 85°C | VFQFPN | 28 | 5.0 x 5.0 x 0.8 | 6.756 |

| 2:12 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | RF Buffers | -40 to 85°C | VFQFPN | 40 | 6.0 x 6.0 x 0.9 | 7.428 |

| Dual 1:2 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 5.972 |

| Dual 1:4 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 28 | 5.0 x 5.0 x 0.8 | 6.756 |

| Dual 1:6 LVDS Output 1.8V / 2.5V Fanout Buffer | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | WLCSP | 48 | 3.59 x 3.04 x 0.6 | 7.629 |

| Dual 1:6 LVDS Output 1.8V / 2.5V Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 40 | 6.0 x 6.0 x 0.9 | |

| Dual 1:8 LVDS 1.8V / 2.5V Fanout Buffer for 1PPS and High-Speed Clocks | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 48 | 7.0 x 7.0 x 0.9 | 11.37 |

| Low Additive Jitter 2:8 Buffer with Universal Differential Outputs | Clock Buffers & Drivers | -40 to 85°C | VFQFPN | 32 | 5.0 x 5.0 x 0.9 | 5.29 |

| Low Additive Jitter 2:8 Buffer with CMOS / Differential Outputs | Clock Buffers & Drivers | -40 to 85°C | VFQFPN | 32 | 5.0 x 5.0 x 0.9 | 6.985 |

| Programmable Low Additive Jitter 2:8 Buffer with Dividers and Universal Outputs | Clock Buffers & Drivers | -40 to 85°C | VFQFPN | 32 | 5.0 x 5.0 x 0.9 | 4.404 |

| 2:4, LVDS Output Fanout Buffer, 2.5V | RF Buffers | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 4.226 |

| 2:4, LVDS Output Fanout Buffer, 3.3 V | RF Buffers | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 4.226 |

| 1:8, LVDS Output Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 28 | 5.0 x 5.0 x 0.8 | 9.574 |

| 1:12, LVDS Output Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 40 | 6.0 x 6.0 x 0.9 | 5.113 |

| Dual 1:4, LVDS Output Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 28 | 5.0 x 5.0 x 0.8 | 4.363 |

| 1:2,LVPECL Output Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 3.906 |

| Low Phase Noise,1-to-4, 3.3V, 2.5V LVPECL Output Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 3.858 |

| 2:4 LVPECL Output Fanout Buffer | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 3.613 |

| 2:8,LVPECL Output Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 28 | 5.0 x 5.0 x 0.8 | 5.249 |

| 2:12,3.3V,2.5V LVPECL Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 40 | 6.0 x 6.0 x 0.9 | 12.25 |

| Dual 1:2, 3.3V, 2.5V LVPECL Output Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 16 | 3.0 x 3.0 x 1.0 | 3.763 |

| Dual 1:4, 3.3V, 2.5V LVPECL Output Fanout Buffer | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 28 | 5.0 x 5.0 x 0.8 | 5.044 |

| Dual 1:6, 3.3V, 2.5V LVPECL Output Fanout Buffer | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 40 | 6.0 x 6.0 x 0.9 | 6.353 |

| デュアル1:8、3.3V、2.5V LVPECL出力ファンアウトバッファ | RF Buffers | -40 to 85°C | VFQFPN | 48 | 7.0 x 7.0 x 0.9 | 7.522 |

| 1:18, 2.5V, 3.3V Selectable LVPECL or LVDS Fanout Buffer | RF Buffers | -40 to 85°C | VFQFPN | 48 | 7.0 x 7.0 x 0.9 | 15.34 |

| Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 81 | 8.0 x 8.0 x 1.35 | 18.45 |

| Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 81 | 8.0 x 8.0 x 1.35 | |

| JESD204B/C Clock Jitter Attenuator | Jitter Attenuators with Frequency Translation | -40 to 85°C | CABGA | 81 | 8.0 x 8.0 x 1.35 | 23.06 |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 100 | 11.0 x 11.0 x 1.2 | |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 100 | 11.0 x 11.0 x 1.2 | |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 100 | 11.0 x 11.0 x 1.2 | |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 100 | 11.0 x 11.0 x 1.2 | 17.56 |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 100 | 11.0 x 11.0 x 1.2 | |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 100 | 11.0 x 11.0 x 1.2 | |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | VFQFPN | 88 | 10.0 x 10.0 x 0.9 | |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | CABGA | 100 | 11.0 x 11.0 x 1.2 | |

| JESD204B/C クロックジッタ減衰器 | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | VFQFPN | 88 | 10.0 x 10.0 x 0.9 | 14.31 |

| JESD204B/C Clock Jitter Attenuator | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | VFQFPN | 88 | 10.0 x 10.0 x 0.9 | 15.54 |

| 無線シンクロナイザ | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | VFQFPN | 88 | 10.0 x 10.0 x 0.9 | 26.94 |

| JESD204B/C クロックジッタ減衰器 | Radio Synchronizers & JESD204B/C Clock Jitter Attenuators | -40 to 85°C | VFQFPN | 76 | 9.0 x 9.0 x 0.85 | 14.63 |

| JESD204B Compliant Fanout Buffer and Divider | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 64 | 9.0 x 9.0 x 0.9 | |

| JESD204B/C準拠のファンアウトバッファ及び分周器 | RF Buffers | -40 to 85°C (Tc ≤ 105°C) | VFQFPN | 64 | 9.0 x 9.0 x 0.9 | 13.83 |

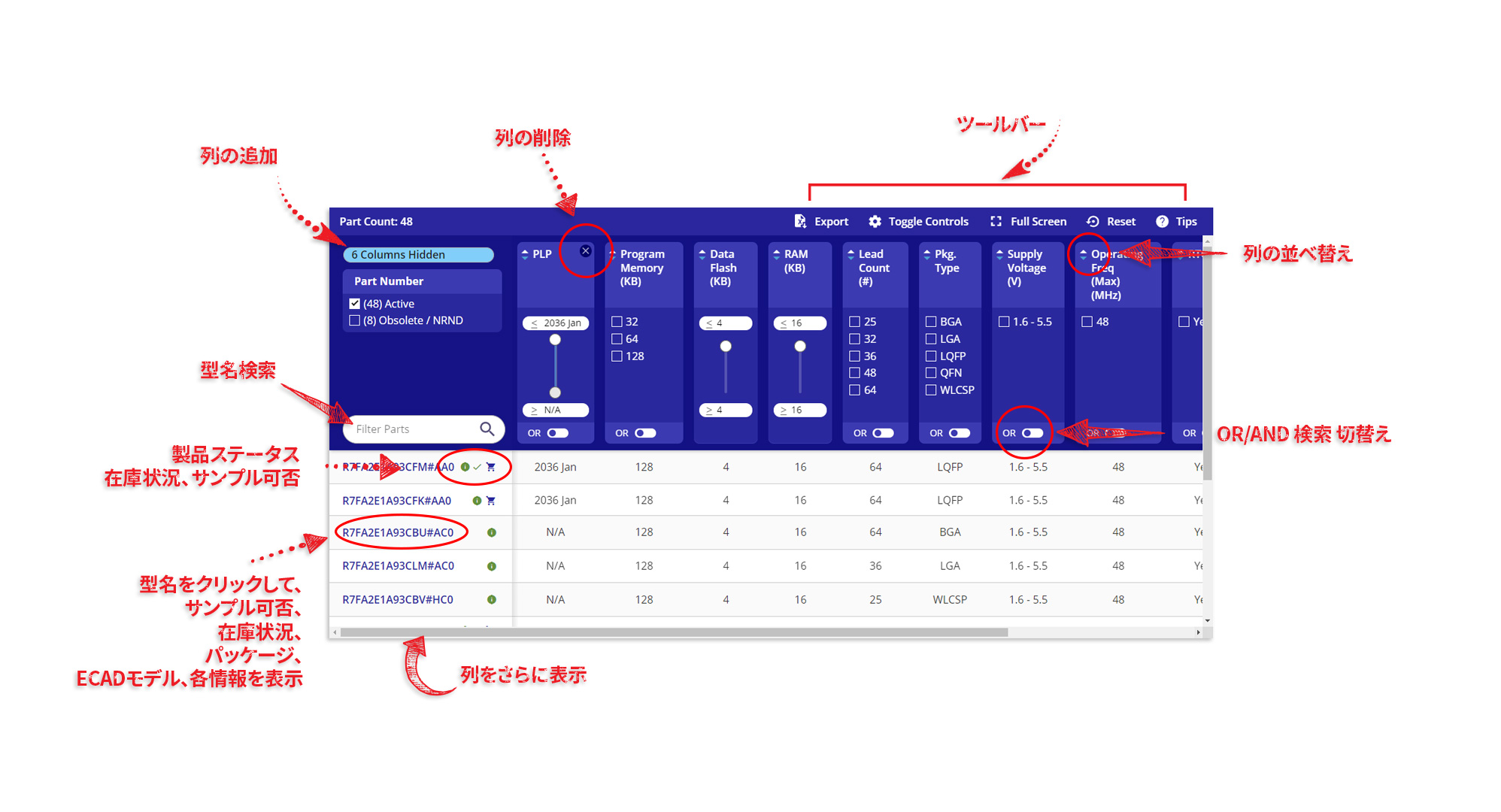

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

ビデオ&トレーニング

This video introduces the industry’s first fully-integrated synchronizer for 5G enhanced common public radio interface (eCPRI) radio synchronization.

ニュース&ブログ

| Selecting the Best Device for Converter Clocking Applications | ブログ | 2022年2月1日 | |

|

5Gネットワークシステムの構築を容易化するIEEE1588対応のLinuxベース高精度時刻同期ソフトウェア「PTP Clock Manager」を提供開始 | ニュース | 2021年2月2日 |

|

Your Guide to Executing pcm4l Software Flawlessly | ブログ | 2021年1月30日 |

|

5Gやブロードバンド無線用途に向け、業界最高クラスの性能を誇る広帯域ミリ波シンセサイザを発売 | ニュース | 2020年3月11日 |