# RENESAS

# Bench-Testing Important DC-Parameters of Operational Amplifiers

Today many engineers rely on Spice models when assessing the performance of operational amplifiers (op-amps). If you suspect a Spice model to be inaccurate or lacking certain parameters, you can build your own op-amp test system and still determine the key device parameters.

This application note discusses a universal test circuit that allows you to measure the key DC parameters of an op-amp on your lab workbench.

# Contents

| 1. | DC F | Parameters                                                          | 2 |

|----|------|---------------------------------------------------------------------|---|

|    | 1.1  | Servo-Loop Operating Principle                                      | 3 |

|    | 1.2  | Input Errors of the AUX Op-Amp are Negligible                       | 4 |

|    | 1.3  | Input Offset Voltage, V <sub>OS</sub> , Measurement                 |   |

|    | 1.4  | Negative Input Bias Current, I <sub>B-</sub> , Measurement          |   |

|    | 1.5  | Positive Input Bias Current, I <sub>B+</sub> , Measurement          |   |

|    | 1.6  | DC Open-Loop Gain, A <sub>OL(DC)</sub> , Measurement                |   |

|    | 1.7  | DC Common-Mode Rejection Ratio, CMRR <sub>(DC)</sub> , Measurement  |   |

|    | 1.8  | DC Power Supply Rejection Ratio, PSRR <sub>(DC)</sub> , Measurement |   |

|    | 1.9  | Measurement Results for the Dual Op-Amp ISL28325                    |   |

| 2. | Revi | ision History                                                       | 9 |

# 1. DC Parameters

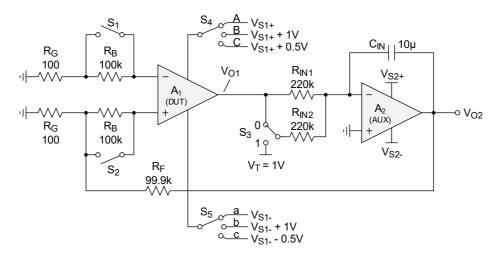

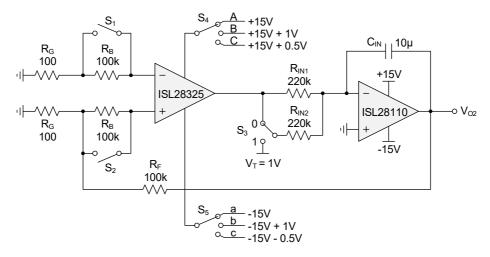

The test circuit in Figure 1 enables you to measure the key DC parameters of an op-amp Device Under Test (DUT) with the help of an auxiliary amplifier (AUX) in a servo-loop configuration.

Figure 1. Test Circuit for Measuring Key DC Parameters of Op-Amps

The various DC parameters measurable with this circuit and their corresponding switch positions are listed in Table 1.

| Parameter Measurements |                 | Switch Positions <sup>[1]</sup> |                |                |                |                |

|------------------------|-----------------|---------------------------------|----------------|----------------|----------------|----------------|

| Farameter meas         |                 |                                 | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> |

|                        | V <sub>OS</sub> | 1                               | 1              | 0              | А              | а              |

|                        | I <sub>B-</sub> | 0                               | 1              | 0              | А              | а              |

| DC (Output = TP1)      | I <sub>B+</sub> | 1                               | 0              | 0              | А              | а              |

|                        | A <sub>OL</sub> | 1                               | 1              | 1              | А              | а              |

|                        | CMRR            | 1                               | 1              | 0              | В              | b              |

|                        | PSRR            | 1                               | 1              | 0              | С              | С              |

Table 1. Switch Positions for Measuring the Key DC Parameters of an Op-Amp

1. For S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>: 1 = closed, 0 = open

The circuit uses dual supplies but works well for both single-supply and dual-supply op-amps. It basically amplifies the input error voltages of the DUT and makes them available at the output of the AUX amplifier.

For the DUT, apply the nominal supply voltage in dual supply fashion, even for a single-supply op-amp. For example, in the case of a 3.3V single supply op-amp, make  $V_{S1} = \pm 1.65V$ .

For the AUX amplifier, select an op-amp with large dual supply rails of  $\pm 12V$  to  $\pm 20V$  to obtain a wide dynamic output voltage range at V<sub>O2</sub>. The AUX amplifier does not need to be a precision amplifier but can be a general-purpose op-amp because the impact of its input errors on the measurement accuracy are negligible. This is explained in section Input Errors of the AUX Op-Amp are Negligible.

## 1.1 Servo-Loop Operating Principle

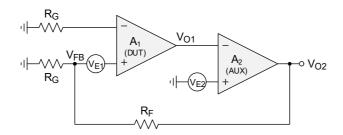

The operation of the servo or negative feedback loop is shown in Figure 2. Here, the DUT operates at open-loop gain. For better understanding, we can separate the DUT into an ideal op-amp with the external input DC error voltage,  $V_E$ . At t = 0,  $V_E$  is amplified by the high DC open-loop gain of the DUT; therefore, driving the output voltage ( $V_{O1}$ ) to one of the supply rails, in this case the positive rail ( $V_{S1+}$ ). This abrupt rise of  $V_{O1}$  is converted into gradually declining, negative output voltage,  $V_{O2}$ , by the integrator.  $V_{O2}$  is attenuated by the R<sub>F</sub>-R<sub>G</sub> voltage divider and fed back to the positive input of the DUT as feedback voltage ( $V_{FB}$ ):  $V_{FB} = V_{FB} \times \beta$ . As the feedback factor is the reciprocal of the circuit gain,  $\beta = 1/G$ , we can also write:  $V_{FB} = V_{O2}/G$ .

Figure 2. Servo-Loop Operation

With  $V_{FB}$  having the opposite polarity of  $V_E$ , the sum,  $V_E + V_{FB}$ , results in a smaller negative  $V_{O1}$ . This causes the integrator to integrate towards a smaller positive  $V_{O2}$ .

This regulating process continues until V<sub>O1</sub> equals the positive input of the AUX amplifier, which is 0V. At that point, the current into the integrator is zero, the integration stops, and V<sub>O</sub> remains constant. If V<sub>O1</sub> = 0V, the total input error must be also zero volt:  $V_{FB} + V_E = 0V$ , which requires that  $V_E = -V_{FB}$ .

To express the input error through the output voltage, we can substitute  $V_{FB}$  with  $V_{FB} = V_{O2}/G$  and receive  $V_E = -V_{O2}/G$ . This means that the input error voltage is the measured inverted output voltage, divided by the circuit gain.

### **1.2** Input Errors of the AUX Op-Amp are Negligible

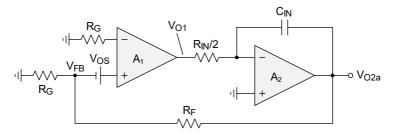

Figure 3 depicts the simplified test circuit in the steady state, when  $V_{O2}$  has stabilized and remains constant. In this state,  $C_{IN}$  is fully charged and high-impedance and no current flows through  $R_{IN}$ . Therefore, both components can be omitted, indicating that  $A_2$  operates at open-loop gain. The input errors of each op-amp are consolidated in the error voltages,  $V_{E1}$  and  $V_{E2}$ .

Figure 3. Test Circuit with Input Error Voltages,  $\rm V_{E1}$  and  $\rm V_{E2}$

To determine the impact of  $V_{E2}$  on the circuit output voltage, we establish the equation for  $V_{O2}$  with:

(EQ. 1)  $V_{O2} = A_2(V_{E2} - V_{O1})$

The output voltage of  $A_1$  is derived in the same way:

(EQ. 2)  $V_{O1} = A_1(V_{E1} + V_{FB} - 0) = A_1(V_{E1} + V_{FB})$

As mentioned earlier, the feedback voltage equals the output voltage divided by the circuit gain:

(EQ. 3)

$$V_{FB} = V_{O2}/G$$

with  $G = 1 + R_F/R_G$

Then, inserting Equation 2 and Equation 3 into Equation 1 and solving for V<sub>O2</sub> gives:

(EQ. 4)

$$V_{O2} = -G \times (V_{E1} - V_{E2}/A_1)$$

Equation 4 shows that the input errors of  $A_2$  are suppressed by the high DC open-loop gain of  $A_1$ , which reduces the error contribution of  $A_2$  to zero:  $V_{E2}/A_1 \approx 0$ . Therefore, the output voltage solely represents the input error of  $A_1$  amplified by the circuit gain:

(EQ. 5)  $V_{O2} = -V_{E1} \times G$

### 1.3 Input Offset Voltage, V<sub>OS</sub>, Measurement

Figure 4 shows the equivalent test circuit for measuring  $V_{OS}$  of  $A_1$ . Here, the switches  $S_1$  and  $S_2$  are closed, shunting the input bias resistors  $R_B$ . The input bias currents still flow through the gain resistors,  $R_G$ , but their voltages across these resistors are much smaller than  $V_{OS}$  and therefore, can be ignored.

Figure 4. Equivalent DC Test Circuit for measuring  $\mathrm{V}_{\mathrm{OS}}$

Because the steady state of  $V_{O2}$  is reached when  $V_{O1}$  is zero, we can write the equation for  $V_{O1}$  as:

(EQ. 6)

$$V_{O1} = 0 = A_1(V_{OS} + V_{FB} - 0)$$

With  $V_{FB} = V_{O2}/G$ , solving for  $V_{OS}$  yields  $V_{OS} = -V_{O2}/G$ .

Because  $V_{O2}$  is going to change for each parametric measurement, we distinguish between the various  $V_{O2}$  values through indices. In the case of the  $V_{OS}$  measurement, we denote the output voltage as  $V_{O2a}$ :

(EQ. 7)

$$V_{OS} = 0 = \frac{V_{O2a}}{G}$$

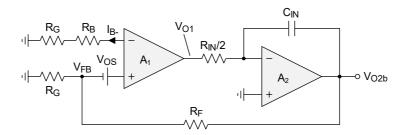

### 1.4 Negative Input Bias Current, I<sub>B-</sub>, Measurement

To measure  $I_{B-}$ , switch  $S_1$  is opened and  $S_2$  remains closed. This inserts a large bias resistor,  $R_B >> R_G$ , into the inverting input path, causing  $V_{O2}$  to change from  $V_{O2a}$  to  $V_{O2b}$ .

The equation for  $V_{O1}$  now includes the large voltage drop across  $R_B$  due to  $I_{B-}$ :

(EQ. 8)  $V_{O1} = 0 = V_{OS} + V_{FB} - I_{B-} \times R_B = V_{OS} + \frac{V_{O2b}}{G} - I_{B-} \times R_B$

Figure 5. Inserting  $R_B$  into the inverting Input Path to measure  $I_{B-}$

Then, solving for I<sub>B-</sub> yields: I<sub>B-</sub> =  $\frac{1}{R_B} \left( V_{OS} + \frac{V_{O2b}}{G} \right)$ , and substituting V<sub>OS</sub> with the term in Equation 7 gives:

(EQ. 9)

$$I_{B-} = \frac{1}{R_B} \left( \frac{V_{O2b} - V_{O2a}}{G} \right)$$

#### **1.5** Positive Input Bias Current, I<sub>B+</sub>, Measurement

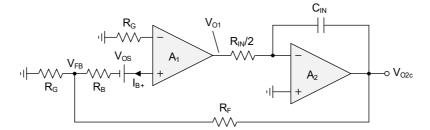

To measure  $I_{B+}$ , switch  $S_2$  is opened and  $S_1$  is closed. This inserts a large bias resistor,  $R_B$ , into the non-inverting input path, causing  $V_{O2}$  to change from  $V_{O2a}$  to  $V_{O2c}$ .

Figure 6. Inserting  $R_B$  into the Non-Inverting Input Path to Measure  $I_{B+}$

The equation for  $V_{O1}$  now includes the large voltage drop across  $R_B$  due to  $I_{B+}$ :

(EQ. 10)  $V_{O1} = 0 = V_{OS} + V_{FB} = V_{OS} + I_{B+} \times R_B + \frac{V_{O2c}}{G}$

Then, solving for I<sub>B+</sub> yields:  $I_{B+} = -\frac{1}{R_B} \left( V_{OS} + \frac{V_{O2c}}{G} \right)$ , and substituting V<sub>OS</sub> with the term in Equation 7 gives:

(EQ. 11)  $I_{B+} = \frac{1}{R_B} \left( \frac{V_{O2a} - V_{O2c}}{G} \right)$

*Note:* For op-amps with high bias currents, the output of  $A_2$  can saturate. In this case, reduce the value of  $R_B$  (typically by a factor of 10) until the output of  $A_2$  stays within the supply rails.

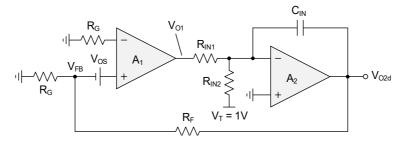

# 1.6 DC Open-Loop Gain, A<sub>OL(DC)</sub>, Measurement

To measure the DC open-loop gain, switches  $S_1$  and  $S_1$  are closed, and  $S_3$  connects  $R_{IN2}$  to the test voltage,  $V_T$  (Figure 7). Now,  $V_{O2}$  reaches the steady state when  $V_{O1}$  = - $V_T$  and no charge current flows.

Figure 7. Applying a Test Voltage, V<sub>T</sub>, to Measure A<sub>1</sub> at DC

Except for V<sub>T</sub>, the circuit is identical to the one, measuring V<sub>OS</sub>. Therefore, we can apply Equation 6 with the modification that  $V_{O1} = -V_T$  and  $V_{O2}$  changes from  $V_{O2a}$  to  $V_{O2d}$ .

(EQ. 12)

$$V_{O1} = -V_T = A(V_{OS} + V_{FB}) = A_1 \left( V_{OS} + \frac{V_{O2d}}{G} \right)$$

Then solving for A<sub>1</sub> gives: A<sub>1</sub> =  $\frac{-V_T}{V_{OS} + \frac{V_{O2d}}{G}}$  and substituting V<sub>OS</sub> with the term in Equation 7 yields:

(EQ. 13)  $A_1 = \frac{V_T \times G}{V_{O2a} - V_{O2d}}$

*Note:* Making  $V_T$  = 1V, reduces Equation 13 to:

(EQ. 14)

$$A_1 = \frac{G}{V_{O2a} - V_{O2d}}$$

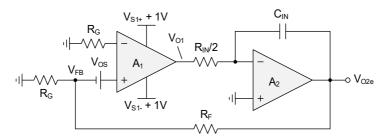

## 1.7 DC Common-Mode Rejection Ratio, CMRR<sub>(DC)</sub>, Measurement

The common-mode rejection ratio (CMRR) of an op-amp is the ratio of the applied change in common-mode voltage to the change in offset voltage (due to a change in common-mode voltage):

(EQ. 15)

$$CMRR = \frac{A_{DM}}{A_{CM}} = \frac{\Delta V_O / \Delta V_{OS}}{\Delta V_O / \Delta V_{CM}} = \frac{\Delta V_{CM}}{\Delta V_{OS}}$$

In the circuit of Figure 8, the common-mode voltage is not applied to the input terminals of A<sub>1</sub>, where low-level effects could disrupt the measurement, but to the power-supply voltages instead. Here, both supply rails are altered in the same (common) direction by  $\Delta V_{CM} = +1V$ , relative to the input.

Figure 8. Changing A<sub>1</sub> Supply Voltages in a Common Direction to Measure CMRR at DC

The input offset voltage at V<sub>S1+</sub> and V<sub>S1-</sub> is given in Equation 7 with V<sub>OS</sub> = -V<sub>O2a</sub>/G. A change in input offset because of a common-mode change of V<sub>S1</sub> can therefore be expressed through V<sub>OS(CM)</sub> = -V<sub>O2e</sub>/G. This makes  $\Delta V_{OS}$ :

(EQ. 16)

$$\Delta V_{OS} = V_{OS} - V_{OS(CM)} = \frac{V_{O2e} - V_{O2a}}{G}$$

Then, inserting Equation 15 into Equation 14 gives the common-mode rejection ratio:

(EQ. 17)

$$CMRR_{(DC)} = \frac{G \times \Delta V_{CM}}{V_{O2e} - V_{O2a}}$$

*Note:* Making  $\Delta V_{CM}$  = +1V, reduces Equation 17 to:

(EQ. 18)  $CMRR_{(DC)} = \frac{G}{V_{O2e} - V_{O2a}}$

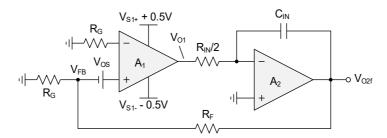

# 1.8 DC Power Supply Rejection Ratio, PSRR<sub>(DC)</sub>, Measurement

The power supply rejection ratio (PSRR) of an op-amp is the ratio of a change in supply voltage to the change in offset voltage.

(EQ. 19) PSRR =  $\frac{\Delta V_S}{\Delta V_{OS}}$

In the circuit of Figure 9, the positive rail is increased by 0.5V and the negative rail is decreased by -0.5V, therefore, resulting in a total supply change of  $\Delta V_{S1} = +1V$ .

Figure 9. Changing A1 total Supply Voltage to Measure PSRR at DC

Again, the input offset voltage at V<sub>S1+</sub> and V<sub>S1-</sub> is V<sub>OS</sub> = -V<sub>O2a</sub>/G, and the input offset voltage due to the change in total supply by  $\Delta V_{S1}$  is V<sub>OS(PS)</sub> = -V<sub>O2f</sub>/G. This makes  $\Delta V_{OS}$ :

(EQ. 20)

$$\Delta V_{OS} = V_{OS} - V_{OS(PS)} = \frac{V_{O2f} - V_{O2a}}{G}$$

Then, inserting Equation 20 into Equation 19 gives the power supply rejection ratio:

(EQ. 21)

$$PSRR_{(DC)} = \frac{G \times \Delta V_{S1}}{V_{O2f} - V_{O2a}}$$

*Note:* Making  $\Delta V_S$  = +1V, reduces Equation 21 to:

$(\textbf{EQ. 22}) \quad \textbf{PSRR}_{(DC)} = \frac{G}{V_{O2f} - V_{O2a}}$

### 1.9 Measurement Results for the Dual Op-Amp ISL28325

As a final check, the discussed DC parameters of the dual op-amp, ISL28325, were measured with the test circuit in Figure 10. Table 2 lists the measured results and the calculated parameters in comparison with the corresponding datasheet values.

Figure 10. DC-Test Circuit for Dual Op-Amp ISL28325

| Measured V <sub>O2</sub> |         | Equations Applied                                                         | Calculated Parameter |          | Datasheet Value |

|--------------------------|---------|---------------------------------------------------------------------------|----------------------|----------|-----------------|

| V <sub>O2a</sub>         | -0.0188 | V <sub>OS</sub> = -V <sub>O2a</sub> /G                                    | V <sub>OS</sub>      | 0.019mV  | 0.1mV (typical) |

| V <sub>O2b</sub>         | -0.0168 | $I_{B-} = (V_{O2b} - V_{O2a})/R_B/G$                                      | I <sub>B-</sub>      | 0.020nA  | 0.2nA (typical) |

| V <sub>O2c</sub>         | -0.0183 | I <sub>B+</sub> = (V <sub>O2a</sub> -V <sub>O2c</sub> )/R <sub>B</sub> /G | I <sub>B+</sub>      | -0.005nA | 0.2nA (typical) |

| V <sub>O2d</sub>         | -0.0179 | $A_1 = G/(V_{O2a} - V_{O2d})$                                             | A <sub>OL(DC)</sub>  | 120.8dB  | 110dB (typical) |

| V <sub>O2e</sub>         | -0.0174 | $CMRR_{(DC)} = G/(V_{O2e}-V_{O2a})$                                       | CMRR <sub>(DC)</sub> | 117.0dB  | 80dB (minimum)  |

| V <sub>O2f</sub>         | -0.0177 | $PSRR_{(DC)} = G/(V_{O2f}/V_{O2a})$                                       | PSRR <sub>(DC)</sub> | 118.5dB  | 80dB (minimum)  |

| Table 2. DC-Test | Circuit for Dual | Op-Amp ISL28325                       |

|------------------|------------------|---------------------------------------|

|                  |                  | • • • • • • • • • • • • • • • • • • • |

# 2. Revision History

| R | Revision | Date         | Description      |

|---|----------|--------------|------------------|

|   | 1.00     | Nov 16, 2022 | Initial release. |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/