# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                        |           | Document<br>No.         | TN-RL*-A008A/E                                         | Rev. | 1.00 |

|-----------------------|----------------------------------------------------------------------------------------------------------------|-----------|-------------------------|--------------------------------------------------------|------|------|

| Title                 | Correction for Incorrect Description Notice<br>RL78/I1A Descriptions in the Hardware User<br>Rev. 1.00 Changed | 's Manual | Information<br>Category | Technical Notification                                 |      |      |

|                       |                                                                                                                | Lot No.   |                         |                                                        |      |      |

| Applicable<br>Product | RL78/I1A<br>R5F107xxx                                                                                          | All lots  | Reference<br>Document   | RL78/I1A User's Manu<br>Rev.1.00<br>R01UH0169EJ0100 (、 |      |      |

This document describes misstatements found in the RL78/I1A User's Manual: Hardware Rev.1.00 (R01UH0169EJ0100).

**Corrections**

| Applicable Item                                                                                               | Applicable Page    | Contents                       |

|---------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------|

| Internal data memory space                                                                                    | Page 42            | Specifications extended        |

| Table 3-6. Extended SFR (2nd SFR) List                                                                        | Pages 58 to 69     | Specifications added           |

| High-speed on-chip oscillator frequency select register (HOCODIV)                                             | -                  | Specifications added           |

| 16-bit timer KC output pin control register                                                                   | -                  | Specifications added           |

| (16) Peripheral function switch register 0 (PFSEL0)                                                           | Page 301           | Incorrect descriptions revised |

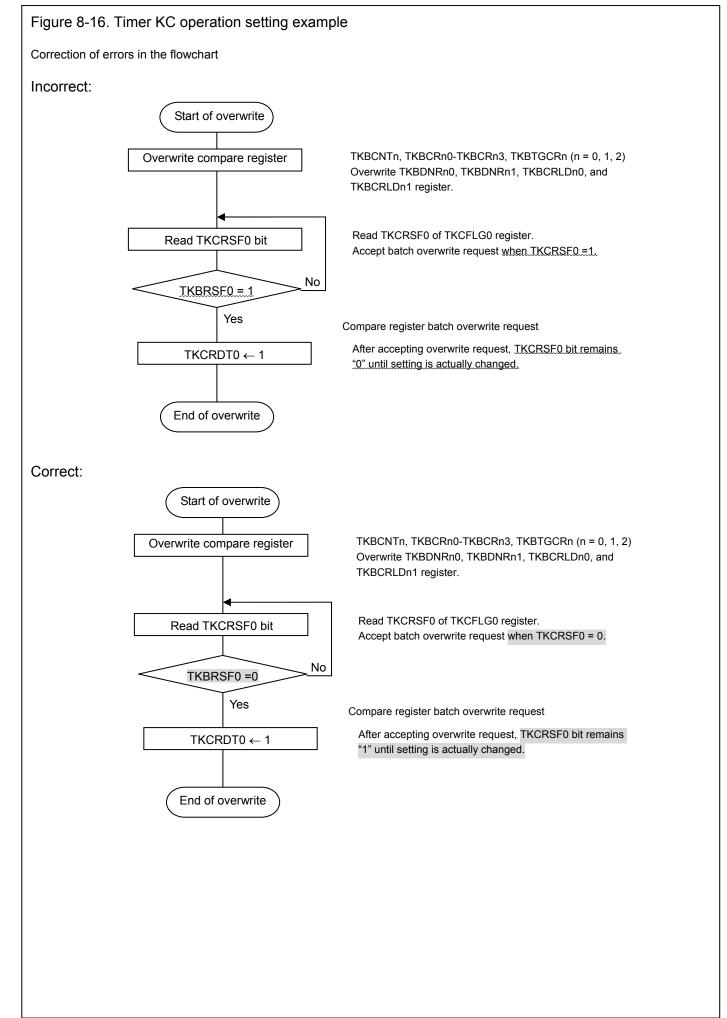

| Figure 8-16. Timer KC operation setting example                                                               | Page 410           | Incorrect descriptions revised |

| A/D converter mode register 0 (ADM0)                                                                          | Page 463           | Incorrect descriptions revised |

| (5)Comparator rising edge enable register 0 (CMPEGP0),<br>comparator falling edge enable register 0 (CMPEGN0) | Page 532           | Incorrect descriptions revised |

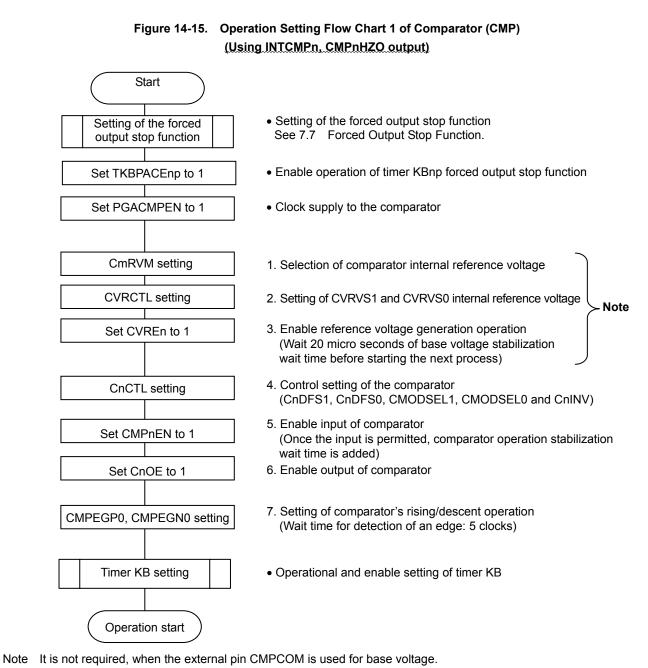

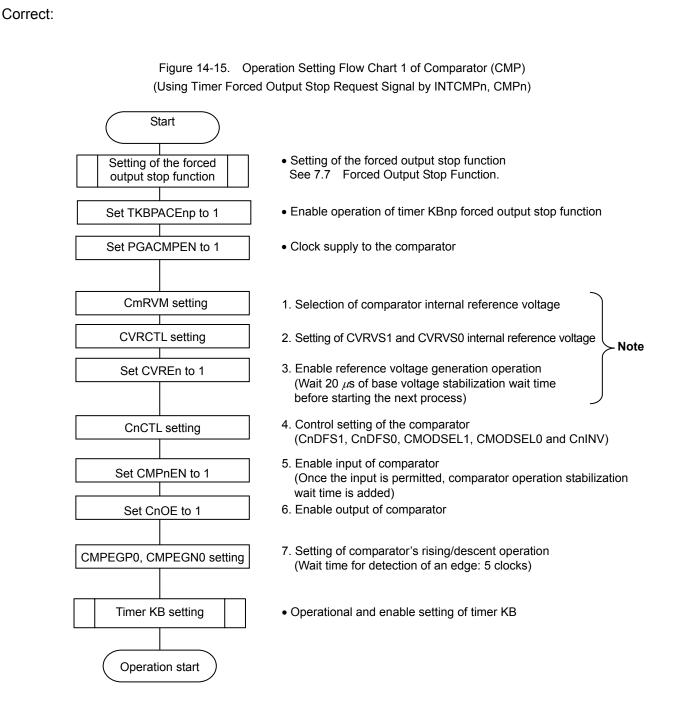

| Figure 14-15. Operation Setting Flow Chart 1 of Comparator                                                    | Page 541           | Incorrect descriptions revised |

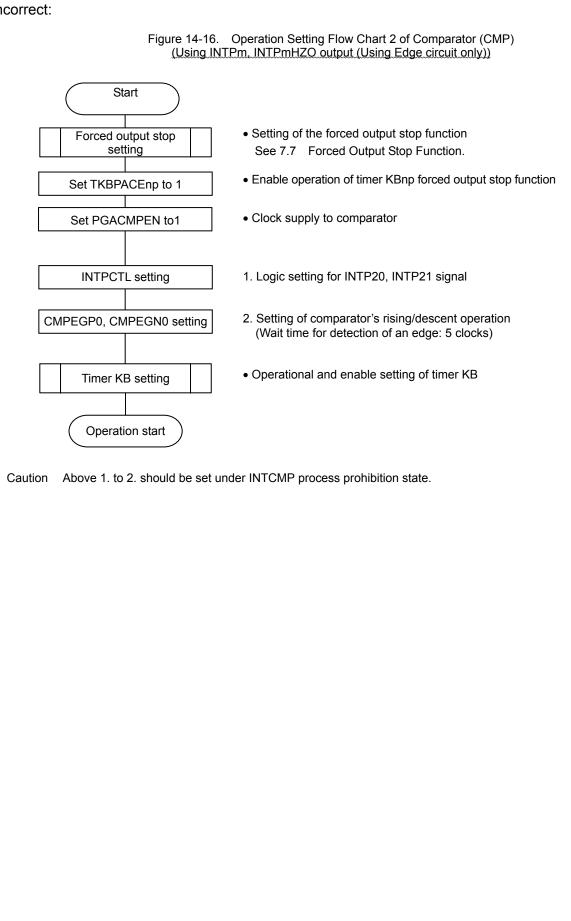

| Figure 14-16. Operation Setting Flow Chart 2 of Comparator                                                    | Page 542           | Incorrect descriptions revised |

| 15. 6. 3 SNOOZE mode function                                                                                 | Page 663           | Specifications changed         |

| 16.6 DALI Mode                                                                                                | Page 732           | Specifications extended        |

| 16.6.1 DALI transmission                                                                                      | Page 735           | Specifications extended        |

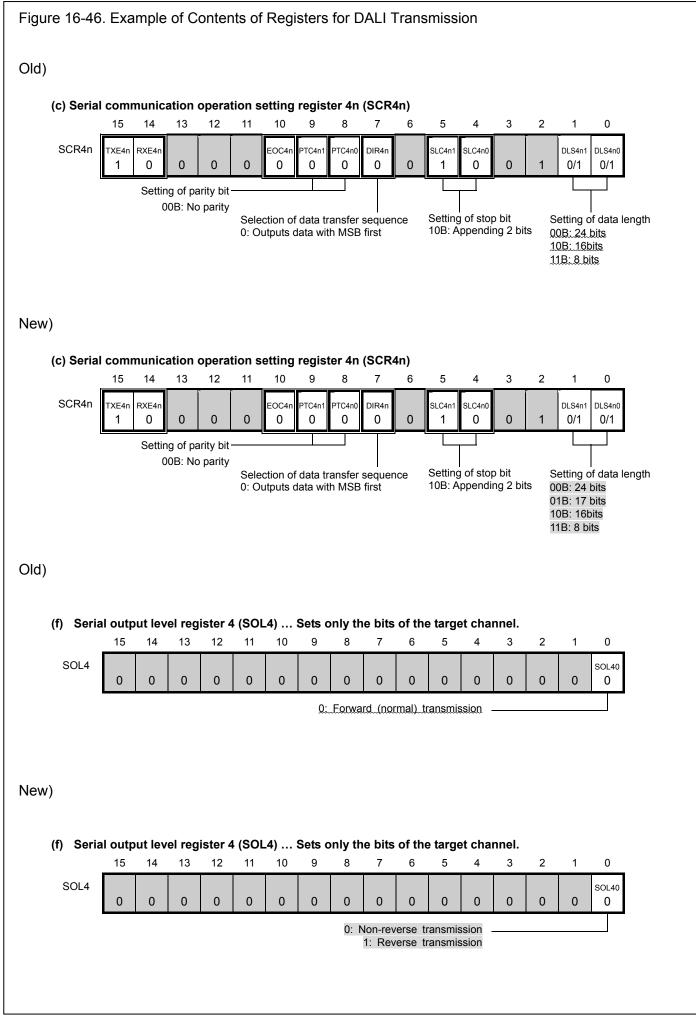

| Figure 16-46. Example of Contents of Registers for DALI Transmission                                          | Pages 736 to 737   | Specifications extended        |

| 16.6.2 DALI reception                                                                                         | Page 743           | Specifications extended        |

| Figure 16-52. Example of Contents of Registers for DALI Reception                                             | Pages 744 to 745   | Specifications extended        |

| 16.7 SNOOZE Mode Function(OnlyDALI/UART4 Reception)                                                           | Pages 750 to 755   | Specifications extended        |

| Figure 20-5. Format of Priority Specification Flag Registers                                                  | Page 903           | Incorrect descriptions revised |

| 21.2.2 STOP mode                                                                                              | Page 931           | Incorrect descriptions revised |

| 21.2.3 SNOOZE mode                                                                                            | Page 934           | Incorrect descriptions revised |

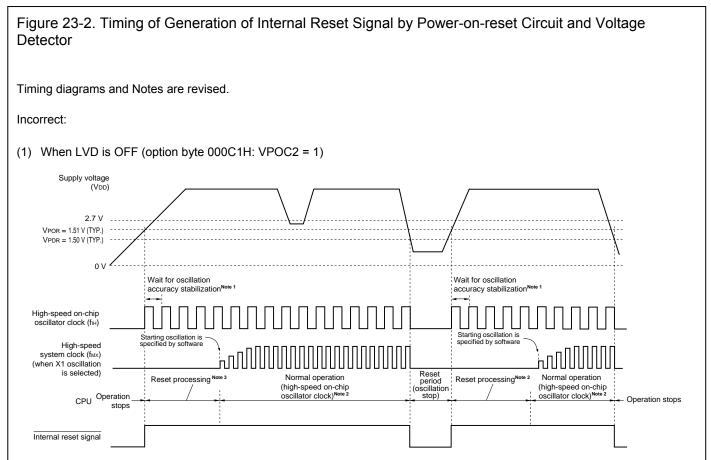

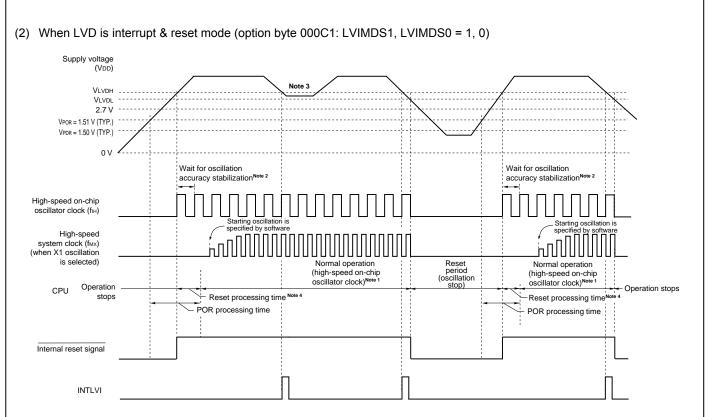

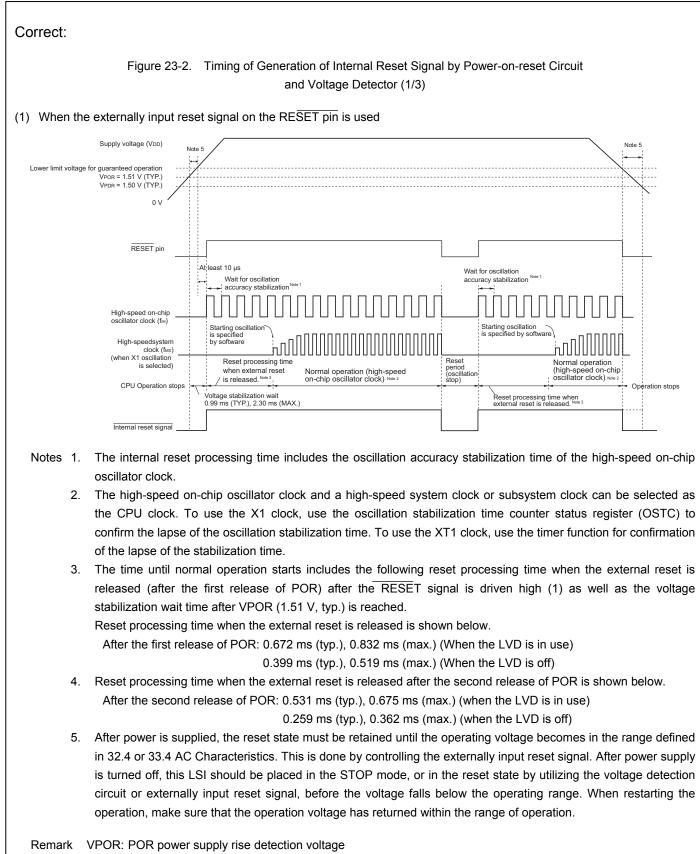

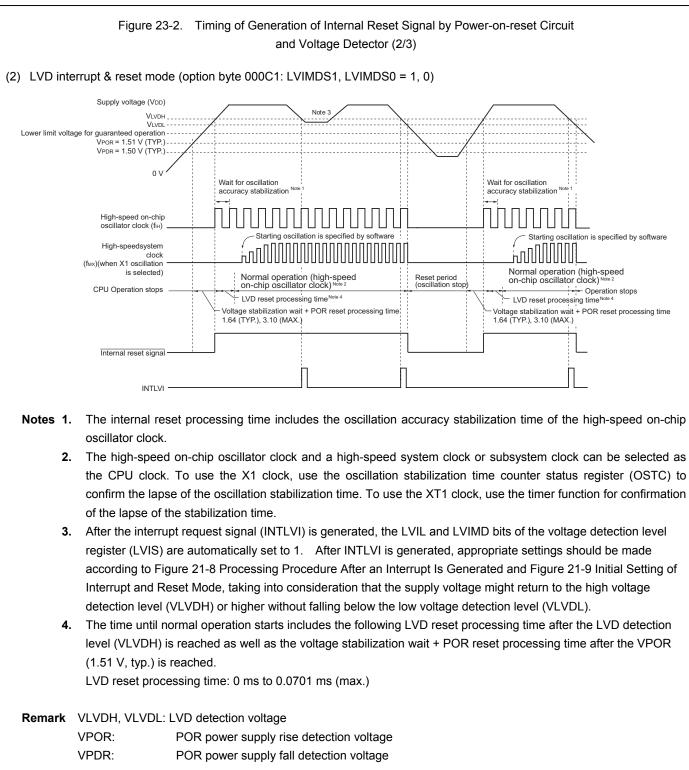

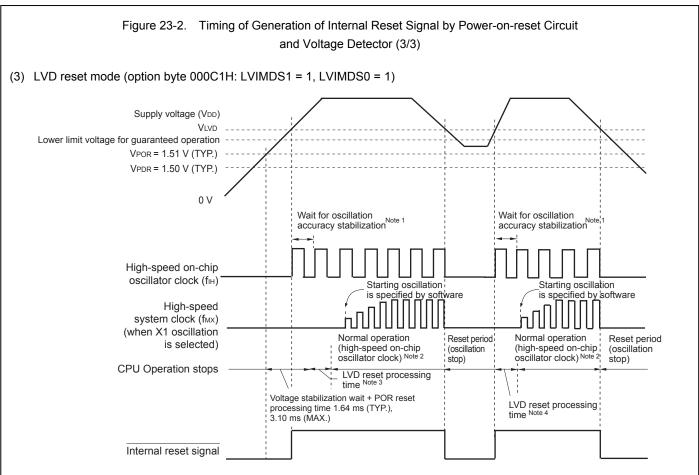

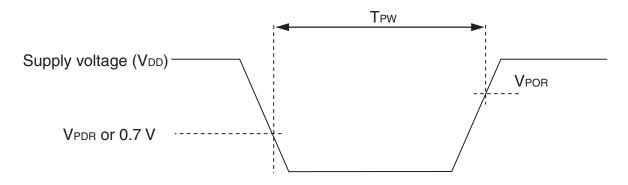

| Figure 23-2. Timing of Generation of Internal Reset Signal by Power-on-reset Circuit and Voltage Detector     | Pages 952 to 953   | Incorrect descriptions revised |

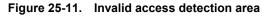

| 25.3.6 Invalid memory access detection function                                                               | Page 984           | Incorrect descriptions revised |

| 27.3 Format of On-chip Debug Option Byte                                                                      | Page 998           | Specifications extended        |

| 28.3.1 Data flash overview                                                                                    | Page 1008          | Caution added                  |

| 28.6 Flash Memory Programming by Self-Programming                                                             | Page 1017          | Caution added                  |

| 32.3.2 Supply current characteristics                                                                         | Pages 1059 to 1062 | Incorrect descriptions revised |

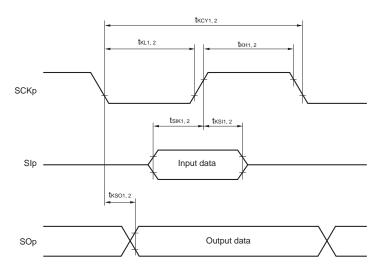

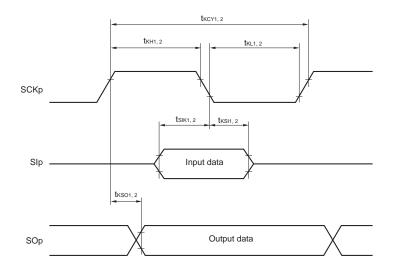

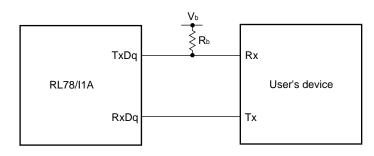

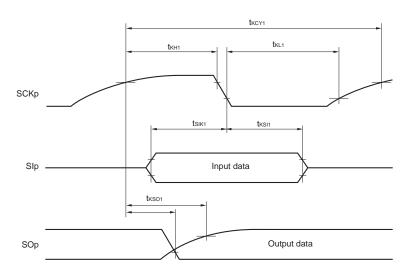

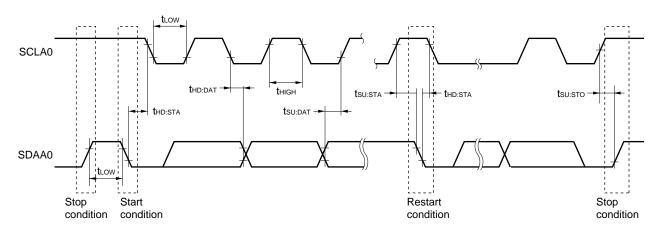

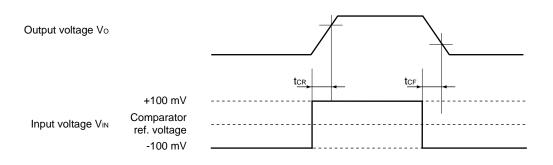

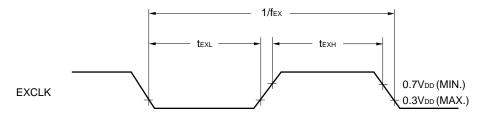

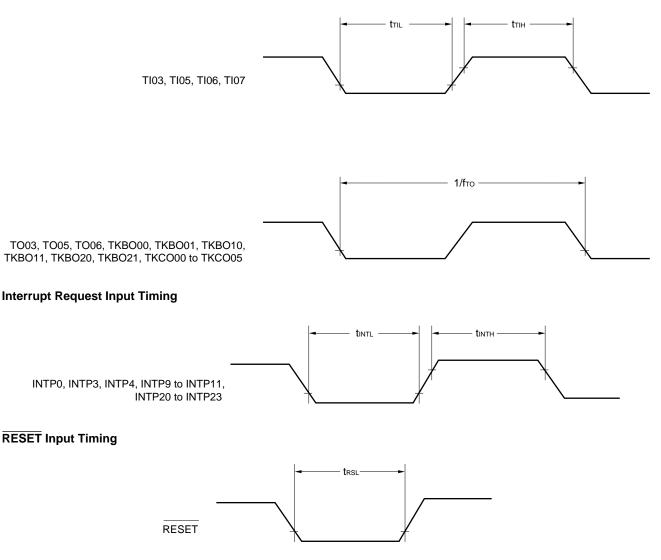

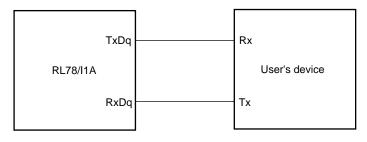

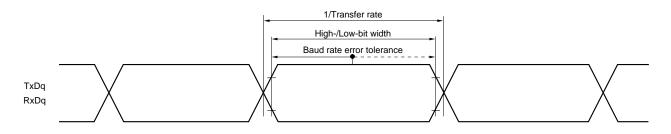

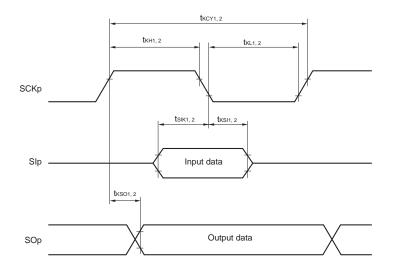

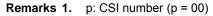

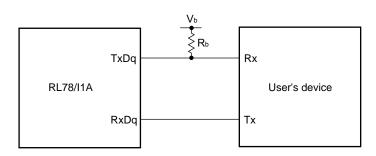

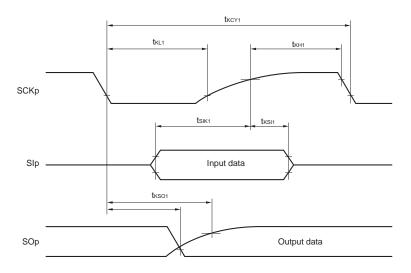

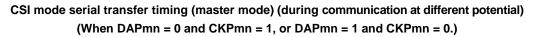

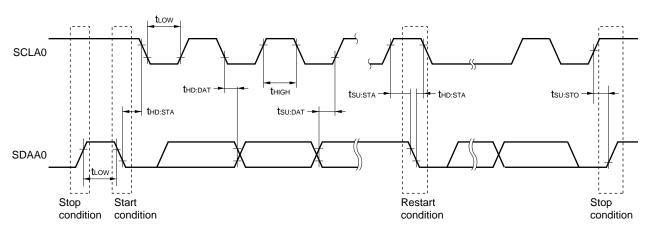

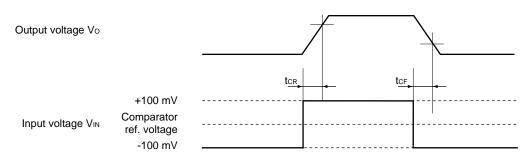

| 32.5 Peripheral Functions Characteristics                                                                     | Pages 1067 to 1080 | Specifications changed         |

| 32.6.1 A/D converter characteristics                                                                          | Pages 1082 to 1085 | Incorrect descriptions revised |

| 32.6.2 Temperature sensor characteristics                                                                     | Page 1085          | Specifications added           |

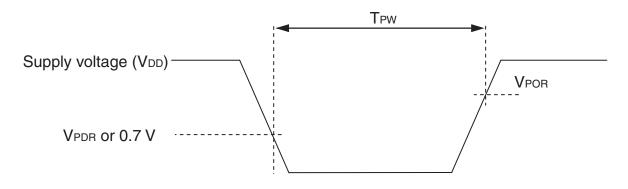

| Supply Voltage Rise Time                                                                                      | -                  | Specifications added           |

| 32.7 Data Memory STOP Mode Low Supply Voltage Data<br>Retention Characteristics                               | Page 1089          | Specifications extended        |

| 32.8 Flash Memory Programming Characteristics                                                                 | Page 1089          | Incorrect descriptions revised |

| 32.9 Timing Specs for Switching Flash Memory<br>Programming Modes                                             | Page 1090          | Incorrect descriptions revised |

| Chapter 33 ELECTRICAL SPECIFICATIONS<br>(for $T_A = -40$ to +125°C product)                                   | -                  | Specifications added           |

#### **Document Improvement**

The above corrections will be made for the next revision of the User's Manual: Hardware.

Corrections in the User's Manual: Hardware

| No. | Corrections and                                                                          | Applicable Items |                    | Pages in this  |

|-----|------------------------------------------------------------------------------------------|------------------|--------------------|----------------|

|     | Document No.                                                                             | English          | R01UH0169EJ0100    | document for   |

|     | Document No.                                                                             | Eligiisti        | R010H0109EJ0100    | corrections    |

| 1   | Internal data memory space                                                               |                  | Page 42            | Page 3         |

| 2   | Table 3-6. Extended SFR (2nd SFR) List                                                   |                  | Pages 58 to 69     | Page 4         |

| 3   | High-speed on-chip oscillator frequency (HOCODIV)                                        | select register  | -                  | Page 5         |

| 4   | 16-bit timer KC output pin control register                                              |                  | -                  | Page 6         |

| 5   | (16) Peripheral function switch register 0 (                                             | PFSEL0)          | Page 301           | Pages 7 to 8   |

| 6   | Figure 8-16. Timer KC operation setting e                                                | xample           | Page 410           | Page 9         |

| 7   | A/D converter mode register 0 (ADM0)                                                     |                  | Page 463           | Page 10        |

| 8   | (5)Comparator rising edge enable<br>(CMPEGP0), comparator falling edge er<br>(CMPEGN0)   |                  | Page 532           | Page 11        |

| 9   | Figure 14-15. Operation Setting Flov<br>Comparator                                       |                  | Page 541           | Pages 12 to 13 |

| 10  | Figure 14-16. Operation Setting Flov<br>Comparator                                       | v Chart 2 of     | Page 542           | Pages 14 to 15 |

| 11  | 15. 6. 3 SNOOZE mode function                                                            |                  | Page 663           | Pages 16 to 17 |

| 12  | 16.6 DALI Mode                                                                           |                  | Page 732           | Page 18        |

| 13  | 16.6.1 DALI transmission                                                                 |                  | Page 735           | Page 19        |

| 14  | Figure 16-46. Example of Contents of Re<br>Transmission                                  | gisters for DALI | Pages 736 to 737   | Page 20        |

| 15  | 16.6.2 DALI reception                                                                    |                  | Page 743           | Page 21        |

| 16  | Figure 16-52. Example of Contents of Re<br>Reception                                     | gisters for DALI | Pages 744 to 745   | Page 21        |

| 17  | 16.7 SNOOZE Mode Function(Or Reception)                                                  | nlyDALI/UART4    | Pages 750 to 755   | Pages 22 to 23 |

| 18  | Figure 20-5. Format of Priority Spe<br>Registers                                         | cification Flag  | Page 903           | Page 24        |

| 19  | 21.2.2 STOP mode                                                                         |                  | Page 928           | Page 25        |

| 20  | 21.2.3 SNOOZE mode                                                                       |                  | Page 934           | Page 26        |

| 21  | Figure 23-2. Timing of Generation of Inter<br>Signal by Power-on-reset Circuit and Volta |                  | Pages 952 to 953   | Pages 27 to 31 |

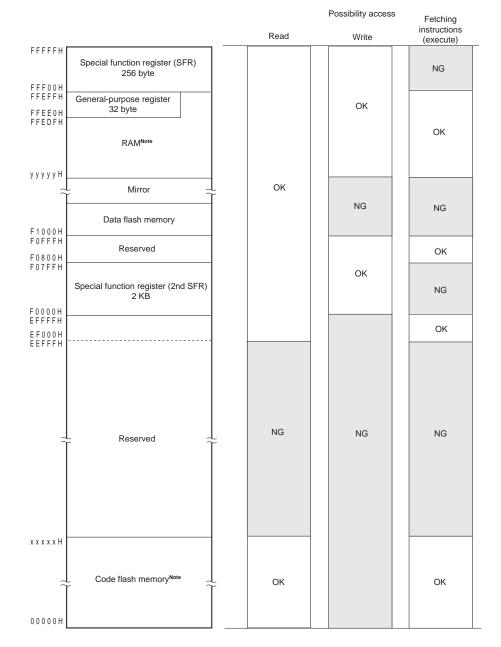

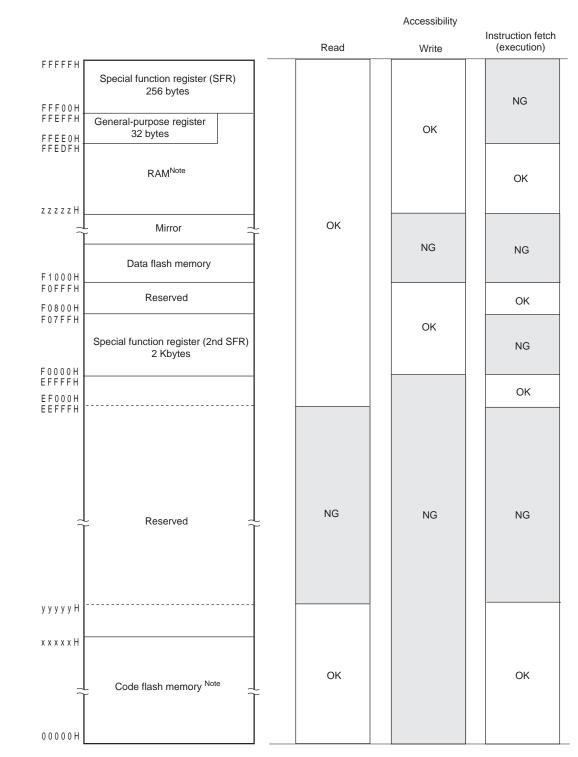

| 22  | 25.3.6 Invalid memory access detection fu                                                | unction          | Page 984           | Pages 32 to 33 |

| 23  | 27.3 Format of On-chip Debug Option Byt                                                  | e                | Page 998           | Pages 34 to 35 |

| 24  | 28.3.1 Data flash overview                                                               |                  | Page 1008          | Page 36        |

| 25  | 28.6 Flash Memory Programming by Self-                                                   | Programming      | Page 1017          | Page 37        |

| 26  | 32.3.2 Supply current characteristics                                                    |                  | Pages 1059 to 1062 | Page 38        |

| 27  | 32.5 Peripheral Functions Characteristics                                                |                  | Pages 1067 to 1080 | Page 38        |

| 28  | 32.6.1 A/D converter characteristics                                                     |                  | Pages 1082 to 1085 | Page 39        |

| 29  | 32.6.2 Temperature sensor characteristics                                                | 6                | Page 1085          | Page 39        |

| 30  | Supply Voltage Rise Time                                                                 |                  | -                  | Page 39        |

| 31  | 32.7 Data Memory STOP Mode Low State Retention Characteristics                           | Supply Voltage   | Page 1089          | Page 39        |

| 32  | 32.8 Flash Memory Programming Charac                                                     | teristics        | Page 1089          | Page 40        |

| 33  | 32.9 Timing Specs for Switching Flash Me<br>Programming Modes                            | emory            | Page 1090          | Page 40        |

| 34  | Chapter 33 ELECTRICAL SPECIFICAT<br>(for T <sub>A</sub> = -40 to +125°C product)         | IONS             | -                  | Page 40        |

Incorrect: Bold with underline: Correct: Gray hatched

<u>Revision History</u> RL78/I1<u>A User's Manual: Hardware Rev.1.00 Correction for Incorrect Description Notice</u>

| Document Number | Date         | Description                             |

|-----------------|--------------|-----------------------------------------|

| TN-RL*-A008A/E  | Aug. 6, 2013 | First edition issued                    |

|                 |              | No.1 to 34 in corrections (This notice) |

## Internal data memory space

## Incorrect:

The internal RAM can be used as a data area and a program area where instructions are written and executed. Four general-purpose register banks consisting of eight 8-bit registers per bank are assigned to the 32-byte area of FFEE0H to FFEEFH of the internal RAM area. However, instructions cannot be executed by using the general-purpose registers. The internal RAM is used as a stack memory.

Cautions 1. It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space for fetchinginstructions or as a stack area.

2. While using the self-programming function and data flash function, the area FFE20H to FFEFFH cannot be used as stack memory. Furthermore, the areas of FEF00H to FF309H also cannot beused with the R5F107AE and R5F107DE.

## Correct:

The internal RAM can be used as a data area and a program area where instructions are fetchod (it is prohibited to use the general-purpose register area for fetching instructions). Four general-purpose register banks consisting of eight 8-bit registers per bank are assigned to the 32-byte area of FFEE0H to FFEFFH of the internal RAM area. The internal RAM is used as stack memory.

Cautions 1. It is prohibited to use the general-purpose register (FFEE0H to FFEFFH) space for fetching instructions or as a stack area.

2. Do not allocate RAM addresses which are used as a stack area, a data buffer, a branch destination of vector interrupt processing, and a DMA transfer destination/transfer source to the area FFE20H to FFEDFH when performing self-programming and rewriting the data flash memory.

3. Use of the RAM areas of the following products is prohibited when performing self-programming and rewriting the data flash memory, because these areas are used for each library. R5F107AE, R5F107DE: FEF00H to FF309H

## Table 3-6. Extended SFR (2nd SFR) List

## TKBCNT0,1,2 and TKCCNT0 registers added in "Extended SFR(2<sup>nd</sup> SFR).

## Old:

## New:

## The following registers are added.

| F0620H | 16-bit timer counter KB0 | TKBCNT0 | R | — | — | $\checkmark$ | FFFFH |

|--------|--------------------------|---------|---|---|---|--------------|-------|

| F0621H |                          |         |   |   |   |              |       |

| F0660H | 16-bit timer counter KB1 | TKBCNT1 | R | - | - |              | FFFFH |

| F0661H |                          |         |   |   |   |              |       |

| F06A0H | 16-bit timer counter KB2 | TKBCNT2 | R | - | - |              | FFFFH |

| F06A1H |                          |         |   |   |   |              |       |

| F06F0H | 16-bit timer counter KC0 | TKCCNT0 | R | _ | _ |              | FFFFH |

## High-speed on-chip oscillator frequency select register (HOCODIV)

High-speed on-chip oscillator frequency select register (HOCODIV) is added.

## Old:

## New:

## High-speed on-chip oscillator frequency select register (HOCODIV)

The frequency of the high-speed on-chip oscillator which is set by an option byte (000C2H) can be changed by using high-speed on-chip oscillator frequency select register (HOCODIV). However, the selectable frequency depends on the FRQSEL3 bit of the option byte (000C2H).

The HOCODIV register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to the value set by FRQSEL2 to FRQSEL0 of the option byte (000C2H).

### Figure 5-12. Format of High-speed On-chip Oscillator Frequency Select Register (HOCODIV)

| Address: | F00A8H | After reset: | the value set by | y FRQSEL2 to | o FRQSEL0 c | of the option by | yte (000C2H) | R/W      |

|----------|--------|--------------|------------------|--------------|-------------|------------------|--------------|----------|

| Symbol   | 7      | 6            | 5                | 4            | 3           | 2                | 1            | 0        |

| HOCODIV  | 0      | 0            | 0                | 0            | 0           | HOCODIV2         | HOCODIV1     | HOCODIV0 |

| HOCODIV2 | HOCODIV1      | HOCODIV0 | High-Speed On-Chip Oscillator Clock Frequency |                     |  |  |

|----------|---------------|----------|-----------------------------------------------|---------------------|--|--|

|          |               |          | FRQSEL3 Bit is 0                              | FRQSEL3 Bit of is 1 |  |  |

| 0        | 0             | 0        | 24 MHz                                        | 32 MHz              |  |  |

| 0        | 0             | 1        | 12 MHz                                        | 16 MHz              |  |  |

| 0        | 1             | 0        | 6 MHz                                         | 8 MHz               |  |  |

| 0        | 1             | 1        | 3 MHz                                         | 4 MHz               |  |  |

| 1        | 0             | 0        | Setting prohibited                            | 2 MHz               |  |  |

| 1        | 0             | 1        | Setting prohibited                            | 1 MHz               |  |  |

| 0        | ther than abo | ve       | Setting p                                     | rohibited           |  |  |

## Caution 1. Set the HOCODIV register within the operable voltage range of the flash operation mode set in the option byte (000C2H) before and after the frequency change.

| Option Byte (00 | 00C2H) Value | Flash Operation Mode      | Operating       | Operating Voltage |

|-----------------|--------------|---------------------------|-----------------|-------------------|

| CMODE1          | CMODE2       | T lash Operation Mode     | Frequency Range | Range             |

| 1               | 0            | LS (low-speed main) mode  | 1 MHz to 8 MHz  |                   |

| 1               | 1            | HS (high-speed main) mode | 1 MHz to 16 MHz | 2.7V to 5.5V      |

|                 |              |                           | 1 MHz to 32 MHz |                   |

2. Set the HOCODIV register with the high-speed on-chip oscillator clock (fill) selected as the CPU/peripheral hardware clock (fcLK).

- 3. After the frequency is changed with the HOCODIV register, the frequency is switched after the following transition time has elapsed.

- Operation for up to three clocks at the pre-change frequency

- CPU/peripheral hardware clock wait at the post-change frequency for up to three clocks

## 16-bit timer KC output pin control register

16-bit timer KC output pin control register is added.

## Old:

## New:

16-bit timer KC output pin contorol register (TOETKC0)

It is the register that controls output enable/disable toward pins for the timer output generated from 16-bit timer KC. The output control of TKCOn is possible regardless of the setting of the timer output gate function which is coupled with 16-bit timer KB.

TOETKC0 can be read by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

| Figure 8-9.  | Format of 16-bit timer KC ou | tout pin contorol | register (TC | DETKC0) |

|--------------|------------------------------|-------------------|--------------|---------|

| i iguic 0-0. |                              | iput pin contoror | register (re |         |

| Address: F05C8 | 3H After | reset: 00H     | R/W           |               |            |          |          |          |

|----------------|----------|----------------|---------------|---------------|------------|----------|----------|----------|

| Symbol         | 7        | 6              | <5>           | <4>           | <3>        | <2>      | <1>      | <0>      |

| TOETKC0        | 0        | 0              | TOETKC05      | TOETKC04      | TOETKC03   | TOETKC02 | TOETKC01 | TOETKC00 |

|                |          |                |               |               |            |          |          |          |

|                | TOETKC0m | Pin of timer c | output TKCO0  | m output enab | le/disable |          |          |          |

|                | 0        | Disables pin   | output of TKC | :00m.         |            |          |          |          |

|                | 1        | Enables pin o  | output of TKC | 00m.          |            |          |          |          |

Remark m = 0 to 5

| (16) Peripheral                              | function s                      | switch reg                     | jister 0 (Pl                          | FSEL0)                                       |                 |                                                          |          |          |

|----------------------------------------------|---------------------------------|--------------------------------|---------------------------------------|----------------------------------------------|-----------------|----------------------------------------------------------|----------|----------|

| Bit explanat                                 | ion is incorre                  | ct and Rema                    | ark added                             |                                              |                 |                                                          |          |          |

| Incorrect:<br>(16) Periphera<br>PFSEL0 selec | al function s<br>ts function se | witch regis<br>etting I/O in p | <b>ter 0 (PFSEL</b><br>beripheral fur | <b>-0)</b><br>nction and 1<br>:<br>(omitted) | 6-bit timers I  | <b0, a<="" kb1,="" th=""><th>nd KB2.</th><th></th></b0,> | nd KB2.  |          |

|                                              |                                 |                                |                                       |                                              |                 |                                                          |          |          |

| Address: F                                   | 05C6H                           | After reset: 00                | )H R/W                                |                                              |                 |                                                          |          |          |

| Symbol                                       | 7                               | <6>                            | <5>                                   | <4>                                          | 3               | 2                                                        | <1>      | <0>      |

| PFSEL0                                       | 0                               | CMP2STEN                       | <b>CMP0STEN</b>                       | PNFEN                                        | ADTRG11         | ADTRG10                                                  | TMRSTEN1 | TMRSTEN0 |

|                                              |                                 |                                |                                       |                                              |                 |                                                          |          |          |

|                                              | CMP2STEN                        | <b>CMP0STEN</b>                |                                       | С                                            | omparator int   | errupt selectio                                          | n        |          |

|                                              | See CHAPTE                      | ER 14 CON                      | IPARATOR.                             |                                              |                 |                                                          |          |          |

|                                              |                                 |                                |                                       |                                              |                 |                                                          |          |          |

|                                              | PNFEN                           |                                |                                       | o not use ext                                | ernal interrupt | INTP20 noise                                             | e filter |          |

|                                              | 0                               | Use noise filt                 |                                       |                                              |                 |                                                          |          |          |

|                                              | 1                               | Do not use no                  | oise filter                           |                                              |                 |                                                          |          |          |

|                                              |                                 |                                |                                       |                                              |                 |                                                          |          |          |

|                                              | ADTRG11                         | ADTRG10                        | <b>T</b> I 1/20/11                    |                                              | rigger selectio | on for A/D con                                           | version  |          |

|                                              | 0                               | 0                              | Timer KB0 trig                        |                                              |                 |                                                          |          |          |

|                                              | 0                               | 1<br>0                         | Timer KB1 tri                         |                                              |                 |                                                          |          |          |

|                                              | 1                               | 1                              | Timer KB2 trig<br>Setting prohib      |                                              |                 |                                                          |          |          |

|                                              | '                               | !                              |                                       |                                              |                 |                                                          |          |          |

|                                              | TMRSTEN1                        |                                | Ļ                                     | Ise selection                                | for external in | terrupt INTP2                                            | 1        |          |

|                                              | 0                               | Can be used                    | to clear STOP                         |                                              |                 |                                                          | -        |          |

|                                              | 1                               |                                | for timer resta                       |                                              |                 |                                                          |          |          |

|                                              |                                 |                                |                                       |                                              |                 |                                                          |          |          |

|                                              | TMRSTEN0                        |                                | Ļ                                     | Ise selection                                | for external in | terrupt INTP2                                            | 0        |          |

|                                              | 0                               | Can be used                    | to clear STOP                         | mode (cann                                   | ot be used for  | timer restart f                                          | unction) |          |

1

Can be used for timer restart function (cannot be used to clear STOP mode)

## Correct:

|            |            |                                                                                             |                 | (omitted)       |                  |                 |          |        |

|------------|------------|---------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|-----------------|----------|--------|

|            |            |                                                                                             |                 | (,              |                  |                 |          |        |

| Address: F | 05C6H      | After reset: 00                                                                             | H R/W           |                 |                  |                 |          |        |

| Symbol     | 7          | <6>                                                                                         | <5>             | <4>             | 3                | 2               | <1>      | <0>    |

| PFSEL0     | 0          | CMP2STEN                                                                                    | <b>CMP0STEN</b> | PNFEN           | ADTRG11          | ADTRG10         | TMRSTEN1 | TMRSTE |

|            |            |                                                                                             |                 |                 |                  |                 |          |        |

|            | CMP2STEN   | <b>CMP0STEN</b>                                                                             |                 | C               | comparator int   | errupt selectic | n        |        |

|            | See CHAPTI | ER 14 CON                                                                                   | IPARATOR.       |                 |                  |                 |          |        |

| -          |            |                                                                                             |                 |                 |                  |                 |          |        |

|            | PNFEN      | Use/Do not use external interrupt INTP20 noise filter                                       |                 |                 |                  |                 |          |        |

|            | 0          | Use noise filt                                                                              | er              |                 |                  |                 |          |        |

|            | 1          | Do not use n                                                                                | oise filter     |                 |                  |                 |          |        |

| _          |            |                                                                                             |                 |                 |                  |                 |          |        |

|            | ADTRG11    | ADTRG10                                                                                     |                 | Timer           | trigger selectio | on for A/D con  | version  |        |

|            | 0          | 0                                                                                           | Timer KB0 trig  | gger source     |                  |                 |          |        |

|            | 0          | 1                                                                                           | Timer KB1 trig  | gger source     |                  |                 |          |        |

|            | 1          | 0                                                                                           | Timer KB2 tri   | gger source     |                  |                 |          |        |

|            | 1          | 1                                                                                           | Setting prohib  | oited           |                  |                 |          |        |

| -          |            |                                                                                             |                 |                 |                  |                 |          |        |

|            | TMRSTEN1   |                                                                                             | Fun             | ction selection | on for external  | interrupt INTF  | P21      |        |

|            | 0          | External interrupt function (external interrupt generation enabled, timer restart disabled) |                 |                 |                  |                 |          | blod)  |

| TMRSTEN0 | Function selection for external interrupt INTP20                                            |  |  |  |

|----------|---------------------------------------------------------------------------------------------|--|--|--|

| 0        | External interrupt function (external interrupt generation enabled, timer restart disabled) |  |  |  |

| 1        | Timer restart function (external interrupt generation disabled, standby release disabled)   |  |  |  |

Timer restart function (external interrupt generation disabled, standby release disabled)

Remark See Block Diagram of Comparator.

1

A/D converter mode register 0 (ADM0)

Incorrect:

A/D converter mode register 0 (ADM0)

(omitted) .

- Caution 1. Change the ADMD, FR2 to FR0, LV1, LV0, and ADCE bits while conversion is stopped or on standby (ADCS = 0).

- 2. Do not change the ADCE and ADCS bits from 0 to 1 at the same time by using an 8-bit manipulation instruction. Be sure to set these bits in the order described in 12.7 A/D Converter Setup Flowchart.

Correct:

A/D converter mode register 0 (ADM0)

: (omitted) :

Cautions 1. Change the ADMD, FR2 to FR0, LV1, and LV0 bits while conversion is stopped (ADCS = 0, ADCE = 0).

- 2. Do not set the ADCS bit to 1 and the ADCE bit to 0 at the same time.

- 3. Do not change the ADCS and ADCE bits from 0 to 1 at the same time by using an 8-bit manipulation instruction. Be sure to set these bits in the order described in 12.7 A/D Converter Setup Flowchart.

(5)Comparator rising edge enable register 0 (CMPEGP0), comparator falling edge enable register 0 (CMPEGN0)

## Incorrect:

Figure 14-6. Format of Comparator Rising Edge Enable Register 0 (CMPEGP0) and Comparator Falling Edge Enable Register 0 (CMPEGN0)

| CEGP7 | CEGN7 | INTP21 pin valid edge selection                                                              |

|-------|-------|----------------------------------------------------------------------------------------------|

| 0     | 0     | Edge detection disabled (disables output of timer forced output stop signal (output signal = |

|       |       | fixed to low level))                                                                         |

| 0     | 1     | Falling edge (enables output of timer forced output stop signal)                             |

| 1     | 0     | Rising edge (enables output of timer forced output stop signal)                              |

| 1     | 1     | Both rising and falling edges (enables output of timer forced output stop signal)            |

| CEGP6 | CEGN6 | INTP20 pin valid edge selection                                                              |

|-------|-------|----------------------------------------------------------------------------------------------|

| 0     | 0     | Edge detection disabled (disables output of timer forced output stop signal (output signal = |

|       |       | fixed to low level))                                                                         |

| 0     | 1     | Falling edge (enables output of timer forced output stop signal)                             |

| 1     | 0     | Rising edge (enables.output of timer forced.output stop.signal)                              |

| 1     | 1     | Both rising and falling edges (enables output of timer forced output stop signal)            |

## Correct:

## Figure 14-6.Format of Comparator Rising Edge Enable Register 0 (CMPEGP0) and Comparator Falling Edge Enable Register 0 (CMPEGN0)

| CEGP7 | CEGN7 | INTP21 pin valid edge selection                                                                |

|-------|-------|------------------------------------------------------------------------------------------------|

| 0     | 0     | Edge detection disabled (disables output of timer restart signal (output signal = fixed to low |

|       |       | level))                                                                                        |

| 0     | 1     | Falling edge (enables output of timer restart signal)                                          |

| 1     | 0     | Rising edge (enables output of timer restart signal)                                           |

| 1     | 1     | Both rising and falling edges (enables output of timer restart signal)                         |

| CEGP6 | CEGN6 | INTP20 pin valid edge selection                                                                |

|-------|-------|------------------------------------------------------------------------------------------------|

| 0     | 0     | Edge detection disabled (disables output of timer restart signal (output signal = fixed to low |

|       |       | level))                                                                                        |

| 0     | 1     | Falling edge (enables output of timer restart signal)                                          |

| 1     | 0     | Rising edge (enables output of timer restart signal)                                           |

| 1     | 1     | Both rising and falling edges (enables output of timer restart signal)                         |

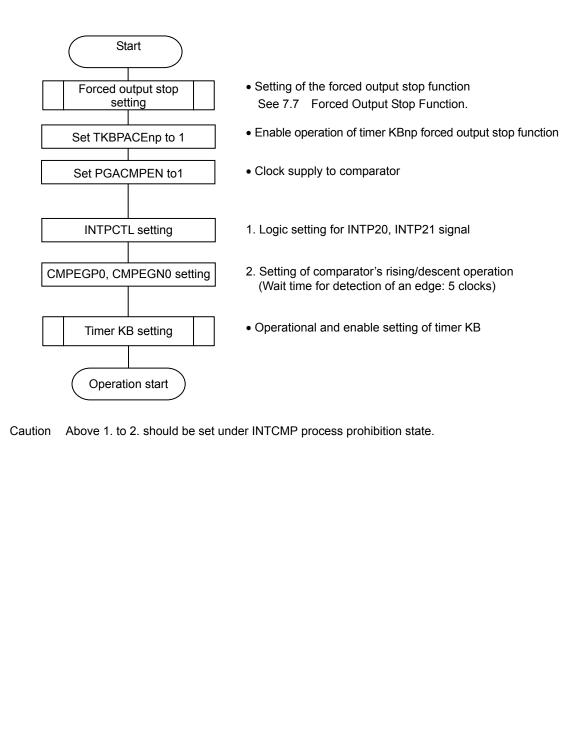

## Figure 14-15. Operation Setting Flow Chart 1 of Comparator

## Incorrect:

Caution Above 1. to 7. should be set under INTCMP process prohibition state.

Note It is not required, when the external pin CMPCOM is used for base voltage.

Caution Above 1. to 7. should be set under INTCMP process prohibition state.

## **RENESAS TECHNICAL UPDATE TN-RL\*-A008A/E**

## Figure 14-16. Operation Setting Flow Chart 2 of Comparator

Incorrect:

### Correct:

Figure 14-16. Operation Setting Flow Chart 2 of Comparator (CMP) (Using Timer Forced Output Stop Request Signal by INTPm, INTPm(Using Edge Circuit only))

## 15. 6. 3 SNOOZE mode function

## Incorrect:

SNOOZE mode makes UART operate reception by RxD0 pin input detection while the STOP mode. Normally UART stops communication in the STOP mode. But, using the SNOOZE mode makes reception UART operate unless the CPU operation by detecting RxD0 pin input. Only UART0 can be set to the SNOOZE mode. When using the SNOOZE mode function, set the SWC0 bit of serial standby control register 0 (SSC0) to 1 just before switching to the STOP mode.

Cautions 1. The SNOOZE mode can only be specified when the high-speed on-chip oscillator clock is selected for fCLK.

2. The maximum transfer rate when using UART0 in the SNOOZE mode is 9600 bps.

### Correct:

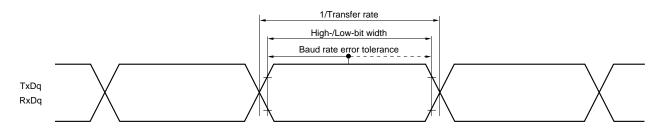

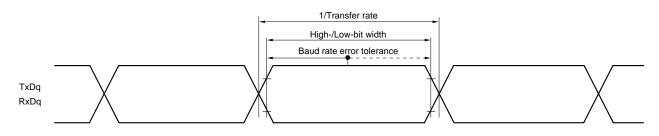

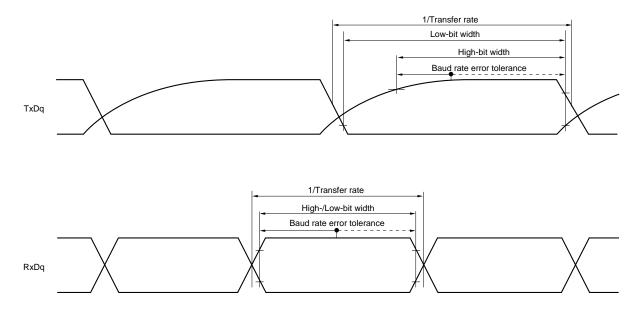

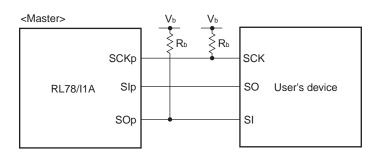

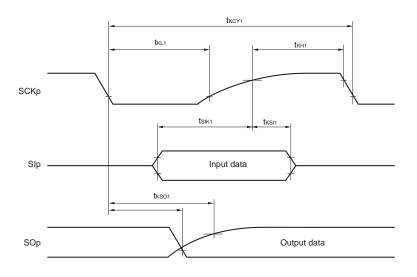

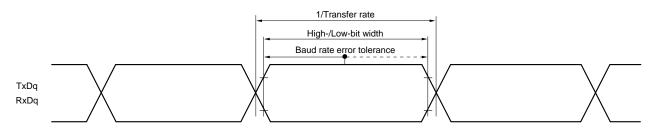

The SNOOZE mode makes the UART perform reception operations upon RxDq pin input detection while in the STOP mode. Normally the UART stops communication in the STOP mode. However, using the SNOOZE mode enables the UART to perform reception operations without CPU operation. UART0 channel can be set to the SNOOZE mode.

When using UARTq in the SNOOZE mode, make the following settings before entering the STOP mode. (See Figure 12-92 Flowchart of SNOOZE Mode Operation (EOCm1 = 0, SSECm = 0/1 or EOCm1 = 1, SSECm = 0) and Figure 12-94 Flowchart of SNOOZE Mode Operation (EOCm1 = 1, SSECm = 1).)

• In the SNOOZE mode, the baud rate setting for UART reception needs to be changed to a value different from that

- in normal operation. Set the SPSm register and bits 15 to 9 of the SDRmn register with reference to Table 12-3. • Set the EOCmn and SSECmn bits. This is for enabling or stopping generation of an error interrupt (INTSRE0) when a communication error occurs.

- When using the SNOOZE mode function, set the SWCm bit of serial standby control register m (SSCm) to 1 just before switching to the STOP mode. After the initial setting has completed, set the SSm1 bit of serial channel start register m (SSm) to 1.

Upon detecting the edge of RxDq (start bit input) after a transition was made to the STOP mode, UART reception is started.

- Cautions 1. The SNOOZE mode can only be used when the high-speed on-chip oscillator clock (fIH) is selected for fCLK.

- 2. The transfer rate in the SNOOZE mode is only 4800 bps.

- 3. When SWCm = 1, UARTq can be used only when the reception operation is started in the STOPmode. When used simultaneously with another SNOOZE mode function or interrupt, if the reception operation is started in a state other than the STOP mode, such as those given below, data may not be received correctly and a framing error or parity error may be generated.

- When after the SWCm bit has been set to 1, the reception operation is started before the STOP mode is entered

- · When the reception operation is started while another function is in the SNOOZE mode

- When after returning from the STOP mode to normal operation due to an interrupt or other cause, the reception operation is started before the SWCm bit is returned to 0

4. If a parity error, framing error, or overrun error occurs while the SSECm bit is set to 1, the PEFmn,FEFmn, or OVFmn flag is not set and an error interrupt (INTSREq) is not generated. Therefore,when the setting of SSECm = 1 is made, clear the PEFmn, FEFmn, or OVFmn flag before setting the SWC0 bit to 1 and read the value in bits 7 to 0 (RxDq register) of the SDRm1 register.

| High-speed on-chip oscillator   | UART reception baud rate in SNOOZE mode |        |                  |                  |  |

|---------------------------------|-----------------------------------------|--------|------------------|------------------|--|

| (fін)                           |                                         |        |                  |                  |  |

|                                 | <b>Operating clock</b>                  | SDRmn  | Maximum          | Minimum          |  |

|                                 | ( <b>f</b> мск)                         | [15:9] | acceptable value | acceptable value |  |

| 32 MHz ± 1.0% <sup>(note)</sup> | f <sub>ськ</sub> /2 <sup>5</sup>        | 105    | 2.27%            | -1.53%           |  |

| 24 MHz ± 1.0% <sup>(note)</sup> | f <sub>ськ</sub> /2 <sup>5</sup>        | 79     | 1.60%            | -2.18%           |  |

| 16 MHz ± 1.0% <sup>(note)</sup> | $f_{CLK}/2^4$                           | 105    | 2.27%            | -1.53%           |  |

| 12 MHz ± 1.0% <sup>(note)</sup> | $f_{CLK}/2^4$                           | 79     | 1.60%            | -2.19%           |  |

| 8 MHz ± 1.0% <sup>(note)</sup>  | $f_{CLK}/2^3$                           | 105    | 2.27%            | -1.53%           |  |

| 6 MHz ± 1.0% <sup>(note)</sup>  | $f_{CLK}/2^3$                           | 79     | 1.60%            | -2.19%           |  |

| 4 MHz ± 1.0% <sup>(note)</sup>  | f <sub>ськ</sub> /2 <sup>2</sup>        | 105    | 2.27%            | -1.53%           |  |

| 3 MHz ± 1.0% <sup>(note)</sup>  | f <sub>ськ</sub> /2 <sup>2</sup>        | 79     | 1.60%            | -2.19%           |  |

| 2 MHz ± 1.0% <sup>(note)</sup>  | f <sub>CLK</sub> /2 <sup>1</sup>        | 105    | 2.27%            | -1.54%           |  |

| 1 MHz ± 1.0% <sup>(note)</sup>  | f <sub>ськ</sub> /2 <sup>0</sup>        | 105    | 2.27%            | -1.57%           |  |

#### Table 15-3. Baud Rate Setting for UART Reception in SNOOZE Mode

Note: When the high-speed on-chip oscillator clock accuracy is at ± 1.5% or 2.0%,

the acceptable range is limited as follows:

• fin ± 1.5%: Subtract 0.5% from the maximum acceptable value of fin ± 1.0%, and add 0.5% to the minimum acceptable value of fin ± 1.0%.

• fin ± 2.0%: Subtract 1.0% from the maximum acceptable value of fin ± 1.0%, and add 1.0% to the minimum acceptable value of fin ± 1.0%.

Remarks: Maximum and minimum acceptable values in the above table are the baud rate acceptable values in UART reception. Make sure to set the baud rate for transmission within this range.

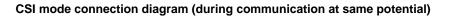

## 16.6 DALI Mode

Master mode of DALI communication is added.

Old:

This mode is used to perform slave transmission/reception of DALI (Digital Addressable Lighting Interface). DALI performs communication using the following protocol.

New:

This mode is used to perform data transmission/reception as master and slave of DALI (Digital Addressable Lighting Interface).

DALI performs communication using the following protocol.

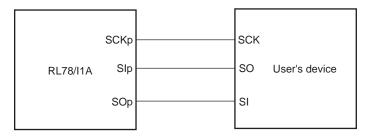

## 16.6.1 DALI transmission

## DALI transmission functions are extended.

## Old)

## P.735 Figure

| DALI transmission    |                                     |  |  |

|----------------------|-------------------------------------|--|--|

| Transfer data length | 8.16. or 24 bits                    |  |  |

| Data phase           | Forward output(default: high level) |  |  |

New)

| DALI transmission                                                                        |                       |  |  |

|------------------------------------------------------------------------------------------|-----------------------|--|--|

| Transfer data length                                                                     | 8, 16, 17, or 24 bits |  |  |

| Data phase Non-reverse output (default: high level), reverse output (default: low level) |                       |  |  |

## RENESAS TECHNICAL UPDATE TN-RL\*-A008A/E

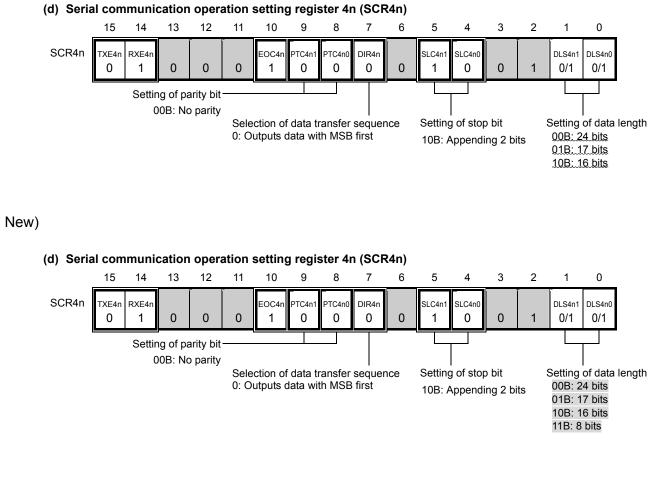

## 16.6.2 DALI reception

DALI reception functions are extended.

## Old)

| DALI Reception       |                                      |  |  |

|----------------------|--------------------------------------|--|--|

| Transfer data length | 16.17.or.24.bits                     |  |  |

| Data phase           | Forward output (default: high level) |  |  |

## New)

| DALI Reception       |                                                                               |  |  |  |

|----------------------|-------------------------------------------------------------------------------|--|--|--|

| Transfer data length | 8, 16, 17, or 24 bits                                                         |  |  |  |

| Data phase           | Non-reverse output (default: high level), reverse output (default: low level) |  |  |  |

## Figure 16-52. Example of Contents of Registers for DALI Reception

## Old)

## P.744 Register setting

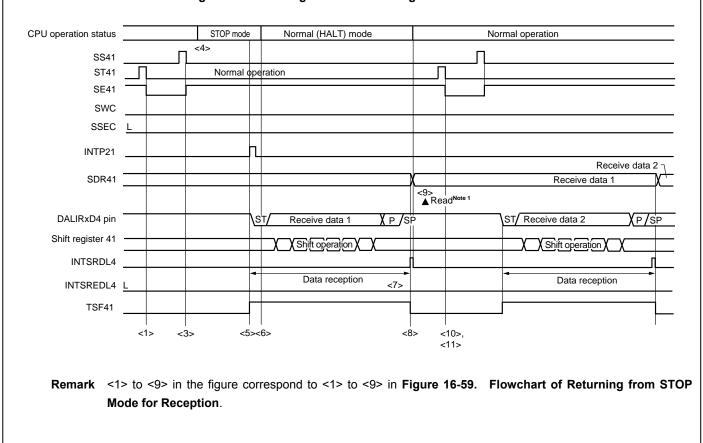

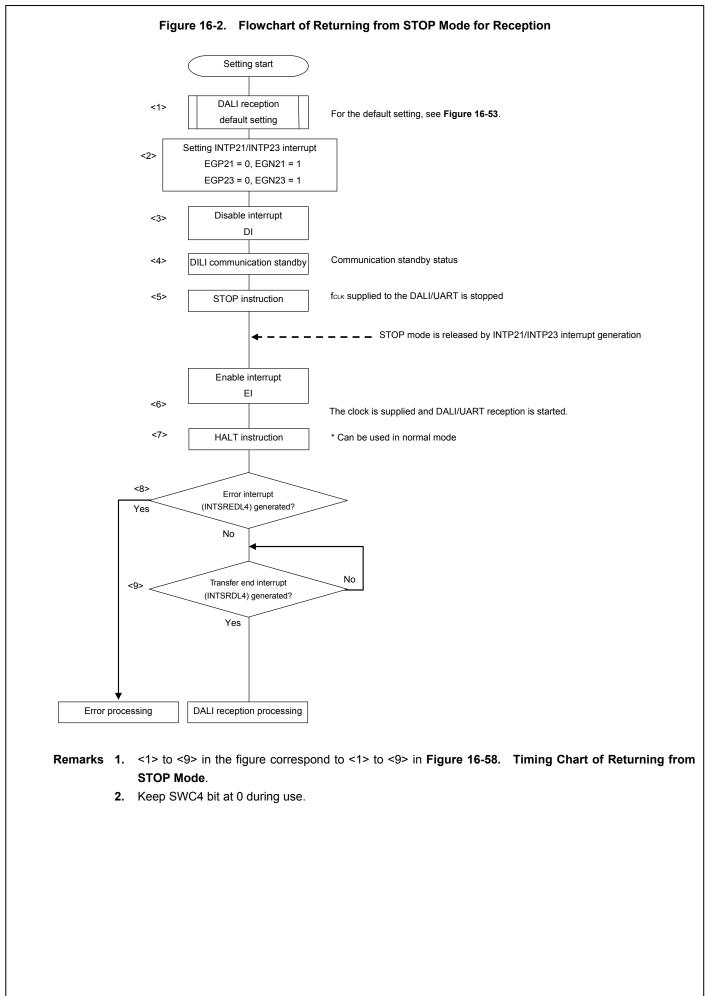

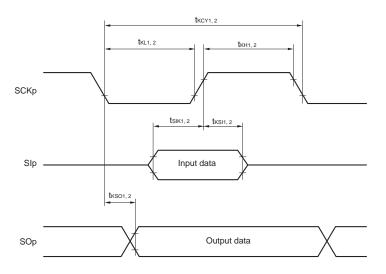

## 16.7 SNOOZE Mode Function (Only DALI/UART4 Reception)

#### Use of SNOOZE mode

During the SNOOZE mode function of DALI mode, the manchester framing error may occur depending on the baud rate and the start bit waveform even if the data is correct. In this case, the data is received but it is impossible to distinguish the error. To avoid this problem, please use "STOP & HALT Mode Function (Only DALI/UART4 Reception)" described

## Old)

### 16.7 SNOOZE Mode Function (Only DALI/UART4 Reception)

DALI reception and UART reception (channel 1) support the SNOOZE mode. When DALIRxD4 pin input is detected while in the STOP mode, the SNOOZE mode makes data reception that does not require the CPU possible. When using the SNOOZE mode function, set the SWC bit of serial standby control register 4 (SSC4) to 1 before switching to the STOP mode.

## (omitted)

**Remark** <1> to <11> in the figure correspond to <1> to <11> in Figure 16-60. Flowchart of SNOOZE Mode Operation (Normal Operation/Abnormal Operation <1>)).

## New)

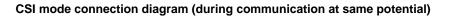

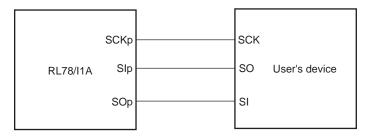

### 16.7 STOP & HALT Mode Function (Only DALI/UART4 Reception) (1) Returning from STOP & HALT modes (when DALI is received)

DALI cannot be received in the SNOOZE mode but it can be receive wait at a STOP mode by using the RxD4 pin input with the interrupt function of INTP21 or INTP23. As a result, power-saving communication can be realized in the same manner as in the SNOOZE mode.

RENESAS

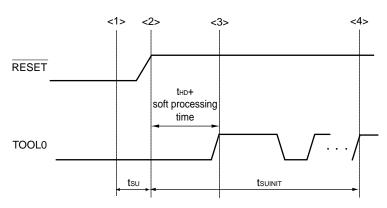

## Figure 16-1. Timing Chart of Returning from STOP Mode

## Figure 20-5. Format of Priority Specification Flag Registers

Incorrect:

## Figure 20-5. Format of Priority Specification Flag Registers (PR00L, PR00H, PR01L, PR01H, PR02L, PR02H, PR10L, PR10H, PR10H, PR11L, PR11H, PR12L, PR12H) (38-pin) (2/2)

| Address: FF     | FEBH A         | fter reset: F    | FH R/W                |                 |        |              |               |              |

|-----------------|----------------|------------------|-----------------------|-----------------|--------|--------------|---------------|--------------|

| Symbol          | <7>            | <6>              | <5>                   | <4>             | 3      | <2>          | <1>           | <0>          |

| PR01H           | TMPR004        | PPR020<br>PPR120 | SRDLPR04<br>SREDLPR04 | STDLPR04        | 1      | ITPR0        | RTCPR0        | ADPR0        |

|                 |                |                  |                       |                 |        |              |               |              |

| Address: FF     |                | fter reset: F    |                       |                 |        |              |               |              |

| Symbol          | <7>            | <6>              | <5>                   | <4>             | 3      | <2>          | <1>           | <0>          |

| PR11H           | TMPR104        | PPR022<br>PPR122 | SRDLPR14<br>SREDLPR14 |                 | 1      | ITPR1        | RTCPR1        | ADPR1        |

| Correct:        |                |                  |                       |                 |        |              |               |              |

| Address: FF     | FEBH A         | fter reset: F    | FH R/W                |                 |        |              |               |              |

| Symbol          | <7>            | <6>              | <5>                   | <4>             | 3      | <2>          | <1>           | <0>          |

| PR01H           | TMPR004        | PPR020<br>PPR022 | SRDLPR04<br>SREDLPR04 | STDLPR04        | 1      | ITPR0        | RTCPR0        | ADPR0        |

|                 |                |                  |                       |                 |        |              |               |              |

| Address: FF     |                | fter reset: F    |                       | - 4 >           | 2      | -05          | -45           | -05          |

| Symbol<br>PR11H | <7><br>TMPR104 | <6><br>PPR022    | <5><br>SRDLPR14       | <4><br>STDLPR14 | 3<br>1 | <2><br>ITPR1 | <1><br>RTCPR1 | <0><br>ADPR1 |

| FRIIN           |                | PPR022<br>PPR120 | SREDLPR14             |                 | I      | IIFRI        | RICFRI        | ADERT        |

|                 |                |                  |                       |                 |        |              |               |              |

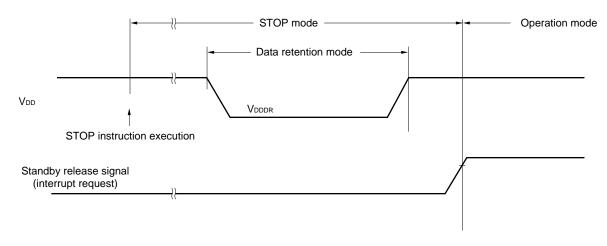

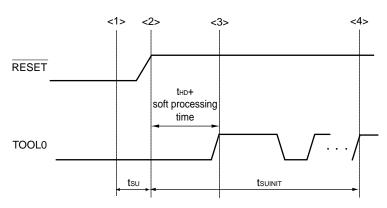

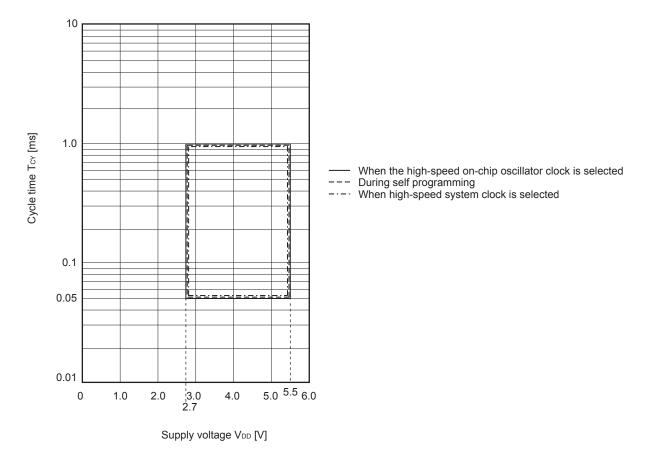

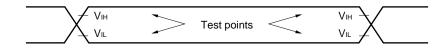

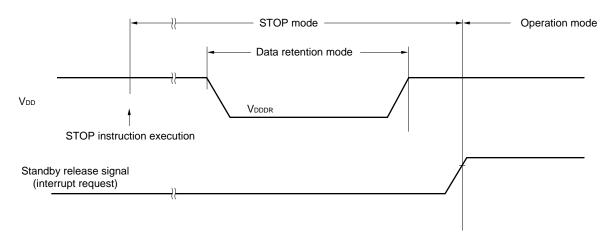

## 21.2.2 STOP mode Incorrect: Figure 21-5. STOP Mode Release by Interrupt Request Generation (1) When high-speed system clock (X1 oscillation) is used as CPU clock Note 2. STOP mode release time Supply of the clock is stopped: 18.96 µ s to "whichever is longer 28.95 µ s and the oscillation stabilization time. (set by OSTS)" Wait ·When vectored interrupt servicing is carried out: 10 to 11 clocks ·When vectored interrupt servicing is not carried out: 4 to 5 clocks (2) When high-speed system clock (external clock input) is used as CPU clock (3) When high-speed on-chip oscillator clock is used as CPU clock (omitted) : Note 2. STOP mode release time Supply of the clock is stopped: 19.08 to 32.99 µs Wait · When vectored interrupt servicing is carried out: 7 clocks · When vectored interrupt servicing is not carried out: 1 clock Correct: Figure 21-5. STOP Mode Release by Interrupt Request Generation (1) When high-speed on-chip oscillator clock is used as CPU clock Note 2. STOP mode release time Supply of the clock is stopped:18 $\mu$ s to "whichever is longer 65 $\mu$ s and the oscillation stabilization time (set by OSTS)" Wait •When vectored interrupt servicing is carried out: 10 to 11 clocks •When vectored interrupt servicing is not carried out: 4 to 5 clocks (2) When high-speed system clock (X1 oscillation) is used as CPU clock (3) When high-speed system clock (external clock input) is used as CPU clock (omitted) 1 Note 2. STOP mode release time Supply of the clock is stopped: 18 to 65 $\mu$ s Wait • When vectored interrupt servicing is carried out: 7 clocks • When vectored interrupt servicing is not carried out: 1 clock

## 21.2.3 SNOOZE mode

## Incorrect:

In SNOOZE mode transition, wait status to be only following time. From STOP to SNOOZE HS (High-speed main) mode : 18.96 to 28.95 µs LS (Low-speed main) mode : 20.24 to 28.95 µs

From SNOOZE to normal operation

- When vectored interrupt servicing is carried out HS (High-speed main) mode : 6.79 to 12.4 µs + 7 clocks LS (Low-speed main) mode : 2.58 to 7.8 µs + 7 clocks

- When vectored interrupt servicing is not carried out: HS (High-speed main) mode : 6.79 to 12.4 µs + 1 clock LS (Low-speed main) mode : 2.58 to 7.8 µs + 1 clock

Correct:

In SNOOZE mode transition, wait status to be only following time. Transition time from STOP mode to SNOOZE mode: 18 to 65  $\mu$ s

Transition time from SNOOZE mode to normal operation:

- When vectored interrupt servicing is carried out: HS (High-speed main) mode: 4.99 to 9.44 μs + 7 clocks

LS (Low-speed main) mode: 1.10 to 5.08 μs + 7 clocks

- When vectored interrupt servicing is not carried out: HS (High-speed main) mode: 4.99 to 9.44 μs + 1 clock

LS (Low-speed main) mode: 1.10 to 5.08 μs + 1 clock

- **Notes 1.** The internal reset processing time includes the oscillation accuracy stabilization time of the high-speed on-chip oscillator clock.

- 2. The high-speed on-chip oscillator clock and a high-speed system clock or subsystem clock can be selected as the CPU clock. To use the X1 clock, use the oscillation stabilization time counter status register (OSTC) to confirm the lapse of the oscillation stabilization time. To use the XT1 clock, use the timer function for confirmation of the lapse of the stabilization time.

- **3.** Reset processing time: 265 to 407  $\mu$  s

- Remark

VPOR: POR power supply rise detection voltage

VPDR:

POR power supply fall detection voltage

- **Notes 1.** The high-speed on-chip oscillator clock and a high-speed system clock or subsystem clock can be selected as the CPU clock. To use the X1 clock, use the oscillation stabilization time counter status register (OSTC) to confirm the lapse of the oscillation stabilization time. To use the XT1 clock, use the timer function for confirmation of the lapse of the stabilization time.

- 2. The internal reset processing time includes the oscillation accuracy stabilization time of the high-speed on-chip oscillator clock.

- 3. After the first interrupt request signal (INTLVI) is generated, the LVIL and LVIMD bits of the voltage detection level register (LVIS) are automatically set to 1. If the operating voltage returns to 2.7 V or higher without falling below the voltage detection level (VLVDL), after INTLVI is generated, perform the required backup processing, and then use software to specify the initial settings in order (see Figure 24-8. Initial Setting of Interrupt and Reset Mode).

- **4.** Reset processing time: 497 to 720  $\mu$  s

Remark VLVDH, VLVDL: LVD detection voltage

| VPOR: | POR power supply rise detection voltage |

|-------|-----------------------------------------|

| VPDR: | POR power supply fall detection voltage |

VPDR: POR power supply fall detection voltage

Caution For power-on reset, be sure to use the externally input reset signal on the RESET pin when the LVD is off. For details, see CHAPTER 21 VOLTAGE DETECTOR.

- Notes 1. The internal reset processing time includes the oscillation accuracy stabilization time of the high-speed on-chip oscillator clock.

- 2. The high-speed on-chip oscillator clock and a high-speed system clock or subsystem clock can be selected as the CPU clock. To use the X1 clock, use the oscillation stabilization time counter status register (OSTC) to confirm the lapse of the oscillation stabilization time. To use the XT1 clock, use the timer function for confirmation of the lapse of the stabilization time.

- The time until normal operation starts includes the following LVD reset processing time after the LVD detection level (VLVD) is reached as well as the voltage stabilization wait + POR reset processing time after the VPOR (1.51 V, typ.) is reached.

LVD reset processing time: 0 ms to 0.0701 ms (max.)

- 4. When the power supply voltage is below the lower limit for operation and the power supply voltage is then restored after an internal reset is generated only by the voltage detector (LVD), the following LVD reset processing time is required after the LVD detection level (VLVD) is reached. LVD reset processing time: 0.0511 ms (typ.), 0.0701 ms (max.)

- Remarks 1. VLVDH, VLVDL: LVD detection voltage VPOR: POR power supply rise detection voltage VPDR: POR power supply fall detection voltage

- 2. When the LVD interrupt mode is selected (option byte 000C1H: LVIMD1 = 0, LVIMD0 = 1), the time until normal operation starts after power is turned on is the same as the time specified in Note 3 of Figure 23-2 (3).

## 25.3.6 Invalid memory access detection function

## Incorrect:

## Figure 25-11. Invalid Access Detection Area

Note Code flash memory and RAM address of each product are as follows.

| Products           | Code Fash Memory<br>(00000H to xxxxxH) | RAM<br>(yyyyyH to FFEFFH)              |  |

|--------------------|----------------------------------------|----------------------------------------|--|

| R5F1076C, R5F107AC | 32768 × 8 bit (00000H to 07FFFH)       | 2048 × 8 bit (FF700H to FFEFFH)        |  |

| R5F107AE, R5F107DE | 65536 $\times$ 8 bit (00000H to 0FFFH) | 4096 $\times$ 8 bit (FEF00H to FFEFFH) |  |

Correct:

#### Note

te The following table lists the code flash memory, RAM, and lowest detection address for each product:

| Products           | Code flash memory<br>(00000H to xxxxxH) | RAM<br>(zzzzzH to FFEFFH)   | Detected lowest address for<br>read/instruction fetch |

|--------------------|-----------------------------------------|-----------------------------|-------------------------------------------------------|

|                    |                                         | (execution) (yyyy           |                                                       |

| R5F1076C, R5F107AC | 32768 × 8 bit                           | $2048 \times 8 \text{ bit}$ | 10000H                                                |

|                    | (00000H to 07FFFH)                      | (FF700H to FFEFFH)          |                                                       |

| R5F107AE, R5F107DE | 65536 × 8 bit                           | 4096 × 8 bit                | 10000H                                                |

|                    | (00000H to 0FFFFH)                      | (FEF00H to FFEFFH)          |                                                       |

## 27.3 Format of On-chip Debug Option Byte

Old:

Figure 27-3. Format of Option Byte (000C2H/010C2H)

Address: 000C2H/010C2H<sup>Note</sup>

| 6          | 5                                                                                                                                                                                     | 4                                                             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMODE0     | 1                                                                                                                                                                                     | 0                                                             | FRQSEL3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FRQSEL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FRQSEL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FRQSEL0                                                                                                                                                                    |

|            |                                                                                                                                                                                       |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                            |