## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## SuperH RISC engine C/C++ Compiler Package

## **APPLICATION NOTE:** [Compiler Use guide] #pragma Extension Guide

This document explains the extended #pragma directives available in SuperH RISC engine C/C++ Compiler version 9. Some of these directives can reduce the program size or improve execution speed while others provide useful functions.

#### Table of contents

| 1.    | Extended #pragma Directives for Reducing Program Size and Improving Execution Speed    | 2  |

|-------|----------------------------------------------------------------------------------------|----|

| 1.1   | Specifies address range                                                                | 2  |

| 1.2   | Performs inline expansion of functions                                                 |    |

| 1.3   | Expands an assembly-language description function                                      | 7  |

| 1.4   | Generates or does not generate save and restore code at the start and end of functions |    |

| 1.5   | Allocating global variables to registers                                               | 19 |

| 1.6   | Specifying GBR base variables                                                          | 22 |

| 2.    | Other Useful Extended #pragma Directives                                               |    |

| 2.1   | Specifying section name replacement                                                    |    |

| 2.2   | Specifying the order of bit fields                                                     |    |

| 2.3   | Specification of alignment for structures, unions, and classes                         |    |

| Websi | ite and Support <website and="" support,ws=""></website>                               | 34 |

# RENESAS

# 1. Extended #pragma Directives for Reducing Program Size and Improving Execution Speed

This chapter explains extended #pragma directives that can be effective in reducing program size and improving execution speed. Table 1-1 lists the extended #pragma directives explained in this chapter.

| No. | #pragma                                                          | Explanation                                                                                  | Effectiveness<br>on size | Effectiveness<br>on speed | See<br>section |

|-----|------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------|---------------------------|----------------|

| 1   | #pragma abs16<br>#pragma abs20<br>#pragma abs28<br>#pragma abs32 | Specifies address range                                                                      | A+                       | В                         | 1.1            |

| 2   | #pragma inline                                                   | Performs inline expansion of<br>functions                                                    | С                        | A+                        | 1.2            |

| 3   | #pragma<br>inline_asm                                            | Expands an assembly-language description function                                            | С                        | A                         | 1.3            |

| 4   | #pragma regsave<br>#pragma noregsave<br>#pragma noregalloc       | Generates or does not generate<br>save and restore code at the<br>start and end of functions | A                        | A                         | 1.4            |

| 5   | #pragma<br>global_register                                       | Allocates global variables to registers                                                      | В                        | В                         | 1.5            |

| 6   | #pragma gbr_base<br>#pragma gbr_base1                            | Specifies GBR base variables                                                                 | A+                       | А                         | 1.6            |

| Table 1 1  |          | 4       |            | f      |          |             |   |

|------------|----------|---------|------------|--------|----------|-------------|---|

| 1 able 1-1 | Extended | #pragma | directives | tor im | nproving | performance | ; |

A+: Very effective.

- A: Effective.

- B: Effective, but must be used with caution.

- C: Lowers performance.

Note that the expanded assembly code examples in this document were obtained by specifying code=asmcode and cpu=sh2. This code might vary depending on the specification of the cpu option. It is also subject to change if the compiler is improved in the future. Accordingly, you should use these code examples for reference only.

#### 1.1 Specifies address range

The #pragma absn (n: 16, 20, 28, or 32) directive is a declaration that tells the compiler that the variable or function is in the n-bit address area. The default is the 32-bit address area.

For example, #pragma abs16 specified for a variable or function means that the variable or function is placed in an address area that can be represented by 16 bits. Compared with the default 32-bit addressing, which uses four bytes for an address value, 16-bit addressing uses only two bytes, and therefore reduces program size. Address area specification for variables and functions that are referenced from many locations effectively reduces program size. Note that if a #pragma absn directive is specified for a variable or function, the same #pragma absn directive must be specified for all occurrences of the variable or function throughout the source code. For example, you must not specify #pragma abs16 and #pragma abs32 for separate occurrences of the same variable or function. Renesas recommends that you specify the #pragma absn directive in a common header file.

You can specify #pragma abs20 and #pragma abs28 for only the SH-2A and SH2A-FPU microcomputers. For details, see 2.1 20-bit Long Immediate Load in the manual SuperH RISC engine C/C++ Compiler Package APPLICATION NOTE: [Compiler use guide] SH-2A / SH2A-FPU.

You can also use an advanced option to specify the address area. If you specify both the advanced option and the #pragma directive that specify the address area, the #pragma directive takes precedence. As an example of use, when the 16-bit address area is specified for a variable or function, you can use the #pragma abs32 directive to change the address area to the 32-bit address area, which is the default.

Format:

#pragma abs16 (identifier [,identifier...])

#pragma abs20 (identifier [,identifier...])

#pragma abs28 (identifier [,identifier...])

#pragma abs32 (identifier [,identifier...])

identifier: variable name | function name

Example:

When abs16 is specified for a variable or function, the address storage area of the variable or function changes from a .DATA.L (4 bytes) to a .DATA.W (2 bytes).

| Source code with #pragma abs16 not specified: |               |                       | Source c | ode with #pı    | agma abs16 s | specified:      |      |

|-----------------------------------------------|---------------|-----------------------|----------|-----------------|--------------|-----------------|------|

|                                               |               |                       | -        |                 |              |                 |      |

|                                               |               |                       |          |                 | absl6 (x,y,z | z )             |      |

|                                               | int x(void);  |                       |          | -               | nt x(void);  |                 |      |

| int y;                                        |               |                       |          | int y;          |              |                 |      |

| long z;                                       |               |                       |          | long z;         |              |                 |      |

| void f(v                                      | void)         |                       |          | void f(v        | oid)         |                 |      |

| {                                             |               |                       |          | - {             |              |                 |      |

| z = x()                                       | + у;          |                       |          | z = x()         | + y;         |                 |      |

| }                                             |               |                       |          | _ }             |              |                 |      |

| _                                             |               |                       |          |                 |              |                 |      |

| Expanded                                      | d assembly co | de:                   |          | <u>Expanded</u> | assembly co  | ode:            |      |

| <i>с</i> .                                    |               |                       |          |                 |              |                 |      |

| _f:                                           | 000 1         |                       |          | f:              | ота т        |                 |      |

|                                               | STS.L         | PR,@-R15              |          | -               | STS.L        | _PR,@-R15       |      |

|                                               | MOV.L         | L11+2,R2<br>@R2       | ; _x     | :               | MOV.W        | L11,R2<br>@R2   | ; _x |

|                                               | JSR<br>NOP    | WRZ                   |          | -               | JSR<br>NOP   | WRZ             |      |

|                                               | MOV.L         | T11.6 DE              |          | -               |              | T11,0 DE        |      |

|                                               |               | L11+6,R5<br>L11+10,R4 | ; _Y     | 1               | MOV.W        | L11+2,R5        |      |

|                                               | MOV.L         |                       | _        | -               | MOV.W        | L11+4,R4        | ; _z |

|                                               | MOV.L<br>ADD  | @R5,R1                | ' Y      | -               | MOV.L<br>ADD | @R5,R1<br>R1,R0 | ; у  |

|                                               | LDS.L         | R1,R0<br>@R15+,PR     |          | 1               | LDS.L        | @R15+,PR        |      |

|                                               | RTS           | WRIS+,PR              |          | -               | RTS          | WRIS+,PR        |      |

|                                               | MOV.L         | R0,@R4                | ; z      | 1               | MOV.L        | R0,@R4          | i z  |

| L11:                                          | MOV.L         | RU, WR4               | / 2      | :<br>L11:       | MOV.L        | KU, WK4         | / 2  |

|                                               | .RES.W        | 1                     |          |                 | .DATA.W      | _x              |      |

|                                               | .DATA.L       | _x                    |          | 1               | .DATA.W      | _x<br>_y        |      |

|                                               | .DATA.L       |                       |          | -               | .DATA.W      | -               |      |

|                                               | .DATA.L       | _Y                    |          | -               | .DAIA.W      | _z              |      |

|                                               | .DAIA.L       | _z                    |          | 1               |              |                 |      |

| 1                                             |               |                       |          | -               |              |                 |      |

Note:

- If you specify abs16, abs20, abs28, or abs32 for a variable or function, use the #pragma section directive to switch the section so that the section is placed in an address area that can be represented by the specified bit addressing during linkage.

- The following table shows the #pragma absn directives and the address ranges in which a section can be placed.

| Table 1-2 Address ranges in which the | he section can be placed |

|---------------------------------------|--------------------------|

|---------------------------------------|--------------------------|

| #progmo       | Address range |             |  |

|---------------|---------------|-------------|--|

| #pragma       | Beginning     | End         |  |

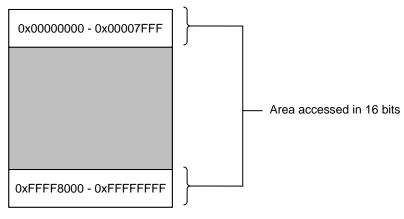

| #pragma abs16 | 0x0000000     | 0x00007FFF  |  |

|               | 0xFFFF8000    | 0xFFFFFFF   |  |

| #pragma abs20 | 0x0000000     | 0x0007FFFF  |  |

| 1 0           | 0xFFF80000    | 0xFFFFFFF   |  |

| #pragma abs28 | 0x0000000     | 0x07FFF7F * |  |

| 1 0           | 0xF8000000    | 0xFFFFFFF   |  |

| #pragma abs32 | 0x0000000     | 0xFFFFFFF   |  |

\* Note that the address is 0x07FFFF7F.

• If you specify abs16, place the section in either of the areas shown in the following figure.

• If generation of position-independent code is specified (pic=1 option) at compile time, function addresses are not generated for the specified bit value because addresses are referenced by relative access.

| Source         | code:                                 |               |           |          |             |              |                    |

|----------------|---------------------------------------|---------------|-----------|----------|-------------|--------------|--------------------|

|                | absl6 (x,y,z<br>int x(void);<br>void) | z )           |           |          |             |              |                    |

| {              | voia,                                 |               |           | -        |             |              |                    |

|                | x() + y;                              |               |           |          |             |              |                    |

| }              |                                       |               |           |          |             |              |                    |

|                |                                       |               |           |          |             |              |                    |

| Torre o re d o |                                       | de (min 0 me  |           | :<br>    |             | de (min 1 m  |                    |

| Expanded       | d assembly co                         | de (pic=0 spe | ecilied). | Expanded | assembly co | de (pic=i sp | pecified).         |

| _f:            |                                       |               |           | _f:      |             |              |                    |

| _              | STS.L                                 | PR,@-R15      |           | : _      | STS.L       | PR,@-R15     |                    |

|                | MOV.W                                 | L11,R2        | ; _x      | :        | MOV.L       | L12+6,R3     | ; H'FFFFFFC+_x-L11 |

|                | JSR                                   | @R2           |           | L11      |             |              |                    |

|                | NOP                                   |               |           | :        | BSRF        | R3           |                    |

|                | MOV.W                                 | L11+2,R5      | ; _y      |          | NOP         |              |                    |

|                | MOV.W                                 | L11+4,R4      | ; _z      |          | MOV.W       | L12,R5       | ; _у               |

|                | MOV.L                                 | @R5,R1        | ; y       | :        | MOV.W       | L12+2,R2     | ; _z               |

|                | ADD                                   | R1,R0         |           |          | MOV.L       | @R5,R1       | ; у                |

|                | LDS.L                                 | @R15+,PR      |           |          | ADD         | R1,R0        |                    |

|                | RTS                                   |               |           | :        | LDS.L       | @R15+,PR     |                    |

|                | MOV.L                                 | R0,@R4        | ; z       | :        | RTS         |              |                    |

| L11:           |                                       |               |           |          | MOV.L       | R0,@R2       | ; z                |

|                | .DATA.W                               | _x            |           | L12:     |             |              |                    |

|                | .DATA.W                               | Y             |           | :        | .DATA.W     | _У           |                    |

|                | .DATA.W                               | Z             |           | -        | .DATA.W     | Z            |                    |

|                |                                       |               |           |          | .RES.W      | 1            |                    |

|                |                                       |               |           |          | .DATA.L     | H'FFFFFFF    | C+_x-L11           |

|                |                                       |               |           |          |             |              |                    |

# 1.2 Performs inline expansion of functions

NESAS

Inline expansion is a type of optimization that inserts the body of a function at the point at which the function is called. You can use inline expansion when you expect that it will reduce function call overhead, making the program smaller and allowing it to run faster. In particular, inline expansion can be very effective for functions that are called repeatedly in a loop. Since the compiler performs inline expansion before optimizing the source code, note that inline expansion for large functions increases program size, and might reduce the efficiency of compiler optimization. Inline expansion is more effective when it is performed for small functions that are called frequently.

Format:

#### #pragma inline [(]function-name[,...][)]

When you specify functions in a #pragma inline directive, make sure that the body of each function is defined after the directive.

The compiler also generates external definitions for the functions specified in a #pragma inline directive. If these external definitions are not necessary, specify static for the function declarations. Since the compiler does not generate the body of a static function when performing inline expansion, specifying static might reduce program size.

Whereas automatic inline expansion of the inline option specified for a function stops before the specified limit on increase in function size (expressed as a percentage) is reached, automatic inline expansion of the #pragma inline directive does not.

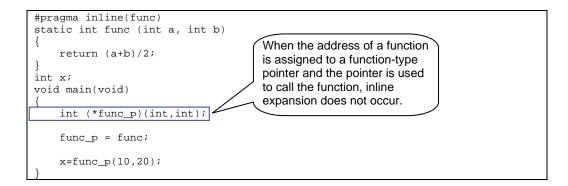

Note that, when #pragma inline is specified, inline expansion for a function does not occur if the function satisfies any of the following conditions:

- The function is defined before the #pragma inline directive.

- The function has variable parameters.

- The function is called via its address.

Example: Source before and after inline expansion

```

Source code:

```

```

#pragma inline(func)

static int func (int a, int b)

{

return (a+b)/2;

}

int x;

void main(void)

{

x=func(10,20);

}

Source after expansion:

int x;

void main(void)

{

int func_result;

{

int a_1=10, b_1=20;

func_result=(a_1+b_1)/2;

}

,

x=func_result;

}

```

#### 1.3 Expands an assembly-language description function

Inline expansion for assembly functions is effective when you want to use CPU instructions that C does not support or when you want to improve performance by coding the functions in assembly language rather than in C. In a C source file, you can code functions in assembly language by using the <code>#pragma inline\_asm</code> directive to declare that the functions are written in assembly language. Such assembly functions are called *inline assembly functions*. In the <code>#pragma inline\_asm</code> directive, you can also specify a <code>size=numeric-value</code> option to specify the size of an assembly function. Specifying this option might improve the efficiency of optimization.

Note that when you specify the size of a function in the #pragma inline\_asm directive, you must make sure that the size is the same as or larger than the actual object size. If you specify a size smaller than the actual object size, operation of the compiler is not guaranteed.

#### Format:

#### #pragma inline\_asm [(]function-name[(size=numeric-value)] [,...][)]

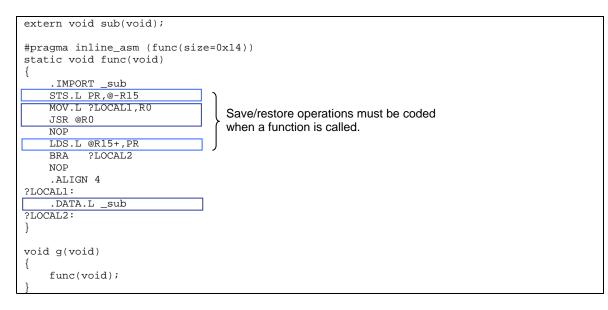

Note the following when you code inline assembly functions:

- Make sure that each label is a local label (begins with a question mark (?) and consists of 16 or fewer characters).

- Do not code an instruction that automatically generates a literal pool. For details, see Example 2.

- Do not code an RTS (return) instruction at the end of a definition.

- Save and restore the contents of guaranteed registers.

Save/restore operations must also be performed even for the registers specified in the #pragma global\_register directive. Also note that the save/restore operations of the procedure register (PR) must be coded because the contents of the register are overwritten every time a function is called.

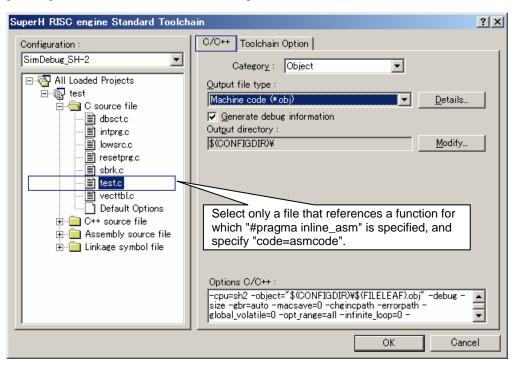

A C source file that includes assembly functions must be output in an assembly file format (code=asmcode).

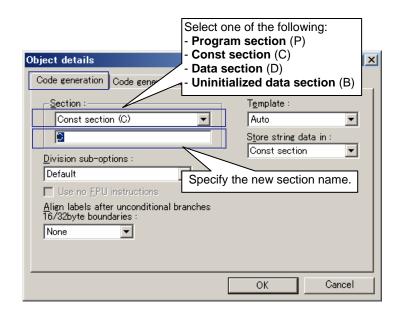

Option settings in High-Performance Embedded Workshop (Renesas IDE hereafter):

#### Figure 1-2

If a function specified in the <code>#pragma inline\_asm</code> directive causes a compilation error when the output of compiler debug information is enabled, the C source program line information is output in Renesas IDE. You cannot use the line information to jump to the assembly program location that caused the error. If you disable output of the compiler debug information, the assembly program line information is displayed in Renesas IDE. Renesas recommends that you disable output of the compiler debug information when you debug a function specified in the <code>#pragma inline\_asm</code> directive.

Note that the interface between functions must comply with the generation rules for the C or C++ compiler (see Table 1-3 and Table 1-4).

|                                    | Assignment rules                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                    | ments passed via registers                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Registers for storing<br>arguments | Supported data types                                                                                                                                                                                                                                                               | Arguments passed via stacks                                                                                                                                                                                                                                                    |  |  |  |  |  |

| R4 - R7                            | char, unsigned char, bool, short,<br>unsigned short, int, unsigned int,<br>long, unsigned long, float (when<br>the CPU is other than SH-2E,<br>SH2A-FPU, SH-4, or SH-4A), pointer,<br>pointer to a data member, and<br>references                                                  | <ul> <li>Arguments that cannot be stored in registers R4 to R7 because other arguments have already been stored in these registers</li> <li>Arguments that cannot be stored in</li> </ul>                                                                                      |  |  |  |  |  |

| FR4 - FR11 <sup>#1</sup>           | <ul> <li>When the CPU is SH-2E:</li> <li>float</li> <li>double (with the double=float option specified)</li> <li>When the CPU is SH2A-FPU, SH-4, or SH-4A:</li> <li>float (with the fpu=double option specified)</li> <li>double (with the fpu=single option specified)</li> </ul> | <ul> <li>registers FR4 (DR4) to FR11 (DR10)<br/>because other arguments have already<br/>been stored in these registers</li> <li>Arguments of types long long and<br/>unsigned long long</li> <li>Arguments of typesfixed, long<br/>fixed,accum, and long<br/>accum</li> </ul> |  |  |  |  |  |

| DR4 - DR10 <sup>#2</sup>           | <ul> <li>When the CPU is SH2A-FPU, SH-4,<br/>SH-4A:</li> <li>double (without the fpu=single<br/>option specified)</li> <li>float (with the fpu=double option<br/>specified)</li> </ul>                                                                                             |                                                                                                                                                                                                                                                                                |  |  |  |  |  |

#### Table 1-3 General rules for assigning arguments in C

Notes: #1: SH-2E, SH2A-FPU, SH-4, and SH-4A registers used for single-precision floating-point numbers

#2: SH2A-FPU, SH-4, and SH-4A registers used for double-precision floating-point numbers

| Table 1-4 Return value types and setting location in C programs | 5 |

|-----------------------------------------------------------------|---|

|-----------------------------------------------------------------|---|

| Return value types                                                                                                                                                                             | Setting location                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>(singed) char, unsigned char,<br/>(singed) short, unsigned short,<br/>(singed) int, unsigned int, long,<br/>unsigned long, pointers, bool,<br/>references, pointers to data members</pre> | R0: 32 bits<br>The contents of the upper three bytes of (signed) char, or<br>unsigned char and the contents of the upper two bytes of<br>(signed) short or unsigned short are not guaranteed.<br>However, when the rtnext option is specified, sign extension is<br>performed for (signed) char or (signed) short type, and zero<br>extension is performed for unsigned char or unsigned short<br>type. |

| float                                                                                                                                                                                          | <ul> <li>FR0: 32 bits</li> <li>(1) For CPU is SH-2E <ul> <li>Return value is float type.</li> <li>Return value is double type and double=float is specified.</li> </ul> </li> <li>(2) For SH2A-FPU,SH-4, or SH-4A <ul> <li>Return value is float type and fpu=double is not specified.</li> <li>Return value is floating-point type and fpu=single is specified.</li> </ul> </li> </ul>                 |

| double and long double                                                                                                                                                                         | <ul> <li>Return value setting area (memory)</li> <li>For SH2A-FPU, SH-4, or SH-4A</li> <li>Return value is double type and fpu=single is not specified.</li> <li>Return value is floating-point type and fpu=double is specified.</li> </ul>                                                                                                                                                            |

| Structure, union, and class types, and pointers to function members                                                                                                                            | Return value setting area (memory).                                                                                                                                                                                                                                                                                                                                                                     |

| (signed) long long <b>and</b> unsigned<br>long long                                                                                                                                            | Return value setting area (memory).                                                                                                                                                                                                                                                                                                                                                                     |

| fixed, longfixed,accum,<br>and longaccum                                                                                                                                                       | Return value setting area (memory).                                                                                                                                                                                                                                                                                                                                                                     |

Example 1: Specifying an inline assembly function

```

Source code:

/* Inline function definition */

/* FILE: inlasm.h */

#pragma inline_asm(rev4b(size=0x04))

static unsigned long rev4b(unsigned long p)

/* Function is declared as static */

{

; In a definition, comment lines begin with a semicolon, as in assembly language.

SWAP.W R4,R0

SWAP.B R0,R0

; Do not specify an RTS instruction at the end of the definition.

#pragma inline_asm(ovf)

static unsigned long ovf(void)

?LABEL001 ; In an inline assembly function, use local labels.

; Local label: String beginning with ? and consisting of 16 or fewer characters

MOV R4,R0

:

CMP/EQ #1,R0

BT ?LBABEL001

}

```

Example 2: Notes on automatic generation of a literal pool

| Incorrect source code:                              | Correct source code 1:                            |

|-----------------------------------------------------|---------------------------------------------------|

|                                                     | <pre>#pragma inline_asm(f(size=0x0c))</pre>       |

| <pre>/* Incorrect inline assembly function */</pre> | <pre>/* Correct inline assembly function */</pre> |

|                                            | · · · · · · · · · · · · · · · · · · ·       |

|--------------------------------------------|---------------------------------------------|

| static unsigned long f(void)               | static unsigned long f(void)                |

| {                                          | : {                                         |

| MOV.L #H'f000000,R0                        | MOV.L ?LOCAL1,R0 ; Data is referenced from  |

|                                            |                                             |

|                                            | ; the local label.                          |

| ; This code causes the assembler to        | BRA ?LOCAL2 ; Jumps over data definitions.  |

| ; automatically generate a literal pool.   | NOP                                         |

| ; As a result, the compiler-generated code | .ALIGN 4                                    |

|                                            | ?LOCAL1:                                    |

| , might not be alighed correctly.          |                                             |

| }                                          | .DATA.L H'F000000                           |

|                                            | ?LOCAL2:                                    |

|                                            | : }                                         |

|                                            |                                             |

|                                            | 1_0.                                        |

|                                            | Correct source code 2:                      |

|                                            |                                             |

|                                            | <pre>#pragma inline_asm(f(size=0x06))</pre> |

|                                            | /* Correct inline assembly function */      |

|                                            | static unsigned long f(void)                |

|                                            | ' r                                         |

|                                            | : {                                         |

|                                            | MOV #-16,R0 ; H'FFFFFF0                     |

|                                            | SHLL8 R0                                    |

|                                            | SHLL16 R0                                   |

|                                            |                                             |

|                                            | ; No data is referenced from labels.        |

|                                            | : }                                         |

Example 3: Optimization with the "size" option specified

| Evaluation at | branches | is further | optimized by | y specifying the size.                |

|---------------|----------|------------|--------------|---------------------------------------|

|               |          |            |              | · · · · · · · · · · · · · · · · · · · |

|                                                                        |              |          | ed)           | -                       |              | )x20" specifi | ied)  |

|------------------------------------------------------------------------|--------------|----------|---------------|-------------------------|--------------|---------------|-------|

| Source code ("size" not specified)<br>#include <machine.h></machine.h> |              |          |               | <machine.h></machine.h> |              | <u> </u>      |       |

| extern int a;                                                          |              |          | extern int a; |                         |              |               |       |

| CAUCTIN T                                                              |              |          |               | . CAUCITII I            | u,           |               |       |

| #pragma                                                                | inline_asm ( | func)    |               | #pragma                 | inline asm ( | func(size=0>  | (20)) |

|                                                                        | nt func(void |          |               |                         | nt func(void |               |       |

| {                                                                      |              | - /      |               | : {                     |              | - /           |       |

| ۱<br>NOP                                                               |              |          |               | NOP                     |              |               |       |

| }                                                                      |              |          |               | : NOP<br>: }            |              |               |       |

| ſ                                                                      |              |          |               | 1                       |              |               |       |

| void g(v                                                               | oid)         |          |               | void g(v                | oid)         |               |       |

| {                                                                      | /            |          |               | {                       | /            |               |       |

|                                                                        | a) {         |          |               | if (                    | a) {         |               |       |

|                                                                        | func();      |          |               |                         | func();      |               |       |

| ı                                                                      |              |          |               |                         |              |               |       |

| )<br>;<br>;<br>;<br>;                                                  | ) (          |          |               | ; }<br>; ; (            | ) (          |               |       |

|                                                                        | a) {         |          |               | : if (                  |              |               |       |

|                                                                        | nop();       |          |               |                         | nop();       |               |       |

| }                                                                      |              |          |               | }                       |              |               |       |

| }                                                                      |              |          |               | }                       |              |               |       |

| Evmanded                                                               | assembly co  | do.      |               | :<br>. Exmanded         | assembly co  | do.           |       |

| _g:                                                                    | assembly CC  | Jue ·    |               | : _g:                   | assembly CC  |               |       |

| _a.                                                                    | MOV.L        | L16+2,R6 | ; _a          | : _a.                   | MOV.L        | L15+2,R6      | ; _a  |

|                                                                        | MOV.L        | @R6,R2   | ; _a          |                         | MOV.L        | @R6,R2        | ; _a  |

|                                                                        |              |          | , a           | :                       |              |               | , a   |

|                                                                        | TST          | R2,R2    |               | :                       | TST          | R2,R2         | _     |

|                                                                        | BF           | L20      | • • 10        |                         | BT           | L13           |       |

|                                                                        | MOV.L        | L16+6,R3 | ; L13         | NOP                     | ATTON        | 4             |       |

| L                                                                      | JMP          | @R3      |               | :                       | .ALIGN       | 4<br>115:0 DC |       |

| <b>T</b> 00.                                                           | NOP          |          |               |                         | MOV.L        | L15+2,R6      | ; _a  |

| L20:                                                                   |              | - 1 -    |               |                         | MOV.L        | @R6,R2        | ; a   |

|                                                                        | BRA          | L15      |               |                         | TST          | R2,R2         |       |

|                                                                        | NOP          |          |               | :                       | BT           | L13           |       |

| L16:                                                                   |              |          |               | :                       | NOP          |               |       |

|                                                                        | .RES.W       | 1        |               | L13:                    |              |               |       |

|                                                                        | .DATA.L      | _a       |               |                         | RTS          |               |       |

|                                                                        | .DATA.L      | L13      |               | :                       | NOP          |               |       |

| L15:                                                                   |              |          |               | : L15:                  |              |               |       |

| NOP                                                                    |              |          |               |                         | .RES.W       | 1             |       |

|                                                                        | .ALIGN       | 4        |               |                         | .DATA.L      | _a            |       |

|                                                                        | MOV.L        | L18+2,R6 | ; _a          | :                       |              |               |       |

|                                                                        | BRA          | L17      | —             | :                       |              |               |       |

|                                                                        | MOV.L        | @R6,R2   | ; a           |                         |              |               |       |

| L18:                                                                   |              | · · · ·  |               |                         |              |               |       |

| -                                                                      | .RES.W       | 1        |               | :                       |              |               |       |

|                                                                        | .DATA.L      | _a       |               | :                       |              |               |       |

| L17:                                                                   |              | _~       |               |                         |              |               |       |

|                                                                        | TST          | R2,R2    |               |                         |              |               |       |

|                                                                        | BT           | L13      |               | :                       |              |               |       |

|                                                                        | 101          | цт.)     |               |                         |              |               |       |

### APPLICATION NOTE

| N    | 10P |  |

|------|-----|--|

| L13: |     |  |

| F    | RTS |  |

| Ň    | JOP |  |

# 1.4 Generates or does not generate save and restore code at the start and end of functions

Program execution speed and efficiency of ROM usage can be improved by deleting the register save operation at function entry points and the register restore operation at function exit points. You can use the #pragma noregsave, #pragma noregalloc, and #pragma regsave directives for fine-grained control of the saving and restoring of the guaranteed registers listed in Table 1-5.

## Table 1-5 Guaranteed registers that can be controlled by using "#pragma noregsave", "#pragma noregalloc", and "#pragma regsave"

| Register      | Explanation                                                                                 |

|---------------|---------------------------------------------------------------------------------------------|

| R8 - R14      |                                                                                             |

| FR12 - FR15   | SH-2E, SH2A-FPU, SH-4, and SH-4A registers used for single-precision floating-point numbers |

| DR12 and DR14 | SH2A-FPU, SH-4, and SH-4A registers used for double-precision floating-point numbers        |

Specifying #pragma noregsave for frequently executed functions can reduce program size and improve execution speed.

- (1) The #pragma noregsave directive specifies that guaranteed registers are not saved and restored at the entry and exit points of functions.

- (2) The #pragma noregalloc directive is used to create an object that does not save/restore guaranteed registers at function entry/exit points, and does not allocate guaranteed registers across function calls.

- (3) The #pragma regsave directive is used to create an object which saves and restores guaranteed-registers at function entry/exit points, and does not allocate guaranteed registers.

- (4) #pragma regsave and #pragma noregalloc can be specified simultaneously for the same function. Such overlapping specifications causes an object to be created in which all guaranteed-registers are saved and restored at the function entry/exit points, and no guaranteed registers are allocated across function calls.

| Table 1-6 Operation of | "#pragma regsave" | , "#pragma noregs                       | save", and "#pragr | na noregalloc" |

|------------------------|-------------------|-----------------------------------------|--------------------|----------------|

|                        |                   | , , , , , , , , , , , , , , , , , , , , |                    |                |

| #pragma                                 | Register save/restore operations                 | Register use                                                                                                                                        |

|-----------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| #pragma noregsave                       | Guaranteed registers are not saved and restored. | Guaranteed registers are used.                                                                                                                      |

| #pragma noregalloc                      | Guaranteed registers are not saved and restored. | Guaranteed registers are not used across multiple function calls.                                                                                   |

| #pragma regsave                         | Guaranteed registers are saved and restored.     | Guaranteed registers are not used across<br>multiple function calls.<br>The frequency of using guaranteed registers<br>within one function is low.  |

| #pragma regsave +<br>#pragma noregalloc | Guaranteed registers are saved and restored.     | Guaranteed registers are not used across<br>multiple function calls.<br>The frequency of using guaranteed registers<br>within one function is high. |

A function for which #pragma noregsave is specified might not operate correctly if it is called from ordinary functions. Make sure that a function for which #pragma is specified is called from one of the following types of functions:

- Function for which #pragma regsave is specified

- Function for which #pragma noregalloc is specified and that is called from a function for which #pragma regsave is specified

Before allowing a function for which the #pragma noregsave, #pragma noregalloc, or #pragma regsave directive is specified to be called, make sure that the directive is specified for all instances of the function throughout the project. Renesas recommends that you specify the directive in a common header file.

#### Example 1:

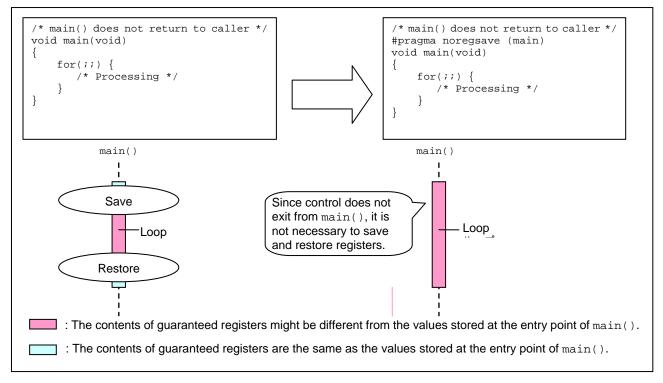

For a function that does not return to the caller, the contents of registers do not need to be saved and restored. You can therefore reduce object size and improve execution speed by specifying #pragma noregsave for such a function.

#### Example 2:

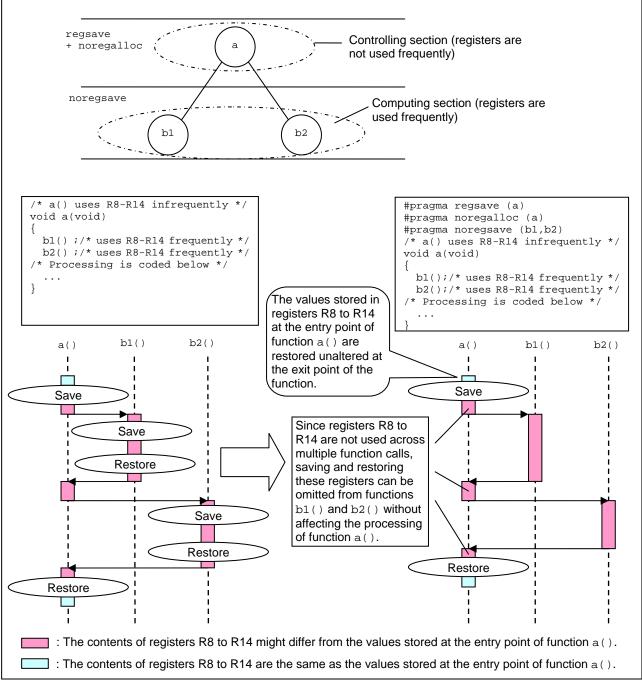

If functions bl() and b2() use guaranteed registers, the contents of these registers are saved at the entry points of the functions and restored at the exit points of the functions. For example, if function a() frequently calls functions bl() and b2(), the guaranteed registers are also saved and restored frequently, lowering efficiency. If function a() does not use guaranteed registers, functions bl() and b2(), the guaranteed registers need not be saved and restored. If #pragma regsave is specified for function a(), the contents of guaranteed registers are saved at the entry point and restored at the exit point of the function, but the guaranteed registers are not used across multiple function calls. In addition, if #pragma noregsave is specified for functions bl() and b2(), the guaranteed registers are never saved and restored for these functions. When #pragma directives are specified in this way, guaranteed registers are saved and restored only for function a().

You can optimize the location of register save and restore operations as described above to decrease their frequency.

Specifying #pragma noregsave together with #pragma regsave results in effective optimization because the frequency of using guaranteed registers within a function increases. If you specify #pragma regsave, you should also specify #pragma noregsave.

Figure 1-4

#### Example 3:

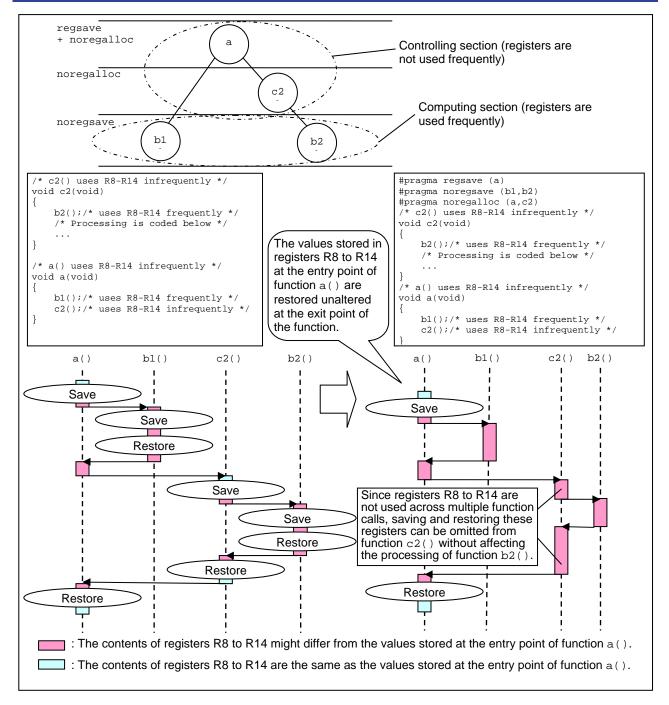

When functions b1() and b2() use guaranteed registers, the contents of these registers are saved at the entry points of the functions and restored at the exit points of the functions. For example, when functions b1() and b2() are also frequently called from function c2(), which is called from function a(), the guaranteed registers are also saved and restored frequently, lowering the efficiency of program execution.

If functions a() and c2() do not use the same guaranteed registers, functions b() and b2() do not require that these registers be saved and restored. If you specify function a() in #pragma regsave and #pragma noregalloc directives, the contents of the guaranteed registers are saved at the entry point and restored at the exit point of function a(), and the guaranteed registers used by function a() are not used by other functions. If you specify function c2() in the #pragma noregalloc directive, the guaranteed registers used by function c2()are not used by other functions. If you specify functions b1() and b2() in the #pragma regsave directive, you can suppress saving and restoring of the guaranteed registers used by these functions.

When the directive settings are specified as described above, guaranteed registers are saved and restored for function a(), but are not saved and restored for functions b1() and b2(). Accordingly, you can reduce the frequency of register save and restore operations by changing the register save and restore locations.

### APPLICATION NOTE

Figure 1-5

#### 1.5 Allocates global variables to registers

You can use the #pragma global\_register directive to allocate global variables to registers. By allocating global variables to registers, you can reduce the number of load and store instructions.

You must specify the <code>#pragma global\_register</code> directive in all files. Use the <code>preinclude</code> option to specify a header file that contains the <code>#pragma global\_register</code> declaration. This option specifies the directive in all files. For details about how to specify the option settings in Renesas IDE, see Figure 1-6.

For the standard library as well, you must specify the <code>#pragmaglobal\_register</code> directive. Use the preinclude option to specify a header file that contains the <code>#pragmaglobal\_register</code> declaration. For details about how to specify the option settings in Renesas IDE, see Figure 1-7.

#### Format:

#### #pragma global\_register [(]variable-name=register-name[,...][)]

- For *variable-name*, you can specify a global variable of the integer, float, or pointer type. If the CPU is not SH2A-FPU, SH-4, or SH-4A, you can specify a global variable of type double when the double=float option is specified.

- For *register-name*, you can specify R8 to R14, FR12 to FR15 (when the CPU is SH-2E, SH2A-FPU, SH-4, or SH-4A), DR12, or DR14 (when the CPU is SH2A-FPU, SH-4, or SH-4A).

- Types of variables that can be allocated to registers FR12 to FR15

- (i) SH-2E

- float type

- double type (when the double=float option is specified)

- (ii) SH2A-FPU, SH-4, and SH-4A

- float type (when the fpu=double option is not specified)

- double type (when the fpu=single option is not specified)

- Types of variables that can be allocated to registers DR12 to DR14

- (i) SH2A-FPU, SH-4, and SH-4A

- float type (when the fpu=double option is specified)

- double type (when the fpu=single option is not specified)

- You can neither set initial values for the variables nor use the variables for address reference.

- If the #pragma global\_register directive settings are the same for all files and the library, correct operation cannot be guaranteed.

- You can specify only static data members. You cannot specify non-static data members.

Option settings in Renesas IDE:

| Configuration :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C/C++ Assembly Link/Library Standard Library CPU Deb                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dhry21       □ - □       All Loaded Projects       □ - □       dhry21       □ - □       C source file       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □       □ - □ <t< td=""><td>Category : Source  Show entries for :  Preinclude files  \$(FILEDIR)¥gregister.h  Add  Insert  Remove  Move up  Move up</td></t<> | Category : Source  Show entries for :  Preinclude files  \$(FILEDIR)¥gregister.h  Add  Insert  Remove  Move up  Move up                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Options C/C++ :<br>-cpu=sh2 -preinclude="\$(FILEDIR)¥gregister.h" -<br>object="\$(CONFIGDIR)¥\$(FILELEAF).obj" -debug -show=tab=4<br>-speed -goptimize -map="\$(CONFIGDIR)<br>OK Cancel |

Figure 1-6

| SuperH RISC engine Standard Toolch | ain                                                                                                                                                                                                                          | <u>?</u> × |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Configuration :                    | C/C++ Assembly Link/Library Standard Library CPU                                                                                                                                                                             | Deb 💶      |

| Dhry21                             | Category: Other Miscellaneous options: Check against EC++ language specification Check against DSP-C language specification Saves/restores SSR and SPC registers User defined options: -preinclude="\$(PROJDIR)¥gregister.h" |            |

|                                    | Options Standard Library :                                                                                                                                                                                                   | A F        |

|                                    | OK Ca                                                                                                                                                                                                                        | ncel       |

Figure 1-7

Example:

```

Source code:

#pragma global_register(x=R13,y=R14)

int x;

char *y;

void func1(void)

{

x++;

}

void func2(void)

{

*y=0;

}

void func(int a)

{

x = a;

func1();

func2();

Expanded assembly code:

_func1:

RTS

ADD

#1,R13

_func2:

MOV

#0,R2

; H'0000000

RTS

MOV.B

R2,@R14

; *(y)

_func:

STS.L

PR,@-R15

_func1

R4,R13

BSR

MOV

BRA

_func2

@R15+,PR

LDS.L

```

#### 1.6 Specifies GBR base variables

A GBR base variable is a variable for which a GBR base is specified and which can be accessed GBR relative access code. The use of a relative address means that the variable address does not have to be loaded, resulting in a smaller object.

Note, however, that the number and size of variables that can be used as GBR base variables are limited. Specify as GBR base variables only those variables that will be used frequently.

Format:

## #pragma gbr\_base (variable-name [,variable-name...]) #pragma gbr\_base1 (variable-name [,variable-name...])

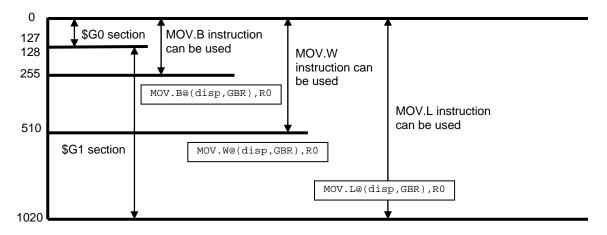

The #pragma gbr\_base directive allocates the specified variables in the \$G0 section, which occupies relative byte positions 0 to 127 from the address indicated by GBR.

The #pragma gbr\_basel directive allocates the specified variables in the \$G1 section, which occupies relative byte positions 128 to 1020 from the address indicated by GBR. However, in this section, the maximum byte position at which a variable can be allocated depends on the data type. For a variable of type char or unsigned char, the maximum byte position is 255. For a variable of type unsigned short, the maximum byte position is 510. For a variable of type int, unsigned int, long, unsigned long, float, or double, the maximum byte position is 1020.

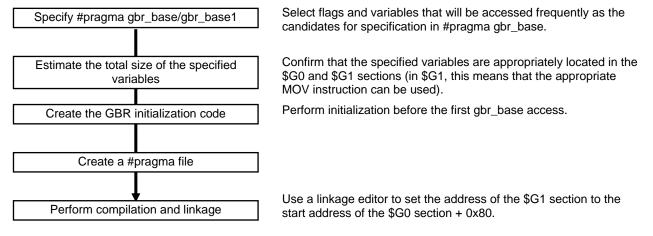

Figure 1-8

Variables that are frequently accessed or used for bitwise operations should be allocated in the \$G0 section if at all possible. An object that accesses data in the \$G0 section is faster and smaller than an object that accesses data in the \$G1 section (see Example 2 below).

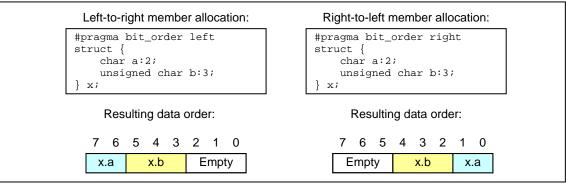

The #pragma gbr\_base and #pragma gbr\_base1 directives allocate the specified variables in the appropriate sections in the order in which the variables are declared. Since alternately declaring variables of different sizes wastes space, as much as possible, try to declare variables of the same size together.

If GBR base variables overflow the appropriate area, the following error occurs during linkage:

```

L2330 (E)Relocation size overflow

```

If this error occurs, delete specification of the relevant variables from the <code>#pragma gbr\_base</code> or <code>#pragma gbr\_base1</code> directive.

To use the <code>#pragma gbr\_base</code> directive, use a linkage editor to set the \$G0 section. To use the <code>#pragma gbr\_base1</code> directive, use a linkage editor to set the \$G0 and \$G1 sections. When you set the \$G1 section, make sure that the address of the section is the start address of the \$G0 section + 0x80.

Note that the same specification of the #pragma gbr\_base and #pragma gbr\_base1 directives should be used throughout the project. The preinclude option is useful for ensuring the same specification throughout the project.

The variables specified in the #pragma gbr\_base or #pragma gbr\_base1 directive are allocated in either the \$G0 or \$G1 section whether or not an initial value is specified. When the compiler generates an object, the compiler treats the \$G0 and \$G1 sections as initialized data. The initialized data (variables) has initial values. Although the initial values

# RENESAS

must be prepared in the ROM area, the data must be stored in the RAM area because the data might change during program execution.

Therefore, after an initial value is set in the ROM area, the initial value must be copied from the ROM area to the RAM area. To set an initial value in the ROM area and to access data with an address in the RAM area, you must use a linkage editor to specify the appropriate ROM support option. For the \$G0 and \$G1 sections, you must also add processing that copies the initial data from the ROM area to the RAM area, and use a linkage editor to specify the appropriate ROM support option. For the \$G0 and \$G1 sections, you must also add processing that copies the initial data from the ROM area to the RAM area, and use a linkage editor to specify the appropriate ROM support option. For details, see 4.Memory Initialization in the manual SuperH RISC engine C/C++ Compiler Package APPLICATION NOTE: [Introduction guide] Sample file Guide for SH-1, SH-2, and SH-2A.

Make sure that the address of the RAM area for the G1 section is the address of the RAM area for the G0 section + 0x80.

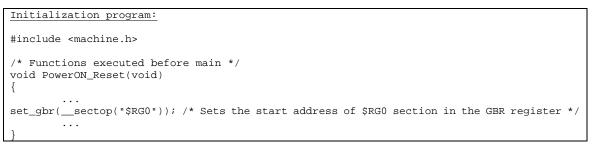

Before you can use GBR base variables, you must set the start address of the RAM area for copying the \$G0 section in the GBR register. You can use intrinsic function set\_gbr() to perform this operation.

The following is an example of code that copies the \$G0 section in the ROM area to the \$G1 section in the RAM area.

The following explains the tasks required before you can use the GBR base.

#### Figure 1-9

If you specify the <code>#pragma gbr\_base</code> or <code>#pragma gbr\_base1</code> directive, specify the <code>gbr=user</code> option (Figure 1-10). If you do not specify the option, a warning is output for the directive and specification of the directive is ignored.

# RENESAS

Note that if you select **User(gnenrate logic operation**) from the **GBR relative operation** drop-down list, the gbr=user and logic\_gbr options are specified. If these options are specified, GBR relative logical operation instructions might be used for operations that do not use GBR base variables.

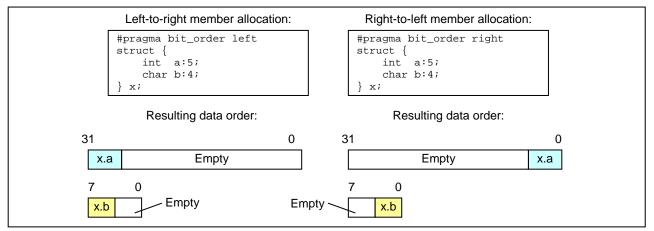

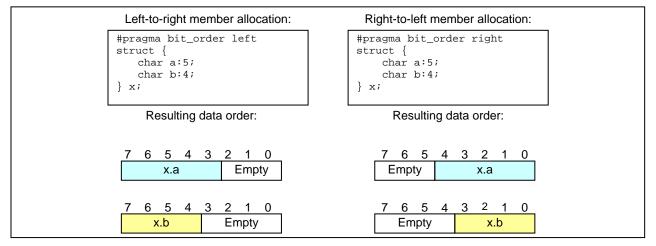

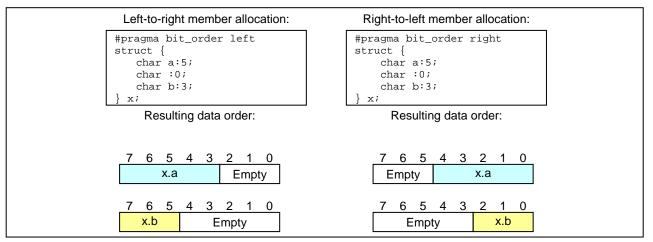

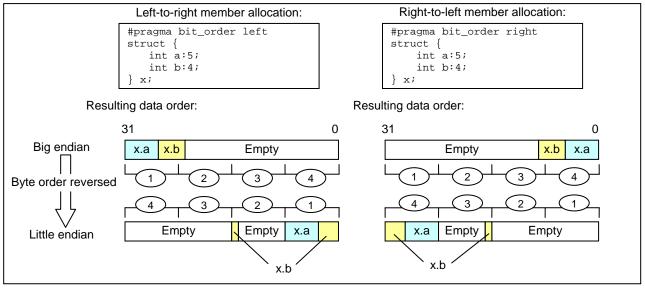

| SuperH RISC engine Standard Toolcha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ain 🤶 🕺                                              |