# RL78/F13, F14

# DTC (高速転送, チェイン転送) 使用例

R01AN3261JJ0100 Rev.1.00 2017.12.01

# 要旨

本資料では、DTC(高速転送,チェイン転送)を使用して、A/D 変換完了を DTC のトリガとし、A/D 変換結果を RAM に転送(高速転送)、A/D 変換結果を UARTO によるシリアル送信(チェイン転送)、および A/D 変換結果を PWM 出力幅に反映(チェイン転送)する方法を説明します。

# 目次

| 1. DTC(高速転送, チェイン転送)の動作概要       | 2  |

|---------------------------------|----|

| 2. 仕様                           | 6  |

| 3. 周辺機能の設定手順                    |    |

| 3.1 周辺機能の初期化手順                  | 12 |

| 3.2 DTC(高速転送)およびDTC(通常転送)の初期化手順 | 13 |

| 3.3 A/Dコンバータの初期化手順              |    |

| 3.4 TAUの初期化手順                   | 17 |

| 3.5 SAUの初期化手順                   |    |

| 3.6 周辺機能の動作許可(DTC(高速転送)転送開始)手順  | 20 |

| 3.7 DTC転送完了割り込み処理               | 20 |

| 4. 注意事項                         |    |

| 4.1 DTC転送サイクル数                  | 21 |

| 4.2 DTC使用上の注意事項                 | 23 |

# 1. DTC (高速転送, チェイン転送) の動作概要

RL78/F13, F14 に搭載している DTC は、CPU を介さずにメモリとメモリ間でデータを転送する機能です。 転送方式として、コントロール・データを RAM に配置した転送 (通常転送と称す) と専用のコントロール・データを持ち通常転送より転送サイクルが少ない高速転送を持ちます。また、転送モードとしてノーマル・モードとリピート・モードがあり、転送終了後に設定された次の転送を連続で行うチェイン転送の機能があります。

DTC (高速転送、チェイン転送)では、DTC 起動要因の発生により、初めに DTC (高速転送)を行います。チェイン転送が選択されている場合、次に DTC (通常転送)を行い、チェイン転送禁止に設定された DTC 転送が完了するまで、チェイン転送を連続して実行します。チェイン転送はすべて DTC (通常転送)になります。初めの DTC (高速転送)の実行により DTC 転送完了割り込み要求を出力しますが、チェイン転送による DTC 転送時は割り込みを保留します。よって、すべての転送の完了により、DTC 転送完了割り込みが受け付け可能となります。

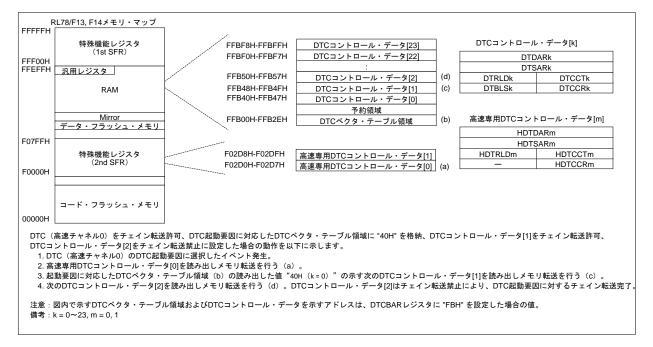

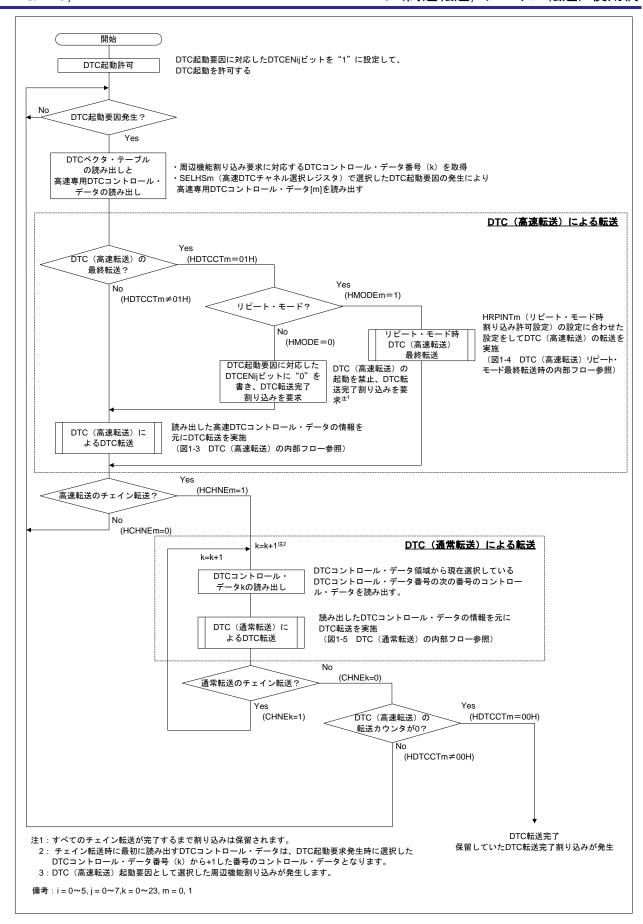

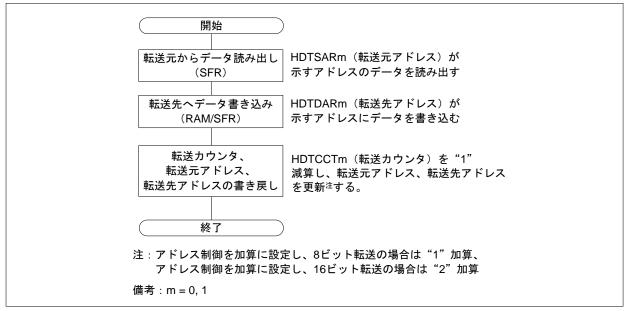

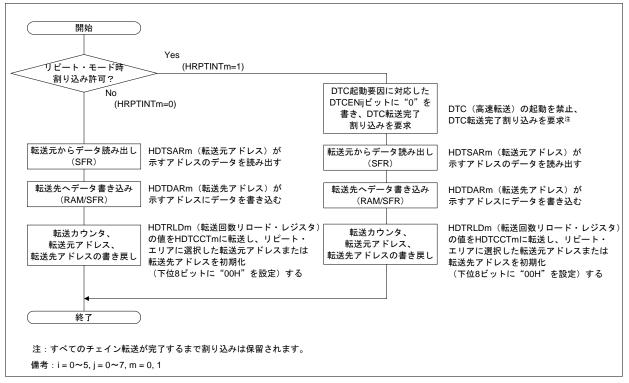

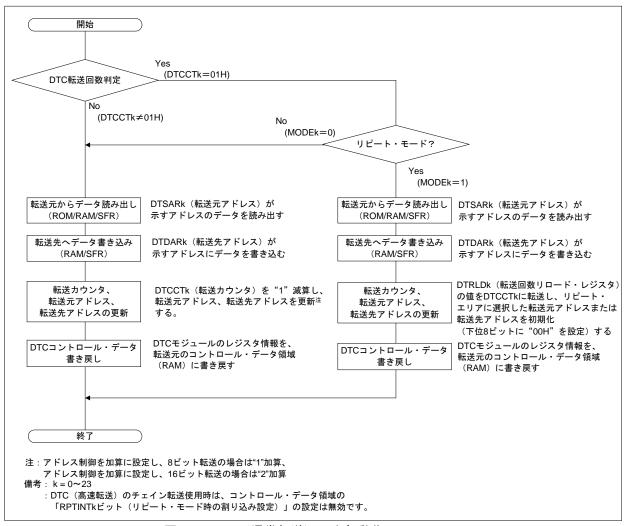

DTC (高速転送, チェイン転送) の動作フロー (概略) を図1-1に、DTC (高速転送, チェイン転送) の内 部動作フローを図1-2~図1-5に示します。

図1-1 DTC (高速転送, チェイン転送) の動作フロー (概略)

図1-2 DTC (高速転送, チェイン転送) の内部動作フロー

図1-3 DTC (高速転送) の内部動作フロー

図1-4 DTC (高速転送) のリピート・モード最終転送時の内部動作フロー

図1-5 DTC (通常転送) の内部動作フロー

#### 2. 仕様

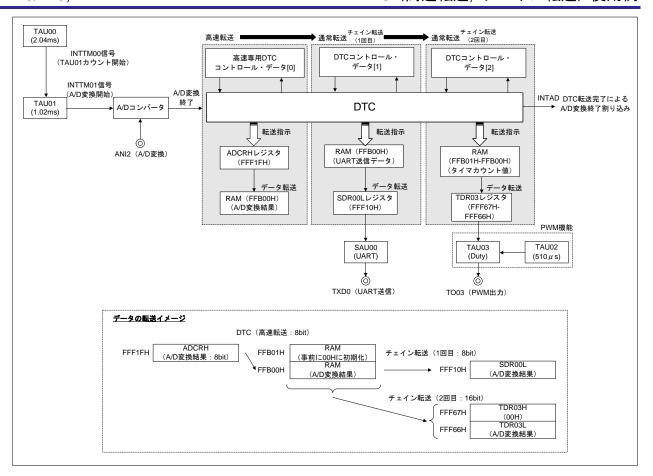

DTC、A/D コンバータ、TAU (タイマ・アレイ・ユニット) のチャネル 0~3 (以降 TAU00~TAU03)、 UARTO の送信(SAU(シリアル・アレイ・ユニット)のチャネル 0(以降 SAU00)) を組み合わせた使用例 を示します。

TAU00 (2.04ms) と連動して TAU01 (1.02ms) のカウントを行い、A/D コンバータは TAU01 の割り込み 要求信号をトリガとして ANI2 端子の入力電圧を A/D 変換します。 また、 TAU02 (510μs) と連動して TAU03 のカウントを行い TO03 端子から PWM 信号を出力します。DTC は、A/D 変換終了を DTC (高速転送) の起 動要因として DTC 動作を開始し、チェイン転送により以下のメモリ転送を行います。

- ・A/D 変換結果を RAM に転送 (DTC (高速転送))

- ・RAM に格納した A/D 変換結果を SDR00L レジスタに転送 (DTC (通常転送))

- ・RAM に格納した A/D 変換結果を TDR03 レジスタに転送(DTC(通常転送)) 以降、この処理を繰り返します。

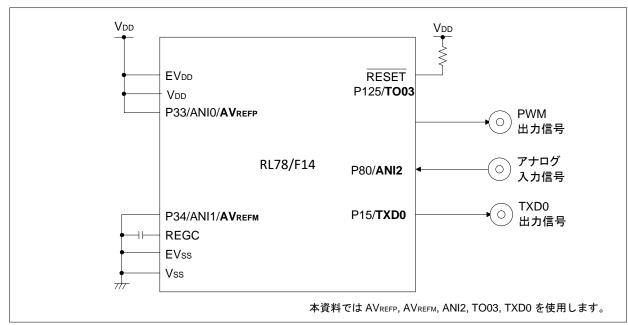

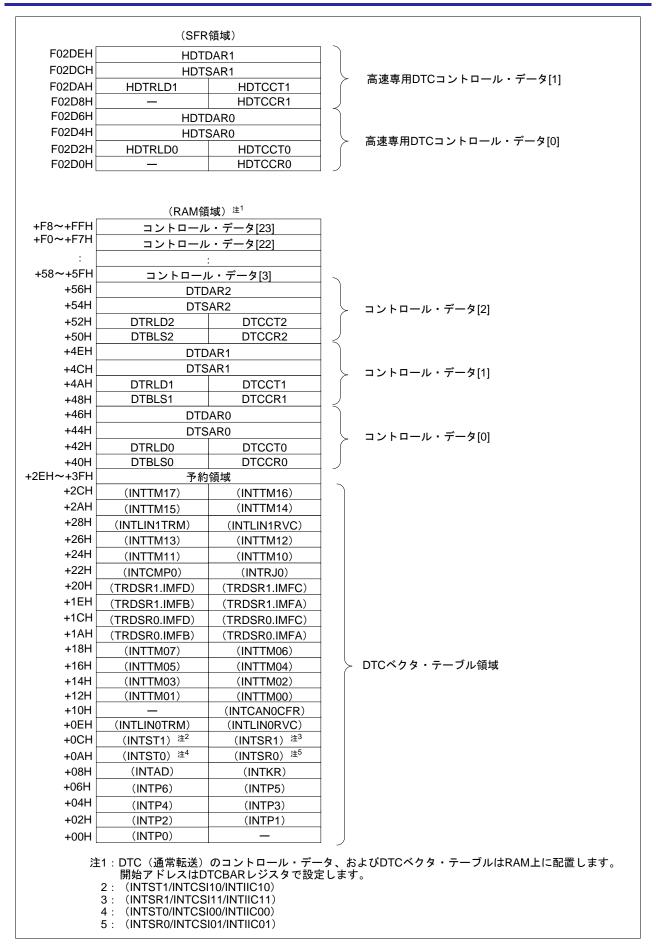

図2-1に使用端子の接続図、表2.1に使用する周辺機能と用途、図2-2に使用する周辺機能の構成図、図2-3に DTCコントロール・データとDTCベクタ・テーブルの配置、図2-4と図2-5に DTC 転送タイミングを示します。

図2-1 使用端子の接続図

# 表2.1 使用する周辺機能と用途

| 周辺機能               | 用途                                                      |

|--------------------|---------------------------------------------------------|

| A/D コンバータ          | ANI2 端子のアナログ入力信号を A/D 変換                                |

|                    | 8 ビット分解能                                                |

|                    | ハードウエア・トリガ・ノーウエイト・モード(要因:INTTM01)                       |

|                    | ハードウェア・ドリカ・ノーウェイド・モード(安因:INTTMOT)  <br>  セレクト・モード(1 端子) |

|                    | フンショット変換モード                                             |

| TAU00              | 定周期タイマ                                                  |

| 17.000             | インターバル・タイマ・モード(2.04ms)                                  |

|                    | マスタ・チャネルとして使用                                           |

| TAU01              | A/D 変換トリガ(INTTM01)の発生                                   |

|                    | ワンカウント・モード (1.02ms)                                     |

|                    | TAU00 のスレーブ・チャネルとして使用                                   |

| TAU02              | 定周期タイマ                                                  |

|                    | インターバル・タイマ・モード(510μs)                                   |

|                    | マスタ・チャネルとして使用                                           |

| TAU03              | PWM 信号の出力                                               |

|                    | ワンカウント・モード                                              |

|                    | 出力端子 : TO03                                             |

|                    | High 幅  :0~510 μ s                                      |

|                    | (A/D 変換結果の上位 8 ビットを 0 拡張したデータ)                          |

|                    | TAU02 のスレーブ・チャネルとして使用                                   |

| SAU00              | UART モードで TXD0 端子から送信を行う                                |

|                    | 動作モード : UART モード(送信機能)                                  |

|                    | ボー・レート : 9600bps (誤差:+0.16%)                            |

|                    | (8 ビット・データ、パリティなし、ストップ・ビット: 1 ビット、                      |

|                    | LSB ファースト)                                              |

| DTC(高速 DTC チャネル 0) | A/D 変換結果レジスタ値を RAM に転送                                  |

|                    | DTC 起動要因 : A/D 変換の完了                                    |

|                    | 転送元アドレス : ADCRH レジスタ                                    |

|                    | 転送先アドレス : RAM                                           |

|                    | 転送サイズ : 1 バイト                                           |

|                    | 転送回数 : 1回                                               |

|                    | 動作モード:リピート・モード、チェイン転送許可                                 |

| DTC(コントロール・データ 1)  | A/D 変換結果レジスタ値をシリアル・データ・レジスタ 00 に転送                      |

|                    | DTC 起動要因 :-                                             |

|                    | 転送元アドレス : RAM(A/D 変換結果の格納先)                             |

|                    | 転送先アドレス : SDR00L レジスタ                                   |

|                    | 転送サイズ : 1 バイト                                           |

|                    | 転送回数 :1回                                                |

|                    | 動作モード : リピート・モード、チェイン転送許可                               |

| DTC(コントロール・データ 2)  | A/D 変換結果レジスタ値をタイマ・データ・レジスタ 03 に転送                       |

|                    | DTC 起動要因 : -                                            |

|                    | 転送元アドレス : RAM(A/D 変換結果の格納先)                             |

|                    | 転送先アドレス : TDR03 レジスタ                                    |

|                    | 転送サイズ : 2 バイト                                           |

|                    | 転送回数 :1回                                                |

|                    | 転送回数 : 「回<br>  動作モード : リピート・モード、チェイン転送禁止                |

|                    | 刧ルし ドー・フロード・モード、チェイノ料込示単                                |

図2-2 使用する周辺機能の構成図

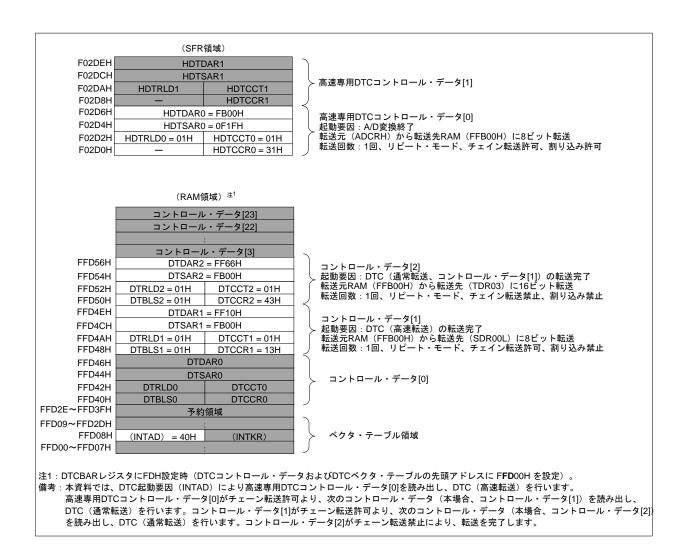

図2-3 DTC コントロール・データと DTC ベクタ・テーブルの配置

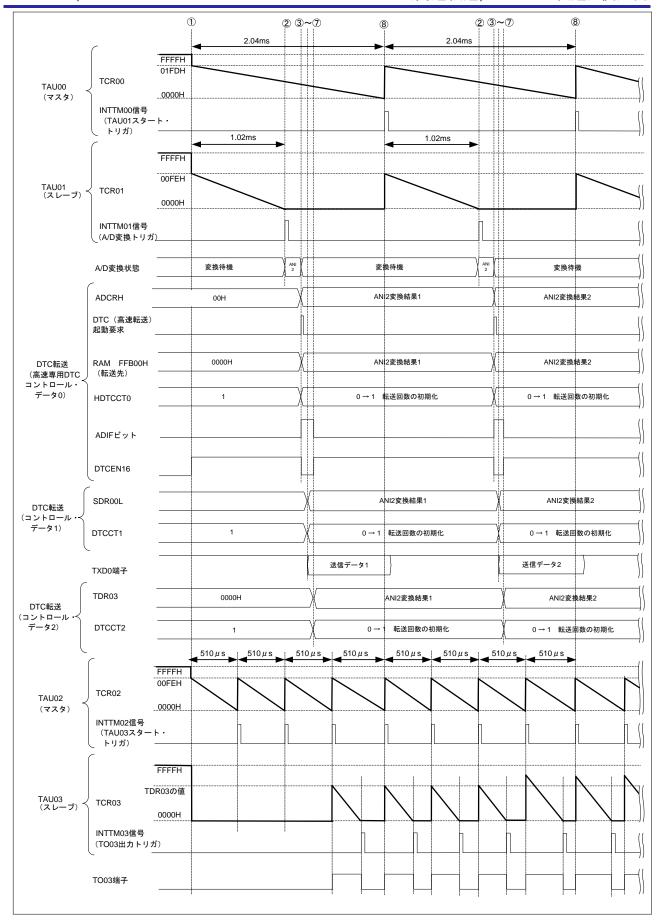

図2-4 DTC 転送タイミング (1/2)

- ① ソフトウェアで以下のレジスタを設定して機能を動作状態にします。

- ・DTCEN1レジスタのDTCEN16ビットを1(DTC起動許可(要因: A/D変換完了))に設定。

- ・TS0レジスタのTS00, TS01, TS02, TS03ビットを1(TAU00, TAU01, TAU02, TAU03カウント開始)に 設定。

- ・SSOレジスタのSE00ビットを1(SAU0 CH0を通信待機状態)に設定。

- ② TAU01のカウント完了時にINTTM01信号を出力します。また、本信号をトリガとしてA/D変換を開始します。

- ③ A/D変換終了後、ADIFビットが1に変化し、A/D変換終了割り込み要求信号をトリガとしてDTC(高速転送)がメモリ転送(ADCRHレジスタ→RAM)を行います。

また、DTC転送時にHDTCCT0レジスタの減算を行います。

- ④ HDTCCT0レジスタが1から0になる転送実行時に、以下の動作を行います。

- ・DTCEN16ビットを0(DTC起動禁止)

- ・DTC(高速転送)転送完了によるA/D変換終了割り込み要求の発生(チェイン転送によるすべてのDTC転送が完了するまで割り込み発生は保留されます。)

- ・DTC(高速転送)データ転送実施(ADCRHレジスタ→RAM)

- ・HDTCCT0レジスタにHDTRLD0レジスタの値を格納(DTC(高速転送)転送回数の初期化)

- ⑤ HDTCCR0レジスタのHCHNE0ビットが1になっていることを確認し、コントロール・データ領域のコントロール・データ1を読み込み、以下の動作を行います。

- ・DTC (通常転送) データ転送実施 (RAM (A/D変換結果格納領域) →SDR00Lレジスタ)

- ・DTCCT1レジスタを減算

また、SAU0はSDR00Lレジスタへのデータ転送により、TXD0端子からA/D変換結果を送信します。

- ⑥ DTCCR1レジスタのCHNEビットが1になっていることを確認し、コントロール・データ領域のコントロール・データ2を読み込み、以下の動作を行います。

- ・DTC(通常転送)データ転送実施(RAM(A/D変換結果格納領域の16ビット拡張値)→TDR03レジスタ)

- ・DTCCT2レジスタを減算

- ⑦DTC転送完了によるA/D変換完了割り込み要求が発生します。この時ソフトウェアで以下の設定を行います。

- ・ソフトウェアでDTCEN1レジスタのDTCEN16ビットに1を設定。(DTC(高速転送)起動許可)

- ®TAU00、TAU01は以下の動作を行います。

- ・TAU00のカウント完了時にINTTM00信号を出力。(TAU00割り込み要求信号の発生)

- ・TAU01 (スレーブ) のカウントを開始。

- また、②~8の間にTAU02、TAU03は以下の動作を行います。

- ・TAU02のカウント完了時にINTTM02信号を出力し(TAU02割り込み要求信号の発生)、TO03端子からHレベルを出力。(TDR03レジスタの値が0000Hの場合は除く)

- ・TAU03(スレーブ)のカウントを開始。

- ・TAU03のカウント完了時にTO03端子からLレベルを出力。

備考 TCR00 : タイマ・カウンタ・レジスタ00

INTTM00信号 : タイマ・チャネル0のカウント完了/キャプチャ完了割り込み要求信号

TCR01 : タイマ・カウンタ・レジスタ01

INTTM01信号 : タイマ・チャネル1のカウント完了/キャプチャ完了割り込み要求信号 (A/D変換開始トリガとして使用)

A/D変換状態 : 10ビット逐次変換レジスタ

ADCRH :8ビットA/D変換結果レジスタ (ADCRの上位8ビット) DTC (高速転送) 起動要求:1端子のA/D変換終了割り込み信号

FFB00H : HDTDAR0(高速DTC転送先アドレスレジスタ)の示すRAM(A/D変換結果格納用)

HDTCCT0 : 高速DTC転送回数レジスタ0 ADIFビット : A/D変換終了割り込みフラグ DTCEN16 : DTCEN1レジスタのDTCEN16ビット

SDR00L : シリアル・データ・レジスタ00 (SDR00の下位8ビット)

TXD0端子 : UART0送信端子

DTCCT1: DTCコントロール・データ領域に配置するDTC転送回数レジスタ1

TCR02 : タイマ・カウンタ・レジスタ02

INTTM02信号 : タイマ・チャネル2のカウント完了/キャプチャ完了割り込み要求信号

TCR03 : タイマ・カウンタ・レジスタ03

INTTM03信号 : タイマ・チャネル3のカウント完了/キャプチャ完了割り込み要求信号

TDR03 : タイマ・データ・レジスタ3

TO03端子 : タイマ・チャネル3のPWM信号出力端子

DTCCT2 : DTCコントロール・データ領域に配置するDTC転送回数レジスタ2

TAU00, TAU01のカウント・クロックはCK03 (fcLk/128 = 250KHz) を選択 TAU02, TAU03のカウント・クロックはCK02 (fcLk/64 = 500KHz) を選択

図2-5 DTC 転送タイミング(2/2)

# 3. 周辺機能の設定手順

本章では、「2. 仕様」で説明した周辺機能(DTC、A/D コンバータ、TAU、SAU)の設定手順を示します。

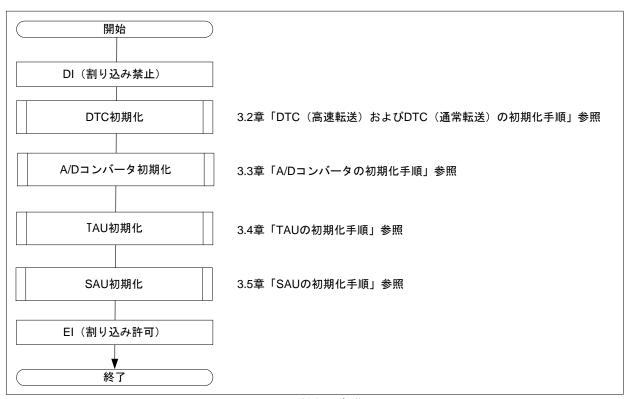

# 3.1 周辺機能の初期化手順

使用する周辺機能の初期化手順を図3-1に示します。

図3-1 周辺機能の初期化手順

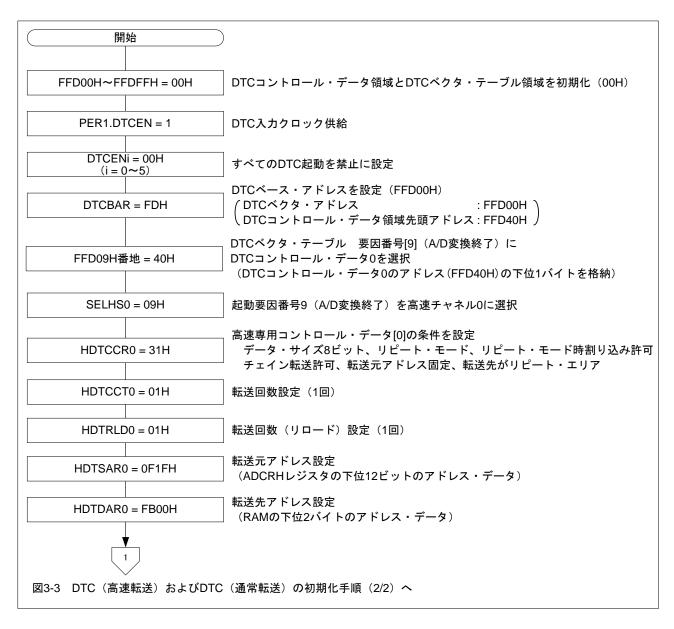

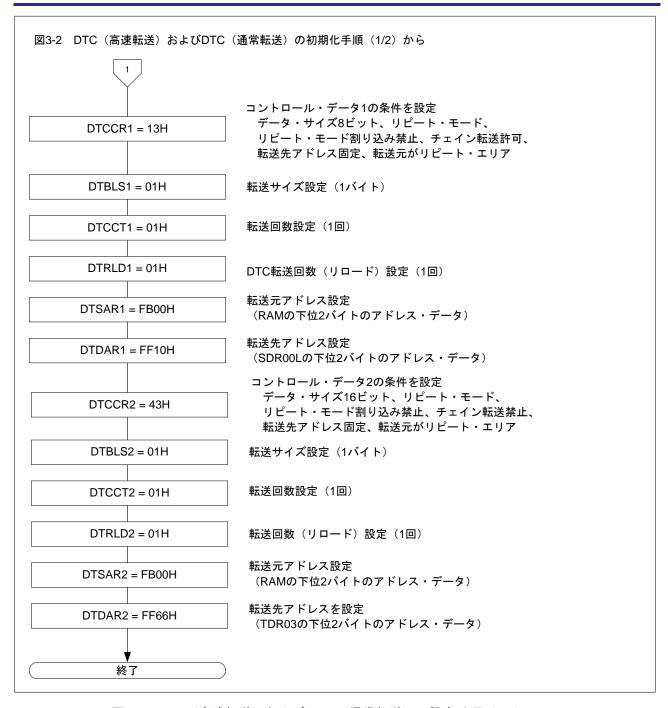

# 3.2 DTC(高速転送) および DTC(通常転送) の初期化手順

A/D 変換終了を起動要因として、A/D 変換結果の RAM 上の変換結果格納領域への転送(高速転送)、A/D 変換結果格納領域に格納した A/D 変換結果の SDR00L レジスタへの転送(チェイン転送)、A/D 変換結果格納領域に格納した A/D 変換結果(16 ビット拡張)の TDR03 レジスタへの転送(チェイン転送)を連続して実施します。

図3-2および図3-3に、DTC (高速転送) および DTC (通常転送) の初期化手順を示します。また図3-4にDTC コントロール・データの配置を示します。

図3-2 DTC (高速転送) および DTC (通常転送) の初期化手順 (1/2)

図3-3 DTC(高速転送)およびDTC(通常転送)の設定手順(2/2)

図3-4 DTC コントロール・データの配置

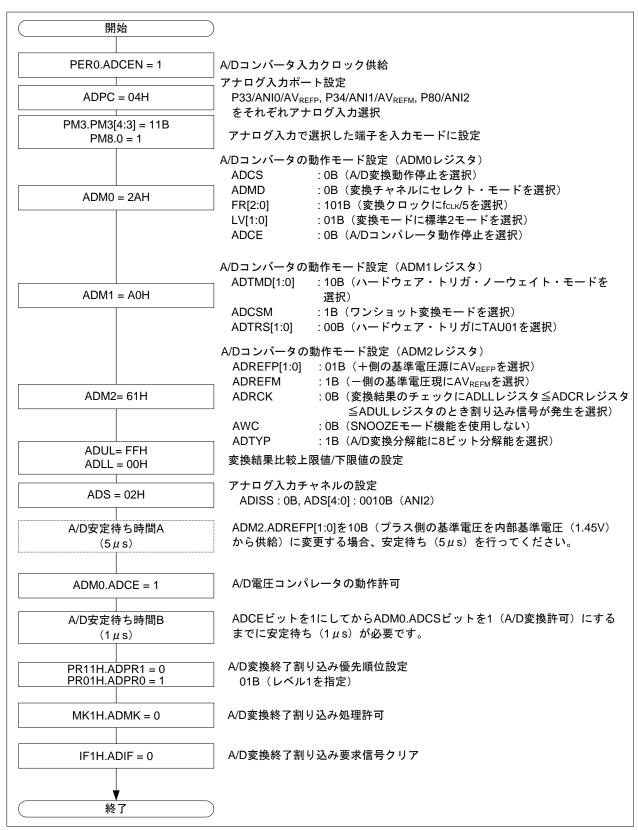

#### 3.3 A/D コンバータの初期化手順

ANI2 端子のアナログ入力信号を A/D 変換する設定を行います。

図3-5にA/Dコンバータの初期化手順を示します。

図3-5 A/D コンバータの初期化手順

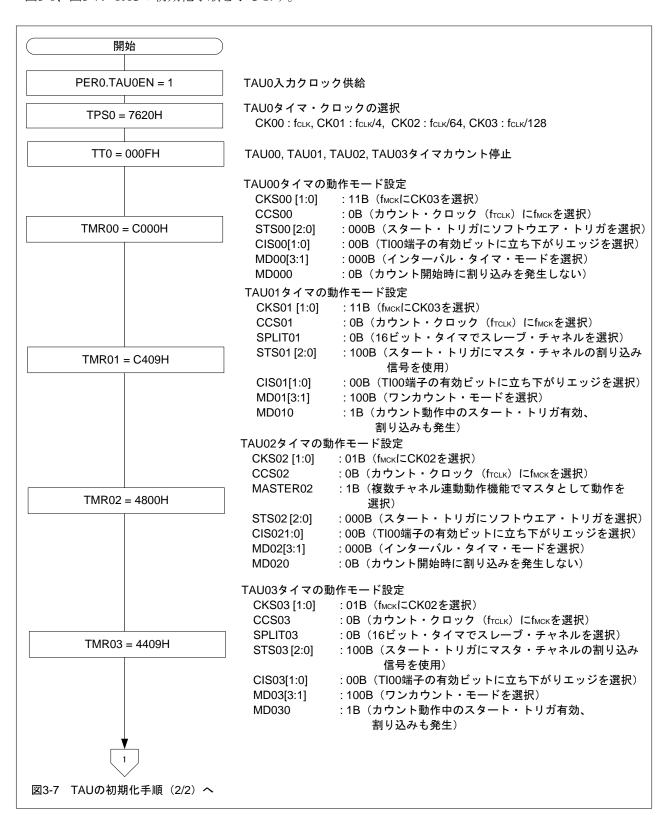

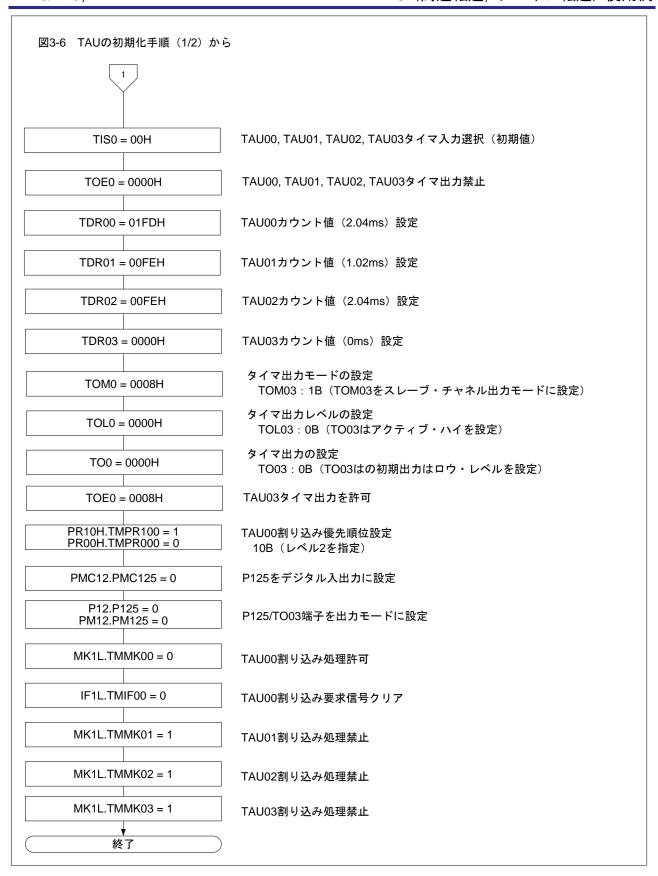

#### 3.4 TAU の初期化手順

TAU00 を 2.04ms 周期のタイマ、TAU01 を TAU00 のスレーブ・チャネルとして 1.02ms を設定します。次に、TAU02 をマスタ・チャネル、TAU03 をスレーブ・チャネルとして周期  $510\,\mu$  s の PWM 機能として設定します。

図3-6、図3-7にTAUの初期化手順を示します。

図3-6 TAU の初期化手順(1/2)

図3-7 TAU の初期化手順(2/2)

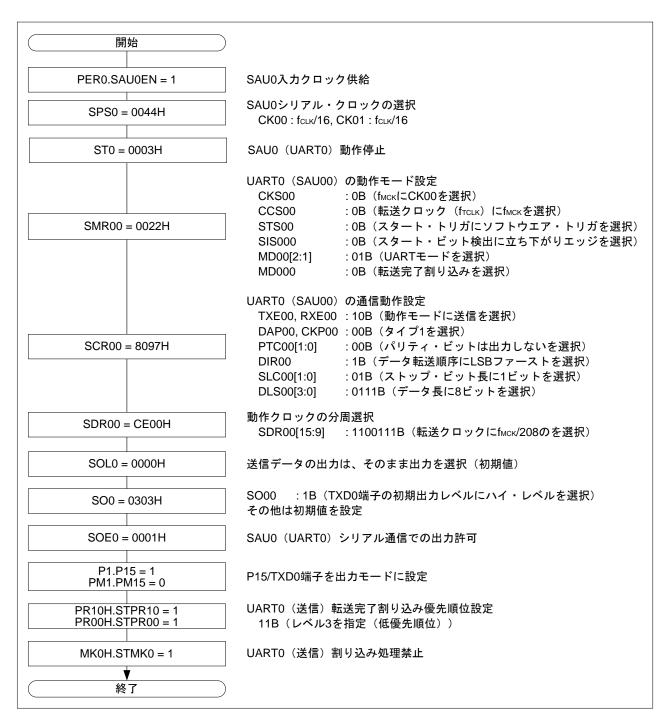

#### 3.5 SAU の初期化手順

SAU0 を UART モードで送信するための設定を行います。

図3-8にSAUの初期化手順を示します。

図3-8 SAU の初期化手順

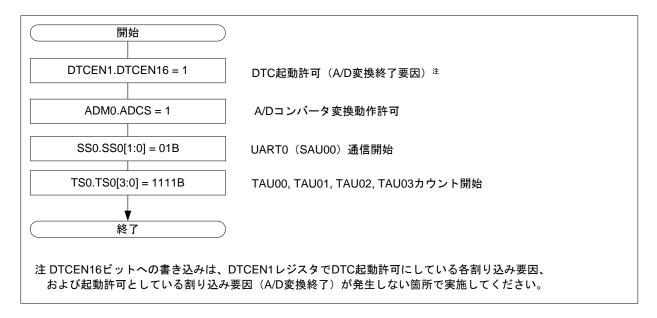

#### 3.6 周辺機能の動作許可(DTC(高速転送)転送開始)手順

周辺機能の初期化終了後、周辺機能(DTC、A/D コンバータ、TAU、SAU)の動作許可(開始)を行います。

図3-9に周辺機能の動作許可(DTC(高速転送)転送開始)手順を示します。

図3-9 周辺機能の動作許可(DTC(高速転送)転送開始)手順

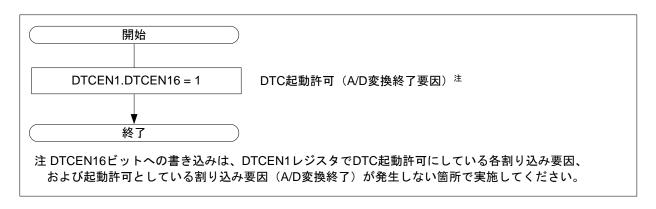

#### 3.7 DTC 転送完了割り込み処理

DTC 転送が終了すると対応する割り込み(本資料では A/D 変換終了割り込み)が発生します。 図3-10にDTC転送完了割り込み処理(A/D変換終了割り込み)を示します。DTC 転送を再度許可に設定します。

図3-10 DTC 転送完了割り込み処理(A/D 変換終了割り込み)

# 4. 注意事項

#### 4.1 DTC 転送サイクル数

転送サイクル数は、DTC (通常転送)では最速で8クロック、DTC (高速転送)では4クロック (最速)となります。本資料の使用例で示す仕様でDTCを使用した場合、1転送 (高速転送1回+チェイン転送による通常転送2回)につき20クロックになります。詳細は表4.1を参照してください。

表4.1 DTC 転送クロック数 (リピート・モード)

| 転送種別 | 転送元   | 転送先    | ベクタ コントロール |      | コントロール・データ |      | データ  | 合計 |

|------|-------|--------|------------|------|------------|------|------|----|

|      |       |        | 読み出し       | 読み出し | 書き戻し       | 読み出し | 書き込み |    |

| 高速転送 | ADCRH | RAM    |            | 1    | 1          | 1    | 1    | 4  |

| 通常転送 | RAM   | SDR00L | _          | 4    | 2          | 1    | 1    | 8  |

| 通常転送 | RAM   | TDR03  | _          | 4    | 2          | 1    | 1    | 8  |

備考:コントロール・データ書き戻しクロック数は表4.2および表4.3、データ読み出しクロック数は表4.4および表4.5、データ書き 込みクロック数は表4.6および表4.7を参照してください。また、本資料の設定は表4.2~表4.7の白抜き箇所となります。

ー:チェイン転送時は非該当

表4.2 DTC コントロール・データ書き戻し時に必要なクロック数

|       | DTCCRL | <b>,</b> ジスタ |      | アドレス固定/加算 |      | 書き戻すコントロール・データ領域のレジスタ |        |        |        | <b>夕</b> □ <b>夕</b> *b |

|-------|--------|--------------|------|-----------|------|-----------------------|--------|--------|--------|------------------------|

| DAMOD | SAMOD  | RPTSEL       | MODE | 転送元       | 転送先  | DTCCTj                | DTRLDj | DTSARj | DTDARj | クロック数                  |

| 0     | 0      | Х            | 0    | 固定        | 固定   | 書き戻す                  | 書き戻す   | -      | _      | 1                      |

| 0     | 1      | X            | 0    | 加算        | 固定   | 書き戻す                  | 書き戻す   | 書き戻す   | _      | 2                      |

| 1     | 0      | X            | 0    | 固定        | 加算   | 書き戻す                  | 書き戻す   | _      | 書き戻す   | 2                      |

| 1     | 1      | Х            | 0    | 加算        | 加算   | 書き戻す                  | 書き戻す   | 書き戻す   | 書き戻す   | 3                      |

| 0     | Х      | 1            | 1    | リピート      | 固定   | 書き戻す                  | 書き戻す   | 書き戻す   | _      | 2                      |

| 1     | Х      | 1            | 1    | リピート      | 加算   | 書き戻す                  | 書き戻す   | 書き戻す   | 書き戻す   | 3                      |

| Х     | 0      | 0            | 1    | 固定        | リピート | 書き戻す                  | 書き戻す   | _      | 書き戻す   | 2                      |

| Х     | 1      | 0            | 1    | 加算        | リピート | 書き戻す                  | 書き戻す   | 書き戻す   | 書き戻す   | 3                      |

備考 X:0または1、-:書き戻さない、j=0~23

表4.3 DTC (高速転送) コントロール・データ書き戻し時に必要なクロック数

|         | HDTCCRmレジスタ設定 |          |        | アドレス設定 |      | 書き戻すコントロール・レジスタ |         |         |         | クロック |

|---------|---------------|----------|--------|--------|------|-----------------|---------|---------|---------|------|

| HDAMODm | HSAMODm       | HRPTSELm | HMODEm | 転送元    | 転送先  | HDTCCTm         | HDTRLDm | HDTSARm | HDTDARm | 数    |

| 0       | 0             | Х        | 0      | 固定     | 固定   | 書き戻す            | _       | _       | _       | 1    |

| 0       | 1             | Х        | 0      | 加算     | 固定   | 書き戻す            | ı       | 書き戻す    | _       | 1    |

| 1       | 0             | X        | 0      | 固定     | 加算   | 書き戻す            | 1       | 1       | 書き戻す    | 1    |

| 1       | 1             | X        | 0      | 加算     | 加算   | 書き戻す            | ı       | 書き戻す    | 書き戻す    | 1    |

| 0       | Х             | 1        | 1      | リピート   | 固定   | 書き戻す            | ı       | 書き戻す    | _       | 1    |

| 1       | X             | 1        | 1      | リピート   | 加算   | 書き戻す            | 1       | 書き戻す    | 書き戻す    | 1    |

| Х       | 0             | 0        | 1      | 固定     | リピート | 書き戻す            |         |         | 書き戻す    | 1    |

| Х       | 1             | 0        | 1      | 加算     | リピート | 書き戻す            | _       | 書き戻す    | 書き戻す    | 1    |

備考 X:0または1、一:書き戻さない、m=0,1

#### 表4.4 DTC データ読み出しクロック数

| RAM   | フラッシ <i>=</i> | 1・メモリ     | SFR     |                 |                              |  |

|-------|---------------|-----------|---------|-----------------|------------------------------|--|

| KAIVI | コード・フラッシュ     | データ・フラッシュ | 1st SFR | 2nd SFR(ウェイトなし) | 2nd SFR(ウェイトあり) <sup>注</sup> |  |

| 1     | 2             | 4         | 1       | 1               | 1+ウェイト数                      |  |

注 CAN, LIN 関連レジスタおよびタイマ RJ の TRJO レジスタをアクセスする場合、ウェイト数(1 クロック )が必要になります。

# 表4.5 DTC (高速転送) データ読み出しクロック数

| RAM  | フラッシュ     | 1・メモリ     | SFR     |                 |                              |  |

|------|-----------|-----------|---------|-----------------|------------------------------|--|

| KAWI | コード・フラッシュ | データ・フラッシュ | 1st SFR | 2nd SFR(ウェイトなし) | 2nd SFR(ウェイトあり) <sup>注</sup> |  |

| -    | _         | _         | 1       | 1               | 1+ウェイト数                      |  |

注 CAN, LIN 関連レジスタおよびタイマ RJ の TRJO レジスタをアクセスする場合、ウェイト数: 1 クロックが必要になります。

# 表4.6 DTC データ書き込みクロック数

| RAM    | フラッシュ     | ュ・メモリ     | SFR     |                 |                              |  |

|--------|-----------|-----------|---------|-----------------|------------------------------|--|

| IVAIVI | コード・フラッシュ | データ・フラッシュ | 1st SFR | 2nd SFR(ウェイトなし) | 2nd SFR(ウェイトあり) <sup>注</sup> |  |

| 1      | -         |           |         | 1               | 1+ウェイト数                      |  |

注 CAN, LIN 関連レジスタおよびタイマ RJ の TRJO レジスタをアクセスする場合、ウェイト数(1 クロック )が必要になります。

#### 表4.7 DTC (高速転送) データ書き込みクロック数

| RAM   | フラッシ <i>=</i> | 1・メモリ     | SFR     |                 |                              |  |

|-------|---------------|-----------|---------|-----------------|------------------------------|--|

| KAIVI | コード・フラッシュ     | データ・フラッシュ | 1st SFR | 2nd SFR(ウェイトなし) | 2nd SFR(ウェイトあり) <sup>注</sup> |  |

| 1     | -             | -         | 1       | 1               | 1+ウェイト数                      |  |

注 CAN, LIN 関連レジスタおよびタイマ RJ の TRJO レジスタをアクセスする場合、ウェイト数: 1 クロックが必要になります。

#### 4.2 DTC 使用上の注意事項

- ・DTC 関連レジスタ(DTCBAR, SELHSm, HDTCCRm, HDTCCTm, HDTRLDm, HDTSARm, HDTDARm)、RAM 上に配置する DTC コントロール・データ領域、DTC ベクタ・テーブル領域、汎用レジスタ (FFEE0H-FFEFFH) の空間を DTC 転送でアクセスしないでください。また、セルフ・プログラミング、データ・フラッシュの各ライブラリ、オンチップ・トレース機能およびホット・プラグイン機能を使用される場合、各機能が使用するメモリ領域をアクセスしないでください。

- ・DTCENi レジスタの設定・変更は、対象のレジスタで DTC 起動許可としている各割り込み要因、および 起動許可として設定する割り込み要因が発生しない箇所で行ってください。

- ・汎用レジスタ (FFEE0H-FFEFFH) の空間、セルフ・プログラミング、データ・フラッシュの各ライブラリ、 オンチップ・トレース機能およびホット・プラグイン機能を使用される場合、各機能が使用するメモリ領 域は、DTC コントロール・データ領域および DTC ベクタ・テーブル領域に使用しないでください。

- ・DTC 関連レジスタ(DTCBAR, SELHSm, HDTCCRm, HDTCCTm, HDTRLDm, HDTSARm, HDTDARm)、DTC コントロール・データ領域に配置する各レジスタ(DTCCRj, DTBLSj, DTCCTj, DTRLDj, DTSARj, DTDARj) および DTC ベクタ・テーブル領域は、すべての DTC 起動要因を起動禁止(DTCENi レジスタの各ビットが 0(DTC 起動禁止))に設定した状態で変更してください。

- ・RAM 上に配置する DTC コントロール・データ領域および DTC ベクタ・テーブル領域は、初期設定(任意の値の書き込み)を実施してください。 DTC ベクタ・テーブル領域(64 バイト(予約領域含む))は、ユーザ・プログラムで汎用 RAM として使用しないでください。なお、DTC コントロール・データ領域(192 バイト)のうち、 DTC で使用しない領域は汎用 RAM として使用できます。

- ・DTCBAR を2回以上書き換えないでください。

- ・DTC 転送保留命令 (コール・リターン命令/無条件分岐命令/条件付分岐命令/コード・フラッシュ・メモリへのアクセス命令/割り込み関連レジスタ (IFxx, MKxx, PRxx) および PSW へのアクセス命令/データ・フラッシュへのアクセス命令/乗除積和算命令 (MULU 命令を除く)) 実行時、DTC は転送を行わず要求を保留します。また、PREFIX 命令コードと直後の1命令の間は DTC 転送を行いません。

- ・DTC のデータ転送が起きた1命令後にデータ・フラッシュアクセス命令が実行された場合、内部バスの 仕様により3クロック分のウェイトが発生します。

- ・ウェイトが必要な SFR (CAN, LIN の各レジスタおよびタイマ RJ の TRJ0 レジスタ) をアクセスした場合、DTC は転送を保留します。

- ・DTC 起動要因発生から DTC 転送が完了するまでに同一の起動要因を発生させないでください。

- ・DTC 起動要因が競合した場合は、起動要因の優先順位を判定し、優先順位が高い要因(要因番号により 決まります)を実行し、低い要因は保留します。

- ・高速転送時も DTC コントロール・データ領域および DTC ベクタ・テーブル領域の読み出しを行うため、 任意の値で初期設定してください。

- ・リピート・モード使用時は、リピート・エリアに設定するアドレス(設定値)の下位1バイトを00Hにしてください。また、転送回数、リロード転送回数は、転送データ・サイズにより異なります。

8 ビット転送時 01H~FFH(1 回~255 回)

16 ビット転送時 01H~7FH(1 回~127 回)

# ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

http://japan.renesas.com/

お問合せ先

http://japan.renesas.com/contact/

すべての商標および登録商標は、それぞれの所有者に帰属します。

# 改訂記録

|      |            | 改訂内容 |      |  |  |  |

|------|------------|------|------|--|--|--|

| Rev. | 発行日        | ページ  | ポイント |  |  |  |

| 1.00 | 2017.12.01 |      | 初版   |  |  |  |

# ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器・システムの設計におい て、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因して、お客様または第三 者に生じた損害に関し、当社は、一切その責任を負いません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報 の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 3. 本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権 に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許 苦するものではありません。

- 4. 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、

各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準・ コンピュータ OA機器 通信機器 計測機器 AV機器 家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、

防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生さ せるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。たとえ、意図しない用 途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。なお、ご不明点がある場合は、当社営業にお問い 合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製 品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 7 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合がありま す。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせ ないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証 を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に 関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。ま た、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外 国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負 担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数 を直接または間接に保有する会社をいいます。

- 注2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

ルネサスエレクトロニクス株式会社

■営業お問合せ窓口

http://www.renesas.com

※営業お問合せ窓口の住所は変更になることがあります。最新情報につきましては、弊社ホームページをご覧ください。

ルネサス エレクトロニクス株式会社 〒135-0061 東京都江東区豊洲3-2-24 (豊洲フォレシア)

■技術的なお問合せおよび資料のご請求は下記へどうぞ。 総合お問合せ窓口: https://www.renesas.com/contact/