# RENESAS

## Analog-to-Digital Converters

Operation of a SAR-ADC Based on Charge Redistribution

### Abstract

Analog-to-Digital Converters (ADCs) that convert the sampled input signal through Successive Approximation (SAR), are known as SAR-ADCs. While there are various methods of performing successive approximation, Renesas SAR-ADCs use a method known as capacitive charge redistribution.

This application note explains the functional principle of a SAR-ADC based on charge redistribution

### Contents

| 1. | Introduction        | 2 |

|----|---------------------|---|

| 2. | Sample Mode         | 2 |

| 3. | Hold Mode           | 3 |

| 4. | Redistribution Mode | 3 |

| 5. | Conversion Example  | 4 |

| 6. | Timing Diagram      | 6 |

| 7. | Revision History    | 7 |

|    |                     |   |

### **List of Figures**

| Figure 1.  | Simplified 5-Bit SAR-ADC Principle                                                                 | 2 |

|------------|----------------------------------------------------------------------------------------------------|---|

| Figure 2.  | Sample Mode                                                                                        | 2 |

| Figure 3.  | Hold Mode                                                                                          | 3 |

| Figure 4.  | Conversion Step 1 Determines the MSB (Bit 4)                                                       | 3 |

| Figure 5.  | Sample Mode: All Capacitors are Charged up to V <sub>IN</sub> = +3V                                | 4 |

| Figure 6.  | Hold Mode: All Capacitors are Charged up to $V_{IN}$ = +3V                                         | 4 |

| Figure 7.  | Bit-4 (MSB): Because $V_0$ = H, Bit 4 = 1. Therefore, $S_4$ Must Remain in its Current Position    | 5 |

| Figure 8.  | Bit-3: Because $V_0$ = L, Bit 3 = 0. Therefore, S <sub>3</sub> Must be Switched Back to GND        | 5 |

| Figure 9.  | Bit-2: Because $V_0 = L$ , Bit 2 = 0. Therefore, $S_2$ Must be Switched Back to GND                | 5 |

| Figure 10. | Bit 1: Because $V_0$ = H, Bit 1 = 1. Therefore, S <sub>1</sub> Must Remain in its Current Position | 6 |

| Figure 11. | Bit 0: Because $V_0$ = H, Bit 0 = 1. Therefore, S <sub>0</sub> Must Remain in its Current Position | 6 |

| Figure 12. | SAR Conversion Timing Diagram                                                                      | 6 |

|            |                                                                                                    |   |

### **Related Literature**

For a full list of related documents, visit our website:

• SAR A/D Converter page

### 1. Introduction

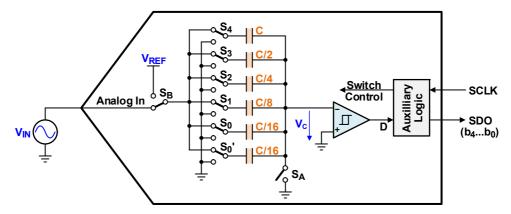

<u>Figure 1</u> shows the simplified, switched-capacitor structure of a 5-bit SAR-ADC. The capacitor values are binary weighted from C, C/2 ...C/16 or C/2<sup>n-1</sup>. The last two capacitors have the same value of C/2<sup>n-1</sup>. Only the first capacitor (connected to S<sub>0</sub>) is switched during the charge redistribution (the actual conversion). The other capacitor remains connected to ground.

MOS-transistors implement the required n+3 switches, and the voltage comparator provides the appropriate steering of these switches using auxiliary logic circuitry.

The conversion process is performed in three steps:

- Sample mode

- · Hold mode

- · Redistribution mode (the actual conversion)

Figure 1. Simplified 5-Bit SAR-ADC Principle

# 2. Sample Mode

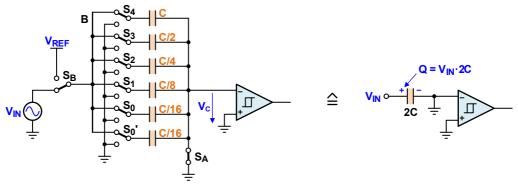

In the sampling mode (Figure 2), bus switch SB is switched to the input voltage,  $V_{IN}$ , and  $S_A$  is closed to ground. The capacitor switches,  $S_4...S_0$ ', are turned to the common bus B and all capacitors are charged to  $V_{IN}$ . The total charge of  $Q_{IN} = V_{IN} \cdot 2C$  is stored on the left plates of the capacitors.

Figure 2. Sample Mode

### 3. Hold Mode

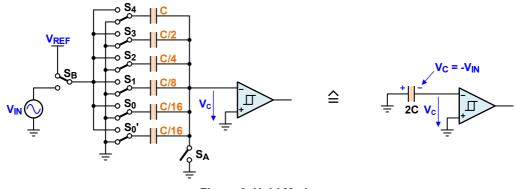

During the hold mode (Figure 3), switch  $S_A$  is open while the switches  $S_4...S_0$ ' are connected to ground, thereby making the voltage at the inverting comparator input  $V_C = -V_{IN}$ . This means that the switched-cap circuit already has a built-in sample-and-hold function.

#### Figure 3. Hold Mode

### 4. Redistribution Mode

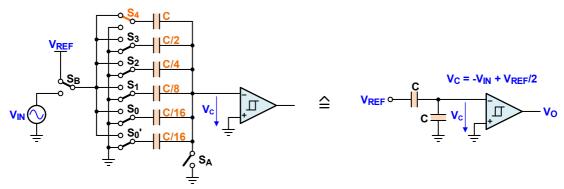

The actual conversion is performed by charge redistribution. The first conversion step, shown in Figure 4, connects C (the largest capacitor) using  $S_4$  to the reference voltage  $V_{REF}$ , which corresponds to the Full-Scale Range (FSR) of the ADC.

Figure 4. Conversion Step 1 Determines the MSB (Bit 4)

Capacitor C forms a 1:1 capacitance divider with the remaining capacitors connected to ground. The comparator input voltage becomes  $V_C = -V_{IN} + V_{REF}/2$ . This voltage is compared with the voltage potential of 0V at the non-inverting input. Therefore, if  $|V_{IN}| > V_{REF}/2$ ,  $V_C < 0$ , and the comparator output  $V_O$  goes high, setting the Most Significant Bit (MSB) (Bit 4) = 1. However, if  $|V_{IN}| < V_{REF}/2$ ,  $V_C > 0$ ,  $V_O$  remains low, and Bit 4 = 0. If  $V_O$  = high,  $S_4$  remains connected to  $V_{REF}$  for the rest of the conversion. If  $V_O$  = low,  $S_4$  is switched back to GND.

This procedure is repeated for switches, S3 to S0, except S0', which remains connected to GND for the entire conversion.

Summarizing, the conversion or charge redistribution procedure can be expressed by two equations:

(EQ. 1) If  $-V_{IN} + V_{REF} \cdot X > 0 \implies V_O = \text{High} [1] \implies \text{maintain switch position}$

(EQ. 2) If  $-V_{IN} + V_{REF} \cdot X < 0 \implies V_O = Low[0] \implies \text{connect switch back to GND}$

with X as the ratio of the capacitive voltage divider because of a given switch position.

Therefore, the comparator input voltage of the final conversion step is:

$$(\textbf{EQ. 3}) \qquad V_{C} = -V_{IN} + bit \ 4 \cdot \frac{V_{REF}}{2} + bit \ 3 \cdot \frac{V_{REF}}{4} + bit \ 2 \cdot \frac{V_{REF}}{8} + bit \ 1 \cdot \frac{V_{REF}}{16} + bit \ 0 \cdot \frac{V_{REF}}{32}$$

### 5. Conversion Example

The following example shows the conversion process of a 5-bit SAR-ADC for  $V_{IN}$  = 3V and  $V_{REF}$  = 5V. According to Equation 3, the comparator input voltage of the final conversion step must be:

(EQ. 4)  $V_{C} = -3V + [1] \cdot 2.5V + [0] \cdot 1.25V + [0] \cdot 0.625V + [1] \cdot 0.3125V + [1] \cdot 0.15625V = -0.03125V$

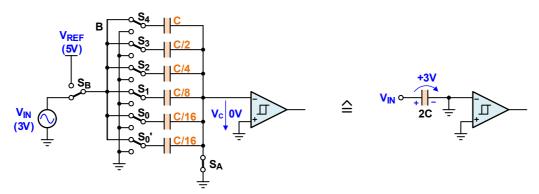

**Sample Mode:** All capacitors are connected to voltage bus B using S<sub>4</sub> to S<sub>0</sub>' and to ground using S<sub>A</sub>. Bus B is connected to V<sub>IN</sub>. All capacitors are charged up to V<sub>IN</sub> = 3V (<u>Figure 5</u>).

Figure 5. Sample Mode: All Capacitors are Charged up to V<sub>IN</sub> = +3V

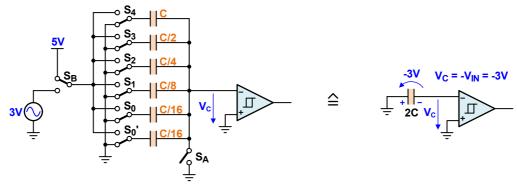

**Hold Mode:** The left side of the capacitors is connected to ground using S<sub>4</sub> to S<sub>0</sub>'. The common (right) side of the capacitors is disconnected from ground using S<sub>A</sub>, therefore, creating a comparator input voltage of  $-V_{IN} = -3V$  (Figure 6).

Figure 6. Hold Mode: All Capacitors are Charged up to V<sub>IN</sub> = +3V

**Redistribution Mode:** The actual conversion starts by connecting  $S_B$  to  $V_{REF}$  = 5V.

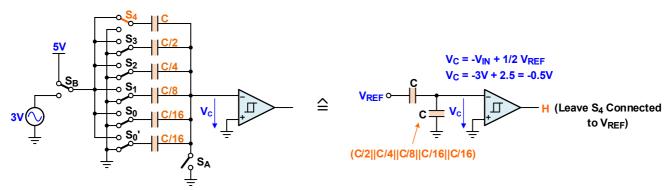

**Bit 4 (MSB):** The first conversion step determines the most significant bit (MSB = Bit 4) connecting C to  $V_{REF}$  using S<sub>4</sub>. The ratio of the capacitive voltage divider becomes X = 1/2 and creates a comparator input voltage of  $V_C$  = -0.5V. This turns the comparator output high and sets Bit 4 to 1. It also means that S<sub>4</sub> must remain in the present position for the rest of the conversion process (Figure 7).

RENESAS

Figure 7. Bit-4 (MSB): Because V<sub>O</sub> = H, Bit 4 = 1. Therefore, S<sub>4</sub> Must Remain in its Current Position

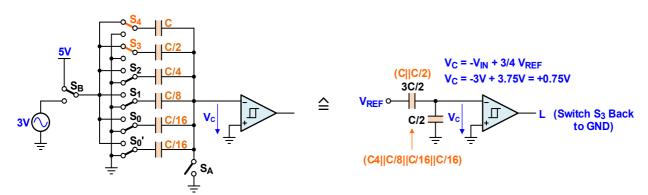

**Bit 3:** The second conversion step determines Bit 3 by connecting C/2 to  $V_{REF}$  using S<sub>3</sub>. The divider ratio changes to X =  ${}^{3}/_{4}$ , causing a comparator input of V<sub>C</sub> = +0.75V. This turns the comparator output low and sets Bit 3 to 0. It also means that S<sub>3</sub> must be switched back to ground (<u>Figure 8</u>).

Figure 8. Bit-3: Because  $V_0 = L$ , Bit 3 = 0. Therefore, S<sub>3</sub> Must be Switched Back to GND

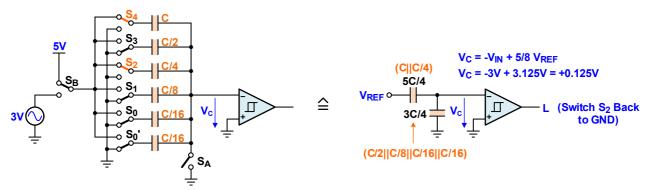

**Bit 2:** The third conversion step determines Bit 2 by connecting C/4 to  $V_{REF}$  using S<sub>2</sub>. The divider ratio changes to X =  ${}^{5}\!/_{8}$ , causing a comparator input of V<sub>C</sub> = +0.125V. This turns the comparator output low and sets Bit 2 to 0. It also means that S<sub>2</sub> must be switched back to ground (<u>Figure 9</u>).

Figure 9. Bit-2: Because  $V_0 = L$ , Bit 2 = 0. Therefore,  $S_2$  Must be Switched Back to GND

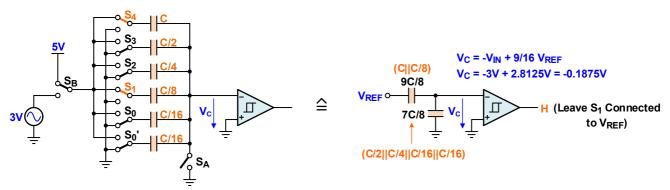

**Bit 1:** The fourth conversion step determines Bit 1 by connecting C/8 to  $V_{REF}$  using S<sub>1</sub>. The divider ratio changes to X =  ${}^{9}/_{16}$ , causing a comparator input of V<sub>C</sub> = -0.1875V. This turns the comparator output high and sets Bit 1 to 1. It also means that S<sub>1</sub> must remain in the present position for the rest of the conversion process (Figure 10).

Figure 10. Bit 1: Because  $V_0$  = H, Bit 1 = 1. Therefore, S<sub>1</sub> Must Remain in its Current Position

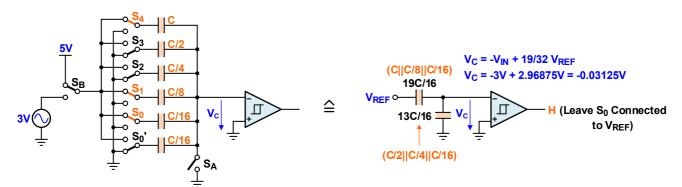

**Bit 0:** The fifth conversion step determines Bit 0 by connecting C/16 to  $V_{REF}$  using S<sub>0</sub>. The divider ratio changes to X = <sup>19</sup>/<sub>32</sub>, causing a comparator input of V<sub>C</sub> = -0.03125V. This turns the comparator output high and sets Bit 0 to 1. It also means that S<sub>0</sub> must remain in the present position (<u>Figure 11</u>).

Figure 11. Bit 0: Because V<sub>O</sub> = H, Bit 0 = 1. Therefore, S<sub>0</sub> Must Remain in its Current Position

# 6. Timing Diagram

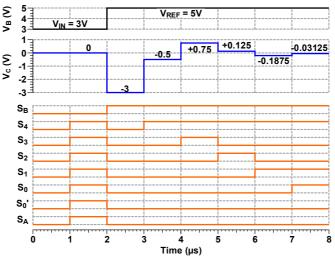

<u>Figure 12</u> shows the timing diagrams for the bus voltage ( $V_B$ ) the comparator input voltage ( $V_C$ ) the On/Off status of all switches (1 = On), and the individual capacitor voltages,  $V_{C1}$  to  $V_{C16}$ '.

Figure 12. SAR Conversion Timing Diagram

# 7. Revision History

| Rev. | Date      | Description     |

|------|-----------|-----------------|

| 1.00 | Sep.17.20 | Initial release |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/