## RX230/RX231 Group, RX630 Group

## Points of Difference Between RX231 Group and RX630 Group

## Summary

This application note is intended principally as a reference providing an overview of the peripheral functions of the RX231 Group and RX630 Group, to enable checking of the points of difference between the I/O registers and pin functions of the two groups, and to allow confirmation of key points related to migration.

Unless specifically otherwise noted, the information in this application note applies to the 100-pin LQFP package version B of the RX231 Group and the 100-pin LQFP package version of the RX630 Group. To confirm details of differences in the specifications of the electrical characteristics, usage notes, and setting procedures, refer to the user's manuals of the products in question.

## **Target Devices**

RX231 Group and RX630 Group

## Contents

| 1.   | Comparison of Functions of RX231 Group and RX630 Group | 4   |

|------|--------------------------------------------------------|-----|

| 2.   | Comparative Overview of Functions                      | 6   |

| 2.1  | CPU                                                    | 6   |

| 2.2  | Operating Modes                                        | 7   |

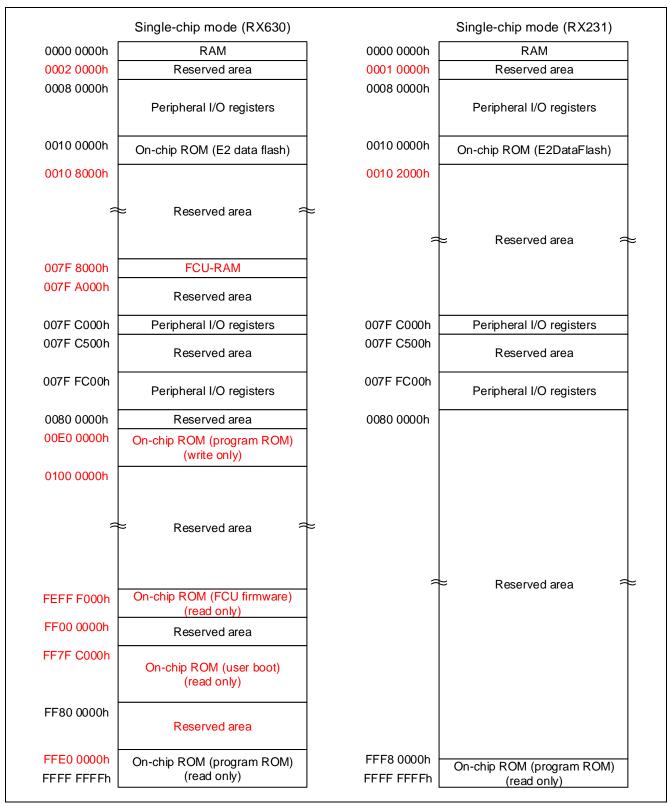

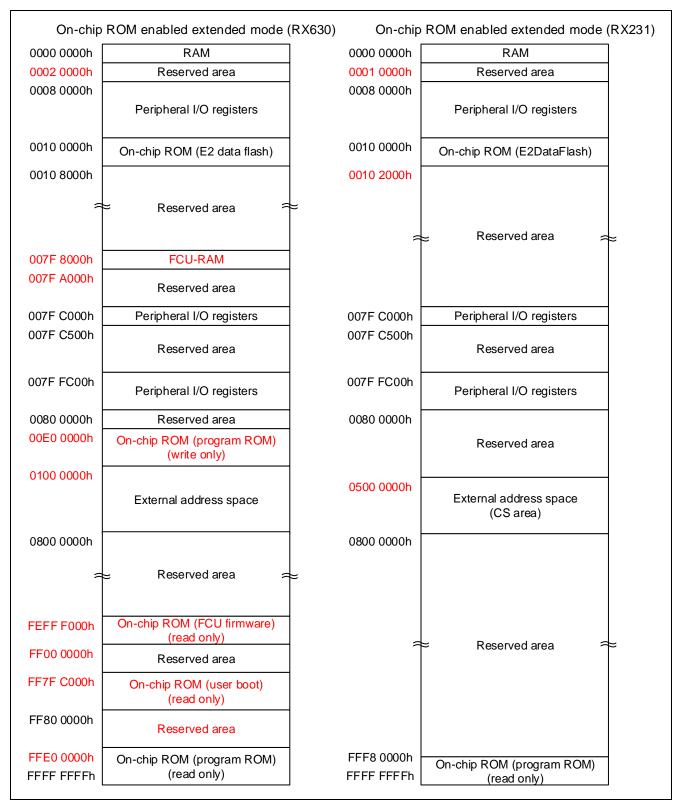

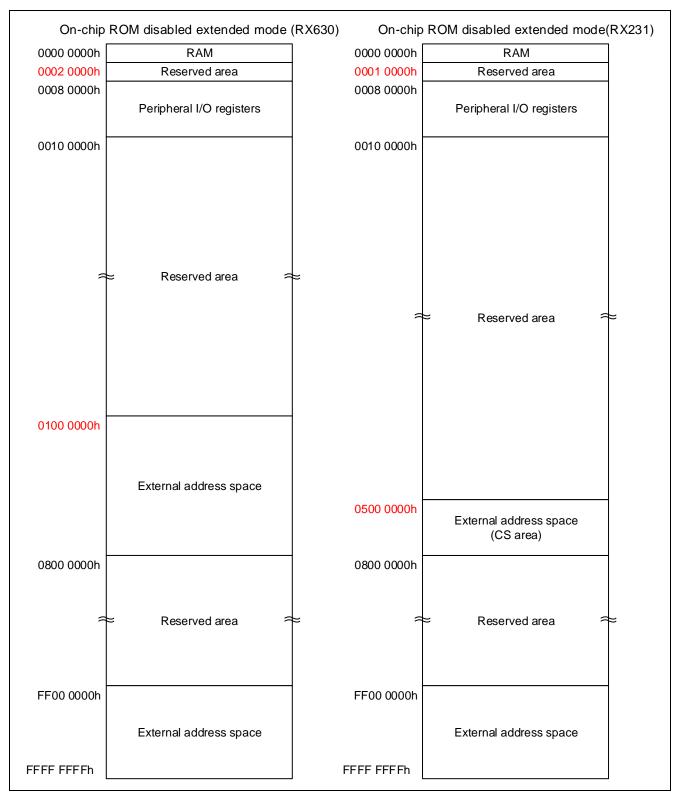

| 2.3  | Address Space                                          | 8   |

| 2.4  | Resets                                                 | 11  |

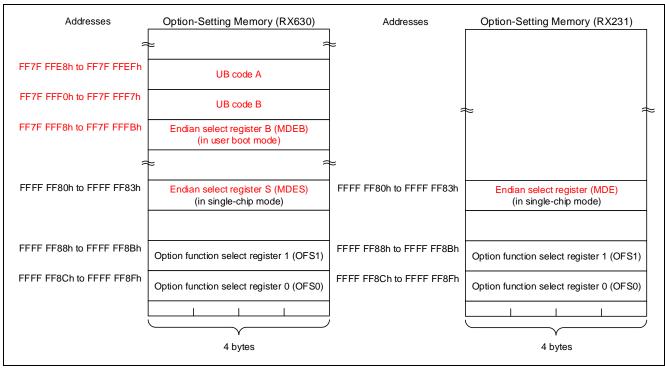

| 2.5  | Option-Setting Memory                                  | 12  |

| 2.6  | Voltage Detection Circuit                              | 14  |

| 2.7  | Clock Generation Circuit                               |     |

| 2.8  | Low Power Consumption Functions                        | 23  |

| 2.9  | Battery Backup Function                                |     |

| 2.10 | Register Write Protection Function                     |     |

| 2.11 | Exception Handling                                     | 34  |

| 2.12 | Interrupt Controller                                   | 35  |

| 2.13 | Buses                                                  |     |

| 2.14 | Memory Protection Unit                                 |     |

| 2.15 | DMA Controller                                         |     |

| 2.16 | Data Transfer Controller                               |     |

| 2.17 | I/O Ports                                              |     |

| 2.18 | Multi-Function Pin Controller                          |     |

| 2.19 | Multi-Function Timer Pulse Unit 2                      | 68  |

| 2.20 | Port Output Enable 2                                   |     |

| 2.21 | 16-Bit Timer Pulse Unit                                | 70  |

| 2.22 | 8-Bit Timer                                            | 71  |

| 2.23 | Compare Match Timer                                    | 72  |

| 2.24 | Realtime Clock                                         | 73  |

| 2.25 | Independent Watchdog Timer                             | 76  |

| 2.26 | USB 2.0 Function Module                                | 79  |

| 2.27 | Serial Communication Interface                         |     |

| 2.28 | I <sup>2</sup> C Bus Interface                         | 91  |

| 2.29 | CAN Module                                             | 94  |

| 2.30 | Serial Peripheral Interface                            |     |

| 2.31 | 12-Bit A/D Converter                                   |     |

| 2.32 | D/A Converter                                          | 110 |

| 2.33 | •                                                      |     |

| 2.34 |                                                        |     |

| 2.35 | Flash Memory (ROM)                                     | 113 |

| 2.36 | Flash memory (E2 DataFlash)                            |     |

| 2.37  | Package (LQFP100 only)                                             |  |

|-------|--------------------------------------------------------------------|--|

| 3.    | Comparison of Pin Functions                                        |  |

| 3.1   | 100-Pin LQFP Package                                               |  |

| 4.    | Notes on Migration                                                 |  |

| 4.1   | Operating Voltage Range                                            |  |

| 4.1.1 | Power Supply Voltage                                               |  |

| 4.1.2 | Analog Power Supply Voltage                                        |  |

| 4.2   | Notes on the Pin Design                                            |  |

| 4.2.1 | Power Supply Pins and Operating Frequency                          |  |

| 4.2.2 | Main Clock Oscillator                                              |  |

| 4.2.3 | VCL Pin (External Capacity)                                        |  |

| 4.2.4 | Mode Setting Pins                                                  |  |

| 4.2.5 | General I/O Ports                                                  |  |

| 4.2.6 | Analog Input Pins for A/D Converter                                |  |

| 4.2.7 | Integrated Pull-Up and Pull Down Resistors for USB DP and DM Pins. |  |

| 4.2.8 | Inputting an External Clock                                        |  |

| 4.3   | Notes on the Function Settings                                     |  |

| 4.3.1 | UB Code                                                            |  |

| 4.3.2 | Battery Backup Function                                            |  |

| 4.3.3 | 12-Bit A/D Converter                                               |  |

| 4.3.4 | 12-Bit D/A Converter                                               |  |

| 4.3.5 | Memory Wait Cycle                                                  |  |

| 4.3.6 | Transferring Firmware Contents to FCU RAM                          |  |

| 4.3.7 | Using Commands to Program Flash Memory                             |  |

| 4.3.8 | Supplemental Information on RAM Self-Diagnostics                   |  |

| 5.    | Reference Documents                                                |  |

## 1. Comparison of Functions of RX231 Group and RX630 Group

A comparison of the functions of the RX231 Group and RX630 Group is provided below. For details of the functions, see 2, Comparative Overview of Functions, and 5, Reference Documents.

Table 1.1 is a comparative listing of the functions of the RX231 and RX630.

#### Table 1.1 Comparison of Functions of RX231 and RX630

| Function                                                     | RX630                                                                                   | RX231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                                                          | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Operating mode                                               | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Address Space                                                | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Resets                                                       | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Option-setting memory                                        | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Voltage detection circuit (LVDA): RX630, (LVDAb): RX231      | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Clock generation circuit                                     | $\bigtriangleup$                                                                        | $\triangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Frequency measurement circuit (MCK)                          | 0                                                                                       | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Clock frequency accuracy measurement circuit (CAC)           | ×                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Low power consumption function                               | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Battery backup function                                      | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Register write protection function                           | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Exception handling                                           | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interrupt controller (ICUb)                                  | $\bigtriangleup$                                                                        | $\bigtriangleup$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Buses                                                        | [] U00<br>100<br>100<br>100<br>100<br>100                                               | () 10.00<br>() |

| Memory-protection unit (MPU)                                 | 0                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DMA controller (DMACA)                                       | [1] (20)<br>) - 21<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1 | 7-82<br>7-82<br>7-82<br>7-92<br>8-92<br>8-92<br>8-92<br>8-92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Data transfer controller (DTCa)                              | [1] (1)(2)<br>) - 1)<br>(1)(1)<br>(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(              | 5-00<br>7-004<br>2-017<br>8419<br>8419                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Event link controller (ELC)                                  | X                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O ports                                                    | [1] (20)<br>) - 11<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(  | 5-00<br>7-00<br>2-00<br>840                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multi-function pin controller (MPC)                          | [1] (20)<br>) - 11<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(  | 5-00<br>7-00<br>2-00<br>840                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Multi-function timer pulse unit 2 (MTU2a)                    | [7 12/3<br>30/4<br>487                                                                  | 5-03<br>721-1<br>3-17<br>8-17<br>8-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port output enable 2 (POE2a)                                 | [1] (20)<br>) - 11<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(  | 5-00<br>7-00<br>8-01<br>8-01<br>8-01<br>8-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16-bit timer pulse unit (TPUa)                               | [7 10/8<br>30/0<br>487                                                                  | 5-03<br>12-1<br>3-17<br>8-11<br>1-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |