# A New PSPICE Subcircuit for the Power MOSFET Featuring Global Temperature Options

AN9210 Rev.1.00 Oct 1, 1999

# Abstract

An empirical sub-circuit was implemented in PSPICE® and is presented. It accurately portrays the vertical DMOS power MOSFET electrical and, for the first time, thermal responses. Excellent agreement is demonstrated between measured and modeled responses including first and third quadrant MOSFET and gate charge behavior, body diode effects, breakdown voltage at high and low currents, gate equivalent series resistance, and package inductances for temperatures between -55°C and 175°C. Parameter extraction is relatively straightforward as described.

# Introduction

Circuit simulation commonly uses one of the SPICE [1] programs. However, power circuits require proper models for unique devices which are not included in the supplied libraries. Efforts have been published to model the power MOSFET [2-10] with varying degrees of success. The more successful papers have used sub-circuit representation. To date, a thermal model has not been offered.

# **Objective**

It is the goal of this effort to provide for the first time a thermal sub-circuit model capable of providing accurate simulation throughout all of the power MOSFET regimes. In addition, the sub-circuit should be readily understood and accepted by users, and the ease of parameter extraction should be demonstrated.

## Method

A sub-circuit approach is employed which is empirical. It is developed to provide black box conformity to the power MOSFET throughout the operating regime normally traversed by the dictates of most power circuit applications, including junction temperature. Although device thermal behavior is the driving force, respect is maintained toward the physics and the SPICE algorithms.

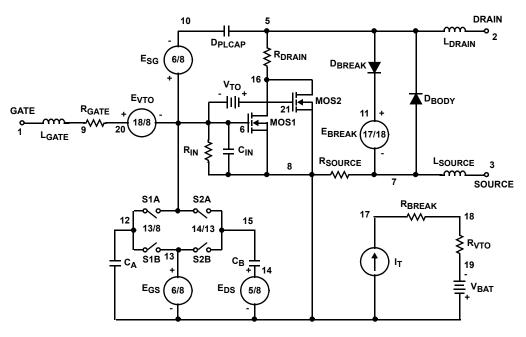

The developed sub-circuit schematic is shown in Figure 1.

There are many forms of SPICE, each with its own strengths and weaknesses. PSPICE was chosen for the following reasons.

- 1. An evaluation copy capable of considerable circuit analysis for power circuits is available.

- 2. The PROBE feature provides excellent displays.

- 3. Programmed time slice defaults and DC convergence routines make it very friendly.

- 4. The switch algorithm of PSPICE provides a very smooth transition from off to on.

Other forms of SPICE were not investigated, but they should be amenable to the development of a similar sub-circuit by paralleling the teachings of this work.

FIGURE 1. PSPICE MODEL SUBCIRCUIT

Driving constraints for this work were:

- 5. The SPICE device equations should not be modified.

- 6. Global temperature should be included.

- 7. All modes and levels of power MOSFET operation should be modeled.

- 8. The sub-circuit should be empirically developed to complement the device physics and the source code algorithms.

- 9. The sub-circuit should be acceptable to a circuit design user.

- 10. Parameter extraction should require little or no iteration.

# Temperature Modeling

Use is made of voltage controlled voltage sources and model statements in order to form master/slave circuit relationships. In this manner, resistors can often be used to establish a first and second order temperature correction where direct PSpice algorithms will not permit thermal modeling.

# An Overview (Figure 1)

The primary device for gate controlled positive or negative current flow is provided by Mos1 which is defined by the level 1 model MOSMOD. The second order effect of threshold voltage is set by Mos2 combined with the voltage  $V_{TO}$ . Model MOSMOD also defines Mos2 but with a 1 percent scaling.

It is necessary that  $R_{SOURCE}$  and  $R_{DRAIN}$  be provided as separate resistors, rather than being included with the MOSFETs. In this manner, 1st and 2nd order temperature effects may be added as described by model RDSMOD.

The thermal variation of KP as provided by the source code is a satisfactory representation. However, the threshold voltage of Mos1 must be modified by the voltage dependent voltage source  $E_{VTO}$ .  $E_{VTO}$  provides an additive or subtractive voltage in series with the gate as a function of temperature. It is equal to the sum of V<sub>BAT</sub> and the product of It and R<sub>VTO</sub>. Temperature variation is provided by model RVTOMOD.

Avalanche breakdown of the MOSFET is provided by the clamp circuit of  $D_{BREAK}$  in series with  $E_{BREAK}$ . The value of  $E_{BREAK}$  is provided by the multiplier of  $E_{BREAK}$  and the product of It times  $R_{BREAK}$ . Temperature variation is provided by model RBKMOD. High current voltage drops are provided by RS of the model DBKMOD including thermal sensitivity.

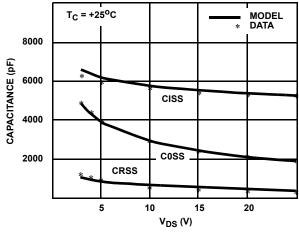

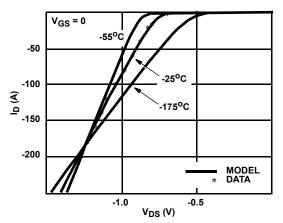

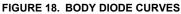

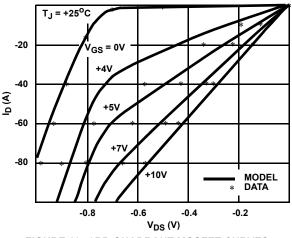

The power MOSFET being modeled contains a third quadrant diode as a fabrication consequence, and it is represented by  $D_{BODY}$ . Model DBDMOD provides the leakage current IS, the transit time for stored charge effects TT, the body diode series resistance RS, temperature dependence of this resistor TRS1 and TRS2, and the MOSFET output capacitance CJO.

The inductances associated with the device terminals are represented by  $L_{SOURCE},\,L_{GATE},$  and  $L_{DRAIN}.$

The effective series resistance associated with the gate is modeled by the resistor  $\mathsf{R}_{GATE}.$

A gate to source input capacitance is represented by  $C_{IN}$ . MOSFET output capacitance is provided by model DBDMOD as described above. Feedback capacitance is provided by  $\mathsf{D}_{\mathsf{PLCAP}}$  as defined by model DPLCAPMOD. A diode was used for this function to provide a square root dependency with drain to source voltage. The voltage dependent voltage generator  $\mathsf{E}_{SG}$  is added to assure that the drain to source voltage is imposed across the feedback capacitor while forcing the feedback current flow into the gate node. It is further necessary that the ideality factor N of model DPLCAPMOD be made large to exclude forward diode conduction during third quadrant operation of the MOSFET.

A capacitor  $C_A$  is switched in parallel with  $C_{IN}$  when the gate to source voltage becomes sufficiently negative. This switching is implemented by the switch S1A. Model S1AMOD defines the switch closed resistance, open resistance, and the gate to source voltages through which the fully on to fully off transition occurs. During this transition, switch S1B also transitions from fully off to fully on. Switch S1B is defined by model S1BMOD. Voltage controlled voltage generator  $E_{GS}$  provides the proper charge state for  $C_A$  when switch S1A is open.

In a similar manner, the capacitor  $C_B$  is switched in parallel with  $C_{\rm IN}$  when the drain to gate voltage becomes negative. Switch S2A is defined by model S2AMOD for the on resistance, off resistance, and drain to gate voltage transition range. During this transition, switch S2B also transitions as defined by model S2BMOD. Voltage controlled voltage generators  $E_{DS}$  and  $E_{GS}$  provide the proper charge state for  $C_B$  when switch S2A is open.

In order to facilitate DC convergence, PSPICE provides a minimum conductance between all nodes as defined by the PSPICE analysis options. In order to assure that a floating gate initial condition will not exist should a modeler drive from a current source, a very large gate to source resistor  $R_{IN}$  is added. Inclusion of  $R_{IN}$  is recommended but not required.

All sub-circuit elements are treated as being independent of temperature if they are not otherwise defined.

Gate propagation effects [15], radiation effects, and inherent VDMOS design deficiencies are not modeled. This is discussed later.

All discussions apply equally to the P channel, although the N channel is discussed exclusively.

# Applications

The sub-circuit combined with external circuitry may be analyzed for responses. Three circuits are modeled to demonstrate the capability of the PSPICE sub-circuit model. A synchronous rectifier producing 100W at 5VDC from a 100KHz square wave demonstrates the ability to handle the first and third quadrant regimes of two MOSFETs, including conversion efficiency versus temperature. Calculated waveforms are presented, but they are unsupported by measured data. The diode recovery waveform is modeled and compared to the measured response. Switching waveforms of the power MOSFET are also modeled and are compared to the measured results.

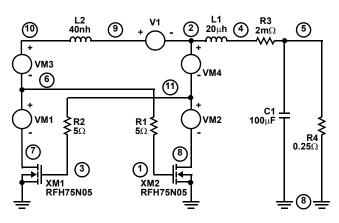

#### SYNCHRONOUS RECTIFIER

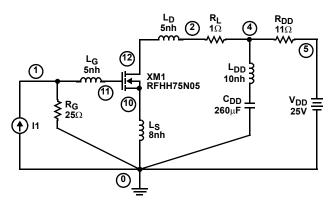

The schematic of a synchronous rectifier circuit is shown in Figure 2. The rectifier power MOSFETs are a pair of

cross coupled RFH75N05 megaFET devices. Conduction is offered by a forward gate bias with negative drain current (third quadrant mosfet operation) and voltage blocking is assured by a slightly negative gate bias for first quadrant MOSFET operation.

FIGURE 2. SYNCHRONOUS RECTIFIER CIRCUIT

VM1 to VM4 are voltage sources of zero potential and are used to permit a recording of branch currents. The transformer secondary normally used in a supply of this sort is represented by voltage source V1 and leakage inductance L2. Filter inductor L1 and capacitor C1 provide energy storage and smoothing for the 100KHz square wave of V1. Rise and fall times of the square wave are not critical, but were set at 40ns. Gate coupling resistors R1 and R2 are somewhat critical, in that too high a value will restrict the conduction transition time of the MOSFET. Alternatively, a value too low will permit a high voltage drain spike to appear on the gate of the MOSFET.

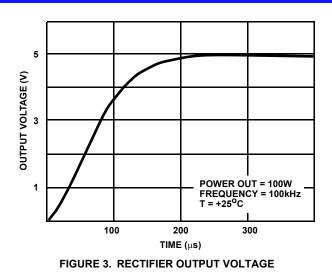

The calculated output voltage turn on transient is shown in Figure 3. Of course this represents a feed forward circuit response only. In practice, the modeled drive circuit with pulse width modulation and feedback would provide a much faster response which would be slew rate limited. The ripple voltage is 5mV RMS.

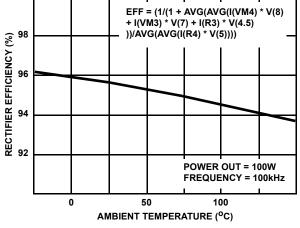

The efficiency for this portion of the synchronous rectifier circuit is plotted in Figure 4 as a function of temperature from  $-25^{\circ}$ C to  $150^{\circ}$ C. As a convenience, the equation used by PROBE (PSPICE's waveform plotter routine) is included. This equation yields a solution rapidly.

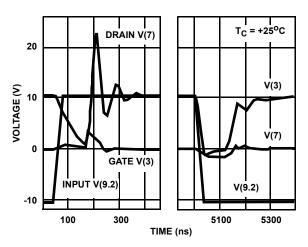

Transition voltage waveforms of the input voltage, one drain voltage, and one gate voltage are plotted in Figure 5. The value of drain voltage during third quadrant conduction is approximately -0.2 volts. Other waveforms are readily available by use of the PSPICE system.

FIGURE 5. TRANSITION VOLTAGE WAVEFORMS

#### **RECOVERY WAVEFORMS**

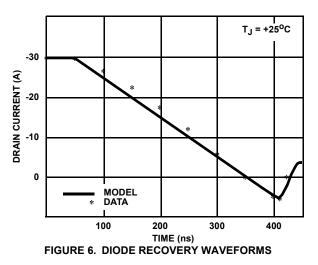

Figure 6 shows the MOSFET current of the parasitic 3rd quadrant diode vs time as modeled with the sub-circuit and as measured using the Berman SM30 equipment. Measurements show very little temperature sensitivity. Therefore it is not modeled.

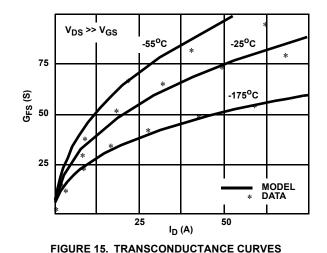

#### SWITCHING WAVEFORMS

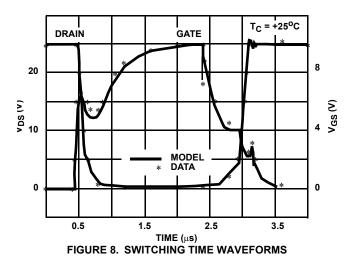

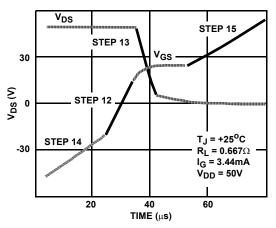

Switching time measurements of the power MOSFET are usually taken in a circuit similar to that of Figure 7. Although parasitic wiring inductance is not normally shown, it exists and is modeled as shown. The waveforms of gate and drain voltages are presented as measured and modeled in Figure 8. Switching times of Figure 8 are listed in Table 1.

| TABLE 1. SWIT | CHING | TIME DATA |

|---------------|-------|-----------|

|---------------|-------|-----------|

| PARAMETER           | DATA | MODEL | UNITS |

|---------------------|------|-------|-------|

| Turn on Delay Time  | 72   | 67    | ns    |

| Rise time           | 238  | 208   | ns    |

| Turn Off Delay Time | 440  | 460   | ns    |

| Fall Time           | 259  | 240   | ns    |

FIGURE 7. SWITCHING TIME CIRCUIT

## Measured vs Modelled Characteristics

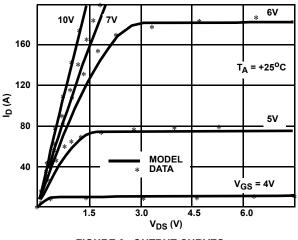

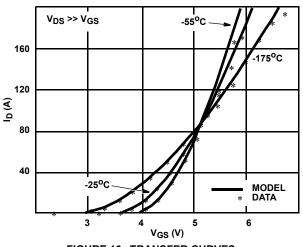

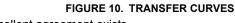

The device characteristics have been measured (data points) and modeled (solid line) as plotted in Figures 9 to 19. Thermal responses were omitted from some figures to improve the clarity of presentation.

## **Discussion Of Results**

Excellent correlation generally exists between measured and modeled information over the current range from zero to three times the device rated current. As the drain voltage is increased from zero volts with a constant gate voltage, the MOSFET transitions from the linear mode to the saturated mode. Conformance of modeled to actual data is very good in the constant current regime (saturated mode). A forcing of conformance exists for the very high gate voltages in the linear mode, with departure existing for the linear mode with lesser values of constant gate voltages.

The actual drain voltage in the linear mode is seen to be as much as 20 percent below the modeled value in worst cases. This represents a conservative error for circuit calculations in that the conduction loss is somewhat less than modeled. In addition, the gate drive is usually high under MOSFET conduction, thereby avoiding operation in the regions of discussion.

**FIGURE 9. OUTPUT CURVES**

The discrepancy results because the PSPICE algorithm for a mosfet assumes the channel surface concentration to be constant. In the power MOSFET, the surface concentration is Gaussian along the channel length. Hence, the observed behavior is as would be expected.

The modeled response can be improved by changing the PSPICE algorithm, however changes of this type were ruled out for this work.

Excellent agreement exists.

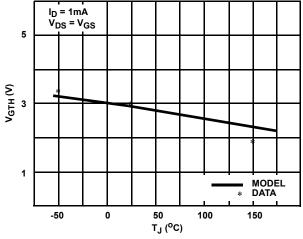

FIGURE 11. THRESHOLD VOLTS

Excellent agreement exists. This would not be so without the inclusion of Mos2 to represent the sharp corners of the many hexagonal cells of the structure. The flat part of the hex cells results in a two dimensional diffusion during processing and the establishment of a source to body junction cross-over concentration at the surface, resulting in Mos1 as modeled. However, the corners of the hex cells introduce a three dimensional diffusion resulting in a lower source to body junction cross-over concentration at the surface. The unpublished work of Klodzinski, et al [11] processed test and control devices upon a common wafer where the corners of the hex source implant were excluded versus included, revealing threshold voltages approximately 0.4 volts higher for the test.

Omission of Mos2 would not impact circuit performance,

however a reverence of attached importance to the MOSFET threshold voltage mandates modelled to measured agreement.

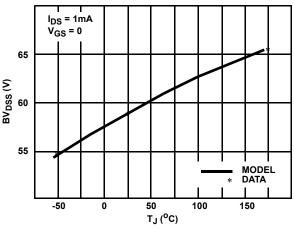

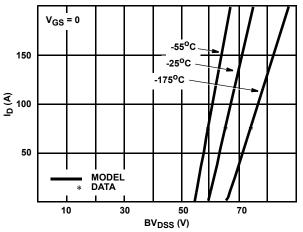

FIGURE 12. BREAKDOWN VOLTAGE, LOW CURRENT BV<sub>DSS</sub> Excellent agreement exists.

Excellent agreement exists.

FIGURE 16. GATE CHARGE CURVES

Excellent agreement exists. The non linear behavior of gate charge for negative gate bias is seldom shown. A significant increase in turn on delay results by operating from a negative gate voltage.

FIGURE 17. CAPACITANCE CURVES Excellent agreement exists.

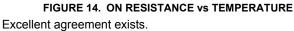

All three measured data curves were noted to cross at a drain current of 180amps. Excellent agreement exists.

Good agreement exists. The departure seen between modelled and measured exists for the same reason as the departure of the output curves in the linear regime. This would also be improved by changing the PSpice algorithm as suggested relative to Figure 9.

## Parameter Extraction

The sub-circuit is chosen to minimize interdependencies between parameters. A listing of the sub-circuit is presented in Table 2 as a template which routes the Modeler through extraction with guiding comments. Although the template is a complete and workable PSPICE sub-circuit listing, all parameter values except KP and VTO are chosen to be transparent to the results of the analysis. As the transparent values are replaced with extracted values, the model is developed. The listing in Table 2 is structured so that parameters being extracted have very little dependency upon those values which are not yet determined. If desired after completing the extraction, an iteration may be made for the comfort of the Modeler.

## EXTRACTION OF MODEL PARAMETERS FROM PHYSICAL MEASUREMENTS

| TABEL 2. TEMPLATE                                                                                                                                                                                                           |         | TABLE 3. FINAL MODEL                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .SUBCKT TEMPLATE 2 1 3;rev 12/17/90<br>*Nom Temp=25 deg C                                                                                                                                                                   |         | .SUBCKT RFH75N05 2 1 3 ; rev 3/20/91<br>*Nom Temp=25 deg C                                                                                                                                                                      |

| Mos1 16 6 8 8 MOSMOD M=0.99 ;<br>.MODEL MOSMOD NMOS (VTO=3 KP=10<br>+IS=1e-30 N=10 TOX=1 L=1u W=1u)                                                                                                                         | Step 1  | Mos1 16 6 8 8 MOSMOD M=0.99<br>.MODEL MOSMOD NMOS (VTO=3.48 KP=78.5<br>+IS=1e-30 N=10 TOX=1 L=1u W=1u)                                                                                                                          |

| Mos2 16 21 8 8 MOSMOD M=0.01 ;<br>Vto 21 6 0                                                                                                                                                                                | Step 2  | Mos2 16 21 8 8 MOSMOD M=0.01<br>Vto 21 6 0.6                                                                                                                                                                                    |

| Rsource 8 7 RDSMOD 1e-12 ;                                                                                                                                                                                                  | Step 3  | Rsource 8 7 RDSMOD 2e-3                                                                                                                                                                                                         |

| Rdrain 5 16 RDSMOD 1e-12 ;                                                                                                                                                                                                  | Step 4  | Rdrain 5 16 RDSMOD 3.07e-3                                                                                                                                                                                                      |

| .MODEL RDSMOD RES (TC1=0 TC2=0)                                                                                                                                                                                             | Step 5  | .MODEL RDSMOD RES (TC1=5.2e-3 TC2=1.37e-5)                                                                                                                                                                                      |

| Evto 20 6 18 8 1 ;<br>Rvto 18 19 RVTOMOD 1<br>It 8 17 1<br>Vbat 8 19 DC 1<br>.MODEL RVTOMOD RES (TC1=0 TC2=0)                                                                                                               | Step 6  | Evto 20 6 18 8 1<br>Rvto 18 19 RVTOMOD 1<br>It 8 17 1<br>Vbat 8 19 DC 1<br>.MODEL RVTOMOD RES (TC1=-3.78e-3 TC2=-7.51e-7)                                                                                                       |

| Ebreak 11 7 17 18 1000 ;<br>Dbreak 5 11 DBKMOD<br>Rbreak 17 18 RBKMOD 1                                                                                                                                                     | Step 7  | Ebreak 11 7 17 18 58.4<br>Dbreak 5 11 DBKMOD<br>Rbreak 17 18 RBKMOD 1                                                                                                                                                           |

| .MODEL RBKMOD RES (TC1=0 TC2=0);                                                                                                                                                                                            | Step 8  | .MODEL RBKMOD RES (TC1=9.5e-4 TC2=-1.17e-6)                                                                                                                                                                                     |

| .MODEL DBKMOD D (RS=0 TRS1=0 TRS2=0) ;                                                                                                                                                                                      | Step 9  | .MODEL DBKMOD D (RS=8e-2 TRS1=2.5e-3 TRS2=0)                                                                                                                                                                                    |

| Dbody 7 5 DBDMOD ;<br>.MODEL DBDMOD D (IS=1e-30 RS=0 TRS1=0<br>+TRS2=0 CJO=0 TT=0)                                                                                                                                          | Step 10 | Dbody 7 5 DBDMOD<br>.MODEL DBDMOD D (IS=2.23e-12 RS=2.28e-3 TRS1=2.98e-3<br>+TRS2=2.22E-12 CJO=7.55e-9 TT=4e-8)                                                                                                                 |

| Lgate 1 9 1e-12 ;<br>Ldrain 2 5 1e-12<br>Lsource 3 7 1e-12<br>Rgate 9 20 1                                                                                                                                                  | Step 11 | Lgate 1 9 5e-9<br>Ldrain 2 5 1e-9<br>Lsource 3 7 3e-9<br>Rgate 9 20 1.2                                                                                                                                                         |

| Cin 6 8 1e-15 ;                                                                                                                                                                                                             | Step 12 | Cin 6 8 4.48e-9                                                                                                                                                                                                                 |

| Dplcap 10 5 DPLCAPMOD ;<br>.MODEL DPLCAPMOD D (CJO=0 IS=1e-30 N=10)<br>Esg 6 10 6 8 1                                                                                                                                       | Step 13 | Dplcap 10 5 DPLCAPMOD<br>.MODEL DPLCAPMOD D (CJO=2.14e-9 IS=1e-30 N=10)<br>Esg 6 10 6 8 1                                                                                                                                       |

| Ca 12 8 1e-15 ;<br>S1a 6 12 13 8 S1AMOD<br>S1b 13 12 13 8 S1BMOD<br>.MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=-3 VOFF=-1)<br>.MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=-1 VOFF=-3)<br>Egs 13 8 6 8 1          | Step 14 | Ca 12 8 8.98e-9<br>S1a 6 12 13 8 S1AMOD<br>S1b 13 12 13 8 S1BMOD<br>.MODEL S1AMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=-2.48 VOFF=-0.48)<br>.MODEL S1BMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=-0.48 VOFF=-2.48)<br>Egs 13 8 6 8 1  |

| Cb 15 14 1e-15 ;<br>S2a 6 15 14 13 S2AMOD<br>S2b 13 15 14 13 S2BMOD<br>.MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=-2.5 VOFF=2.5)<br>.MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=2.5 VOFF=-2.5)<br>Eds 14 8 5 8 1 | Step 15 | Cb 15 14 8.81e-9<br>S2a 6 15 14 13 S2AMOD<br>S2b 13 15 14 13 S2BMOD<br>.MODEL S2AMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=-2.25 VOFF=2.75)<br>.MODEL S2BMOD VSWITCH (RON=1e-5 ROFF=0.1<br>+VON=2.75 VOFF=-2.25)<br>Eds 14 8 5 8 1 |

| Rin 6 8 1e9 ;                                                                                                                                                                                                               | Step 16 | Rin 6 8 1e9                                                                                                                                                                                                                     |

| .ENDS                                                                                                                                                                                                                       |         | .ENDS                                                                                                                                                                                                                           |

#### **OBTAINING EXPERIMENTAL DATA**

When the authors experienced difficulty in parameter extraction the problems were traceable to erroneous data in all cases. The following caveats are offered:

- 11. Obtain all data from a single device.

- 12. Read gate voltage data to the nearest 0.01 volt.

- 13. Employ Kelvin sensing to the package leads.

- 14. Avoid self heating (a difficult assignment)

- 15. Inconsistencies lurk in data sheet curves and specifications.

#### FINAL MODEL

The final model for the RFH75N05 is shown in Table 3 and serves as an aid to understanding as it is developed from the template.

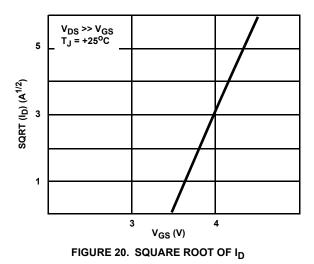

#### STEP 1 - MODEL MOSMOD (VTO AND KP)

The square root of drain current is plotted versus the gate to source voltage for the MOSFET in the saturated regime; a straight line results. The zero current intercept defines VTO and the slope defines the square root of (KP/2). Vary VTO and KP to obtain the best fit to data for the low to medium current experimental data at  $25^{\circ}$ C.

VTO is not the threshold voltage as measured. In order to use the algorithm of the PSPICE Level 1 model, W (the channel width) and L (the channel length) are defined as one micron. Therefore KP times W divided by L reduces to the model value called KP. Likewise IS, N, and TOX are set to values chosen to avoid other algorithm problems. Figure 20 shows the PSPICE generated curve after the correct values of KP and VTO of model MOSMOD are chosen.

#### STEP 2 - VTO

The threshold voltage is set by fixing the value of V<sub>TO</sub>. Threshold voltage of a power MOSFET is usually measured in the saturated regime at a low current, typically 1mA. If the PSPICE model is run at  $25^{\circ}$ C with the gate and drain voltage equal, a voltage will be found to yield 1mA drain current. V<sub>TO</sub> is this voltage reduced by the measured threshold voltage. The value identified was 0.6 volts.

### STEP 3 - R<sub>SOURCE</sub>

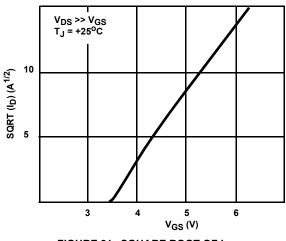

The straight line curve of Figure 20 is modified by a chosen value of  $\mathsf{R}_{SOURCE}$  in order to better fit the measured data for medium to high currents at 25°C. This is shown in Figure 21, where 2E-3 provided the best fit.

FIGURE 21. SQUARE ROOT OF ID

## STEP 4 - R<sub>DRAIN</sub>

$R_{DRAIN}$  is chosen to fix the PSPICE calculated  $R_{DS(ON)}$  value to the measured value at  $25^{o}\text{C}$  when the template is biased to the gate voltage and drain current of the specifications. Do not use the specified maximum of  $R_{DS(ON)}$ . The value developed was 3.07E-3.

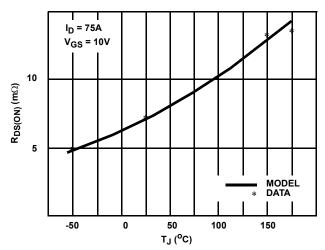

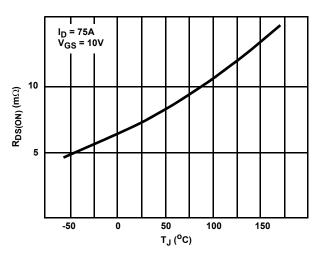

#### STEP 5 - MODEL RDSMOD (TC1 AND TC2)

$R_{SOURCE}$  and  $R_{DRAIN}$  are assumed to have the same temperature coefficients. Although this is not accurate, it is convenient and is deemed to be sufficient for this purpose. If  $R_{DS(ON)}$  is measured as a function of temperature, best fit can be obtained by appropriately choosing TC1 and TC2 values of 5.2E-3 and 1.37E-5.  $R_{DS(ON)}$  is shown in Figure 22.

FIGURE 22. R<sub>DS(ON)</sub> vs TEMPERATURE

#### STEP 6 - MODEL RVTOMOD (TC1 AND TC2)

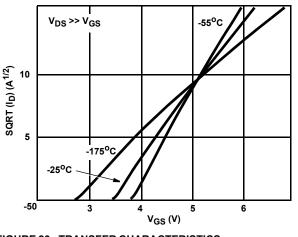

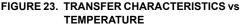

The plot of Figure 21 must be modified to add curves at low and high temperature. A temperature sensitive additive or subtractive voltage is placed in series with the gates of Mos1 and Mos2 by use of  $E_{VTO}$ . A 1 volt drop equal to It times  $R_{VTO}$ is canceled by a 1 volt supply,  $V_{BAT}$  and applied to  $E_{VTO}$ . By choosing the values of TC1 and TC2 for model RVTOMOD, the voltage of  $E_{VTO}$  is made temperature sensitive. The result is shown in Figure 23, where TC1 and TC2 were chosen for best fit at -3.78E-3 and -7.51E-7.

#### STEP 7 - EBREAK

$\mathsf{E}_{BREAK}$  derives a thermally variant voltage from the product of  $\mathsf{I}_T$  and  $\mathsf{R}_{BREAK}$  equal to 1.00 volt at 25°C. When the drain voltage rises sufficiently, diode  $\mathsf{D}_{BREAK}$  provides a voltage clamp to  $\mathsf{E}_{BREAK}$ . The value of the  $\mathsf{E}_{BREAK}$  multiplier is equal to the low current value of  $\mathsf{BV}_{DSS}$  less the forward drop of  $\mathsf{D}_{BREAK}$ . The multiplier was set at 58.4 for the final model.

#### STEP 8 - MODEL RBKMOD (TC1 AND TC2)

The low current breakdown voltage of the MOSFET may be measured at several temperatures, such that TC1 and TC2 may be determined for model RBKMOD. Figure 24 plots the low current breakdown voltage as a function of temperature as modeled with TC1 and TC2 equal to 9.5E-4 and -1.17E-6.

FIGURE 24. BREAKDOWN VOLTAGE vs TEMPERATURE

#### STEP 9 - MODEL DBKMOD (RS, TRS1 AND TRS2)

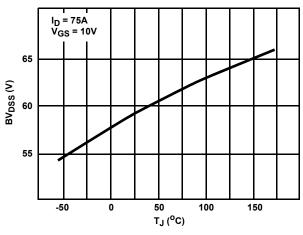

Although reliable data is difficult to obtain for the breakdown voltage at many tens of amperes, it can be done with a small inductive flyback circuit of very low duty cycle. RS of the diode  $D_{BREAK}$  may be determined at 25°C. TRS1 and TRS2 may be determined with similar measurements at several temperatures. The curves of Figure 25 present the modelled behavior for RS, TRS1 and TRS2 equal to 8E-2, 2.5E-3, and 0.

FIGURE 25. BREAKDOWN VOLTAGE vs TEMPERATURE

#### STEP 10(a) - MODEL DBDMOD (IS, RS, TRS1 and TRS2)

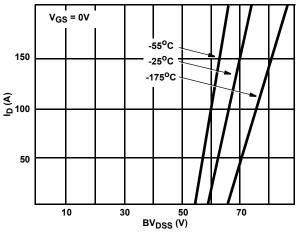

When operating  $D_{BODY}$  in the forward mode, one may develop IS and RS at 25°C assuming a diode ideality value of 1.0, the default value. Measurements at elevated current levels and several temperatures will define TRS1 and TRS2. Measurements are taken with V<sub>GS</sub> equal to zero. Figure 26 presents the body diode forward characteristics for several temperatures where IS, RS, TRS1, and TRS2 are found to equal 2.23E-12, 2.28E-3, 2.98-E3, and 2.22E-12.

#### STEP 10(b) - MODEL DBDMOD (CJO, TT)

$C_{OSS}$  minus  $C_{RSS}$  may be determined at 25 volts and 25<sup>o</sup>C. Then CJO is this value when adjusted to zero drain volts by the factor of the square root of (25+0.7) or 5.07. For the example this equals 7.55E-9.

In order to determine TT, equipment similar to the Bermar SM30 may be used. This equipment forces a forward body diode current (If) for a sufficiently long period of time, after which a linear amplifier with high current capability ramps the diode current off at a constant rate, di/dt. (Feedback control is used.) The diode current equals zero at time  $T_F$ , after the ramp off is initiated. The current continues to ramp, extracting charge from the diode, for an added time  $T_A$ . At this time, the constant ramp (di/dt) can no longer be maintained and the reverse current has attained a maximum. TT may be solved [12] and entered using:

$$TT = T_A / (1 - \exp(-(T_A + T_F) / TT))$$

The value of TT was determined to equal 4E-8.

## STEP 11 - LGATE, LDRAIN, LSOURCE, RGATE

$L_{GATE},\ L_{DRAIN},\ L_{SOURCE},\ and\ R_{GATE}$  may be measured, estimated or calculated and entered. An approximation for the inductances in nH may be calculated using:

$L = (5)(length)(log_e(4(length/diam))) nH$

where wire length and diameter are in inches [13]. Values of Lgate, Ldrain, Lsource, and Rgate were approximated at 5E-9, 1E-9, 3E-9, and 1.2 for the final model.

#### CAPACITANCES

The capacitances are derived from the measured gate charge curve of Figure 27. They will require some iteration and some judgement calls as will be explained.

FIGURE 27. GATE CHARGE CURVES

#### STEP 12 - CIN

The value of  $C_{IN}$  should be chosen for best fit to the solid line portion of the  $V_{GS}$  curve of Figure 27 labeled step 12. A value of 4.48E-9 was found to provide a good fit.

#### STEP 13 - MODEL DPLCAPMOD (CJO)

A feedback capacitor is modeled by using the junction capacitance of a reverse biased diode,  $D_{PLCAP}$ , as defined by model DPLCAPMOD. IS and N of model DPLCAPMOD were chosen to avoid undesired diode effects. CJO is chosen as 2.14E-9 to best fit the solid line portion of the V<sub>DS</sub> curve of Figure 27.

# STEP 14 - $C_A$ , MODELS S1AMOD and S1BMOD (VON and VOFF)

The value of  $C_{A}$  is chosen to be 8.98E-9 to best parallel the dotted line portion of the  $V_{GS}$  curve of Figure 27 labeled step 14.

In order to match the dotted line portion it may be necessary to increment VON and VOFF of both model S1AMOD and model S1BMOD. Note that all four values must be incremented by an identical amount before making a PSPICE run. This incremental change will vertically displace the slope provided by  $C_A$ . The transition voltages of S1A and S1B must always be negative values.

The sharpness of transition between the dashed line of step 14 and the solid line of step 12 may be adjusted if necessary by changing the increment between VON and VOFF equally for both S1A and S1B.

# STEP 15 - $\rm C_B,$ MODELS S2AMOD and S2BMOD (VON and VOFF)

The value of  $C_B$  is chosen to be 8.81E-9 to best parallel the solid line portion of the  $V_{GS}$  curve of Figure 27 labeled step 15.

In order to match the solid line portion it may be necessary to increment VON and VOFF of both model S2AMOD and model S2BMOD. Note that all four values must be incremented by an identical amount before making a PSpice run. This increment change will horizontally displace the slope provided by  $C_B$ .

The sharpness of transition between the solid line and the low voltage dotted line of the  $V_{DS}$  curve may be adjusted if necessary by changing the increment between VON and VOFF equally for both S2A and S2B. It is recommended that this increment be small, of the order of several volts.

#### STEP 16 - RIN

${\sf R}_{\sf IN}$  can be set to a very large value such as 1E15. However it is recommended that it be chosen low enough to cause 10nA to flow at a gate bias of moderately high voltage, typically 1E9 ohms.  ${\sf R}_{\sf in}$  functions to provide an initial gate reference voltage near zero even though the Modeler may choose to drive the MOSFET from a current generator.

#### EPILOGUE

The final model is completed as shown in Table 3. One may iterate through the steps if desired, but it should not be necessary. Any changes made in the model outside of the above routine should be minimal, if at all.

# Anomalies

Some commercially available power MOSFETs exhibit anomalous behavior which is not modelled in this work.

#### THE VERTICAL JFET PROBLEM

A vertical JFET type of structure exists in the VDMOS device used for the industry standard power MOSFET. Many works describe this portion of the device, including Wheatley, et al [14]. The N- lightly doped drain region reaches to the surface of the silicon die, which is bounded by the P doped body. This region of N- is often called the neck of the MOSFET. As the breakdown voltage of the device is designed for increasing

values, the depletion layer extends further within the neck laterally, for relatively low drain voltages. In this manner, the neck or vertical JFET becomes pinched off, causing the  $R_{DS(ON)}$  to exhibit excess non-linearity with current. In addition an abrupt limiting of the drain current (at large values of drain voltages) occurs for increasing values of gate voltage. This current limiting has a highly localized thermal assist constrained to the neck with time responses in the microsecond region. This anomaly may be suppressed by increasing the neck width and/or implanting a low dose of N type dopant into the neck, just below the surface.

Devices of this type are not properly modeled.

#### NON OHMIC CONTACT PROBLEMS

Some commercially available devices exhibit a non-ohmic series contact resistance from the metalization to the silicon. This seldom happens with present day devices, but, when present, it is most likely to occur from source metal to source silicon for N channel devices, and from drain metal to drain silicon for P channel devices. The effect is seen as a low current non-linearity in  $R_{DS(ON)}$  vs drain current for the former case and an excessive voltage drop for the body diode for the latter case.

Devices of this type are not properly modeled.

## Conclusions

An equivalent circuit model for power MOSFETs that is suitable for use with PSPICE has been demonstrated. The model requires no modifications to the PSPICE algorithms. The model features global temperature representation from -55°C to 175°C for the first time. It addresses static and dynamic behavior over the normal circuit operating range of the device, including 1st and 3rd guadrant MOSFET operation, high current avalanche breakdown operation, body diode stored charge effects, gate charge non-linearities, gate equivalent series resistance (ESR), and package inductances. Gate propagation delay is not modeled [15]. The sub-circuit is empirical in nature and the parameters may be readily extracted by use of terminal measurements. Experimental verification shows excellent agreement between measured and simulated results over the entire thermal, static, and dynamic regimes.

### **Recommendations For Future Work**

A supporting program of algorithms should be written to address the parameter extraction effort.

Accurate testing for characterization of power MOSFETs as a function of temperature is required. Studies should be made to identify and correct methods prone to testing error.

PSPICE algorithms should be modified to refine and incorporate many of the findings of this work into a new MOS level.

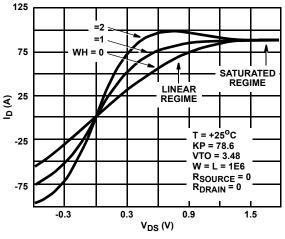

If a new MOS level is formed, a modification should be made to the drain current equation in the linear regime to accommodate the non-uniform channel surface concentration of the power MOSFET as described elsewhere. If done, the MOSFET may be more closely modeled in the linear regime of the output characteristic curves and the third quadrant MOSFET regime. (See Figure 9 and Figure 19.) The authors suggest a user defined model value WH to be used in a multiplier which would be applied to ld in the linear regime such that:

$$\text{Aultiplier} = (1 + \text{WH}^*(1 - \text{V}_{\text{DS}}/(\text{V}_{\text{GS}} - \text{V}_{\text{TO}}))^2)$$

If the multiplier were applied to the MOSFET of Table 3, the 1st and 3rd quadrant characteristics would be approximately as shown in Figure 28 for V<sub>GS</sub> = 5 volts. Here, WH is shown for values of 0, 1, and 2. The drain and source are interchanged for V<sub>DS</sub> < 0, as is done in PSPICE.

FIGURE 28. THE WH ADJUSTMENT

A value of zero for WH forces the multiplier to equal unity for all values of  $V_{DS}$ , thereby retaining the original linear regime equation. Zero should be the default value. Any value of WH greater than 1 results in a negative output resistance and is unacceptable. Therefore WH is bounded by 0 and 1.

If this multiplier option were offered, it would be extracted for the model MOSMOD between steps 3 and 4 of Table 2, probably requiring some iteration between WH and Rdrain.

# **Acknowledgements**

The authors express appreciation to Don Burke, Gene Freeman, Nick Magda, Hal Ronan, and Wally Williams for their support and assistance.

#### REFERENCES

- [1] L. W. Nagel, "SPICE2: A COMPUTER PROGRAM TO SIMULATE SEMICONDUCTOR CIRCUITS," <u>ERL Memo</u> <u>UCB/ERL M520</u>, University of California, Berkley, May 1975.

- [2] H. A. Nienhaus, J. C. Bowers, and P. C. Herren, "A High Power MOSFET Computer Model," <u>Power Conversion</u> <u>International</u>, Jan 1982, pp. 65-73.

- [3] J. C. Bowers, and H. A. Nienhaus, "SPICE-2 Computer Models for HEXFETs," <u>International Rectifier HEXFET</u> <u>Data Book</u>, Application Note 954A, pp A153-A160.

- [4] G. M. Dolny, H. R. Ronan, Jr., and C. F. Wheatley, Jr., "A SPICE II Subcircuit Representation for Power MOSFETs Using Empirical Methods," <u>RCA Review</u>", Vol 46, Sept 1985.

- [5] C. F. Wheatley, Jr., H. R. Ronan, Jr., and G. M. Dolny, "Spicing-up SPICE II Software For Power MOSFET Modeling," <u>GE/RCA Solid State</u>, Application Note AN8610.

- [6] S. Malouyans, "SPICE Computer Models for HEXFET Power MOSFETs," <u>International Rectifier</u>, Application Note 975.

- [7] H. P. Yee and P.O. Lauritzen, "SPICE Models for Power Mosfets: An Update," <u>Proc. APEC'88</u>, Feb 1988, pp. 281-289, (Third Annual IEEE Applied Power Electronics Conference and Exposition, New Orleans), IEEE Cat no: 88CH2504-9.

- [8] C. E. Cordonnier, "Spice Model for TMOS Power MOSFETs," <u>Motorola Semiconductor</u>, Application Note AN1043, 1989.

- [9] D. F. Haslam, M. E. Clarke, and J.A. Houldsworth, "SIM ULATING POWER MOSFETS WITH SPICE" <u>Proc.</u> <u>HFPC</u>, May 1990, p. 296.

- [10] A. Vladimirescu and M. Walker, "A Power MOSFET Macro-Model for Circuit Simulation," <u>Proc. POWER</u> <u>CONVERSION</u>, Oct 1990, p. 112.

- [11] S. Klodzinski, C. F. Wheatley, Jr., and J. M. Neilson, Intersil Power, unpublished.

- [12] Y. C. Kao and J. R. Davis, "Correlations Between Reverse Recovery Time and Lifetime of p-n Junction Driven by a Current Ramp," <u>IEEE TRANSACTIONS on ELECTRON</u> <u>DEVICES</u>, VOL. ED-17 No. 9, Sept 1970.

- [13] F. Langford-Smith, Editor, "<u>Radiotron Designer's</u> <u>Handbook</u>," Fourth Edition, Wireless Press, 1953, Chapter 36.1, p. 1287

- [14] C. F. Wheatley, Jr. and H. R. Ronan, Jr., "Switching Waveforms of the L<sup>2</sup>FET: A 5-Volt Gate Drive Power MOSFET," <u>Power Electronics Specialist Conference</u> <u>Record</u>, June 1984, p. 238.

- [15] G. M. Dolny, C. F. Wheatley, Jr., and H. R. Ronan, Jr., "COMPUTER-AIDED ANALYSIS OF GATE-VOLTAGE PROPAGATION EFFECTS IN POWER MOSFETs" <u>Proc.</u> <u>HFPC</u>, May 1986, p. 146.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard" Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances; machine tools; personal electronic equipment: industrial robots: etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc. Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics oroducts outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Plea e contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Renesas Electronics Corporation**

http://www.renesas.com

SALES OFFICES Refer to "http://www.renesas.com/" for the latest and detailed information Renesas Electronics America Inc. 1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351 Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tei: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 Renesas Electronics Hong Kong Limited Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022 Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amco Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Unit 1207, Block B, Menara Amcorp, Amcorp Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tei: +822-558-3737, Fax: +822-558-5338