# **RX13T Group, RX130 Group**

Differences Between the RX13T Group and the RX130 Group

#### Summary

This application note is intended as a reference to points of difference between the peripheral functions, I/O registers, and pin functions of the RX13T Group and RX130 Group, as well as a guide to key points to consider when migrating between the two groups.

Unless specifically otherwise noted, the information in this application note applies to the 48-pin package version of the RX13T Group and the 100-pin package version of the RX130 Group as the maximum specifications. To confirm details of differences in the specifications of the electrical characteristics, usage notes, and setting procedures, refer to the User's Manual: Hardware of the products in question.

#### **Target Devices**

RX13T Group and RX130 Group

# **Contents**

| 1.    | Comparison of Built-In Functions of RX13T Group and RX130 Group           | 4  |

|-------|---------------------------------------------------------------------------|----|

| 2.    | Comparative Overview of Specifications                                    | 5  |

| 2.1   | CPU                                                                       | 5  |

| 2.2   | Address space                                                             | 6  |

| 2.3   | Option-Setting Memory                                                     | 7  |

| 2.4   | Voltage Detection Circuit                                                 | 8  |

| 2.5   | Clock Generation Circuit                                                  | 12 |

| 2.6   | Clock Frequency Accuracy Measurement Circuit                              | 15 |

| 2.7   | Low Power Consumption                                                     | 17 |

| 2.8   | Register Write Protection Function                                        | 21 |

| 2.9   | Exception Handling                                                        | 22 |

| 2.10  | Interrupt Controller                                                      | 23 |

| 2.11  | Buses                                                                     | 25 |

| 2.12  | Data Transfer Controller                                                  | 27 |

| 2.13  | I/O Ports                                                                 | 29 |

| 2.14  | Multi-Function Pin Controller                                             | 32 |

| 2.15  | Multi-Function Timer Pulse Unit 2/Multi-Function Timer Pulse Unit 3       | 45 |

| 2.16  | Port Output Enable 2/Port Output Enable 3                                 | 49 |

| 2.17  | Compare Match Timer                                                       | 52 |

| 2.18  | Serial Communications Interface                                           | 53 |

| 2.19  | I <sup>2</sup> C Bus Interface                                            | 58 |

| 2.20  | 12-Bit A/D Converter                                                      | 61 |

| 2.21  | D/A Converter/D/A Converter for Generating Comparator C Reference Voltage | 67 |

| 2.22  | Comparator B/Comparator C                                                 | 68 |

| 2.23  | Data Operation Circuit                                                    | 70 |

| 2.24  | RAM                                                                       | 71 |

| 2.25  | Flash Memory                                                              | 72 |

| 2.26  | Packages                                                                  | 74 |

| 2     | Comparison of Din Eurotions                                               | 75 |

|       | Comparison of Pin Functions                                               |    |

| 3.1   | 48-Pin Package                                                            | 75 |

| 4.    | Important Information when Migrating Between MCUs                         | 77 |

| 4.1   | Notes on Functional Design                                                | 77 |

| 4.1.1 | Exception Vector Table                                                    | 77 |

| 4.1.2 | Port Direction Register (PDR) Initialization                              | 77 |

| 4.1.3 | PB1 Pin Input Level                                                       | 77 |

| 4.1.4 | MTIOC Pin Output Level when Counter Operation Stopped                     | 77 |

| 4.1.5 | Conversion Start Requests in Complementary PWM Mode                       | 77 |

| 4.1.6 | Pulse Width of Count Clock Source                                         | 78 |

| 4.1.7  | High-Impedance Control when MTU Pins Deselected                       | 78 |

|--------|-----------------------------------------------------------------------|----|

| 4.1.8  | A/D Scan Conversion End Interrupt Generation                          | 78 |

| 4.1.9  | A/D Conversion Start Trigger in Group Scan Mode                       | 78 |

| 4.1.10 | A/D Conversion Start Bit                                              | 78 |

| 4.1.11 | Scan Conversion Time of 12-bit A/D Converter                          | 78 |

| 4.1.12 | D/A Converter Settings                                                | 79 |

| 4.1.13 | Comparator                                                            | 79 |

| 4.1.14 | Comparator C Operation in Module Stop State                           | 79 |

| 4.1.15 | Comparator C Operation in Software Standby Mode                       | 79 |

| 4.1.16 | Comparator C Operation with 12-Bit A/D Converter in Module Stop State | 79 |

| 5. R   | eference Documents                                                    | 80 |

| Revisi | on History                                                            | 82 |

# 1. Comparison of Built-In Functions of RX13T Group and RX130 Group

A comparison of the built-in functions of the RX13T Group and RX130 Group is provided below. For details of the functions, see section 2, Comparative Overview of Specifications and section 5, Reference Documents.

Table 1.1 is a comparison of built-in functions of RX13T Group and RX130 Group.

Table 1.1 Comparison of Built-In Functions of RX13T Group and RX130 Group

| Function                                                                 | RX130 | RX13T    |

|--------------------------------------------------------------------------|-------|----------|

| <u>CPU</u>                                                               | ,     |          |

| Operating modes                                                          | ,     | 0        |

| Address space                                                            |       | <u> </u> |

| Resets                                                                   | -     | 0        |

| Option-setting memory (OFSM)                                             |       |          |

| Voltage detection circuit (LVDAb)                                        |       |          |

| Clock generation circuit                                                 |       |          |

| Clock frequency accuracy measurement circuit (CAC)                       |       |          |

| Low power consumption                                                    |       |          |

| Register write protection function                                       |       |          |

| Exception handling                                                       |       |          |

| Interrupt controller (ICUb)                                              |       |          |

| Buses                                                                    |       | <u> </u> |

| Data transfer controller (DTCa): RX130, (DTCb): RX13T                    |       | /        |

| Event link controller (ELC)                                              | 0     | X        |

| I/O ports                                                                |       | /        |

| Multi-function pin controller (MPC)                                      |       | <u> </u> |

| Multi-function timer pulse unit 2 (MTU2a): RX130,                        | 1     |          |

| Multi-function timer pulse unit 3 (MTU3c): RX13T                         |       |          |

| Port output enable 2 (POE2a): RX130, Port output enable 3 (POE3C): RX13T |       |          |

| 8-bit timer (TMR)                                                        | 0     | ×        |

| Compare match timer (CMT)                                                |       |          |

| Realtime clock (RTC)                                                     | 0     | ×        |

| Low-power timer (LPT)                                                    | 0     | ×        |

| Independent watchdog timer (IWDTa)                                       |       | 0        |

| Serial communications interface (SClg, SClh)                             |       | /        |

| Remote Control Signal Receiver (REMC)                                    | 0     | ×        |

| I <sup>2</sup> C bus interface (RIICa)                                   |       |          |

| Serial peripheral interface (RSPIa)                                      | 0     | ×        |

| CRC calculator (CRC)                                                     | ,     | Ö        |

| Capacitive touch sensing unit (CTSUa)                                    | 0     | ×        |

| 12-bit A/D converter (S12ADE): RX130, (S12ADF): RX13T                    |       | 1        |

| D/A converter (DAa): RX130,                                              |       |          |

| D/A converter for generating comparator C reference voltage (DA): RX13T  |       |          |

| Temperature sensor                                                       | 0     | X        |

| Comparator B (CMPBa): RX130, Comparator C (CMPC): RX13T                  |       | /        |

| Data operation circuit (DOC)                                             |       |          |

| RAM                                                                      |       |          |

| Flash memory (FLASH)                                                     |       | <u> </u> |

| <u>Packages</u>                                                          |       | /        |

○: Available, X: Unavailable, •: Differs due to added functionality,

▲: Differs due to change in functionality, ■: Differs due to removed functionality.

# 2. Comparative Overview of Specifications

This section presents a comparative overview of specifications, including registers.

In the comparative overview, red text indicates functions which are included only in one of the MCU groups and also functions for which the specifications differ between the two groups.

In the register comparison, red text indicates differences in specifications for registers that are included in both groups and **black text** indicates registers which are included only in one of the MCU groups. Differences in register specifications are not listed.

#### 2.1 CPU

Table 2.1 is a comparative overview of CPU, and Table 2.2 is a comparison of CPU registers.

**Table 2.1 Comparative Overview of CPU**

| Item | RX130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RX13T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU  | <ul> <li>Maximum operating frequency: 32 MHz</li> <li>32-bit RX CPU</li> <li>Minimum instruction execution time: One instruction per clock cycle</li> <li>Address space: 4 GB, linear</li> <li>Register set of the CPU  — General purpose: Sixteen 32-bit registers  — Control: Eight 32-bit registers  — Accumulator: One 64-bit register</li> <li>Basic instructions: 73, variable-length instruction format</li> <li>DSP instructions: 9</li> <li>Addressing modes: 10</li> <li>Data arrangement  — Instructions: Little endian  — Data: Selectable between little endian or big endian</li> <li>On-chip 32-bit multiplier: 32 × 32 → 64 bits</li> <li>On-chip divider: 32 / 32 → 32 bits</li> <li>Barrel shifter: 32 bits</li> </ul> | <ul> <li>Maximum operating frequency: 32 MHz</li> <li>32-bit RX CPU</li> <li>Minimum instruction execution time: One instruction per clock cycle</li> <li>Address space: 4 GB, linear</li> <li>Register set of the CPU  — General purpose: Sixteen 32-bit registers — Control: Nine 32-bit registers</li> <li>— Accumulator: One 64-bit registers</li> <li>Basic instructions: 73, variable-length instruction format</li> <li>Floating point instructions: 8</li> <li>DSP instructions: 9</li> <li>Addressing modes: 10</li> <li>Data arrangement  — Instructions: Little endian  — Data: Selectable between little endian or big endian</li> <li>On-chip 32-bit multiplier: 32 × 32 → 64 bits</li> <li>On-chip divider: 32 / 32 → 32 bits</li> <li>Barrel shifter: 32 bits</li> </ul> |

| FPU  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>Single-precision floating-point (32 bits)</li> <li>Data types and floating-point exceptions conform to IEEE 754 standard</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 2.2 Comparison of CPU Registers

| Register | Bit | RX130 | RX13T                      |

|----------|-----|-------|----------------------------|

| FPSW     |     | _     | Floating-point status word |

# 2.2 Address space

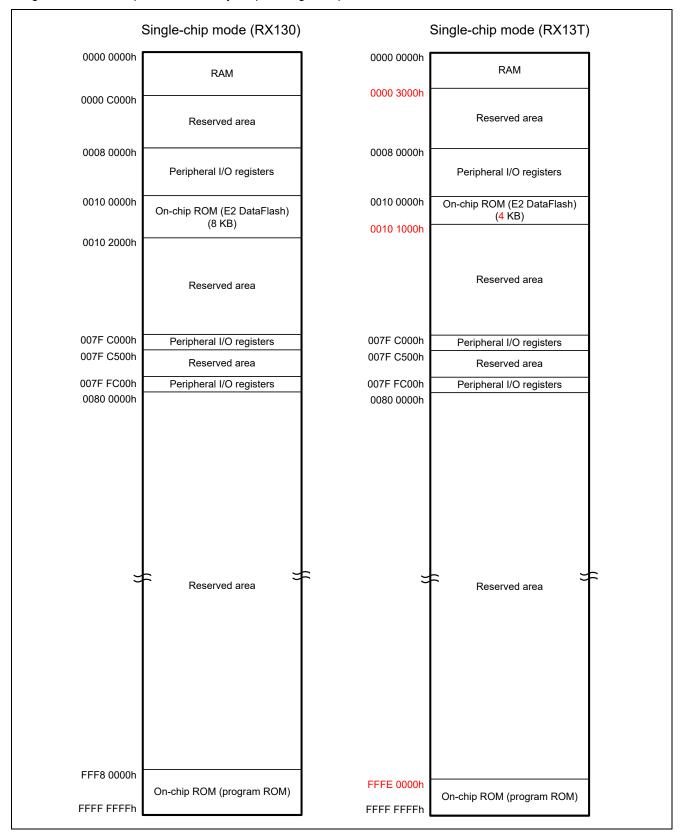

Figure 2.1 is a comparative memory map of single-chip mode.

Figure 2.1 Comparative Memory Map of Single-Chip Mode

# 2.3 Option-Setting Memory

Table 2.3 is a comparison of option-setting memory registers.

Table 2.3 Comparison of Option-Setting Memory Registers

| Register | Bit        | RX130 (OFSM)                     | RX13T (OFSM)                     |

|----------|------------|----------------------------------|----------------------------------|

| OFS1     | VDSEL[1:0] | Voltage detection 0 level select | Voltage detection 0 level select |

|          |            | bits                             | bits                             |

|          |            | b1 b0                            | b1 b0                            |

|          |            | 0 0: 3.84 V is selected          | 0 0: 3.84 V is selected          |

|          |            | 0 1: 2.82 V is selected          | 0 1: 2.82 V is selected          |

|          |            | 1 0: 2.51 V is selected          | 1 0: 2.51 V is selected          |

|          |            | 1 1: 1.90 V is selected          |                                  |

|          |            |                                  | Do not set a value other than    |

|          |            |                                  | those above when using the       |

|          |            |                                  | voltage detection 0 circuit.     |

|          | FASTSTUP   | Power-on fast startup time bit   | _                                |

# 2.4 Voltage Detection Circuit

Table 2.4 is a comparative overview voltage detection circuits, Table 2.5 is a comparison of voltage detection circuit registers, Table 2.6 is a comparative listing of the Vdet2 monitor setting procedure, and Table 2.7 is a comparative listing of the procedures for setting bits related to the voltage monitoring 2 interrupt and voltage monitoring 2 reset.

**Table 2.4 Comparative Overview of Voltage Detection Circuits**

|                                    |                      | RX130 (LVDAb)                                                                                                               |                                                                                                                                                          |                                                                                                                                                                                                         | RX13T (LVDAb)                                                                                                               |                                                                                                                                                          |                                                                                                                                                          |  |

|------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Item                               |                      | Voltage<br>Monitoring 0                                                                                                     | Voltage<br>Monitoring 1                                                                                                                                  | Voltage<br>Monitoring 2                                                                                                                                                                                 | Voltage<br>Monitoring 0                                                                                                     | Voltage<br>Monitoring 1                                                                                                                                  | Voltage<br>Monitoring 2                                                                                                                                  |  |

| VCC<br>monitoring                  | Monitored voltage    | Vdet0                                                                                                                       | Vdet1                                                                                                                                                    | Vdet2                                                                                                                                                                                                   | Vdet0                                                                                                                       | Vdet1                                                                                                                                                    | Vdet2                                                                                                                                                    |  |

|                                    | Detection<br>target  | Voltage drops<br>past Vdet0                                                                                                 | When voltage<br>rises above or<br>drops below<br>Vdet1                                                                                                   | When voltage rises above or drops below Vdet2 Input voltages to VCC and CMPA2 pin can be switched using LVCMPCR.EXV CCINP2 bit                                                                          | Voltage drops<br>past Vdet0                                                                                                 | Voltage rises or<br>drops past<br>Vdet1                                                                                                                  | Voltage rises or<br>drops past<br>Vdet2                                                                                                                  |  |

|                                    | Detection<br>voltage | Voltage<br>selectable from<br>four levels using<br>OFS1 register                                                            | Voltage<br>selectable from<br>14 levels using<br>the<br>LVDLVLR.LVD1<br>LVL[3:0] bits                                                                    | Voltage<br>selectable from<br>four levels using<br>the<br>LVDLVLR.LVD2<br>LVL[1:0] bits                                                                                                                 | Voltage<br>selectable from<br>three levels<br>using OFS1<br>register                                                        | Voltage<br>selectable from<br>nine levels<br>using the<br>LVDLVLR.LVD1<br>LVL[3:0] bits                                                                  | Voltage<br>selectable from<br>four levels using<br>the<br>LVDLVLR.LVD2<br>LVL[1:0] bits                                                                  |  |

|                                    | Monitor<br>flag      |                                                                                                                             | LVD1SR.LVD1<br>MON flag:<br>Monitors<br>whether voltage<br>is higher or<br>lower than<br>Vdet1<br>LVD1SR.LVD1<br>DET flag:<br>Vdet1 passage<br>detection | LVD2SR.LVD2<br>MON flag:<br>Monitors<br>whether voltage<br>is higher or<br>lower than<br>Vdet2<br>LVD2SR.LVD2<br>DET flag:<br>Vdet2 passage<br>detection                                                |                                                                                                                             | LVD1SR.LVD1<br>MON flag:<br>Monitors<br>whether voltage<br>is higher or<br>lower than<br>Vdet1<br>LVD1SR.LVD1<br>DET flag:<br>Vdet1 passage<br>detection | LVD2SR.LVD2<br>MON flag:<br>Monitors<br>whether voltage<br>is higher or<br>lower than<br>Vdet2<br>LVD2SR.LVD2<br>DET flag:<br>Vdet2 passage<br>detection |  |

| Voltage<br>detection<br>processing | Reset                | Voltage<br>monitoring 0<br>reset<br>Reset when<br>Vdet0 > VCC<br>CPU restart<br>after specified<br>time with VCC<br>> Vdet0 | Voltage monitoring 1 reset  Reset when Vdet1 > VCC CPU restart timing selectable: after specified time with VCC > Vdet1 or Vdet1 > VCC                   | Voltage monitoring 2 reset  Reset when Vdet2 > VCC or CMPA2 pin CPU restart timing selectable: after specified time with VCC or CMPA2 pin > Vdet2 or after specified time with Vdet2 > VCC or CMPA2 pin | Voltage<br>monitoring 0<br>reset<br>Reset when<br>Vdet0 > VCC<br>CPU restart<br>after specified<br>time with VCC<br>> Vdet0 | Voltage<br>monitoring 1<br>reset  Reset when Vdet1 > VCC CPU restart timing selectable: after specified time with VCC > Vdet1 or Vdet1 > VCC             | Voltage monitoring 2 reset  Reset when Vdet2 > VCC CPU restart timing selectable: after specified time with VCC > Vdet2 or Vdet2 > VCC                   |  |

|                                    |           |                         |                                                                     |                                                                                                | RX13T (LVDAb)           |                                                                     |                                                                     |

|------------------------------------|-----------|-------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| Item                               |           | Voltage<br>Monitoring 0 | Voltage<br>Monitoring 1                                             | Voltage<br>Monitoring 2                                                                        | Voltage<br>Monitoring 0 | Voltage<br>Monitoring 1                                             | Voltage<br>Monitoring 2                                             |

| Voltage<br>detection<br>processing | Interrupt | _                       | Voltage<br>monitoring 1<br>interrupt                                | Voltage<br>monitoring 2<br>interrupt                                                           | _                       | Voltage<br>monitoring 1<br>interrupt                                | Voltage<br>monitoring 2<br>interrupt                                |

|                                    |           |                         | Non-maskable or maskable is selectable                              | Non-maskable or maskable is selectable                                                         |                         | Non-maskable or maskable selectable                                 | Non-maskable or maskable selectable                                 |

|                                    |           |                         | Interrupt request issued when Vdet1 > VCC and VCC > Vdet1 or either | Interrupt request issued when Vdet2 > VCC or CMPA2 pin and VCC or CMPA2 pin > Vdet2, or either |                         | Interrupt request issued when Vdet1 > VCC and VCC > Vdet1 or either | Interrupt request issued when Vdet2 > VCC and VCC > Vdet2 or either |

| Event link function                |           |                         | Available<br>Vdet1 passage<br>detection event<br>output             |                                                                                                |                         |                                                                     |                                                                     |

Table 2.5 Comparison of Voltage Detection Circuit Registers

| Register                 | Bit       | RX130 (LVDAb)                                                                                                                    | RX13T (LVDAb)                                                              |

|--------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| LVD2CR1 LVD2IDTSEL [1:0] |           | Voltage monitoring 2 interrupt generation condition select bits                                                                  | Voltage monitoring 2 interrupt generation condition select bits            |

|                          |           | b1 b0<br>0 0: When VCC or CMPA2 pin<br>≥ Vdet2 (rise) is detected<br>0 1: When VCC or CMPA2 pin                                  | b1 b0<br>0 0: VCC ≥ Vdet2 (rise) is detected<br>0 1: VCC < Vdet2 (drop) is |

|                          |           | <ul> <li>&lt; Vdet2 (drop) is detected</li> <li>1 0: When drop and rise are detected</li> <li>1 1: Setting prohibited</li> </ul> | detected  1 0: When drop and rise are detected  1 1: Setting prohibited    |

| LVD2SR                   | LVD2MON   | Voltage monitoring 2 signal monitor flag  0: VCC or CMPA2 pin < Vdet2                                                            | Voltage monitoring 2 signal monitor flag  0: VCC < Vdet2                   |

|                          |           | 1: VCC or CMPA2pin ≥ Vdet2 or LVD2MON is disabled                                                                                | 1: VCC ≥ Vdet2 or LVD2MON is disabled                                      |

| LVCMPCR                  | EXVCCINP2 | Voltage detection 2 comparison voltage external input select bit                                                                 | _                                                                          |

| Register | Bit     | RX130 (LVDAb)                         | RX13T (LVDAb)                                 |

|----------|---------|---------------------------------------|-----------------------------------------------|

| LVDLVLR  | LVD1LVL | Voltage detection 1 level select bits | Voltage detection 1 level select bits         |

|          | [3:0]   | (Standard voltage during drop in      | (Standard voltage during drop in              |

|          |         | voltage)                              | voltage)                                      |

|          |         |                                       |                                               |

|          |         | b3 b0                                 | b3 b0                                         |

|          |         | 0 0 0 0: 4.29 V                       | 0 0 0 0: 4.29 V                               |

|          |         | 0 0 0 1: 4.14 V                       | 0 0 0 1: 4.14 V                               |

|          |         | 0 0 1 0: 4.02 V                       | 0 0 1 0: 4.02 V                               |

|          |         | 0 0 1 1: 3.84 V                       | 0 0 1 1: 3.84 V                               |

|          |         | 0 1 0 0: 3.10 V                       | 0 1 0 0: 3.10 V                               |

|          |         | 0 1 0 1: 3.00 V                       | 0 1 0 1: 3.00 V                               |

|          |         | 0 1 1 0: 2.90 V<br>0 1 1 1: 2.79 V    | 0 1 1 0: 2.90 V<br>0 1 1 1: 2.79 V            |

|          |         | 1 0 0 0: 2.68 V                       | 1 0 0 0: 2.68 V                               |

|          |         | 1 0 0 0. 2.08 V                       |                                               |

|          |         | 1 0 1 1: 2:36 V                       | Settings other than the above are prohibited. |

|          |         | 1 0 1 0. 2.46 V                       | prombited.                                    |

|          |         | 1 1 0 0: 1.96 V                       |                                               |

|          |         | 1 1 0 0: 1.90 V                       |                                               |

|          |         | Settings other than the above are     |                                               |

|          |         | prohibited.                           |                                               |

| LVD2CR0  | LVD2RN  | Voltage monitoring 2 reset            | Voltage monitoring 2 reset                    |

|          |         | negation select bit                   | negation select bit                           |

|          |         |                                       |                                               |

|          |         | 0: Negation follows stabilization     | 0: Negation follows stabilization             |

|          |         | time (tLVD2) after VCC or             | time (tLVD2) after VCC > Vdet2                |

|          |         | CMPA2 pin > Vdet2 is detected.        | is detected.                                  |

|          |         | 1: Negation follows stabilization     | 1: Negation follows stabilization             |

|          |         | time (tLVD2) after assertion of       | time (tLVD2) after assertion of               |

|          |         | voltage monitoring 2 reset.           | voltage monitoring 2 reset.                   |

Table 2.6 Comparison of Setting Procedures for Vdet2 Voltage Monitoring

| Item                             |   | RX130 (LVDAb)                                                                                                                  | RX13T (LVDAb)                                                                                                                               |

|----------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Vdet2 voltage monitoring setting | 1 | Set the LVDLVLR.LVD2LVL[1:0] bits (voltage detection 2 detection voltage).                                                     | Set the LVDLVLR.LVD2LVL[1:0] bits (voltage detection 2 detection voltage).                                                                  |

| procedure                        | 2 | Set the LVCMPCR.EXVCCINP2 bit to                                                                                               | — (voltage detection 2 detection voltage).                                                                                                  |

|                                  |   | 0 (VCC voltage) or 1 (CMPA2 pin input voltage).                                                                                |                                                                                                                                             |

|                                  | 3 | Set the LVCMPCR.LVD2E bit to 1 (voltage detection 2 circuit enabled).                                                          | Set the LVCMPCR.LVD2E bit to 1 (voltage detection 2 circuit enabled).                                                                       |

|                                  | 4 | After waiting for td(E-A), set the LVD2CR0.LVD2CMPE bit to 1 (voltage monitoring 2 circuit comparison results output enabled). | After waiting for Td <sub>(E-A)</sub> , set the LVD2CR0.LVD2CMPE bit to 1 (voltage monitoring 2 circuit comparison results output enabled). |

Table 2.7 Comparison of Operation Setting Procedures for Voltage Monitoring 2 Interrupt and Voltage Monitoring 2 Reset Related Bits

| Item                          |    | RX130 (LVDAb)                                                                                                                                            | RX13T (LVDAb)                                                                                                                                            |

|-------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage<br>monitoring 2       | 1  | Select the detection voltage by setting the LVDLVLR.LVD2LVL[1:0] bits.                                                                                   | Select the detection voltage by setting the LVDLVLR.LVD2LVL[1:0] bits.                                                                                   |

| interrupt                     | 2  | Set the LVCMPCR.EXVCCINP2 bit to 0 (VCC voltage) or 1 (CMPA2 pin input voltage).                                                                         |                                                                                                                                                          |

|                               | 3  | Clear the LVD2CR0.LVD2RI bit to 0 (voltage monitoring 2 interrupt).                                                                                      | Clear the LVD2CR0.LVD2RI bit to 0 (voltage monitoring 2 interrupt).                                                                                      |

|                               | 4  | Select the timing of interrupt requests by setting the LVD2CR1.LVD2IDTSEL[1:0] bits. Select the type of interrupt by setting the LVD2CR1.LVD2IRQSEL bit. | Select the timing of interrupt requests by setting the LVD2CR1.LVD2IDTSEL[1:0] bits. Select the type of interrupt by setting the LVD2CR1.LVD2IRQSEL bit. |

|                               | 5  | Set the LVCMPCR.LVD2E bit to 1 (voltage detection 2 circuit enabled).                                                                                    | Set the LVCMPCR.LVD2E bit to 1 (voltage detection 2 circuit enabled).                                                                                    |

|                               | 6  | Wait for at least td(E-A).                                                                                                                               | Wait for at least Td <sub>(E-A)</sub> .                                                                                                                  |

|                               | 7  | Set the LVD2CR0.LVD2CMPE bit to 1 (voltage monitoring 2 circuit comparison results output enabled).                                                      | Set the LVD2CR0.LVD2CMPE bit to 1 (voltage monitoring 2 circuit comparison results output enabled).                                                      |

|                               | 8  | Wait for at least 2 µs.                                                                                                                                  | Wait for at least 2 µs.                                                                                                                                  |

|                               | 9  | Clear the LVD2SR.LVD2DET bit to 0.                                                                                                                       | Clear the LVD2SR.LVD2DET bit to 0.                                                                                                                       |

|                               | 10 | Set the LVD2CR0.LVD2RIE bit to 1 (voltage monitoring 2 interrupt/reset enabled).                                                                         | Set the LVD2CR0.LVD2RIE bit to 1 (voltage monitoring 2 interrupt/reset enabled).                                                                         |

| Voltage<br>monitoring 2 reset | 1  | Select the detection voltage by setting the LVDLVLR.LVD2LVL[1:0] bits.                                                                                   | Select the detection voltage by setting the LVDLVLR.LVD2LVL[1:0] bits.                                                                                   |

|                               | 2  | Set the LVCMPCR.EXVCCINP2 bit to 0 (VCC voltage) or 1 (CMPA2 pin input voltage).                                                                         |                                                                                                                                                          |

|                               | 3  | Set the LVD2CR0.LVD2RI bit to 1 (voltage monitoring 2 reset). Select the type of reset negation by setting the LVD2CR0.LVD2RN bit.                       | Set the LVD2CR0.LVD2RI bit to 1 (voltage monitoring 2 reset). Select the type of reset negation by setting the LVD2CR0.LVD2RN bit.                       |

|                               | 4  | Set the LVD2CR0.LVD2RIE bit to 1 (voltage monitoring 2 interrupt/reset enabled).                                                                         | Set the LVD2CR0.LVD2RIE bit to 1 (voltage monitoring 2 interrupt/reset enabled).                                                                         |

# 2.5 Clock Generation Circuit

Table 2.8 is a comparative overview of the clock generation circuits, and Table 2.9 is a comparison of clock generation circuit registers.

**Table 2.8 Comparative Overview of Clock Generation Circuits**

| Item      | RX130                                                                                                                                                                                                                                                  | RX13T                                                                                                                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use       | Generates the system clock (ICLK) to<br>be supplied to the CPU, DTC, ROM,<br>and RAM.                                                                                                                                                                  | Generates the system clock (ICLK) to<br>be supplied to the CPU, DTC, ROM,<br>and RAM.                                                                                                                              |

|           | Of the peripheral module clocks<br>(PCLKB and PCLKD) supplied to the<br>peripheral modules, PCLKD is the<br>operating clock for the S12AD, and<br>PCLKB is the operating clock for<br>modules other than S12AD.                                        | Of the peripheral module clocks<br>(PCLKB and PCLKD) supplied to the<br>peripheral modules, PCLKD is the<br>operating clock for the S12AD and<br>PCLKB is the operating clock for the<br>other peripheral modules. |

|           | Generates the FlashIF clock (FCLK) to<br>be supplied to the FlashIF.                                                                                                                                                                                   | Generates the FlashIF clock (FCLK) to<br>be supplied to the FlashIF.                                                                                                                                               |

|           | <ul> <li>Generates the CAC clock (CACCLK) to<br/>be supplied to the CAC.</li> <li>Generates the RTC-dedicated sub-<br/>clock (RTCSCLK) to be supplied to the</li> </ul>                                                                                | Generates the CAC clock (CACCLK) to<br>be supplied to the CAC.                                                                                                                                                     |

|           | <ul> <li>RTC.</li> <li>Generates the IWDT-dedicated clock (IWDTCLK) to be supplied to the IWDT.</li> <li>Generates the LPT clock (LPTCLK) to be supplied to the LPT.</li> <li>Generates the REMC clock (REMCLK) to be supplied to the REMC.</li> </ul> | Generates the IWDT-dedicated clock<br>(IWDTCLK) to be supplied to the IWDT.                                                                                                                                        |

| Operating | ICLK: 32 MHz (max.)                                                                                                                                                                                                                                    | ICLK: 32 MHz (max.)                                                                                                                                                                                                |

| frequency | <ul><li>PCLKB: 32 MHz (max.)</li><li>PCLKD: 32 MHz (max.)</li></ul>                                                                                                                                                                                    | <ul><li>PCLKB: 32 MHz (max.)</li><li>PCLKD: 32 MHz (max.)</li></ul>                                                                                                                                                |

|           | PCLKD: 32 MHz (max.)     FCLK:                                                                                                                                                                                                                         | PCLKD: 32 MHz (max.)     FCLK:                                                                                                                                                                                     |

|           | <ul> <li>1 MHz to 32 MHz (for programming<br/>and erasing the ROM and E2<br/>DataFlash)</li> </ul>                                                                                                                                                     | <ul> <li>1 MHz to 32 MHz (for programming<br/>and erasing the ROM and E2<br/>DataFlash)</li> </ul>                                                                                                                 |

|           | — 32 MHz (max.) (for reading from the E2 DataFlash)                                                                                                                                                                                                    | — 32 MHz (max.) (for reading from the E2 DataFlash)                                                                                                                                                                |

|           | CACCLK: Same as clock from respective oscillators                                                                                                                                                                                                      | CACCLK: Same as clock from respective oscillators                                                                                                                                                                  |

|           | RTCSCLK: 32.768 kHz     IWDTCLK: 15 kHz                                                                                                                                                                                                                | IWDTCLK: 15 kHz                                                                                                                                                                                                    |

|           | LPTCLK: Same as clock from selected oscillator                                                                                                                                                                                                         | WETCH. TO REE                                                                                                                                                                                                      |

|           | REMCLK: Same as clock from respective oscillators                                                                                                                                                                                                      |                                                                                                                                                                                                                    |

| Item                                        | RX130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RX13T                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main clock<br>oscillator                    | <ul> <li>Resonator frequency:         <ul> <li>1 MHz to 20 MHz (VCC ≥ 2.4 V),</li> <li>1 MHz to 8 MHz (VCC &lt; 2.4 V)</li> </ul> </li> <li>External clock input frequency:         <ul> <li>20 MHz (max.)</li> </ul> </li> <li>Connectable resonator or additional circuit: ceramic resonator, crystal</li> <li>Connection pins: EXTAL, XTAL</li> <li>Oscillation stop detection function:         <ul> <li>When a main clock oscillation stop is detected, the system clock source is switched to LOCO and MTU pin can be forcedly driven to high-impedance.</li> </ul> </li> <li>Drive capacity switching function</li> </ul> | Resonator frequency: 1 MHz to 20 MHz  External clock input frequency: 20 MHz (max.) Connectable resonator or additional circuit: ceramic resonator, crystal Connection pins: EXTAL, XTAL Oscillation stop detection function: When a main clock oscillation stop is detected, the system clock source is switched to LOCO and MTU pin can be forcedly driven to high-impedance.  Drive capacity switching function |

| Sub-clock<br>oscillator                     | Resonator frequency: 32.768 kHz     Connectable resonator or additional circuit: crystal     Connection pins: XCIN and XCOUT     Drive capacity switching function                                                                                                                                                                                                                                                                                                                                                                                                                                                               | — Drive capacity switching function                                                                                                                                                                                                                                                                                                                                                                                |

| PLL circuit                                 | <ul> <li>Input clock source: Main clock</li> <li>Input pulse frequency division ratio:<br/>Selectable from 1, 2, and 4</li> <li>Input frequency: 4 MHz to 8 MHz</li> <li>Frequency multiplication ratio:<br/>Selectable from 4 to 8 (increments of 0.5)</li> <li>Oscillation frequency:<br/>24 MHz to 32 MHz (VCC ≥ 2.4 V)</li> </ul>                                                                                                                                                                                                                                                                                            | <ul> <li>Input clock source: Main clock</li> <li>Input pulse frequency division ratio:<br/>Selectable from 1, 2, and 4</li> <li>Input frequency: 4 MHz to 8 MHz</li> <li>Frequency multiplication ratio:<br/>Selectable from 4 to 8 (increments of 0.5)</li> <li>Oscillation frequency:<br/>24 MHz to 32 MHz</li> </ul>                                                                                            |

| High-speed on-<br>chip oscillator<br>(HOCO) | Oscillation frequency: 32 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Oscillation frequency: 32 MHz                                                                                                                                                                                                                                                                                                                                                                                      |

| Low-speed on-<br>chip oscillator<br>(LOCO)  | Oscillation frequency: 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Oscillation frequency: 4 MHz                                                                                                                                                                                                                                                                                                                                                                                       |

| IWDT-dedicated on-chip oscillator           | Oscillation frequency: 15 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Oscillation frequency: 15 kHz                                                                                                                                                                                                                                                                                                                                                                                      |

Table 2.9 Comparison of Clock Generation Circuit Registers

| Register | Bit        | RX130                                                                                   | RX13T                                                                |

|----------|------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| SCKCR3   | CKSEL[2:0] | Clock source select bits                                                                | Clock source select bits                                             |

|          |            | b10 b8 0 0 0: LOCO 0 0 1: HOCO 0 1 0: Main clock oscillator 0 1 1: Sub-clock oscillator | b10 b8<br>0 0 0: LOCO<br>0 0 1: HOCO<br>0 1 0: Main clock oscillator |

|          |            | 1 0 0: PLL circuit Settings other than the above are prohibited.                        | 1 0 0: PLL circuit Settings other than the above are prohibited.     |

| SOSCCR   |            | Sub-clock oscillator control register                                                   | profibiled.                                                          |

| HOFCR    | _          | High-speed on-chip oscillator forced oscillation control register                       | _                                                                    |

| CKOCR    | _          | CLKOUT output control register                                                          | _                                                                    |

| MOFCR    | MODRV21    | Main clock oscillator drive capability switch bit                                       | Main clock oscillator drive capability switch bit                    |

|          |            | VCC ≥ 2.4 V<br>0: 1 MHz to 10 MHz<br>1: 10 MHz to 20 MHz                                | 0: 1 MHz to less than 10 MHz<br>1: 10 MHz to 20 MHz                  |

|          |            | VCC < 2.4 V 0: 1 MHz to 8 MHz 1: Setting prohibited                                     |                                                                      |

# 2.6 Clock Frequency Accuracy Measurement Circuit

Table 2.10 is a comparative overview of clock frequency accuracy measurement circuits, and Table 2.11 is a comparison of clock frequency accuracy measurement circuit registers.

**Table 2.10 Comparative Overview of Clock Frequency Accuracy Measurement Circuits**

| Item                | RX130 (CAC)                             | RX13T (CAC)                                |

|---------------------|-----------------------------------------|--------------------------------------------|

| Measurement target  | The frequencies of the following clocks | The frequencies of the following clocks    |

| clocks              | can be measured:                        | can be measured:                           |

|                     | Main clock                              | Main clock                                 |

|                     | Sub-clock                               |                                            |

|                     | HOCO clock                              | HOCO clock                                 |

|                     | LOCO clock                              | LOCO clock                                 |

|                     | IWDTCLK clock                           | IWDT-dedicated clock (IWDTCLK)             |

|                     | Peripheral module clock B (PCLKB)       | Peripheral module clock B (PCLKB)          |

| Measurement         | External clock input on CACREF pin      | External clock input on CACREF pin         |

| reference clocks    | Main clock                              | Main clock                                 |

|                     | Sub-clock                               |                                            |

|                     | HOCO clock                              | HOCO clock                                 |

|                     | LOCO clock                              | LOCO clock                                 |

|                     | IWDTCLK clock                           | IWDT-dedicated clock (IWDTCLK)             |

|                     | Peripheral module clock B (PCLKB)       | Peripheral module clock B (PCLKB)          |

| Selectable function | Digital filter function                 | Digital filter function                    |

| Interrupt sources   | Measurement end interrupt               | Measurement end interrupt                  |

|                     | Frequency error interrupt               | Frequency error interrupt                  |

|                     | Overflow interrupt                      | Overflow interrupt                         |

| Low power           | Ability to specify module stop state    | Ability to transition to module stop state |

| consumption         |                                         |                                            |

| function            |                                         |                                            |

Table 2.11 Comparison of Clock Frequency Accuracy Measurement Circuit Registers

| Register | Bit       | RX130 (CAC)                                   | RX13T (CAC)                                   |

|----------|-----------|-----------------------------------------------|-----------------------------------------------|

| CACR1    | FMCS[2:0] | Measurement target clock select bits          | Measurement target clock select bits          |

|          |           |                                               |                                               |

|          |           | b3 b1                                         | b3 b1                                         |

|          |           | 0 0 0: Main clock                             | 0 0 0: Main clock                             |

|          |           | 0 0 1: Sub-clock                              |                                               |

|          |           | 0 1 0: HOCO clock                             | 0 1 0: HOCO clock                             |

|          |           | 0 1 1: LOCO clock                             | 0 1 1: LOCO clock                             |

|          |           | 1 0 0: IWDTCLK clock                          | 1 0 0: IWDT-dedicated clock (IWDTCLK)         |

|          |           | 1 0 1: Peripheral module clock B (PCLKB)      | 1 0 1: Peripheral module clock B (PCLKB)      |

|          |           | Settings other than the above are             | Settings other than the above are             |

|          |           | prohibited.                                   | prohibited.                                   |

| CACR2    | RSCS[2:0] | Measurement reference clock select            | Measurement reference clock select            |

|          |           | bits                                          | bits                                          |

|          |           | b3 b1                                         | b3 b1                                         |

|          |           | 0 0 0: Main clock                             | 0 0 0: Main clock                             |

|          |           | 0 0 1: Sub-clock oscillator                   |                                               |

|          |           | 0 1 0: HOCO clock                             | 0 1 0: HOCO clock                             |

|          |           | 0 1 1: LOCO clock                             | 0 1 1: LOCO clock                             |

|          |           | 1 0 0: IWDTCLK clock                          | 1 0 0: IWDT-dedicated clock (IWDTCLK)         |

|          |           | 1 0 1: Peripheral module clock B (PCLKB)      | 1 0 1: Peripheral module clock B (PCLKB)      |

|          |           | Settings other than the above are prohibited. | Settings other than the above are prohibited. |

# 2.7 Low Power Consumption

Table 2.12 is a comparative overview of the low power consumption functions, Table 2.13 is a comparison of procedures for entering and exiting low power consumption modes and operating states in each mode, and Table 2.14 is a comparison of low power consumption registers.

**Table 2.12 Comparative Overview of Low Power Consumption Functions**

| Item                                                           | RX130                                                                                                                                                                                                                                                                                                                                                                              | RX13T                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reducing power consumption by switching clock signals          | The frequency division ratio can be set independently for the system clock (ICLK), peripheral module clock (PCLKB), S12AD clock (PCLKD), and FlashIF clock (FCLK).                                                                                                                                                                                                                 | The frequency division ratio can be set independently for the system clock (ICLK), peripheral module clock (PCLKB), S12AD clock (PCLKD), and FlashIF clock (FCLK).                                                                                                                                                                                                                  |

| Module stop function                                           | Each peripheral module can be stopped independently by the module stop control register.                                                                                                                                                                                                                                                                                           | Each peripheral module can be stopped independently by the module stop control register.                                                                                                                                                                                                                                                                                            |

| Function for<br>transition to low<br>power consumption<br>mode | Transition to a low power consumption mode in which the CPU, peripheral modules, or oscillators are stopped is enabled.                                                                                                                                                                                                                                                            | Transition to a low power consumption mode in which the CPU, peripheral modules, or oscillators are stopped is enabled.                                                                                                                                                                                                                                                             |

| Low power consumption modes                                    | <ul><li>Sleep mode</li><li>Deep sleep mode</li><li>Software standby mode</li></ul>                                                                                                                                                                                                                                                                                                 | <ul><li>Sleep mode</li><li>Deep sleep mode</li><li>Software standby mode</li></ul>                                                                                                                                                                                                                                                                                                  |

| Function for lower operating power consumption                 | <ul> <li>Power consumption can be reduced in normal operation, sleep mode, and deep sleep mode by selecting an appropriate operating power control mode according to the operating frequency and operating voltage.</li> <li>Three operating power control modes are available         <ul> <li>High-speed operating mode</li> <li>Low-speed operating mode</li> </ul> </li> </ul> | <ul> <li>Power consumption can be reduced in normal operation, sleep mode, and deep sleep mode by selecting an appropriate operating power control mode according to the operating frequency and operating voltage.</li> <li>Two operating power control modes are available         <ul> <li>High-speed operating mode</li> <li>Middle-speed operating mode</li> </ul> </li> </ul> |

Table 2.13 Comparison of Procedures for Entering and Exiting Low Power Consumption Modes and Operating States in Each Mode

|            | Entering and Exiting Low Power Consumption Modes and               |                                       |                                       |

|------------|--------------------------------------------------------------------|---------------------------------------|---------------------------------------|

| Mode       | Operating States                                                   | RX130                                 | RX13T                                 |

| Sleep mode | Transition method                                                  | Control register                      | Control register                      |

|            |                                                                    | + instruction                         | + instruction                         |

|            | Method of cancellation other than reset                            | Interrupt                             | Interrupt                             |

|            | State after cancellation                                           | Program execution                     | Program execution                     |

|            |                                                                    | state (interrupt                      | state (interrupt                      |

|            | Main alask assillator                                              | processing)                           | processing)                           |

|            | Main clock oscillator                                              | Operation possible                    | Operation possible                    |

|            | Sub-clock oscillator                                               | Operation possible                    |                                       |

|            | High-speed on-chip oscillator                                      | Operation possible                    | Operation possible                    |

|            | Low-speed on-chip oscillator                                       | Operation possible                    | Operation possible                    |

|            | IWDT-dedicated on-chip oscillator                                  | Operation possible                    | Operation possible                    |

|            | PLL                                                                | Operation possible                    | Operation possible                    |

|            | CPU                                                                | Stopped (retained)                    | Stopped (retained)                    |

|            | RAMO                                                               | Operation possible                    | Operation possible                    |

|            | (0000 0000h to 0000 BFFFh: RX130, 0000 0000h to 0000 2FFFh: RX13T) | (retained)                            | (retained)                            |

|            | DTC                                                                | Operation possible                    | Operation possible                    |

|            | Flash memory                                                       | Operation                             | Operation                             |

|            | Independent watchdog timer (IWDT)                                  | Operation possible                    | Operation possible                    |

|            | Remote control signal receiver (REMC)                              | Operation possible                    | _                                     |

|            | Realtime clock (RTC)                                               | Operation possible                    |                                       |

|            | Low-power timer (LPT)                                              | Operation possible                    | _                                     |

|            | Voltage detection circuit (LVD)                                    | Operation possible                    | Operation possible                    |