# ISL81601

60V 双方向4スイッチ同期昇降圧コントローラ

FN9299 Rev.3.00 2018年11月21日

ISL81601 は真の双方向4スイッチ同期整流型昇降圧コントローラで、ピーク電流および平均電流を両端で検出してモニタします。入出力の電圧範囲が広いため、産業用機器、電気通信アプリケーションに適しています。

ISL81601では、昇圧モード制御にバレー電流モジュレーション、降圧モード制御にピーク電流モジュレーションを備えた独自の昇降圧制御アルゴリズムを使用しています。

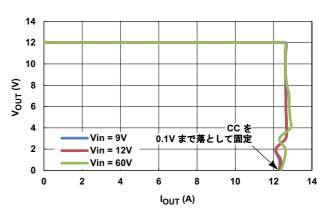

ISL81601には、入力と出力、電流と電圧の独立した4系統 の制御ループがあります。この製品ファミリは、回路の両 端に固有ピーク電流検出機能とサイクルごとの電流リ ミット機能を備えています。これらの機能により、いずれ かの端に高速過渡状態において瞬時電流を両方向で制限 することにより、高い信頼性が得られます。また、入出力 の両方の端子には電流モニタリングピンが2本あり、定電 流(CC) リミットなどのシステム管理機能を促進します。 CC動作を使って電圧を低下させることにより、過負荷状 態や短絡状態での回路の暴走を防ぐことができます。複数 の過電流保護に加えて、OVP、UVP、OTPや両端における 平均電流リミットやピーク電流リミットといった総合的 な保護機能を提供することにより、双方向および一方向操 作のどちらでも高い信頼性を確保します。このICは、省ス ペースを意識した32 Ld 5mmx5mm QFNパッケージまたは アセンブリが容易な4.4mmx9.7mm 38 Ld HTSSOPパッケー ジに組み込まれています。どちらのパッケージにも、放熱 性とノイズ耐性を改善するために EPAD を使用していま す。ISL81601はピン数も外付け部品も少なく、デフォルト で内部値が設定されているため、シンプルな電源設計の市 場への早期参入にとって理想的なソリューションです。軽 負荷での独自のDE(ダイオードエミュレーション)バース トモードでは、さまざまな負荷レベルに渡って一定の出力 リップルを持ち、スタンバイ電力消費量を大幅に低減する ことができます。

#### 関連資料

全ての関連文書の一覧は、弊社 Web サイトを参照してください。

• <u>ISL81601</u>製品ページ

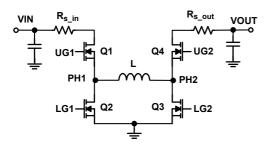

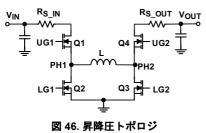

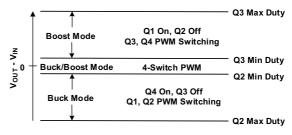

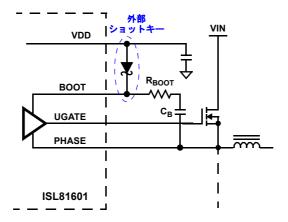

図 1. 昇降圧パワートレイントポロジ

#### 特長

- 単一インダクタ4スイッチ昇降圧コントローラ

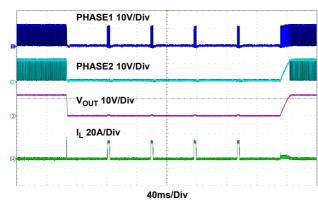

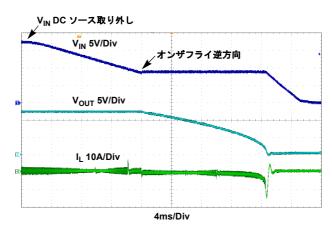

- 両端での電圧と電流の独立制御を備えたオンザフライ双方向操作

- 独自のアルゴリズムでスムーズなモード切り替え

- 適応型シュートスルー保護機能を備えたMOSFETドライバ

- 幅広い入力電圧範囲: 4.5V~60V

- 幅広い出力電圧範囲:0.8V~60V

- •SRソフトスタート付きプリバイアス出力をサポート

- プログラマブル周波数:100kHz~600kHz

- カスケードフェーズインターリービング機能による パラレル動作カレントシェアをサポート

- クロックアウトまたは周波数ディザリングを備えた 同期

- 高効率のための外部バイアスで入力 8V-36V をサポート

- 出力および入力電流モニタ

- PWMモード操作をPWM/DE/バーストモードから 選択可能

- 正確なEN/UVLOおよびPGOODインジケータ

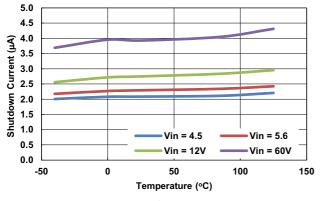

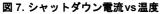

- 低シャットダウン電流: 2.7μA

- 完全な保護機能: OCP、SCP、OVP、OTP、UVP

- ・平均電流リミットとパルスバイパルスのピーク電流リミット付きデュアルレベルOCP保護

- OCP応答をヒカップモードまたは定電流モードから選択可能

- ネガティブパルスバイパルスピーク電流リミット

## アプリケーション

- バッテリ・バックアップ

- UPS/ストレージシステム

- バッテリ式産業用機器アプリケーション

- 再生可能エネルギー

- 冗長電源

- ロボットとドローン

- 医療用機器

- 建設用および産業用オートメーション

- セキュリティ監視

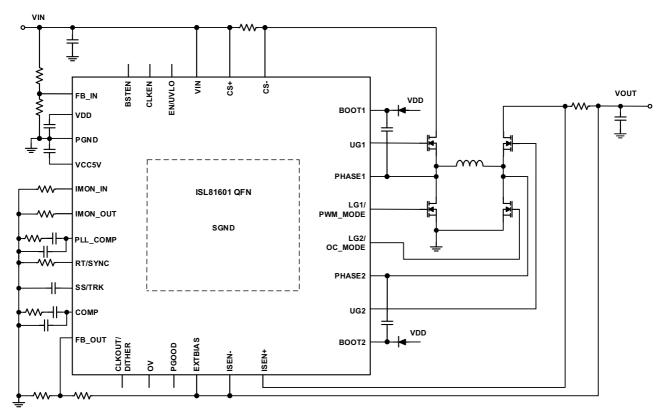

図 2. アプリケーションダイアグラム例

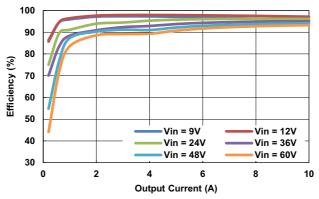

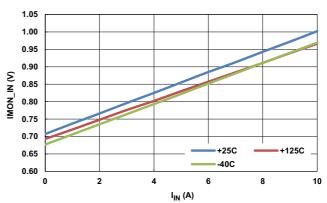

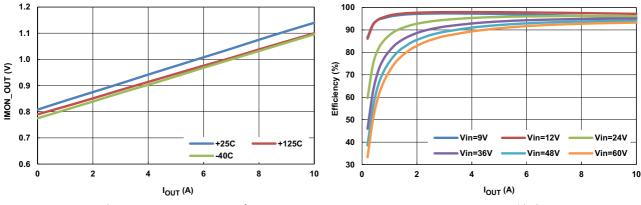

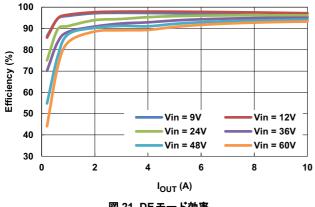

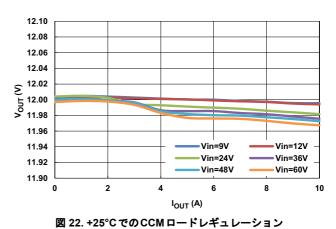

図 3. 効率(V<sub>OUT</sub>=12V、DEモード)

# 目次

| 1.   | 概要                                     | 4  |

|------|----------------------------------------|----|

| 1.1  | アプリケーション回路図例                           | 4  |

| 1.2  | ブロック図                                  |    |

| 1.3  | 注文情報                                   |    |

| 1.4  | ピン構成                                   |    |

| 1.5  | ピンの説明                                  |    |

| 1.5  | C > 00 Bit 91                          | -  |

| 2.   | 仕様                                     | 12 |

| 2.1  | 絶対最大定格                                 | 12 |

| 2.2  | 熱に関する情報                                |    |

| 2.3  | 推奨動作条件                                 |    |

| 2.4  | 電気的仕様                                  |    |

|      |                                        |    |

| 3.   | 代表的な性能曲線                               | 19 |

|      |                                        |    |

| 4.   | 機能説明                                   | 25 |

| 4.1  | 概要                                     | 25 |

| 4.2  | 内部8Vリニア・レギュレータ(VDD)、外部バイアス電源(EXTBIAS)、 |    |

|      | 5V リニア・レギュレータ (VCC5V) 25               |    |

| 4.3  | イネーブル (EN/UVLO) およびソフトスタート操作           | 25 |

| 4.4  | トラッキング動作                               |    |

| 4.5  | 制御ループ                                  |    |

| 4.6  | <br>昇降圧変換トポロジおよび制御アルゴリズム               |    |

| 4.7  | 軽負荷時の効率向上                              |    |

| 4.8  | プリバイアス・パワーアップ                          |    |

| 4.9  | 周波数の選択                                 |    |

| 4.10 | · · · · · · · · · · · · · · · · · · ·  |    |

| 4.11 |                                        |    |

| 4.12 |                                        |    |

| 4.13 |                                        |    |

| 4.14 |                                        |    |

|      |                                        |    |

| 5.   | 保護回路                                   | 39 |

| 5.1  | 入力アンダーボルテージ・ロックアウト                     | 39 |

| 5.2  | VCC5Vパワーオン・リセット(POR)                   |    |

| 5.3  | 過電流保護(OCP)                             |    |

| 5.4  | 過電圧保護                                  |    |

| 5.5  | 過熱保護                                   |    |

|      |                                        |    |

| 6.   | レイアウトのガイドライン                           | 41 |

| 6.1  | レイアウトの考慮事項                             | 41 |

| 6.2  | 一般的なEPAD設計検討事項                         | 42 |

|      |                                        |    |

| 7.   | 外部部品選択ガイドライン                           | 43 |

| 7.1  | MOSFETの検討事項                            | 43 |

| 7.2  | インダクタの選択                               | 44 |

| 7.3  | 出力コンデンサの選択                             |    |

| 7.4  | 入力コンデンサの選択                             |    |

|      |                                        |    |

| 8.   | 改定履歴                                   | 46 |

|      |                                        |    |

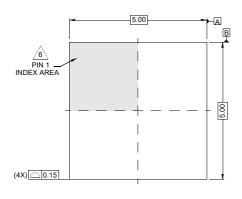

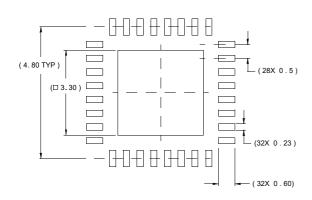

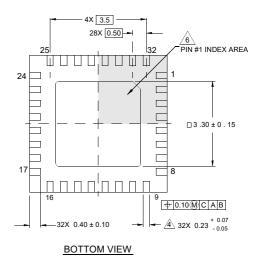

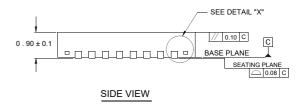

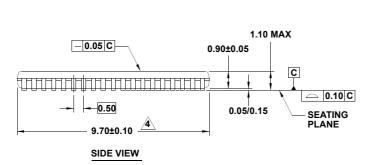

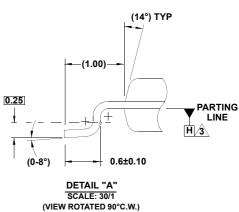

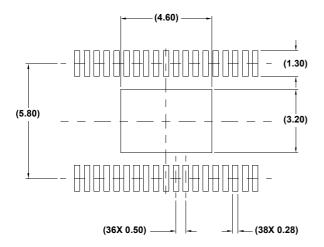

| 9.   | パッケージの外形図                              | 47 |

# 1. 概要

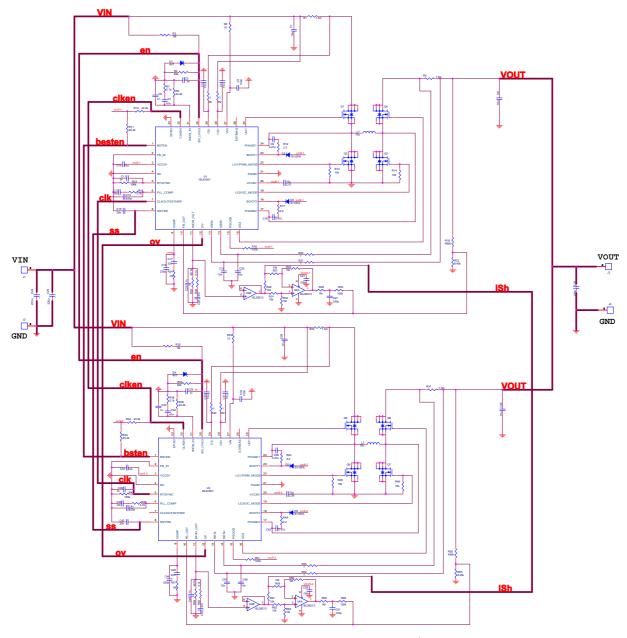

# 1.1 アプリケーション回路図例

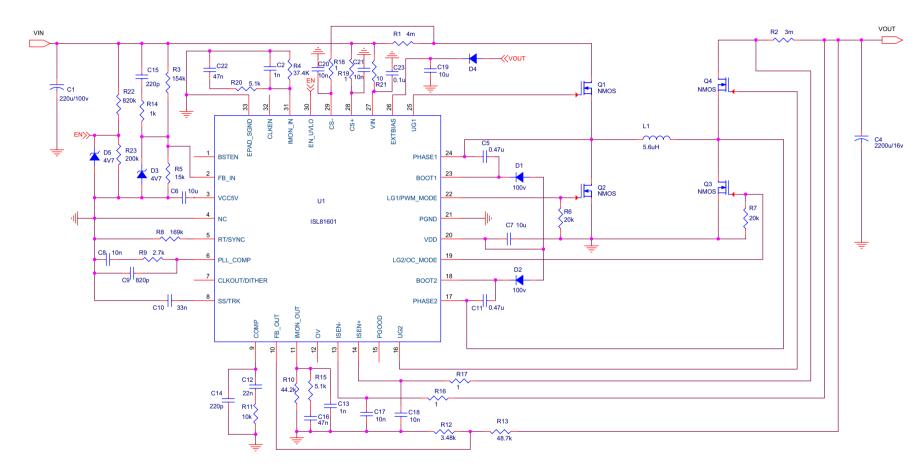

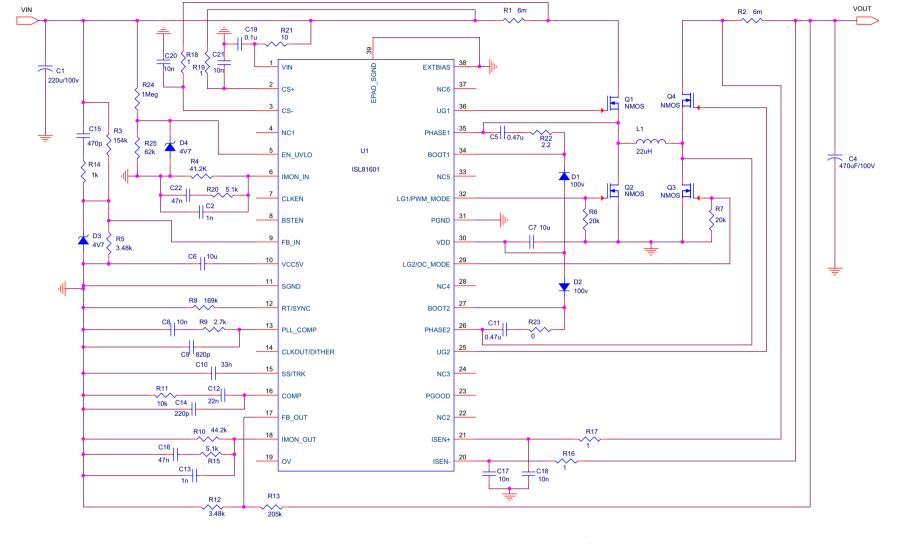

図 4. ISL81601EVAL1Z (V<sub>IN</sub>=9V~60V、V<sub>OUT</sub>=12V、I<sub>OUT</sub>=10A)評価ポード回路図

1. 姨要

図 5. ISL81601EVAL2Z ( $V_{IN}$ =32V  $\sim$  60V、 $V_{OUT}$ =48V、 $I_{OUT}$ =5A)評価ボード回路図

# 1.2 ブロック図

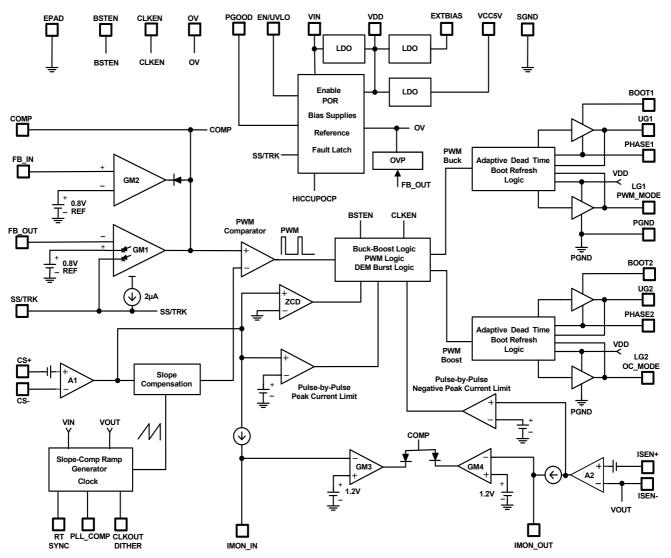

図 6. ブロック図

### 1.3 注文情報

| 製品型番<br>( <u>Notes 2, 3</u> ) | 部品マーキング    | 温度範囲 (°C)         | テープ、リール (ユニット)<br>( <u>Note 1</u> ) | パッケージ<br>(RoHS準拠) | パッケージ<br>Dwg.# |

|-------------------------------|------------|-------------------|-------------------------------------|-------------------|----------------|

| ISL81601FRZ                   | 81601 FRZ  | -40 <b>~</b> +125 | -                                   | 32 Ld 5x5 QFN     | L32.5x5B       |

| ISL81601FRZ-T                 | 81601 FRZ  | -40 <b>~</b> +125 | 6k                                  | 32 Ld 5x5 QFN     | L32.5x5B       |

| ISL81601FRZ-T7A               | 81601 FRZ  | -40 <b>~</b> +125 | 250                                 | 32 Ld 5x5 QFN     | L32.5x5B       |

| ISL81601FVEZ                  | 81601 FVEZ | -40 ~ +125        | -                                   | 38 Ld HTSSOP      | M38.173C       |

| ISL81601FVEZ-T                | 81601 FVEZ | -40 ~ +125        | 2.5k                                | 38 Ld HTSSOP      | M38.173C       |

| ISL81601FVEZ-T7A              | 81601 FVEZ | -40 ~ +125        | 250                                 | 38 Ld HTSSOP      | M38.173C       |

| ISL81601EVAL1Z                | QFN用評価ボート  | *                 |                                     |                   | •              |

| ISL81601EVAL2Z                | HTSSOP用評価が | <b>≒</b> −ド       |                                     |                   |                |

#### Notes:

- 1. リールの詳細な仕様はTB347を参照してください。

- 2. これらの鉛フリーのプラスチック・パッケージ製品には、特殊な鉛フリーの材料一式、成形コンパウンド/ダイ・アタッチ材料、 艶消しスズ100% プレートプラスアニールを採用しています (終端仕上げはe3で、RoHS準拠かつSnPbおよび鉛フリー・ハン ダ付け作業の両方と互換性があります)。インターシルの鉛フリー製品は、IPC/JEDEC J STD-020 の鉛フリー要件を満たす、 またはそれを超える鉛フリー・ピークリフロー温度でMSLに分類されています。

- 3. 耐湿性レベル (MSL) については ISL81601 製品の詳細ページを参照してください。MSL に関する詳細は IB363 を参照してください。

| No. of the contract of the con |                              |                     |      |      |        |                                 |      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|------|------|--------|---------------------------------|------|--|

| 製品型番                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>IN</sub> 動作/最大<br>(V) | V <sub>DD</sub> (V) | 電流制御 | 並列動作 | ディザリング | 取り外したピン                         | ピン12 |  |

| ISL81601                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60/70                        | 8                   | 双方向  | あり   | あり     | なし                              | OV   |  |

| ISL81401                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40/45                        | 5.3                 | 双方向  | あり   | あり     | BSTEN, CLKEN                    | MODE |  |

| ISL81401A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40/45                        | 5.3                 | 一方向  | なし   | なし     | BSTEN, CLKEN,<br>FIB IN. CLKOUT | MODE |  |

表 1. 当製品ファミリにおける主な機能の違い

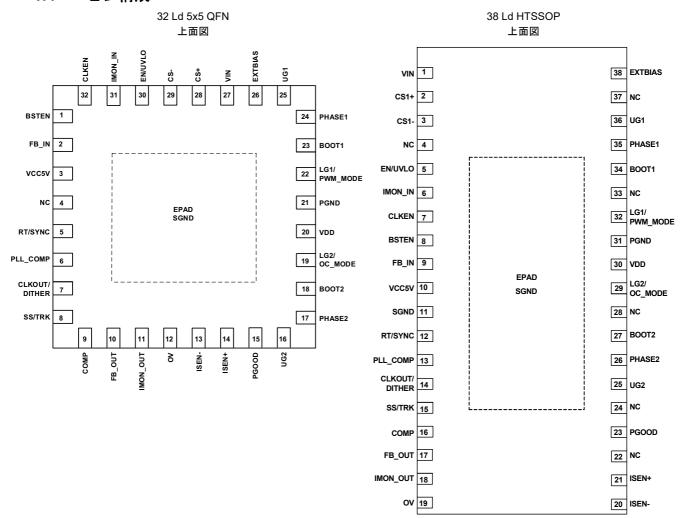

# 1.4 ピン構成

# 1.5 ピンの説明

| ピン番号<br>(QFN) | ピン番号<br>(HTSSOP)         | ピン名               | 機能                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|--------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | 8                        | BSTEN             | DEバーストモード有効信号です。PWMモードおよびDEモードのときは内部抵抗250kにより信号を5Vにプルアップします。バーストモードではローレベルになります。プルダウン MOSFET r <sub>DS(ON)</sub> 抵抗は約4.5kです。全てのチップをバーストモードで同期して動作させるためには、マルチチップ並列動作アプリケーションにてこのピンを互いに接続します。                                                                                                                                                                                            |

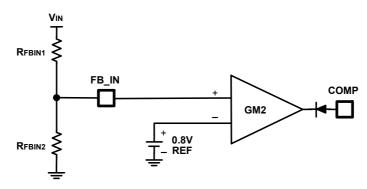

| 2             | 9                        | FB_IN             | 逆方向動作用の入力電圧フィードバックピンです。抵抗分割器を使用して入力電圧をこのピンに戻します。入力電圧が低下し、このピン電圧が0.8V未満まで下がると、内部制御ループがデューティ・サイクルを低減し、出力側から入力側へのシンク電流でピン電圧が0.8Vになるように調整します。<br>ピン電圧が0.3V未満になると逆方向動作しなくなります。<br>逆方向動作機能を使用しないときは、このピンをVCC5VまたはSGNDに接続します。インターリービング並列処理用にフェーズシフトも設定されます。                                                                                                                                   |

| 3             | 10                       | VCC5V             | 5Vの内部リニア・レギュレータの出力です。ICに出力バイアスを供給します。VCC5Vピンにごく近い場所に4.7μF以上のセラミックコンデンサを接続し、常時SGNDにデカップリングする必要があります。                                                                                                                                                                                                                                                                                    |

| 4             | 4、22、<br>24、28、<br>33、37 | NC                | 非接続ピンです。                                                                                                                                                                                                                                                                                                                                                                               |

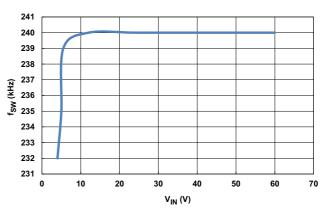

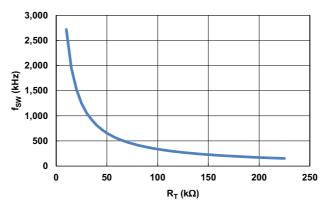

| 5             | 12                       | RT/SYNC           | このピンとグラウンド間の抵抗を使ってデフォルトのスイッチング周波数を100kHz~600kHz の範囲に設定します。PWMコントローラのスイッチング周波数のデフォルト値は、 <u>式 1</u> の抵抗R <sub>T</sub> で定義されます。 $(式 1) \qquad \qquad R_T = \left(\frac{34.7}{f_{SW}} - 4.78\right) \cdot k\Omega$ ここで、 $f_{SW}$ はスイッチング周波数で、単位はMHzです。                                                                                                                                     |

|               |                          |                   | このピンをVCC5Vに接続すると、f <sub>SW</sub> は120kHzに設定されます。GNDに接続すると、f <sub>SW</sub> は575kHzに設定されます。<br>このピンに外部クロック信号を入力すると、内部周波数が外部クロック周波数と同期します。                                                                                                                                                                                                                                                |

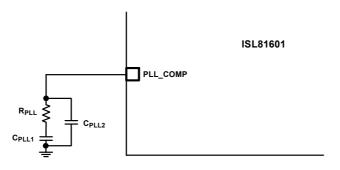

| 6             | 13                       | PLL_COMP          | 内部PLL 回路の補償ピンです。 <u>34ページの図 52</u> に示す補償ネットワークが必要です。<br>R <sub>PLL</sub> (2.7kΩ)、C <sub>PLL1</sub> (10nF)、C <sub>PLL2</sub> (820pF) が推奨されます。                                                                                                                                                                                                                                           |

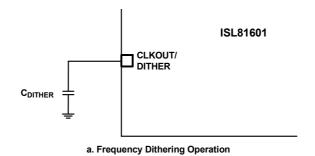

| 7             | 14                       | CLKOUT/<br>DITHER | デュアルファンクションピンです。このピンにコンデンサが接続されていない場合は、他の ISL81601と同期するクロック信号を提供します。クロック信号のフェーズシフトは、FB_IN およびIMON_INピン電圧で設定されます。このピンにコンデンサを接続するとクロック出力機能が無効になり、ソフトスタート前の周波数ディザリング機能が有効になります。このコンデンサは内部電流源を使って充放電されます。ピンの電圧はランプアップ、ランプダウンします。その発振周波数は抵抗R <sub>T</sub> で設定された公称周波数の-15%から+15%の間で変調します。外部同期モードのとき、またはRTピンが開放または短絡されているときは、周波数ディザリング機能が無効になります。                                            |

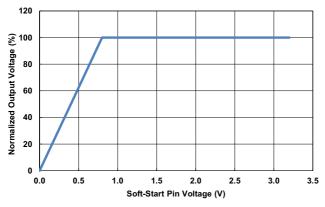

| 8             | 15                       | SS/TRK            | デュアルファンクションピンです。ソフトスタート制御に使用するには、このピンからソフトスタートコンデンサを介してグランドに接続します。安定化された2µAソフトスタート電流がソフトスタートコンデンサを充電します。ソフトスタートコンデンサの値で出力電圧の立ち上がり時間を設定します。<br>トラッキング制御に使用すると、マスタとして外部電源レールを設定し、抵抗分割器を使ってマスタ電源の出力電圧をこのピンに供給します。出力電圧はマスタ電源電圧に追従します。                                                                                                                                                      |

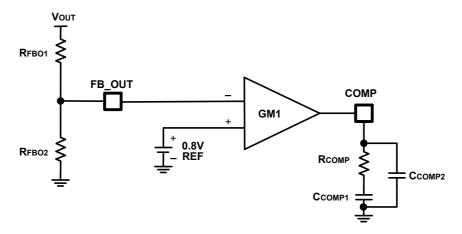

| 9             | 16                       | COMP              | 電圧エラー・GMアンプの出力です。内部電流ループの基準値を設定します。フィードバック補償ネットワークは、COMPピンとSGNDピンの間に接続されます。COMPピンを1V未満までプルダウンすると、PWMのデューティ・サイクルは0%まで下がります。                                                                                                                                                                                                                                                             |

| 10            | 17                       | FB_OUT            | 出力電圧のフィードバック入力用です。FB_OUTピンを出力とSGNDとの間にある抵抗分割器に接続すると、出力電圧を調整できます。FB_OUTピン電圧は、内部リファレンス値0.8Vに合わせて調節されます。                                                                                                                                                                                                                                                                                  |

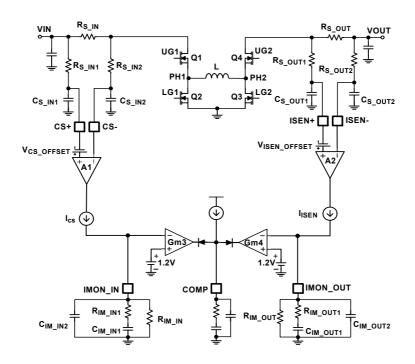

| 11            | 18                       | IMON_OUT          | 出力カレントモニタです。このピンから出力される電流は、ISEN+ピンとISEN-ピンの間の差動電圧に比例します。抵抗とコンデンサのネットワークをピンとSGNDの間に接続すると、ピン電圧が出力電流の平均値に比例します。ピン電圧が1.2Vに到達すると内部平均電流リミットループが出力電圧を抑制します。また、定電流OCPモードに設定されていると出力電流が一定になり、ヒカップOCPモードに設定されているとコンバータが遮断されます。DEバーストモードでは、このピン電圧が850mV未満であればコントローラがバーストモードになります。このピン電圧が880mVを上回るとコントローラがバーストモードから抜けます。このピンの抵抗を大きくして、負荷なしの状態で電圧が880mVを上回るように設定すると、コントローラはバースト動作することなくDEモードで動作します。 |

| ピン番号<br>(QFN) | ピン番号<br>(HTSSOP) | ピン名              | 機能                                                                                                                                                                                                                                                          |

|---------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12            | 19               | OV               | OVPコンパレータ出力信号です。通常操作のとき、内部抵抗250kにより信号をGNDにプルダウンします。出力OVPがトリップする場合はハイレベルにプルアップします。プルアップ MOSFET r <sub>DS(ON)</sub> 抵抗は約4.5kです。マルチチップ並列動作アプリケーションにてこのピンを互いに接続すると、全てのチップがOVPリアクションに同期して動作します。                                                                  |

| 13            | 20               | ISEN-            | 出力電流検出信号のマイナス側入力ピンです。                                                                                                                                                                                                                                       |

| 14            | 21               | ISEN+            | 出力電流検出信号のプラス側入力ピンです。                                                                                                                                                                                                                                        |

| 15            | 23               | PGOOD            | 出力電圧のステータスを示すために使用するオープンドレインロジック出力です。出力が公称電圧の±10%の範囲外にあるか、ENピンがローレベルになっていると、このピンがローレベルになります。                                                                                                                                                                |

| 16            | 25               | UG2              | 昇圧PWM信号で制御されたハイサイドMOSFETゲートドライバ出力です。                                                                                                                                                                                                                        |

| 17            | 26               | PHASE2           | 昇圧コンバータのフェーズノード接続です。このピンは、ハイサイド側のMOSFETのソース、<br>出力フィルタ・インダクタ、昇圧コンバータのローサイド側のMOSFETのドレインの連結部に<br>接続されます。                                                                                                                                                     |

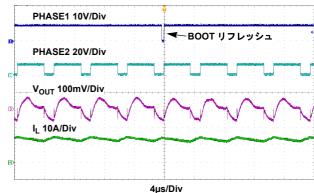

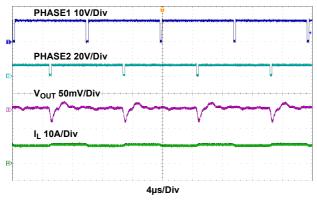

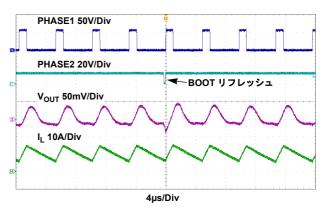

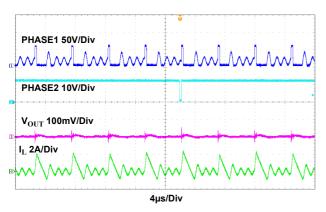

| 18            | 27               | BOOT2            | 昇圧ハイサイドドライバ用のバイアスを供給するブートストラップピンです。ブートストラップ・コンデンサの正極をこのピンに接続します。このピンとVDDの間にブートストラップダイオードを接続すると、ハイサイドドライバにバイアスがかかります。BOOT2とPHASE2の間の電圧は内部モニタされています。スイッチングのない状態で電圧が5.95Vまで下がると、最小オフタイムパルスが出力されてUG2をオフに、LG2をオンにしてブートストラップコンデンサをリフレッシュし、ハイサイドドライバのバイアス電圧を維持します。 |

| 19            | 29               | LG2/<br>OC_MODE  | 昇圧PWM信号およびOCPモード設定ピンで制御されたローサイドMOSFETゲートドライバ出力です。OCPモードの設定にはピンとグラウンドの間に接続された抵抗を使用し、設定はソフトスタートの前の初期段階で行います。その初期段階では、ピンから10µAの電流を出力してピンの電圧を設定します。ピン電圧が0.3V未満のときOCPは定電流モードに設定されます。ピン電圧が0.3Vを超えるときOCPはヒカップモードに設定されます。                                           |

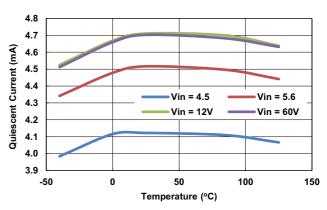

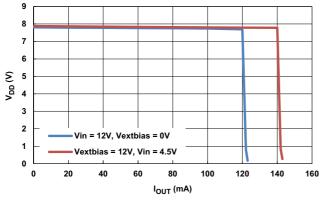

| 20            | 30               | VDD              | VINまたはEXTBIASのいずれかから供給される8V内部リニア・レギュレータの出力です。この出力では、IC、ローサイド・ドライバ、およびハイサイド・ドライバのブート回路用のバイアスを供給します。VDDピンにごく近い場所に4.7μF以上のセラミックコンデンサを接続し、常時PGNDにデカップリングしてください。                                                                                                 |

| 21            | 31               | PGND             | 電源グラウンド接続用です。このピンはローサイド側MOSFETのソースとVDDデカップリング・コンデンサの負極(-)に接続します。                                                                                                                                                                                            |

| 22            | 32               | LG1/<br>PWM_MODE | 降圧PWM信号およびPWMモード設定ピンで制御されたローサイドMOSFETゲートドライバ出力です。PWMモードの設定にはピンとグラウンドの間に接続された抵抗を使用し、設定はソフトスタートの前の初期段階で行います。その初期段階では、ピンから10µAの電流を出力してピンの電圧を設定します。ピン電圧が0.3V未満のときコンバータは強制PWMモードに設定されます。ピン電圧が0.3V超のときコンバータはDEモードに設定されます。                                         |

| 23            | 34               | BOOT1            | 降圧ハイサイドドライバ用のバイアスを供給するブートストラップピンです。ブートストラップ・コンデンサの正極をこのピンに接続します。このピンとVDDの間にブートストラップダイオードを接続すると、ハイサイドドライバにバイアスがかかります。BOOT1とPHASE1の間の電圧は内部モニタされています。スイッチングのない状態で電圧が5.95Vまで下がると、最小オフタイムパルスが出力されてUG1をオフに、LG1をオンにしてブートストラップコンデンサをリフレッシュし、ハイサイドドライバのバイアス電圧を維持します。 |

| 24            | 35               | PHASE1           | 降圧コンバータのフェーズノード接続です。このピンは、ハイサイド側のMOSFETのソース、<br>出力フィルタ・インダクタ、降圧コンバータのローサイド側のMOSFETのドレインの連結部に<br>接続します。                                                                                                                                                      |

| 25            | 36               | UG1              | 降圧PWM信号によって制御されるハイサイドMOSFETゲートドライバ出力です。                                                                                                                                                                                                                     |

| 26            | 38               | EXTBIAS          | オプションのVDD LDO用の外部バイアス入力です。EXTBIAS電圧が7.5Vを超えると、内部スイッチによりVIN LDOが切断されます。使用時には、このピンとグラウンドの間に10µFセラミック・コンデンサを接続してグラウンドから切り離します。使用しないときはこのピンをグラウンドに接続してください。このピンをフロートにしないでください。                                                                                  |

| 27            | 1                | VIN              | 5-10 $\Omega$ の抵抗を使用してこのピンと入力レールを接続してください。こうすることでVDD用の内部LDOに電源が供給されます。小容量のセラミック・コンデンサ $(10nF\sim1\mu F)$ を使ってこのピンとグラウンドの間をデカップリングします。                                                                                                                       |

| 28            | 2                | CS+              | 入力電流検出信号のプラス側入力ピンです。                                                                                                                                                                                                                                        |

| 29            | 3                | CS-              | 入力電流検出信号のマイナス側入力ピンです。                                                                                                                                                                                                                                       |

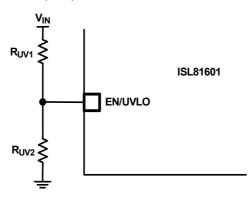

| 30            | 5                | EN/<br>UVLO      | このピンを使うと、有効/無効と正確なUVLO機能を設定できます。このピンをグラウンドに<br>プルダウンすると出力が無効になります。このピンの電圧が1.3Vに達するとVDDとVCC5V<br>LDOがアクティブになります。このピンの電圧が1.8Vに達するとPWMモジュレータが有効に<br>なります。このピンがフロートの場合、内部プルアップによりデフォルトで有効になります。                                                                 |

| ピン番号<br>(QFN) | ピン番号<br>(HTSSOP) | ピン名          | 機能                                                                                                                                                                                                                                                                                               |

|---------------|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31            | 6                | IMON_IN      | 入力カレントモニタです。このピンから出力される電流は、CS+ピンとCS-ピンの間の差動電圧に比例します。抵抗とコンデンサのネットワークをこのピンとSGNDの間に接続すると、入力電流の平均値に比例したピン電圧が発生します。ピン電圧が1.2Vに達すると、内部平均電流リミットループにより出力電圧が抑制され、定電流OCPモードが設定されているときは入力電流が一定になり、ヒカップOCPモードがセットされているときはコンバータが遮断されます。入力カレントモニタ機能を使用しない場合はこのピンをVCC5VまたはSGNDに接続してインターリービング並列動作用のフェーズシフトを設定します。 |

| 32            | 7                | CLKEN        | DEモードバースト動作オフ状態の有効信号です。PWMモードのとき、および、DEモードと<br>バーストモードのとき、内部抵抗250kにより信号を5Vにプルアップします。バーストモード<br>がオフのときはローレベルになります。プルダウンMOSFET r <sub>DS(ON)</sub> 抵抗は約4.5kです。マル<br>チチップ並列動作アプリケーションにて、全てのチップをバースト動作に同期して動作させる<br>ときは、このピンを互いに接続します。                                                               |

| -             | 11               | SGND<br>EPAD | 全回路を制御するための小信号コモングラウンドです。このピンを含む経路は高電流グラウンド(PGND)と切り離してください。チップ周辺にノイズの高い電流がなく共有できるベタグラウンド層があれば、そこにSGNDとPGNDを接続できます。このピンを使って全ての電圧を測定します。 EPADはグラウンド電位です。EPADはSGNDに内部接続されています。ただし、熱に関する性能やノイズ耐性を向上するため、EPADをグラウンドプレーンに直接はんだ付けすることを強くお勧めします。                                                        |

# 2. 仕様

# 2.1 絶対最大定格

| パラメータ                                                                                                  | 最小値                      | 最大値                   | 単位 |

|--------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|----|

| VCC5V、EN/UVLO、FB_IN とGNDとの間                                                                            | -0.3                     | +5.9                  | V  |

| VDDとGNDとの間                                                                                             | -0.3                     | +9                    | V  |

| EXTBIASとGNDとの間                                                                                         | -0.3                     | +40                   | V  |

| VIN、CS+、CS-、ISEN+、ISEN-とGNDとの間                                                                         | -0.3                     | +70                   | V  |

| BOOT1、2/UG1、2とPHASE1、2との間                                                                              | -0.3                     | V <sub>DD</sub> + 0.3 | V  |

| PHASE1、2とGNDとの間                                                                                        | -5 (<20ns)/<br>-0.3 (DC) | +70                   | V  |

| FB_OUT、SS/TRK、COMP、RT/SYNC、PLL_COMP、<br>CLKOUT/DITHER、BSTEN、CLKEN、OV、PGOOD、IMON_IN、<br>IMON_OUTとGNDとの間 | -0.3                     | VCC5V -0.3            | V  |

| LG1/PWM_MODE、LG2/OC_MODEとGNDとの間                                                                        | -0.3                     | V <sub>DD</sub> + 0.3 | V  |

| CS+とCS-との間、およびISEN+とISEN-との間                                                                           | -0.3                     | +0.3                  | V  |

| VCC5V、VDD GND との短絡時間                                                                                   |                          | 1                     | s  |

| ESD定格                                                                                                  |                          | 値                     | 単位 |

| 人体モデル(JS-001-2017に従いテスト)                                                                               |                          | 2                     | kV |

| 機械モデル(JESD22-A115Cに従いテスト)                                                                              | 150                      |                       | V  |

| 荷電デバイス・モデル(JS-002-2014に従いテスト)                                                                          |                          | 1.5                   | kV |

| ラッチアップ(JESD78EクラスII、レベルAに従いテスト、+125°C(T <sub>J</sub> ))                                                |                          | 100                   | mA |

注:長期間にわたって、最大定格またはそれに近い状態で動作することは避けてください。このような状況に置かれると、製品の信頼性に悪影響を及ぼし、保証の対象外の障害を引き起こす恐れがあります。

# 2.2 熱に関する情報

| 熱抵抗(標準値)                                        | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------------------------|------------------------|------------------------|

| 32 Ld QFNパッケージ( <u>Notes 4</u> 、 <u>5</u> )     | 29                     | 1.2                    |

| 38 Ld HTSSOP パッケージ( <u>Notes 4</u> , <u>5</u> ) | 29                     | 2                      |

#### Notes:

4.  $\theta_{JA}$  の測定は、「ダイレクト・アタッチ」機能を備えた高効率の熱伝導テストボードに搭載された部品を使用して自由空間で行います。  $\underline{\text{TB379}}$  を参照。

5.  $\theta_{JC}$ については、「ケースの温度」はパッケージ下側のメタルパッド露出部分の中央位置の温度を表します。

| パラメータ           | 最小値 | 最大値       | 単位 |

|-----------------|-----|-----------|----|

| 接続部温度           | -55 | +150      | °C |

| 動作温度            | -40 | +125      | °C |

| 保存温度範囲          | -65 | +150      | °C |

| 鉛フリー・リフロープロファイル | 1   | 「B493を参照。 |    |

# 2.3 推奨動作条件

| Parameter                    | Minimum | Maximum | Unit |

|------------------------------|---------|---------|------|

| Temperature                  | -40     | +125    | °C   |

| VIN to GND                   | 4.5     | 60      | V    |

| VCC5V, EN/UVLO, FB_IN to GND | 0       | 5.25    | V    |

| VDD to GND                   | 0       | 8.3     | V    |

| EXTBIAS to GND               | 0       | 36      | V    |

### 2.4 電気的仕様

特に記載のない場合、下記の使用条件が推奨されます。 $\frac{6\,\text{^{\prime}}-\text{^{\prime}}\text{^{\prime}}}{\text{^{\prime}}}$  「ブロック図」と $\frac{4\,\text{^{\prime}}-\text{^{\prime}}\text{^{\prime}}}{\text{^{\prime}}}$  「アプリケーション回路図例」を参照してください。特に記載のない場合、 $T_A$ = +25°Cでの標準的な値は、 $V_{IN}$ = 4.5V  $\sim$  60V、またはVDD=8V±10%、 $C_{IN}$ - 4.7 $\mu$ F、 $T_A$  = -40°C  $\sim$  +125°Cです。太字で表示された箇所には、動作温度範囲として-40°C  $\sim$  +125°Cが適用されます。

| Parameter                                                | Symbol               | Test Conditions                                                | Min<br>( <u>Note 6</u> ) | Тур  | Max<br>(Note 6) | Unit |

|----------------------------------------------------------|----------------------|----------------------------------------------------------------|--------------------------|------|-----------------|------|

| V <sub>IN</sub> Supply                                   |                      |                                                                |                          |      | 1               |      |

| Input Voltage Range                                      | V <sub>IN</sub>      |                                                                | 4.5                      |      | 60.0            | V    |

| V <sub>IN</sub> Supply Current                           |                      |                                                                |                          |      | 1               |      |

| Shutdown Current (Note 7)                                | I <sub>VINQ</sub>    | EN = 0V, PGOOD is floating                                     |                          | 2.7  | 6.0             | μΑ   |

| Operating Current (Note 8)                               | I <sub>VINOP</sub>   | PGOOD is floating                                              |                          | 4.7  | 6.0             | mA   |

| VCC5V Supply                                             |                      | -                                                              |                          |      | <u> </u>        |      |

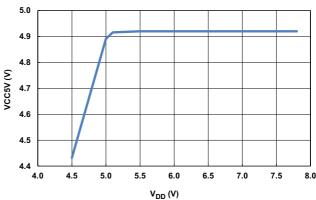

| Internal LDO Output Voltage                              | V <sub>CC5V</sub>    | V <sub>IN</sub> = 8V, I <sub>L</sub> = 0mA                     | 4.70                     | 5.10 | 5.25            | V    |

|                                                          |                      | V <sub>IN</sub> = 60V, I <sub>L</sub> = 0mA                    | 4.70                     | 5.10 | 5.25            | V    |

|                                                          |                      | V <sub>IN</sub> = 4.5V, I <sub>L</sub> = 5mA                   | 4.00                     | 4.25 |                 | V    |

|                                                          |                      | V <sub>IN</sub> > 5.6V, I <sub>L</sub> = 10mA                  | 4.65                     | 5.00 |                 | V    |

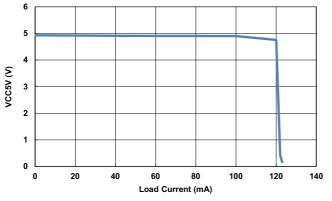

| Maximum Supply Current of Internal LDO                   | I <sub>VCC_MAX</sub> | V <sub>VCC5V</sub> = 0V, V <sub>IN</sub> = 8V                  |                          | 120  |                 | mA   |

| V <sub>DD</sub> Supply                                   |                      | -                                                              |                          |      | <u> </u>        |      |

| Internal LDO Output Voltage                              | $V_{DD}$             | V <sub>IN</sub> = 12V, EXTBIAS = 0V, I <sub>L</sub> = 0mA      | 7.5                      | 8.0  | 8.3             | V    |

|                                                          |                      | $V_{IN}$ = 60V, EXTBIAS = 0V, $I_L$ = 0mA                      | 7.5                      | 8.0  | 8.3             | V    |

|                                                          |                      | V <sub>IN</sub> = 4.5V, EXTBIAS = 12V, I <sub>L</sub> = 0mA    | 7.5                      | 8.0  | 8.3             | V    |

|                                                          |                      | $V_{IN}$ = 60V, EXTBIAS = 12V, $I_L$ = 0mA                     | 7.6                      | 8.0  | 8.3             | V    |

|                                                          |                      | $V_{IN}$ = 4.5V, EXTBIAS = 0V, $I_L$ = 30mA                    | 3.9                      | 4.3  |                 | V    |

|                                                          |                      | $V_{IN}$ = 4.5V, EXTBIAS = 7.8V, $I_L$ = 30mA                  | 7.4                      | 7.6  |                 | V    |

|                                                          |                      | $V_{IN}$ > 8.6V, EXTBIAS = 0V, $I_L$ = 75mA                    | 7.30                     | 7.85 |                 | V    |

|                                                          |                      | V <sub>IN</sub> = 4.5V, EXTBIAS > 9.0V, I <sub>L</sub> = 75mA  | 7.30                     | 7.85 |                 | V    |

| Maximum Supply Current of                                | I <sub>VDD_MAX</sub> | V <sub>VDD</sub> = 0V, EXTBIAS = 0V, V <sub>IN</sub> = 12V     |                          | 120  |                 | mA   |

| Internal LDO                                             |                      | V <sub>VDD</sub> = 4.5V, EXTBIAS = 12V, V <sub>IN</sub> = 4.5V |                          | 160  |                 | mA   |

| EXTBIAS Supply                                           |                      |                                                                | 1                        |      |                 | 1    |

| Switch Over Threshold Voltage,<br>Rising                 | $V_{EXT\_THR}$       | EXTBIAS voltage                                                | 7.10                     | 7.38 | 7.55            | V    |

| Switch Over Threshold Voltage,<br>Falling                | V <sub>EXT_THF</sub> | EXTBIAS voltage                                                | 6.60                     | 6.85 | 7.10            | V    |

| V <sub>IN</sub> UVLO                                     |                      | ,                                                              | 1                        |      |                 |      |

| V <sub>IN</sub> Rising UVLO Threshold ( <u>Note 10</u> ) | V <sub>UVLOTHR</sub> | V <sub>IN</sub> voltage, 0mA on VCC5V and VDD                  | 3.20                     | 3.50 | 3.85            | V    |

| V <sub>IN</sub> Falling UVLO Threshold                   | V <sub>UVLOTHF</sub> | V <sub>IN</sub> voltage, 0mA on VCC5V and VDD                  | 3.0                      | 3.2  | 3.4             | V    |

| VCC5V Power-On Reset                                     |                      | •                                                              |                          |      |                 | •    |

| VCC5V Rising POR Threshold                               | V <sub>PORTHR</sub>  | VCC5V voltage, 0mA on VCC5V and VDD                            | 3.7                      | 4.0  | 4.3             | V    |

特に記載のない場合、下記の使用条件が推奨されます。6ページの「ブロック図」と4ページの「アプリケーション回路図例」を参照してください。特に記載のない場合、 $T_A$ = +25°Cでの標準的な値は、 $V_{IN}$ = 4.5V ~ 60V、またはVDD=8V±10V、C\_VCC5V= 4.7VF、V0V0V0V125°Cです。太字で表示された箇所には、動作温度範囲として-40°C ~+125°Cが適用されます。(続き)

| Parameter                                                  | Symbol                 | Test Conditions                         | Min<br>( <u>Note 6</u> ) | Тур   | Max<br>(Note 6) | Unit |

|------------------------------------------------------------|------------------------|-----------------------------------------|--------------------------|-------|-----------------|------|

| VCC5V Falling POR Threshold                                | $V_{PORTHF}$           | VCC5V voltage, 0mA on VCC5V and VDD     | 3.30                     | 3.55  | 3.75            | V    |

| EN/UVLO Threshold                                          |                        |                                         |                          |       | 1               |      |

| EN Rise Threshold                                          | V <sub>ENSS_THR</sub>  | V <sub>IN</sub> > 5.6V                  | 0.75                     | 1.05  | 1.30            | V    |

| EN Fall Threshold                                          | V <sub>ENSS_THF</sub>  | V <sub>IN</sub> > 5.6V                  | 0.60                     | 0.90  | 1.10            | V    |

| EN Hysteresis                                              | V <sub>ENSS_HYST</sub> | V <sub>IN</sub> > 5.6V                  | 70                       | 150   | 300             | mV   |

| UVLO Rise Threshold                                        | V <sub>UVLO_THR</sub>  | V <sub>IN</sub> > 5.6V                  | 1.77                     | 1.80  | 1.83            | V    |

| UVLO Hysteresis Current                                    | I <sub>UVLO_HYST</sub> | V <sub>IN</sub> = 12V, EN/UVLO = 1.815V | 2.5                      | 4.2   | 5.5             | μΑ   |

| Soft-Start Current                                         |                        | ,                                       |                          | I     |                 |      |

| SS/TRK Soft-Start Charge Current                           | I <sub>SS</sub>        | SS/TRK = 0V                             |                          | 2.00  |                 | μΑ   |

| Default Internal Minimum Soft-Startin                      | ng                     | ,                                       |                          | I     |                 |      |

| Default Internal Output Ramping Time                       | tss_min                | SS/TRK open                             |                          | 1.7   |                 | ms   |

| Power-Good Monitors                                        |                        |                                         |                          |       | · L             |      |

| PGOOD Upper Threshold                                      | V <sub>PGOV</sub>      |                                         | 107                      | 109   | 112             | %    |

| PGOOD Lower Threshold                                      | V <sub>PGUV</sub>      |                                         | 87                       | 90    | 92              | %    |

| PGOOD Low Level Voltage                                    | $V_{PGLOW}$            | I_SINK = 2mA                            |                          |       | 0.35            | V    |

| PGOOD Leakage Current                                      | I <sub>PGLKG</sub>     | PGOOD = 5V                              |                          | 0     | 150             | nA   |

| PGOOD Timing                                               |                        | ,                                       |                          | I     |                 |      |

| V <sub>OUT</sub> Rising Threshold to PGOOD Rising (Note 9) | t <sub>PGR</sub>       |                                         |                          | 1.1   | 5               | ms   |

| V <sub>OUT</sub> Falling Threshold to PGOOD Falling        | t <sub>PGF</sub>       |                                         |                          | 80    |                 | μs   |

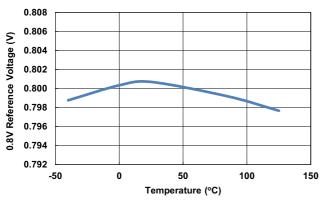

| Reference Section                                          |                        | ,                                       |                          | ı     |                 |      |

| Internal Voltage Loop Reference<br>Voltage                 | $V_{REFV}$             |                                         |                          | 0.800 |                 | V    |

| Reference Voltage Accuracy                                 |                        | T <sub>A</sub> = 0°C to +85°C           | -0.75                    |       | +0.75           | %    |

|                                                            |                        | T <sub>A</sub> = -40°C to +125°C        | -1.00                    |       | +1.00           | %    |

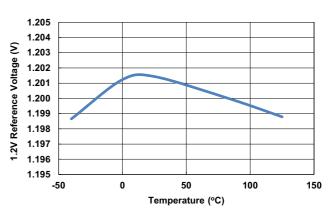

| Internal Current Loop Reference<br>Voltage                 | $V_{REFI}$             |                                         |                          | 1.200 |                 | V    |

| Reference Voltage Accuracy                                 |                        | T <sub>A</sub> = 0°C to +85°C           | -0.75                    |       | +0.75           | %    |

|                                                            |                        | T <sub>A</sub> = -40°C to +125°C        | -1.00                    |       | +1.00           | %    |

| PWM Controller Error Amplifiers                            |                        |                                         |                          | ı     | · L             | 1    |

| FB_OUT Pin Bias Current                                    | I <sub>FBOUTLKG</sub>  |                                         | -50                      | 0     | +50             | nA   |

| FB_OUT Error Amp GM                                        | Gm1                    |                                         |                          | 1.75  |                 | mS   |

| FB_OUT Error Amp Voltage Gain                              | AV1                    |                                         |                          | 82    |                 | dB   |

| FB_OUT Error Amp Gain-BW Product                           | GBW1                   |                                         |                          | 8     |                 | MHz  |

| FB_OUT Error Amp Output Current Capability                 |                        |                                         |                          | ±310  |                 | μΑ   |

| COMP Max High Voltage                                      | V <sub>COMP_HIGH</sub> | FB_OUT = 0V                             |                          | 3.8   |                 | ٧    |

| COMP Min Low Voltage                                       | V <sub>COMP_LOW</sub>  | FB_OUT = 1V                             |                          | 0.01  |                 | ٧    |

| FB_IN Pin Bias Current                                     | I <sub>FBINLKG</sub>   |                                         | -50                      | 0     | +50             | nA   |

| FB_IN Error Amp GM                                         | Gm2                    |                                         |                          | 12    |                 | μS   |

| FB_IN Error Amp Voltage Gain                               | AV2                    |                                         |                          | 72    |                 | dB   |

| FB_IN Error Amp Gain-BW Product                            | GBW2                   |                                         |                          | 5     |                 | MHz  |

| FB_IN Active Range (Note 10)                               | V <sub>FB_IN_ACT</sub> | VCC5V = 5V                              | 0                        |       | 4.3             | V    |

特に記載のない場合、下記の使用条件が推奨されます。6ページの「ブロック図」と4ページの「アプリケーション回路図例」を参照してください。特に記載のない場合、 $T_A$ = +25°Cでの標準的な値は、 $V_{IN}$ = 4.5V ~ 60V、またはVDD=8V±10%、 $C_{IN}$ 00%、V00%、V10% V10% V

| Parameter                                                    | Symbol                                  | Test Conditions                                                                   | Min<br>(Note 6) | Тур  | Max<br>(Note 6) | Unit |

|--------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------|-----------------|------|-----------------|------|

| FB_IN Logic Low Threshold (Note 10)                          | $V_{FB\_IN\_L}$                         |                                                                                   | 0.2             |      |                 | V    |

| FB_IN Logic High Threshold (Note 10)                         | V <sub>FB_IN_H</sub>                    | VCC5V = 5V                                                                        |                 |      | 4.7             | V    |

| PWM Regulator                                                |                                         |                                                                                   |                 |      |                 |      |

| Buck Mode Minimum Off-Time                                   | t <sub>OFF_MIN1</sub>                   |                                                                                   |                 | 220  |                 | ns   |

| Buck Mode Minimum On-Time                                    | t <sub>ON_MIN1</sub>                    |                                                                                   |                 | 100  |                 | ns   |

| Boost Mode Minimum Off-Time                                  | t <sub>OFF_MIN2</sub>                   |                                                                                   |                 | 180  |                 | ns   |

| Boost Mode Minimum On-Time                                   | t <sub>ON_MIN2</sub>                    |                                                                                   |                 | 140  |                 | ns   |

| Buck Mode Peak-to-Peak Sawtooth Amplitude                    | DV <sub>RAMP1</sub>                     | V <sub>IN</sub> = V <sub>OUT</sub> = 12V, f <sub>SW</sub> = 300kHz                |                 | 1.0  |                 | V    |

| Boost Mode Peak-to-Peak Sawtooth Amplitude                   | DV <sub>RAMP2</sub>                     | V <sub>IN</sub> = V <sub>OUT</sub> = 12V, f <sub>SW</sub> = 300kHz                |                 | 0.93 |                 | V    |

| Buck Mode Ramp Offset                                        | V <sub>ROFFSET1</sub>                   |                                                                                   | 0.88            | 0.95 | 1.11            | V    |

| Boost Mode Ramp Offset                                       | V <sub>ROFFSET2</sub>                   |                                                                                   | 2.84            | 3.15 | 3.7             | V    |

| Current Sense, Current Monitors, an                          | d Average Curre                         | nt Loop                                                                           |                 |      |                 |      |

| Input Current Sense Differential<br>Voltage Range            | V <sub>CS+</sub> - V <sub>CS-</sub>     |                                                                                   | -80             |      | +150            | mV   |

| Input Current Sense Common-Mode<br>Voltage Range             | CMIR <sub>CS</sub>                      |                                                                                   | 0               |      | 60              | V    |

| IMON_IN Offset Current                                       | I <sub>CSOFFSET</sub>                   | CS+ = CS- = 12V                                                                   | 15.5            | 19.5 | 22.5            | μΑ   |

| Input Current Sense Voltage to IMON_IN Current Source Gain   | Gm <sub>CS</sub>                        | 12V common-mode voltage applied to CS+/- pins, 0 to 40mV differential voltage     | 170             | 200  | 220             | μS   |

| IMON_IN Error Amp GM                                         | Gm3                                     |                                                                                   |                 | 12   |                 | μS   |

| IMON_IN Error Amp Voltage Gain                               | AV3                                     |                                                                                   |                 | 72   |                 | dB   |

| IMON_IN Active Range (Note 10)                               | V <sub>IMON_IN_ACT</sub>                | VCC5V = 5V                                                                        | 0               |      | 4.3             | V    |

| IMON_IN Logic High Threshold (Note 10)                       | $V_{IMON\_IN\_H}$                       | VCC5V = 5V                                                                        |                 |      | 4.7             | V    |

| IMON_IN Error Amp Gain-BW<br>Product                         | GBW3                                    |                                                                                   |                 | 5    |                 | MHz  |

| Output Current Sense Differential Voltage Range              | V <sub>ISEN+</sub> - V <sub>ISEN-</sub> |                                                                                   | -80             |      | +150            | mV   |

| Output Current Sense<br>Common-Mode Voltage Range            | CMIR <sub>ISEN</sub>                    |                                                                                   | 0               |      | 60              | V    |

| IMON_OUT Offset Current                                      | I <sub>ISENOFFSET</sub>                 | ISEN+ = ISEN- = 12V                                                               | 17.5            | 20   | 22              | μΑ   |

| IMON_OUT Current                                             |                                         | ISEN+ = 12V. ISEN- = 11.96V                                                       | 25              | 27.8 | 29.5            | μΑ   |

| Output Current Sense Voltage to IMON_OUT Current Source Gain | Gm <sub>ISEN</sub>                      | 12V common-mode voltage applied to ISEN+/- pins, 0mV to 40mV differential voltage | 170             | 200  | 220             | μS   |

| IMON_OUT Error Amp GM                                        | Gm4                                     |                                                                                   |                 | 12   |                 | μS   |

| IMON_OUT Error Amp Voltage Gain                              | AV4                                     |                                                                                   |                 | 72   |                 | dB   |

| IMON_OUT Error Amp Gain-BW<br>Product                        | GBW4                                    |                                                                                   |                 | 5    |                 | MHz  |

| Switching Frequency and Synchron                             | zation                                  |                                                                                   |                 |      |                 |      |

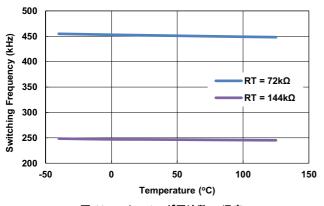

| Switching Frequency                                          | f <sub>SW</sub>                         | $R_T = 144k\Omega$                                                                | 220             | 245  | 265             | kHz  |

|                                                              |                                         | $R_T = 72k\Omega$                                                                 | 420             | 450  | 485             | kHz  |

|                                                              |                                         | R <sub>T</sub> Open or to VCC5V                                                   | 90              | 120  | 145             | kHz  |

|                                                              |                                         | $R_T = 0V$                                                                        | 470             | 575  | 650             | kHz  |

| RT Voltage                                                   | $V_{RT}$                                | $R_T = 72k\Omega$                                                                 |                 | 580  |                 | mV   |

特に記載のない場合、下記の使用条件が推奨されます。6ページの「ブロック図」と4ページの「アプリケーション回路図例」を参照してください。特に記載のない場合、 $T_A$ = +25°Cでの標準的な値は、 $V_{IN}$ = 4.5V ~ 60V、またはVDD=8V±10%、 $C_{IN}$ 00%、V00%、V10% V10% V

| Parameter                                               | Symbol                      | Test Conditions                                                                     | Min<br>( <u>Note 6</u> ) | Тур  | Max<br>(Note 6) | Unit |

|---------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------|--------------------------|------|-----------------|------|

| SYNC Synchronization Range                              | f <sub>SYNC</sub>           |                                                                                     | 140                      |      | 600             | kHz  |

| SYNC Input Logic High                                   | V <sub>SYNCH</sub>          |                                                                                     | 3.2                      |      |                 | V    |

| SYNC Input Logic Low                                    | V <sub>SYNCL</sub>          |                                                                                     |                          |      | 0.5             | V    |

| Clock Output and Frequency Dither                       |                             |                                                                                     | <b>'</b>                 |      |                 | •    |

| CLKOUT Output High                                      | V <sub>CLKH</sub>           | I <sub>SOURCE</sub> = 1mA, VCC5V = 5V                                               | 4.55                     |      |                 | V    |

| CLKOUT Output Low                                       | V <sub>CLKL</sub>           | I <sub>SINK</sub> = 1mA                                                             |                          |      | 0.3             | V    |

| CLKOUT Frequency                                        | f <sub>CLK</sub>            | $R_T = 72k\Omega$                                                                   | 420                      | 450  | 485             | kHz  |

| Dither Mode Setting Current Source                      | I <sub>DITHER_MODE_SO</sub> |                                                                                     |                          | 10   |                 | μΑ   |

| Dither Mode Setting Threshold Low                       | V <sub>DITHER_MODE_L</sub>  |                                                                                     | 0.26                     |      |                 | V    |

| Dither Mode Setting Threshold High                      | V <sub>DITHER_MODE_H</sub>  |                                                                                     |                          |      | 0.34            | V    |

| Dither Source Current                                   | I <sub>DITHERSO</sub>       |                                                                                     |                          | 8    |                 | μΑ   |

| Dither Sink Current                                     | I <sub>DITHERSI</sub>       |                                                                                     |                          | 10   |                 | μΑ   |

| Dither High Threshold Voltage                           | V <sub>DITHERH</sub>        |                                                                                     |                          | 2.2  |                 | V    |

| Dither Low Threshold Voltage                            | V <sub>DITHERL</sub>        |                                                                                     |                          | 1.05 |                 | V    |

| Diode Emulation Mode Detection                          | L                           |                                                                                     |                          |      | 1               |      |

| LG1/PWM_MODE Current Source                             | I <sub>MODELG1</sub>        |                                                                                     | 7.5                      | 10   | 12.5            | μΑ   |

| LG1/PWM_MODE Threshold Low                              | V <sub>MODETHL</sub>        |                                                                                     | 0.26                     |      |                 | V    |

| LG1/PWM_MODE Threshold High                             | V <sub>MODETHH</sub>        |                                                                                     |                          |      | 0.34            | V    |

| Buck Mode Diode Emulation Phase Threshold (Note 11)     | V <sub>CROSS1</sub>         | V <sub>IN</sub> = 12V                                                               |                          | 2    |                 | mV   |

| Boost Mode Diode Emulation Shunt<br>Threshold (Note 12) | V <sub>CROSS2</sub>         | V <sub>IN</sub> = 12V                                                               |                          | -2   |                 | mV   |

| Diode Emulation Burst Mode                              |                             |                                                                                     |                          |      |                 |      |

| Burst Mode Enter Threshold                              | V <sub>IMONOUTBSTEN</sub>   | IMON_OUT pin voltage                                                                | 0.81                     | 0.85 | 0.89            | V    |

| Burst Mode Exit Threshold                               | V <sub>MONOUTBSTEX</sub>    | IMON_OUT pin voltage                                                                | 0.83                     | 0.88 | 0.92            | V    |

| Burst Mode Peak Current Limit Input<br>Shunt Set Point  | V <sub>BST-CS</sub>         | V <sub>CS+</sub> - V <sub>CS-</sub> , 12V common-mode voltage applied to CS+/- pins | 16                       | 27   | 39              | mV   |

| Burst Mode Peak FB Voltage Limit<br>Set Point           | V <sub>BST-VFB-UTH</sub>    |                                                                                     |                          | 0.82 |                 | V    |

| Burst Mode Exit FB Voltage Set Point                    | V <sub>BST-VFB-LTH</sub>    |                                                                                     |                          | 0.78 |                 | V    |

| BSTEN Output Logic High                                 | V <sub>BSTEN-OH</sub>       | No load, VCC5V = 5V                                                                 |                          | 4.9  |                 | V    |

| BSTEN Output Logic Low                                  | V <sub>BSTEN-OL</sub>       | Pull-up resistance 100kΩ                                                            |                          | 0.07 |                 | V    |

| BSTEN Input Logic High                                  | V <sub>BSTEN-IH</sub>       |                                                                                     | 3.2                      |      |                 | V    |

| BSTEN Input Logic Low                                   | V <sub>BSTEN-IL</sub>       |                                                                                     |                          |      | 1               | V    |

| CLKEN Output Logic High                                 | V <sub>CLKEN-OH</sub>       | No load, VCC5V = 5V                                                                 |                          | 4.9  |                 | V    |

| CLKEN Output Logic Low                                  | V <sub>CLKEN-OL</sub>       | Pull-up resistance 100kΩ                                                            |                          | 0.07 |                 | V    |

| CLKEN Input Logic High                                  | V <sub>CLKEN-IH</sub>       |                                                                                     | 3.2                      |      |                 | V    |

| CLKEN Input Logic Low                                   | V <sub>CLKEN-IL</sub>       |                                                                                     |                          |      | 1               | V    |

| PWM Gate Drivers                                        | L                           | ı                                                                                   | 1 1                      |      | 1               | 1    |

| Driver 1, 2 BOOT Refresh Trip<br>Voltage                | V <sub>BOOTRF1,2</sub>      | BOOT voltage - PHASE voltage                                                        | 5.4                      | 5.95 | 6.65            | V    |

| Driver 1, 2 Source and Upper Sink<br>Current            | I <sub>GSRC1,2</sub>        |                                                                                     |                          | 2000 |                 | mA   |

| Driver 1, 2 Lower Sink Current                          | I <sub>GSNK1,2</sub>        |                                                                                     |                          | 3000 |                 | mA   |

| Driver 1, 2 Upper Drive Pull-Up                         | R <sub>UG_UP1,2</sub>       |                                                                                     |                          | 2.2  |                 | Ω    |

特に記載のない場合、下記の使用条件が推奨されます。6ページの「ブロック図」と4ページの「アプリケーション回路図例」を参照してください。特に記載のない場合、 $T_A$ = +25°Cでの標準的な値は、 $V_{IN}$ = 4.5V ~ 60V、またはVDD=8V±10%、 $C_{IN}$ 00%、V00%、V10% V10% V

| Parameter                                                              | Symbol                    | Test Conditions                                                                                                                                          | Min<br>(Note 6) | Тур | Max<br>(Note 6) | Unit |

|------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|------|

| Driver 1, 2 Upper Drive Pull-Down                                      | R <sub>UG_DN1,2</sub>     |                                                                                                                                                          |                 | 1.7 |                 | Ω    |

| Driver 1, 2 Lower Drive Pull-Up                                        | R <sub>LG_UP1,2</sub>     |                                                                                                                                                          |                 | 3   |                 | Ω    |

| Driver 1, 2 Lower Drive Pull-Down                                      | R <sub>LG_DN</sub>        |                                                                                                                                                          |                 | 2   |                 | Ω    |

| Driver 1, 2 Upper Drive Rise Time                                      | t <sub>GR_UP</sub>        | C <sub>OUT</sub> = 1000pF                                                                                                                                |                 | 10  |                 | ns   |

| Driver 1, 2 Upper Drive Fall Time                                      | t <sub>GF_UP</sub>        | C <sub>OUT</sub> = 1000pF                                                                                                                                |                 | 10  |                 | ns   |

| Driver 1, 2 Lower Drive Rise Time                                      | t <sub>GR_DN</sub>        | C <sub>OUT</sub> = 1000pF                                                                                                                                |                 | 10  |                 | ns   |

| Driver 1, 2 Lower Drive Fall Time                                      | t <sub>GF_DN</sub>        | C <sub>OUT</sub> = 1000pF                                                                                                                                |                 | 10  |                 | ns   |

| Overvoltage Protection                                                 |                           |                                                                                                                                                          | •               |     | •               | •    |

| Output OVP Threshold                                                   | V <sub>OVTH_OUT</sub>     |                                                                                                                                                          | 112             | 114 | 116             | %    |

| OV Pin Output Logic High                                               | V <sub>OV-OH</sub>        | Load resistance 100k, VCC5V = 5V                                                                                                                         |                 | 4.9 |                 | V    |

| OV Pin Output Logic Low                                                | V <sub>OV-OL</sub>        | No load                                                                                                                                                  |                 | 0   |                 | V    |

| OV Pin Input Logic High                                                | V <sub>OV-IH</sub>        |                                                                                                                                                          | 3.2             |     |                 | V    |

| OV Pin Input Logic Low                                                 | V <sub>OV-IL</sub>        |                                                                                                                                                          |                 |     | 1               | V    |

| Overcurrent Protection                                                 |                           | 1                                                                                                                                                        |                 |     |                 | 1    |

| LG2/OC_MODE Current Source                                             | I <sub>MODELG2</sub>      |                                                                                                                                                          | 7.5             | 10  | 12.5            | μA   |

| LG2/OC_MODE Threshold Low                                              | V <sub>MODETHLOC</sub>    |                                                                                                                                                          | 0.26            |     |                 | V    |

| LG2/OC_MODE Threshold High                                             | V <sub>MODETHHOC</sub>    |                                                                                                                                                          |                 |     | 0.34            | V    |

| Pulse-by-Pulse Peak Current Limit<br>Input Shunt Set Point             | V <sub>OCSET-CS</sub>     | V <sub>CS+</sub> - V <sub>CS-</sub> , 12V common-mode voltage applied to CS+/- pins                                                                      | 68              | 82  | 96              | mV   |

| Hiccup Peak Current Limit Input<br>Shunt Set Point                     | V <sub>OCSET-CS-HIC</sub> | V <sub>CS+</sub> - V <sub>CS-</sub>                                                                                                                      |                 | 100 |                 | mV   |

| Pulse-by-Pulse Negative Peak<br>Current Limit Output Shunt Set Point   | V <sub>OCSET-ISEN</sub>   | V <sub>ISEN+</sub> - V <sub>ISEN-</sub> , 12V common-mode voltage applied to ISEN+/- pins                                                                | -72             | -59 | -48             | mV   |

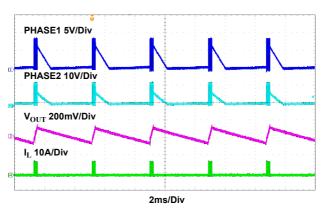

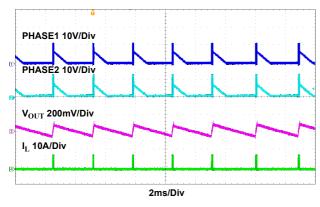

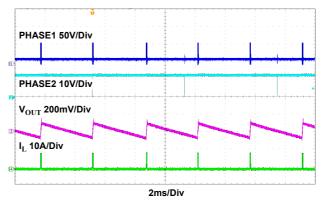

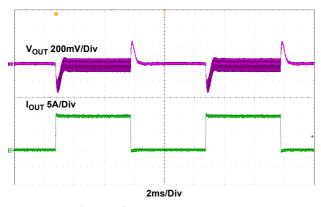

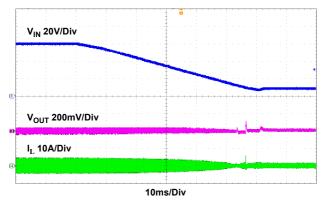

| Input Constant and Hiccup Current<br>Limit Set Point                   | V <sub>IMONINCC</sub>     | IMON_IN Pin Voltage                                                                                                                                      | 1.18            | 1.2 | 1.22            | V    |