# Introduction

It is important to consume as little current as possible when monitoring battery level as not to completely drain the source. This document will detail how to implement a low current 1.0  $\mu$ A battery voltage monitor with the wake-sleep method.

This solution makes use of three essential blocks: Analog Comparator (ACMP), Wake-Sleep Controller (WSCtrl) and Low Frequency Oscillator (LFOSC). The method which this app note describes can be applied to any Analog Block (ACMP or ADC) and any other devices with wake-sleep controllers. For more examples, see AN-1076 Wake/Sleep Timing Generator.

## **Analog Comparator**

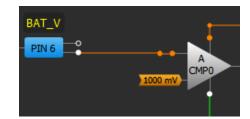

The Analog Comparator will be used to monitor battery level. Select an ACMP from the components window and check the positive input source; this pin will need to be configured as an "Analog I/O". For ACMP0, that pin is PIN6. By default, the pin has a 1 M $\Omega$  pull-down resistor. Configure this to "Floating" to avoid the extra pull-down current.

For the negative input, choose the threshold to compare with battery voltage. Use gain for voltages > 1.2V. In Figure 1, the negative input is set to 1000mV and gain set to 0.33x. Assuming a single cell LiION battery, a low voltage indication threshold is 3.0V.

All Analog Blocks require the use of the bandgap reference. The bandgap consumes ~35uA when ON and is powered by a voltage > 2.7V.

This voltage is supplied either by VDD or an internal charge pump. If not forced on, the bandgap can be turned on and off by the analog block power on and off signal. Using the bandgap only when needed reduces the average current consumed.

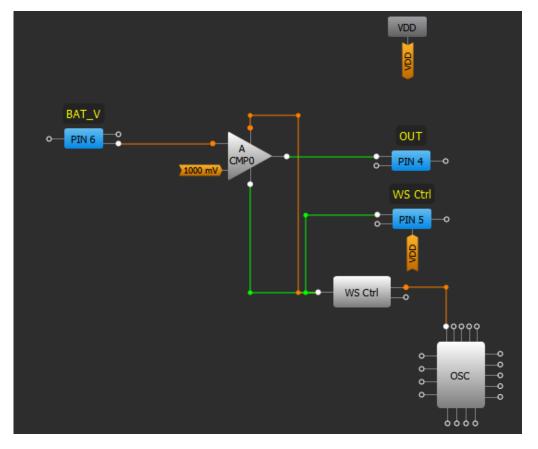

Figure 1. Analog In PIN6 hooked up to ACMP0

## Wake-Sleep Controller & LF OSC

The Analog power consumption can be reduced by using the wake-sleep method. This method turns on the analog blocks for a short amount of time (wake), latches in the values and then turns off the block. This is repeated every wake-sleep period.

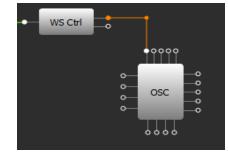

This method can be implemented in GPAK with CNT/DLY/WSCtrl, which is sourced by the low current Low Frequency Oscillator. Connecting the wake sleep controller to the "PWR ON/OFF" and "WAKE SLEEP" inputs of the ACMP will effectively control when analog blocks ACMP and BG are enabled and disabled. The WSCtrl operates the same as a counter. It loads in the counter data, counts down until zero and generates a 'High' when the counter data equals zero. An ACMP block is powered on if it's "PWR ON" input is 'High'. The ACMP output latch is unlatched when the "WAKE SLEEP" input is 'High'. Therefore the length that WSCtrl out is 'High' is the wake period, equivalent to one LF OSC period.

## **Wake Period**

The minimum wake period depends on bandgap and charge pump turn on time. Refer to tables in Datasheet section 5.8.1 ACMP Power On Delay. There are two tables, one for the BG setting 500  $\mu$ s and another for the BG setting 100  $\mu$ s. Choose the correct table based on your voltage supply range and BG setting. At VDDs < 2.7V, BG power on delay is 550  $\mu$ s to allow for charge pump turn on time; this is the default setting. At VDDs > 2.7V, the charge pump does not need to turn on, therefore the turn on setting can be set to 100  $\mu$ s.

For this example, we apply the first table for a worst case scenario: BG turn on time of 550  $\mu$ s across full temperature range. According to the column "maximum", the longest time it would take for the ACMP to turn on is 2092.2  $\mu$ s. Therefore, the WSCtrl's wake time must be greater than the 2092.2  $\mu$ s.

To enable the Wake Sleep Controller, select WSCtrl macro-cell and configure the mode to "wake sleep controller". Enable the analog block wake sleep through the WSCtrl settings (See Appendix A). Set the LF OSC power setting to 'Forced Power On'. Adjust the counter data to the desired response period. Here, the counter data was set to 2000. The minimum pre-divider is calculated in the equations below. To achieve a minimum 2092.2µs wake period, use a pre-divider of at least 4 (rounding up from 3.6467).

$LFOSC = 1.743 kHz \text{ or } 574 \mu s$

$$\frac{2092.2\mu s}{574\mu s} = 3.6467$$

Figure 2. WS Controller to OSC connection

# Analog Comparator Current Consumption

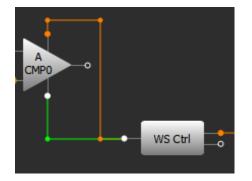

The two control signals: "PWR UP" (bottom input) which turns the ACMP on/off and "WAKE SLEEP" (top input) which controls the output latching mechanism, work together to save current.

Table 1 shows a comparison of guiescent current measured for different combinations of "PWR UP" and "WAKE SLEEP" signals. If configured correctly as shown in Figure 3, the quiescent current is limited by the LF OSC rather than the analog bandgap at  $\sim 1\mu$ A. Otherwise, the bandgap is always on which ~35µA of current. consumes Refer to datasheet section 5.6 Typical Current Consumption for expected component power usage.

| PWR | W/S | Quiescent Current                     |  |

|-----|-----|---------------------------------------|--|

| On  | Off | 44µA                                  |  |

| On  | W/S | 44µA                                  |  |

| W/S | W/S | 1.0μA (see functionality<br>waveform) |  |

#### Table 1. WS and PWR UP Configurations

# RENESAS

Figure 3. ACMP Wake Sleep and PWR UP inputs connected to WS Controller

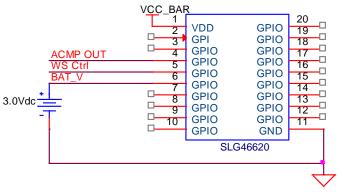

**Figure 4. Typical Application Circuit**

# **Typical Application Circuit**

The typical application circuit in Figure 4, has been bench tested using the on-board emulator and an external power supply. The battery can be used to power the chip as well, down to the minimum chip supply 1.71V.

Set the signal generator on BAT\_V (PIN#6) as a constant voltage signal greater than the 3V ACMP IN- threshold. Start and Stop the signal generator to observe changes at the output.

Waveforms can be found in the section Functionality Waveforms.

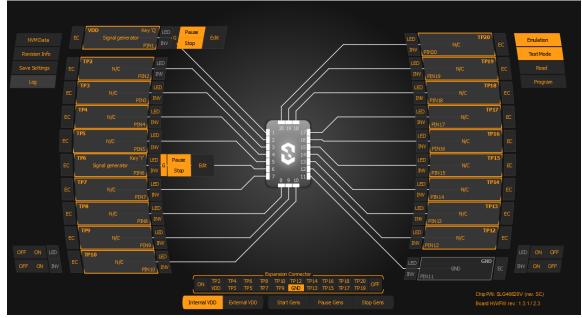

Figure 5. Emulator Configuration

## **Typical Response Time**

The typical response time is determined by the ACMP power-on delay and wake-sleep period.

In this example, the wake-sleep period is 4.63 seconds (counter data 2000) and ACMP Power On Delay is 2092.2  $\mu$ s.

$T_{response_max} = T_{1st} + T_{sleep}$

$T_{response\ max} = 2092.2 \mu s + 4.63 s = 4.63 s$

The power on delay is << sleep time, so the response period is essentially equal to the sleep period.

### Conclusion

The wake-sleep method is both an energy and resource efficient solution because it cuts current consumption from 44µA to 1µA and uses only one component, the WSCtrl. Any battery voltage within the GPAK operating range can use an ACMP to self-monitor its voltage; resistor dividers cost no extra current. For correct operation across voltage and temperature, refer to the datasheet section 5.8.1 for minimum ACMP power on delay and adjust the LF OSC accordingly. Use this method for all other GPAK devices where Wake-Sleep Controllers exist.

# RENESAS

# 1.0 µA Battery Voltage Monitor

## **Functionality Waveforms**

Channel 2 (light blue) – PIN#4 (ACMP0) Channel 3 (magenta) – PIN#5 (WSCtrl) Channel 1 (yellow) – PIN#6 (BAT\_V) Waveform 1 and 2 displays the functionality of the low current battery voltage sense circuit. At every Wake, the ACMP samples the input. At the end of the wake, the output is latched. In the event that the Wake-Sleep input is disconnected, the ACMP sample is not latched as shown in Waveform 3.

Waveform 1. Wake-Sleep on PWR and W/S ACMP and Battery Voltage < 1000mV

Waveform 2. Wake-Sleep on PWR and W/S ACMP and Battery Voltage >

# **1.0 µA Battery Voltage Monitor**

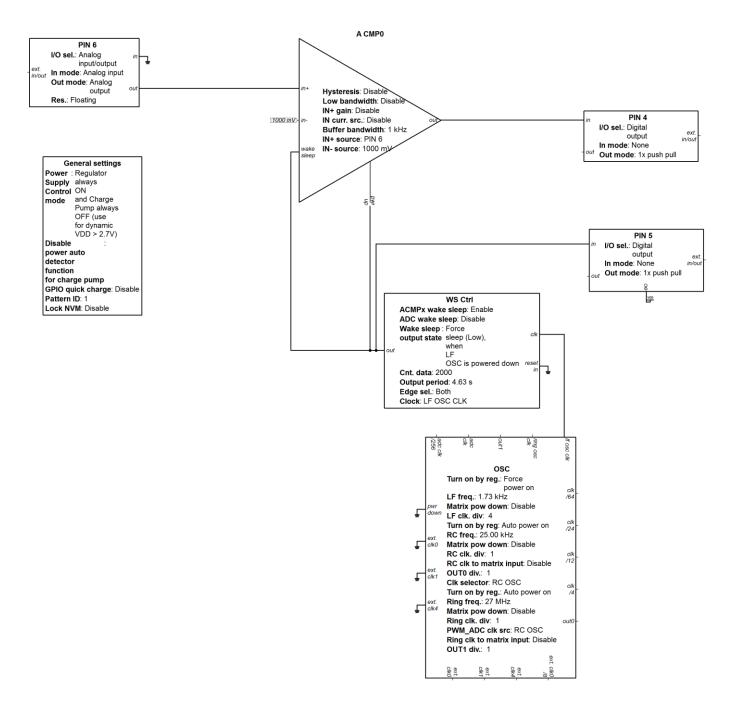

# Appendix A. GP Design

| A                              | CMP0      | PIN 6                  |                     |  |

|--------------------------------|-----------|------------------------|---------------------|--|

| Hysteresis:                    | Disable 🗘 | I/O selection:         | Analog input/output |  |

| Low bandwidth:                 | Disable 🔷 |                        |                     |  |

| Buffer<br>bandwidth:           | 1 kHz     | Input mode:<br>OE = 0  | Analog input 🔰      |  |

| Speed:                         | None 🗘    | Output mode:<br>OE = 1 | Analog output       |  |

| Input 100uA<br>current source: | Disable 🔷 | Resistor:              | Floating 🗘          |  |

| IN+ gain:                      | Disable   | Resistor value:        | Floating \$         |  |

| Con                            | inections | Reset:                 | None 🔷              |  |

| IN+ source:                    | PIN 6     | Bypass:                | None 🔷              |  |

| IN- source:                    | 1000 mV 🔷 | Edge detect<br>mode:   | None 🔷              |  |

| WS Ctrl/14                  | 4-bit CNT0/DLY0       |  |  |  |  |

|-----------------------------|-----------------------|--|--|--|--|

| Туре:                       | Wake sleep controll   |  |  |  |  |

| Mode:                       | Counter 🔷             |  |  |  |  |

| ACMPx wake<br>sleep:        | Enable 🔷              |  |  |  |  |

| ADC wake sleep:             | Disable 🔷             |  |  |  |  |

| Wake sleep<br>output state: | Force sleep (Low),    |  |  |  |  |

| Counter data:               | 2000                  |  |  |  |  |

|                             | (Range: 1 - 16383)    |  |  |  |  |

| Output period:              | 4.63 s <u>Formula</u> |  |  |  |  |

| Edge select:                | Both                  |  |  |  |  |

| Counter value<br>control:   | None 🔷                |  |  |  |  |

| DFF bypass<br>enable:       | None                  |  |  |  |  |

| Connections                 |                       |  |  |  |  |

| FSM data:                   | None                  |  |  |  |  |

| Clock:                      | LF OSC CLK            |  |  |  |  |

| Clock source:               | LF OSC CLK Freq.      |  |  |  |  |

| OSC                    |         |             |  |  |  |  |  |

|------------------------|---------|-------------|--|--|--|--|--|

| LF OSC                 | RC OSC  | RING OSC    |  |  |  |  |  |

| LF OSC pow<br>mode:    | Force p | ower on 🔰 🗢 |  |  |  |  |  |

| LF OSC<br>frequency:   | 1.73 kH | z 🔷         |  |  |  |  |  |

| LF matrix p<br>down:   | Disable | \$          |  |  |  |  |  |

| LF clock<br>predivider | by: 4   | \$          |  |  |  |  |  |

## 1.0 µA Battery Voltage Monitor

# **Appendix B. Block Diagram**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.