### **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category | MPU/MCU                                                                                            | Document<br>No.         | TN-SY*-A029A/E         | Rev.       | 1.00 |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|-------------------------|------------------------|------------|------|--|--|--|

| Title               | Revised information for current version of User's Manuals                                          | Information<br>Category | Technical Notification |            |      |  |  |  |

|                     | Applicable Product  Renesas Synergy™ S7G2, S5D9, S5D5, S3A7, S3A6, S3A3, S128, and S124 MCU Groups |                         | Lot No                 |            |      |  |  |  |

|                     |                                                                                                    |                         | Reference<br>Document  | See below. |      |  |  |  |

This Technical Update describes corrections for published User's Manuals of Synergy Microcontrollers. You can search for the affected User's Manual by its document number shown in parenthesis ().

S7G2 Rev.1.20 (R01UM0001EU0120), S5D9 Rev.1.00 (R01UM0004EU0100),

S5D5 Rev.1.10 (R01UM0009EU0110), S3A7 Rev.1.20 (R01UM0002EU0120),

S3A6 Rev.1.00 (R01UM0007EU0100), S3A3 Rev.1.00 (R01UM0006EU0100),

S124 Rev.1.20 (R01UM0003EU0120), and S128 Rev.1.00 (R01UM0005EU0100)

### [Changes summary]

| Chapter                  | Item           | Description                                                                                                       | S7G2     | S5D9     | S5D5     | S3A7     | S3A6     | S3A3     | S124     | S128     |

|--------------------------|----------------|-------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Option-Setting<br>Memory | 1              | Revised the reserved area                                                                                         | ✓        | -        | -        | -        | -        | -        | -        | -        |

| I/O Ports                | 2              | P402 and P404 are not 5 V-tolerant                                                                                | ✓        | -        | -        | -        | -        | -        | -        | -        |

|                          | 3              | Revised description of UF, VF, WF bits in OPSCR register                                                          | ✓        | ✓        | -        | ✓        | -        | -        | ✓        | -        |

| GPT                      | 4              | Revised description of EN bit in OPSCR register                                                                   | ✓        | ✓        | <b>√</b> | ✓        | <b>√</b> | <b>√</b> | ✓        | ✓        |

| OI I                     | 5              | Revised explanation for Settings of GTCCRn in Usage Notes                                                         | ✓        | <b>√</b> | <b>√</b> | <b>√</b> | <b>√</b> | <b>√</b> | ✓        | ✓        |

| AGT                      | 6, 7           | Revised the AGT block diagram and the explanation to update the value from the AGT Reload register to the counter | <b>√</b> | ✓        | <b>√</b> | ✓        | <b>√</b> | <b>√</b> | <b>√</b> | <b>\</b> |

| RTC                      | 8              | Added the TCEN bit to the RTCCRy register                                                                         | ✓        | ✓        | ✓        | ✓        | ✓        | ✓        | -        | -        |

| USBFS                    | 9, 10          | Revised the example connections                                                                                   | -        | -        | -        | ✓        | -        | -        | ✓        | -        |

| ETHERC                   | 11, 12         | Revised description of MPR, MAHR, and MAFCR registers                                                             | ✓        | ✓        | -        | -        | -        | -        | -        | -        |

| SPI                      | 13, 14         | Added UDRF bit to description for error flag                                                                      | ✓        | ✓        | -        | ✓        | -        | -        | ✓        | -        |

| DRW                      | 15, 16, 17, 18 | Corrected typographical errors                                                                                    | ✓        | ✓        | -        | -        | -        | -        | -        | -        |

|                          | 19             | Revised recommended operating conditions of VCC and AVCC0                                                         | -        | -        | -        | ✓        | <b>√</b> | ✓        | ✓        | <b>✓</b> |

| Electrical               | 20             | Added VBATWIOn I/O output characteristics                                                                         | -        | -        | -        | ✓        | -        | -        | -        | -        |

| Characteristics          | 21             | Added note about VREF condition for ACMPLP                                                                        | -        | -        | -        | -        | ✓        | ✓        | -        | -        |

|                          | 22             | Revised VIH/L characteristics of RTCICn pin                                                                       | ✓        | -        | -        | -        | -        | -        | -        | -        |

|                          | 23             | Added note for 5 V-tolerant ports                                                                                 | ✓        | -        | -        | -        | -        | -        | -        | -        |

| I/O Registers            | 24             | Revised the number of access cycles                                                                               | ✓        | -        | -        | -        | -        | -        | -        | -        |

#### Note:

The locations where corrections are made in the User's Manual can be in a paragraph, table, figure, sub-section, and section in a chapter. Depending on the product manuals that are affected, the chapter number can be different. For example, the SPI chapter of the S7G2 MCU User's Manual is chapter 38 but for the S124 MCU User's Manual, this is chapter 28. In the User's Manual, a section, table, or figure number is preceded by the chapter number. When a chapter, section, sub-section, table, or figure number is different, n is used to express them as explained in the following pages.

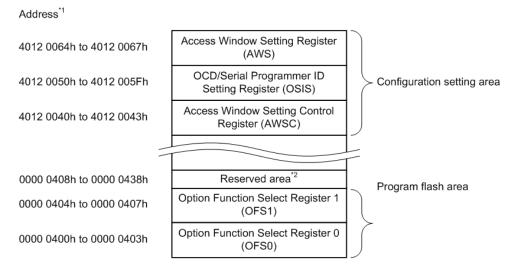

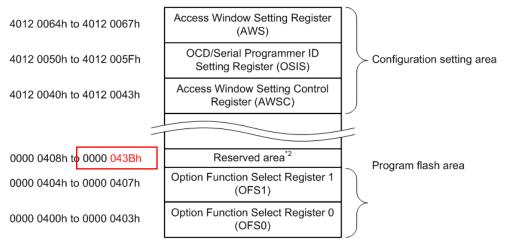

## (S7G2) Option-Setting Memory, Figure 7.1 Option-setting memory area [Before]

- Note 1. The option-setting memory must be allocated to the flash user area.

- Note 2. Do not access reserved area.

### [After]

Address\*1

- Note 1. The option-setting memory must be allocated to the flash user area.

- Note 2. Do not access reserved area.

2. (S7G2) I/O Ports, Table 20.2 I/O port functions

[Before]

| Port   | Port name    | Input pull-up | Open-drain output | Drive capacity switching | 5-V tolerant |

|--------|--------------|---------------|-------------------|--------------------------|--------------|

| Port 4 | P400, P401   | ✓             | <b>✓</b>          | Middle                   | ✓            |

|        | P402 to P404 | ✓             | ✓                 | Low, middle              | ✓            |

|        | P405 to P406 | ✓             | ✓                 | Low, middle, high        | -            |

|        | P407         | ✓             | ✓                 | Low, middle, high        | ✓            |

|        | P408 to P415 | ✓             | ✓                 | Low, middle, high        | ✓            |

### [After]

| Port   | Port name    | Input pull-up | Open-drain output | Drive capacity switching | 5-V tolerant |

|--------|--------------|---------------|-------------------|--------------------------|--------------|

| Port 4 | P400, P401   | ✓             | ✓                 | Middle                   | ✓            |

|        | P402 to P404 | ✓             | ✓                 | Low, middle              | -            |

|        | P405 to P406 | ✓             | ✓                 | Low, middle, high        | -            |

|        | P407         | ✓             | ✓                 | Low, middle, high        | ✓            |

|        | P408 to P415 | ✓             | ✓                 | Low, middle, high        | ✓            |

3. (S7G2, S5D9, S3A7, S124) General PWM Timer (GPT), n.2.32 Output Phase Switching Control Register (OPSCR)

[Before]

UF, VF, WF bits (Input Phase Soft Setting)

The UF, VF, and WF bits set the input phase from the software settings. When OPSCR.FB bit = 0, these bits are valid.

[After]

UF, VF, WF bits (Input Phase Soft Setting)

The UF, VF, and WF bits set the input phase from the software settings. When OPSCR.FB bit = 1, these bits are valid.

4. (All Series) General PWM Timer (GPT), n.2.32 Output Phase Switching Control Register (OPSCR) [Before]

EN bit (Enable-Phase Output Control)

When OPSCR.EN bit = 0, first set OPSCR.FB, OPSCR.UF/VF/WF (software setting is selected), OPSCR.P/N, OPSCR.INV, OPSCR.ALIGN, OPSCR.NFCS, OPSCR.GRP, OPSCR.GODF, OPSCR.NFEN, OPSCR.NFCS. Then, set his bit to 1.

[After]

EN bit (Enable-Phase Output Control)

When OPSCR.EN bit = 0, first set OPSCR.FB, OPSCR.UF/VF/WF (software setting is selected), OPSCR.P/N, OPSCR.INV, OPSCR.RV, OPSCR.ALIGN, OPSCR.GRP, OPSCR.GODF, OPSCR.NFEN, OPSCR.NFCS. Then, set his bit to 1.

5. (All Series) General PWM Timer (GPT), n.10.2 GTCCRn Settings during Compare Match Operation (n = A to F), (2) When automatic dead time setting is not made in triangle-wave PWM mode

The GTCCRA register must be set within the range of 0 < GTCCRA < GTPR. If GTCCRA = 0 or GTCCRA ≥ GTPR is set, a compare match occurs within the cycle only when GTCCRA = 0 or GTCCRA = GTPR is satisfied. When GTCCRA > GTPR, no compare match occurs.

Similarly, GTCCRB must be set within the range of 0 < GTCCRB < GTPR. If GTCCRB = 0 or GTCCRA ≥ GTPR is set, a compare match occurs within the cycle only when GTCCRB = 0 or GTCCRB = GTPR is satisfied. When GTCCRB > GTPR, no compare match occurs.

[After]

[Before]

The GTCCRA register must be set within the range of 0 < GTCCRA < GTPR. If GTCCRA = 0 or GTCCRA = GTPR is set, a compare match occurs within the cycle only when GTCCRA = 0 or GTCCRA = GTPR is satisfied. When GTCCRA > GTPR, no compare match occurs.

Similarly, GTCCRB must be set within the range of 0 < GTCCRB < GTPR. If GTCCRB = 0 or GTCCRB = GTPR is set, a compare match occurs within the cycle only when GTCCRB = 0 or GTCCRB = GTPR is satisfied. When GTCCRB > GTPR, no compare match occurs.

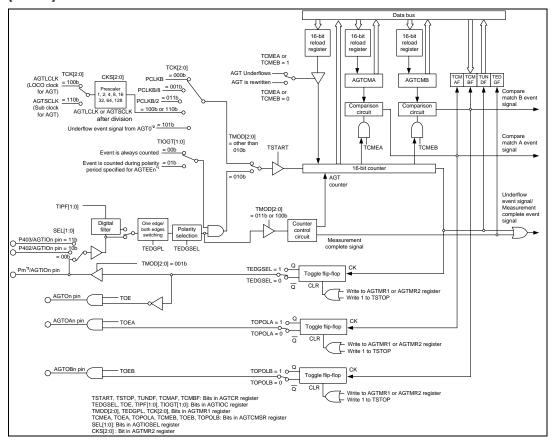

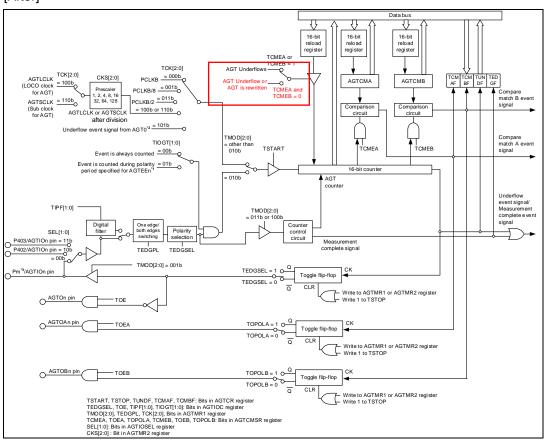

### 6. (All Series) Asynchronous General-Purpose Timer (AGT), Figure n.1 AGT block diagram [Before]

7. (All Series) Asynchronous General-Purpose Timer (AGT), n.3.1 Reload Register and Counter Rewrite Operation

#### [Before]

When the TSTART bit is 0 (count stops), the count value is directly written to the reload register and the counter. When the TSTART bit is 1 (count starts) and the TCMEA bit or TCMEB bit is 0 (compare match A/B register is invalid), the value is written to the reload register in synchronization with the count source, and then to the counter in synchronization with the next count source.

### [After]

When the TSTART bit is 0 (count stops), the count value is directly written to the reload register and the counter. When the TSTART bit is 1 (count starts) and the TCMEA bit and TCMEB bit is 0 (compare match A/B register is invalid), the value is written to the reload register in synchronization with the count source, and then to the counter in synchronization with the next count source.

8. (S7G2, S5D9, S5D5, S3A7, S3A6, S3A3) Realtime Clock (RTC), n.2.22 Time Capture Control Register y (RTCCRy) (y = 0 to 2)

### [Before]

| Bit    | Symbol | Bit name | Description                                            | R/W |

|--------|--------|----------|--------------------------------------------------------|-----|

| b7, b6 | _      | Reserved | These bits are read as 0. The write value should be 0. | R/W |

### [After]

| Bit | Symbol | Bit name                               | Description                                                                                                                | R/W |

|-----|--------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----|

| b6  | _      | Reserved                               | This bit is read as 0. The write value should be 0.                                                                        | R/W |

| b7  | TCEN   | Time Capture Event Input<br>Pin Enable | 0: The time capture event input pin RTCICn is disabled 1: The time capture event input pin RTCICn is enabled. (n = 0 to 2) | R/W |

### TECN bit (Time Capture Event Input Pin Enable)

This bit enables or disables the time capture event input pins (RTCIC0, RTCIC1, and RTCIC2). When the functions of the time capture event input pins (RTCIC0, RTCIC1, and RTCIC2) are multiplexed, VBTICTLR should be set first. If the TCEN bit is set to 0, also set the TCCT[1:0] bits to 00b.

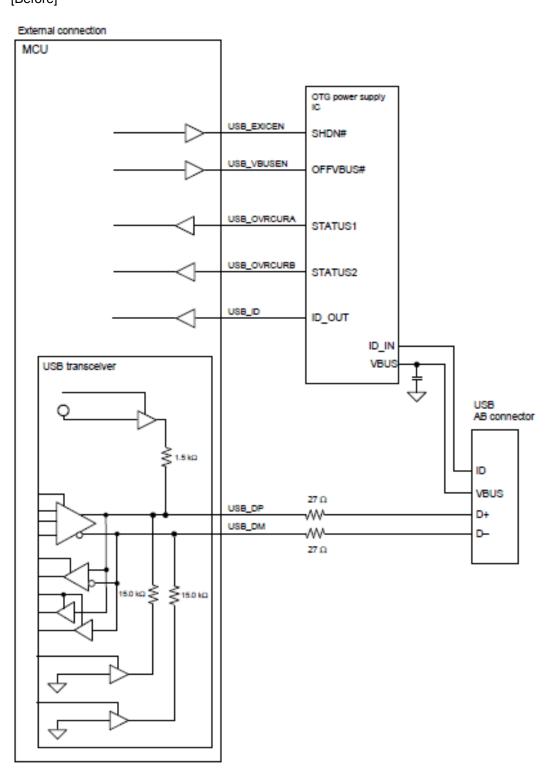

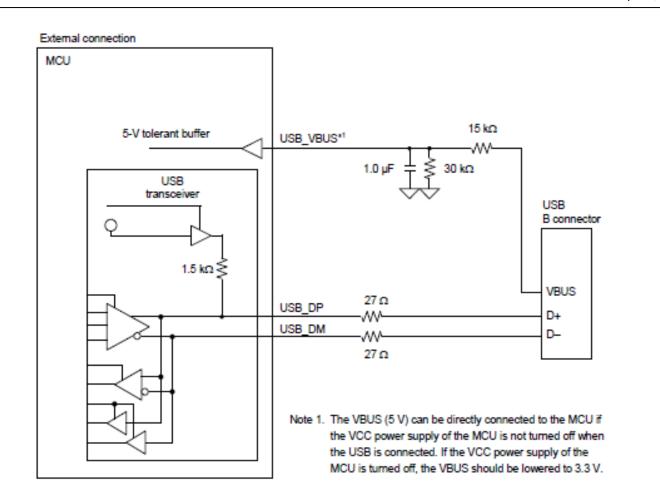

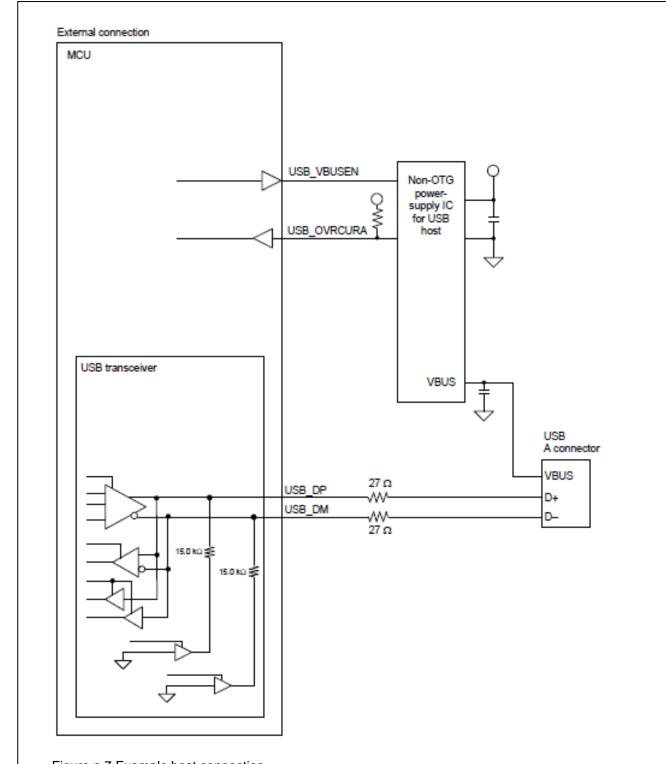

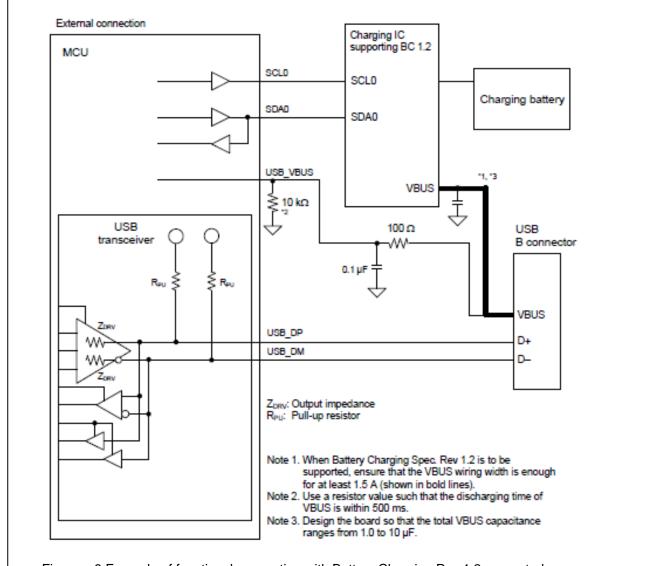

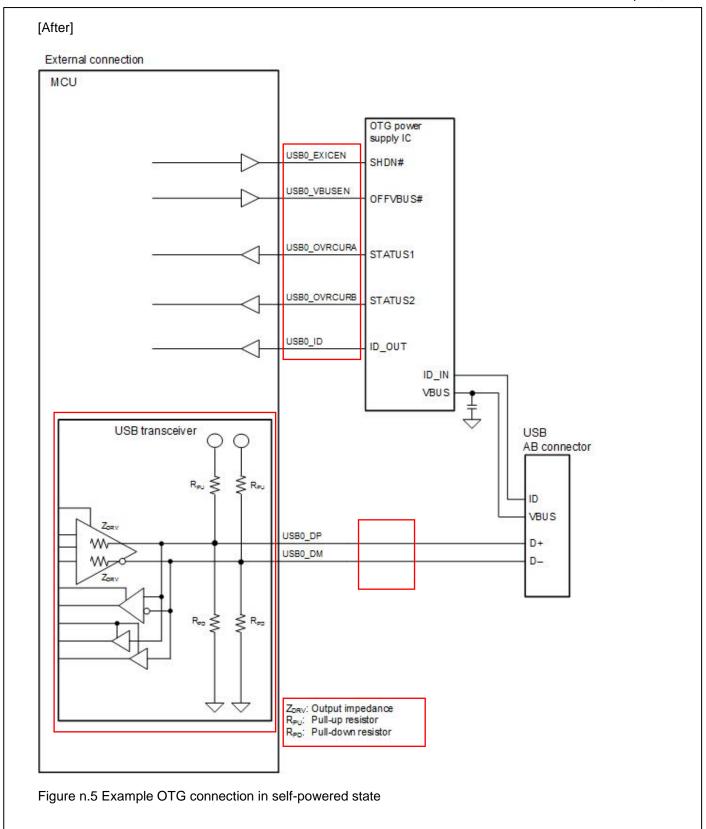

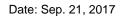

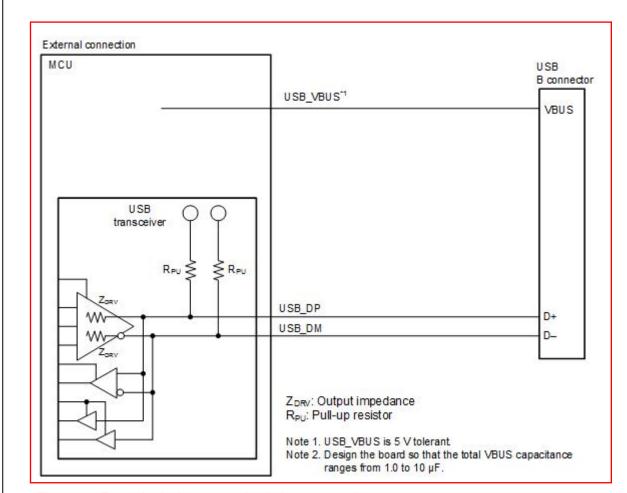

9. (S3A7, S124) USB 2.0 Full-Speed Module (USBFS), Figure n.5 Example OTG connection in self-powered state to Figure n.9 Example of functional connection with Battery Charging Rev.1.2 supported [Before]

Figure n.5 Example OTG connection in self-powered state

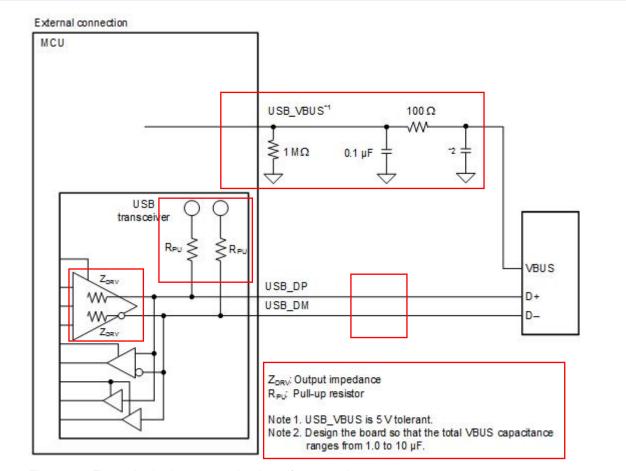

Figure n.6 Example device connection in self-powered state

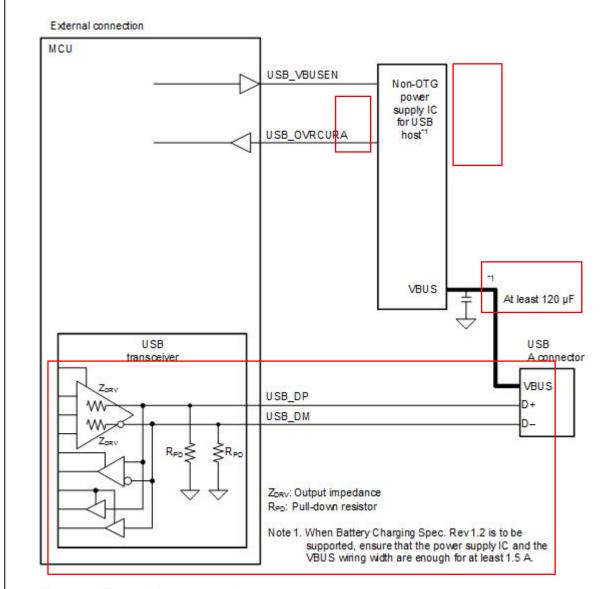

Figure n.7 Example host connection

Figure n.9 Example of functional connection with Battery Charging Rev.1.2 supported

Figure n.6 Example device connection in self-powered state

Figure n.7 Example host connection

Figure n.10 Example of functional connection with Battery Charging Rev.1.2 supported

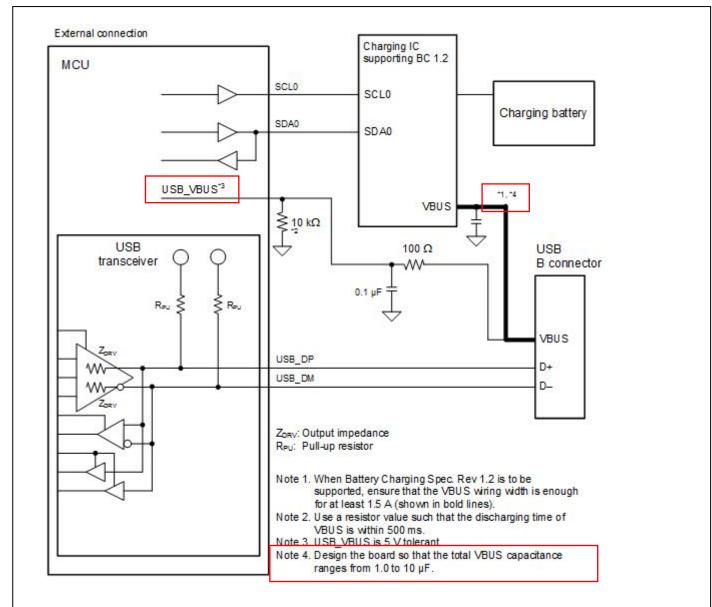

10. (S3A7, S124) USB 2.0 Full-Speed Module (USBFS), Figure n.8 Example device connection in bus-powered state

[Before]

Figure n.8 Example device connection in bus-powered state

Figure n.8 Example device connection in bus-powered state 1

Figure n.9 Example device connection in bus-powered state 2

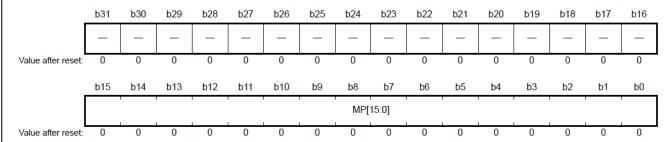

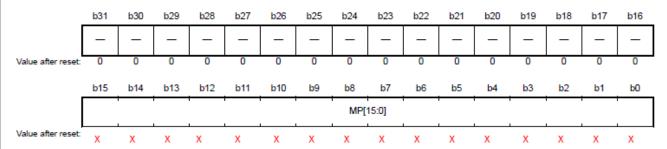

### 11. (S7G2, S5D9) Ethernet MAC Controller (ETHERC), n.2.10 Manual PAUSE Frame Register (MPR) [Before]

Address(es): ETHERC0.MPR 4006 4158h, ETHERC11.MPR 4006 4358h

### [After]

Address(es): ETHERCO.MPR 4006 4158h, ETHERC11.MPR 4006 4358h

## 12. (S7G2, S5D9) Ethernet MAC Controller (ETHERC), n.2.26 Multicast Address Frame Receive Counter Register (MAFCR)

### [Before]

The MAFCR register is a counter that indicates the number of times a frame with the multicast address set was received. When the register value becomes FFFF FFFFh, the counter stops. Writing any value to the RFCR register clears the counter value to 0.

### [After]

The MAFCR register is a counter that indicates the number of times a frame with the multicast address set was received. When the register value becomes FFFF FFFFh, the counter stops. Writing any value to the MAFCR register clears the counter value to 0.

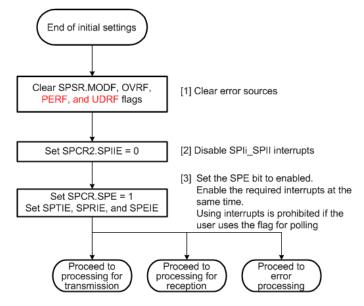

13. (S7G2, S5D9, S3A7, S124) Serial Peripheral Interface (SPI), Figure n.37 Transmission flow in master mode transmission to Figure n.39 Error processing flow for master mode [Before]

processing

Pre-transfer processing End of initial settings Clear SPSR.MODF, OVRF, and [1] Clear error sources PERF flags Set SPCR2.SPIIE = 0 [2] Disable SPIi\_SPII interrupts [3] Set the SPE bit to enabled. Enable the required interrupts at the Set SPCR.SPE = 1 same time. Set SPTIE, SPRIE, and SPEIE Using interrupts is prohibited if the user uses the flag for polling Proceed to Proceed to Proceed to processing for transmission processing for reception error

### [After]

Pre-transfer processing

14. (S7G2, S5D9, S3A7, S124) Serial Peripheral Interface (SPI), Table n.13 SPI interrupt sources

### [Before]

| Interrupt source                                                 | Symbol    | Interrupt condition                                                     | DMAC or DTC activation |

|------------------------------------------------------------------|-----------|-------------------------------------------------------------------------|------------------------|

| SPI error (mode fault,<br>underrun, overrun, or<br>parity error) | SPIi_SPEI | SPSR.MODF, OVRF, or PERF flag is set to 1 while the SPCR.SPEIE bit is 1 | Invalid                |

### [After]

| Interrupt source                                           | Symbol    | Interrupt condition                                                           | DMAC or DTC activation |

|------------------------------------------------------------|-----------|-------------------------------------------------------------------------------|------------------------|

| SPI error (mode fault, underrun, overrun, or parity error) | SPIi_SPEI | SPSR.MODF, OVRF, PERF, or UDRF flag is set to 1 while the SPCR.SPEIE bit is 1 | Invalid                |

15. (S7G2, S5D9) 2D Drawing Engine (DRW), n.2.2 Surface Control Register (CONTROL2)

### [Before]

| Bit      | Symbol              | Bit name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W |

|----------|---------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b23, b22 | WRITE<br>ALPHA[1:0] | Writeback Alpha<br>Source for Framebuffer | In non-alpha channel blending mode (USEACB = 0):  Sets the alpha source for the framebuffer.  b23 b22  0 0: Use alpha from color 2  1 : Use source alpha (pixel coverage)  1 : Use 0.0 as alpha  1 : Use alpha from framebuffer.  In alpha channel blending mode (USEACB = 1):  Blends alpha in color 2 instead of framebuffer alpha.  00 <sub>B</sub> : BC2A = 1: Use alpha from framebuffer as destination (DST_A) else: BC2A = 0: Use alpha in color 2 as destination (DST_A). | W   |

### [After]

| Bit      | Symbol              | Bit name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W |

|----------|---------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b23, b22 | WRITE<br>ALPHA[1:0] | Writeback Alpha<br>Source for Framebuffer | In non-alpha channel blending mode (USEACB = 0):  Sets the alpha source for the framebuffer.  In alpha source alpha (pixel coverage)  In the source alpha from framebuffer.  In alpha channel blending mode (USEACB = 1):  In alpha channel blending mode (USEACB = 1): | W - |

### 16. (S7G2, S5D9) 2D Drawing Engine (DRW), n.2.6 Hardware Version and Feature Set ID Register (HWREVISION) [Before]

| Bit | Symbol      | Bit name                                         | Description                                       | R/W |

|-----|-------------|--------------------------------------------------|---------------------------------------------------|-----|

| b21 | TEXCLUT     | Texture CLUT with 16 or 256<br>Entries Available | Texture CLUT with 16 or 256 entries is available. | R   |

| b22 | _           | Reserved                                         | This bit is read as 0.                            | R   |

| b23 | RLEUNIT     | RLE Unit Available                               | RLE unit is available.                            | R   |

| b24 | TEX CLUT256 | Texture CLUT Available                           | Texture CLUT is available.                        | R   |

### [After]

| Bit | Symbol      | Bit name                                         | Description                                       | R/W |

|-----|-------------|--------------------------------------------------|---------------------------------------------------|-----|

| b21 | TEXCLUT     | Texture CLUT Available                           | Texture CLUT is available.                        | R   |

| b22 | _           | Reserved                                         | This bit is read as 0.                            | R   |

| b23 | RLEUNIT     | RLE Unit Available                               | RLE unit is available.                            | R   |

| b24 | TEX CLUT256 | Texture CLUT with 16 or 256<br>Entries Available | Texture CLUT with 16 or 256 entries is available. | R   |

### 17. (S7G2, S5D9) 2D Drawing Engine (DRW), n.3.1.1 Color Formats

### [Before]

Supported color formats are:

Framebuffer formats

• 8-bit: a (8)

• 16-bit: RGB (565), aRGB (4444), aRGB (1555)

• 32-bit: aRGB (8888).

### [After]

Supported color formats are:

Framebuffer formats

• 8-bit: a (8)

• 16-bit: RGB (565), aRGB (4444)

• 32-bit: aRGB (8888).

### 18. (S7G2, S5D9) 2D Drawing Engine (DRW), n.6.2.6 Rasterization Optimization, (1) Spanstore [Before]

In this case, spanstore cannot be activated in the top left corner but can be activated in the bottom left corner.

The empty corners in the top right and the bottom left cannot be rasterized because of the spanabort optimization.

### [After]

In this case, spanstore cannot be activated in the top left corner but can be activated in the bottom left corner.

The empty corners in the top right and the bottom right cannot be rasterized because of the spanabort optimization.

19. (S3A7, S3A6, S3A3, S124, S128) Electrical Characteristics, Table n.2 Recommended operating conditions (S3A7, S3A3, S124, S128)

[Before]

Note 1. Use AVCC0 and VCC under the following conditions:

AVCC0 and VCC can be set individually within the operating range when VCC  $\geq$  2.0 V

AVCC0 = VCC when VCC < 2.0 V

[After]

Note 1. Use AVCC0 and VCC under the following conditions:

AVCC0 and VCC can be set individually within the operating range when VCC ≥ 2.2 V and AVCC0 ≥ 2.2 V

AVCC0 = VCC when VCC < 2.2 V or AVCC0 < 2.2 V

(S3A6)

[Before]

Note 1. Use AVCC0 and VCC under the following conditions:

AVCC0 and VCC can be set individually within the operating range when VCC  $\geq$  2.2 V and AVCC0  $\geq$  2.2 V

AVCC0 = VCC when VCC < 2.2 V or AVCC < 2.2 V

[After]

Note 1. Use AVCC0 and VCC under the following conditions:

AVCC0 and VCC can be set individually within the operating range when VCC  $\geq$  2.2 V and AVCC0  $\geq$  2.2 V

AVCC0 = VCC when VCC < 2.2 V or AVCC0 < 2.2 V

20. (S3A7) Electrical Characteristics, 51.10 Battery Backup Function Characteristics

[Before]

No description in Electrical Characteristics

[After]

Table n.xx VBATT-I/O characteristics

| Parameter                       |                            |                                                                                     | Symbol          | Min                     | Тур | Max | Unit | Test conditions          |

|---------------------------------|----------------------------|-------------------------------------------------------------------------------------|-----------------|-------------------------|-----|-----|------|--------------------------|

| VBATWIOn I/O                    | VCC > V <sub>DETBATT</sub> | VCC = 4.0 to 5.5 V                                                                  | V <sub>OH</sub> | VCC - 0.8               | _   | -   | V    | I <sub>OH</sub> = -200μA |

| output                          |                            |                                                                                     | V <sub>OL</sub> | _                       | _   | 0.8 |      | I <sub>OL</sub> = 200μA  |

| characteristics<br>(n = 0 to 2) |                            | $VCC = 2.7 \text{ to } 4.0 \text{ V}$ $VCC = V_{DETBATT} \text{ to } 2.7 \text{ V}$ | V <sub>OH</sub> | VCC - 0.5               | -   | -   |      | I <sub>OH</sub> = -100μA |

|                                 |                            |                                                                                     | V <sub>OL</sub> | -                       | -   | 0.5 |      | I <sub>OL</sub> = 100μA  |

|                                 |                            |                                                                                     | V <sub>OH</sub> | VCC - 0.3               | -   | -   |      | I <sub>OH</sub> = -50μA  |

|                                 |                            |                                                                                     | V <sub>OL</sub> | -                       | -   | 0.3 |      | $I_{OL} = 50 \mu A$      |

|                                 | VCC < V <sub>DETBATT</sub> | VBATT = 2.7 to 3.6 V                                                                | V <sub>OH</sub> | V <sub>BATT</sub> – 0.5 | _   | -   |      | I <sub>OH</sub> = -100μA |

|                                 | TO STATE SETENT            |                                                                                     | V <sub>OL</sub> | _                       | -   | 0.5 |      | I <sub>OL</sub> = 100μA  |

|                                 |                            | VBATT = 1.6 to 2.7 V                                                                | V <sub>OH</sub> | V <sub>BATT</sub> – 0.3 | -   | -   |      | I <sub>OH</sub> = -50μA  |

|                                 |                            |                                                                                     | V <sub>OL</sub> | _                       | _   | 0.3 |      | I <sub>OL</sub> = 50μA   |

21. (S3A6, S3A3) Electrical Characteristics, Table n.73 ACMPLP characteristics

(S3A6)

[Before]

| Parameter               |                 |         | Symbol | Min | Тур | Max     | Unit | Test conditions |

|-------------------------|-----------------|---------|--------|-----|-----|---------|------|-----------------|

| Reference voltage range | Standard mode \ |         | VREF   | 0   | -   | VCC-1.4 | V    | -               |

|                         | Window mode     | CMPREF1 | VREFH  | 1.4 | -   | VCC     | V    | -               |

|                         |                 | CMPREF0 | VREFL  | 0   | -   | VCC-1.4 | V    | -               |

Note: When 8-bit DAC output is used as the reference voltage, the offset voltage increases up to 2.5 x VCC/256.

Note: In window mode, be sure to satisfy the following condition: VREFH - VREFL  $\geq$  0.2 V.

### [After]

| Parameter                                                    |             |        | Symbol | Min | Тур     | Max     | Unit | Test conditions |

|--------------------------------------------------------------|-------------|--------|--------|-----|---------|---------|------|-----------------|

| Reference voltage range Standard mode $ VREFn $ $(n = 0, 1)$ |             | VREF   | 0      | -   | VCC-1.4 | V       | -    |                 |

|                                                              | Window mode | IVREF1 | VREFH  | 1.4 | -       | VCC     | V    | -               |

|                                                              |             | IVREF0 | VREFL  | 0   | -       | VCC-1.4 | V    | -               |

Note: When 8-bit DAC output is used as the reference voltage, the offset voltage increases up to 2.5 x VCC/256.

Note: In window mode, be sure to satisfy the following condition: IVREF1 - IVREF0  $\geq$  0.2 V.

### (S3A3)

### [Before]

| Item                    |                 |         | Symbol | Min | Тур | Max     | Unit | Test conditions |

|-------------------------|-----------------|---------|--------|-----|-----|---------|------|-----------------|

| Reference voltage range | Standard mode V |         | VREF   | 0   | -   | VCC-1.4 | V    | -               |

|                         | Window mode     | CMPREF1 | VREFH  | 1.4 | -   | VCC     | ٧    | -               |

|                         |                 | CMPREF0 | VREFL  | 0   | -   | VCC-1.4 | V    | -               |

Note: When 8-bit DAC output is used as the reference voltage, the offset voltage increases up to 2.5 x VCC/256.

Note: In window mode, you must satisfy the following condition:  $Vref1 - Vref0 \ge 0.2 V$ .

### [After]

| Parameter                                                  |             |        | Symbol | Min | Тур | Max     | Unit | Test conditions |

|------------------------------------------------------------|-------------|--------|--------|-----|-----|---------|------|-----------------|

| Reference voltage range Standard mode $VREFn$ $(n = 0, 1)$ |             | l      | VREF   | 0   | -   | VCC-1.4 | V    | -               |

|                                                            | Window mode | IVREF1 | VREFH  | 1.4 | -   | VCC     | V    | -               |

|                                                            |             | IVREF0 | VREFL  | 0   | -   | VCC-1.4 | V    | -               |

Note: When 8-bit DAC output is used as the reference voltage, the offset voltage increases up to 2.5 x VCC/256.

Note: In window mode, be sure to satisfy the following condition: IVREF1 - IVREF0  $\geq$  0.2 V.

### 22. (S7G2) Electrical Characteristics, Table 59.4 I/O VIH, IIL

### [Before]

| Item            | Item                              |                                                   |                 |                          | Тур | Max                     | Unit |

|-----------------|-----------------------------------|---------------------------------------------------|-----------------|--------------------------|-----|-------------------------|------|

| Schmitt trigger | Peripheral                        | RTCIC0, RTCIC1,                                   | V <sub>IH</sub> | V <sub>BATT</sub> × 0.8  | -   | V <sub>BATT</sub> + 0.3 | V    |

| input voltage   | input voltage function pin RTCIC2 |                                                   | V <sub>IL</sub> | -0.3                     | -   | V <sub>BATT</sub> × 0.2 |      |

|                 |                                   | (When V <sub>BATT</sub> power supply is selected) | ΔV <sub>T</sub> | V <sub>BATT</sub> × 0.05 | -   | -                       |      |

| Item            |                 |                   |                            |                                         | Symbol          | Min                    | Тур | Max                                                | Unit      |  |

|-----------------|-----------------|-------------------|----------------------------|-----------------------------------------|-----------------|------------------------|-----|----------------------------------------------------|-----------|--|

| Schmitt trigger | Peripheral      | RTCICO,           | When using the             | When VBATT                              | V <sub>IH</sub> | $V_{BATT} \times 0.8$  | -   | V <sub>BATT</sub> + 0.3                            | V         |  |

| input voltage   | function<br>pin | RTCIC1,<br>RTCIC2 | Battery Backup<br>Function | power supply is selected                | V <sub>IL</sub> | -                      | -   | $V_{BATT} \times 0.2$                              |           |  |

|                 | Pili            | KTOIOZ            | Tunction                   | Sciected                                | $\Delta V_T$    | $V_{BATT} \times 0.05$ | -   | -                                                  |           |  |

|                 |                 |                   |                            | When VCC<br>power supply is<br>selected | V <sub>IH</sub> | VCC × 0.8              | -   | Higher voltage either VCC + 0.3 V or VBATT + 0.3 V |           |  |

|                 |                 |                   |                            |                                         | V <sub>IL</sub> | -                      | -   | VCC × 0.2                                          |           |  |

|                 |                 |                   |                            |                                         | $\Delta V_T$    | VCC × 0.05             | -   | -                                                  | 1         |  |

|                 |                 |                   | When not using the         | he Battery Backup                       | V <sub>IH</sub> | VCC × 0.8              | -   | VCC + 0.3                                          |           |  |

|                 |                 |                   | Function                   |                                         |                 | V <sub>IL</sub>        | -   | -                                                  | VCC × 0.2 |  |

|                 |                 |                   |                            |                                         |                 | VCC × 0.05             | -   | -                                                  | 1         |  |

### 23. (S7G2) Electrical Characteristics, Table 59.4 I/O VIH, IIL

### [Before]

| Item                          |                         |                     | Symbol                                         | Min                    | Тур | Max                    | Unit |

|-------------------------------|-------------------------|---------------------|------------------------------------------------|------------------------|-----|------------------------|------|

| Schmitt trigger input voltage | Peripheral function pin | 5V-tolerant ports*3 | V <sub>IH</sub>                                | VCC × 0.8              | -   | VCC + 3.5<br>(max 5.8) | V    |

|                               |                         |                     | V <sub>IL</sub>                                | -0.3                   | -   | VCC × 0.2              |      |

|                               |                         |                     | $\Delta V_T$                                   | VCC × 0.05             | -   | -                      |      |

|                               | Ports                   | 5V-tolerant ports*5 | /-tolerant ports*5 V <sub>IH</sub> VCC × 0.8 - | VCC + 3.5<br>(max 5.8) |     |                        |      |

|                               |                         |                     | V <sub>IL</sub>                                | -0.3                   | -   | VCC × 0.2              |      |

- Note 1. SCL0\_B, SCL1\_B, SDA1\_B (total 3 pins).

- Note 2. SCL0\_A, SDA0\_A, SDA0\_B, SCL1\_A, SDA1\_A, SCL2, SDA2 (total 7 pins).

- Note 3. RES and peripheral function pins associated with P205, P206, P400, P401, P407 to P415, P511, P512, P708 to P713, PB01 (total 23 pins).

- Note 4. All input pins except for the peripheral function pins already described in the table.

- Note 5. P205, P206, P400, P401, P407 to P415, P511, P512, P708 to P713, PB01 (total 22pins).

- Note 6. All input pins except for the ports already described in the table.

| Item                          |                         |                       | Symbol          | Min        | Тур | Max                    | Unit |

|-------------------------------|-------------------------|-----------------------|-----------------|------------|-----|------------------------|------|

| Schmitt trigger input voltage | Peripheral function pin | 5V-tolerant ports*3*7 | V <sub>IH</sub> | VCC × 0.8  | -   | VCC + 3.5<br>(max 5.8) | V    |

|                               |                         |                       | V <sub>IL</sub> | -0.3       | -   | VCC × 0.2              |      |

|                               |                         |                       | $\Delta V_T$    | VCC × 0.05 | -   | -                      |      |

|                               | Ports                   | 5V-tolerant ports*5*7 | V <sub>IH</sub> | VCC × 0.8  | -   | VCC + 3.5<br>(max 5.8) |      |

|                               |                         |                       | V <sub>IL</sub> | -0.3       | -   | VCC × 0.2              |      |

- Note 1. SCL0\_B, SCL1\_B, SDA1\_B (total 3 pins).

- Note 2. SCL0\_A, SDA0\_A, SDA0\_B, SCL1\_A, SDA1\_A, SCL2, SDA2 (total 7 pins).

- Note 3. RES and peripheral function pins associated with P205, P206, P400, P401, P407 to P415, P511, P512, P708 to P713, PB01 (total 23 pins).

- Note 4. All input pins except for the peripheral function pins already described in the table.

- Note 5. P205, P206, P400, P401, P407 to P415, P511, P512, P708 to P713, PB01 (total 22 pins).

- Note 6. All input pins except for the ports already described in the table.

- Note 7. When VCC is less than 2.7 V, the input voltage of 5 V-tolerant ports should be less than 3.6 V. Otherwise, a breakdown might occur because the 5 V-tolerant ports are electrically controlled to not violate the breakdown voltage.

### 24. (S7G2) Appendix I/O Registers, Table 3.2 Access cycles for non-GPT modules [Before]

Table 3.2 Access cycles for non-GPT modules (1 of 3)

|            |            |                                                                                  |        | Num   | ber of acc | ess cycles |                                                                                                                                                |                                                                                                                                                                                             |

|------------|------------|----------------------------------------------------------------------------------|--------|-------|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ado        | dress      |                                                                                  | ICLK = | PCLK  | ICLK >     | PCLK*1     |                                                                                                                                                |                                                                                                                                                                                             |

| From       | То         | Peripherals                                                                      | Read   | Write | Read       | Write      | Cycle unit                                                                                                                                     | Related function                                                                                                                                                                            |

| 4000 0000h | 4001 CFFFh | MMPU, SMPU,<br>SPMON, MMF, SRAM,<br>BUS, DMACn, DMA,<br>DTC, ICU, DBG,<br>FCACHE |        |       | 6          | ICLK       | Memory Protection Unit, Memory Mirror Function, SRAM, Buses, DMA Controller, Data Transfer Controller, Interrupt Controller, CPU, Flash Memory |                                                                                                                                                                                             |

| 4001 E000h | 4001 E3FFh | SYSTEM                                                                           | 7      |       |            |            | ICLK                                                                                                                                           | Operation Modes,<br>Resets, Clock<br>Generation<br>Function, Register<br>Write Protection<br>Function                                                                                       |

| 4001 E400h | 4001 E6FFh | SYSTEM                                                                           | 1      | 1     | 6          | ~ 9        | PCLKB                                                                                                                                          | Low Power Mode,<br>Resets, Low<br>Voltage Detect,<br>Battery Backup<br>Function                                                                                                             |

| 4004 0000h | 4004 7FFFh | PORTn, PFS, PMISC,<br>ELC, POEG, RTC,<br>WDT, IWDT, CAC,<br>MSTP                 |        | 5     | 1          | ~ 4        | PCLKB                                                                                                                                          | I/O Ports, Event Link Controller, Port Output Enable for GPT, Realtime Clock, Watchdog Timer, Independent Watchdog Timer, Clock Frequency Accuracy Measurement Circuit, Module Stop Control |

Table 3.2 Access cycles for non-GPT modules (2 of 3)

|            |            |                                                      |        | Num        | ber of acce                | ess cycles           | )          |                                                                                                                                                                                |

|------------|------------|------------------------------------------------------|--------|------------|----------------------------|----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add        | dress      |                                                      | ICLK = | PCLK       | ICLK >                     | PCLK*1               |            |                                                                                                                                                                                |

| From       | То         | Peripherals                                          | Read   | Write      | Read                       | Write                | Cycle unit | Related function                                                                                                                                                               |

| 4004 8000h | 4004 DFEFh | SRCRAM                                               | 6      | 5          | 2~5                        | 1 ~ 4                | PCLKB      | Sampling Rate                                                                                                                                                                  |

| 4004 DFF0h | 4004 DFF7h | SRC                                                  |        | 7          | 3 -                        | ~ 6                  | PCLKB      | Converter                                                                                                                                                                      |

| 4004 DFF8h | 4004 DFFFh | SRC                                                  | ,      | 5          | 1 ·                        | ~ 4                  | PCLKB      |                                                                                                                                                                                |

| 4004 E000h | 4005 FFFFh | SSIn, CANn, IICn,<br>DOC, ADC12n, TSN,<br>DAC12, AMI |        | 5          | 1~4                        |                      | PCLKB      | Serial Sound Interface, Controller Area Network Module, I <sup>2</sup> C Bus Interface, Data Operation Circuit, 12-Bit A/D Converter, Temperature Sensor, 12-Bit D/A Converter |

| 4006 0000h | 4006 0FFFh | USBHS                                                | (5+BV  | VAIT)*2    | (1+BWAIT) ~<br>(4+BWAIT)*2 |                      | PCLKA      | USB 2.0 High-<br>Speed Module                                                                                                                                                  |

| 4006 2000h | 4006 2FFFh | SDHIn                                                | 5 1~4  |            | 1 ~ 4                      |                      | PCLKA      | SD/MMC Host<br>Interface                                                                                                                                                       |

| 4006 4000h | 4006 40FFh | EDMAC0                                               | (      | 6          |                            | 2~5                  |            | Ethernet DMA<br>Controller                                                                                                                                                     |

| 4006 4100h | 4006 41FFh | ETHERC0                                              | 1      | 15         | 11 ~ 14                    |                      | PCLKA      | Ethernet MAC<br>Controller                                                                                                                                                     |

| 4006 4200h | 4006 42FFh | EDMAC1                                               |        | 6          | 2~5                        |                      | PCLKA      | Ethernet DMA<br>Controller                                                                                                                                                     |

| 4006 4300h | 4006 43FFh | ETHERC1                                              |        | 5          | 11 ~ 14                    |                      | PCLKA      | Ethernet MAC<br>Controller                                                                                                                                                     |

| 4006 4400h | 4006 44FFh | PTPEDMAC                                             | (      | 6          | 2~5                        |                      | PCLKA      | Ethernet DMA<br>Controller                                                                                                                                                     |

| 4006 4500h | 4006 45FFh | EPTPC_CFG, EPTPC,<br>EPTPCn                          | ,      | cycle)*3   | (2+wai                     | cle-1) ~<br>t cycle) | PCLKA      | Ethernet PTP<br>Controller                                                                                                                                                     |

| 4007 2000h | 4007 2FFFh | SPI0, SPI1                                           |        | <b>*</b> 5 | 1 ~                        | 4*5                  | PCLKA      | Serial Peripheral<br>Interface                                                                                                                                                 |

| 4007 4000h | 4007 4FFFh | CRC                                                  | :      | 5          | 1                          | ~ 4                  | PCLKA      | CRC Calculator                                                                                                                                                                 |

| 4007 8000h | 4007 8FFFh | GPT32EHi, GPT32Ej,<br>GPT32k, GPT_OPS                |        | Refer to   | Table 3*6                  |                      | PCLKA      | General PWM<br>Timer                                                                                                                                                           |

| 4007 B000h | 4007 BFFFh | GPT_ODC                                              |        | 4          | 1                          | ~ 3                  | PCLKA      | PWM Delay<br>Generation Circuit                                                                                                                                                |

| 4008 0000h | 4008 1FFFh | KINT, CTSU                                           |        | 4          | 1~3                        |                      | PCLKB      | Key Interrupt Function, Capacitive Touch Sensing Unit                                                                                                                          |

| 4008 4000h | 4008 4FFFh | AGTn                                                 | 7      | 5          | 3~6                        | 1 ~ 4                | PCLKB      | Asynchronous<br>General Purpose<br>Timer                                                                                                                                       |

| 4008 5000h | 4008 5FFFh | ACMPHSn                                              | 4      |            | 1~3                        |                      | PCLKB      | High-Speed Analog<br>Comparator                                                                                                                                                |

| 4009 0000h | 4009 03FFh | USBFS                                                | 6      |            | 2~5                        |                      | PCLKB      | USB 2.0 Full-<br>Speed Module                                                                                                                                                  |

Date: Sep. 21, 2017

Table 3.2 Access cycles for non-GPT modules (3 of 3)

|            |            |             |       | Num     | ber of acce | ess cycles | 1          |                                     |

|------------|------------|-------------|-------|---------|-------------|------------|------------|-------------------------------------|

| Add        | dress      |             | ICLK: | PCLK    | ICLK >      | PCLK*1     |            |                                     |

| From       | То         | Peripherals | Read  | Write   | Read        | Write      | Cycle unit | Related function                    |

| 4009 0400h | 4009 04FFh | USBFS       | 4     |         | 1~3         |            | PCLKB      | USB 2.0 Full-<br>Speed Module       |

| 4009 4000h | 4009 4FFFh | PDC         |       | 5       | 1 ~ 4       |            | PCLKB      | Parallel Data<br>Capture Unit       |

| 400E 0000h | 400E 4FFFh | GLCDC, DRW  |       | 5       | 1 ~ 4       |            | PCLKA      | Graphics LCD<br>Controller          |

| 400E 6000h | 400E 603Fh | JPEG        | 15    | 7       | 11 ~ 14     | 3 ~ 6      | PCLKA      | JPEG Codec                          |

| 400E 6040h | 400E 6FFFh | JPEG        | 7     | 6       | 3~6         | 2~5        | PCLKA      | JPEG Codec                          |

| 6400 0000h | 6400 000Fh | QSPI        | 5     | 15 ~ *7 | 1 ~ 4       | 11 ~ *7    | PCLKA      | Quad Serial<br>Peripheral Interface |

| 6400 0010h | 6400 0013h | QSPI        | 26 ~  | 7 ~ *7  | 22 ~ *7     | 3 ~ *7     | PCLKA      | Quad Serial<br>Peripheral Interface |

| 6400 0014h | 6400 0037h | QSPI        | 5     | 15 ~ *7 | 1~4         | 11 ~ *7    | PCLKA      | Quad Serial<br>Peripheral Interface |

| 6400 0804h | 6400 0807h | QSPI        | 4     | 4       | 1~3         | 1~3        | PCLKA      | Quad Serial<br>Peripheral Interface |

Table 3.2 Access cycles for non-GPT modules (1 of 3)

|            |            | Number of access cycles                                                          |                           |       |       |                                                                                 |            |                                                                                                                                                                                             |

|------------|------------|----------------------------------------------------------------------------------|---------------------------|-------|-------|---------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address    |            |                                                                                  | ICLK = PCLK ICLK > PCLK*1 |       |       |                                                                                 |            |                                                                                                                                                                                             |

| From       | То         | Peripherals                                                                      | Read                      | Write | Read  | Write                                                                           | Cycle unit | Related function                                                                                                                                                                            |

| 4000 0000h | 4001 CFFFh | MMPU, SMPU,<br>SPMON, MMF, SRAM,<br>BUS, DMACn, DMA,<br>DTC, ICU, DBG,<br>FCACHE | 6                         |       |       |                                                                                 | ICLK       | Memory Protection<br>Unit, Memory<br>Mirror Function,<br>SRAM, Buses,<br>DMA Controller,<br>Data Transfer<br>Controller, Interrupt<br>Controller, CPU,<br>Flash Memory                      |

| 4001 E000h | 4001 E3FFh | SYSTEM                                                                           | 7                         |       |       |                                                                                 | ICLK       | Operation Modes,<br>Resets, Clock<br>Generation<br>Function, Register<br>Write Protection<br>Function                                                                                       |

| 4001 E400h | 4001 E6FFh | SYSTEM                                                                           | 11 7~9                    |       | PCLKB | Low Power Mode,<br>Resets, Low<br>Voltage Detect,<br>Battery Backup<br>Function |            |                                                                                                                                                                                             |

| 4004 0000h | 4004 7FFFh | PORTn, PFS, PMISC,<br>ELC, POEG, RTC,<br>WDT, IWDT, CAC,<br>MSTP                 |                           | 5     | 2     | ~ 4                                                                             | PCLKB      | I/O Ports, Event Link Controller, Port Output Enable for GPT, Realtime Clock, Watchdog Timer, Independent Watchdog Timer, Clock Frequency Accuracy Measurement Circuit, Module Stop Control |

Date: Sep. 21, 2017

Table 3.2 Access cycles for non-GPT modules (2 of 3)

|            |            |                                                      |                           | Numl                |                                  |       |            |                                                                                                                                                                                                              |

|------------|------------|------------------------------------------------------|---------------------------|---------------------|----------------------------------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address    |            |                                                      | ICLK = PCLK ICLK > PCLK*1 |                     |                                  |       |            |                                                                                                                                                                                                              |

| From       | То         | Peripherals                                          | Read                      | Write               | Read                             | Write | Cycle unit | Related function                                                                                                                                                                                             |

| 4004 8000h | 4004 DFEFh | SRCRAM                                               | 6                         | 5                   | <b>3</b> ~ 5                     | 2~4   | PCLKB      | Sampling Rate                                                                                                                                                                                                |

| 4004 DFF0h | 4004 DFF7h | SRC                                                  | 7                         |                     | 4~6                              |       | PCLKB      | Converter                                                                                                                                                                                                    |

| 4004 DFF8h | 4004 DFFFh | SRC                                                  | 5                         |                     | 2 ~ 4                            |       | PCLKB      |                                                                                                                                                                                                              |

| 4004 E000h | 4005 FFFFh | SSIn, CANn, IICn,<br>DOC, ADC12n, TSN,<br>DAC12, AMI | 5                         |                     | 2~4                              |       | PCLKB      | Serial Sound<br>Interface,<br>Controller Area<br>Network Module,<br>I <sup>2</sup> C Bus Interface,<br>Data Operation<br>Circuit, 12-Bit A/D<br>Converter,<br>Temperature<br>Sensor, 12-Bit D/A<br>Converter |

| 4006 0000h | 4006 0FFFh | USBHS                                                |                           | /AIT)* <sup>2</sup> | (2+BWAIT) ~<br>(4+BWAIT)*2       |       | PCLKA      | USB 2.0 High-<br>Speed Module                                                                                                                                                                                |

| 4006 2000h | 4006 2FFFh | SDHIn                                                |                           | 5                   | 2.                               | ~ 4   | PCLKA      | SD/MMC Host<br>Interface                                                                                                                                                                                     |

| 4006 4000h | 4006 40FFh | EDMAC0                                               | 6                         |                     | <b>3</b> ~ 5                     |       | PCLKA      | Ethernet DMA<br>Controller                                                                                                                                                                                   |

| 4006 4100h | 4006 41FFh | ETHERC0                                              | 15                        |                     | 12 ~ 14                          |       | PCLKA      | Ethernet MAC<br>Controller                                                                                                                                                                                   |

| 4006 4200h | 4006 42FFh | EDMAC1                                               | 6                         |                     | <b>3</b> ~ 5                     |       | PCLKA      | Ethernet DMA<br>Controller                                                                                                                                                                                   |

| 4006 4300h | 4006 43FFh | ETHERC1                                              | 15                        |                     | 12 ~ 14                          |       | PCLKA      | Ethernet MAC<br>Controller                                                                                                                                                                                   |

| 4006 4400h | 4006 44FFh | PTPEDMAC                                             | 6                         |                     | <b>3</b> ~ 5                     |       | PCLKA      | Ethernet DMA<br>Controller                                                                                                                                                                                   |

| 4006 4500h | 4006 45FFh | EPTPC_CFG, EPTPC,<br>EPTPCn                          | (3+wait cycle)*3          |                     | (wait cycle) ~<br>(2+wait cycle) |       | PCLKA      | Ethernet PTP<br>Controller                                                                                                                                                                                   |

| 4007 0000h | 4007 0EFFh | SCI0 to SCI9                                         | 5*4                       |                     | 2 ~ 4*4                          |       | PCLKA      | Serial<br>Communications<br>Interface                                                                                                                                                                        |

| 4007 0F00h | 4007 0FFFh | IRDA                                                 | 5                         |                     | 2 ~ 4                            |       | PCLKA      | IrDA Interface                                                                                                                                                                                               |

| 4007 2000h | 4007 2FFFh | SPI0, SPI1                                           | 5*5                       |                     | 2 ~ 4*5                          |       | PCLKA      | Serial Peripheral<br>Interface                                                                                                                                                                               |

| 4007 4000h | 4007 4FFFh | CRC                                                  | 5                         |                     | 2~4                              |       | PCLKA      | CRC Calculator                                                                                                                                                                                               |

| 4007 8000h | 4007 8FFFh | GPT32EHi, GPT32Ej,<br>GPT32k, GPT_OPS                | Refer to                  |                     | Table 3* <sup>6</sup>            |       | PCLKA      | General PWM<br>Timer                                                                                                                                                                                         |

| 4007 B000h | 4007 BFFFh | GPT_ODC                                              | 4                         |                     | 1~3                              |       | PCLKA      | PWM Delay<br>Generation Circuit                                                                                                                                                                              |

| 4008 0000h | 4008 1FFFh | KINT, CTSU                                           | 4                         |                     | 1~3                              |       | PCLKB      | Key Interrupt<br>Function,<br>Capacitive Touch<br>Sensing Unit                                                                                                                                               |

| 4008 4000h | 4008 4FFFh | AGTn                                                 | 7                         | 5                   | <b>4</b> ~ 6                     | 2~4   | PCLKB      | Asynchronous<br>General Purpose<br>Timer                                                                                                                                                                     |

| 4008 5000h | 4008 5FFFh | ACMPHSn                                              | 4                         |                     | 1~3                              |       | PCLKB      | High-Speed Analog<br>Comparator                                                                                                                                                                              |

| 4009 0000h | 4009 03FFh | USBFS                                                | 6                         |                     | 3~5                              |       | PCLKB      | USB 2.0 Full-<br>Speed Module                                                                                                                                                                                |

Date: Sep. 21, 2017

Table 3.2 Access cycles for non-GPT modules (3 of 3)

|            |            |             | Number of access cycles |                     |               |         |            |                                     |

|------------|------------|-------------|-------------------------|---------------------|---------------|---------|------------|-------------------------------------|

| Address    |            |             | ICLK = PCLK             |                     | ICLK > PCLK*1 |         |            |                                     |

| From       | То         | Peripherals | Read                    | Write               | Read          | Write   | Cycle unit | Related function                    |

| 4009 0400h | 4009 04FFh | USBFS       | 4                       |                     | 1~3           |         | PCLKB      | USB 2.0 Full-<br>Speed Module       |

| 4009 4000h | 4009 4FFFh | PDC         | 5                       |                     | 2~4           |         | PCLKB      | Parallel Data<br>Capture Unit       |

| 400E 0000h | 400E 4FFFh | GLCDC, DRW  | 5                       |                     | 2 ~ 4         |         | PCLKA      | Graphics LCD<br>Controller          |

| 400E 6000h | 400E 603Fh | JPEG        | <b>1</b> 5              | 7                   | 12 ~ 14       | 4~6     | PCLKA      | JPEG Codec                          |

| 400E 6040h | 400E 6FFFh | JPEG        | 7                       | 6                   | 4~6           | 3~5     | PCLKA      | JPEG Codec                          |

| 6400 0000h | 6400 000Fh | QSPI        | 5                       | 15 ~ * <sup>7</sup> | 2~4           | 12 ~ *7 | PCLKA      | Quad Serial<br>Peripheral Interface |

| 6400 0010h | 6400 0013h | QSPI        | 26 ~                    | 7 ~ *7              | 23 ~ *7       | 4 ~ *7  | PCLKA      | Quad Serial<br>Peripheral Interface |

| 6400 0014h | 6400 0037h | QSPI        | 5                       | 15 ~ * <sup>7</sup> | 2~4           | 12 ~ *7 | PCLKA      | Quad Serial<br>Peripheral Interface |

| 6400 0804h | 6400 0807h | QSPI        | 4                       | 4                   | 1~3           | 1~3     | PCLKA      | Quad Serial<br>Peripheral Interface |