発行日: 2016年9月27日

# **RENESAS TECHNICAL UPDATE**

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシア ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製品 | 品分類      | システムLSI                                                     | 発行番号   | TN-RIN-A | 011B/J                                                       | Rev.  | 第2版 |  |

|----|----------|-------------------------------------------------------------|--------|----------|--------------------------------------------------------------|-------|-----|--|

| 題名 | (Rev.8.0 | M3 シリーズ ユーザーズ・マニュアル 周:<br>00→Rev.9.00)<br>T内容:誤記訂正、新規機能追加など | 情報分類   | 技術情報     |                                                              |       |     |  |

| 適用 |          |                                                             | 対象ロット等 |          | R-IN32M3 シリーズ<br>ユーザーズ・マニュア                                  | ル周辺機能 | 七編  |  |

| 製品 | 下記参照     | Z.                                                          | 全ロット   | 関連資料     | • R-IN32M3-EC<br>• R-IN32M3-CL Rev.9.00<br>(R18UZ0006JJ0900) |       |     |  |

R-IN32M3 シリーズ ユーザーズ・マニュアル周辺機能編・R-IN32M3-EC・R-IN32M3-CL Rev.9.00 (R18UZ0006JJ0900) をリリースいたしました。その改定内容を第 2 版として全て記載し直しました。詳細については「2. 改訂内容」を参照願います。なお、"※要注意"マークがついている項目は、デバイスを動作させる上で重要な項目ですので、ご確認をお願い致します。

#### 1 適用製品

| V=7114X HH    |     |               |                      |

|---------------|-----|---------------|----------------------|

| 製品分類          |     | マーク型名         | <b>製品型名</b>          |

|               | 旧製品 | MC-10287F1    | MC-10287F1-HN4-A     |

| R-IN32M3-EC   |     | WC-10207F1    | MC-10287F1-HN4-M1-A  |

| R-INSZIVIS-EC | 現行品 | MC-10287BF1   | MC-10287BF1-HN4-A    |

|               |     | WC-10207 BF 1 | MC-10287BF1-HN4-M1-A |

|               | 旧製品 | D60510F1      | UPD60510F1-HN4-A     |

| R-IN32M3-CL   |     | D00310F1      | UPD60510F1-HN4-M1-A  |

| R-IN32IVI3-CL | 現行品 | D60510BF1     | UPD60510BF1-HN4-A    |

|               |     | D00310Bi 1    | UPD60510BF1-HN4-M1-A |

#### 2 改訂内容

(1/5)

| No | 訂正箇所(Rev9.00 見出し番号)                   | 該当ページ<br>(Rev9.00 番号) | 内容   | 2 版<br>追加 |

|----|---------------------------------------|-----------------------|------|-----------|

| 1  | 2. クロック機能/リセット機能                      | p.2-1                 | 補足   | *         |

| 2  | 2.1.1 内部クロックの定義                       | p.2-1                 | 補足   | *         |

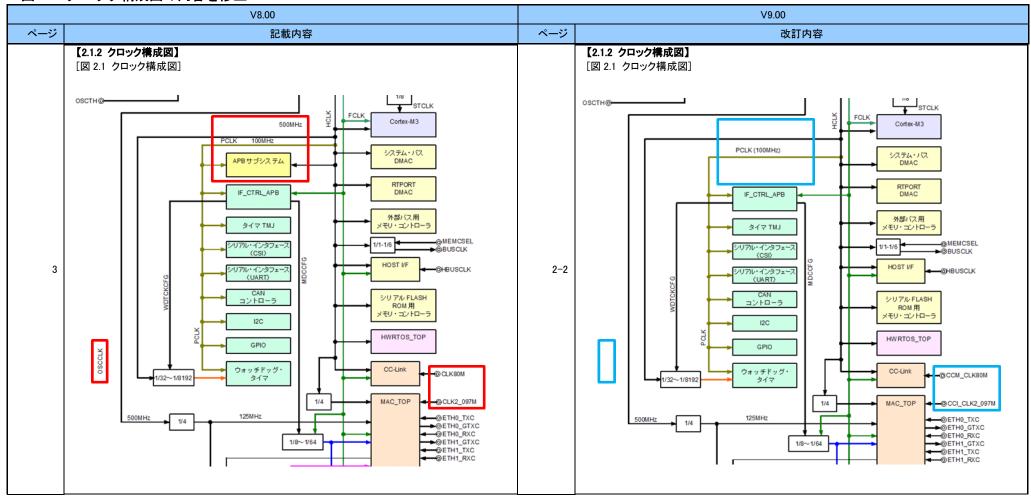

| 3  | 2.1.2 クロック構成図                         | p.2-2                 | 誤記訂正 | *         |

| 4  | 2.2.2 クロック制御レジスタ (CLKGTD0, CLKGTD1)   | p.2-4                 | 誤記訂正 | *         |

| 5  | 2.3.2 (5) リセット出力 (RSTOUTZ 出力)         | p.2-7                 | 誤記訂正 | *         |

| 6  | 2.3.4 (1) ソフトウェア・リセット・レジスタ (SFTRES1)  | p.2-10                | 表記変更 | *         |

| 7  | 3. CPU/内蔵 RAM                         | p.3.1                 | 補足   | *         |

| 8  | 3.4.2 リード・バッファ機能                      | p.3-3                 | 誤記訂正 |           |

| 9  | 3.5 内蔵データ RAM                         | p.3-4                 | 補足   | *         |

| 10 | 3.6 バッファ RAM                          | p.3-5                 | 誤記訂正 | *         |

| 11 | 4. バス構成                               | p.4-1                 | 誤記訂正 |           |

| 12 | 6.2 セマフォ                              | p.6-1                 | 誤記訂正 | *         |

| 13 | 6.6 サービス・コール                          | <b>-</b> .            | 表記変更 | *         |

| 14 | 7. ギガビット・イーサネット MAC                   | p.7-1.                | 表記変更 | *         |

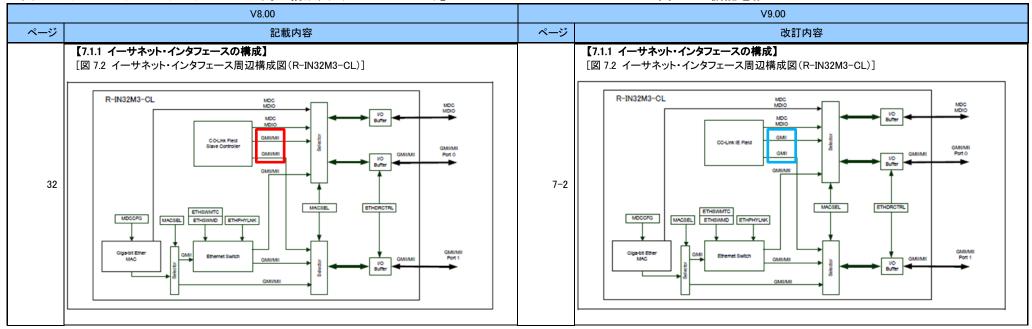

| 15 | 7.1.1 イーサネット・インタフェースの構成               | p.7-2                 | 表記変更 | *         |

| 16 | 7.3.1 (3) ギガビット・イーサネット MAC 制御レジスタ     | p.7-4, 7-5            | 誤記訂正 | *         |

| 17 | 7.3.1 (3) ギガビット・イーサネット MAC 制御レジスタ     | p.7-5                 | 表記変更 | *         |

| 18 | 7.3.1 (4) ハードウェア・ファンクション・コール・レジスタ     | p.7-5                 | 表記変更 |           |

| 19 | 7.3.2.1 MAC セレクト・レジスタ                 | p.7-6                 | 誤記訂正 |           |

| 20 | 7.3.3.1 MDC クロック選択レジスタ(MDCCFG)        | p.7-7                 | 誤記訂正 | *         |

| 21 | 7.3.4.1 MIIM レジスタ(GMAC_MIIM)          | p.7-9                 | 表記変更 | *         |

| 22 | 7.3.4.2 TX ID レジスタ(GMAC_TXID)         | p.7-10                | 補足   | *         |

| 23 | 7.3.4.3 TX RESULT レジスタ(GMAC_TXRESULT) | p.7-10                | 表記変更 | *         |

| 24 | 7.3.4.4 MODE レジスタ(GMAC_MODE)          | p.7-11                | 補足   | *         |

| 25 | 7.3.4.5 RX MODE レジスタ(GMAC_RXMODE)     | p.7-11                | 表記変更 | *         |

| 26 | 7.3.4.6 TX MODE レジスタ(GMAC_TXMODE)     | p.7-13                | 誤記訂正 |           |

| 27 | 7.3.4.6 TX MODE レジスタ(GMAC_TXMODE)     | p.7-14                | 表記変更 | *         |

| 28 | 7.3.4.7 RESET レジスタ(GMAC_RESET)        | p.7-15                | 補足   | *         |

| No       | 訂正箇所(Rev9.00 見出し番号)                                                     | 該当ページ            | 内容           | (2 |

|----------|-------------------------------------------------------------------------|------------------|--------------|----|

| INO      |                                                                         | (Rev9.00 番号)     | 四谷           | 追  |

| 29       | 7.3.4.8 PAUSE パケットデータレジスタ(GMAC_PAUSEn)                                  | p.7-15           | 補足           | 1  |

| 30       | 7.3.4.9 RX FLOW CONTROL レジスタ(GMAC_FLWCTL)                               | p.7-17           | 補足           | 1  |

| 31       | 7.3.4.10 PAUSE パケットレジスタ(GMAC_PAUSPKT)                                   | p.7-17           | 補足           | 7  |

| 32       | 7.3.4.11 MAC アドレス・レジスタ(GMAC_ADRnA, GMAC_ADRnB)                          | p.7-18           | 誤記訂正         | 7  |

| 33       | 7.3.4.12 RX FIFO ステータス・レジスタ(GMAC_RXFIFO)                                | p.7-19           | 補足           | 7  |

| 34       | 7.3.4.13 TX FIFO ステータス・レジスタ(GMAC_TXFIFO)                                | p.7-20           | 誤記訂正         | 7  |

| 35       | 7.3.4.14 TCPIPACC レジスタ(GMAC_ACC)                                        | p.7-21           | 補足           | 7  |

| 36       | 7.3.4.15 RX MAC ENABLE レジスタ(GMAC_RXMAC_ENA)                             | p.7-21           | 補足           | 7  |

| 37       | 7.3.4.16 LPI モード制御レジスタ(GMAC_LPI_MODE)                                   | p.7-22           | 補足           | 7  |

| 38       | 7.3.4.17 LPI CLIENT タイミング制御レジスタ(GMAC_LPI_TIMING)                        | p.7-22           | 誤記訂正         | 7  |

| 39       | 7.3.4.18 受信 Buffer 情報レジスタ(BUFID)                                        | p.7-23           | 誤記訂正         | 7  |

| 40       | 7.3.5 ハードウェア・ファンクション・コールレジスタ                                            | p.7-24           | 表記変更         |    |

| 41       | 7.3.5.1 ハードウェア・ファンクション・システム・コールレジスタ (SYSC)                              | p.7-24           | 機能追加         |    |

| 42       | 7.3.5.1 ハードウェア・ファンクション・システム・コールレジスタ (SYSC)                              | p.7-24           | 誤記訂正         | ٦, |

| 43       | 7.3.5.2 ハードウェア・ファンクション・引数レジスタ(R4-7)                                     | p.7-25           | <u> </u>     | Ť  |

| 44       | 7.3.5.3 ハードウェア・ファンクション・動作モード制御レジスタ (CMD)                                | p.7-26           | 機能追加         |    |

| 45       | 7.3.5.4 ハードウェア・ファンクション・戻り値レジスタ(R0, R1)                                  | p.7-26           | 補足           |    |

| 10       | 7.3.5.5 ハードウェア・ファンクション・タイプレジスタ(CNTX TYPE0)                              | p.1-20           | THIAC        | +  |

| 46       | 7.3.5.6 ハードウェア・ファンケション・状態レジスタ (CNTX_STATO)                              | p.7-27,28        | 機能追加         |    |

| -0       | 7.3.5.6 ハードウェア・ファングション・状態レジスタ (CNTX_STATO) 7.4.1 ハードウェア・ファンクション         | ρ. ι - Ζ ι , Ζ Ο | 汲化坦川         |    |

| 47       | 7.4.1.1 初期設定                                                            | p.7-29           | 機能追加         | +- |

| 47<br>48 |                                                                         | p.7-29           |              | 7  |

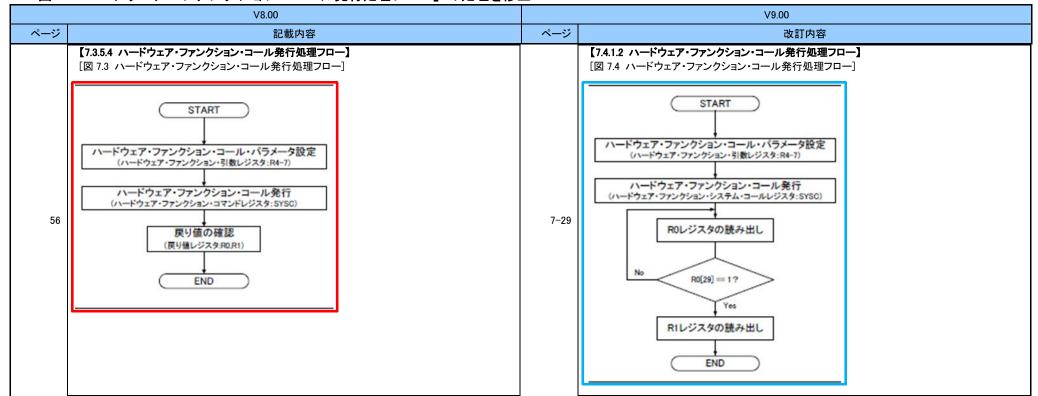

| +0       | 7.4.1.2 ハードウェア・ファンクション・コール発行処理フロー<br>7.4.1.3 Buffer Allocator           | p.1-29           | <b>识記訂止</b>  | 7  |

|          | 7.4.1.3 Bullet Allocator<br>7.4.1.4 MAC DMA コントローラ                      |                  |              | 7  |

| 49       | 7.4.1.4 MAC DMA コントローラ<br>7.4.1.5 バッファ RAM DMA コントローラ                   | p.7-30~50        | 機能追加         |    |

|          | 7.4.2 割り込み機能                                                            |                  |              |    |

| 50       | 7.4.1.1 初期設定                                                            | p.7-53           | 表記変更         | +  |

| 51       | 7.4.3.1 送信処理用バッファの獲得                                                    | p.7-54           | 表記发史<br>誤記訂正 | 7  |

|          |                                                                         |                  |              | _  |

| 52       | 7.4.3.2 送信データの作成                                                        | p.7-55           | 表記変更         | 7  |

| 53       | 7.4.2.1 初期設定                                                            | p.7-59           | 誤記訂正         |    |

| 54       | 7.4.4.5 受信データ・フォーマット ※要注意                                               | p.7-60           | 誤記訂正         | -  |

| 55       | 7.4.4.5 受信データ・フォーマット <u>※要注意</u>                                        | p.7-61           | 機能追加         | -  |

| 56       | 8.3.1 (2) スイッチ・コンフィギュレーション・レジスタ                                         | p.8-3            | 誤記訂正         |    |

| 57       | 8.3.1(3) ラーニング・インタフェース・レジスタ                                             | p.8-4            | 誤記訂正         | 7  |

| 58       | 8.3.2.1 イーサネット PHY LINK モード・レジスタ(ETHPHYLNK)                             | p.8-6            | 補足           | 7  |

| 59       | 8.3.2.1 イーサネット PHY LINK モード・レジスタ(ETHPHYLNK)                             | p.8-6            | 表記変更         | 7  |

| 60       | 8.3.3.5 入力ラーニング・ブロッキング・レジスタ (INPUT_LEARN_BLOCK)                         | p.8-14           | 誤記訂正         | 7  |

| 61       | 8.5.2 イーサネット・スイッチの初期化                                                   | p.8-98           | 誤記訂正         | -  |

| 62       | 8.5.2 イーサネット・スイッチの初期化                                                   | p.8-99           | 誤記訂正         | 7  |

| 33       | 9. 非同期 SRAM MEMC(ROM/SRAM)                                              | p.9-1            | 補足           | 7  |

| 64       | 9.2 (1) (a) SRAM, 外部 I/O 接続機能                                           | p.9-2            | 誤記訂正         |    |

| 65       | 9.2 (1) (b) ページ ROM 接続機能                                                | p.9-2            | 誤記訂正         | 1  |

| 36       | 9.3.3 スタティック・メモリ制御レジスタ 0-3 (SMC0-SMC3)                                  | p.9-8            | 誤記訂正         | ١, |

| 67       | 9.3.5 ライト・イネーブル切り替えレジスタ(WREN)                                           | p.9-12           | 表記変更         | 7  |

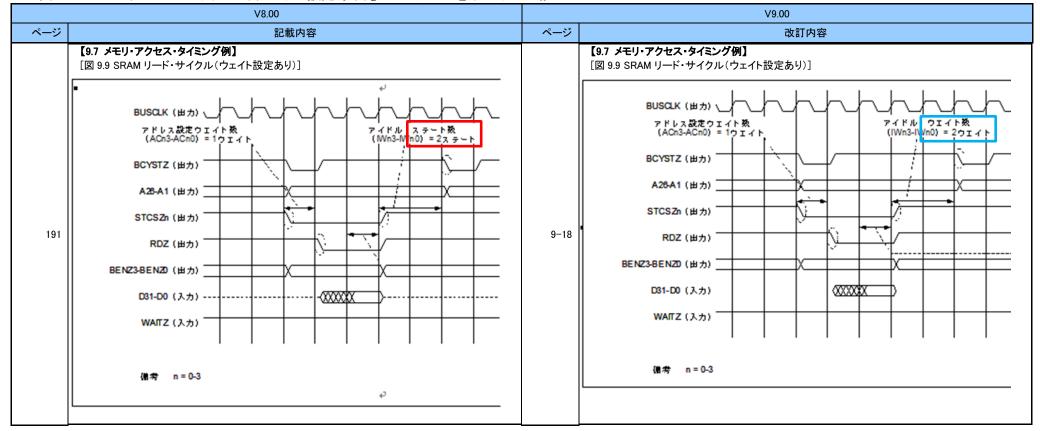

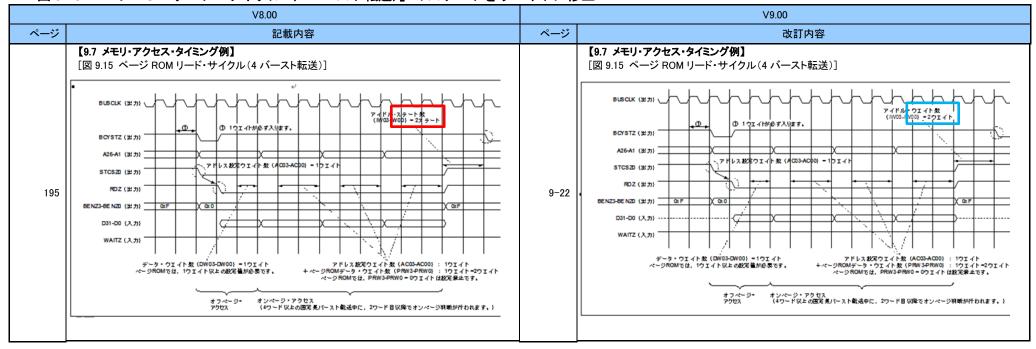

| 38       | 9.7 メモリ・アクセス・タイミング例                                                     | p.9-18~22        | 誤記訂正         | Τ, |

| 69       | 9.7 メモリ・アクセス・タイミング例                                                     | p.9-18           | 誤記訂正         | -  |

| 70       | 9.7 メモリ・アクセス・タイミング例                                                     | p.9-22           | <u> </u>     | 7  |

| 71       | 10. 同期式バースト・アクセス MEMC                                                   | p.10-1           | 誤記訂正         | 7  |

| 72       | 10.1 特徴                                                                 | p.10-1<br>p.10-1 | 誤記訂正         | +  |

| 73       | 10.1 特徴                                                                 | p.10-1           |              | _  |

|          |                                                                         | p.10-2<br>p.10-3 | 誤記訂正         | 7  |

| 74       | 10.2 制御レジスタ                                                             |                  | 誤記訂正         | 7  |

| 75<br>70 | 10.2.1 WAITZ選択レジスタ(WAITZSEL)                                            | p.10-4           | 誤記訂正         |    |

| 76       | 10.2.1 WAITZ選択レジスタ(WAITZSEL)                                            | p.10-4           | 補足           |    |

| 77       | 10.2.2 同期式バースト・アクセス MEMC 領域選択レジスタ(SMADSEL0-3)                           | p.10-7           | 誤記訂正         |    |

| 78       | 10.2.4 同期式 バースト・アクセス MEMC 動作設定レジスタ(SMC352MD) ※要注意                       | p.10-9           | 誤記訂正         | 7  |

| 79       | 10.2.6 サイクル設定レジスタ(SET_CYCLE)                                            | p.10-11          | 誤記訂正         | 7  |

| 80       | 10.2.8 同期式バースト・アクセス MEMC リフレッシュ設定レジスタ(REF_PERIOD0)<br><mark>※要注意</mark> | p.10-15          | 誤記訂正         | 7  |

| 31       | 10.2.10 同期式バースト・アクセス MEMC CSn モード・レジスタ (OPMODE0_n)                      | p.10-17          | 誤記訂正         | 7  |

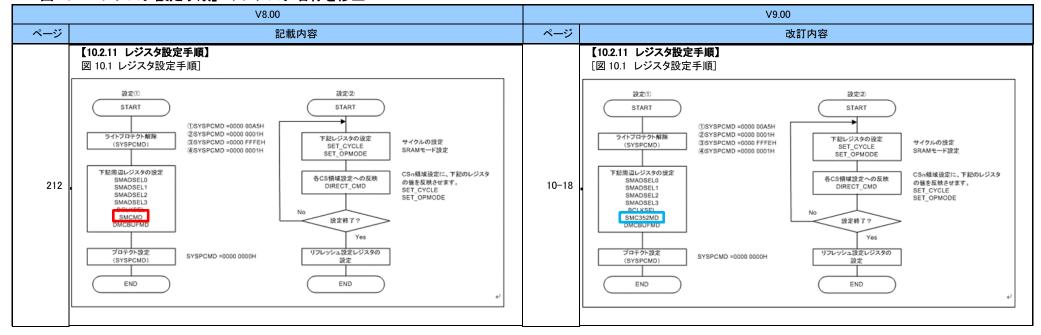

| 32       |                                                                         | p.10-18          | 誤記訂正         | 7  |

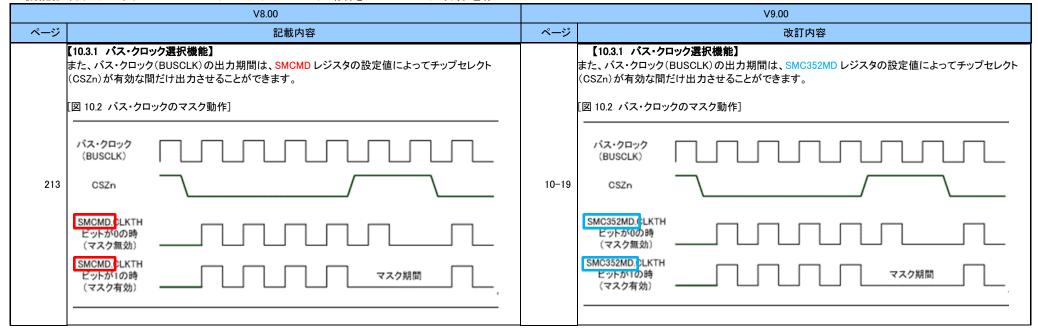

|          | 10.3.1 バス・クロック選択機能 10.2.11 レジスタ設定手順                                     | p.10-19          | 誤記訂正         | 7  |

| 33       | 10.3.1 ハス・プロック選択機能 10.2.11 レンスグ設定于順                                     | p. 10 10         | ᅈᅼᄓᄓ         | ,  |

**発行日**: 2016年9月27日

|            |                                                                            |                       |           | (3/5)          |

|------------|----------------------------------------------------------------------------|-----------------------|-----------|----------------|

| No         | 訂正箇所(Rev9.00 見出し番号)                                                        | 該当ページ<br>(Rev9.00 番号) | 内容        | 2 版<br>追加      |

| 85         | 10.3.4 ライト・イネーブル(WRZn)信号拡張機能                                               | p.10-21               | 誤記訂正      | *              |

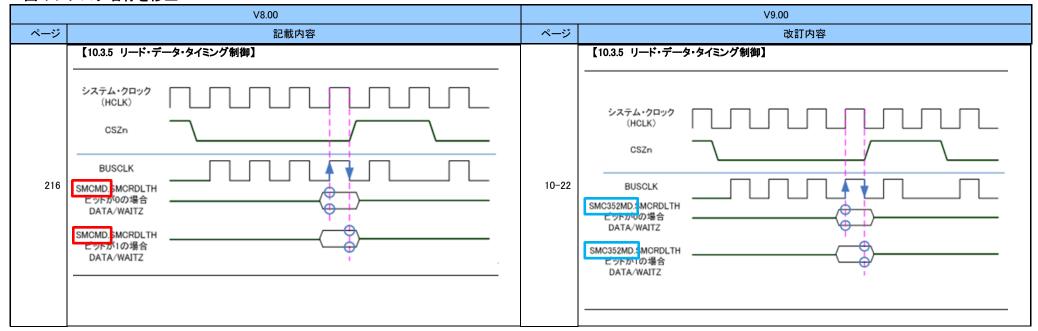

| 86         | 10.3.5 リード・データ・タイミング制御                                                     | p.10-22               | 誤記訂正      | *              |

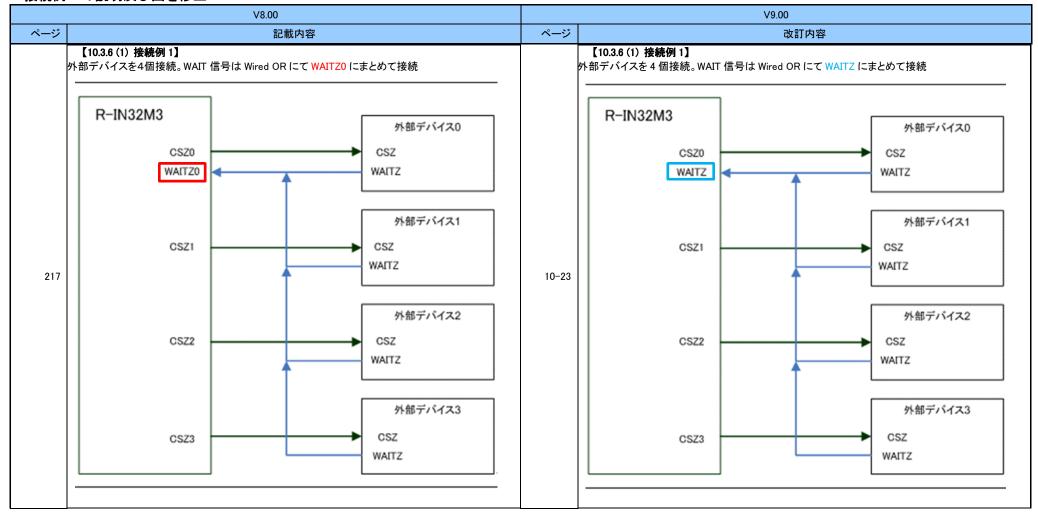

| 87         | 10.3.6 (1) 接続例 1                                                           | p.10-23               | 誤記訂正      | *              |

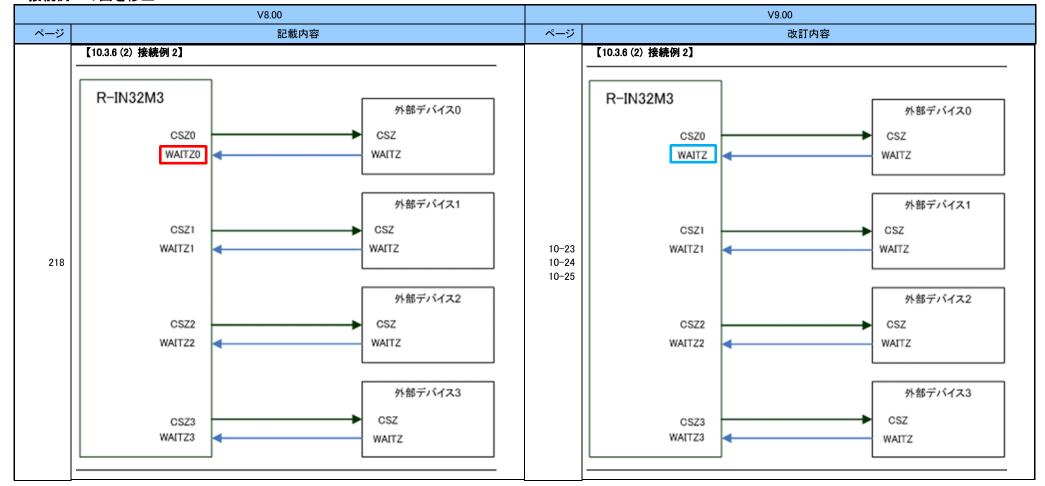

| 88         | 10.3.6 (2) 接続例 2                                                           | p.10-24               | 誤記訂正      | *              |

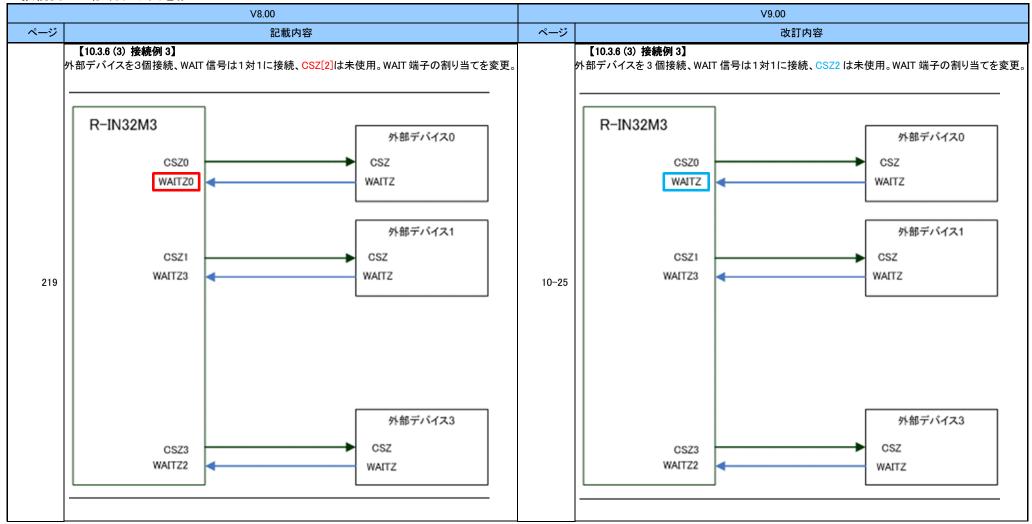

| 89         | 10.3.6 (3) 接続例 3                                                           | p.10-25               | 表記変更      | *              |

| 90         | 10.4.2 同期アクセス・タイミング                                                        | p.10-44               | 補足        |                |

| 91         | 11. 外部マイコン・インタフェース                                                         | p.11-1                | 補足        |                |

| 92         | 11.2.5 (2) HOSTIF バス制御レジスタ(HIFBCC)                                         | p.11-18               | 表記変更      | *              |

| 93         | 11.3.2 動作モードの選択                                                            | p.11-27               | 補足        | *              |

| 94         | 11.3.4 (2) HOSTIF 同期 SRAM 制御レジスタ 0(HIFEXT0)                                | p.11-29               | 補足        |                |

| 95         | 11.3.4 (3) HOSTIF 同期式 SRAM 制御レジスタ 1(HIFEXT1)                               | p.11-30               | 補足        |                |

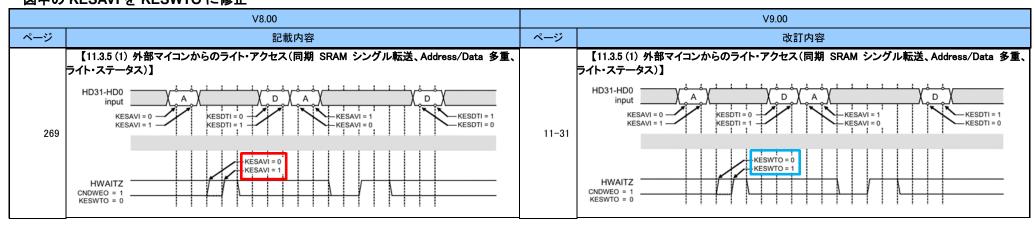

| 96         | 11.3.5 (1) 外部マイコンからのライト・アクセス(同期 SRAM シングル転送、<br>Address/Data 多重、ライト・ステータス) | p.11-31               | 誤記訂正      | *              |

| 97         | 11.3.5 (2) 外部マイコンからのライト・アクセス(同期 SRAM シングル転送、<br>Address/Data 多重、ライト・ストローブ) | p.11-32               | 誤記訂正      | *              |

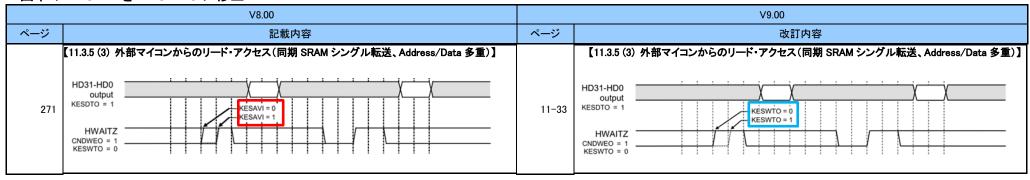

| 98         | 11.3.5 (3) 外部マイコンからのリード・アクセス(同期 SRAM シングル転送、<br>Address/Data 多重)           | p.11-33               | 誤記訂正      | *              |

| 99         | 12.2.1 転送モード制御レジスタ(SFMSMD)                                                 | p.12-3                | 誤記訂正      | *              |

| 100        | 12 章全体                                                                     | p.12-1~29             | 誤記訂正      | *              |

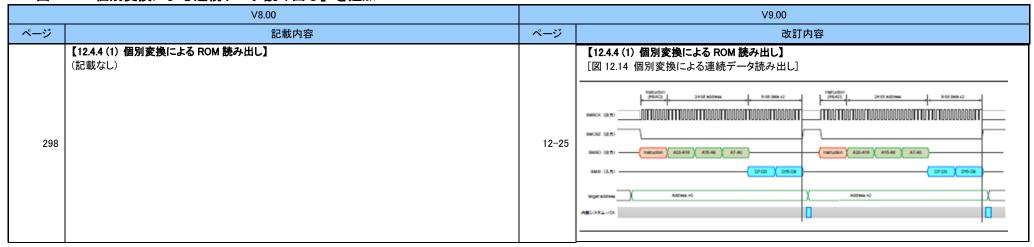

| 101        | 12.4.4 (1) 個別変換による ROM 読み出し                                                | p.12-25               | 補足        | *              |

| 102        | 12.4.4 (2) SPI バス・サイクル延長機能を用いた ROM 読み出し                                    | p.12-26               |           | *              |

| 103        | 12.4.4 (4) SPI バス・サイクル延長機能を用いた ROM 読み出し                                    | p.12-27               | 補足        | *              |

| 104        | 12.4.5 Deep Power-Down の自動解除                                               | p.12-28               |           | *              |

| 105        | 12.4.6 (3) 直接通信での SPI バス・サイクル生成                                            | p.12-29               |           |                |

| 106        | 13.1.1 概要                                                                  | p.13-4                | 補足        |                |

| 107        | 13.4.3.2 (4) チャネル・レジスタ・セット                                                 | p.13-21               | 補足        | *              |

| 108        | 13.4.3.2 (4) チャネル・レジスタ・セット                                                 | p.13-25               | 誤記訂正      | *              |

| 109        | 13.4.3.2 (4) チャネル・レジスタ・セット                                                 | p.13-32               |           | <del>*</del>   |

| 110        | 13.4.3.2 (4) チャネル・レジスタ・セット                                                 | p.13-33               | 表記変更      | *              |

| 111        | 13.4.4.2 (4) チャネル・レジスタ・セット                                                 | p.13-59               | 誤記訂正      | *              |

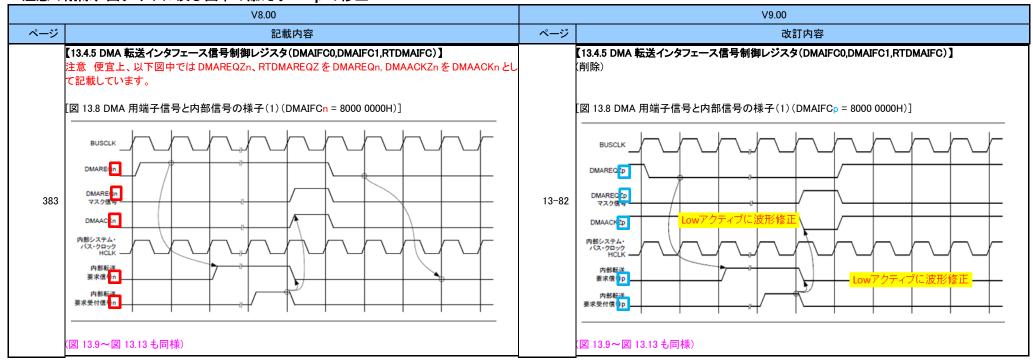

| 112        | 13.4.5 DMA 転送インタフェース信号制御レジスタ (DMAIFC0,DMAIFC1,RTDMAIFC)                    | p.13-80               | 誤記訂正      | <del>  ^</del> |

| 113        | 13.4.5 DMA 転送インタフェース信号制御レジスタ (DMAIFC0,DMAIFC1,RTDMAIFC)                    | p.13-81               | 誤記訂正      | <del> </del> ★ |

| 114        | 13.4.5 DMA 転送インタフェース信号制御レジスタ (DMAIFC0,DMAIFC1,RTDMAIFC)                    | p.13-82               | 誤記訂正      | <del>*</del>   |

| 115        | 13.4.6 DMA トリガ要因選択レジスタ(DTFRn, RTDTFR)                                      | p.13-85               | 誤記訂正      | <del>  ^</del> |

| 116        | 13.4.6 DMA トリガ要因選択レジスタ(DTFRn, RTDTFR)                                      | p.13-88               | 誤記訂正      | <del>*</del>   |

| 117        | 13.5.1 BUSCLK 同期                                                           | p.13-89               | 誤記訂正      | <b>★</b>       |

| 118        | 13.5.2 転送要求とアクノリッジ                                                         | p.13-89               | 表記変更      | <b>★</b>       |

| 119        | 13.7.1 レジスタ・モードとリンク・モードの選択                                                 | p.13-09<br>p.13-91    | 誤記訂正      | *              |

| 120        | 13.7.2 (1) レジスタ・モードとりファ・モードの医療                                             | p.13-91               |           |                |

| 121        | 13.7.2 (1) レンスタ・モートの動TFフロー<br>  13.7.2 (2) レジスタの設定                         | p.13-94<br>p.13-96    | 誤記訂正      | <b>★</b>       |

|            |                                                                            |                       | 誤記訂正      | -              |

| 122<br>123 | 13.7.2 (3) レジスタの設定例                                                        | p.13-98<br>p.13-99    | 誤記訂正      | *              |

| 123        | 13.7.2 (3) レジスタの設定例   13.7.3 (1) リンク・エードの動作フロー                             |                       | 誤記訂正      | *              |

| 124        | 13.7.3 (1) リンク・モードの動作フロー<br>  13.7.3 (2) レジスタ設定                            | p.13-102              |           | _              |

|            | ` '                                                                        | p.13-103              |           | *              |

| 126        | 13.8.3 (2) エッジ検出   13.8.3 (2) エッジ検出   13.8.3 (2) エッジ検出                     | p.13-122              | 誤記訂正      | *              |

| 127        | 13.8.3 (3) レベル検出   13.8.4 DMA スカノリッジ出力機能                                   | p.13-123              | 誤記訂正      | *              |

| 128        | 13.8.4 DMA アクノリッジ出力機能                                                      | p.13-124              | 表記変更      | *              |

| 129        | 13.8.4 (1) DMA 転送要求の要因ごとのアクノリッジ信号モード指定                                     | p.13-125              | 誤記訂正      | *              |

| 130        | 13.8.4 (2) パルス出力                                                           | p.13-126              | 表記変更      | *              |

| 131        | 13.8.4 (3) レベル出力                                                           | p.13-127              | 補足<br># D | *              |

| 132        | 13.8.4 (4) バス・サイクル出力                                                       | p.13-128              | 補足        | *              |

| 133        | 13.8.7 強制掃き出し機能                                                            | p.13-134              | 誤記訂正      | *              |

| 134        | 13.9.1 設定例 1 (レジスタ・モード、シングル転送モード、ハードウエア・トリガ)                               | p.13-142              | 誤記訂正      | *              |

| 135        | 13.9.2 設定例 2 (レジスタ・モード、ブロック転送モード、ソフトウェア・トリガ)                               | p.13-145              | 誤記訂正      | *              |

| 136        | 13.9.2 設定例 2 (レジスタ・モード、ブロック転送モード、ソフトウェア・トリガ)                               | p.13-146              | 誤記訂正      | *              |

| 137        | 13.9.3 設定例3 (レジスタ・モード:連続実行、ブロック転送モード、ソフトウェア・トリガ)                           | p.13-148              | 誤記訂正      | *              |

| 138        | 14.1 TAUJ2 の特徴                                                             | p.14-1                | 表記変更      | *              |

| 139        | 14.1 TAUJ2 の特徴                                                             | p.14-2                | 誤記訂正      | *              |

| 140        | 14.3.2 (1) TAUJ2 プリスケーラ・クロック選択レジスタ(TAUJ2TPS)                               | p.14-12               | 表記変更      | *              |

| 141        | 14.3.3 (2) TAUJ2 チャネル・カウンタ・レジスタ(TAUJ2CNTm)                                 | p.14-15               | 表記変更      | *              |

| 142        | 14.3.3 (3) TAUJ2 チャネル・モード OS レジスタ(TAUJ2CMORm)                              | p.14-19               | 補足        | *              |

|            |                                                                            |                       |           |                |

**発行日**: 2016 年 9 月 27 日

| No  | 訂正箇所(Rev9.00 見出し番号)                                            | 該当ページ<br>(Rev9.00 番号) | 内容   | 2 版 追力 |

|-----|----------------------------------------------------------------|-----------------------|------|--------|

| 143 | 14.5.1 チャネル連動動作ルール                                             | p.14-31               | 表記変更 | *      |

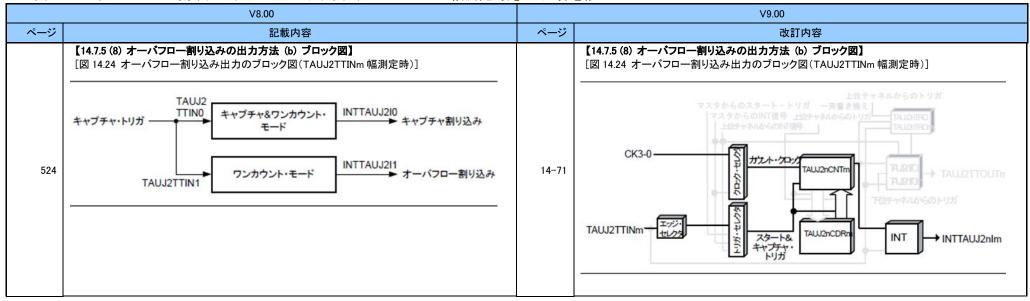

| 144 | 14.7.5 (8) オーバフロー割り込みの出力方法 (b) ブロック図                           | p.14-71               | 表記変更 | *      |

| 145 | 15. ウインドウ・ウォッチドッグ・タイマ A(WDTA)                                  | p.15-1                | 表記変更 | *      |

| 146 | 15.1 WDTA の特徴                                                  | p.15-1                | 表記変更 | *      |

| 147 | 15.2 機能概要                                                      | p.15-2                | 表記変更 | *      |

| 148 | 16. アシンクロナス・シリアル・インタフェース J(UARTJ)                              | p.16-1                | 表記変更 | *      |

| 149 | 16.1 UARTJn の特徴                                                | p.16-1                | 表記変更 | *      |

| 150 | 16.1 UARTJn の特徴                                                | p.16-2                | 誤記訂正 | *      |

| 151 | 16.4 (2) UARTJn 制御レジスタ 1(URTJnCTL1)                            | p.16-9                | 誤記訂正 |        |

| 152 | 16.4 (5) UARTJn ステータス・レジスタ 0(URTJnSTR0)                        | p.16-15               | 補足   |        |

| 153 | 16.4 (6) UARTJn ステータス・レジスタ 1(URTJnSTR1)                        | p.16-16               | 補足   |        |

| 154 | 16.4 (6) UARTJn ステータス・レジスタ 1(URTJnSTR1)                        | p.16-17               | 補足   |        |

| 155 | 16.5.2 (1) 受信エラー発生時の INTUAJnTIR                                | p.16-29               | 誤記訂正 | *      |

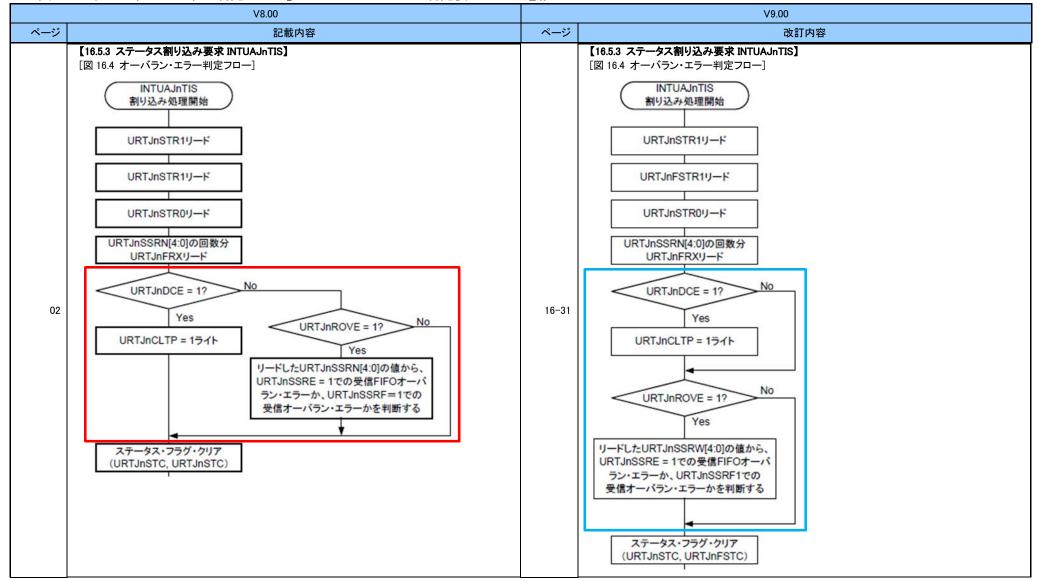

| 156 | 16.5.3 ステータス割り込み要求 INTUAJnTIS ※要注意                             | p.16-31               | 誤記訂正 |        |

| 157 | 16.6.6 (2) 受信の開始と停止                                            | p.16-47               | 補足   |        |

| 158 | 16.7 ボー・レート・ジェネレータ                                             | p.16-54               | 補足   |        |

| 159 | 17. クロック同期シリアル・インタフェース H (CSIH)                                | p.17-1                | 表記変更 | *      |

| 60  | 17.1 CSIH の特徴                                                  | p.17-1                | 表記変更 | *      |

| 61  | 17.1 CSIH の特徴                                                  | p.17-2                | 誤記訂正 | *      |

| 62  | 17.3 CSIH 制御レジスタ                                               | p.17-14               | 誤記訂正 | *      |

| 63  | 17.3 (4) CSIH ステータス・レジスタ 0(CSIHnSTR0)                          | p.17-16               | 表記変更 | *      |

| 64  | 17.3 (6) CSIH メモリ制御レジスタ 0(CSIHnMCTL0)                          | p.17-19               | 誤記訂正 | *      |

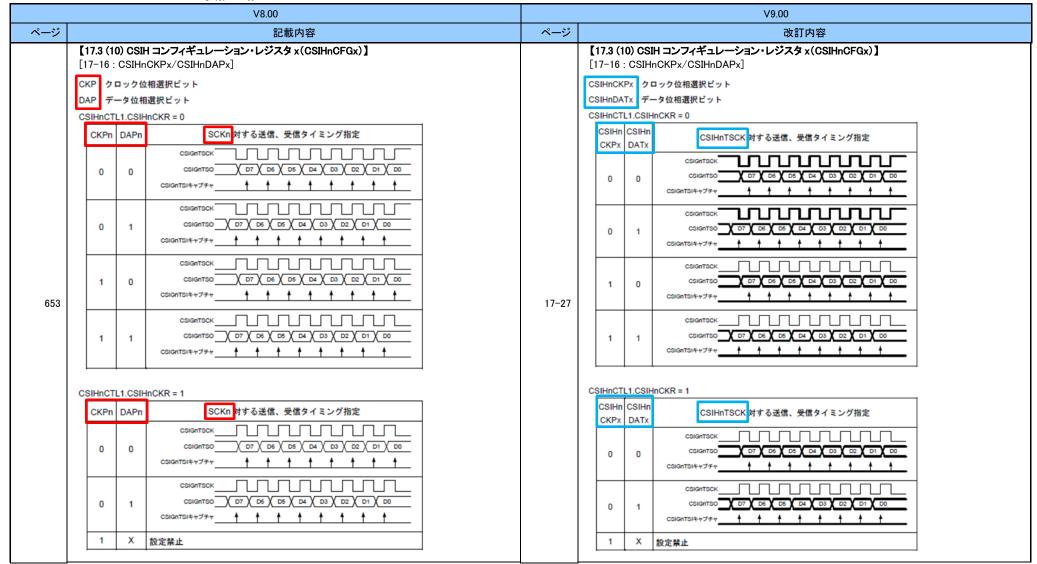

| 65  | 17.3 (10) CSIH コンフィギュレーション・レジスタ x(CSIHnCFGx)                   | p.17-27               | 表記変更 | *      |

| 166 | 17.3 (10) CSIH コンフィギュレーション・レジスタ x(CSIHnCFGx)                   | p.17-28               | 補足   | *      |

| 167 | 17.3 (10) CSIH コンフィギュレーション・レジスタ x(CSIHnCFGx)                   | p.17-29               | 表記変更 | *      |

| 68  | 17.3 (10) CSIH コンフィギュレーション・レジスタ x(CSIHnCFGx)                   | p.17-30               | 表記変更 | *      |

| 69  | 17.3 (10) CSIH コンフィギュレーション・レジスタ x(CSIHnCFGx)                   | p.17-31               | 補足   | 7      |

| 70  | 17.3 (14) CSIH ハーフ・ワード・アクセス用受信データ・レジスタ 0 (CSIHnRX0H)           | p.17-36               | 誤記訂正 | 4      |

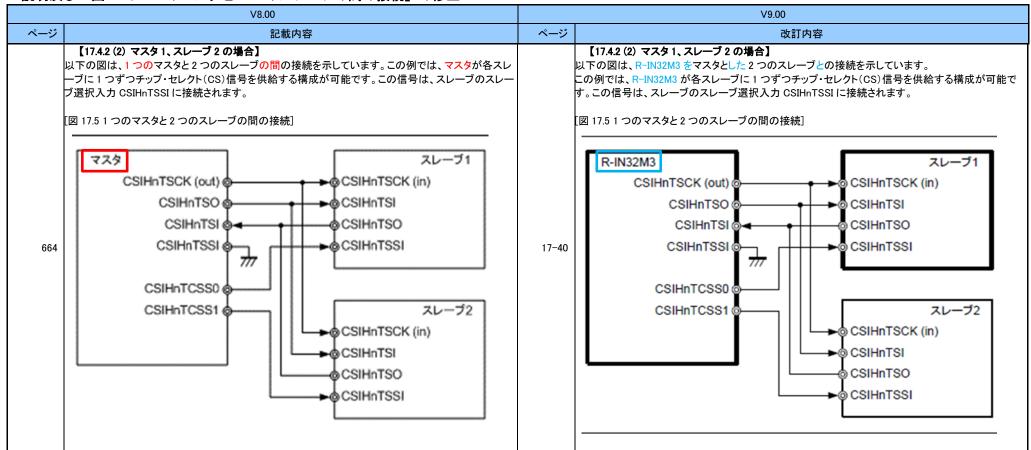

| 71  | 17.4.2 (2) マスタ 1、スレーブ 2 の場合                                    | p.17-40               | 表記変更 | 4      |

| 72  | 17.4.3 (1) コンフィギュレーション・レジスタ                                    | p.17-42               | 誤記訂正 | *      |

| 73  | 17.4.14 ループ・バック・モード                                            | p.17-81               | 誤記訂正 | *      |

| 74  | 18. I2C バス(IICB)                                               | p.18-1                | 表記変更 | 4      |

| 75  | 18.1 IICB の特徴                                                  | p.18-1                | 表記変更 | 4      |

| 176 | 18.1 IICB の特徴                                                  | p.18-1                | 誤記訂正 | 4      |

| 177 | 18.3 (6) (a) IICBnWL, IICBnWH レジスタによる転送クロック設定方法                | p.18-16               | 誤記訂正 |        |

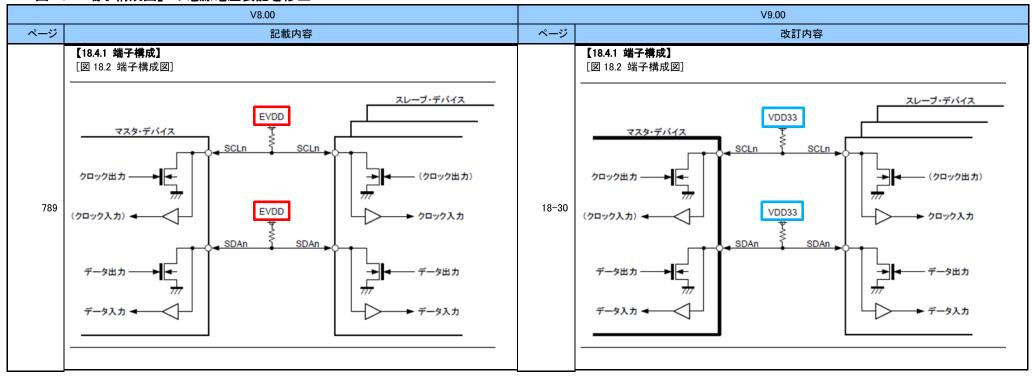

| 178 | 18.4.1 端子構成                                                    | p.18-30               | 誤記訂正 | *      |

| 79  | 18.6.1(4) シングル転送モード(スレーブ送信)の通信例                                | p.18-44               | 補足   | 4      |

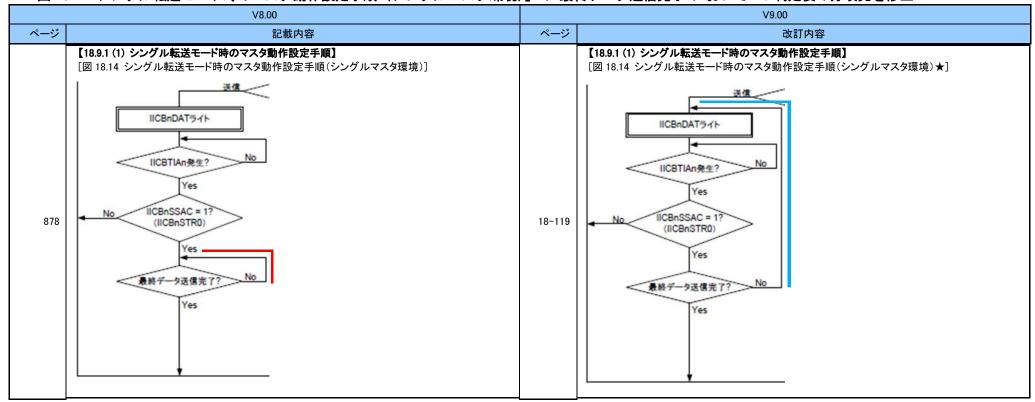

| 80  | 18.9.1 (1) シングル転送モード時のマスタ動作設定手順                                | p.18-119              | 誤記訂正 |        |

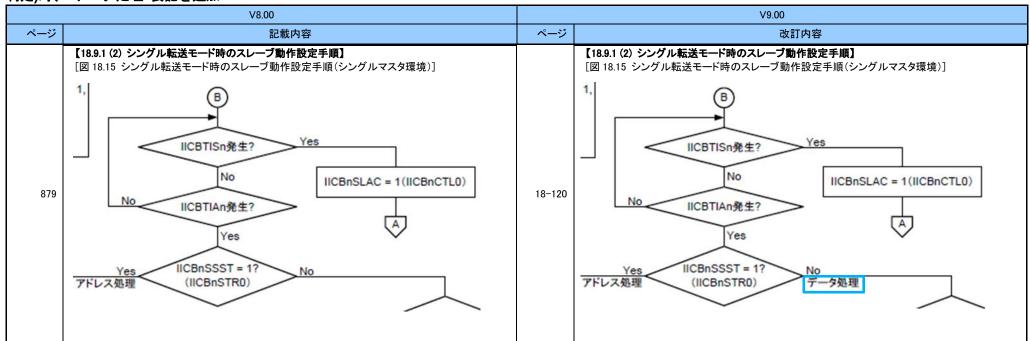

| 81  | 18.9.1 (2) シングル転送モード時のスレーブ動作設定手順                               | p.18-120              | 誤記訂正 | 7      |

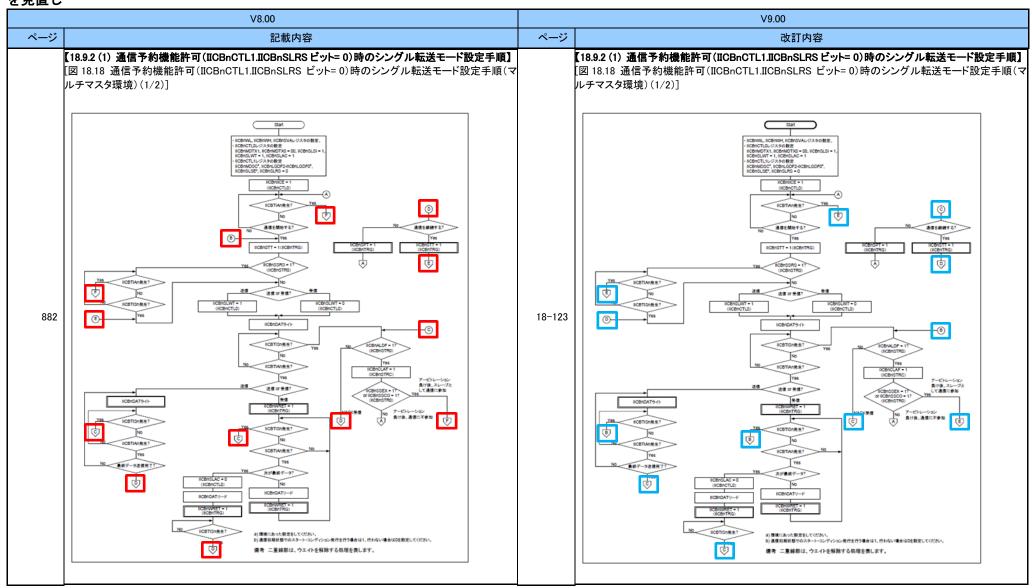

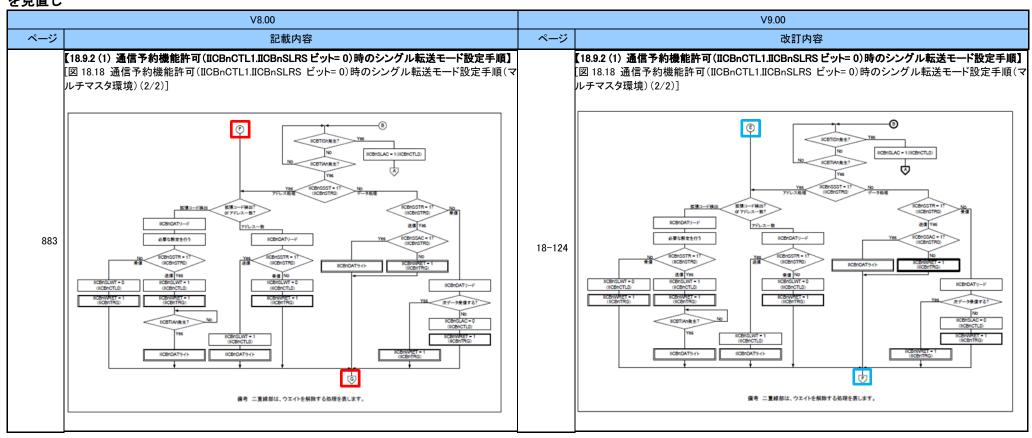

| 82  | 18.9.2 (1) 通信予約機能中可 (ICBnCTL1.IICBnSLRS ビット=0) 時のシングル転送モード設定手順 | p.18-123              | 誤記訂正 |        |

| 83  | 18.9.2 (1) 通信予約機能中可 (ICBnCTL1.IICBnSLRS ビット=0) 時のシングル転送モード設定手順 | p.18-124              | 誤記訂正 |        |

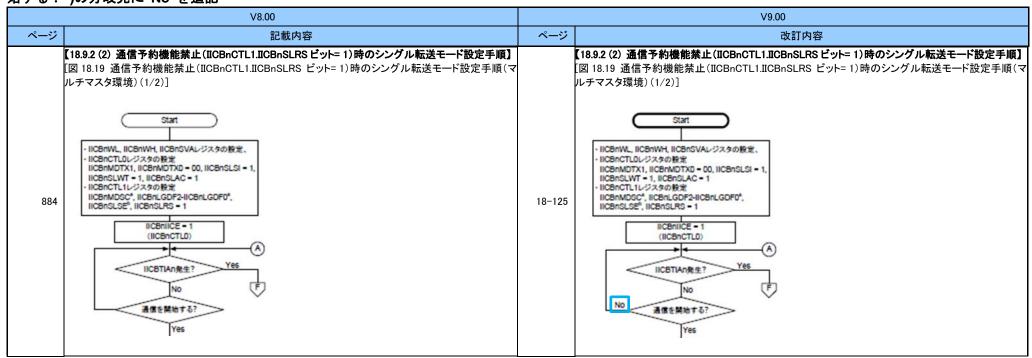

| 84  | 18.9.2 (2) 通信予約機能禁止 (ICBnCTL1.IICBnSLRS ビット=1) 時のシングル南送モート設定手順 | p.18-125              | 補足   |        |

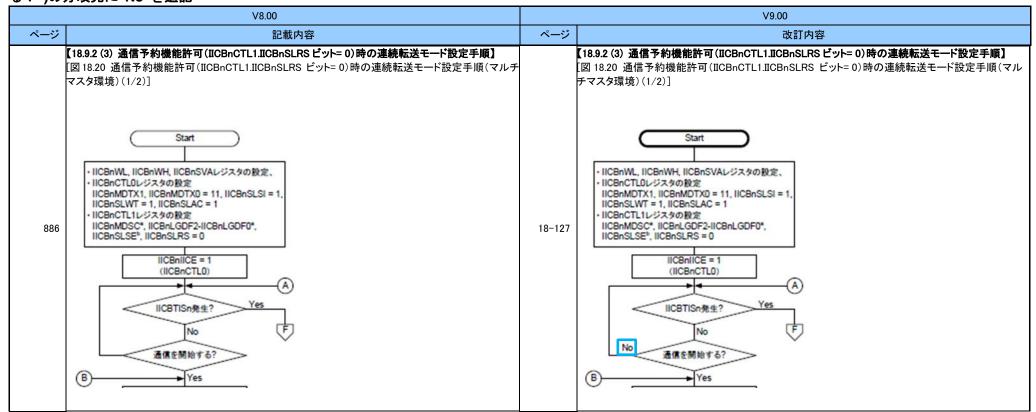

| 85  | 18.9.2 (3) 通信予約機能中可 (IICBnCTL1.IICBnSLRS ビット=0) 時の連続送モード設定手順   | p.18-127              | 補足   |        |

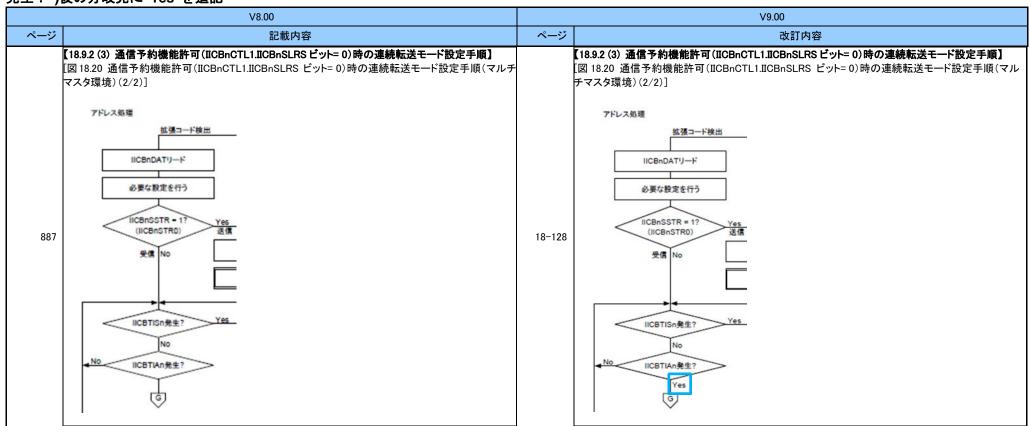

| 86  | 18.9.2 (3) 通信予約機能中可 (IICBnCTL1.IICBnSLRS ビット=0) 時の連続送モード設定手順   | p.18-128              | 補足   |        |

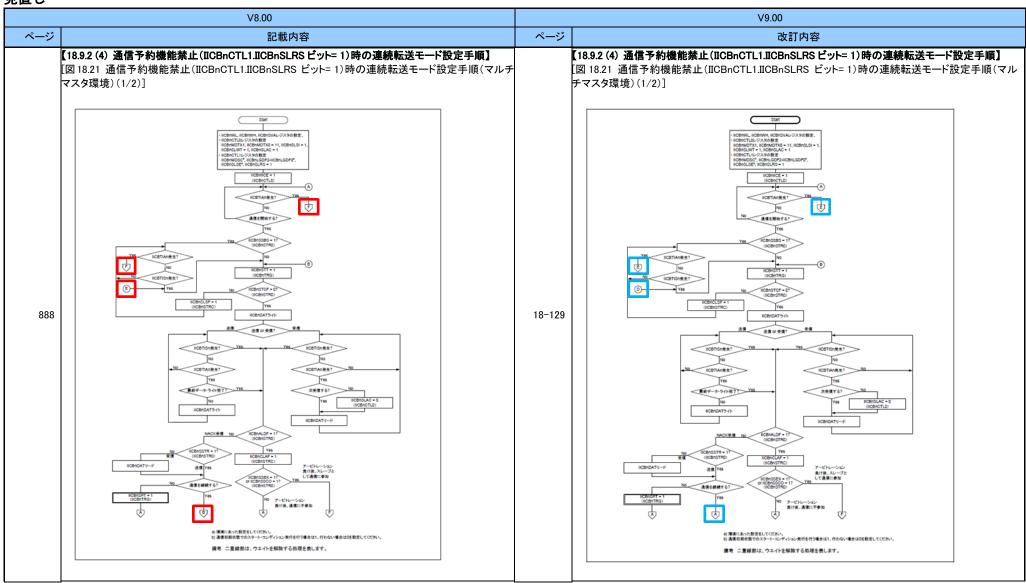

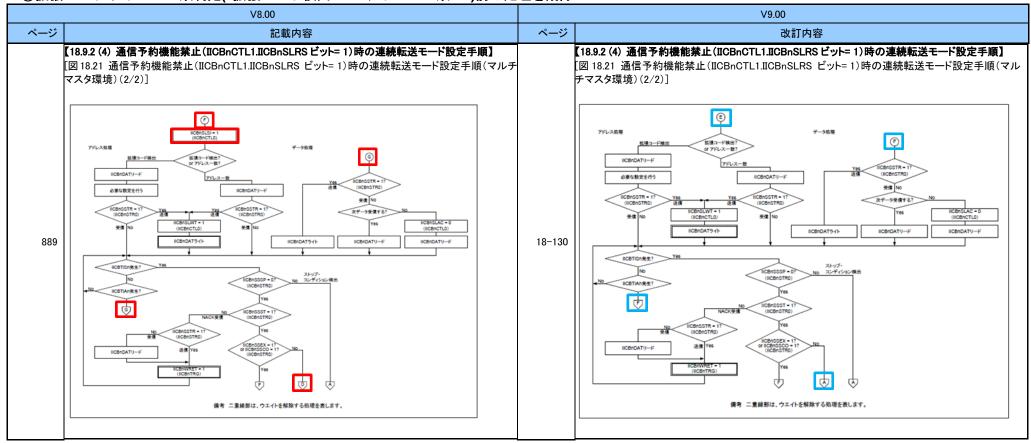

| 87  | 18.9.2 (4) 通信予約機能禁止 (IICBnCTL1.IICBnSLRS ビット=1) 時の連続設士―下設定手順   | p.18-129              | 補足   |        |

| 88  | 18.9.2 (4) 通信予約機能禁止 (IICBnCTL1.IICBnSLRS ビット=1) 時の連続送モード設定手順   | p.18-130              | 誤記訂正 |        |

| 89  | 19. CAN コントローラ(FCN)                                            | p.19-1                | 表記変更 | +      |

| 90  | 19.1 FCN の特徴                                                   | p.19-1                | 表記変更 | 1      |

| 91  | 19.1 R-IN32M3 の FCN の特徴                                        | p.19-2                | 誤記訂正 | +      |

| 92  | 19.3.2 (1) FCNn グローバル・レジスタと FCNn モジュール・レジスタ                    | p.19-12               | 誤記訂正 | 1      |

| 93  | 19.5.2 (1) FCNn モジュール・マスク制御レジスタ(FCNnCMMKCTLaH, FCNnCMMKCTLaW)  | p.19-32               | 誤記訂正 | 1      |

| 94  | 19.5.2 (3) FCNn モジュール最終エラー情報レジスタ(FCNnCMLCSTR)                  | p.19-41               | 誤記訂正 | 7      |

| 95  | 19.13.1 ボー・レートの設定条件                                            | p.19-109              | 誤記訂正 | 7      |

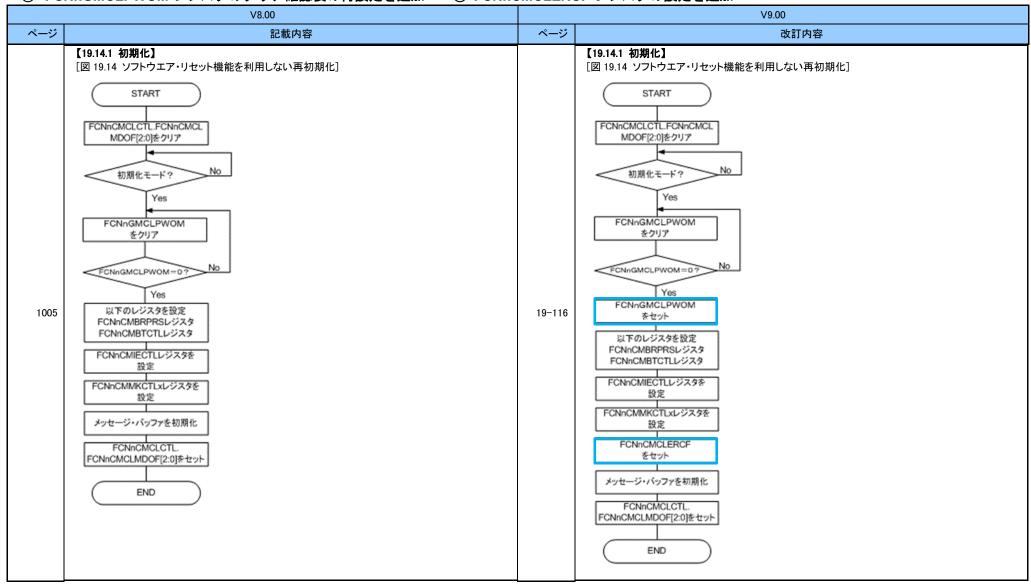

| 96  | 19.14.1 初期化                                                    | p.19-116              | 補足   |        |

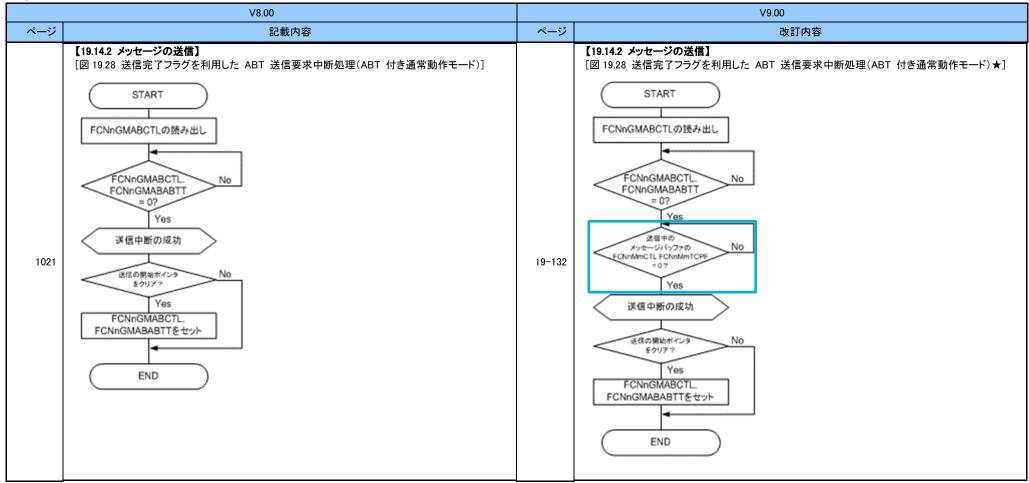

| 97  | 19.14.2 メッセージの送信                                               | p.19-132              | 補足   |        |

| 98  | 20. CC-Link インタフェース                                            | p.20-1                | 表記変更 | 7      |

| 99  | 20.1.2 CC-Link バス・サイズ制御レジスタ(CCBSC)                             | p.20-2                | 誤記訂正 | +      |

|     | 20.1.3 CC-Link バス・ブリッジ制御レジスタ 0(CCSMC0)                         | p.20-2                | 表記変更 | 4      |

| 200 |                                                                |                       |      | _      |

| 201 | 20.1.4 CC-Link バス・ブリッジ制御レジスタ 1(CCSMC1)                         | p.20-2                | 表記変更 | *      |

|     |                                                                |                       |      | _      |

**発行日**: 2016年9月27日

|     |                                                    |                       |      | (5/5      |

|-----|----------------------------------------------------|-----------------------|------|-----------|

| No  | 訂正箇所(Rev9.00 見出し番号)                                | 該当ページ<br>(Rev9.00 番号) | 内容   | 2 版<br>追加 |

| 204 | 21.1 レジスター覧                                        | p.21-2                | 表記変更 |           |

| 205 | 21.3 IDCODE レジスタ(IDCODE)                           | p.21-3                | 表記変更 | *         |

| 206 | 21.7 システム・プロテクト・コマンド・レジスタ (SYSPCMD)                | p.21-7                | 表記変更 | *         |

| 207 | 21.9.1 タイマ入力機能選択レジスタ (SELCNT)                      | p.21-10               | 表記変更 | *         |

| 208 | 21.9.1 タイマ入力機能選択レジスタ (SELCNT)                      | p.21-11               | 表記変更 | *         |

| 209 | 21.9.2 タイマ・トリガ要因レジスタ(TMTFR0-3)                     | p.21-15               | 誤記訂正 | *         |

| 210 | 21.10.1 ノイズ・フィルタ設定レジスタ 0-3 (NFC0-3)                | p.21-17               | 補足   | *         |

| 211 | 21.11 外部割り込みモード・レジスタ 0, 1, 2 (INTM0, INTM1, INTM2) | p.21-21               | 誤記訂正 | *         |

| 212 | 21.11 外部割り込みモード・レジスタ 0, 1, 2 (INTM0, INTM1, INTM2) | p.21-22               | 誤記訂正 | *         |

| 213 | 21.12.2 トリガ同期式ポート要因レジスタ(RP0TFR-RP3TFR)             | p.21-29               | 誤記訂正 | *         |

| 214 | 21.14 CPU バス動作モード・レジスタ(CPUBUSMD)                   | p.21-31               | 表記変更 | *         |

| 215 | 21.15 SRAM ブリッジ選択レジスタ(SRAMBRSEL)                   | p.21-32               | 機能追加 |           |

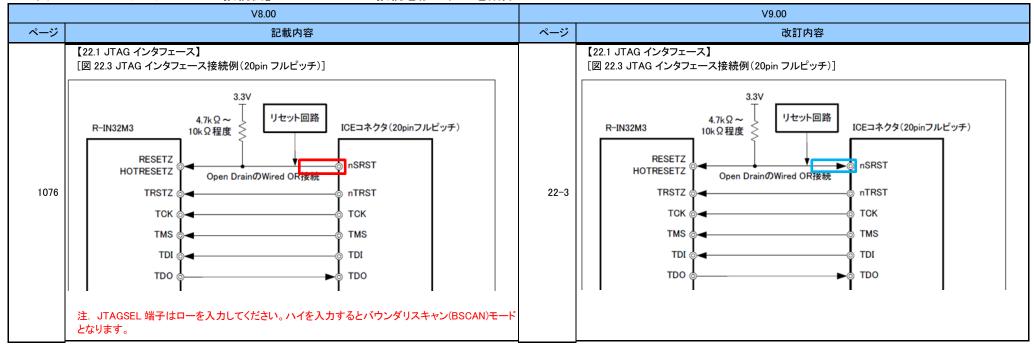

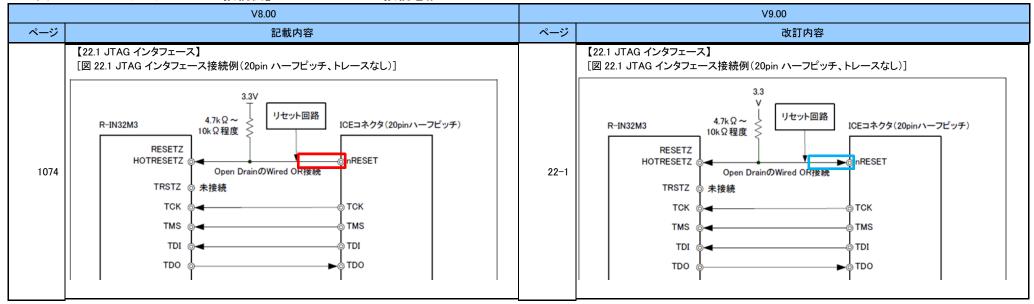

| 216 | 22.1 JTAG インタフェース                                  | p.22-1                | 誤記訂正 | *         |

| 217 | 22.1 JTAG インタフェース                                  | p.22-2                | 誤記訂正 | *         |

| 218 | 22.1 JTAG インタフェース                                  | p.22-3                | 誤記訂正 | *         |

**発行日**: 2016 年 9 月 27 日

#### No.1 <u>2. クロック機能</u>

# 2章タイトルを変更

|     | V8.00       | V9.00 |                    |  |  |  |  |

|-----|-------------|-------|--------------------|--|--|--|--|

| ページ | 記載内容        | ページ   | 改訂内容               |  |  |  |  |

| 2   | 【2. クロック機能】 | 2-1   | 【2. クロック機能/リセット機能】 |  |  |  |  |

# No.2 2.1.1 内部クロックの定義

#### LKOUT25M0-1 に注 3 を追加

|     | V8.00                                       | V9.00 |                                                           |  |  |  |

|-----|---------------------------------------------|-------|-----------------------------------------------------------|--|--|--|

| ページ | 記載内容                                        | ページ   | 改訂内容                                                      |  |  |  |

| 2   | 【2.1.1 内部クロックの定義】<br>・クロック信号 : CLKOUT25M0-1 | 2-1   | 【2.1.1 内部クロックの定義】<br>・クロック信号 : CLKOUT25M0-1 <sup>注3</sup> |  |  |  |

| 2   | 注 1<br>2                                    | 2-1   | 注 1<br>2<br>3. CLKOUT25M0-1 端子は、R-IN32M3-CL 版のみ搭載しています。   |  |  |  |

#### No.3 2.1.2 クロック構成図

#### 図 2.1 クロック構成図の内容を修正

#### No.4 <u>2.2.2 クロック制御レジスタ(CLKGTD0, CLKGTD1)</u>

#### bit13 のビット名を修正

|     | V8.00                                                         | V9.00 |                                                                |  |  |  |

|-----|---------------------------------------------------------------|-------|----------------------------------------------------------------|--|--|--|

| ページ | 記載内容                                                          | ページ   | 改訂内容                                                           |  |  |  |

|     | 【2.2.2 クロック制御レジスタ(CLKGTD0, CLKGTD1)】<br>・ビットフィールド図(13): GC2C0 |       | 【2.2.2 クロック制御レジスタ(CLKGTD0, CLKGTD1)】<br>・ビットフィールド図(13): GCI2C0 |  |  |  |

| 5   | [13: GC2C0]<br>I2C バス(I2C0)機能(1:動作 / 0:停止)                    | 2–4   | [13: GCI2C0]<br>I2C バス(I2C0)機能(1:動作 / 0:停止)                    |  |  |  |

#### No.5 <u>2.3.2 (5) リセット出力(RSTOUTZ 出力)</u>

# 「表 2.1 リセット発生要因とリセット対象」の内容を修正

|     | V8.00                                                     |          |     |                              |         |          |       |      |     | V9.00                             |          |     |                              |         |          |       |      |

|-----|-----------------------------------------------------------|----------|-----|------------------------------|---------|----------|-------|------|-----|-----------------------------------|----------|-----|------------------------------|---------|----------|-------|------|

| ページ |                                                           |          |     | 記載内容                         |         |          |       |      | ページ | 改訂内容                              |          |     |                              |         |          |       |      |

|     | 【2.3.2 (5) リセット出力(RSTOUTZ 出力)】<br>[表 2.1 リセット発生要因とリセット対象] |          |     |                              |         |          |       |      |     | 【2.3.2 (5) リセット出<br>[表 2.1 リセット発生 |          |     | - · <del>-</del>             |         |          |       |      |

|     |                                                           |          |     | リセ                           | ット対象    | _        |       |      |     |                                   | リセット対象   |     |                              |         |          |       |      |

|     | リセット発生要因                                                  | 命令 RAM   | PLL | CC-Link IE                   | CC-Link | EtherCAT | CPU の | その他の |     | リセット発生要因                          | 命令 RAM   | PLL | CC-Link IE                   | CC-Link | EtherCAT | CPU の | その他の |

| 8   | りセット光生委囚                                                  | データ RAM  |     | Field Network <sup>注 1</sup> |         | 2 2      | デバッグ・ | 周辺回路 | 2-7 |                                   | データ RAM  |     | Field Network <sup>注 1</sup> |         | 注2       | デバッグ・ | 周辺回路 |

| ٥   |                                                           | バッファ RAM |     | パワーオンリセット                    |         |          | ユニット  |      | 2 / |                                   | バッファ RAM |     | パワーオンリセット                    |         |          | ユニット  |      |

|     | PONRZ 端子                                                  | 0        | 0   | 0                            | 0       | 0        | -     | 0    |     | PONRZ 端子                          | 0        | 0   | 0                            | 0       | 0        | _     | 0    |

|     | RESETZ 端子                                                 | -        | 0   | 0                            | 0       | 0        | -     | 0    |     | RESETZ 端子                         | _        | 0   | 0                            | 0       | 0        | _     | 0    |

|     | HOTRESETZ 端子 <sup>注1</sup>                                | -        | -   | -                            | 0       | 0        | -     | 0    |     | HOTRESETZ 端子 <sup>注1</sup>        | _        | -   | _                            | 0       | _        | -     | 0    |

|     |                                                           |          |     |                              |         | •        |       |      |     | -                                 |          |     | -                            | -       |          |       |      |

#### No.6 <u>2.4 (1) ソフトウェア・リセット・レジスタ(SFTRES1)</u>

#### RSWDT の説明を修正

|     | V8.00                                                                     | V9.00 |                                                                                   |  |  |  |

|-----|---------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------|--|--|--|

| ページ | 記載内容                                                                      | ページ   | 改訂内容                                                                              |  |  |  |

| 11  | 【2.3.4 (1) ソフトウェア・リセット・レジスタ(SFTRES1)】<br>[4: RSWDT]<br>Watch Dog Timer 機能 | 2-10  | 【2.4 (1) ソフトウェア・リセット・レジスタ(SFTRES1)】<br>[4:RSWDT]<br>Watch Dog Timer 機能用ソフトウェアリセット |  |  |  |

#### No.7 <u>3. CPU</u>

#### 表題の変更、説明を修正

|     | V8.00                                                                   | V9.00    |                                                                       |  |  |

|-----|-------------------------------------------------------------------------|----------|-----------------------------------------------------------------------|--|--|

| ページ | 記載内容                                                                    | ページ 改訂内容 |                                                                       |  |  |

| 12  | 【3. CPU】<br><mark>ここ</mark> では、R-IN32M3 <mark>製品固有の情報</mark> について説明します。 | 3-1      | 【3. CPU/内蔵 RAM】<br>本章では、R-IN32M3 に内蔵している CPU および、内蔵 RAM の概要について説明します。 |  |  |

# No.8 <u>3.4.2 リード・バッファ機能</u> リード・バッファ機能の説明を修正

|     | V8.00                                                                                   | V9.00 |                                                                 |  |  |

|-----|-----------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------|--|--|

| ページ | 記載内容                                                                                    | ページ   | 改訂内容                                                            |  |  |

| 14  | 【3.4.2 リード・バッファ機能】<br>リード応答時の 2bit ECC エラーは、AHB のエラー応答として扱うのと同時に、ECC エラー割り込みを<br>発生させる。 |       | 【3.4.2 リード・バッファ機能】<br>リード応答時の 2bit ECC エラーは、ECC エラー割り込みを発生させる。★ |  |  |

#### No.9 3.5 内蔵データ RAM

# 内蔵データ RAM の説明を修正

|     | V8.00                                                                                  | V9.00 |                                                                                                           |  |  |

|-----|----------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------|--|--|

| ページ | 記載内容                                                                                   | ページ   | 改訂内容                                                                                                      |  |  |

| 15  | 【3.5 内蔵データRAM】<br>内蔵データ RAM は、512k バイトの RAM です。Header Endec と AHB の双方からのアクセスが可能<br>です。 | 3-4   | 【3.5 内蔵データRAM】<br>内蔵データ RAM は、512k バイトの RAM です。Header Endec (Communication-BUS)と AHB の双方<br>からのアクセスが可能です。 |  |  |

#### No.10 <u>3.6 バッファ RAM</u>

#### バッファ RAM の説明を修正

|     | V8.00                                                                                           | V9.00 |                                                                                     |  |  |  |

|-----|-------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------|--|--|--|

| ページ | 記載内容                                                                                            | ページ   | 改訂内容                                                                                |  |  |  |

| 16  | 【3.6 <b>バッファ RAM】</b><br>バッファ RAM は、64k バイトの RAM です。AHB および Communication-BUS からのアクセスが可能<br>です。 |       | 【3.6 <b>バッファ RAM】</b><br>バッファ RAM は、64k バイトの RAM です。Communication-BUS からのアクセスが可能です。 |  |  |  |

### No.11 <u>4. バス構成</u>

#### 「表 4.1 R-IN32M3 の AHB 内部バス」に CC-Link を追加

|     | V8.00                                    |   |   |    |     |   | V9.00 |                                          |     |                              |     |                  |    |     |   |   |                                      |   |

|-----|------------------------------------------|---|---|----|-----|---|-------|------------------------------------------|-----|------------------------------|-----|------------------|----|-----|---|---|--------------------------------------|---|

| ページ |                                          |   |   | 記載 | 战内容 |   |       |                                          | ページ |                              |     |                  | 改訂 | 丁内容 |   |   |                                      |   |

|     | 【4. バス構成】<br>[表 4.1 R-IN32M3 の AHB 内部バス] |   |   |    |     |   |       | 【4. バス構成】<br>[表 4.1 R-IN32M3 の AHB 内部バス] |     |                              |     |                  |    |     |   |   |                                      |   |

| 47  | Ether MAC <sup>独 6</sup>                 | 0 | 0 | -  | 0   | 0 | -     | ラウンドロビン<br>(alternate) <sup>注3</sup>     | 4-1 | Ether MAC 12 6               | 0   | 0                | -  | 0   | 0 | - | ラウンドロビン<br>(alternate) <sup>注3</sup> |   |

| 17  | APB 内蔵<br>周辺機能 <sup>注 1</sup>            | 0 | 0 | -  | 0   | 0 | -     | ラウンドロビン<br>(alternate) <sup>注3</sup>     |     | 4-1                          | 4-1 | CC-Link <b>★</b> | 0  | 0   | - | 0 | 0                                    | _ |

|     |                                          |   |   |    |     |   |       | ,                                        |     | APB 内蔵<br>周辺機能 <sup>注1</sup> | 0   | 0                | -  | 0   | 0 | - | ラウンドロビン<br>(alternate) <sup>注3</sup> |   |

|     |                                          |   |   |    |     |   |       |                                          |     |                              |     |                  |    |     |   |   | '                                    |   |

#### No.12 <u>6.2 セマフォ</u>

#### セマフォの識別子数を修正

|     | V8.00                                                       | V9.00 |                                        |  |  |  |

|-----|-------------------------------------------------------------|-------|----------------------------------------|--|--|--|

| ページ | 記載内容                                                        | ページ   | 改訂内容                                   |  |  |  |

| 24  | 【 <b>6.2 セマフォ】</b><br>セマフォの識別子数は <mark>125</mark> 個搭載しています。 |       | 【6.2 セマフォ】<br>セマフォの識別子数は 128 個搭載しています。 |  |  |  |

### No.13 <u>6.6 サービス・コール</u>

#### サービス・コールを削除

|     | V8.00          | V9.00 |      |  |  |  |

|-----|----------------|-------|------|--|--|--|

| ページ | 記載内容           | ページ   | 改訂内容 |  |  |  |

| 27  | 【6.6 サービス・コール】 |       | (削除) |  |  |  |

| ~   |                | _     |      |  |  |  |

| 29  |                |       |      |  |  |  |

# No.14 7. ギガビット・イーサネット MAC

#### 「R-IN32M3-CL」の CC-Link IE Field の機能説明を修正

|     | V8.00                                                                                                                                                               | V9.00 |                                                                                                                                                                  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                                                                                                                                | ページ   | 改訂内容                                                                                                                                                             |  |

| 30  | 【7. ギガビット・イーサネット MAC】 「R-IN32M3-EC」の EtherCAT スレーブ機能と、「R-IN32M3-CL」の CC-Link IE Field スレーブ機能に関しては、それぞれ「R-IN32M3-EC ユーザーズ・マニュアル」、「R-IN32M3-CL ユーザーズ・マニュアル」を参照してください。 | 7-1   | 【7. ギガビット・イーサネット MAC】 「R-IN32M3-EC」の EtherCAT スレーブ機能と、「R-IN32M3-CL」の CC-Link IE Field 機能に関しては、それぞれ「R-IN32M3-EC ユーザーズ・マニュアル」、「R-IN32M3-CL ユーザーズ・マニュアル」を 参照してください。 |  |

#### No.15 7.1.1 イーサネット・インタフェースの構成

# 「図 7.2 イーサネット・インタフェース周辺構成図(R-IN32M3-CL)」の CC-Link IE Filed と Selector 間の I/F 機能を修正

# No.16 <u>7.3.1 (3) ギガビット・イーサネット MAC 制御レジスタ</u> MAC アドレス・レジスタのレジスタ名を修正

|    |                             | V8.00        |            |     |                             | V9.00        |             |

|----|-----------------------------|--------------|------------|-----|-----------------------------|--------------|-------------|

| -ジ | 記載内容                        |              |            |     |                             | 改訂内容         |             |

|    | 【7.3.1 (3) ギガビット・イーサネット MAC | : 制御レジスタ】    |            |     | 【7.3.1 (3) ギガビット・イーサネット MA( | C 制御レジスタ】    |             |

|    | MAC アドレス・レジスタ 0A            | GMAC_ADI 0A  | 4009 0100H |     | MAC アドレス・レジスタ 1A            | GMAC_ADF:1A  | 4009 0100H  |

|    | MAC アドレス・レジスタ 0B            | GMAC_ADI:0B  | 4009 0104H |     | MAC アドレス・レジスタ 1B            | GMAC_ADF 1B  | 4009 0104H  |

|    | MAC アドレス・レジスタ 1A            | GMAC_ADIR1A  | 4009 0108H |     | MAC アドレス・レジスタ 2A            | GMAC_ADF 2A  | 4009 0108H  |

|    | MAC アドレス・レジスタ 1B            | GMAC_ADI:1B  | 4009 010cH |     | MAC アドレス・レジスタ 2B            | GMAC_ADF 2B  | 4009 010CH  |

|    | MAC アドレス・レジスタ 2A            | GMAC_ADI 2A  | 4009 0110H |     | MAC アドレス・レジスタ 3A            | GMAC_ADF3A   | 4009 0110H  |

|    | MAC アドレス・レジスタ 2B            | GMAC_ADI 2B  | 4009 0114H |     | MAC アドレス・レジスタ 3B            | GMAC_ADF:3B  | 4009 0114H  |

|    | MAC アドレス・レジスタ 3A            | GMAC_ADI:3A  | 4009 0118H |     | MAC アドレス・レジスタ 4A            | GMAC_ADF4A   | 4009 0118H  |

|    | MAC アドレス・レジスタ 3B            | GMAC_ADI:3B  | 4009 011cH |     | MAC アドレス・レジスタ 4B            | GMAC_ADF 4B  | 4009 011CH  |

|    | MAC アドレス・レジスタ 4A            | GMAC_ADR4A   | 4009 0120H |     | MAC アドレス・レジスタ 5A            | GMAC_ADF 5A  | 4009 0120H  |

|    | MAC アドレス・レジスタ 4B            | GMAC_ADR4B   | 4009 0124H |     | MAC アドレス・レジスタ 5B            | GMAC_ADF:5B  | 4009 0124H  |

|    | MAC アドレス・レジスタ 5A            | GMAC_ADI:5A  | 4009 0128H |     | MAC アドレス・レジスタ 6A            | GMAC_ADF 6A  | 4009 0128H  |

|    | MAC アドレス・レジスタ 5B            | GMAC_ADR5B   | 4009 012cH |     | MAC アドレス・レジスタ 6B            | GMAC_ADF:6B  | 4009 012CH  |

|    |                             |              |            |     |                             |              | <del></del> |

|    | MAC アドレス・レジスタ 6A            | GMAC_ADR6A   | 4009 0130H |     | MAC アドレス・レジスタ 7A            | GMAC_ADI 7A  | 4009 0130H  |

|    | MAC アドレス・レジスタ 6B            | GMAC_ADR6B   | 4009 0134H |     | MAC アドレス・レジスタ 7B            | GMAC_ADI 7B  | 4009 0134H  |

| 34 | MAC アドレス・レジスタ 7A            | GMAC_ADR7A   | 4009 0138H | 7-4 | MAC アドレス・レジスタ 8A            | GMAC_ADI 8A  | 4009 0138H  |

| 35 | MAC アドレス・レジスタ 7B            | GMAC_ADR7B   | 4009 013CH | 7-5 | MAC アドレス・レジスタ 8B            | GMAC_ADI 8B  | 4009 013CH  |

| 00 | MAC アドレス・レジスタ 8A            | GMAC_ADR8A   | 4009 0140H | , , | MAC アドレス・レジスタ 9A            | GMAC_ADI 9A  | 4009 0140H  |

|    | MAC アドレス・レジスタ 8B            | GMAC_ADR8B   | 4009 0144H |     | MAC アドレス・レジスタ 9B            | GMAC_ADI 9B  | 4009 0144H  |

|    | MAC アドレス・レジスタ 9A            | GMAC_ADR9A   | 4009 0148H |     | MAC アドレス・レジスタ 10A           | GMAC_ADI 10A | 4009 0148H  |

|    | MAC アドレス・レジスタ 9B            | GMAC_ADR9B   | 4009 014CH |     | MAC アドレス・レジスタ 10B           | GMAC_ADI 10B | 4009 014CH  |

|    | MAC アドレス・レジスタ 10A           | GMAC_ADR10A  | 4009 0150H |     | MAC アドレス・レジスタ 11A           | GMAC_ADI 11A | 4009 0150H  |

|    | MAC アドレス・レジスタ 10B           | GMAC_ADR10B  | 4009 0154H |     | MAC アドレス・レジスタ 11B           | GMAC_ADI 11B | 4009 0154H  |

|    | MAC アドレス・レジスタ 11A           | GMAC_ADR11A  | 4009 0158H |     | MAC アドレス・レジスタ 12A           | GMAC_ADI 12A | 4009 0158H  |

|    | MAC アドレス・レジスタ 11B           | GMAC_ADI:11B | 4009 015cH |     | MAC アドレス・レジスタ 12B           | GMAC_ADI 12B | 4009 015cH  |

|    | MAC アドレス・レジスタ 12A           | GMAC_ADR12A  | 4009 0160H |     | MAC アドレス・レジスタ 13A           | GMAC_ADI 13A | 4009 0160H  |

|    | MAC アドレス・レジスタ 12B           | GMAC_ADR12B  | 4009 0164H |     | MAC アドレス・レジスタ 13B           | GMAC_ADI 13B | 4009 0164H  |

|    | MAC アドレス・レジスタ 13A           | GMAC_ADR13A  | 4009 0168H |     | MAC アドレス・レジスタ 14A           | GMAC_ADI 14A | 4009 0168H  |

|    | MAC アドレス・レジスタ 13B           | GMAC_ADR13B  | 4009 016CH |     | MAC アドレス・レジスタ 14B           | GMAC_ADI 14B | 4009 016CH  |

|    | MAC アドレス・レジスタ 14A           | GMAC_ADR14A  | 4009 0170H |     | MAC アドレス・レジスタ 15A           | GMAC_ADI 15A | 4009 0170H  |

|    | MAC アドレス・レジスタ 14B           | GMAC_ADR14B  | 4009 0174H |     | MAC アドレス・レジスタ 15B           | GMAC_ADI 15B | 4009 0174H  |

|    | MAC アドレス・レジスタ 15A           | GMAC_ADR15A  | 4009 0178H |     | MAC アドレス・レジスタ 16A           | GMAC_ADI 16A | 4009 0178H  |

|    | MAC アドレス・レジスタ 15B           | GMAC_ADR 15B | 4009 017CH |     | MAC アドレス・レジスタ 16B           | GMAC_ADI 16B | 4009 017CH  |

#### No.17 7.3.1 (3) ギガビット・イーサネット MAC 制御レジスタ

#### LPI モード制御レジスタ、LPI CLIENT タイミング制御レジスタ用の注削除

|     | V8.00                                                                                                                                                                | V9.00 |                                                                               |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------|--|--|--|

| ページ | 記載内容                                                                                                                                                                 | ページ   | 改訂内容                                                                          |  |  |  |

| 35  | 【7.3.1 (3) ギガビット・イーサネット MAC 制御レジスタ】 LPI モード制御レジスタ <sup>注</sup> LIP CLIENT タイミング制御レジスタ <sup>注</sup> 注 イーサネット・スイッチが LPI モードに対応していないため、MACSEL の値が"0000 0002H"の場合のみ有効です。 | 7–5   | 【7.3.1 (3) ギガビット・イーサネット MAC 制御レジスタ】 LPI モード制御レジスタ LPI CLIENT タイミング制御レジスタ (削除) |  |  |  |

# No.18 <u>7.3.1 (4) ハードウェア・ファンクション・コール・レジスタ</u>

#### レジスタ名の修正、レジスタの追加

|     | V8.00                           |      |            | V9.00 |                                  |            |             |  |  |  |  |

|-----|---------------------------------|------|------------|-------|----------------------------------|------------|-------------|--|--|--|--|

| ページ | 記載は                             | 内容   |            | ページ   | 改訂内                              | 改訂内容       |             |  |  |  |  |

|     | 【7.3.1 (4) ハードウェア・ファンクション・コール・レ | ジスタ】 |            |       | 【7.3.1 (4) ハードウェア・ファンクション・コール・レジ | ジスタ】       |             |  |  |  |  |

|     | レジスタ名                           | 略号   | アドレス       |       | レジスタ名                            | 略号         | アドレス        |  |  |  |  |

|     | ハードウェア・ファンクション・コマンドレジスタ         | SYSC | 4008 F000H |       | ハードウェア・ファンクション・システムコールレジスタ       | SYSC       | 4008 F000H  |  |  |  |  |

|     | ハードウェア・ファンクション・引数レジスタ 4         | R4   | 4008 F004H |       | ハードウェア・ファンクション・引数レジスタ 4          | R4         | 4008 F004H  |  |  |  |  |

|     | ハードウェア・ファンクション・引数レジスタ 5         | R5   | 4008 F008H |       | ハードウェア・ファンクション・引数レジスタ 5          | R5         | 4008 F008H  |  |  |  |  |

|     | ハードウェア・ファンクション・引数レジスタ 6         | R6   | 4008 F00CH |       | ハードウェア・ファンクション・引数レジスタ 6          | R6         | 4008 F00CH  |  |  |  |  |

| 35  | ハードウェア・ファンクション・引数レジスタ 7         | R7   | 4008 F010H | 7–5   | ハードウェア・ファンクション・引数レジスタ7           | R7         | 4008 F010H  |  |  |  |  |

|     | ハードウェア・ファンクション・戻り値レジスタ 0        | R0   | 4008 F020H |       | ハードウェア・ファンクション・動作モード制御レジスタ       | CMD        | 4008 F014H  |  |  |  |  |

|     | ハードウェア・ファンクション・戻り値レジスタ 1        | R1   | 4008 F024H |       | ハードウェア・ファンクション・戻り値レジスタ 0         | R0         | 4008 F020H  |  |  |  |  |

|     |                                 |      |            |       | ハードウェア・ファンクション・戻り値レジスタ 1         | R1         | 4008 F024H  |  |  |  |  |

|     |                                 |      |            |       | ハードウェア・ファンクション・タイプレジスタ           | CNTX_TYPE0 | 04008 0000H |  |  |  |  |

|     |                                 |      |            |       | ハードウェア・ファンクション・状態レジスタ            | CNTX STATO | 04008 0008H |  |  |  |  |

|     |                                 |      |            |       |                                  | •          |             |  |  |  |  |

# No.19 <u>7.3.2.1 MAC セレクト・レジスタ</u>

#### 選択値を修正

|     | V8.00                                                                      | V9.00 |                                                         |  |  |

|-----|----------------------------------------------------------------------------|-------|---------------------------------------------------------|--|--|

| ページ | 記載内容                                                                       | ページ   | 改訂内容                                                    |  |  |

|     | 【 <b>7.3.2.1 MAC セレクト・レジスタ】</b><br>[2-0: MAC2-MAC0]<br><mark>010</mark> 注3 | 7–6   | 【7.3.2.1 MAC セレクト・レジスタ】<br>[2-0: MAC2-MAC0]<br>011 注 3★ |  |  |

### No.20 <u>7.3.3.1 MDC クロック選択レジスタ(MDCCFG)</u>

# 注意 2 の説明を修正

|     | V8.00                                                                                                      |     | V9.00                                                                                                      |  |

|-----|------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                                                                       | ページ | 改訂内容                                                                                                       |  |

| 37  | 【7.3.3.1 MDC クロック選択レジスタ(MDCCFG)】<br>注意 2. 本レジスタの設定は、MACSEL レジスタの値が"0000 0000H"または"0000 0002H"の時の<br>み有効です。 | 7-7 | 【7.3.3.1 MDC クロック選択レジスタ(MDCCFG)】<br>注意 2. 本レジスタの設定は、MACSEL レジスタの値が"0000 0000H"または"0000 0003H"の時の<br>み有効です。 |  |

#### No.21 <u>7.3.4.1 MIIM レジスタ(GMAC\_MIIM)</u>

#### Write 時、Read 時、注意、注の説明を修正

|     | V8.00                                                                                                                                                           |     | V9.00                                                                                                                                               |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                                                                                                                            | ページ | 改訂内容                                                                                                                                                |  |

|     | 【7.3.4.1 MIIM レジスタ(GMAC_MIIM)】<br>1. Write オペレーションの開始: bit26 = 1、bit25-21 に PHY アドレス、bit20-16 に PHY のレジスタアドレス、bit15-0 に Write データを設定                            |     | 【7.3.4.1 MIIM レジスタ(GMAC_MIIM)】  1. Write オペレーションの開始: RWDV ビット = 1、PHYADDR4-0 ビットに PHY アドレス、REGADDR4-0 ビットに PHY のレジスタアドレス、DATA15-0 ビットに Write データを設定 |  |

| 39  | 4. Read オペレーションの開始: bit26 = 0、bit25-21 に PHY アドレス、bit20-16 に PHY のレジスタアドレスを設定                                                                                   | 7-9 | 4. Read オペレーションの開始: RWDV ビット = 0、PHYADDR4-0 ビットに PHY アドレス、REGADDR4-0 ビットに PHY のレジスタアドレスを設定 注意 本レジスタは、MAC セレクト・レジスタ(MACSEL) で設定されたマネージメントインタフェースに    |  |

|     | 注意 MIIM レジスタは、MAC セレクト・レジスタ(MACSEL)の値が"0000 0000H"または"0000 0002H"の場合のみ有効です。その他の場合、書き込みは無効で読み出す値は不定です。                                                           |     | おいて有効です。その他の場合、書き込みは無効で読み出す値は不定になります。                                                                                                               |  |

|     | 注1 リセット <mark>直後の</mark> RWDV ビットは1 <mark>を示していますが、DATA15-0 ビットが</mark> 有効な値 <mark>を示しているわけ</mark> ではありません。オペレーションの開始処理(レジスタへの Write)を行うことで、正常なステータスを示すようになります。 |     | 注 リセット解除後は RWDV ビット = 1 になりますが、このときの DATA15-0 ビットは有効な値ではありません。RWDV ビットでステータスを確認する場合は、必ずオペレーションの開始処理を行うことで、正常なステータスを確認できます。                          |  |

#### No.22 <u>7.3.4.2 TX ID レジスタ(GMAC\_TXID)</u>

# TX ID レジスタの説明を追加

|     | V8.00                                     |     | V9.00                                                                                                                                                                                                                                  |  |

|-----|-------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                      | ページ | 改訂内容                                                                                                                                                                                                                                   |  |

| 40  | 【7.3.4.2 TX ID レジスタ(GMAC_TXID)】<br>(記載なし) |     | 【7.3.4.2 TX ID レジスタ(GMAC_TXID)】 本レジスタは、GMAC_TXRESULT レジスタに対応した送信フレームの ID を示すレジスタです。 送信フレーム結果 ID を確認する場合は、必ず GMAC_TXRESULT レジスタの読み出しより前に本レジスタの読み出しを行ってください。GMAC_TXRESULT レジスタを先に読み出した場合は、送信フレーム結果が更新されるため、本レジスタでは更新後の送信フレーム ID を読み出します。 |  |

#### No.23 <u>7.3.4.3 TX RESULT レジスタ(GMAC\_TXRESULT)</u>

#### TX RESULT レジスタの説明を追加、注意を削除

|     | V8.00                                                                                                                                                                                                                                                                                             |      | V9.00                                                                                                                                |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                                                                                                                                                                                                                                                              | ページ  | 改訂内容                                                                                                                                 |  |

| 40  | 【7.3.4.3 TX RESULT レジスタ(GMAC_TXRESULT)】 (記載なし) 注意 TX ID と TX RESULT レジスタはいずれも送信フレームの結果を示すレジスタです。これら 2 つのレジスタは TX RESULT レジスタを Read した際に更新され、次のフレームの送信結果を読み出すことができます。したがって、読み出す順序として、必ず TX ID レジスタを先に読み出す必要があります。 (TX RESULT レジスタを先に Read した場合、TX ID レジスタで読み出されるフレーム ID は次の送信結果に対する TX ID を示しています) | 7-10 | 【7.3.4.3 TX RESULT レジスタ(GMAC_TXRESULT)】 本レジスタは、送信フレーム結果を示すレジスタです。 送信フレーム結果は本レジスタを読み出すことで更新され、次の読み出しで更新後の送信フレーム 結果を読み出すことが可能です。  (削除) |  |

#### No.24 <u>7.3.4.4 MODE レジスタ(GMAC\_MODE)</u>

#### MODE レジスタの説明、ETHMODE、DUPMODE の意味を追加

|     | V8.00                                                     |      | V9.00                                                                                         |  |

|-----|-----------------------------------------------------------|------|-----------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                      | ページ  | 改訂内容                                                                                          |  |

|     | 【7.3.4.4 MODE レジスタ(GMAC_MODE)】<br>(記載なし)<br>[31: ETHMODE] |      | 【7.3.4.4 MODE レジスタ(GMAC_MODE)】<br>本レジスタは、ギガビット・イーサネット MAC の動作モードを制御するレジスタです。<br>[31: ETHMODE] |  |

| 41  | Ethernet Mode<br>1: Giga bit Ethernet モードで動作します           | 7–11 | Ethernet Mode<br>1: Giga bit Ethernet モードで動作します。<br>イーサネット・スイッチと接続して使用する時は、このモードを使用してください。    |  |

|     | [30 : DUPMODE]<br>Duplex Mode<br>1:Full Duplex モードで動作します  |      | [30: DUPMODE] Duplex Mode 1: Full Duplex モードで動作します。 イーサネット・スイッチと接続して使用する時は、このモードを使用してください。    |  |

#### No.25 7.3.4.5 RX MODE レジスタ(GMAC\_RXMODE)

#### RX MODE レジスタ、 MFILLTEREN の意味を追加

|     | V8.00                                                                                                                           |      | V9.00                                                                                                                              |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                                                                                            | ページ  | 改訂内容                                                                                                                               |  |

|     | 【7.3.4.5 RX MODE レジスタ(GMAC_RXMODE)】<br>(記載なし)                                                                                   |      | 【7.3.4.5 RX MODE レジスタ(GMAC_RXMODE)】<br>本レジスタは、フレーム受信動作を制御するレジスタです。                                                                 |  |

| 41  | [30 : MFILLTEREN]<br>Multicast Filtering Enable<br>1:MAC アドレス・レジスタ(GMAC_ADRnA, GMAC_ADRnB)に登録されたマルチキャスト以外のマルチキャストアドレスフレームを破棄します | 7-11 | [30: MFILLTEREN] Multicast Filtering Enable 1:MAC アドレス・レジスタ(GMAC_ADRnA, GMAC_ADRnB)に登録されたマルチキャスト以外のマルチキャストアドレスフレームを破棄します(n = 1-16) |  |

#### No.26 7.3.4.6 TX MODE レジスタ(GMAC\_TXMODE)

#### TX MODE レジスタの説明を追加、SFOP を削除、LPTXEN の意味に注を追加

|     | V8.00                                                                                                                                                                                                                                                       | V9.00 |                                                                                                                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ページ | 記載内容                                                                                                                                                                                                                                                        | ページ   | 改訂内容                                                                                                                                                                            |

| 43  | 【7.3.4.6 TX MODE レジスタ(GMAC_TXMODE)】 (記載なし) ・ビットフィールド図(26): SFOP ・R/W 属性(26): R/W  [30: LPTXEN] Long Packet TX Enable 1:IEEE802.3 の規格を超えた長さのフレームの送信を可能にします  [26: SFOP] Store & Forward Option 1: TX FIFO において、フレームカウンタを使用します 0: TX FIFO において、フレームカウンタを使用しません | 7–13  | 【7.3.4.6 TX MODE レジスタ(GMAC_TXMODE)】 本レジスタは、フレーム送信動作を制御するレジスタです。 ・ビットフィールド図(26): 0 ・R/W 属性(26): 0  [30: LPTXEN] Long Packet TX Enable 1:IEEE802.3 の規格を超えた長さのフレームの送信を可能にします注 (削除) |

|     | (記載なし)                                                                                                                                                                                                                                                      |       | 注 イーサネット・スイッチのマネージメント・タグ挿入機能を有効にしている場合(ETHSWMTC レジスタ SWTAGEN ビット="1")、フレームの最大サイズ 1518 バイトを超える可能性があるため、<br>LPTXEN を"1"に設定する必要があります。★                                             |

#### No.27 7.3.4.6 TX MODE レジスタ(GMAC\_TXMODE)

#### TRBMODE1-0 の意味を修正

| V8.00 |                                                                                                                                                              | V9.00 |                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ページ   | 記載内容                                                                                                                                                         | ページ   | 改訂内容                                                                                                                                                                     |

| 44    | 【7.3.4.6 TX MODE レジスタ(GMAC_TXMODE)】 [7-6: TRBMODE1-0] Transmission Result Buffer Mode TX RESULT レジスタへ送信結果を書き込む方法を制御します。 00:常時書き込み 01:エラー時のみ書き込み 10:書き込みを行わない | 7–14  | 【7.3.4.6 TX MODE レジスタ(GMAC_TXMODE)】 [7-6: TRBMODE1-0] Transmission Result Buffer Mode GMAC_TXRESULT レジスタへ送信結果を書き込む方法を制御します。 00:常時書き込み 01:エラー時のみ書き込み 10:書き込みを行わない 11:設定禁止 |

#### No.28 <u>7.3.4.7 RESET レジスタ(GMAC\_RESET)</u>

# RESET レジスタの説明を追加、ALLRST, TXRST, RXRST の意味の修正

|     | V8.00                                                                                                                                     | V9.00 |                                                                                                                                                                                                                        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ページ | 記載内容                                                                                                                                      | ページ   | 改訂内容                                                                                                                                                                                                                   |

| 44  | 【7.3.4.7 RESET レジスタ(GMAC_RESET)】 (記載なし)  [31: ALLRST] 全ての Ethernet MAC モジュールをリセットします。このビットは自動的に 0 に戻ります。                                  | 7–15  | 【7.3.4.7 RESET レジスタ(GMAC_RESET)】 本レジスタは、ソフトウェアでギガビット・イーサネット MAC をリセットするトリガレジスタです。各ビットに1をセットすることでモジュールにリセットをかけることが可能です。1をセットしリセット処理完了後に各ビットは自動的に0に戻ります。  [31: ALLRST] 全ての Ethernet MAC モジュールをリセットします。 0:リセット完了後 1:リセット中 |

|     | [15:TXRST] TX MAC, TX FIFO, TX DMA モジュールをリセットします。このビットは自動的に 0 に戻ります。 [13:RXRST] RX MAC, RX FIFO, RX DMA モジュールをリセットします。このビットは自動的に 0 に戻ります。 |       | [15: TXRST] TX MAC, TX FIFO, TX DMA モジュールをリセットします。 0:リセット完了後 1:リセット中 [13: RXRST] RX MAC, RX FIFO, RX DMA モジュールをリセットします。                                                                                                |

|     | TOO MINO, TOO I II O, TOO DIMIN E フェールとうピクロしよう。 COVE フロは自動は別にいて大きよう。                                                                      |       | の:リセット完了後<br>1:リセット中                                                                                                                                                                                                   |

#### No.29 <u>7.3.4.8 PAUSE パケットデータレジスタ(GMAC\_PAUSEn)</u>

#### PAUSE レジスタの説明を追加

| V8.00 |                                                    | V9.00    |                                                                              |

|-------|----------------------------------------------------|----------|------------------------------------------------------------------------------|

| ページ   | 記載内容                                               | ページ 改訂内容 |                                                                              |

| 45    | 【7.3.4.8 PAUSE パケットデータレジスタ(GMAC_PAUSEn)】<br>(記載なし) | 7-15     | 【7.3.4.8 PAUSE パケットデータレジスタ(GMAC_PAUSEn)】<br>本レジスタは、送信されるポーズパケットの指定を行うレジスタです。 |

### No.30 7.3.4.9 RX FLOW CONTROL レジスタ(GMAC\_FLWCTL)

#### RX FLOW CONTROL レジスタの説明を追加

| V8.00 |                                                       | V9.00    |                                                                                |

|-------|-------------------------------------------------------|----------|--------------------------------------------------------------------------------|

| ページ   | 記載内容                                                  | ページ 改訂内容 |                                                                                |

| 46    | 【7.3.4.9 RX FLOW CONTROL レジスタ(GMAC_FLWCTL)】<br>(記載なし) | 7-17     | 【7.3.4.9 RX FLOW CONTROL レジスタ(GMAC_FLWCTL)】<br>本レジスタは、ポーズパケットの受信機能を制御するレジスタです。 |

#### No.31 <u>7.3.4.10 PAUSE パケットレジスタ(GMAC\_PAUSPKT)</u>

#### PAUSE パケットレジスタの説明を追加、PPR の意味を修正

|     | V8.00                                                            |      | V9.00                                                                                                                                                  |  |

|-----|------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                             | ページ  | 改訂内容                                                                                                                                                   |  |

| 46  | 【7.3.4.10 PAUSE パケットレジスタ(GMAC_PAUSPKT)】<br>(記載なし)                | 7-17 | 【7.3.4.10 PAUSE パケットレジスタ(GMAC_PAUSPKT)】<br>本レジスタは、ポーズパケットの送信を制御するレジスタです。<br>PPR ビットに 1 を書き込むとポーズパケットの送信を開始できます。送信開始後、ポーズパケットの<br>送信が完了すると自動的に 0 になります。 |  |

| 40  | [31:PPR]<br>'1'を書き込むことにより、ポーズパケットを送出します。ポーズパケットの送信が終わると'0'に戻ります。 | 7-17 | [31: PPR]<br>ポーズパケットの送信を制御します。<br>0: 何もしない<br>1:ポーズパケットの送信開始                                                                                           |  |

#### No.32 7.3.4.11 MAC アドレス・レジスタ(GMAC\_ADRnA, GMAC\_ADRnB)

#### MAC アドレス・レジスタの説明、BITMSK7-0 の意味を修正

|     | V8.00                                                                                                                                                                                                                                                                                                                                                               |      | V9.00                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ページ | 記載内容                                                                                                                                                                                                                                                                                                                                                                | ページ  | 改訂内容                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 47  | 【7.3.4.11 MAC アドレス・レジスタ(GMAC_ADRnA, GMAC_ADRnB)】 MAC アドレスを設定するレジスタです。 全 16 アドレスを登録することができ、GMAC_ADRnB レジスタの 23~16 ビットにより、複数アドレスのフィルタリングを行うことも可能です。(n = 0, 1,, 15)  [23-16: BITMSK7-0] DA[7:0]の一致比較にビットごとにマスクします。bit[23:16]が DA[7:0]のビット位置に対応し、0 の立っているビットは一致比較の対象から外します。 例えば、マスクレジスタのビット BITMSK2-0 が 0 のとき、DA[2:0]は一致比較の対象から外します。すなわち DA[47:3]が一致していればこのフレームを取り込みます。 | 7-18 | 【7.3.4.11 MAC アドレス・レジスタ(GMAC_ADRnA, GMAC_ADRnB)】 本レジスタは、MAC アドレスを設定するレジスタです。 全 16 アドレスを登録することが可能で、GMAC_ADRnB レジスタの BITMSK7-0 ビットにより、複数アドレスのフィルタリングを行うことも可能です。(n = 1, 2,, 16)  [23-16: BITMSK7-0] Destination MAC Address[7:0]の一致比較にビットごとにマスクします。bit[23:16]が Destination MAC Address[7:0]のビット位置に対応し、0 の立っているビットは一致比較の対象から外します。例えば、マスクレジスタのビット BITMSK2-0 が 0 のとき、Destination MAC Address[2:0]は一致比較の対象から外します。すなわち Destination MAC Address[47:3]が一致していればこのフレームを取り込みます。 |  |

#### No.33 <u>7.3.4.12 RX FIFO ステータス・レジスタ(GMAC\_RXFIFO)</u>

#### RX FIFO ステータス・レジスタの説明を追加

|     | V8.00                                                                                                                             |      | V9.00                                                                                                                                                       |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ページ | 記載内容                                                                                                                              | ページ  | 改訂内容                                                                                                                                                        |  |  |