# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                            | Document<br>No.         | TN-RX*-A164B/E         | Rev.                                                                              | 2.00 |  |  |

|-----------------------|----------------------------------------------------|-------------------------|------------------------|-----------------------------------------------------------------------------------|------|--|--|

| Title                 | Errata to RX65N Group, RX651 Group Use<br>Hardware | Information<br>Category | Technical Notification |                                                                                   |      |  |  |

|                       |                                                    | Lot No.                 |                        | RX65N Group, RX651 Group<br>User's Manual: Hardware Rev.1.00<br>(R01UH0590EJ0100) |      |  |  |

| Applicable<br>Product | RX65N Group, RX651 Group                           | All                     | Reference<br>Document  |                                                                                   |      |  |  |

This document describes corrections, as shown below, to the RX65N Group, RX651 Group User's Manual: Hardware, Rev.1.00.

The changes made from TN-RX\*-A164A/E to TN-RX\*-A164B/E are as follows. Indicate changes in red:

- No.9 is added,

- Contents of No.12 are changed, and

- Expressions in No.10 and No.11 are corrected.

| No. | Section Number                              | Summary                                                                                                                                                       |  |  |  |  |  |

|-----|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | 1. Overview                                 | Note 4 is added to the realtime clock function in Table.1.1 Outline of Specifications.                                                                        |  |  |  |  |  |

| 2   | 23. Multi-Function Pin Controller (MPC)     | Bit Name of the ADRHMS2 bit in 23.2.24 External Bus Control Register 0 (PFBCR0) is corrected.                                                                 |  |  |  |  |  |

| 3   | 41. Quad Serial Peripheral Interface (QSPI) | The title and description of 41.4.3 are modified.                                                                                                             |  |  |  |  |  |

| 4   | 43. SD Host Interface (SDHI)                | Descriptions of b8 to b11 in 43.2.13 SD Error Status Register (SDERSTS1) are corrected.                                                                       |  |  |  |  |  |

| 5   | 44. SD Slave Interface (SDSI)               | Expression in 44.1 Overview is modified.                                                                                                                      |  |  |  |  |  |

| 6   | 50. 12-Bit A/D Converter (S12ADFa)          | Description of operating modes in Table 50.1 in 50.1 Overview is corrected.                                                                                   |  |  |  |  |  |

| 7   | 51. 12-Bit D/A Converter (R12DA)            | The last sentence in (3) in 51.3 Operation is deleted.                                                                                                        |  |  |  |  |  |

| 8   | 51. 12-Bit D/A Converter (R12DA)            | The second sentence in (4), description below Figure 51.3, and Figure 51.4 in 51.3.1 Measure against Interference between D/A and A/D Conversion are deleted. |  |  |  |  |  |

| 9   | 57. Electrical Characteristics              | Junction temperature is added to Table 57.1 Absolute Maximum Rating in 57.1 Absolute Maximum Ratings.                                                         |  |  |  |  |  |

| 10  | 57. Electrical Characteristics              | Values of supply current under deep software standby mode in Table 57.5 DC Characteristics (3) in 57.2 DC Characteristics are corrected.                      |  |  |  |  |  |

| 11  | 57. Electrical Characteristics              | Values of reference power supply current during 12-bit A/D conversion (unit 0) in Table 57.6 DC Characteristics (4) in 57.2 DC Characteristics are corrected. |  |  |  |  |  |

| 12  | 57. Electrical Characteristics              | Table 57.x Thermal Resistance is added to 57.2 DC Characteristics.                                                                                            |  |  |  |  |  |

The corrections are indicated in red.

(c) 2017. Renesas Electronics Corporation. All rights reserved.

#### No.1 1.1 Outline of Specifications

Note 4 is added to Table 1.1 as follows:

Page 65 of 2468

#### Table 1.1Outline of Specifications (5/8)

| Classification | Module/Function         | Description                                                                                                                                                                            |

|----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timers         | Realtime clock (RTCd)*4 | Clock sources: Main clock, sub clock                                                                                                                                                   |

|                |                         | <ul> <li>Selection of the 32-bit binary count in time count/second unit possible</li> </ul>                                                                                            |

|                |                         | Clock and calendar functions                                                                                                                                                           |

|                |                         | <ul> <li>Interrupt sources: Alarm interrupt, periodic interrupt, and carry interrupt</li> </ul>                                                                                        |

|                |                         | Battery backup operation                                                                                                                                                               |

|                |                         | Time-capture facility for three values                                                                                                                                                 |

|                |                         | Event linking by the ELC                                                                                                                                                               |

|                | Watchdog timer (WDTA)   | • 14 bits × 1 channel                                                                                                                                                                  |

|                |                         | <ul> <li>Select from among 6 counter-input clock signals (PCLKB/4, PCLKB/64, PCLKB/128,<br/>PCLKB/512, PCLKB/2048, PCLKB/8192)</li> </ul>                                              |

|                | Independent watchdog    | • 14 bits × 1 channel                                                                                                                                                                  |

|                | timer (IWDTa)           | <ul> <li>Counter-input clock: IWDT-dedicated on-chip oscillator</li> </ul>                                                                                                             |

|                | · · · ·                 | <ul> <li>Dedicated clock/1, dedicated clock/16, dedicated clock/32, dedicated clock/64,<br/>dedicated clock/128, dedicated clock/256</li> </ul>                                        |

|                |                         | <ul> <li>Window function: The positions where the window starts and ends are specifiable (the<br/>window defines the timing with which refreshing is enabled and disabled).</li> </ul> |

|                |                         | Event linking by the ELC                                                                                                                                                               |

|                |                         | Omitted                                                                                                                                                                                |

#### Page 68 of 2468

#### Table 1.1 Outline of Specifications (8/8)

| Classification Module/Function | Description                                                         |

|--------------------------------|---------------------------------------------------------------------|

|                                | Omitted                                                             |

| Operating frequency            | Up to 120 MHz                                                       |

| Power supply voltage           | VCC = AVCC0 = AVCC1 = VCC_USB = 2.7 to 3.6 V, 2.7 ≤ VREFH0 ≤ AVCC0, |

|                                | V <sub>BATT</sub> = 2.0 to 3.6 V                                    |

| Operating temperature          | D-version: –40 to +85°C                                             |

|                                | G-version: –40 to +105°C (in planning)                              |

| Package                        | 145-pin TFLGA (PTLG0145KA-A)                                        |

|                                | 144-pin LFQFP (PLQP0144KA-B)                                        |

|                                | 100-pin TFLGA (PTLG0100JA-A)                                        |

|                                | 100-pin LFQFP (PLQP0100KB-B)                                        |

| On-chip debugging system       | <ul> <li>E1 emulator (JTAG and FINE interfaces)</li> </ul>          |

|                                | <ul> <li>E20 emulator (JTAG interface)</li> </ul>                   |

Note 1. Magic  $\mathsf{Packet}^\mathsf{TM}$  is a registered trademark of Advanced Micro Devices, Inc.

Note 2. The product part number differs according to whether or not it supports encryption.

Note 3. The product part number differs according to whether or not it includes an SDHI (SD host interface) / SDSI (SD slave interface).

Note 4. When the realtime clock is not to be used, initialize the registers in the realtime clock by referring to section 31.6.7, Initialization Procedure When the Realtime Clock is Not to be Used.

# No.2 23.3.24 External Bus Control Register 0 (PFBCR0) (Page 809 of 2468)

Bit name of the ADRHMS2 bit is corrected as follows:

#### Before correction

| Bit | Symbol  | Bit Name                 | Description     | R/W |

|-----|---------|--------------------------|-----------------|-----|

|     |         |                          | Omitted         |     |

| b1  | ADRHMS  | A16 to A23 Output Enable | See Table 23.20 | R/W |

| b2  | ADRHMS2 | A16 to A20 Output Enable |                 | R/W |

## After correction

| Bit | Symbol                   | nbol Bit Name Description  |                 | R/W |

|-----|--------------------------|----------------------------|-----------------|-----|

|     |                          | (                          | Omitted         |     |

| b1  | ADRHMS A16 to A23 Output |                            | See Table 23.20 | R/W |

| b2  | ADRHMS2                  | A16 to A23 Output Enable 2 |                 | R/W |

## No.3 41.4 Usage Notes (Page 1955 of 2468)

Title and description of section 41.4.3 are modified as follows:

#### Before correction

## 41.4.3 When Using SPI Mode 3 in Single-/Dual-/Quad-SPI Operation

When using the serial flash memory in single-/dual-/quad-SPI operation, set the SPCMDn.CPOL and CPHA bits (n = 0 to 3) to 1 before using SPI mode 3.

#### After correction

## 41.4.3 When Using Serial Flash Memory

When using the serial flash memory in dual- or quad-SPI operating mode, set the SPCMDn.CPOL and CPHA bits (n = 0 to 3) to 1 and select SPI mode 3. SPI mode 0 to 2 cannot be used. In addition, set the SPCMDn.SPNDEN, SLNDEN, and SCKDEN bits to 1 to secure delay period.

## No.4 43.2.13 SD Error Status Register 1 (SDERSTS1) (Page 1982 of 2468)

Descriptions of b8 to b11 is corrected as follows:

#### Before correction

| Bit | Symbol   | Bit Name                    | Description                                                                                                                                                                                                                                                       |   |  |  |  |

|-----|----------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

|     |          |                             | Omitted                                                                                                                                                                                                                                                           |   |  |  |  |

| b8  | RSPCRCE0 | Response CRC Error Flag 0   | 0: CRC error detected in command <sup>*1</sup> response<br>1: No CRC error detected in command <sup>*1</sup> response                                                                                                                                             | R |  |  |  |

| b9  | RSPLENE1 | Response CRC Error Flag 1   | <ul> <li>0: CRC error detected in command <sup>*2</sup> response</li> <li>1: No CRC error detected in command <sup>*2</sup> response (by setting the SDCMD.CMDIDX[5:0] bits, the error that occurs by issuing CMD12 is indicated by the RSPCRCE0 flag)</li> </ul> | R |  |  |  |

| b10 | RDCRCE   | Read Data CRC Error Flag    | 0: CRC error detected in read data<br>1: No CRC error detected in read data                                                                                                                                                                                       | R |  |  |  |

| b11 | CRCTKE   | CRC Status Token Error Flag | 0: Error detected in CRC status token<br>1: No error detected in CRC status token                                                                                                                                                                                 | R |  |  |  |

|     |          |                             | Omitted                                                                                                                                                                                                                                                           |   |  |  |  |

#### After correction

| Bit | Symbol   | Bit Name                    | Description                                                                                                                                                                                                                                                        |   |  |  |  |

|-----|----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

|     |          |                             | Omitted                                                                                                                                                                                                                                                            |   |  |  |  |

| b8  | RSPCRCE0 | Response CRC Error Flag 0   | 0: No CRC error detected in command <sup>*1</sup> response<br>1: CRC error detected in command <sup>*1</sup> response                                                                                                                                              | R |  |  |  |

| b9  | RSPLENE1 | Response CRC Error Flag 1   | <ul> <li>0: No CRC error detected in command <sup>*2</sup> response</li> <li>1: CRC error detected in command <sup>*2</sup> response (the error that occurs for CMD12 with the setting of the SDCMD.CMDIDX[5:0] bits is indicated by the RSPCRCE0 flag)</li> </ul> | R |  |  |  |

| b10 | RDCRCE   | Read Data CRC Error Flag    | 0: No CRC error detected in read data<br>1: CRC error detected in read data                                                                                                                                                                                        | R |  |  |  |

| b11 | CRCTKE   | CRC Status Token Error Flag | 0: No error detected in CRC status token<br>1: Error detected in CRC status token                                                                                                                                                                                  | R |  |  |  |

|     |          |                             | Omitted                                                                                                                                                                                                                                                            |   |  |  |  |

## No.5 44.1 Overview (Page 2018 of 2468)

Description of line 3 in section 44.1 is modified as follows:

### Before correction

frequencies up to 50 MHz, and is thus able to realize superior throughput in 20 Mbytes per second and above.

## After correction

frequencies up to 50 MHz, and is thus able to realize superior throughput in 25 Mbytes per second.

## No.6 50.1 Overview (Page 2141 of 2468)

The first line of a description of operating modes in Table 50.1 is corrected as follows:

#### Before correction

Operating modes can be set independently for three units.

## After correction

Operating modes can be set independently for two units.

## No.7 51.3 Operation (Page 2287 of 2468)

The last sentence in (3) in section 51.3 is deleted as follows:

#### Before correction

(3) If the DADR0 register is written to again, the conversion is started. The conversion result is output after the conversion time tDCONV has elapsed.

When the DAADSCR.DAADST bit is 1 (measure against interference between D/A and A/D conversion is enabled), it takes a maximum of one A/D conversion time for D/A conversion to start. When ADCLK is faster than the peripheral module clock, it may take longer than one A/D conversion time.

#### After correction

(3) If the DADR0 register is written to again, the conversion is started. The conversion result is output after the conversion time tDCONV has elapsed.

When the DAADSCR.DAADST bit is 1 (measure against interference between D/A and A/D conversion is enabled), it takes a maximum of one A/D conversion time for D/A conversion to start.

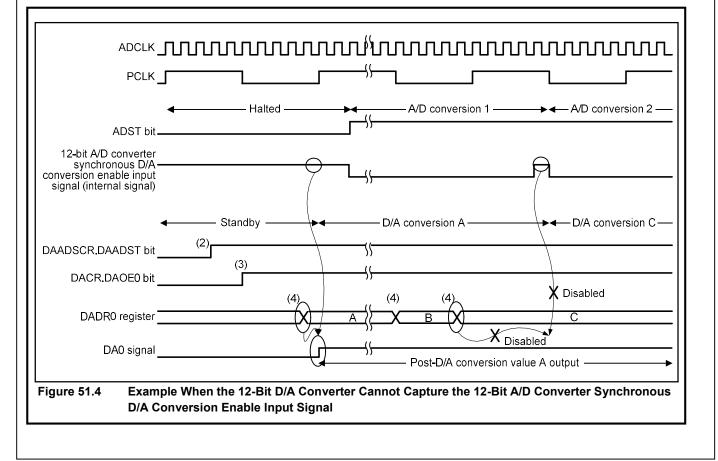

## No.8 51.3.1 Measure against Interference between D/A and A/D Conversion

Descriptions for when ADCLK is faster than the peripheral module clock in section 51.3.1 are deleted.

#### Page 2288 of 2468

The second sentence in (4) in section 51.3.1 is deleted as follows:

#### Before correction

(4) Set the DADR0 register. When ADCLK is faster than the peripheral module clock, it may take longer than one A/D conversion time for D/A conversion to start.

#### After correction

(4) Set the DADR0 register.

#### Page 2289 of 2468

The following description and Figure 51.4 in section 51.3.1 are deleted:

When ADCLK is faster than PCLK, the 12-bit D/A converter may not be able to capture a 12-bit A/D converter synchronous D/A conversion enable input signal for one ADCLK cycle which is output between A/D conversion 1 and A/D conversion 2.

Figure 51.4 shows example when the 12-bit D/A converter cannot capture the 12-bit A/D converter synchronous D/A conversion enable input signal. In this case, post-D/A conversion value A is continuously output as the DA0 signal.

# No.9 57.1 Absolute Maximum Ratings (Page 2382 of 2468)

Junction temperature is added to Table 57.1 as follows:

# Before Correction:

| Item                                                | Symbol            | Value                           | Unit |  |

|-----------------------------------------------------|-------------------|---------------------------------|------|--|

| Power supply voltage                                | VCC, VCC_USB      | -0.3 to +4.0                    | V    |  |

| V <sub>BATT</sub> power supply voltage              | V <sub>BATT</sub> | -0.3 to +4.0                    | V    |  |

| Input voltage (except for ports for 5 V tolerant*1) | V <sub>in</sub>   | -0.3 to VCC + 0.3 (up to 4.0)   | V    |  |

| Input voltage (ports for 5 V tolerant*1)            | V <sub>in</sub>   | -0.3 to VCC + 4.0 (up to 5.8)   | V    |  |

| Reference power supply voltage                      | VREFH0            | -0.3 to AVCC0 + 0.3 (up to 4.0) | V    |  |

| Analog power supply voltage                         | AVCC0, AVCC1*2    | -0.3 to +4.0                    | V    |  |

| Analog input voltage                                | V <sub>AN</sub>   | -0.3 to AVCC + 0.3 (up to 4.0)  | V    |  |

| Storage temperature                                 | T <sub>stg</sub>  | -55 to +125                     | °C   |  |

## After Correction

| I                                      | Item                      | Symbol            | Value                           | Unit |  |

|----------------------------------------|---------------------------|-------------------|---------------------------------|------|--|

| Power supply voltage                   |                           | VCC, VCC_USB      | -0.3 to +4.0                    | V    |  |

| V <sub>BATT</sub> power supply voltage | ge                        | V <sub>BATT</sub> | -0.3 to +4.0                    | V    |  |

| Input voltage (except for              | ports for 5 V tolerant*1) | Vin               | -0.3 to VCC + 0.3 (up to 4.0)   | V    |  |

| Input voltage (ports for 5             | V tolerant*1)             | V <sub>in</sub>   | -0.3 to VCC + 4.0 (up to 5.8)   | V    |  |

| Reference power supply                 | voltage                   | VREFH0            | -0.3 to AVCC0 + 0.3 (up to 4.0) | V    |  |

| Analog power supply volt               | age                       | AVCC0, AVCC1*2    | -0.3 to +4.0                    | V    |  |

| Analog input voltage                   |                           | V <sub>AN</sub>   | -0.3 to AVCC + 0.3 (up to 4.0)  | V    |  |

| Junction temperature                   | D version                 | Tj                | -40 to +105                     | °C   |  |

| Storage temperature                    |                           | T <sub>stg</sub>  | -55 to +125                     | °C   |  |

## No.10 57.2 DC Characteristics (Page 2385 of 2468)

Values of supply current in deep software standby mode in Table 57.5 are corrected as follows:

# Before Correction:

|           | Item          |                                             |                                                                                         |       | Min.    | Тур. | Max. | Unit   | Test Conditions |

|-----------|---------------|---------------------------------------------|-----------------------------------------------------------------------------------------|-------|---------|------|------|--------|-----------------|

| Supply    |               |                                             | Omitted                                                                                 | Icc*3 | Omitted |      |      |        |                 |

| current*1 |               | Power supplied to s detecting unit (USB     | tandby RAM and USB resume<br>0 only)                                                    |       | _       | 15.5 | 51   | μA     |                 |

|           | standby mode  | Power not<br>supplied to<br>standby RAM and | Power-on reset circuit and low-<br>power consumption function<br>disabled <sup>*5</sup> |       | —       | 11.5 | 29   |        |                 |

|           | software star | USB resume<br>detecting unit<br>(USB0 only) | Power-on reset circuit and low-<br>power consumption function<br>enabled <sup>*6</sup>  |       | _       | 4.9  | 20   |        |                 |

|           | Deep so       | Increased by RTC operation                  | When a crystal oscillator for<br>low clock loads is in use                              |       | —       | 1    | _    |        |                 |

|           |               |                                             | When a crystal oscillator for standard clock loads is in use                            |       | -       | 2    | _    |        |                 |

|           |               |                                             | Omitted                                                                                 |       |         |      | С    | mitted |                 |

## After Correction

|                       | Item         |                                                                            |                                                                                              |                    |   | Тур.    | Max. | Unit    | Test Conditions |

|-----------------------|--------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|---|---------|------|---------|-----------------|

| Supply                |              |                                                                            | Omitted                                                                                      | I <sub>CC</sub> *3 |   | Omitted |      |         |                 |

| current <sup>*1</sup> | e            | Power is supplied to standby RAM and USB resume detecting unit (USB0 only) |                                                                                              |                    | _ | 15.5    | 61   | μA      |                 |

|                       | standby mode | Power <mark>is</mark> not<br>supplied to<br>standby RAM and                | Low power consumption<br>function of the power-on reset<br>circuit is disabled <sup>*5</sup> |                    | _ | 11.5    | 38   |         |                 |

|                       | software st  | USB resume<br>detecting unit<br>(USB0 only)                                | Low power consumption<br>function of the power-on reset<br>circuit is enabled <sup>'6</sup>  |                    |   | 4.9     | 29   |         |                 |

|                       | Deep         | Increase current                                                           | When a low C <sub>L</sub> crystal is in use                                                  |                    | _ | 1       |      |         |                 |

|                       | Ō            | by operating RTC                                                           | When a standard C <sub>L</sub> crystal is in use                                             |                    | _ | 2       | —    |         |                 |

|                       |              |                                                                            | Omitted                                                                                      |                    |   |         |      | Dmitted |                 |

## No.11 57.2 DC Characteristics (Page 2386 of 2468)

Values of reference power supply current during 12-bit A/D conversion (unit 0) in Table 57.6 are corrected as follows:

#### Before correction

| Item                    |                                               | Symbol  | Min. | Тур. | Max. | Unit | Test Conditions |  |  |

|-------------------------|-----------------------------------------------|---------|------|------|------|------|-----------------|--|--|

|                         | On                                            | Omitted |      |      |      |      |                 |  |  |

| Reference               | During 12-bit A/D conversion (unit 0)         | AIREFH  | —    | 25   | 40   | μA   | IVREFH0         |  |  |

| power supply<br>current | Waiting for 12-bit A/D conversion (unit 0)    |         | —    | 0.07 | 0.4  | μA   | IVREFH0         |  |  |

|                         | 12-bit A/D converter in standby mode (unit 0) |         | _    | 0.07 | 0.2  | μA   | IVREFH0         |  |  |

|                         | On                                            | nitted  |      |      |      | -    |                 |  |  |

## After correction

| Item                    |                                                        | Symbol             | Min. | Тур. | Max. | Unit | Test Conditions |

|-------------------------|--------------------------------------------------------|--------------------|------|------|------|------|-----------------|

| Omitted                 |                                                        |                    |      |      |      |      |                 |

| Reference               | During 12-bit A/D conversion (unit 0)                  | Al <sub>REFH</sub> | —    | 38   | 60   | μA   | IVREFH0         |

| power supply<br>current | Waiting for 12-bit A/D conversion (unit 0)             |                    | _    | 0.07 | 0.4  | μA   | IVREFH0         |

|                         | 12-bit A/D converter in module stop status<br>(unit 0) |                    | _    | 0.07 | 0.2  | μA   | IVREFH0         |

Omitted

## No.12 57.2 DC Characteristics (Page 2386 of 2468)

The following Table 57.x Thermal Resistances is added to section 57.2.

#### After Correction

#### Table 57.x Thermal Resistances (Reference)

| Item               | Package                      | Symbol          | Max. | Unit | Test Conditions                    |

|--------------------|------------------------------|-----------------|------|------|------------------------------------|

| Thermal resistance | 144-pin LFQFP (PLQP0144KA-B) | θ <sub>ja</sub> | 50.9 | °C/W | JESD51-2 and JESD51-7 compliant    |

|                    | 100-pin LFQFP (PLQP0100KB-B) |                 | 52.5 |      |                                    |

|                    | 145-pin TFLGA (PTLG0145KA-A) |                 | 34.6 |      | JESD51-2 and<br>JESD51-9 compliant |

|                    | 100-pin TFLGA (PTLG0100JA-A) |                 | 34.1 |      |                                    |

|                    | 144-pin LFQFP (PLQP0144KA-B) | Ψ <sub>jt</sub> | 1.5  | °C/W | JESD51-2 and<br>JESD51-7 compliant |

|                    | 100-pin LFQFP (PLQP0100KB-B) |                 | 1.5  |      |                                    |

|                    | 145-pin TFLGA (PTLG0145KA-A) |                 | 0.4  |      | JESD51-2 and<br>JESD51-9 complian  |

|                    | 100-pin TFLGA (PTLG0100JA-A) |                 | 0.4  |      |                                    |

Note: The values are reference values when the 4-layer printed circuit board is used. Thermal resistance depends on the number of layers and size of the board. For details, refer to the JEDEC standards.

End of document