# RH850G3MH

User's Manual: Software

Renesas microcontroller

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by vou.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### NOTES FOR CMOS DEVICES

- (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN: Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (MAX) and VIH (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between VIL (MAX) and VIH (MIN).

- (2) HANDLING OF UNUSED INPUT PINS: Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

- (3) PRECAUTION AGAINST ESD: A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

- (4) STATUS BEFORE INITIALIZATION: Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

- (5) POWER ON/OFF SEQUENCE: In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

- (6) INPUT OF SIGNAL DURING POWER OFF STATE: Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

## **How to Use This Manual**

Target and Readers This manual is intended for users who wish to understand the RH850G3M

software and design application systems using these products.

**Conventions** Data significance: Higher digits on the left and lower digits on the

right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

Memory map address: Higher addresses on the top and lower addresses on

the bottom

Note: Footnote for item marked with Note in the text

Caution: Information requiring particular attention

Remark: Supplementary information

Numeric representation: Binary ... xxxx or xxxx<sub>B</sub>

Decimal ... xxxx

Hexadecimal ... xxxx<sub>H</sub>

Prefix indicating power of 2 (address space, memory capacity):

K (kilo):  $2^{10} = 1,024$

M (mega):  $2^{20} = 1,024^2$

G (giga):  $2^{30} = 1,024^3$

## **Table of Contents**

| Section | n 1   | OVERVIEW                                                             | 8  |

|---------|-------|----------------------------------------------------------------------|----|

| 1.1     | Fe    | atures of the RH850G3MH                                              | 8  |

| 1.2     | Ch    | anges from the RH850G3M                                              | 9  |

| Section | n 2   | PROCESSOR MODEL                                                      | 10 |

| 2.1     | CF    | U Operating Modes                                                    | 10 |

|         | 2.1.1 | Definition of CPU Operating Modes                                    |    |

|         | 2.1.2 | CPU Operating Mode Transition                                        |    |

|         | 2.1.3 | CPU Operating Modes and Privileges                                   |    |

| 2.2     | Ins   | truction Execution                                                   | 14 |

| 2.3     | Ex    | ceptions and Interrupts                                              | 16 |

|         | 2.3.1 | Exception Level                                                      |    |

| 2.4     | Co    | processors                                                           |    |

|         | 2.4.1 | Coprocessor Use Permissions                                          |    |

|         | 2.4.2 | Correspondences between Coprocessor Use Permissions and Coprocessors |    |

|         | 2.4.3 | Coprocessor Unusable Exceptions                                      |    |

|         | 2.4.4 | System Registers                                                     | 17 |

| 2.5     | Re    | gisters                                                              | 18 |

|         | 2.5.1 | Program Registers                                                    | 18 |

|         | 2.5.2 | System Registers                                                     | 18 |

|         | 2.5.3 | Register Updating                                                    | 18 |

|         | 2.5.4 | Accessing Undefined Registers                                        | 20 |

| 2.6     | Da    | ta Types                                                             | 21 |

|         | 2.6.1 | Data formats                                                         | 21 |

|         | 2.6.2 | Data Representation                                                  | 23 |

|         | 2.6.3 | Data Alignment                                                       | 24 |

| 2.7     | Ad    | dress Space                                                          | 26 |

|         | 2.7.1 | Memory Map                                                           | 27 |

|         | 2.7.2 | Instruction Addressing                                               | 28 |

|         | 2.7.3 | Data Addressing                                                      | 30 |

| 2.8     | Ac    | quiring the CPU Number                                               | 35 |

| 2.9     | Sy    | stem Protection Identifier                                           | 35 |

| Section | n 3   | REGISTER SET                                                         | 36 |

| 3.1     | Pro   | ogram Registers                                                      | 36 |

|         | 3.1.1 | General-Purpose Registers                                            | 37 |

|         | 3.1.2 | PC — Program Counter                                                 | 38 |

| 3.2     | Ва    | sic System Registers                                                 | 39 |

| 3.3     |       | errupt Function Registers                                            |    |

|         | 3.3.1 | Interrupt Function System Registers                                  |    |

| 3.4     |       | U Function Registers                                                 |    |

|         | 3.4.1 | Floating-Point Registers                                             |    |

|         | 3.4.2 | Floating-Point Function System Registers                             |    |

| 3.5    | MPU            | J Function Registers                                                  | 69  |

|--------|----------------|-----------------------------------------------------------------------|-----|

|        | 3.5.1          | MPU Function System Registers                                         | 69  |

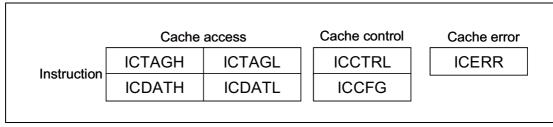

| 3.6    | Cacl           | he Operation Function Registers                                       | 77  |

|        | 3.6.1          | Cache Control Function System Registers                               | 77  |

| 3.7    | Data           | a Buffer Operation Registers                                          | 83  |

|        | 3.7.1          | Data Buffer Control System Registers                                  | 83  |

|        |                |                                                                       |     |

| Sectio | n 4 I          | EXCEPTIONS AND INTERRUPTS                                             | 84  |

| 4.1    | Outl           | ine of Exceptions                                                     | 84  |

|        | 4.1.1          | Exception Cause List                                                  | 84  |

|        | 4.1.2          | Overview of Exception Causes                                          | 87  |

|        | 4.1.3          | Types of Exceptions                                                   |     |

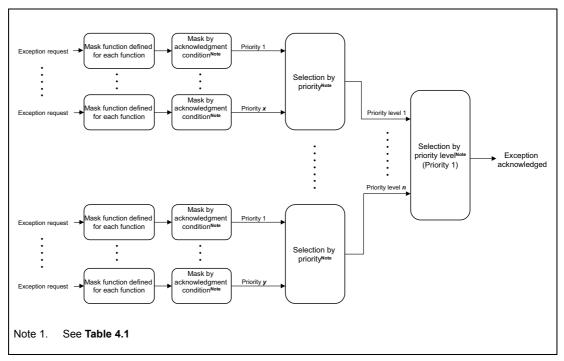

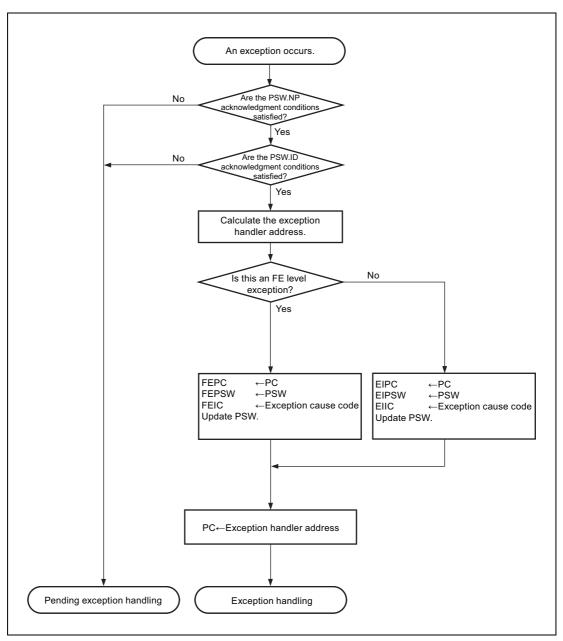

|        | 4.1.4          | Exception Acknowledgment Conditions and Priority Order                |     |

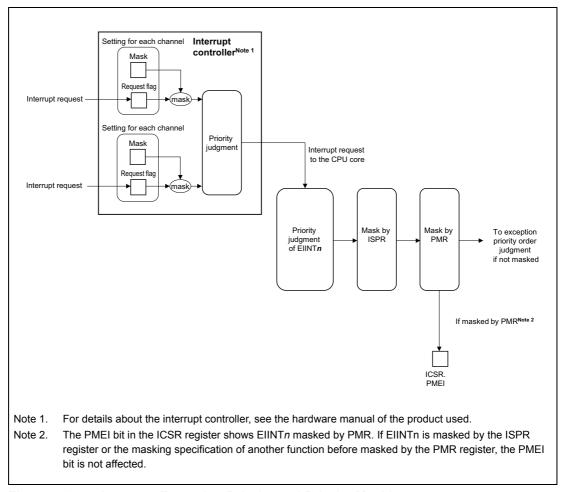

|        | 4.1.5          | Interrupt Exception Priority and Priority Masking                     |     |

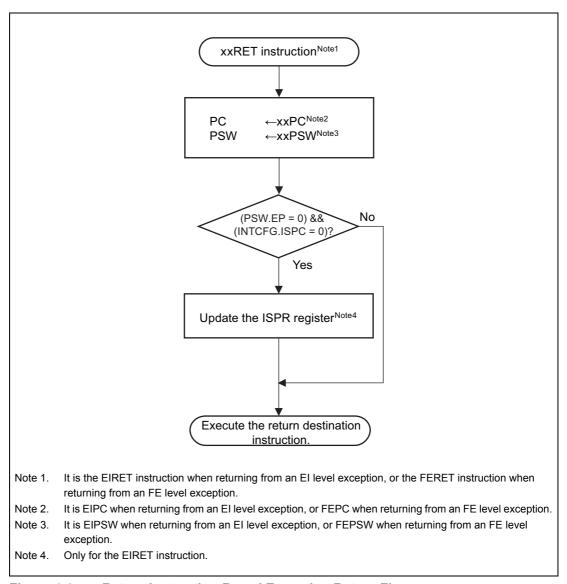

|        | 4.1.6          | Return and Restoration                                                |     |

|        | 4.1.7          | Context Saving                                                        |     |

| 4.2    | Ope            | ration When Acknowledging an Exception                                |     |

|        | 4.2.1          | Special Operations                                                    | 95  |

| 4.3    | Retu           | ırn from Exception Handling                                           | 96  |

| 4.4    | Exce           | eption Handler Address                                                | 98  |

|        | 4.4.1          | Resets, Exceptions, and Interrupts                                    | 98  |

|        | 4.4.2          | System Calls                                                          | 103 |

|        | 4.4.3          | Models for Application                                                | 104 |

| Sectio | n 5 I          | MEMORY MANAGEMENT                                                     | 106 |

|        |                |                                                                       |     |

| 5.1    |                | nory Protection Unit (MPU)                                            |     |

|        | 5.1.1          | Features                                                              |     |

|        | 5.1.2          | Protection Area Settings                                              |     |

|        | 5.1.3<br>5.1.4 | Caution Points for Protection Area Setup                              |     |

|        | 5.1.4<br>5.1.5 | Access Control  Violations and Exceptions                             |     |

|        | 5.1.6          | Memory Protection Setting Check Function                              |     |

| 5.2    |                | he                                                                    |     |

| 5.2    |                |                                                                       |     |

|        | 5.2.1<br>5.2.2 | Cache Operation Registers                                             |     |

|        | 5.2.2          | Cache Operations using CACHE Instruction                              |     |

|        | 5.2.4          | Cache Operations using CACHE Instruction is Executed                  |     |

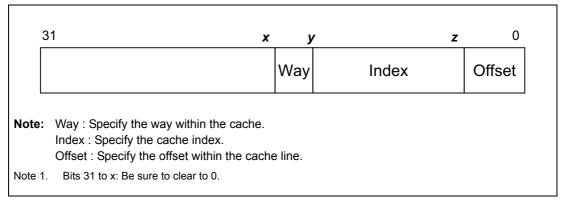

|        | 5.2.5          | Cache Index Specification Method                                      |     |

|        | 5.2.6          | Execution Privilege of the CACHE/PREF Instruction                     |     |

|        | 5.2.7          | Memory Protection for CACHE and PREF Instructions                     |     |

| 5.3    |                | ual Exclusion                                                         |     |

| 0.0    | 5.3.1          | Shared Data that does not Require Mutual Exclusion Processing         |     |

|        | 5.3.2          | Performing Mutual Exclusion by Using the LDL.W and STC.W Instructions |     |

|        | 5.3.3          | Performing Mutual Exclusion by Using the SET1 Instruction             |     |

|        |                | , ,                                                                   |     |

| 5.3.4              | Performing Mutual Exclusion by Using the CAXI Instruction | 121 |

|--------------------|-----------------------------------------------------------|-----|

| 5.4 Sy             | nchronization Function                                    | 122 |

| Section 6          | COPROCESSOR                                               | 124 |

| 6.1 Fl             | pating-Point Operation                                    | 124 |

| 6.1.1              | Configuration of Floating-Point Operation Function        | 124 |

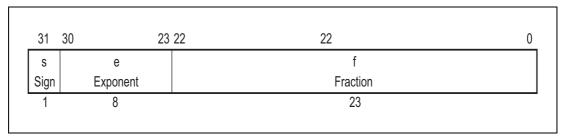

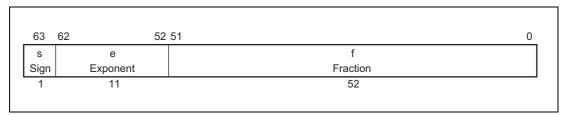

| 6.1.2              | Data Types                                                | 125 |

| 6.1.3              | Register Set                                              | 128 |

| 6.1.4              | Floating-Point Instructions                               | 128 |

| 6.1.5              | Floating-Point Operation Exceptions                       | 129 |

| 6.1.6              | Exception Details                                         | 132 |

| 6.1.7              | Saving and Returning Status                               | 136 |

| 6.1.8              | Flushing Subnormal Numbers                                |     |

| 6.1.9              | Flush to Nearest                                          | 139 |

| Section 7          | INSTRUCTION                                               | 140 |

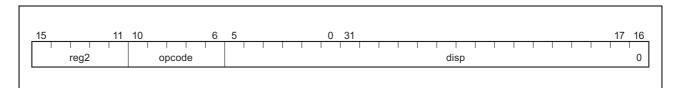

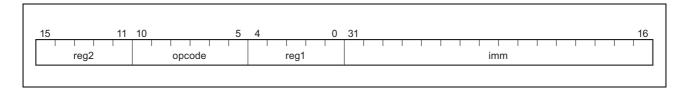

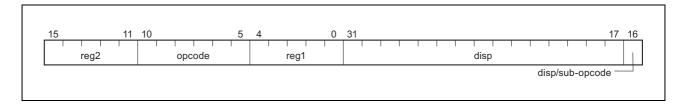

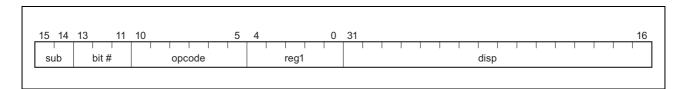

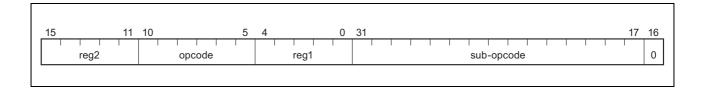

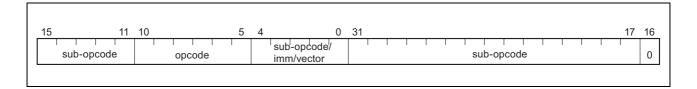

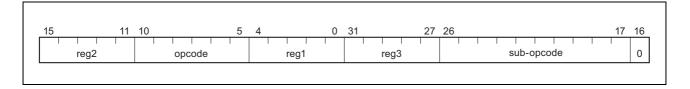

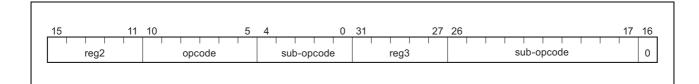

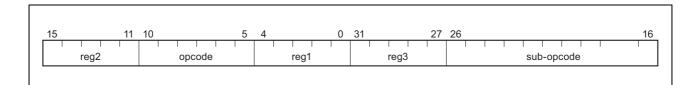

| 7.1 O <sub>l</sub> | ocodes and Instruction Formats                            | 140 |

| 7.1.1              | CPU Instructions                                          | 140 |

| 7.1.2              | Coprocessor Instructions                                  | 145 |

| 7.1.3              | Reserved Instructions                                     | 145 |

| 7.2 Ba             | sic Instructions                                          | 146 |

| 7.2.1              | Overview of Basic Instructions                            | 146 |

| 7.2.2              | Basic Instruction Set                                     | 151 |

| 7.3 Ca             | ache Instructions                                         | 302 |

| 7.3.1              | Overview of Cache Instructions                            | 302 |

| 7.3.2              | Cache Instruction Set                                     | 302 |

| 7.4 Fl             | pating-Point Instructions                                 | 307 |

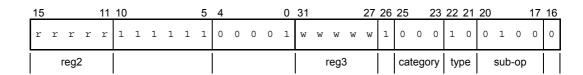

| 7.4.1              | Instruction formats                                       | 307 |

| 7.4.2              | Overview of Floating-Point Instructions                   | 308 |

| 7.4.3              | Conditions for Comparison Instructions                    | 311 |

| 7.4.4              | Floating-Point Instruction Set                            | 313 |

| Section 8          | RESET                                                     | 408 |

| 8.1 St             | atus of Registers After Reset                             | 408 |

| APPENDIX           |                                                           |     |

| APPENDIX           |                                                           |     |

|                    | umbers of Clock Cycles for Execution                      |     |

| B.2 No             | umber of G3MH Instruction Execution Clocks                | 411 |

| APPENDIX           |                                                           |     |

| APPENDIX           | D INSTRUCTION INDEX                                       | 421 |

RH850G3MH Software Section 1 OVERVIEW

## Section 1 OVERVIEW

## 1.1 Features of the RH850G3MH

The RH850G3MH features compatibility with the instruction set for all 32-bit RISC microcontrollers of the RH850G3M Series, but has even better performance.

**Table 1.1** shows the features of the RH850G3MH.

Table 1.1 Features of the RH850G3MH

| Item                  | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                   | High performance 32-bit architecture for embedded control                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       | 32-bit internal data bus                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | Thirty-two 32-bit general-purpose registers                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                       | <ul> <li>RISC type instruction set (compatible with RH850G3M)         Long/short type load/store instructions         Three-operand instructions         Instruction set based on C     </li> </ul>                                                                                                                                                                                                                                                           |

|                       | <ul> <li>CPU operating modes</li> <li>User mode and supervisor mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                |

|                       | <ul> <li>Address space: 4-Gbyte linear space for both data and instructions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

| Coprocessor           | <ul> <li>A floating point operation coprocessor (FPU) can be installed.         Supports single precision (32-bit) and double precision (64-bit)         Supports IEEE754-compliant data types and exceptions         Rounding modes: Nearest, 0 direction, +∞ direction, and -∞ direction         Handling on non-normalized numbers: These are truncated to 0, or an exception is reported because such numbers do not comply with IEEE754.     </li> </ul> |

| Exceptions/interrupts | 16-level interrupt priority that can be specified for each channel     Vector selection method that can be selected according to performance requirements and the amount of consumed memory     Direct branch method exception vector (direct vector method)     Address-table-referencing indirect branch method exception vector (table reference method)                                                                                                   |

|                       | <ul> <li>Support for high-speed context backup and restoration processing on interrupt by<br/>using dedicated instructions (PUSHSP, POPSP)</li> </ul>                                                                                                                                                                                                                                                                                                         |

| Memory management     | A memory protection unit (MPU) can be installed.                                                                                                                                                                                                                                                                                                                                                                                                              |

| Caches                | An instruction cache can be installed.                                                                                                                                                                                                                                                                                                                                                                                                                        |

RH850G3MH Software Section 1 OVERVIEW

## 1.2 Changes from the RH850G3M

Table 1.2 Changes from the RH850G3M

| Item                  | Changes                                                                                                                                                                                                                                                                              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                   | <ul> <li>The specifications of system registers listed below were changed.</li> <li>The specifications of MEI and MCTL were changed (see Section 3.2, Basic System Registers).</li> </ul>                                                                                            |

|                       | <ul> <li>The function of the SYNCE instruction was changed (see Section 7.2.2, Basic<br/>Instruction Set).</li> </ul>                                                                                                                                                                |

|                       | <ul> <li>The hazard resolution procedure does not proceed after updating of SCCFG as it was found to be unnecessary in that case (see APPENDIX A, HAZARD RESOLUTION PROCEDURE FOR SYSTEM REGISTERS).</li> </ul>                                                                      |

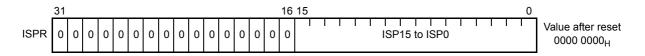

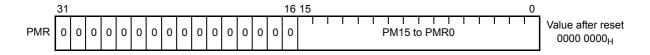

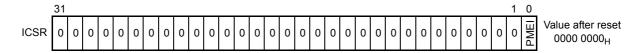

| Exceptions/interrupts | The specifications of system registers were changed and a system register was deleted as stated below.     FPIPR was deleted, and the specifications of ISPR, PMR, and ICSR were changed (see Section 3.3.1, Interrupt Function System Registers).                                   |

|                       | <ul> <li>Changes were made to the exceptions for floating-point operations.</li> <li>The FPP exception and FPI exception were abolished. An FPINT exception was added.</li> </ul>                                                                                                    |

| Coprocessor           | <ul> <li>The specification of a system register was changed and a system register was<br/>deleted as stated below.</li> <li>The specification of FPSR was changed and FPEC was deleted (see Section 3.4.2,<br/>Floating-Point Function System Registers).</li> </ul>                 |

|                       | <ul> <li>The hazard resolution procedure does not proceed after updating of any of the FPU<br/>registers (FPSR, FPEPC, FPST, FPCC, or FPCFG) as it was found to be<br/>unnecessary in these cases (see APPENDIX A, HAZARD RESOLUTION<br/>PROCEDURE FOR SYSTEM REGISTERS).</li> </ul> |

|                       | <ul> <li>In some cases, an approximate result of the following floating-point instructions<br/>differs very small from an approximate result of the same instruction in RH850G3M.</li> <li>RECIPF.D, RECIPF.S, RSQRTF.D and RSQRTF.S</li> </ul>                                      |

| Memory management     | <ul> <li>A specification of the MPU was changed.         The operation in response to memory access spanning contiguous areas to which access is enabled by the MPU was changed (see Section 5.1.3, Caution Points for Protection Area Setup).     </li> </ul>                       |

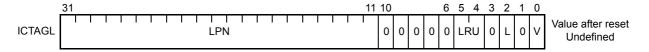

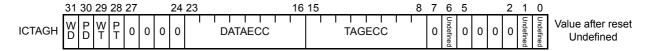

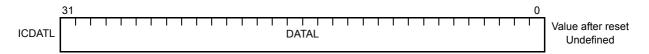

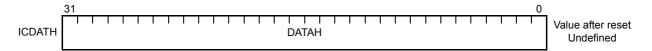

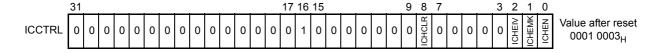

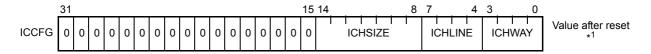

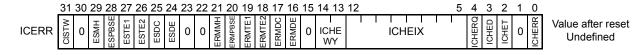

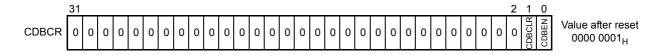

| Cache                 | The specifications of system registers listed below were changed.     The specifications of ICCTRL, ICTAGL, ICTAGH, ICCFG and ICERR were changed (see Section 3.6.1, Cache Control Function System Registers).                                                                       |

|                       | <ul> <li>The wait for the completion of clearing of the instruction cache by the<br/>ICCTRL.ICHCLR bit is not necessary (see APPENDIX A, HAZARD RESOLUTION<br/>PROCEDURE FOR SYSTEM REGISTERS).</li> </ul>                                                                           |

## Section 2 PROCESSOR MODEL

This CPU defines a processor model that has basic operation functions, registers, and an exception management function.

This section describes the unique features of the processor model of this CPU.

## 2.1 CPU Operating Modes

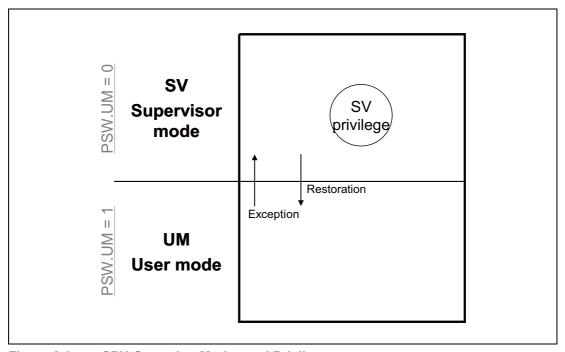

This CPU has defines two operating statuses of the supervisor mode (SV) and the user mode (UM). Whether the system is in supervisor mode or user mode is indicated by the UM bit in the PSW register.

- Supervisor mode (PSW.UM = 0) : All hardware functions can be managed or used.

- User mode (PSW.UM = 1): The usable hardware functions are restricted.

## 2.1.1 Definition of CPU Operating Modes

#### (1) Supervisor mode (SV)

All hardware functions can be managed or used in this mode. The system always starts up in supervisor mode after the end of reset processing.

#### (2) User mode (UM)

This operating mode makes up a pair with the supervisor mode. In user mode, address spaces to which access is permitted by the supervisor and the system registers defined as user resources can be used. Supervisor-privileged instructions cannot be executed and result in exceptions if they are.

Restriction in user mode (PSW.UM = 1)

• Privileged instruction violations due to SV-privileged-instruction operating restrictions (→ PIE exceptions) For details about privileged-instruction operating restrictions, see **Section 2.1.3, CPU Operating Modes and Privileges**

## 2.1.2 CPU Operating Mode Transition

The CPU operating mode changes due to three events.

#### (1) Change due to acknowledging an exception

When an exception is acknowledged, the CPU operating mode changes to the mode specified for the exception.

#### (2) Change due to a return instruction

When a return instruction is executed, the PSW value is restored according to the value of the corresponding bit backed up to EIPSW and FEPSW.

#### (3) Change due to a system register instruction

The CPU operating mode changes when an LDSR instruction is used to directly overwrite the PSW operating mode bits.

#### **CAUTIONS**

- 1. In supervisor mode, the LDSR instruction can be used to directly change the value of the PSW.UM bit, but system-register-related hazards are defined in the hardware specifications. For the change of this bit, it is recommended to use a return instruction to avoid PSW-register-related hazards.

- 2. In user mode, the CPU operating mode cannot be changed because the higher 31 to 5 bits of the PSW register cannot be overwritten. The CPU operating mode might be changed in supervisor mode, but system register access-related hazards are defined in the hardware specifications. For the change of this bit, it is recommended to use a return instruction to avoid PSW-register-related hazards.

## 2.1.3 CPU Operating Modes and Privileges

In this CPU, the usable functions can be restricted according to usage permission settings for specific resources and the CPU operating mode. Specification instructions (including instructions that update specific system registers) can only be executed in the defined operating mode. The permissions necessary to execute these specification instructions are called "privileges" below. In operating modes that do not have privileges, these instructions are not executed and exceptions occur.

This CPU defines the following two types of privileges (and usage permission).

- Supervisor (SV) privilege: Important system resources operation, fatal error processing, privilege necessary for user-mode program execution management

- Coprocessor use permissions: Permissions necessary to use a coprocessor

Figure 2.1 CPU Operating Modes and Privileges

#### (1) Supervisor privilege (SV privilege)

The privilege necessary to perform the operation for important system resources, fatal error processing, and user-mode program execution management is called the supervisor privilege (SV privilege). This privilege is available in supervisor mode. The SV privilege is generally necessary to execute instructions used to perform the operation for important system resources, and these instructions are sometimes called SV privileged instructions.

#### (2) Coprocessor use permissions

Regardless of the CPU operating mode, it is possible to separately specify whether coprocessors can be used.

The CU2 to CU0 bits in the PSW register are used in supervisor mode to specify whether coprocessors can be used by each program. If the CU bits are not set to 1, a coprocessor unusable exception occurs when the corresponding coprocessor instruction is executed or the system register is accessed.

If no coprocessor is installed, it is not possible to set the corresponding CU bits to 1. The setting of the CU2 to CU0 bits is valid regardless of the CPU operating mode, and, if the supervisor accesses coprocessor system registers, it is necessary to set the CU2 to CU0 bits to enable coprocessor use.

#### (3) Operation when there is a privilege violation

When an attempt is made to execute a privileged instruction by someone who does not have the required privilege, a PIE exception or UCPOP exception occurs. **Table 2.1** shows the relationships between the operating mode, usage permission status, and whether instructions can be executed.

Table 2.1 Operation When There is a Privilege Violation

|                                                       | PSW |     |     |     |                               |

|-------------------------------------------------------|-----|-----|-----|-----|-------------------------------|

|                                                       | UM  | CU2 | CU1 | CU0 | Whether Operation is Possible |

| SV privileged instruction                             | 0   | _   | _   | _   | Possible                      |

|                                                       | 1   | _   | _   | _   | Not possible/PIE exception    |

| Coprocessor instruction 1*1                           | _   | _   | _   | 1   | Possible                      |

| (PSW.CU0 bit)                                         | _   | _   | _   | 0   | Not possible/UCPOP exception  |

| Coprocessor instruction 2*1                           | _   | _   | 1   | _   | Possible                      |

| (PSW.CU1 bit)                                         | _   | _   | 0   | _   | Not possible/UCPOP exception  |

| Coprocessor instruction 3*1                           | _   | 1   | _   | _   | Possible                      |

| (PSW.CU2 bit)                                         | _   | 0   | _   |     | Not possible/UCPOP exception  |

| Instructions other than the above (user instructions) | _   | _   | _   | _   | Possible                      |

Note 1. This includes the LDSR/STSR instruction for the coprocessor system register.

**Note:** —: 0 or 1

## 2.2 Instruction Execution

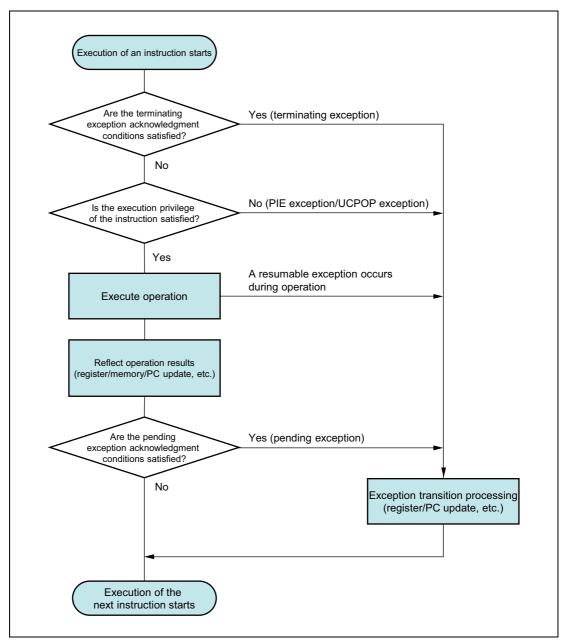

The instruction execution flow of this CPU is shown below.

Figure 2.2 Instruction Execution Flow

If terminating exceptions can be acknowledged or if the execution privilege of the instruction is not satisfied, an exception occurs before the instruction is executed. If a resumable exception occurs during the execution of an instruction, the exception is acknowledged during execution of the instruction. In these cases, the result of instruction execution is not reflected in the registers or memory, and the CPU state before the instruction was executed is retained\*<sup>1</sup>.

For a pending exception such as a software exception, the exception is acknowledged after the result of instruction execution has been reflected.

**Note 1.** The following instructions might cause intermediate results to be reflected in the memory. PREPARE, DISPOSE, PUSHSP, POPSP

## 2.3 Exceptions and Interrupts

Exceptions and interrupts are exceptional events that cause the program under execution to branch to another program. Exceptions and interrupts are triggered by various sources, including interrupts from peripherals and program abnormalities.

For details, see Section 4, EXCEPTIONS AND INTERRUPTS.

#### 2.3.1 Exception Level

In this CPU, if an exception with a high degree of urgency occurs while another exception is being processed, the urgent exception will be processed by priority. To make it possible to return to the interrupted exception handling after acknowledging the urgent exception, even if the context had not been saved to the memory, exception causes are managed in the following two hierarchical levels.

- EI level exception

- FE level exception

EI level exceptions are used for processing such as regular user processing, interrupt servicing, and OS processing. FE level exceptions are used to enable interrupts with a high degree of urgency for the system or exceptions from the memory management function that might occur during OS processing to be acknowledged even while an EI level exception is being processed.

## 2.4 Coprocessors

In this CPU, single-precision and double-precision FPU expansion functions are incorporated.

## 2.4.1 Coprocessor Use Permissions

To execute a coprocessor instruction or defined opcode processing, permission to use the corresponding coprocessor instruction is necessary. Coprocessor use permissions are specified by the PSW.CU2 to PSW.CU0 bits, and, if an attempt is made to execute an instruction for which the corresponding coprocessor use permission is cleared to 0, a coprocessor unusable exception (UCPOP) occurs.

# 2.4.2 Correspondences between Coprocessor Use Permissions and Coprocessors

This CPU defines coprocessor use permissions to control the availability of the coprocessor for each program during CPU operation. There are three coprocessor use permissions (CU0 to CU2), and their correspondences with the coprocessors are shown in the following table.

Table 2.2 Correspondences Between Coprocessor Use Permissions and Coprocessors

| Coprocessor Use Permission | Coprocessor Function                    | Exception Cause Code |  |

|----------------------------|-----------------------------------------|----------------------|--|

| CU0                        | Single-precision FPU expansion function | 80 <sub>H</sub>      |  |

|                            | Double-precision FPU expansion function | _                    |  |

| CU1                        | Reserved                                | 81 <sub>H</sub>      |  |

| CU2                        | Reserved                                | 82 <sub>H</sub>      |  |

#### 2.4.3 Coprocessor Unusable Exceptions

A coprocessor unusable exception occurs if an attempt is made to execute a coprocessor instruction or access a system register of the coprocessor without having the corresponding coprocessor use permission (PSW.CUn = 0).

#### 2.4.4 System Registers

Some coprocessor functions are defined by system registers. The coprocessor use permission is necessary to access the system register of a coprocessor function. For some system registers, the supervisor privilege (SV permission) is necessary in addition to the coprocessor use permission.

For details about the permissions necessary to access system registers, see **Section 2.5, Registers**.

## 2.5 Registers

This CPU defines program registers (general-purpose registers and the program counter PC) and system registers for controlling the status and storing exception information.

## 2.5.1 Program Registers

The program registers include general-purpose registers (r0 to r31) and the program counter (PC).

Table 2.3 Program Registers

| Category                  | Access Permission | Name      |

|---------------------------|-------------------|-----------|

| Program counter           | UM                | PC        |

| General-purpose registers | UM                | r0 to r31 |

Note: UM: User register. This register can always be accessed because no access permission is required.

## 2.5.2 System Registers

For details about program registers, see **Section 3.1**, **Program Registers**.

Group numbers 0 to 3: Registers related to basic functions

Group numbers 4 to 7: Registers related to the memory management function

Group numbers 12 to 15: Registers defined in the CPU hardware specifications

Group numbers 16 and later: Reserved for future expansion

For details about system registers, see the relevant sections in **Section 3**, **REGISTER SET**.

#### 2.5.3 Register Updating

There are several methods used to update registers. Normally, no particular restrictions apply when updating register by using an instruction. However, when updating registers by using the following instructions, some restrictions might apply, depending on the operating mode.

- LDSR

- STSR

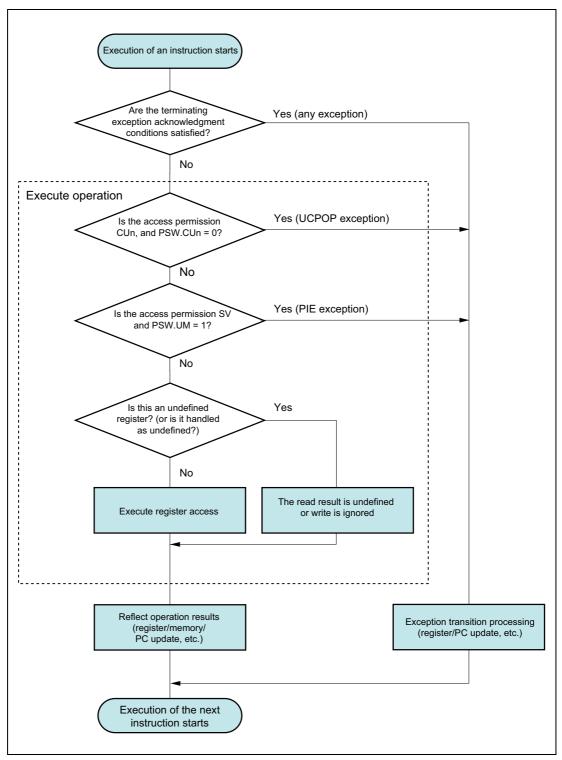

#### (1) LDSR and STSR

The LDSR and STSR instructions can access all the system registers. However, If a system register is accessed without the proper permission, a PIE exception or UCPOP exception might occur. For details about the access permission for each register, see the description of system registers in **Section 3**, **REGISTER SET**. For details about behaviors when a privilege violation occurs, see **Section 2.1.3**, **CPU Operating Modes and Privileges**.

**Figure 2.3** shows the flow of executing the LDSR and STSR instructions.

Figure 2.3 Flow of Executing the LDSR and STSR Instructions

## 2.5.4 Accessing Undefined Registers

If a system register number without any register assigned is accessed or if an inaccessible register is accessed, the following results occur.

- Undefined registers are handled as having the SV permission. When they are accessed by an LDSR or STSR instruction in user mode (PSW.UM = 1), a PIE exception occurs.

- For a read operation, the read result is undefined. If the read value is used in a program, unexpected behaviors might occur.

- For a write operation, the write operation is ignored.

However, writing to the following system register numbers is prohibited.

Writing prohibited: [SR11, 0], [SR1, 1], [SR7, 1], [SR10, 1], [SR13, 1], [SR14, 1], [SR15, 1], [SR16, 1], [SR5, 2], [SR20, 5]

## 2.6 Data Types

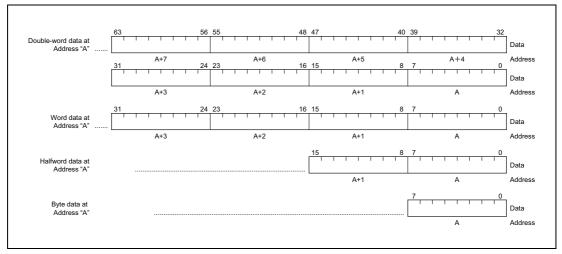

#### 2.6.1 Data formats

This CPU handles data in little endian format. This means that byte 0 of a halfword or a word is always the least significant (rightmost) byte.

The supported data format is as follows.

- Byte (8-bit data)

- Halfword (16-bit data)

- Word (32-bit data)

- Double-word (64-bit data)

- Bit (1-bit data)

#### (1) Byte

A byte is 8 consecutive bits of data that starts from any byte boundary. Numbers from 0 to 7 are assigned to these bits, with bit 0 as the LSB (least significant bit) and bit 7 as the MSB (most significant bit). The byte address is specified as "A".

#### (2) Halfword

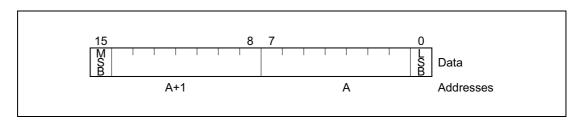

A halfword is two consecutive bytes (16 bits) of data that starts from any byte boundary. Numbers from 0 to 15 are assigned to these bits, with bit 0 as the LSB and bit 15 as the MSB. The bytes in a halfword are specified using address "A", so that the two addresses comprise byte data of "A" and "A + 1".

#### (3) Word

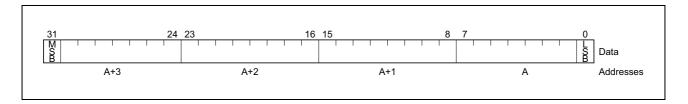

A word is four consecutive bytes (32 bits) of data that starts from any byte boundary. Numbers from 0 to 31 are assigned to these bits, with bit 0 as the LSB (least significant bit) and bit 31 as the MSB (most significant bit). A word is specified by address "A" and consists of byte data of four addresses: "A", "A + 1", "A + 2", and "A + 3".

#### (4) Double-word

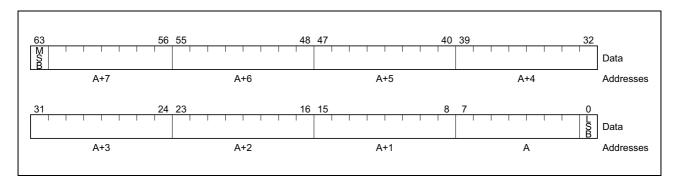

A double-word is eight consecutive bytes (64 bits) that start from any 4-byte boundary. Numbers from 0 to 63 are assigned to these bits, with bit 0 as the LSB and bit 63 as the MSB. A double-word is specified by address "A" and consists of byte data of eight addresses: "A", "A + 1", "A + 2", "A + 3", "A + 4", "A + 5", "A + 6", and "A + 7".

#### (5) Bit

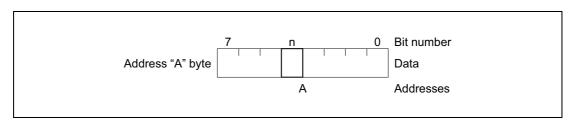

A bit is bit data at the nth bit within 8-bit data that starts from any byte boundary. Each bit is specified using its byte address "A" and its bit number "n" (n = 0 to 7).

#### 2.6.2 Data Representation

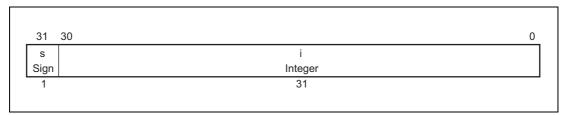

#### (1) Integers

Integers are represented as binary values using 2's complement, and are used in one of four lengths: 64 bits, 32 bits, 16 bits, or 8 bits. Regardless of the length of an integer, its place uses bit 0 as the LSB, and this place gets higher as the bit number increases. Because this is a 2's complement representation, the MSB is used as a signed bit.

The integer ranges for various data lengths are as follows.

- Double-word (64 bits): -9,223,372,036,854,775,808 to +9,223,372,036,854,775,807

- Word (32 bits): -2,147,483,648 to +2,147,483,647

- Halfword (16 bits): -32,768 to +32,767

- Byte (8 bits): -128 to +127

#### (2) Unsigned integers

In contrast to "integers" which are data that can take either a positive or negative sign, "unsigned integers" are never negative integers. Like integers, unsigned integers are represented as binary values, and are used in one of four lengths: 64 bits, 32 bits, 16 bits, or 8 bits. Also like integers, the place of unsigned integers uses bit 0 as the LSB and gets higher as the bit number increases. However, unsigned integers do not use a sign bit.

The unsigned integer ranges for various data lengths are as follows.

- Double-word (64 bits): 0 to 18,446,744,073,709,551,615

- Word (32 bits): 0 to 4,294,967,295

- Halfword (16 bits): 0 to 65,535

- Byte (8 bits): 0 to 255

#### (3) Bits

Bit data are handled as single-bit data with either of two values: cleared (0) or set (1). There are four types of bit-related operations (listed below), which target only single-byte data in the memory space.

- Set

- Clear

- Invert

- Test

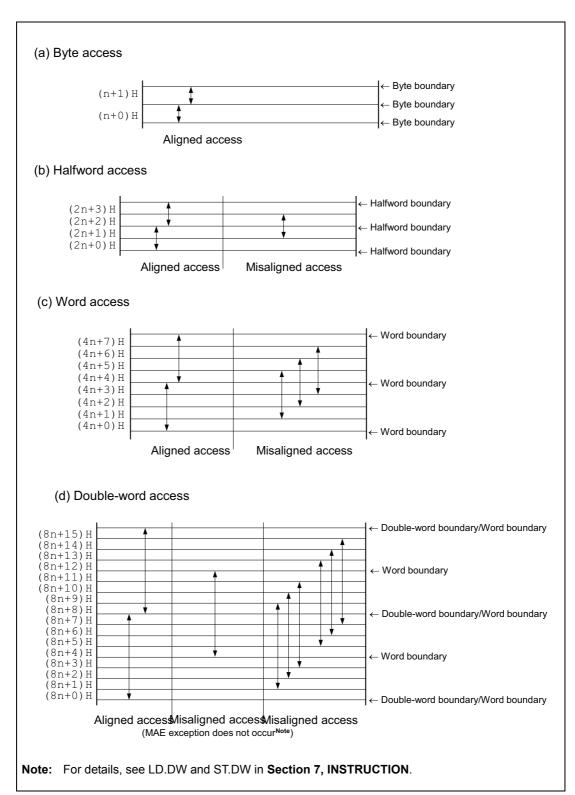

## 2.6.3 Data Alignment

When the result of address calculation is a misaligned address, a misaligned access exception (MAE) occurs.

When the data to be processed is in halfword format, misaligned access indicates the access to an address that is not at the halfword boundary (where the address LSB = 0), and when the data to be processed is in word format, misaligned access indicates the access to an address that is not at the word boundary (where the lower two bits of the address = 0). When the data to be processed is in doubleword format, misaligned access indicates the access to an address that is not at the double-word boundary (where the lower 3 bits of the address = 0).

For the double-word format only, a misaligned access exception does not occur when data is placed at the word boundary rather than the double-word boundary.

#### **CAUTIONS**

- 1. The following instructions might possibly cause misaligned access. For details, see the relevant descriptions in Section 7, INSTRUCTION.

- LD.H, LD.HU, LD.W, LD.DW

- SLD.H, SLD.HU, SLD.W

- ST.H, ST.W, ST.DW

- SST.H, SST.W

- LDL.W, STC.W, CAXI

- 2. The following instructions do not cause misaligned access, because the address is rounded in the instruction specification when the alignment specification is incorrect.

- PREPARE, DISPOSE

- PUSHSP, POPSP

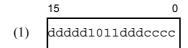

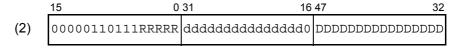

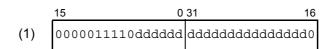

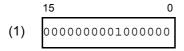

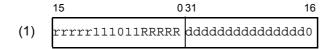

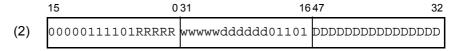

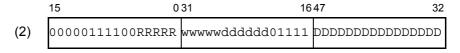

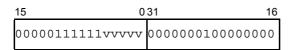

Figure 2.4 Example of Data Placement for Misaligned Access

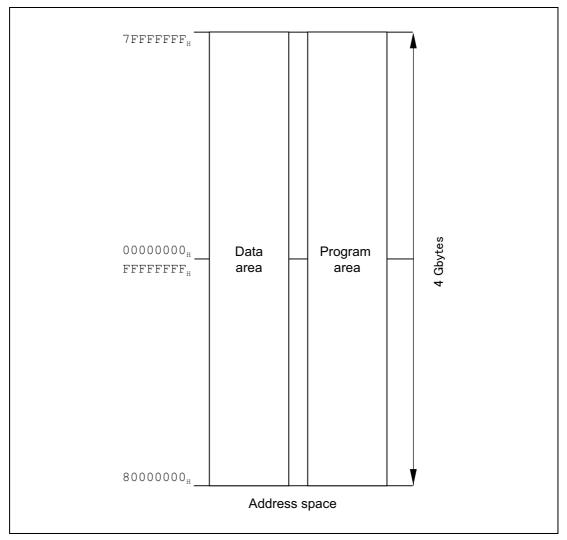

## 2.7 Address Space

This CPU supports a linear address space of up to 4 Gbytes. Both memory and I/O can be mapped to this address space (using the memory mapped I/O method). The CPU outputs a 32-bit address for memory and I/O, in which the highest address number is " $2^{32} - 1$ ".

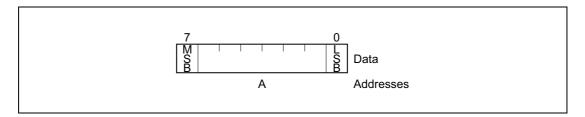

The byte data placed at various addresses is defined with bit 0 as the LSB and bit 7 as the MSB. When the data is comprised of multiple bytes, it is defined so that the byte data at the lowest address is the LSB and the byte data at the highest address is the MSB (i.e., in little endian format).

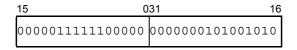

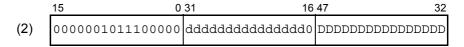

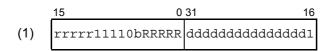

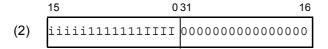

This manual stipulates that, when representing data comprised of multiple bytes, the right edge must be represented as the lower address and the left side as the upper address, as shown below.

Figure 2.5 Address Space Byte Format

## 2.7.1 Memory Map

This CPU is 32-bit architecture and supports a linear address space of up to 4 Gbytes. The whole range of this 4-Gbyte address space can be addressed by instruction addressing (instruction access) and operand addressing (data access).

A memory map is shown in **Figure 2.6**.

Figure 2.6 Memory Map (Address Space)

## 2.7.2 Instruction Addressing

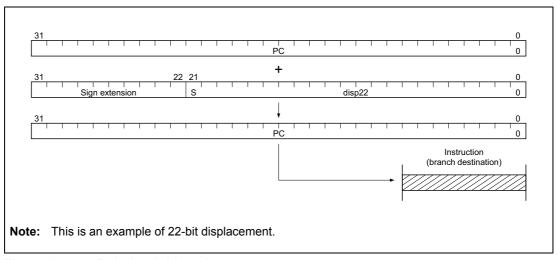

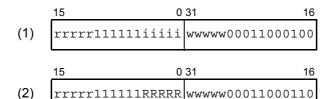

The instruction address is determined based on the contents of the program counter (PC), and is automatically incremented according to the number of bytes in the executed instruction. When a branch instruction is executed, the addressing shown below is used to set the branch destination address to the PC.

#### (1) Relative addressing (PC relative)

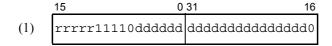

Signed N-bit data (displacement: disp N) is added to the instruction code in the program counter (PC). In this case, displacement is handled as 2's complement data, and the MSB is a signed bit (S). If the displacement is less than 32 bits, the higher bits are sign-extended (N differs from one instruction to another).

The JARL, JR, and Bcond instructions are used with this type of addressing.

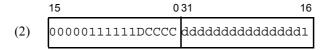

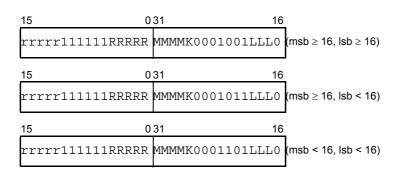

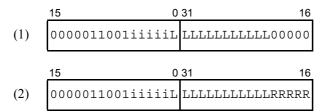

Figure 2.7 Relative Addressing

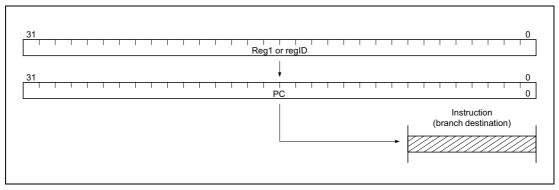

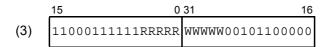

#### (2) Register addressing (register indirect)

The contents of the general-purpose register (reg1) or system register (regID) specified by the instruction are transferred to the program counter (PC).

The JMP, CTRET, EIRET, FERET, and DISPOSE instructions are used with this type of addressing.

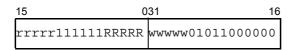

Figure 2.8 Register Addressing

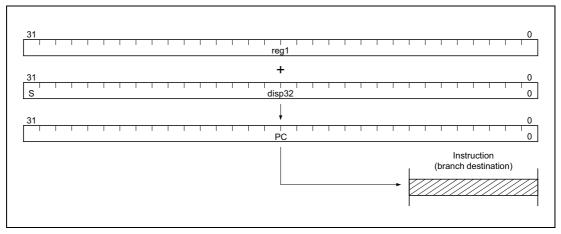

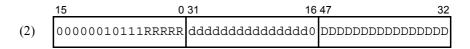

#### (3) Based addressing

Contents that are specified by the instruction in the general-purpose register (reg1) and that include the added N-bit displacement (dispN) are transferred to the program counter (PC). At this time, the displacement is handled as a 2's complement data, and the MSB is a signed bit (S). If the displacement is less than 32 bits, the higher bits are sign-extended (N differs from one instruction to another).

The JMP instruction is used with this type of addressing.

Figure 2.9 Based Addressing

#### (4) Other addressing

A value specified by an instruction is transferred to the program counter (PC). How a value is specified is explained in [Operation] or [Description] of each instruction.

The CALLT, SYSCALL, TRAP, FETRAP, and RIE instructions, and branch in case of an exception are used with this type of addressing.

## 2.7.3 Data Addressing

The following methods can be used to access the target registers or memory when executing an instruction.

#### (1) Register addressing

This addressing method accesses the general-purpose register or system register specified in the general-purpose register field as an operand.

Any instruction that includes the operand reg1, reg2, reg3, or regID is used with this type of addressing.

#### (2) Immediate addressing

This address mode uses arbitrary size data as the operation target in the instruction code.

Any instruction that includes the operand imm5, imm16, vector, or cccc is used with this type of addressing.

#### **NOTE**

vector: This is immediate data that specifies the exception vector (00<sub>H</sub> to 1F<sub>H</sub>), and is an operand used by the TRAP, FETRAP, and SYSCALL instructions. The data width differs from one instruction to another.

cccc: This is 4-bit data that specifies a condition code, and is an operand used in the CMOV instruction, SASF instruction, and SETF instruction. One bit (0) is added to the higher position and is then assigned to an opcode as a 5-bit immediate data.

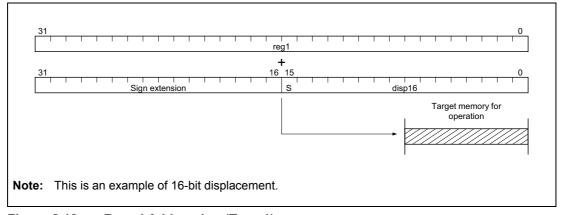

#### (3) Based addressing

There are two types of based addressing, as described below.

#### (a) Type 1

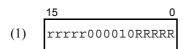

The contents of the general-purpose register (reg1) specified at the addressing specification field in the instruction code are added to the N-bit displacement (dispN) data sign-extended to word length to obtain the operand address, and addressing accesses the target memory for the operation. At this time, the displacement is handled as a 2's complement data, and the MSB is a signed bit (S). If the displacement is less than 32 bits, the higher bits are sign-extended (N differs from one instruction to another).

The LD, ST, and CAXI instructions are used with this type of addressing.

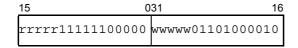

Figure 2.10 Based Addressing (Type 1)

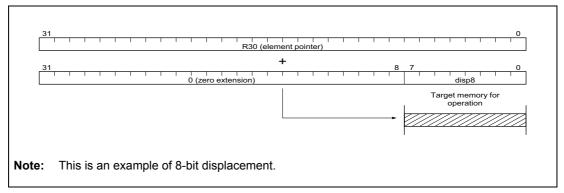

#### (b) Type 2

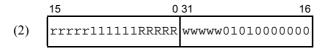

This addressing accesses a memory to be manipulated by using as an operand address the sum of the contents of the element pointer (r30) and N-bit displacement data (dispN) that is zero-extended to a word length. If the displacement is less than 32 bits, the higher bits are sign-extended (N differs from one instruction to another).

The SLD instruction and SST instruction are used with this type of addressing.

Figure 2.11 Based Addressing (Type 2)

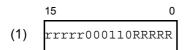

#### (4) Bit addressing

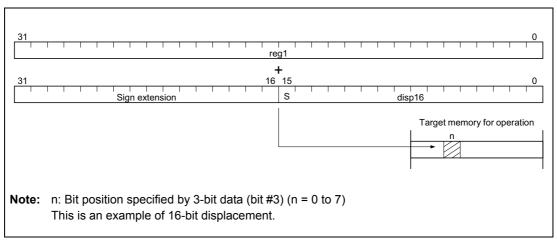

The contents of the general-purpose register (reg1) are added to the N-bit displacement (dispN) data sign-extended to word length to obtain the operand address, and bit addressing accesses one bit (as specified by 3-bit data "bit #3") in one byte of the target memory space. At this time, the displacement is handled as a 2's complement data, and the MSB is a signed bit (S). If the displacement is less than 32 bits, the higher bits are sign-extended (N differs from one instruction to another).

The CLR1, SET1, NOT1, and TST1 instructions are used with this type of addressing.

Figure 2.12 Bit Addressing

#### (5) Post index increment/decrement addressing

The contents of the general-purpose register (reg1) are used as an operand address to access the target memory, and then the general-purpose register (reg1) is updated. The register is updated by either incrementing or decrementing it, and there are three types (1 to 3).

If the result of incrementing the general-purpose register (reg1) value exceeds the positive maximum value 0xFFFF FFFF, the result wraps around to 0x0000 0000, and, if the result of decrementing the general-purpose register value is less than the positive minimum value 0x0000 0000, the result wraps around to 0xFFFF FFFF.

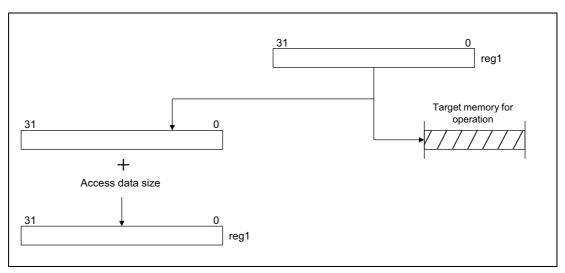

#### (a) Type 1

The general-purpose register (reg1) is updated by adding a constant that depends on the type of accessed data (the size of the accessed data) to the contents of the general-purpose register (reg1). If the type of accessed data is a byte, 1 is added, if the type is a halfword, 2 is added, if the type is a word, 4 is added, and if the type is a double-word, 8 is added.

Figure 2.13 Post Index Increment/Decrement Addressing (Type 1)

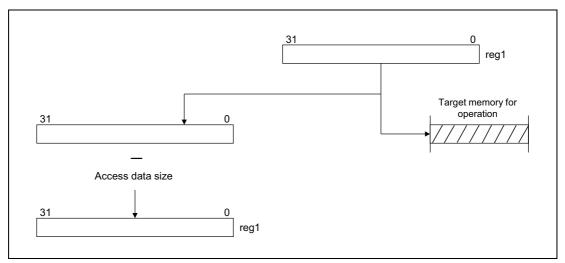

#### (b) Type 2

The general-purpose register (reg1) is updated by subtracting a constant that depends on the size of the accessed data from the contents of the general-purpose register (reg1). If the size of accessed data is a byte, 1 is subtracted, if the size is a halfword, 2 is subtracted, if the size is a word, 4 is subtracted, and if the size is a double-word, 8 is subtracted.

Figure 2.14 Post Index Increment/Decrement Addressing (Type 2)

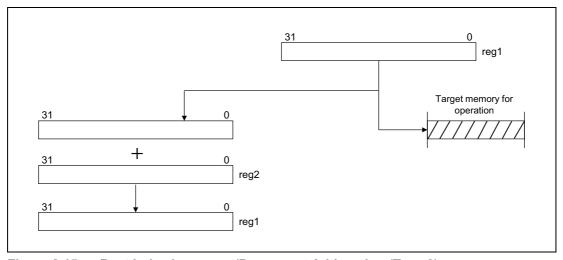

#### (c) Type 3

The general-purpose register (reg1) is updated by adding the contents of another general-purpose register (reg2) to it. If the MSB of the general-purpose register (reg2) is 1, a negative value is indicated, so a post decrement operation is performed. If this MSB is 0, a positive value is indicated, so a post increment operation is performed. The value of the general-purpose register (reg2) does not change.

Figure 2.15 Post Index Increment/Decrement Addressing (Type 3)

#### (6) Other addressing

This addressing is to access a memory to be manipulated by using a value specified by an instruction as the operand address. How a value is specified is explained in [Operation] or [Description] of each instruction.

The SWITCH, CALLT, SYSCALL, PREPARE, DISPOSE, PUSHSP, and POPSP instructions are used with this type of addressing.

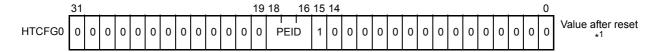

## 2.8 Acquiring the CPU Number

This CPU provides a method for identifying CPUs in a multi-processor system.

In the multi-processor configuration, you can identify which CPU core is running a program by referencing HTCFG0.PEID. With HTCFG0.PEID, unique numbers are assigned within multi-processor systems.

## 2.9 System Protection Identifier

In this CPU, memory resources and peripheral devices are managed by system protection groups. By specifying the group to which the program being executed belongs, you can assign operable memory resources and peripheral devices to each machine.

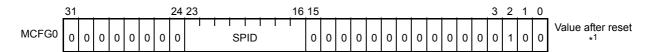

The program being executed belongs to the group shown by MCFG0.SPID, and whether the memory resources and peripheral devices are operable is decided using this SPID. Any value can be set to MCFG0.SPID by the supervisor.

#### **CAUTION**

According to the value of MCFG0.SPID, how operations are assigned to memory resources and peripheral devices is determined by the hardware specifications.

## Section 3 REGISTER SET

This chapter describes the program register and system register mounted on this CPU.

## 3.1 Program Registers

Program registers includes general-purpose registers (r0 to r31) and the program counter (PC). r0 always retains 0, whereas the value after reset is undefined in r1 to r31.

Table 3.1 Program Registers

| Program Register   | Name      | Function                                                                                             | Description                                                                                      |  |

|--------------------|-----------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| General-purpose    | r0        | Zero register                                                                                        | Always retains 0                                                                                 |  |

| registers          | r1        | Assembler reserved register                                                                          | Used as working register for generating addresses                                                |  |

|                    | r2        | Register for address and data variables (used when the real-time OS used does not use this register) |                                                                                                  |  |

|                    | r3        | Stack pointer (SP)                                                                                   | Used for generating a stack frame when a function is called                                      |  |

|                    | r4        | Global pointer (GP)                                                                                  | Used for accessing a global variable in the data area                                            |  |

|                    | r5        | Text pointer (TP)                                                                                    | Used as a register that indicates the start of the text area (area where program code is placed) |  |

|                    | r6 to r29 | Register for addresses and data variables                                                            |                                                                                                  |  |

|                    | r30       | Element pointer (EP)                                                                                 | Used as a base pointer for generating addresses when accessing memory                            |  |

|                    | r31       | Link pointer (LP)                                                                                    | Used when the compiler calls a function                                                          |  |

| Program counter PC |           | Retains instruction addresses during execution of programs                                           |                                                                                                  |  |

**Note:** For further descriptions of r1, r3 to r5, and r31 used for an assembler and/or C compiler, see the manual of each software development environment.

# 3.1.1 General-Purpose Registers

A total of 32 general-purpose registers (r0 to r31) are provided. All of these registers can be used for either data variables or address variables.

Of the general-purpose registers, r0 to r5, r30, and r31 are assumed to be used for special purposes in software development environments, so it is necessary to note the following when using them.

#### (a) r0, r3, and r30

These registers are implicitly used by instructions.

r0 is a register that always retains 0. It is used for operations that use 0, addressing with base address being 0, etc.

r3 is implicitly used by the PREPARE, DISPOSE, PUSHSP, and POPSP instructions.

r30 is used as a base pointer when the SLD instruction or SST instruction accesses memory.

#### (b) r1, r4, r5, and r31

These registers are implicitly used by the assembler and C compiler.

When using these registers, register contents must first be saved so they are not lost and can be restored after the registers are used.

#### (c) r2

This register is used by a real-time OS in some cases. If the real-time OS that is being used is not using r2, r2 can be used as a register for address variables or data variables.

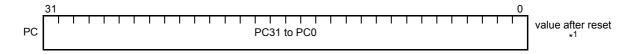

# 3.1.2 PC — Program Counter

The PC retains the address of the instruction being executed.

Table 3.2 PC Register Contents

| Bit     | Name        | Description                                                             | R/W | Value after<br>Reset |

|---------|-------------|-------------------------------------------------------------------------|-----|----------------------|

| 31 to 1 | PC31 to PC1 | These bits indicate the address of the instruction being executed.      | R/W | *1                   |

| 0       | PC0         | This bit is fixed to 0. Branching to an odd number address is disabled. | R/W | 0                    |

Note 1. For details, see the hardware manual of the product used.

# 3.2 Basic System Registers

The basic system registers are used to control CPU status and to retain exception information.

Basic system registers are read from or written to by using the LDSR and STSR instructions and specifying the system register number, which is made up of a register number and selection ID.

Table 3.3 Basic System Registers

|                             | Busic Cystem it |                                                             |                   |

|-----------------------------|-----------------|-------------------------------------------------------------|-------------------|

| Register No. (regID, seIID) | Symbol          | Function                                                    | Access Permission |

| SR0, 0                      | EIPC            | Status save registers when acknowledging El level exception | SV                |

| SR1, 0                      | EIPSW           | Status save registers when acknowledging El level exception | SV                |

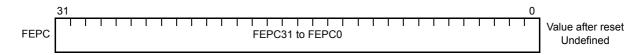

| SR2, 0                      | FEPC            | Status save registers when acknowledging FE level exception | SV                |

| SR3, 0                      | FEPSW           | Status save registers when acknowledging FE level exception | SV                |

| SR5, 0                      | PSW             | Program status word                                         | *1                |

| SR6, 0                      | FPSR            | (See Section 3.4, FPU Function Registers)                   | CU0 and SV        |

| SR7, 0                      | FPEPC           | (See Section 3.4, FPU Function Registers)                   | CU0 and SV        |

| SR8, 0                      | FPST            | (See Section 3.4, FPU Function Registers)                   | CU0               |

| SR9, 0                      | FPCC            | (See Section 3.4, FPU Function Registers)                   | CU0               |

| SR10, 0                     | FPCFG           | (See Section 3.4, FPU Function Registers)                   | CU0               |

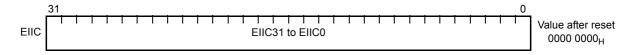

| SR13, 0                     | EIIC            | El level exception cause                                    | SV                |

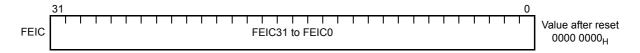

| SR14, 0                     | FEIC            | FE level exception cause                                    | SV                |

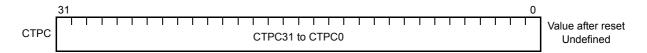

| SR16, 0                     | CTPC            | CALLT execution status save register                        | UM                |

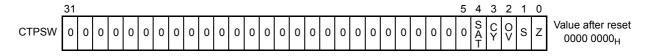

| SR17, 0                     | CTPSW           | CALLT execution status save register                        | UM                |

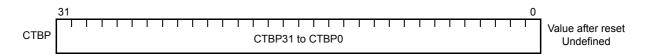

| SR20, 0                     | СТВР            | CALLT base pointer                                          | UM                |

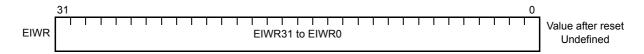

| SR28, 0                     | EIWR            | El level exception working register                         | SV                |

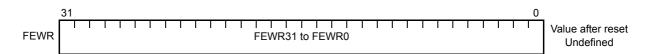

| SR29, 0                     | FEWR            | FE level exception working register                         | SV                |

| SR31, 0                     | (BSEL)          | (Reserved for backward compatibility with V850E2 series)*2  | SV                |

| SR0, 1                      | MCFG0           | Machine configuration                                       | SV                |

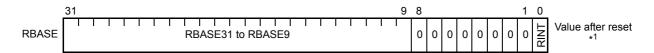

| SR2, 1                      | RBASE           | Reset vector base address                                   | SV                |

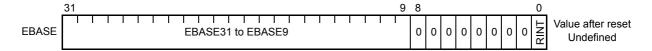

| SR3, 1                      | EBASE           | Exception handler vector address                            | SV                |

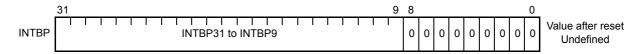

| SR4, 1                      | INTBP           | Base address of the interrupt handler table                 | SV                |

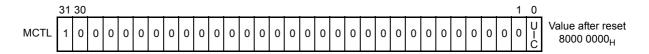

| SR5, 1                      | MCTL            | CPU control                                                 | SV                |

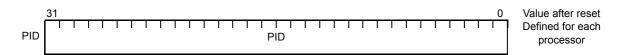

| SR6, 1                      | PID             | Processor ID                                                | SV                |

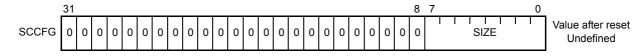

| SR11, 1                     | SCCFG           | SYSCALL operation setting                                   | SV                |

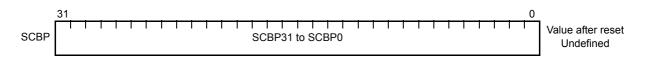

| SR12, 1                     | SCBP            | SYSCALL base pointer                                        | SV                |

| SR0, 2                      | HTCFG0          | Thread configuration                                        | SV                |

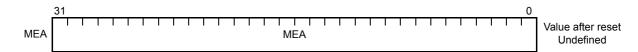

| SR6, 2                      | MEA             | Memory error address                                        | SV                |

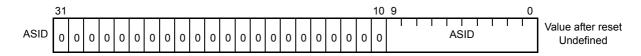

| SR7, 2                      | ASID            | Address space ID                                            | SV                |

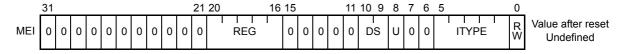

| SR8, 2                      | MEI             | Memory error information                                    | SV                |

- Note 1. The access permission differs depending on the bit. For details, see (5), PSW Program status word in Section 3.2, Basic System Registers.

- Note 2. This bit is reserved to maintain backward compatibility with V850E2 series. This bit is always 0 when read. Writing to this bit is ignored.

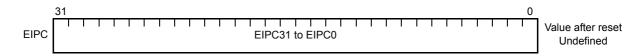

## (1) EIPC — Status save register when acknowledging EI level exception

When an EI level exception is acknowledged, the address of the instruction that was being executed when the EI level exception occurred, or of the next instruction, is saved to the EIPC register (see **Section 4.1.3, Types of Exceptions**).

Because there is only one pair of EI level exception status save registers, when processing multiple exceptions, the contents of these registers must be saved by a program.

Be sure to set an even-numbered address to the EIPC register. An odd-numbered address must not be specified.

Table 3.4 EIPC Register Contents

| Bit     | Name               | Description                                                                                                                                                                                                | R/W | Value after<br>Reset |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|

| 31 to 1 | EIPC31 to<br>EIPC1 | These bits indicate the PC saved when an El level exception is acknowledged.                                                                                                                               | R/W | Undefined            |

| 0       | EIPC0              | This bit indicates the PC saved when an EI level exception is acknowledged. Always set this bit to 0. Even if it is set to 1, the value transferred to the PC when the EIRET instruction is executed is 0. | R/W | Undefined            |

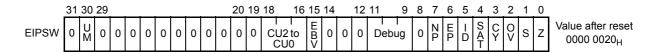

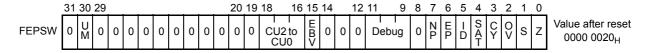

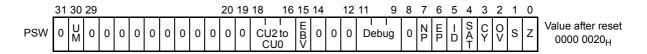

#### (2) EIPSW — Status save register when acknowledging EI level exception

When an EI level exception is acknowledged, the current PSW setting is saved to the EIPSW register.

Because there is only one pair of EI level exception status save registers, when processing multiple exceptions, the contents of these registers must be saved by a program.

#### **CAUTION**

Bits 11 to 9 are related to the debug function and therefore cannot normally be changed.

Table 3.5 EIPSW Register Contents

| Bit      | Name       | Description                                                                                                                                              | R/W | Value after<br>Reset |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|

| 31       | _          | (Reserved for future expansion. Be sure to set to 0.)                                                                                                    | R   | 0                    |

| 30       | UM         | This bit stores the PSW.UM bit setting when an EI level exception is acknowledged.                                                                       | R/W | 0                    |

| 29 to 19 | _          | (Reserved for future expansion. Be sure to set to 0.)                                                                                                    | R   | 0                    |

| 18 to 16 | CU2 to CU0 | These bits store the PSW.CU2-0 field setting when an EI level exception is acknowledged. (CU2-1 are reserved for future expansion. Be sure to set to 0.) | R/W | 0                    |

| 15       | EBV        | This bit stores the PSW.EBV bit setting when an EI level exception is acknowledged.                                                                      | R/W | 0                    |

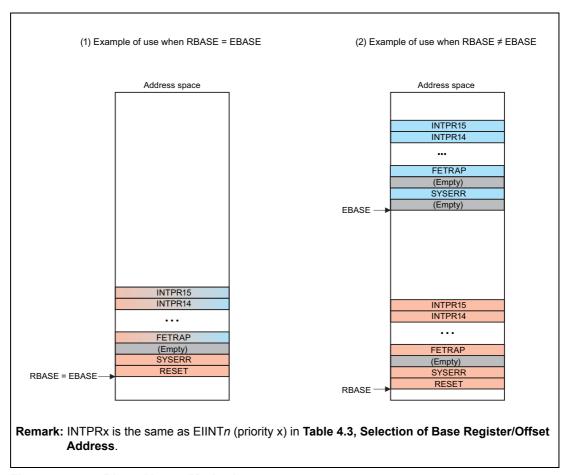

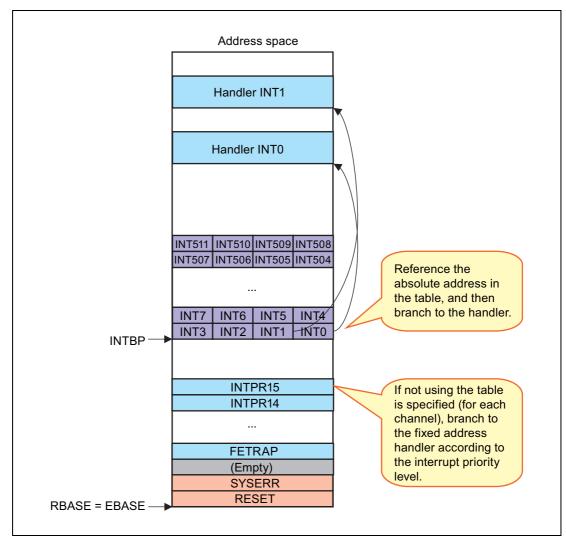

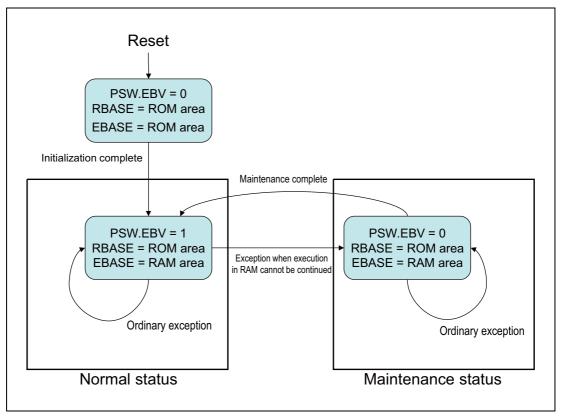

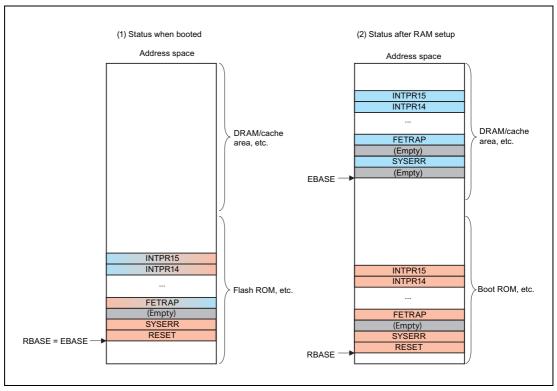

| 14 to 12 | _          | (Reserved for future expansion. Be sure to set to 0.)                                                                                                    | R   | 0                    |