# **Supplemental Information**

This Document Errata reflects changes made on the datasheet for device 854S006l.

# **Revision History**

January 27, 2010: First version of documentation errata for this device. There is no change to the actual

characteristics or design of the device. This is only a change to the datasheet to correct a datasheet error.

a datastieet erro

## **Errata Items**

PAGE DESCRIPTION OF CHANGE

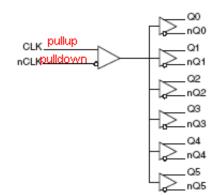

Page 1 Block Diagram. Update Pullup and Pulldown of CLK and nCLK on the block

diagram

#### **FROM**

## **BLOCK DIAGRAM**

#

## TO

# **BLOCK DIAGRAM**

## Page 2 Table 1. Pin Descriptions

Update the Pullup and Pulldown on CLK and nCLK under column type in Table 1. (Illustrated in Page 2)

### Page 3 Table 4C. Differential DC Characteristics

Update the spec for input leakage current to reflect correct Pullup and Pulldown pins and Sage process. (Illustrated in Page 2)

#### **FROM**

TABLE 1. PIN DESCRIPTIONS

| Numbe | r Na | me | Type  |          | Description                             |

|-------|------|----|-------|----------|-----------------------------------------|

| 1     | nC   | LK | Input | Pullup   | Inverting differential clock input.     |

| 2     | С    | LK | Input | Pulldown | Non-inverting differential clock input. |

Table 4C. Differential DC Characteristics,  $V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ , Ta = -40°C to  $85^{\circ}$ C

| Symbol          | Parameter          |      | Test Conditions                                        | Minimum | Typical | Maximum | Units |

|-----------------|--------------------|------|--------------------------------------------------------|---------|---------|---------|-------|

| I <sub>IH</sub> | Input High Current | CLK  | $V_{DD} = V_{IN} = 3.465V$<br>or 2.625V                |         |         | 150     | μA    |

|                 |                    | nCLK | $V_{DD} = 3.465V \text{ or } 2.625V,$<br>$V_{IN} = 0V$ |         |         | 5       | μA    |

| I <sub>IL</sub> | Input Low Current  | CLK  | $V_{DD} = V_{IN} = 3.465V$<br>or 2.625V                | ų       |         |         | μΑ    |

|                 |                    | nCLK | $V_{DD} = 3.465V \text{ or } 2.625V,$<br>$V_{IN} = 0V$ | -150    |         |         | μΑ    |

#### TO:

TABLE 1. PIN DESCRIPTIONS

| Number | Name | Туре  |          | Description                             |

|--------|------|-------|----------|-----------------------------------------|

| 1      | nCLK | Input | pulldown | Inverting differential clock input.     |

| 2      | CLK  | Input | pullup   | Non-inverting differential clock input. |

Table 4C. Differential DC Characteristics,  $V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ , Ta = -40°C to  $85^{\circ}$ C

| Symbol          | Parameter          |      | Test Conditions                                        | Minimum | Typical | Maximum | Units |

|-----------------|--------------------|------|--------------------------------------------------------|---------|---------|---------|-------|

| I <sub>IH</sub> | Input High Current | nCLK | $V_{DD} = V_{IN} = 3.465V$<br>or 2.625V                |         |         | 150     | μΑ    |

|                 |                    | CLK  | $V_{DD} = 3.465V \text{ or } 2.625V,$<br>$V_{IN} = 0V$ |         |         | 10      | μΑ    |

| I <sub>IL</sub> | Input Low Current  | nCLK | $V_{DD} = V_{IN} = 3.465V$<br>or 2.625V                | -10     |         |         | μΑ    |

|                 |                    | CLK  | $V_{DD} = 3.465V \text{ or } 2.625V,$<br>$V_{IN} = 0V$ | -150    |         |         | μΑ    |